**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

H01P 1/20

(45) 공고일자 1999년06월15일

(11) 등록번호 10-0192634

(24) 등록일자 1999년01월29일

|            |                         |           |                |

|------------|-------------------------|-----------|----------------|

| (21) 출원번호  | 10-1995-0041705         | (65) 공개번호 | 특 1996-0019845 |

| (22) 출원일자  | 1995년11월16일             | (43) 공개일자 | 1996년06월17일    |

| (30) 우선권주장 | 1994-309995 1994년11월17일 | 일본(JP)    |                |

|           |                                                                                                                                                                                                     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 특허권자 | 가부시끼가이사 무라따 세이사꾸쇼 무라따 야스따까<br>일본국 교오또후 나가오까꼬시 덴진 2죠메 26방 10고                                                                                                                                        |

| (72) 발명자  | 오카다 다케카즈<br>일본국 교오또후 나가오까꼬시 덴진 2죠메 26방 10고 가부시끼가이사 무라따<br>세이사꾸쇼<br>신무라 사토루<br>일본국 교오또후 나가오까꼬시 덴진 2죠메 26방 10고 가부시끼가이사 무라따<br>세이사꾸쇼<br>가나야 후미오<br>일본국 교오또후 나가오까꼬시 덴진 2죠메 26방 10고 가부시끼가이사 무라따<br>세이사꾸쇼 |

| (74) 대리인  | 윤동열, 이선희                                                                                                                                                                                            |

**심사관 : 이득한**

**(54) 원판상의 정자파 장치**

**요약**

본 발명은 소형화 및 저가격화를 꾀할 수 있는, S/N 강화기, 필터 등의 정자파 장치를 제공하는 것이다. 본 발명의 한 측면에 따른 정자파 장치는, 폐리자성 베이스; 전기한 폐리자성 베이스의 한쪽 측면(제1주면)측에 배치된 부분과, 전기한 폐리자성 베이스의 다른쪽 주면(제2주면)측에 배치된 부분을 갖는 트랜스듀서; 한쪽 말단은 전기한 트랜스듀서의 한쪽 말단에 접속되고, 다른 쪽 말단은 접지되어 있는 입력단자; 및 한쪽 말단은 전기한 트랜스듀서의 다른 쪽 말단에 접속되고, 다른 쪽 말단은 접지되어 있는 출력단자를 포함함을 특징으로 한다. 또한, 본 발명의 다른 측면에 따른 정자파 장치는, 폐리자성 베이스; 전기한 폐리자성 베이스의 제1주면 측에 배치된 부분과, 전기한 폐리자성 베이스의 제2주면 측에 배치된 부분을 갖는 제1트랜스듀서, 전기한 폐리자성 베이스의 제2주면 측에 배치된 부분과, 전기한 폐리자성 베이스의 제1주면 측에 배치된 부분을 갖는 제2트랜스듀서; 한쪽 말단은 전기한 제1트랜스듀서의 한쪽 말단에 접속되고, 다른 쪽 말단은 전기한 제2트랜스듀서의 한쪽 말단에 접속되어 있는 입력단자; 및 한쪽 말단은 전기한 제1트랜스듀서의 다른 쪽 말단에 접속되고, 다른 쪽 말단은 전기한 제2트랜스듀서의 다른 쪽 말단에 접속되어 있는 출력단자를 포함함을 특징으로 한다.

## 대표도

## 명세서

### [발명의 명칭]

원판상의 정자파(靜磁波) 장치

### [도면의 간단한 설명]

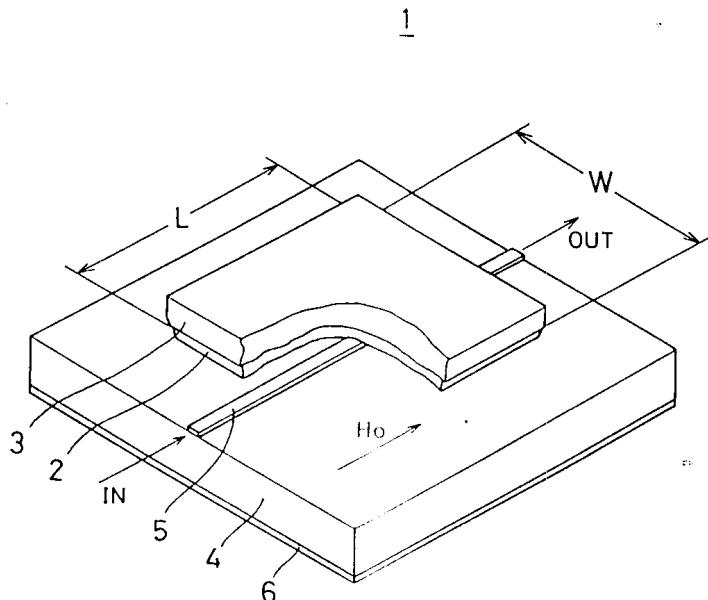

제1도는 종래의 S/N 강화기(S/N enhancer)의 전형적인 예를 보여주는 사시도이다.

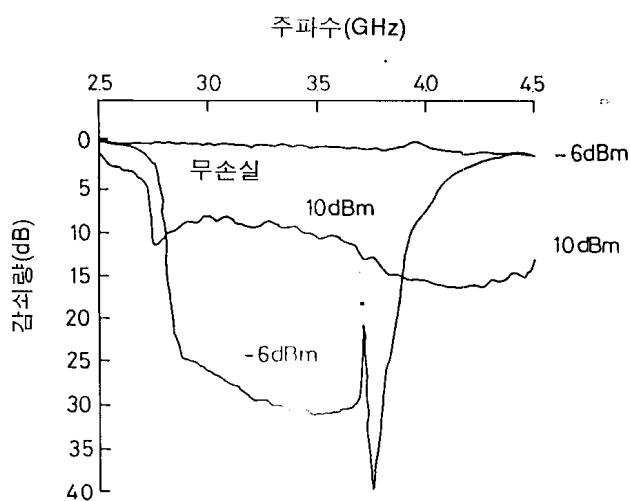

제2도는 제1도에 나타낸 종래의 S/N 강화기의 주파수 특성을 보여주는 그래프이다.

제3도는 제1도에 나타낸 종래의 S/N 강화기의 입/출력 특성을 보여주는 그래프이다.

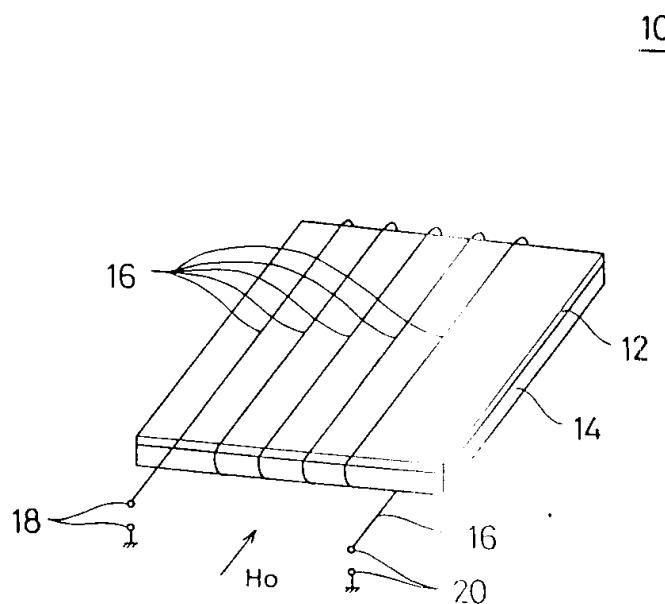

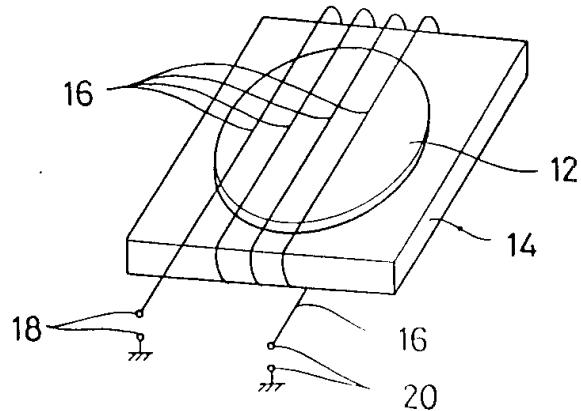

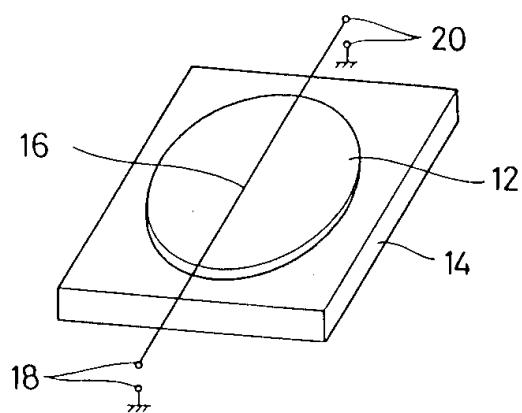

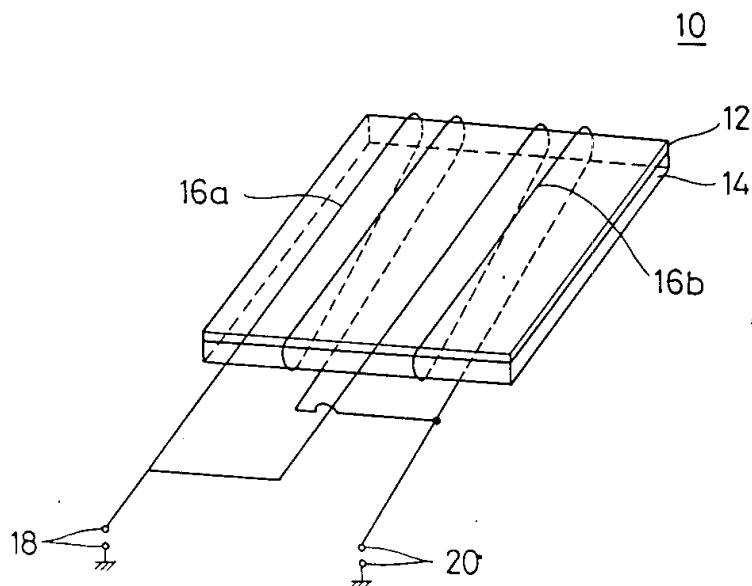

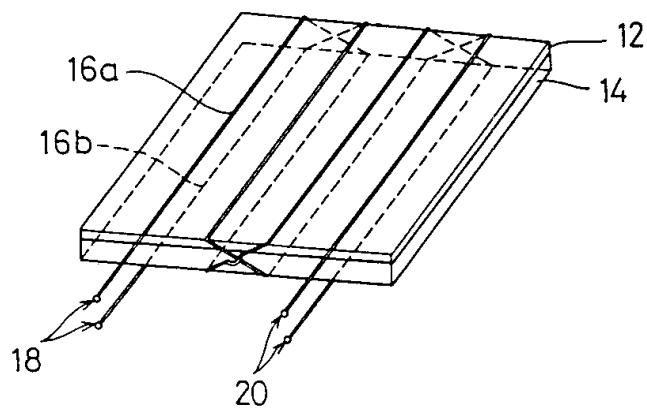

제4도는 본 발명의 실시예에 따른 S/N 강화기를 보여주는 사시도이다.

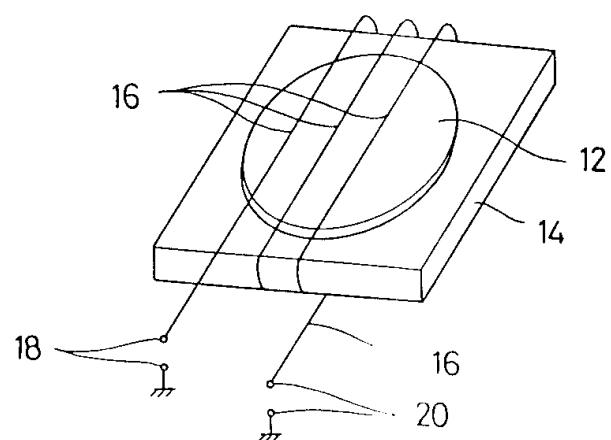

제5도는 본 발명의 변형예에 따른 S/N 강화기를 보여주는 사시도이다.

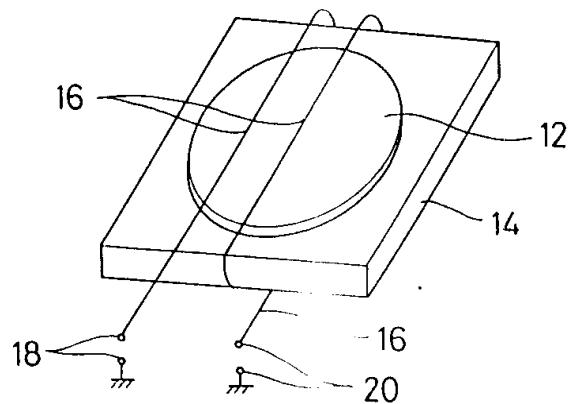

제6도는 본 발명의 다른 변형예에 따른 S/N 강화기를 보여주는 사시도이다.

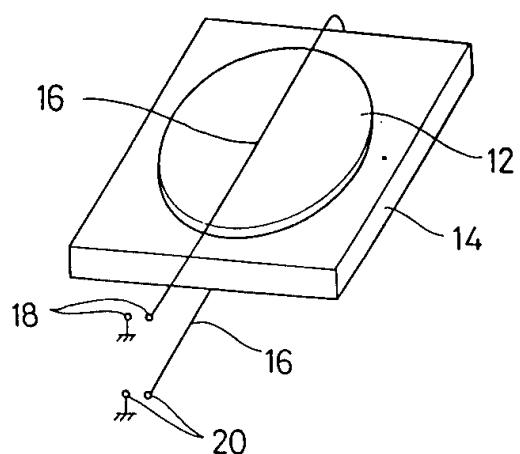

제7도는 본 발명의 또 다른 변형예에 따른 S/N 강화기를 보여주는 사시도이다.

제8도는 본 발명의 또 다른 변형예에 따른 S/N 강화기를 보여주는 사시도이다.

제9도는 비교예를 보여주는 사시도이다.

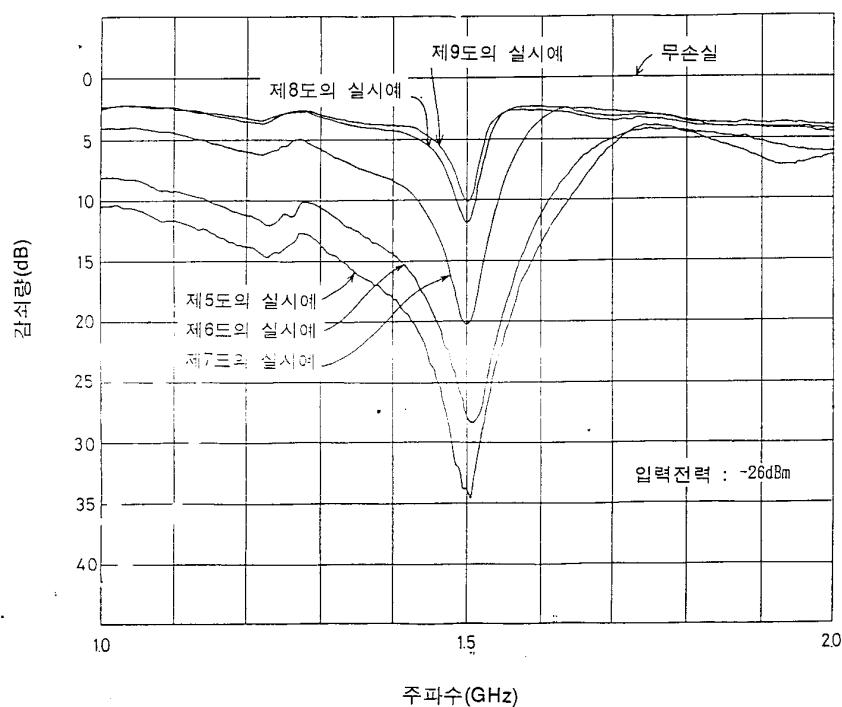

제10도는 제5도 내지 제8도에 나타낸 각각의 실시예와 제9도에 나타낸 비교예에 대한 주파수 특성을 보여주는 그래프이다.

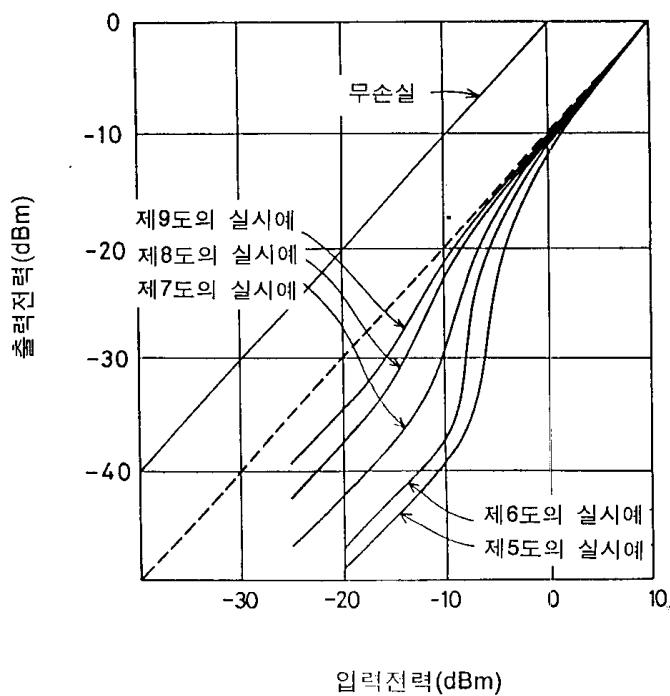

제11도는 제5도 내지 제8도에 나타낸 각각의 실시예와 제9도에 나타낸 비교예에 대한 입/출력 특성을 보여주는 그래프이다.

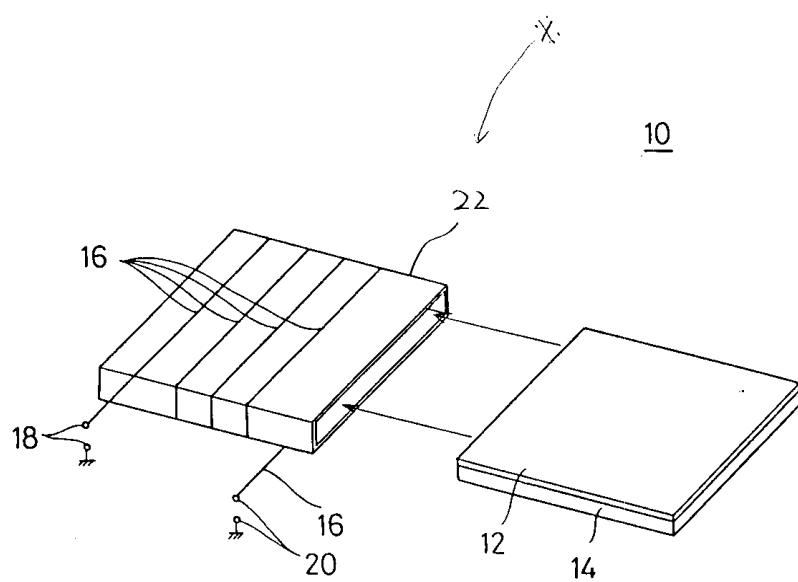

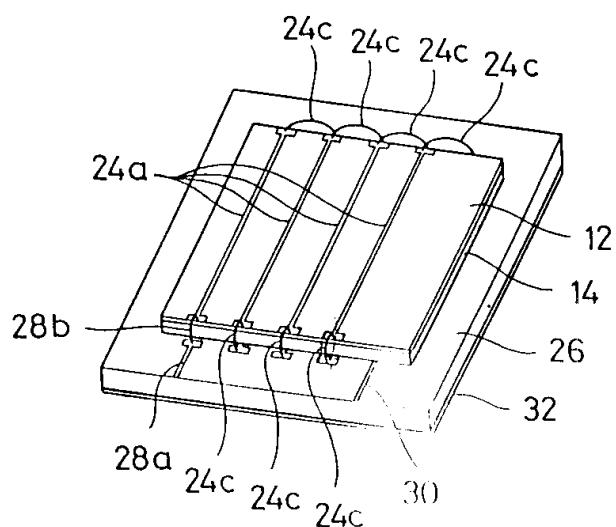

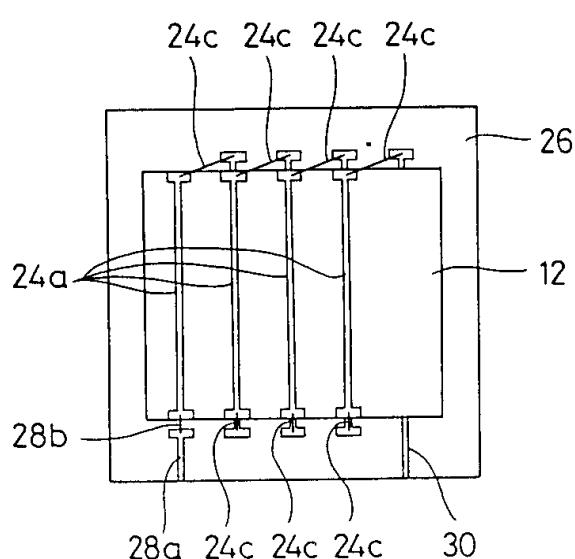

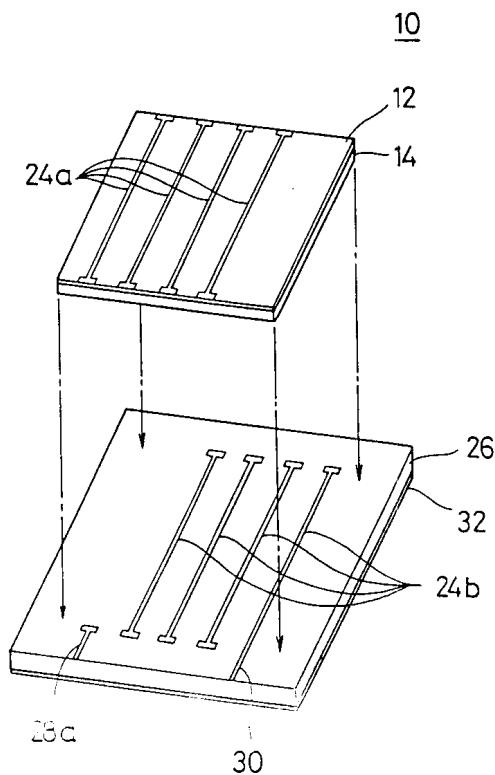

제12도는 본 발명의 다른 실시예에 따른 S/N 강화기를 보여주는 분해사시도이다.

제13도는 본 발명의 또 다른 실시예에 따른 S/N 강화기를 보여주는 분해 사시도이다.

제14도는 제13도의 S/N 강화기를 보여주는 평면도이다.

제15도는 제13도의 S/N 강화기의 요부를 보여주는 분해 사시도이다.

제16도는 본 발명의 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다.

제17도는 본 발명의 또 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다.

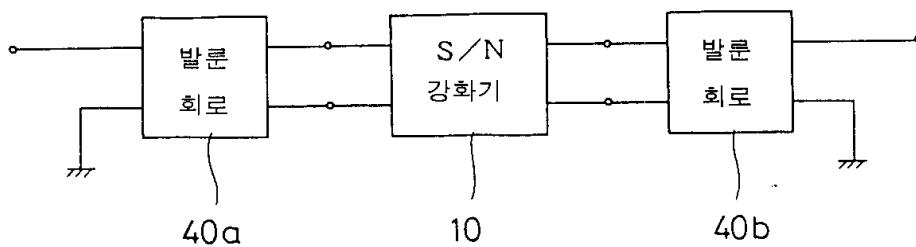

제18도는 제17도에 나타낸 S/N 강화기의 응용예를 보여주는 블록도이다.

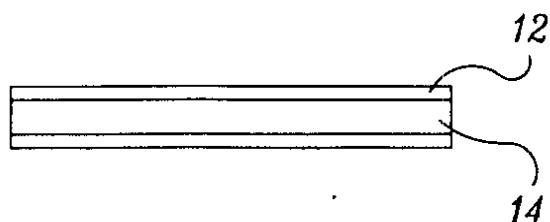

제19a도, 제19b도는 제4도, 제12도~제17도 및 제5도~제8도에 나타낸 각각의 실시예의 변형예에 따른 YIG 박막 12와 GGG 기판 14를 보여주는 측면도이다.

\* 도면의 주요부분에 대한 부호의 설명

10 : S/N 강화기

12 : YIG 박막

|                       |                 |

|-----------------------|-----------------|

| 14 : GGG 기판           | 16, 16a : 트랜스듀서 |

| 16b : 제2트랜스듀서         | 18 : 입력단자       |

| 20 : 출력단자             | 22 : 케이스        |

| 24a, 24b : 선(line) 전극 | 24c : 도선        |

| 26 : 유전체 기판           | 28a : 단자전극      |

| 28b : 도선              | 30 : 다른 쪽 말단    |

| 32 : 접지전극             |                 |

### [발명의 상세한 설명]

본 발명은 정자파(靜磁波; magnetostatic wave) 장치에 관한 것이다. 더욱 상세하게는 본 발명은 S/N 강화기(S/N enhancer)와 필터로서 작용하는 페리자성(ferrimagnetic) 베이스(base; 基體)를 사용한 정자파 장치에 관한 것이다.

본 발명의 배경 기술이 되는 종래의 S/N 강화기의 일례는, 1980 IEEE TRANSACTIONS ON MAGNETICS, Vol. MAG-16, pp1168~1170의 A BROADBAND MICROWAVE SIGNAL TO NOISE ENHANCED(광대역 전자파 신호 대 잡음비 강화기), 및 미국특허 4,283,692에 개시된 것이다. 제1도는 이러한 전형적인 S/N 강화기를 보여주는 사시도이다. 제1도에 나타낸 S/N 강화기 1은 페리자성 베이스로서 사각판 상의 YIG 박막 2를 포함하고 있다. 이 YIG 박막 2는 사각판상의 GGG 기판 3의 한쪽 주면에 형성된다. YIG 박막 2의 표면은 사각판 상의 유전체 기판 4의 한쪽 주면의 중앙에 접착된다. 이 유전체 기판 4의 한쪽 주면에는, 그의 폭방향으로 중앙에, 트랜스듀서(transducer)로서 직선상의 마이크로스트립 라인(microstrip line) 5가, YIG 박막 2를 교차하도록 형성된다. 마이크로스트립 라인 5의 한쪽 말단에는, 입력단자(도시하지 않았음)의 한쪽 말단이 접속되고, 마이크로스트립 라인 5의 다른 쪽 말단에는, 출력단자(도시하지 않았음)의 한쪽 말단이 접속된다. 또 유전체 기판 4의 다른 쪽 주면에는 접지전극 6이 형성되어 있다. 입력단자의 다른 쪽 말단과 출력단자의 다른 쪽 말단은 각각 접지된다.

제1도에 나타낸 S/N 강화기 1에서는, 페리자성 베이스로서의 YIG 박막 2에, 직류자계(DC 자계)  $H_0$ 가 마이크로스트립 라인 5의 길이방향으로 인가된다. 그리고, 이 S/N 강화기 1에는, 입력단자에 고주파 전력(RF 전력)을 입력하면 마이크로스트립라인 5의 주위에 고주파 자계(RF magnetic field; RF 자계)가 발생하고, YIG 박막 2 내에 정자파의 세(3) 모드(mode) 중의 하나인 표면 정자파(MSSW; magnetostatic surface wave)가 여진된다. 입력단자에 입력된 RF 전력이 작은 경우에는, RF 전력의 대부분이 정자파로 변환되기 때문에, 출력단자로부터 얻을 수 있는 출력 전력은 비교적 작다. 한편, 입력단자에 입력된 RF 전력이 클 경우에는, RF 전력의 정자파에로의 변환이 포화되기 때문에, RF 전력의 대부분이 마이크로스트립라인 5를 통하여 출력단자로부터 얻어진다. 따라서, 이런 S/N 강화기 1에는, 입력전력이 작은 잡음(noise) 성분은 거의 출력되지 않으며, 입력 전력이 큰 신호(signal) 성분은 출력된다. 그러므로, 이런 S/N 강화기 1에서는 신호-대-잡음 비(S/N ratio; signal-to-noise ratio)가 증가될 수 있다. S/N 강화기 1에 있어서,  $-6\text{dBm}$  및  $10\text{dBm}$ 에서의 주파수 특성은 제2도에 나타내었고,  $3.3\text{GHz}$ 의 입출력 특성을 제3도에 나타내었다.

제1도에 나타낸 S/N 강화기 1에서는, 페리자성 베이스로서의 YIG 박막 2와, 트랜스듀서로서의 마이크로스트립라인 5와의 대향하는 부분의 길이  $L$ 에 의해, 잡음의 감쇠량을 결정한다. S/N 강화기 1에서, 길이  $L$ 은  $2.1\text{cm}$ 이다. 또, S/N 강화기 1에 있어서, 잡음의 감쇠량을 증가시키는 경우, 이 길이  $L$ 을 증가시키는 것이 효과적이다. 그러나, 이런 경우, 고가의 페리자성 베이스, 즉 YIG 박막의 크기가 커지는 문제가 발생한다. 환연하면, S/N 강화기 1에서, 소형화 및 저가격화를 도모하기 위해 YIG 박막 2를 작게 형성하는 경우, YIG 박막 2와 마이크로스트립라인 5와의 대향하는 부분의 길이  $L$ 은 짧아지며, 따라서 잡음의 감쇠량은 작아지게 된다.

또한, 제1도의 S/N 강화기 1에서, 변환된 정자파는 마이크로스트립라인 5에서 YIG 박막 2의 단부로부터 반사되며, 그런 다음 반사된 정자파는 마이크로스트립라인 5와 같은 S/N 강화기 1의 부품에 의해 RF 전력으로 변환된다. 이와 같이 반사된 정자파가 존재하는 경우, 정자파는 S/N 강화기 1의 전송 대역 내에서 진폭과 위상의 리플(ripple) 성분으로 나타날 수 있다. 결과적으로, 이런 S/N 강화기 1에서는, 정자파의 반사량을 감소시키기 위해서, 정자파의 전파방향으로의 길이, 즉 YIG 박막 2의 폭  $W$ 를 증가시켜야 하며, YIG 박막 2의 단부에 정자파 흡수체를 설치하여야 하는 등이 요구되는 경우도 있다.

이에, 본 발명은 상기한 문제점들을 해소하기 위한 것이며, 본 발명의 주된 목적은 소형화 및 저가격화를 꾀할 수 있는 정자파 장치를 제공하는 것이다.

이러한 목적을 달성하기 위하여, 본 발명의 한 측면에 따른 정자파 장치는, 페리자성 베이스; 전기한 페리자성 베이스의 한쪽 주면(제1주면)측에 배치된 부분과, 전기한 페리자성 베이스의 다른 쪽 주면(제2주면)측에 배치된 부분을 갖는 트랜스듀서; 한쪽 말단이 전기한 트랜스듀서의 한쪽 말단에 접속되고, 다른 쪽 말단은 접지되어 있는 입력단자; 및 한쪽 말단이 전기한 트랜스듀서의 다른 쪽 말단에 접속되고, 다른 쪽 말단은 접지되어 있는 출력단자를 포함함을 특징으로 한다.

본 발명에 따른 정자파 장치에 있어서, 전기한 페리자성 베이스는 원판상(disk shape)으로 형성되는 것이 바람직하며, 이에 대해서는 후술한다.

또한, 본 발명에 따른 정자파 장치는, 전기한 페리자성 베이스의 제1주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제2주면 측에 배치된 부분을 갖고, 전기한 트랜스듀서와 병렬 접속되는 제2트랜스듀서를 더 포함하는 것이 바람직하며, 이에 대해서는 후술한다.

본 발명의 다른 측면에 따른 다른 정자파 장치는, 페리자성 베이스; 전기한 페리자성 베이스의 제1주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제2주면 측에 배치된 부분을 갖는 제1트랜스듀서; 전기한 페리자성 베이스의 제2주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제1주면 측에 배치된 부분을

갖는 제2트랜스듀서; 한쪽 말단이 전기한 제1트랜스듀서의 한쪽 말단에 접속되고, 다른 쪽 말단은 전기한 제2트랜스듀서의 한쪽 말단에 접속되어 있는 입력단자; 및 한쪽 말단이 전기한 제1트랜스듀서의 다른 쪽 말단에 접속되고, 다른 쪽 말단은 전기한 제2트랜스듀서의 다른 쪽 말단에 접속되어 있는 출력단자를 포함할을 틀진으로 한다.

본 발명에 따른 정자파 장치에 있어서, 진기한 폐리자성 베이스는 원판상으로 형성되는 것이 바람직하며, 이에 대해서는 후술한다.

본 발명에 따른 정자파 장치에서는, 페리자성 베이스에 DC 자계를 인가하고 입력단자에 RF 전력을 입력하면, 트랜스듀서 주위에 RF 자계가 발생하고, 이에 의해 페리자성 베이스에서 정자파가 여진된다. 입력단자에 입력된 RF 전력이 작은 경우에는, RF 전력은 정자파로 변환된다. 트랜스듀서가 페리자성 베이스의 제1주면 측에 배치된 부분과 페리자성의 제2주면 측에 배치된 부분을 포함하고 있기 때문에, RF 전력에서 정자파로의 변환효율은 커진다. 따라서, 페리자성 베이스를 작게 형성하였을 때에도, 종래예와 동일한 정도의 잡음 감쇠량(noise attenuation amount)을 얻을 수 있다. 한편, 입력단자로 입력된 RF 전력이 큰 경우에는, RF 전력에서 정자파로의 변환이 포화되기 때문에, 입력된 RF 전력의 대부분이 트랜스듀서를 통해 출력단자로부터 얻어진다. 그러므로, 본 발명에 따른 정자파 장치에서는, 입력전력이 작은 잡음 성분(noise component)은 거의 출력되지 않으며, 반면, 입력전력이 큰 신호 성분(signal component)은 대부분 출력된다. 환언하면, 본 발명에 따른 정자파 장치에서는, 신호-대-잡음(S/N) 비가 커진다.

또, 본 발명에 따른 다른 정자파 장치에서는, 페리자성 베이스에 DC 자계를 인가하고, 입력단자에 RF 전력(고주파 전력)을 입력하면, 제1트랜스듀서 및 제2트랜스듀서의 주위에 RF 자계(고주파 자계)가 발생하며, 페리자성 베이스 내에 정자파가 여진된다. 입력단자에 입력된 RF 전력이 작은 경우에는, RF 전력은 정자파로 변환된다. 제1트랜스듀서가 페리자성 베이스의 제1주면 측에 배치된 부분과 페리자성의 제2주면 측에 배치된 부분을 포함하고 있고, 제2트랜스듀서가 페리자성 베이스의 제2주면 측에 배치된 부분과 페리자성의 제1주면 측에 배치된 부분을 포함하고 있기 때문에, RF 전력에서 정자파로의 변환효율은 커진다. 따라서, 페리자성 베이스를 작게 형성하였을 때에도, 종래에와 동일한 정도의 잡음 감쇠량을 얻을 수 있다. 한편, 입력단자로 입력된 RF 전력이 큰 경우에는, RF 전력에서 정자파로의 변환이 포화되기 때문에, 입력된 RF 전력의 대부분이 제1트랜스듀서 및 제2트랜스듀서를 통해 출력단자로부터 얻어진다. 그러므로, 본 발명에 따른 정자파 장치에서는, 입력전력이 작은 잡음 성분은 거의 출력되지 않으며, 반면, 입력전력이 큰 신호 성분은 대부분 출력된다. 환언하면, 본 발명에 따른 정자파 장치에서는, 신호-대-잡음(S/N) 비가 커진다.

본 발명에 의하면, RF 전력에서 정자파로의 변환효율이 향상되며, 소형화 및 저가격화를 꾼할 수 있는 정자파 장치를 얻을 수 있다.

또한, 본 발명에 따른 정자파 장치에서는, 페리자성 베이스를 원판상으로 형성함으로써, 변환된 정자파가 페리자성 베이스의 단부로부터 트랜스듀서 측에 반사되는 것을 방지할 수 있다. 따라서, 페리자성 베이스의 단부로부터 반사된 정자파가 트랜스듀서와 같은 정자파 장치의 부품에 의해 RF 전력으로 변환되는 일은 거의 없다. 그러므로, 정자파 장치의 전송대역 내에서의 진폭/위상 리플 성분은 줄어들고, 얻어지는 특성은 향상된다. 또, 본 발명에 따른 다른 정자파 장치에서도 페리자성 베이스를 원판상으로 형성함으로써, 동일한 효과를 얻을 수 있다.

또, 본 발명에 따른 정자파 장치에서는, 페리자성 베이스의 제1주면 측에 배치된 부분과, 페리자성 베이스의 제2주면 측에 배치된 부분을 가지며, 제1트랜스듀서에 병렬 접속된 제2트랜스듀서를 더 포함하고, 제1트랜스듀서와 제2트랜스듀서를 입력단자와 출력단자 사이에 병렬로 접속시킴으로써, 입력단자와 출력단자 사이의 임피던스를 감소시키고, 삽입손실을 감쇠시킬 수 있다.

또한, 본 발명에 따른 다른 정자파 장치는, 페리자성 베이스의 제1주면 측에 배치된 부분과, 페리자성 베이스의 제2주면 측에 배치된 부분을 포함하는 제1트랜스듀서와; 페리자성 베이스의 제2주면 측에 배치된 부분과, 페리자성 베이스의 제1주면 측에 배치된 부분을 포함하는 제2트랜스듀서를 포함하고 있다. 또한, 입력단자의 한쪽 말단과 다른 쪽 말단이 제1트랜스듀서의 한쪽 말단과 제2트랜스듀서의 한쪽 말단에 각기 접속되어 있고; 출력단자의 한쪽 말단과 다른 쪽 말단이 제1 트랜스듀서의 다른 쪽 말단과 제2트랜스듀서의 다른 쪽 말단에 각기 접속되어 있다. 환언하면, 입력단자와 출력단자가 피더(feeder)에 의해 서로 접속된 경우와 같이, 두개의 트랜스듀서에 의해 서로 병렬로 접속된 상태로 되어 있기 때문에, 잡음의 감쇠량을 증가시키기 위하여 제1트랜스듀서와 제2트랜스듀서 사이의 거리를 길게 하여도, 입력단자와 출력단자 사이에서의 임피던스는 거의 변하지 않으며, 따라서 삼입손실은 커지지 않는다.

본 발명의 전술한 목적들 및 그 외 다른 목적들, 특징, 측면 및 장점들은 첨부된 도면을 참고로 하여 이해할 수 있다. 구체적으로 설명함으로써 명백해질 것이다.

이하. 본 발명의 실시예를 도면을 참조하여 설명한다.

제4도는 본 발명의 실시예에 따른 정자파 장치로서 작용하는 S/N 강화기 10을 보여주는 사시도이다. S/N 강화기 10은 패리자성 베이스로 작용하는 사각판 상의 YIG 박막 12를 포함한다. 이 YIG 박막 12는, 예를 들면 사각판 상의 GGG 기판 14의 한쪽 주면(제1주면)에 형성된다. YIG 박막 12와 GGG 기판 14의 주위를, 예를 들면 도선으로 된 트랜스듀서 1601 5회 휘감고 있다. 따라서, 이 트랜스듀서 16은 S/N 강화기 12의 제1주면 측에 거의 평행하게 배치된 5개의 부분과, YIG 박막 12의 제2주면 측에 거의 평행하게 배치된 5개의 부분을 갖고 있다. 또 트랜스듀서 16의 한쪽 말단에는 입력단자 18의 한쪽 말단이 접속되어 있고, 트랜스듀서 16의 다른 쪽 말단에는 출력단자 20의 다른 쪽 말단이 접속되어 있다. 또, 입력단자 18의 다른 쪽 말단과 출력단자 20의 다른 쪽 말단은 모두 점지되어 있다.

제4도에 나타낸 S/N 강화기 10에서, 페리자성 베이스로서의 YIG 박막 12에, DC 자계 Ho가 YIG 박막 12의 주면에 평행하게, 또 트랜스듀서 16에 평행하게 인가된다. 그런 다음, 입력단자 18에 RF 전력을 입력하면, 트랜스듀서 16의 주위에 RF 자계가 발생하게 되고, YIG 박막 12내에 표면 정자파가 여진된다. 입력단자 18에 입력된 RF 전력이 작은 경우에는, RF 전력이 정자파로 변환된다. 트랜스듀서 16은 YIG 박막 12의 제1주면 층에 배치된 불분과 YIG 박막 12의 제2주면 층에 배치된 불분을 갖고 있기 때문에, RF

전력으로부터 정자파에로의 변환효율은 증가된다. 그러므로 YIG 박막 12가 작게 형성되더라도 종래의 잡음 감쇠량과 유사한 정도의 잡음 감쇠량을 얻을 수 있다. 한편, 입력단자 18에 입력된 RF 전력이 큰 경우에는, RF 전력으로부터 정자파에로의 변환이 포화되기 때문에, RF 전력의 대부분은 트랜스듀서 16을 통해 출력단자 20으로부터 얻어진다. 따라서, S/N 강화기 10에서는, 입력전력이 작은 잡음 성분은 거의 출력되지 않으며, 반면 입력전력이 큰 신호 성분은 대부분이 출력된다. 확인하면, 이 S/N 강화기 10의 신호-대-잡음(S/N) 비는 증가된다. 또한 이 S/N 강화기 10에서는 RF 전력으로부터 정자파에로의 변환효율이 향상되며, 따라서 S/N 강화기 10을 저렴한 가격으로 소형으로 제작할 수 있다.

제5도는 제4도의 S/N 강화기에 대한 변형예에 따른 S/N 강화기를 보여주는 사시도이다. 본 변형예의 S/N 강화기에서는, 제4도에 나타낸 상기한 실시예에 비해, YIG 박막 12가 GGG 기판 14의 제1주면의 중앙에 원판상으로 형성되고, 트랜스듀서 16은 YIG 박막 12와 GGG 기판 14의 주위를 4회 휘감고 있다.

제6도는 제5도의 S/N 강화기에 대한 변형예에 따른 S/N 강화기를 보여주는 사시도이다. 제6도의 본 변형예의 S/N 강화기에서는, 제5도에 나타낸 상기한 실시예에 비해, 트랜스듀서 16이 YIG 박막 12와 GGG 기판 14의 주위를 3회 휘감고 있다.

제7도는 제5도의 S/N 강화기에 대한 두 번째 변형예에 따른 S/N 강화기를 보여주는 사시도이다. 제7도의 본 변형예의 S/N 강화기에서는, 제5도에 나타낸 상기한 실시예에 비해, 트랜스듀서 16이 YIG 박막 12와 GGG 기판 14의 주위를 2회 휘감고 있다.

제8도는 제5도의 S/N 강화기에 대한 세 번째 변형예에 따른 S/N 강화기를 보여주는 사시도이다. 제8도의 본 변형예의 S/N 강화기에서는, 제5도에 나타낸 상기한 실시예에 비해, 트랜스듀서 16이 YIG 박막 12와 GGG 기판 14의 주위를 1회 휘감고 있다.

제5도 내지 제8도의 각각의 변형예에서는, 제4도의 실시예에서와 유사하게, 트랜스듀서 16이 YIG 박막 12의 제1주면 측에 배치된 부분과, YIG 박막 12의 제2주면 측에 배치된 부분을 갖고 있다. 따라서 입력된 RF 전력으로부터 정자파로의 변환효율은 증가될 수 있으며, S/N 강화기를 저렴한 가격으로 소형으로 제작할 수 있다.

또한 제5도 내지 제8도에 나타낸 각각의 변형된 S/N 강화기에서 YIG 박막 12가 원판상으로 형성되기 때문에, 변환된 정자파가 YIG 박막 12의 단부로부터 트랜스듀서 16에 반사되는 일은 거의 없다. 그러므로 YIG 박막 12의 단부로부터 반사된 정자파가 트랜스듀서 16과 같은 정자파 장치의 부품에 의해 RF 전력으로 변환되는 일은 거의 없다. 따라서, S/N 강화기의 전송대역 내에서 진폭/위상 리플 성분은 적어지고, 특성이 향상될 수 있다.

제9도는 비교예를 보여주는 사시도이다. 제9도의 비교예에 따른 S/N 강화기에서는, 제5도의 실시예와 비교하여, 직선상의 트랜스듀서 16이 YIG 박막 12의 제1주면 측에만 배치되어 있다.

제10도는 제5도 내지 제8도에 나타낸 각각의 실시예의 주파수 특성과 제9도에 나타낸 비교예의 주파수 특성을 그래프로 나타낸 것이다. 제11도는 제5도 내지 제8도에 나타낸 각각의 실시예의 입/출력 특성과 제9도에 나타낸 비교예의 입/출력 특성을 나타낸 것이다. 이때, YIG 박막 12의 두께는  $95\text{ }\mu\text{m}$ 이고, YIG 박막 12의 직경은  $2.2\text{mm}$ 이며, YIG 박막 12의 포화자화  $4\pi\text{Ms}$ 는  $1,780\text{Gauss}$ 이다.

제10도에 나타낸 주파수 특성도와 제11도에 나타낸 입/출력 특성도로부터 명백히 알 수 있는 바와 같이, 트랜스듀서 16의 감는 수(turning number)가 증가할수록, 잡음 감쇠량은 증가한다. 그 결과, 주파수 특성과 입/출력 특성은 향상될 수 있다. 트랜스듀서 16의 감는 수가 증가할수록 임피던스가 증가하므로, 잡음의 감쇠량과 임피던스의 크기를 고려하여, 트랜스듀서 16의 감는 수를 적절히 선택하는 것이 바람직하다.

제12도는 본 발명의 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다. 제12도에 나타낸 S/N 강화기에서는, YIG 박막 12와 GGG 기판 14가 모두 절연성을 갖는 비자성체로 된 프리즘 형상의 케이스 22의 중앙에 수납되어 있으며, 도선으로 된 트랜스듀서 16은 케이스 22의 주위를 4회 휘감고 있다.

제12도에 나타낸 실시예에서도, 트랜스듀서 16은 YIG 박막 12의 제1주면 측에 배치된 부분과, YIG 박막 12의 제2주면 측에 배치될 부분을 갖고 있다. 따라서, 입력된 RF 전력으로부터 정자파로의 변환 효율은 향상되며, 저렴한 가격으로 소형의 S/N 강화기를 제작할 수 있다.

제13도는 본 발명의 또 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다. 제14도는 제13도의 S/N 강화기의 평면도이며, 제15도는 제13도의 S/N 강화기의 요부를 보여주는 분해 사시도이다. 제13도 내지 제15도에 나타낸 실시예에서는, 특히 YIG 박막 12의 표면에 직선상의 4세트의 전극들 24a가 소정의 간격으로 평행하게 형성되어 있다. GGG 기판 14의 표면은, 유전체 기판 26의 제1주면의 중앙에 접착된다. 이 유전체 기판 26의 제1주면의 중앙에도, 직선상의 4세트의 전극들 24b가, 소정의 간격으로 평행하게 형성되어 있다. 그리고, 이들 선(line) 전극 24a, 24b의 소정의 단부는 도선 24c에 의해 서로 접속되며, 이에 의해 YIG 박막 12와 GGG 기판 14의 주위를 4회 휘감는 코일형 트랜스듀서가 구성된다. 또, 트랜스듀서의 한쪽 말단, 즉 1개의 선 전극 24a의 한쪽 단부는, 유전체 기판 26의 제1주면 상의 단자전극(terminal electrode) 28a에 도선 28b에 의해 접속된다. 이 단자전극 28a는, 입력단자의 한쪽 말단으로서 작용한다. 또, 트랜스듀서의 다른 쪽 말단, 즉 1개의 선 전극 24b의 다른 쪽 단부 30은, 유전체 기판 26의 단부까지 연장되어 형성된다. 이 다른 쪽 단부 30은 출력단자의 한쪽 말단으로서 작용한다. 또한, 유전체 기판 26의 제2주면에는, 접지전극 32가 형성된다. 이 접지전극 32는 입력단자의 다른 쪽 말단과 출력단자의 다른 쪽 말단으로서 작용한다.

제13도 내지 제15도에 나타낸 실시예에서도, 트랜스듀서는 YIG 박막 12의 제1주면측에 배치된 부분과, YIG 박막 12의 제2주면 측에 배치된 부분을 갖는다. 따라서, RF 전력으로부터 정자파로의 변환 효율은 증가될 수 있으며, 저렴한 가격으로 소형의 S/N 강화기를 제작할 수 있다.

제16도는 본 발명의 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다. 제16도의 본 실시예에서는, YIG 박막 12와 GGG 기판 14의  $\frac{1}{2}$ 지점의 주위를, 도선으로 된 제1트랜스듀서 16a가 2회 휘감고 있다. 이와 유사하게, YIG 박막 12와 GGG 기판 14의 나머지  $\frac{1}{2}$ 지점의 주위를, 도선으로 된 제2트랜스듀서 16b가 2회

휘감고 있다. 그리고, 제1트랜스듀서 16a의 한쪽 말단과 제2트랜스듀서 16b의 한쪽 말단은 입력단자 18의 한쪽 말단에 접속된다. 또, 제1트랜스듀서 16a의 다른 쪽 말단과 제2트랜스듀서 16b의 다른 쪽 말단은 출력단자 20의 한쪽 말단에 접속된다. 또, 입력단자 18의 다른 쪽 말단과 출력단자 20의 다른 쪽 말단은 각기 접지된다.

또, 제16도에 나타낸 본 실시예에서도, 제1트랜스듀서 16a와 제2트랜스듀서 16b는 각각 YIG 박막 12의 제1주면 측에 배치된 부분과 YIG 박막 12의 제2주면 측에 배치된 부분을 갖는다. 따라서, 입력된 RF 전력으로부터 정자파로의 변환 효율은 증가될 수 있으며, 저렴한 가격으로 소형의 S/N 강화기를 제작할 수 있다.

또한, 제16도의 S/N 강화기에서는, 제1트랜스듀서 16a와 제2트랜스듀서 16b가, 입력단자 18과 출력단자 20과의 사이에 병렬로 접속되기 때문에, 입력단자 18과 출력단자 20과의 사이에서의 임피던스는 감소되고, 따라서 삽입손실이 낮아진다.

제17도는 본 발명의 또 다른 실시예에 따른 S/N 강화기를 보여주는 사시도이다. 제17도의 본 실시예에서는, YIG 박막 12와 GGG 기판 14의 주위를, 도선으로 된 제1트랜스듀서 16a가 2회 휘감고 있다. 여기에 덧붙여, YIG 박막 12와 GGG 기판 14의 주위를, 도선으로 된 제2트랜스듀서 16b가, YIG 박막 12와 GGG 기판 14 사이에 삽입되어 진기한 제1트랜스듀서 16a에 대향하는 위치에서, 2회 휘감고 있다.

그리고, 제1트랜스듀서 16a의 한쪽 말단과 제2트랜스듀서 16b의 한쪽 말단은 입력단자 18의 한쪽 말단과 다른 쪽 말단에 각기 접속된다. 또, 제1트랜스듀서 16a의 다른 쪽 말단과 제2트랜스듀서 16b의 다른 쪽 말단은 출력단자 20의 한쪽 말단과 다른 쪽 말단에 각기 접속된다.

제17도에 나타낸 S/N 강화기 10에서는, 페리자성 베이스로서의 YIG 박막 12에, DC 자계  $H_0$ 가 YIG 박막 12의 주면에 평행한 방향으로, 또 트랜스듀서 16a, 16b에 평행한 방향으로 인가된다. 그리고, 이 S/N 강화기 10에서, 입력단자 18에 RF 전력이 입력되면, 트랜스듀서 16a, 16b의 주위에는 RF 자계가 발생하고, YIG 박막 12내에 표면 정자파가 여진된다. 입력단자 18에 입력된 RF 전력이 작은 경우에는, 입력된 RF 전력은 정자파로 변환된다. 제1트랜스듀서 16a가 YIG 박막 12의 제1주면 측에 배치된 부분과, YIG 박막 12의 제2주면 측에 배치된 부분을 갖고 있고, 제2트랜스듀서 16b가 YIG 박막 12의 제2주면 측에 배치된 부분과, YIG 박막 12의 제1주면 측에 배치된 부분을 갖고 있기 때문에, RF 전력으로부터 정자파로의 변환 효율은 증가된다. 그러므로, YIG 박막 12가 작게 형성된 경우에도, 종래의 잡음 감쇠량과 유사한 정도의 잡음 감쇠량을 얻을 수 있다. 한편, 입력단자 18에 입력된 RF 전력이 큰 경우에는, RF 전력으로부터 정자파로의 변환이 포화되기 때문에, 입력된 RF 전력의 대부분은 제1트랜스듀서 16a와 제2트랜스듀서 16b를 통해 출력단자 20으로부터 얻어진다. 따라서, 제17도의 S/N 강화기 10에서는, 입력전력이 작은 잡음 성분은 거의 출력되지 않으며, 입력전력이 큰 신호 성분은 대부분 출력된다. 환연하면, 제17도의 S/N 강화기 10에서의 신호-대-잡음(S/N) 비도 증가될 수 있다. 또, 제17도의 S/N 강화기 10에서도, RF 전력으로부터 정자파로의 변환 효율이 향상되며, 저렴한 가격으로 소형의 S/N 강화기 10을 제작할 수 있다.

여기에 덧붙여, 제17도의 S/N 강화기 10에서는, 제1트랜스듀서 16a가 YIG 박막 12의 제1주면 측에 배치된 부분과, YIG 박막 12의 제2주면 측에 배치된 부분을 포함하고, 제2트랜스듀서 16b가 YIG 박막 12의 제2주면 측에 배치된 부분과, YIG 박막 12의 제1주면 측에 배치된 부분을 포함한다. 또, 입력단자 18의 한쪽 말단과 다른 쪽 말단이, 제1트랜스듀서 16a의 한쪽 말단과 제2트랜스듀서 16b의 한쪽 말단에 각기 접속되어 있다. 출력단자 20의 한쪽 말단과 다른 쪽 말단이, 제1트랜스듀서 16a의 다른 쪽 말단과 제2트랜스듀서 16b의 다른 쪽 말단에 각기 접속되어 있다. 환연하면, 입력단자 18과 출력단자 20이 피더(feeder)에 의해 서로 접속된 경우와 같이, 두개의 트랜스듀서 16a, 16b에 의해 서로 병렬로 접속된 상태로 설정되어 있어, 잡음의 감쇠량을 증가시키기 위하여 제1트랜스듀서 16a와 제2트랜스듀서 16b 사이의 길이를 길게 형성하여도, 입력단자 18과 출력단자 20과의 사이에서의 임피던스에는 아무런 변화가 없으며, 삽입손실은 커지지 않는다.

상술한 각 실시예에 있어서, 입력측의 전단(前段; prestage)과 출력측의 후단(後段; poststage)에, 임피던스 정합회로를 각각 설치할 수도 있다.

또, 제17도에 나타낸 S/N 강화기 10에서는, 평형 전송선로(balanced transmission line)에서의 신호-대-잡음비를 개선할 수 있다. 제17도의 S/N 강화기 10에서, 제18도에 나타낸 바와 같이, 입력측의 전단과 출력측의 후단에 발룬회로(balun circuit; balanced converter circuit) 40a와 40b를 각기 설치하는 경우에는, 불평형 전송선로(unbalanced transmission line)에서의 신호-대-잡음비도 개선할 수 있다. 반면, 제17도에 나타낸 실시예 이외의 실시예에서는, 불평형 전송선로에서의 신호-대-잡음비를 개선할 수 있다. 이들 실시예에서, 입력측의 전단과 출력측의 후단에 발룬회로 40a, 40b를, 발룬회로 40a, 40b의 입력측과 출력측이 제17도에 나타낸 실시예에서 접속된 것과 각각 역방향으로 설치하는 경우에는, 평형 전송선로에서의 신호-대-잡음비를 개선할 수 있다.

제4도~제8도 및 제12도~제17도에 나타낸 각각의 실시예에서 GGG 기판 14의 제1주면에 단일 YIG 박막 12를 형성하였지만, 제19a도, 제19b도에 나타낸 바와 같이, GGG 기판 14의 양 주면에 두개의 YIG 박막 2를 형성할 수도 있다. 제4도~제8도 및 제12도~제17도에 나타낸 실시예에 두 개의 YIG 박막 12를 적용하는 경우에도, 유사한 정도의 장점을 얻을 수 있다.

제5도~제8도에 나타낸 각 실시예에서만 YIG 박막을 원판상으로 형성하였으나, 다른 실시예에서도 페리자성 베이스로 작용하는 YIG 박막을 원판상으로 형성할 수 있다. 이런 경우에도, 제5도~제8도에 나타낸 실시예에서와 동일한 정도의 효과를 얻을 수 있다.

제12도에 나타낸 실시예에서만 YIG 박막을 둘러싸고 있는 케이스의 주위에 트랜스듀서를 형성하였지만, 다른 실시예에서도, 페리자성 베이스로서의 YIG 박막을 둘러싸고 있는 케이스의 주위에 트랜스듀서를 형성할 수 있다.

또한, 제13도~제15도에 나타낸 실시예에서만 트랜스듀서의 일부를 전극으로 형성하였지만, 다른 실시예에서도, 제1트랜스듀서와 제2트랜스듀서의 적어도 일부를 전극으로 형성할 수 있다.

또, 제16도에 나타낸 실시예에서는 2개의 트랜스듀서를 입력단자와 출력단자와의 사이에 병렬로 접속하였으나, 본 발명에서는, 페리자성 베이스의 제1주면 측에 배치된 부분과 페리자성 베이스의 제2주면 측에 배치된 부분을 갖는 복수개의 트랜스듀서를 입력단자와 출력단자와의 사이에 병렬로 접속시킬 수 있다.

상술한 각 실시예에서, DC 자계는, YIG 박막의 주면에 평행한 방향으로, 또 트랜스듀서에 평행한 방향으로, YIG 박막에 인가된다. 그 결과로서, YIG 박막에는, 표면 정자파가 여진된다. 이와는 달리, DC 자계를, YIG 박막의 주면에 수직인 방향으로, 또는 YIG 박막의 주면에 평행하고 트랜스듀서에 수직인 다른 방향으로, YIG 박막에 인가하여도 좋다. DC 자계를 YIG 박막의 주면에 수직인 방향으로 인가하는 경우에는, YIG 박막에, 정자파의 세(3) 모드 중의 다른 하나인, 체적전진 정자파(體積前進靜磁波; magnetostatic forward volume wave; MSFVW)가 여진된다. 또, DC 자계를 YIG 박막의 주면에 평행하고 트랜스듀서에 수직인 방향으로 인가하는 경우에는, YIG 박막에는, 정자파의 세(3) 모드 중의 또 다른 하나인, 체적후퇴 정자파(體積後退靜磁波; magnetostatic backward volume wave; MSBVW)가 여진된다.

또, 상술한 각 실시예는, 고주파 신호(RF 신호)의 S/N 비를 증가시키는 기능 외에도, 대역 소거 필터(band-stop filter)로서의 기능도 갖고 있기 때문에, 이들 실시예들은 대역 소거 필터로서 사용될 수도 있다.

### (57) 청구의 범위

#### 청구항 1

두 개의 대향하는 주면(main surface)을 가지며 DC 자기장이 인가되어 YIG로 구성된 페리자성 베이스; 전기한 페리자성 베이스의 한쪽 주면(제1주면)측에 배치된 부분과, 전기한 페리자성 베이스의 다른 쪽 주면(제2주면)측에 배치된 부분을 갖는 제1트랜스듀서; 전기한 제1트랜스듀서의 한쪽 말단에 접속되는 입력단자; 및 전기한 제1트랜스듀서의 다른 쪽 말단에 접속되는 출력단자를 포함함을 특징으로 하는 정자파(magnetostatic wave) 장치.

#### 청구항 2

제1항에 있어서, 전기한 페리자성 베이스가 원판상으로 형성됨을 특징으로 하는 정자파 장치.

#### 청구항 3

제1항 또는 제2항에 있어서, 전기한 페리자성 베이스의 제1주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제2주면 측에 배치된 부분을 갖고, 전기한 트랜스듀서와 병렬 접속되는 제2트랜스듀서를 더 포함함을 특징으로 하는 정자파 장치.

#### 청구항 4

두 개의 대향하는 주면(main surface)을 가지며 DC 자기장이 인가되어, YIG로 구성된 페리자성 베이스; 전기한 페리자성 베이스의 제1주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제2주면 측에 배치된 부분을 갖는 제1트랜스듀서; 전기한 페리자성 베이스의 제2주면 측에 배치된 부분과, 전기한 페리자성 베이스의 제1주면 측에 배치된 부분을 갖는 제2트랜스듀서; 제1말단은 전기한 제1트랜스듀서의 한쪽 말단에 접속되고, 제2말단은 전기한 제2트랜스듀서의 한쪽 말단에 접속되어 있는 입력단자; 및 제1말단은 전기한 제1트랜스듀서의 한쪽 말단에 접속되고, 제2말단은 전기한 제2트랜스듀서의 다른 쪽 말단에 접속되어 있는 출력단자를 포함함을 특징으로 하는 정자파 장치.

#### 청구항 5

제4항에 있어서, 전기한 페리자성 베이스가 원판상으로 형성됨을 특징으로 하는 정자파 장치.

### 도면

도면1

도면2

도면3

도면4

도면5

10

도면6

10

도면7

10

도면8

10

도면9

10

도면10

## 도면11

## 도면12

도면13

10

도면14

10

도면15

도면16

도면17

10

도면18

도면19a

도면19b