**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>6</sup>

H01L 21/8238

(45) 공고일자 2005년09월05일

(11) 등록번호 10-0511765

(24) 등록일자 2005년08월25일

---

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-1999-7006907   | (65) 공개번호   | 10-2000-0070658 |

| (22) 출원일자   | 1999년07월30일       | (43) 공개일자   | 2000년11월25일     |

| 번역문 제출일자    | 1999년07월30일       |             |                 |

| (86) 국제출원번호 | PCT/US1998/001942 | (87) 국제공개번호 | WO 1998/34268   |

| 국제출원일자      | 1998년01월29일       | 국제공개일자      | 1998년08월06일     |

---

## (81) 지정국

국내특허 : 일본, 대한민국,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드,

(30) 우선권주장 08/792,107 1997년01월31일 미국(US)

(73) 특허권자 울트라테크 인크.

미국 캘리포니아 95134 산 호세 장커로드 3050(72) 발명자 탈워소밋

미국캘리포니아주94303팔로알토버몬테라스3348크레이머칼-조셉

미국캘리포니아주94025멘로파크콜멘애비뉴810아파트먼트17버마파라브

미국캘리포니아주94303팔로알토버몬테라스3348웨이너커트

미국캘리포니아주95125산호세네바다애비뉴822

(74) 대리인 특허법인코리아나

심사관 : 반성원

---

(54) 소형 접적회로의 제조방법

---

**요약**

결정질 실리콘의 표면층을 울트라 셀로우 (401 및 402)(즉, 100 nm 미만) 깊이가지 예비 비정질화하는 것은, 다음과 같은 제조과정의 문제점에 대한 해결책을 제시한다. 제조과정의 문제점들은, (1) 결정질 실리콘의 높은 열 전도도 및 (2) 이

미 제조된 전계효과 트랜지스터에 의한 입사 레이저 조사에 대한 차광 및 회절-간섭 효과를 포함한다. 종래에는, 그러한 문제점들 때문에, 종래기술인 P-GILD(projection gas immersion laser doping)가, 100 nm 이하의 얕은 접합 기술이 이용되는 MOS 전계효과 트랜지스터를 구비하는 접적회로의 제조에 효과적으로 이용되지 못하였다.

## 대표도

도 4

## 명세서

### 기술분야

본 발명은 접적회로 (IC) 의 제조에 관한 것으로, 좀더 구체적으로는, 100nm 이하의 얕은 접합을 채용하는 금속 산화물 반도체 전계효과 트랜지스터 (MOSFET) 를 구비하는 IC 의 제조에 관한 것이다.

### 배경기술

0.25mm 치수의 게이트 길이를 갖는 CMOS 전계효과 트랜지스터 (FET) 가 곧 상용화 될 것이다. 통상적으로, 그러한 0.25mm 치수의 FETs의 제조에서는, 실리콘 도핑을 위해 이온 주입을 이용하고 있다. 그러나, 현재 0.18 mm 치수 이하의 축소된 게이트 길이를 갖는 MOSFETs를 개발하고 있다. 게이트 길이를 축소하기 위해서는 소오스-드레인 접합 깊이 스케일링이 필요하다. 이러한 0.18 mm CMOS 기술에 대해서는, Semiconductor Industry Association 의 "The National Technical Roadmap for Semiconductors" (1995) 에 의하면, 80nm보다 작은 접합 깊이가 제안되고 있다. 이러한 접합은, 이온-채널링 및 일시적으로 증진된 확산 때문에, 이온 주입을 이용하여 형성되기는 어렵다.

관련 참고 문헌으로는, Jpn. J. Appl. Phys. Vol. 31(Dec. 1992) Pt. 1, No. 12B, 페이지 4437-4440 에 기재된 T. Akane 등의 "Two-Step Doping Using Excimer Laser in Boron Doping of Silicon" 이 있으며, 실리콘 도핑에 관한 다른 방법들이 개시되어 있다. 또한 이에 대한 참고문헌으로써, IEEE Electron Device Letters, Vol. 9, No. 10, (Oct. 1988), 페이지 542-544에 기재된, P. G. Carey 등의 "A Shallow Junction Submicrometer PMOS Process Without High-Temperature Anneals" 논문이 있다.

또한, 관련 참고문헌으로는, J. ElectroChem. Soc., Vol. 137, No. 6(June. 1990), 페이지 1912-1914에 기재된 S. Prussin 등의 "Role of Ion Mass, Implant Dose, and Wafer Temperature on End-of-Range Defects", IEEE Transactions on Electron Devices, Vol. 17. No. 10 (Oct. 1990), 페이지 2237-2241 에 기재된 R. B. Fair 의 "Damage Removal/Dopant Diffusion Tradeoffs in Ultra-Shallow Implanted p<sup>+</sup>-n Junctions" 및 Materials Science and Engineering, B34, (1995) pp 168-174에 기재된 S. Acco 등의 "Avoiding End-of-Range Dislocations in Ion-Implanted Silicon" 등이 있으며, 이들 모두는 실리콘의 비정질화를 위한 이온 주입에 관한 것이다.

결정질 실리콘의 열 전도도가 높지 않다면, 레이저광의 표면 부근 흡수 및 얕은 레이저 펄스폭으로 인해, 종래기술인 프로젝션 가스 이며전 레이저 도핑(projection gas immersion laser doping : P-GILD)을 이용하여 울트라 헬로우 (ultra-shallow) (예를 들어, 100 nm 미만) 접합의 형성이 가능할 것이다. 이경우, 제조되는 MOSFET 디바이스의 기하학적 구조가, 열부하 (thermal loading) 에 큰 영향을 미치는, 디바이스의 표면을 비추는 레이저광의 차광 (shadowing) 및 회절을 일으키게 된다. 그러나, 결정질 실리콘의 높은 열 전도도가 엣지에서 접합 깊이를 감소시키는 역할을 한다. 이러한 열전도 효과는 도핑된 영역의 치수가 열확산 길이에 접근함에 따라 분명해진다. 따라서, 도핑된 영역의 특성은 그 치수 및 외부 형상의 함수이다. CMOS 디바이스내 소오스/드레인 도핑의 경우, 이는 도핑된 영역이 게이트 (네가티브 게이트 오버랩) 또는 격리영역 (isolation) 으로 확장되지 않는 결과를 나타낸다. 접합과 웰 간의 쇼트와 높은 기생저항으로 인해, 디바이스의 성능이 저하되기 때문에, 이는 치명적인 문제점을 일으킨다.

### 발명의 상세한 설명

본 발명의 제조방법은, 전술한 열확산의 문제점에 대한 해결책을 제시함으로써, 울트라 헬로우 (예를 들어, 80 nm 미만) 접합의 형성에 P-GILD를 이용할 수 있게 한다.

좀 더 구체적으로, 본 발명의 제조방법에 따르면, 먼저 결정질 실리콘의 소정 표면층을 소정 깊이로 비정질화 시킨다. 그 후, 소정량의 도핑재를, 소정의 비정질화된 실리콘 표면층의 표면상에 박막으로 증착한다. 그후, 소정 비정질화된 실리콘 표면층의 적어도 일부분을, 비정질 실리콘을 용융시키기에는 충분하지만 결정질 실리콘을 용융시키기에는 불충분한 온도로 (비정질 실리콘의 융점은 결정질 실리콘의 융점보다 실질적으로 낮기 때문에) 소정 시간동안 일시적으로 가열한다. 소정 시간동안의 가열을 완료한 후, 그 가열된 부분의 용융된 실리콘을 냉각시켜, 소정 표면층의 열처리된 부분의 실리콘 재 결정화를 행한다.

### 도면의 간단한 설명

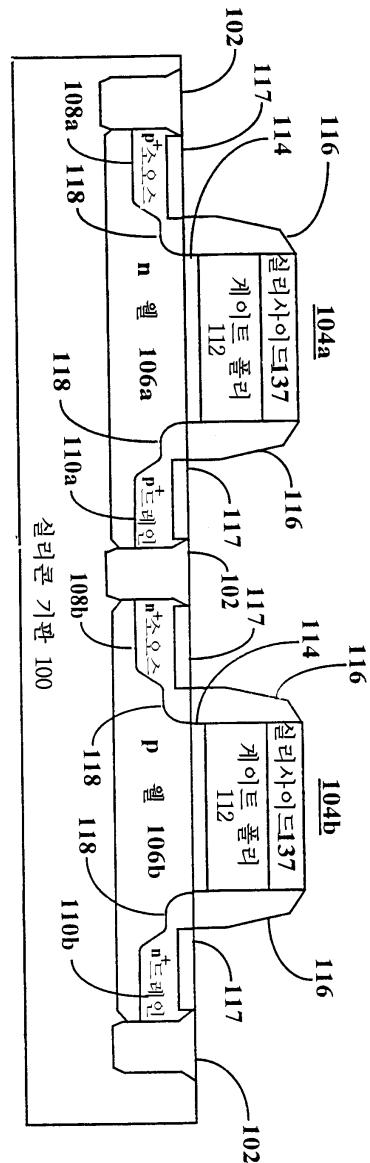

도 1은 기존의 실리콘 CMOS 기술에 따라 제조된 2개의 FETs의 구조를 개략적으로 도시한 것이다.

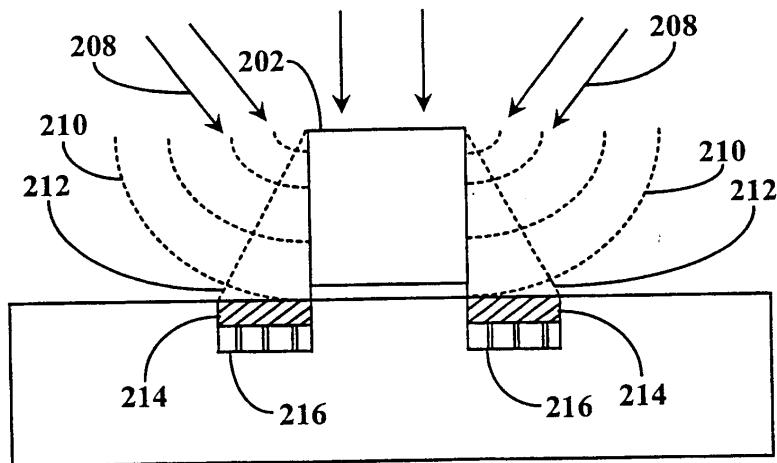

도 2a는 제조시에 P-GILD를 이용하는 경우에 발생하는, MOSFET의 가열된 상부 영역으로부터의 열확산 패턴을 개략적으로 도시한 것이다.

도 2b는 제조시에 P-GILD를 이용하는 경우에 발생하는, MOSFET의 게이트 다결정 (폴리) 구조에 의한 차광 (shadowing) 및 회절-간섭 (diffraction-interference) 효과를 개략적으로 도시한 것이다.

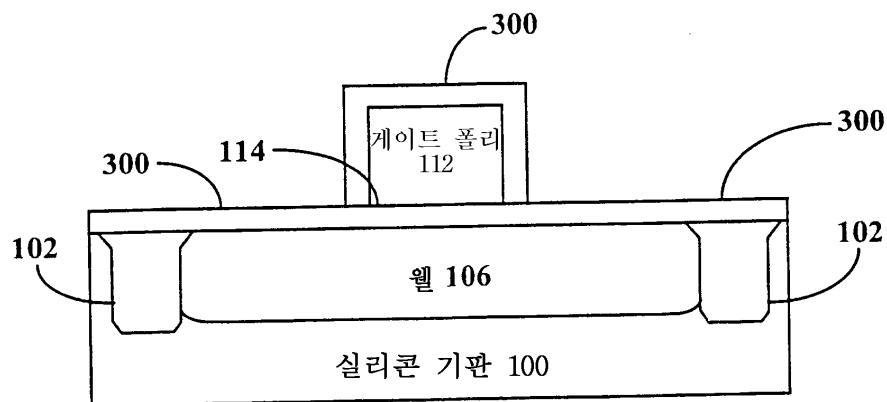

도 3은 본 발명에 따른 제조방법의 단계 중, 확장부의 도핑 또는 소오스 또는 드레인의 도핑 전단계, 웰 도핑 다음 단계의 MOSFET의 제조단계에서, 도 1의 MOSFET 중 하나의 구조를 개략적으로 도시한 것이다.

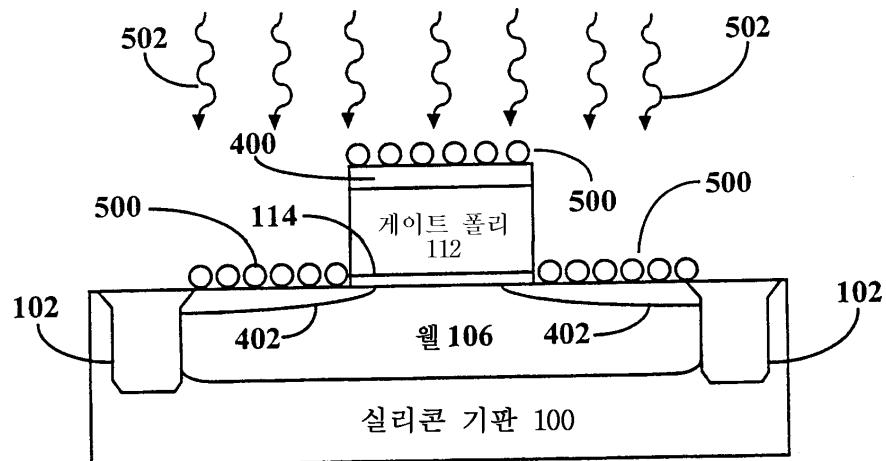

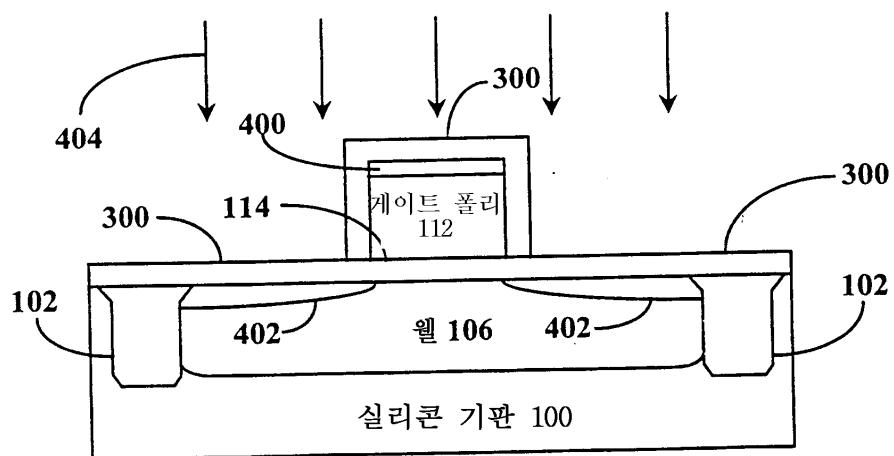

도 4는 도 3의 MOSFET의 상부 영역을 형성하는 실리콘을 이온 주입에 의해 표면을 비정질화하는 단계를 구비하는, 본 발명에 따른 제조단계를 개략적으로 도시한 것이다.

도 5는 제 2 레이저로부터의 조사를 이용하여, 미리 증착된 도핑재 박막으로 FET의 확장부 및 게이트 폴리 양자를 포함하는 도핑을 실시하는 본 발명의 제조방법에 따른 도핑 단계 (도 4의 표면 비정질화 단계와 도핑재 박막을 광분해적으로 미리 증착하는 데 이용되는 제 1 레이저 작동으로부터의 조사를 포함하는 다른 중간단계 후의 단계)를 개략적으로 도시한 것이다.

### 실시예

도 1을 참조하면, 실리콘 기판 (100), 격리부 (102) 및 상보형 FETs (complimentary FETs) (104a, 104b)을 포함하는 CMOS 구조가 도시되어 있다. 상기 상보형 FETs (104a, 104b)의 구조는, FET (104a)는 n 웰 (106a), p+ 소오스 (108a) 및 p+ 드레인 (110a)으로 이루어지지만, FET (104b)는 p 웰 (106b), n+ 소오스 (108b) 및 n+ 드레인 (110b)으로 이루어진다는 점에서만 서로 다르다. 다른 모든점에서, 상보형 FETs (104a, 104b)의 구조는 유사하다. 구체적으로, 양 상보형 FETs (104a, 104b)은, (1)  $\text{SiO}_2$  박막층 (114)에 의해 FET의 웰로부터 절연된 게이트 폴리 (112), (2) 측벽 스페이서 (116), (3) 각 상보형 FETs (102a, 104b)의 게이트 폴리, 소오스 및 드레인 최상부상에 각각 위치한 실리사이드 전기 콘택 (117), 및 (4) 각 상보형 FETs (102a, 104b)의 소오스와 드레인을 게이트 폴리 아래의 채널영역과 결합시키는, 얇게 도핑된 확장부 (118)를 구비한다.

도 1로부터, 가장 얇은 접합은 확장부 (118)로서, 그 확장부 (118)는 깊은 소오스 및 드레인을 채널에 접속시킴을 알 수 있다. 확장부 (118)는, DIBL (drain induced barrier lowering) 및 편치쓰루를 방지해야 하는 것이 필요하다. 상기 확장부는 얇은 저에너지 주입 및 어닐링에 의해 형성한 후, 측벽 스페이서를 형성하고, 깊은 소오스/드레인을 주입한다.

이때, MOSFET 구조의 상업적 제조에서 곧 채용할 수 있는 최소 게이트 치수는 0.25mm이다. 이 경우, 비교적 얇은 저에너지 주입에 의해 확장부 (118)를 형성한 후, 비교적 깊은 고에너지의 이온 주입에 의해 p+ 및 n+ 소오스 (108a, 108b) 및 드레인 (110a, 110b)을 형성한다. 그러나, MOSFET 구조의 제조에 있어서, 0.18mm의 게이트 길이로 스케일을 낮추면, 기존 확장부 (118)의 얇은 접합 깊이가 80nm 미만으로 감소된다. 이러한 확장부 (118)에 대한 얇은 접합 깊이는, 이온 채널링 및 일시적으로 강화된 확산으로 인해 이온 주입을 이용하여 형성하기가 어렵다.

본 발명의 배경기술 부분에서 설명된 바와 같이, 결정질 실리콘의 높은 열 전도도에 기인하여 발생하는 문제점 때문에, 각 확장부 (118)에 대해 80 nm 미만의 접합을 형성하기 위해서는, 이온 주입 대신에 종래의 P-GILD 기술을 이용할 수 없다.

도 2a는 상대적으로 IC 격리부보다 게이트 (202)에 가까운 MOSFET의 실리콘의 일부분의 열확산 패턴만을 도시한 것이다. IC MOSFET 디바이스의 제조 중에 종래기술인 P-GILD를 이용하게 되면, 인접한 IC 격리부들 사이의 전체 단결정 실리콘 상부 표면층 (200)이 가열될 것이다. 이러한 도 2의 실선의 화살표 (204)로 표시한 바와 같이, 게이트 (202)에서 먼 곳에서는, 1차원적인 열확산을 이용하여 가열을 모델링할 수 있다. 그러나, 레이저 광으로부터 차광된 게이트 (202) 아래의 영역은, 게이트 (202)로부터 먼 영역보다는 냉각된 상태로 유지된다. 따라서, 게이트 (202)의 주변에서, 수직 및 수평의 양방향으로 열구배가 존재하게 된다. 이는, 도 2a의 점선 화살표 (206)에 의해 도시한 바와 같이, 게이트 (202)의 주변에서는 2차원적인 열확산이 된다. 따라서, FET의 제조에 종래기술인 P-GILD 레이저 조사를 채용하는 경우에는, 게이트 부근에서의 냉각이 촉진되어, 용융이 더 얕게 되거나 일어나지 않게된다.

또한, 도 2a에는 도시되지 않았지만, FET의 제조에 종래기술인 P-GILD 레이저 조사를 이용하는 경우에는, 도 1의 각 CMOS FETs의 제조 중에, 그 FET의 소오스 및 드레인 영역과 격리부와의 접합부에 2차원 열확산 패턴이 존재함은 명백하다.

도 2b는 게이트 (202)의 존재로 인한 차광효과 (208) 및 회절-간섭 효과 (210)를 개략적으로 도시한 것이다. 좀더 구체적으로 설명하면, 각각의 경사진 점선 (212)에 의해 한정된 실리콘 표면의 최상부 및 게이트 (202)의 수직 측벽의 영역 내에서의 차광효과를 박스 (214)에 의해 도식적으로 나타내었으며, 회절-간섭 효과를 박스 (216)에 의해 도식적으로 나타내었다.

도 2b는 게이트 옆지 부근의 일루미네이션 효과 (illumination effect)를 나타낸 것이다. P-GILD 투사 시스템의 개구율 (numerical aperture)이 크기 때문에, 입사각은 90도로부터 50도까지 변화한다. 조사되는 레이저광의 각도 증가로 인해, 게이트에 의한 차광은 인접 영역내 광의 50%까지 감소시킬 수 있다. 플루언스 손실 (fluence loss)의 일부분은, 게이트 (202)의 실리콘 측벽에서 반사된 추가의 광에 의해 보상될 수 있다. 그러나, 실리콘은, 그레이징각 (grazing angle) 부근에서 TM 편광된 광의 저반사율을 나타냄을 알 수 있다. 이러한 TM 편광된 광의 저반사율 때문에, 실제로는 게이트 측벽 상으로 입사하는 광봉에서 다량의 광이 흡수된다. 따라서, 게이트 (202)에서의 반사는 차광에 기인한 플루언스 손실을 완전히 보상할 수는 없다. 또한, 게이트 (202)의 옆지로부터의 회절 및 게이트 (202)의 반사와 입사광 사이의 간섭은, 게이트 (202)의 옆지 부근의 입사강도를 감소시킨다. 이 때문에, 나머지 소오스 및 드레인 영역보다 게이트 부근의 영역이 더 냉각된다.

따라서, 게이트 옆지에서의 증대된 냉각 및 차광을 결합함으로써, 멜트 (melt)가 게이트 (202)의 옆지까지 연장되는 것을 방지할 수 있다. 충분히 높은 레이저 에너지에 의해 멜트를 게이트 (202)에 도달시킬 수도 있지만, 그렇게 높은 레이저 에너지를 사용하는 것은 바람직하지 않다. 또한, 게이트 (202) 아래에서의 큰 열 구배 때문에, 게이트 (202)와 멜트 사이의 네가티브 오버랩이 게이트의 길이가 증가함에 따라 증가한다. 이 회로는, 가변적인 게이트 길이를 갖는 디바이스들로 이루어질 수도 있다. 따라서, 네가티브 오버랩이 디바이스의 종류에 따라서 변화될 것이다. 네가티브 오버랩은 높은 직렬 저항 및 기판으로의 큰 누설을 유발한다. 현대의 CMOS 기술에서는 이러한 접합은 허용되지 않으므로, 모든 게이트 길이에 대하여 접합을 게이트까지 연장하는 것을 보증하는 방법을 고안할 필요가 있다.

더구나, 실리사이드화가 수행될 때, 2차원 냉각이, 격리부의 옆지부근의 용융을 저해함으로서, 접합과 웰 사이에 쇼트를 유발시키게 된다. 그 결과, 드레인을 웰에 대하여 바이어스시킬 수 없게 된다. 따라서, 격리부 (102)까지 용융시키는 것이 매우 중요하다.

이하, 도 3 내지 도 6에 도시된 본 발명의 방법에 의해 수행된 비교적 단순한 공정을 설명할 것이다. 상기 방법은, 종래기술인 P-GILD 레이저 조사를 도 1의 MOSFETs의 제조에 이용하는 경우, 2차원 냉각에 기인한 네가티브 오버레이 및 차광 및 회절-간섭에 기인한 레이저 플루언스의 감소라는 상기 문제점을 피할 수 있다.

도 3은 도 4 및 도 5에 도시된 본 발명의 제조단계를 포함하는 제조단계의 수행 직전의, 도 1의 MOSFETs 중의 하나의 MOSFET 제조단계를 도시한 것이다. 도 3에 도시된 제조단계에서, 웰(106) 및  $\text{SiO}_2$  박막층 (114) 상에 위치한 게이트 폴리 (112)가 이미 제조되어 있다.

도 4에 도시된 본 발명의 제 1 제조단계는, 게이트 폴리 (112)의 상부 다결정 실리콘층 (400) 및 웰 (106)의 상부 단결정 실리콘층 (402)을 포함하는 도 1의 MOSFET의 영역들을, 원하는 울트라 웰로우 깊이까지 비정질화하는 단계를 포함

한다. 비정질화는 도 4 의 화살표 (404) 로 나타낸 바와 같이, 아르곤, 실리콘 및 게르마늄 등 무거운 원소의 이온 주입에 의해 달성할 수도 있다. 그러나, 게르마늄이, 실리콘을 비정질화하는데 낮은 도우즈를 필요로 하고, 급격한 비정질-결정실계면을 생성시키는 무거운 원자이고, 실리콘 격자내에서 준전자 (isoelectronic) 이기 때문에, 바람직하다.

좀더 구체적으로 설명하면, 도 4 에 도시된 바와 같이, 비정질화될 게이트 폴리 (112) 의 양측의 층 (402) 을 격리부까지 연장한다. 예를 들어, 비정질화되어야 하는 울트라 쉘로우층 (400, 402) 의 깊이를 실질적으로 300Å (80 nm 미만) 이라 하면, 원하는 300Å의 비정질화 깊이를 얻기 위해서는,  $2 \times 10^{14}$  atoms/cm<sup>2</sup> 의 도우즈가 필요하다. 20 KeV 및  $2 \times 10^{14}$  atoms/cm<sup>2</sup> 의 도우즈로 게르마늄을 주입하면, 상기 원하는 300Å의 비정질화 깊이를 갖는 층 (400, 402) 을 얻을 수 있다. 이 주입 조건은 기존 주입기를 이용하여 쉽게 얻을 수 있다.

공지된 바와 같이 (전술된 R. B. Fair 의 논문 참조), 비정질 깊이는 주입 도우즈 및 주입 에너지의 함수이다. 원하는 비정질 깊이에 따라서, 주입 도우즈의 범위는  $1 \times 10^{13}$  atoms/cm<sup>2</sup> 내지  $1 \times 10^{16}$  atoms/cm<sup>2</sup> 사이이고, 주입 에너지의 범위는 5 KeV 내지 400 KeV 사이이다.

도 4 의 실리콘 비정질화 제조단계의 완료 후, (1) SiO<sub>2</sub> 박막층 (300) 의 제거후, (2) ArF 엑시머 레이저 ( $\lambda = 193$  nm) 를 이용하여 소정의 가스 형태의 도편트 화합물을 분해함으로써 (광분해 (photolytic decomposition) 에 의해), 고체 형태의 도핑재 박막을, 제조할 MOSFET의 상부 표면상에 미리 증착하는, 공지된 P-GILD 작업의 제 1 단계 (예를 들어, 상기 작업은, T. Akane 등에 의한 "Two-Step Doping Using Excimer Laser in Boron Doping of Silicon," 에 개시되어 있다)로 이루어지는 2 개의 단계를 수행한다 (상기 2 단계는 도면에 도시되지 않음). 공지된 P-GILD 작업의 제 2 단계 동안 비정질화층 (400, 402) 내에 도입되는 도우즈의 양은, 공지된 P-GILD 작업의 제 1 단계 동안, 미리 증착된 소정 도편트 화합물의 양에 의존한다.

도 5는 전술한 2 개의 도시하지 않은 제조단계의 완료후에 수행되는, P-GILD 작업의 제 2 단계를 도시한 것이다. 도 5에 도시된 바와 같이, 제조될 MOSFET의 상부 표면층 (400, 402) 상에 미리 증착된 도핑재 박막 (500) 을 엑시머 레이저 조사 (502) 로 조사한다. 상기 엑시머 레이저 조사는, 193nm의 파장에서 조사하는 ArF 엑시머 레이저로부터 유도될 수도 있지만 (T. Akan 등의 논문 참조), 다른 유형의 레이저 (예를 들어, 248 nm KrF 레이저, 351 nm XeF 레이저, 또는 308 nm XeCl 레이저)로부터도 유도될 수도 있다. 본 출원인은 308nm의 파장에서 조사하는 펄스형 XeCl 엑시머 레이저를 이용하여, 상술된 P-GILD 작업의 제 2 단계를 수행하였다.

좀더 구체적으로 설명하면, 비정질 실리콘은 결정질 실리콘에 비해, 열 전도도가 10이 낮고, 용점이 300°C 낮으며, 반사율이 30 % 낮다. 이러한 효과들의 결합에 의해, 결정질 실리콘에 비해 비정질 실리콘의 멜트 임계치 (melt threshold) 를 감소시킨다.

다시 도 1 을 참조하면, 확장부 (118) 의 형성공정에서, 비정질화된 층의 깊이를 각 확장부들에 의해 점유될 영역에 필요한 정도로 제한한다. 따라서, 확장부 (118) 영역을 저농도로 도핑하는데 이용되는 P-GILD 작업의 제 2 단계에 의해, 이들 비정질화층의 열 전도도 및 용융 온도가 현저히 감소되기 때문에, 비정질화된 실리콘층이 게이트 폴리 (112) 의 엣지까지 용융되게 된다. 좀더 구체적으로 설명하면, P-GILD 작업의 제 2 단계는 레이저 조사의 연속적인 펄스를 포함한다. 이 연속적인 펄스 각각의 조사 에너지는 비정질화된 실리콘 스팟을 용융시키기에는 충분하지만 결정질 실리콘 스팟을 용융시키기에는 불충분하다. 레이저 펄스로 특정 스팟의 제 1 조사를 마친 후, 방금 도핑된 용융된 실리콘을 즉시 냉각 및 재결정화 시킨다. 이미 조사된 스팟의 재결정화된 실리콘과 중첩되는 소정의 비정질화된 실리콘 스팟을 제 1 펄스에 의해 조사하면, 재결정화된 실리콘을 재용융시키지 않고, 단지 소정의 비정질화된 실리콘 스팟만을 용융시키게 될 것이다. 또한, 액상 실리콘이 매우 불충분하게 냉각되어 있고, 실리콘을 더이상 용융시킬 수 없기 때문에, 비정질 영역을 넘어서 용융이 연장되지 않는 장소에 큰 에너지 원도우가 존재한다. 따라서, 용융깊이를 한정하는데 비정질화를 이용할 수 있다.

레이저 조사를 위한 플루언스 범위는 0.05 Joules/cm<sup>2</sup> 내지 1.0 Joules/cm<sup>2</sup> 이지만, 비정질화된 실리콘을 용융 온도까지 가열하기에는 충분하고 결정질 실리콘을 용융 온도까지 가열하기에는 불충분한, 가장 근사치의 조사 플루언스는 0.4 Joules/cm<sup>2</sup> 이다.

도 4 및 도 5 에 도시된 바와 같이, 게이트 폴리 (112) 의 층 (400) 은 비정질화 및 도핑된다. 게이트 폴리 (112) 의 도핑이 요구되지 않는 경우에는, 도 4 의 비정질화 주입 동안에 게이트 폴리 (112) 상의 마스크층을 채용함으로써, 게이트 폴리 (112) 의 게이트 용융이 P-GILD 작업의 제 2 단계 동안 발생하는 것을 억제할 수도 있다.

상술한 바와 같이, 실리콘의 사전 비정질화에 이은 2 단계의 P-GILD 이용은 확장부 (118)의 울트라 셀로우 접합 (즉 100 nm 미만의 깊이)의 제조에 특히 적합하며, 제조될 MOSFET의 깊은 소오스 및 드레인 영역를 도핑하는데에도 실리콘의 사전 비정질화에 이은 2 단계의 P-GILD를 이용할 수 있다. 자세히 설명하면, 울트라 셀로우 확장부 (118)의 접합의 제조 후, 측벽 스페이서 (116)를 제조한다. 그후, 각 측벽 스페이서 (116)와 격리부 (102) 사이에 위치한 각각의 깊은 소오스 및 드레인 영역을, 전술한 원래의 비정질화 깊이보다 더 깊은 원하는 깊이로 다시 비정질화시킨다. 이는 더 높은 에너지 (예를 들어, 40 KeV) 및 도우즈 (예를 들어,  $6 \times 10^{14}$  atoms/cm<sup>2</sup> 게르마늄 주입)로 수행할 수도 있다. 상기와 같은 재비정질화 (reamorphization)에 이어서, 2 단계의 P-GILD를 이용하여, (1) 이들 2 단계 중 제 1 단계 동안에 도핑재 박막의 적절한 증착 농도 및 (2) 이들 2 단계 중 제 2 단계 동안에 비정질화된 소오스 및 드레인만을 용융시킬 수 있는 적절한 펄스 레이저 에너지를 제공한다.

깊은 소오스 및 드레인의 도핑에, 종래의 이온 주입 도핑 대신에 앞 문단에서 설명된 본 발명의 2 단계를 이용하는 한 이유는, 도핑깊이를 보다 정밀하게 제어할 수 있기 때문이다. 다른 이유는 상기의 방법이 보다 저렴하기 때문이다.

상술된 본 발명의 바람직한 실시예의 방법에서는, 미리 제조된 울트라 셀로우 접합을 측벽 스페이서 (116)까지 연장하기 때문에, 깊은 소오스 및 드레인의 제조는 미리 제조된 울트라 셀로우 (즉, 100 nm 미만의 깊이) 접합의 재비정질화를 수반한다. 그러나, 울트라 셀로우 접합의 범위가 확장부의 위치에 의해서만 제한되므로, 깊은 소오스 및 드레인의 위치를 포함하지 않는다는 것으로 이해하여야 한다. 이 경우, 소오스 및 드레인 위치에 대한 비정질화가 확장부 위치에 대한 비정질화와는 독립적이기 때문에, 소오스 및 드레인 위치에 대한 비정질화는 확장부 위치에 대한 비정질화의 전 또는 후에 일어날 수도 있다. 또한, 본 발명은, MOSFET의 확장부 및 MOSFET의 깊은 소오스 및 드레인 양자의 제조이외에도, MOSFET의 확장부만의 제조 또는 MOSFET의 깊은 소오스 및 드레인만의 제조에 이용될 수도 있다.

공지된 바와 같이, 비정질화 주입은 과포화 점결함을 형성한다. 어닐링을 수행할 때, 점결함의 주입은 광범위한 결함들의 핵생성 (nucleation)을 일으킨다. 통상적인 임계 어닐링 온도는 이러한 광범위한 결함들을 어닐링할 수 있어야 한다. 도 4에 도시 및 상술한 제 1 비정질화 주입에 대해 요구되는 통상적인 어닐링은 1050°C에서 10초 동안이다. 그러나, 2 단계의 P-GILD 작업에 의한 비정질화된 실리콘의 레이저 용융은, 본래 일정 정도의 어닐링을 제공한다. 또한, 상기 레이저 공정 후 적은 수의 점결함이 존재하기 때문에, 이러한 열 순환의 결과로 접합이 많이 이동하지는 않는다. 따라서, 이 경우에, 레이저로 어닐링된 접합에 대해, 추가의 어닐링이 필요하지 않을 수도 있다. 그러나, 어떤 소정의 경우에서는, 어닐링이 추가로 필요한지 결정하기 위해서, 레이저 어닐링 후의 정확한 확산의 범위를 실험적으로 결정해야 한다.

## (57) 청구의 범위

### 청구항 1.

결정질 실리콘 표면층을 구비하는 반도체 기판 상에 MOSFET의 소오스 드레인 접합을 제조하는 방법에 있어서,

- (a) 비정질 표면층을 형성하기 위해, 상기 기판의 상기 결정질 실리콘 표면층의 일부분을 소정의 비정질 깊이까지 비정질화하는 단계;

- (b) 상기 비정질 표면층에 소정의 불순물 레벨을 형성하기 위해, 상기 비정질화 실리콘 표면층의 표면 상에 소정량의 도핑재를 막으로 증착 또는 주입하는 단계; 및

- (c) 상기 비정질 표면층의 적어도 일부분을, 비정질 표면층을 용융시키기에는 충분하지만 상기 결정질 실리콘 표면층을 용융시키기에는 불충분한 온도까지 가열하여, 상기 막의 도핑재를 상기 용융된 비정질 표면층으로 확산시키는 단계를 구비하되,

상기 일부분의 용융된 실리콘을 상기 일정 시간 동안 냉각시켜, 상기 비정질 표면층을 재결정화시키는, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 2.

청구항 2은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 반도체 기판은 결정질 반도체 재료인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 3.

청구항 3은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 단계 (a) 는,

(d) 이온 주입기에 의해 충분한 에너지 레벨로 이온화되고 가속된 원소를, 소정의 단위 면적당 농도로 적절한 원소의 원자를 주입하는 단계를 구비하는, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 4.

청구항 4은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서,

상기 원소는 게르마늄인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 5.

청구항 5은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서,

상기 원소의 단위 면적당 농도는 실질적으로  $2 \times 10^{14}$  atoms/cm<sup>2</sup> 이고, 상기 에너지 레벨은 실질적으로 20KeV 인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 6.

청구항 6은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서,

상기 원소의 단위 면적당 농도는 실질적으로  $6 \times 10^{14}$  atoms/cm<sup>2</sup> 이고, 상기 에너지 레벨은 실질적으로 40KeV 인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 7.

청구항 7은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 단계 (b) 는,

(d) 레이저로부터의 조사를 이용하여 가스 형태로 분해하여, 상기 도핑재를, 상기 비정질 표면층에 고상 (solid form)의 박막으로 증착시키는 단계를 구비하는, MOSFET의 소오스 드레인 접합을 제조하는 방법.

**청구항 8.**

제 1 항에 있어서,

상기 단계 (c) 는,

(d) 레이저로부터의 소정 레벨의 방사상 플루언스를 이용하여, 상기 비정질 표면층의 적어도 일부분을 효과적으로 가열하는 단계를 구비하는, MOSFET의 소오스 드레인 접합을 제조하는 방법.

**청구항 9.**

청구항 9은(는) 설정등록료 납부시 포기되었습니다.

제 8 항에 있어서,

상기 레이저로부터의 상기 방사상 플루언스의 레벨은 실질적으로  $0.4 \text{ Joules/cm}^2$  인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

**청구항 10.**

청구항 10은(는) 설정등록료 납부시 포기되었습니다.

제 8 항에 있어서,

상기 단계 (d) 는,

(e) 펄스 레이저로부터의 방사 에너지의 연속적인 펄스 중 단일 펄스를, 상기 비정질 표면층의 조사된 영역에 인가하여, 상기 연속적인 펄스 중 단일 펄스가 지속되는 동안 상기 조사된 영역을 가열하는 단계를 구비하고,

상기 연속적인 펄스 중 단일 펄스의 방사 에너지는, 상기 하부의 비정질 표면층의 조사된 영역을 그 용융 온도까지 가열하기에는 충분하지만, 상기 결정질 반도체 표면층을 그 용융 온도까지 가열하기에는 불충분한, MOSFET의 소오스 드레인 접합을 제조하는 방법.

**청구항 11.**

반도체 기판 상에 MOSFETs을 제조하기 위한 집적회로의 제조방법에 있어서,

인접한 FETs가 격리부에 의해 서로 분리되고, 각 제조된 FET 는, (1) 적절하게 도핑된 단결정 반도체 웨이퍼 표면 상에 형성된 (2) 반도체 게이트, (3) 상기 반도체 게이트의 한쪽에 각각 위치한 제 1 및 제 2 측벽 스페이서, (4) 제 1 격리부로부터 상기 제 1 측벽 스페이서와 근접하는 부분으로 세로로 연장되는 비교적 깊고 적절하게 도핑된 단결정 반도체 소오스, (5) 제 2 격리부로부터 상기 제 2 측벽 스페이서와 근접하는 부분으로 세로로 연장되는, 비교적 깊고 적절하게 도핑된 반도체 드레인, (6) 상기 소오스를 인접한 게이트 옆지에 접속하기 위한, 상기 제 1 측벽 스페이서 아래에 위치한 제 1 울트라 웰로우 (ultra shallow) 반도체 확장부, 및 (7) 상기 드레인을 인접한 게이트 옆지에 접속하기 위한, 상기 제 2 측벽 스페이서 아래에 위치한 제 2 울트라 웰로우 반도체 확장부를 구비하며,

상기 방법은, 상기 웨이퍼 및 상기 반도체 게이트의 제조 이후 및 상기 제 1 및 제 2 측벽 스페이서의 제조 전에, 각각의 상기 제 1 및 제 2 울트라 웰로우 반도체 확장부의 제조를 위해,

(a) 상기 반도체의 게이트 엣지로부터 경리부로 세로로 연장된 상기 단결정 반도체 웰의 제 1 및 제 2 표면층 각각에, 소정의 원소의 원자를 단위 면적당 소정의 농도 및 소정의 에너지 레벨로 이온 주입하여, 상기 제 1 및 제 2 층을 100 nm 미만의 소정 깊이까지 비정질화하는 단계;

(b) 상기 확장부를 도핑하기 위해, 소정의 도핀트 화합물을 레이저로부터의 조사에 의해 가스 형태로 분해하여, 소정량의 도핑재를 고상의 박막으로 증착함으로써, 상기 제 1 및 제 2 비정질 표면층 상에 소정의 불순물 레벨을 형성하는 단계;

(c) 펄스 레이저로부터의 방사 에너지의 복수개의 연속적인 펄스 중 제 1 펄스를, 상기 제 1 및 제 2 비정질 표면층 각각에 인가하여, 상기 연속적인 펄스의 상기 제 1 펄스가 지속되는 동안 상기 제 1 영역을 가열하고, 그 후, 상기 펄스 레이저로부터의 방사 에너지의 상기 연속적인 펄스들 중 다른 펄스를, 상기 제 1 또는 제 2 비정질층의 이미 조사된 영역과 중첩되는 연속적인 영역을 각각 갖는, 상기 제 1 및 제 2 비정질 표면층의 다른 영역들에 순차적으로 인가하여, 상기 연속적인 펄스의 단일 펄스 (single pulse) 가 지속되는 동안 상기 다른 영역을 각각 가열하는 단계로서, 분리된 각각의 상기 연속적인 펄스들의 조사 에너지는, 상기 조사된 영역의 제 1 또는 제 2 비정질 표면층을 그 용융 온도까지 가열하기에는 충분하지만, 하부의 결정질 반도체를 그 용융 온도까지 가열하기에는 불충분한 단계; 및

(d) 상기 각각의 연속적인 펄스 사이에, 상기 연속적인 펄스를 상기 제 1 또는 제 2 비정질 표면층에 인가하기 전에, 제 1 또는 제 2 비정질 표면층의 용융된 영역이 재결정화되고 초기 온도로 냉각되기에 충분한 시간 간격을 제공하는 단계를 구비하는, 집적회로의 제조 방법.

## 청구항 12.

청구항 12은(는) 설정등록료 납부시 포기되었습니다.

제 11 항에 있어서,

상기 이온 주입된 원자의 상기 소정 단위 면적당 농도는 실질적으로  $2 \times 10^{14}$  atoms/cm<sup>2</sup> 이고 상기 에너지 레벨은 실질적으로 20KeV 인, 집적회로의 제조 방법.

## 청구항 13.

청구항 13은(는) 설정등록료 납부시 포기되었습니다.

제 11 항에 있어서,

상기 이온 주입되는 원자는 게르마늄인, 집적회로의 제조 방법.

## 청구항 14.

청구항 14은(는) 설정등록료 납부시 포기되었습니다.

제 13 항에 있어서,

상기 이온 주입된 게르마늄 원자의 상기 소정의 단위 면적당 농도는 실질적으로  $2 \times 10^{14}$  atoms/cm<sup>2</sup> 이고 상기 에너지 레벨은 실질적으로 20KeV 이며,

상기 제 1 및 제 2 층의 비정질화된 깊이는 실질적으로 300Å 인, 집적회로의 제조 방법.

## 청구항 15.

청구항 15은(는) 설정등록료 납부시 포기되었습니다.

제 11 항에 있어서,

상기 단계 (a) 는,

상기 다결정 실리콘 게이트의 상부 표면층에 게르마늄 원자를 소정 단위면적당 농도 및 충분한 에너지 레벨로 이온 주입하여, 상기 다결정 실리콘 게이트의 상기 상부 표면층을 실질적으로 300Å 깊이로 비정질화하는 단계를 더 구비하는, 집적회로의 제조 방법.

### 청구항 16.

제 11 항에 있어서,

상기 제 1 및 제 2 측벽 스페이서의 제조후에, 상기 비교적 깊고 적절하게 도핑된 실리콘 소오스 및 드레인 각각을 제조하는 방법은,

(a) (1) 상기 제 1 측벽 스페이서의 엣지로부터 격리부로 세로로 연장된 소오스층 및 (2) 상기 제 2 측벽 스페이서의 엣지로부터 격리부로 세로로 연장된 드레인층 각각에, 실질적으로  $6 \times 10^{14}$  atoms/cm<sup>2</sup> 의 농도와 40KeV의 에너지로 원자를 이온 주입하여, 상기 소오스 및 드레인층을 비교적 깊은 깊이까지 비정질화하는 단계;

(b) 상기 소오스 및 드레인층을 도핑하기 위해, 소정의 도펀트 화합물을 가스 형태로 광분해하여, 상기 비정질화된 소오스 및 드레인층의 표면 상에, 상기 비정질 소오스 및 드레인층에 소정의 불순물 레벨을 달성하기 위한 소정량의 도핑재를 고상의 박막으로 증착하는 단계;

(c) 펠스 레이저로부터의 방사 에너지의 연속적인 펠스들 중 선택된 제 1 펠스를, 상기 비정질화된 소오스 및 드레인층의 각각에 인가하여, 상기 연속적인 펠스 중 상기 제 1 펠스가 지속되는 동안 상기 제 1 영역을 가열한 후, 상기 펠스 레이저로부터의 방사 에너지의 다른 연속적인 펠스를, 상기 이전의 조사 영역과 적어도 부분적으로 중첩되는 비정질층들 중 다른 영역에 순차적으로 인가하여, 상기 연속적인 펠스 중 단일 펠스가 지속되는 동안 다른 영역을 각각 가열하는 단계로서, 분리된 각각의 상기 연속적인 펠스의 조사 에너지는, 상기 조사 영역의 비정질층을 그 용융 온도까지 가열하기에는 충분하지만, 하부의 결정질 반도체를 그 용융 온도까지 가열하기에는 불충분한 단계; 및

(d) 상기 연속적인 펠스의 인가 사이에, 상기 비정질층에 연속적인 펠스를 인가하기 전에, 상기 비정질층의 용융 영역이 재결정화되고 초기 온도로 냉각되기에 충분한 시간 간격을 제공하는 단계를 더 구비하는, 집적회로의 제조 방법.

### 청구항 17.

청구항 17은(는) 설정등록료 납부시 포기되었습니다.

제 16 항에 있어서,

(e) 상기 비정질층 중 다른 층에 대해 상기 단계 (c) 및 상기 단계 (d) 를 반복하는 단계를 더 구비하는, 집적회로의 제조 방법.

### 청구항 18.

청구항 18은(는) 설정등록료 납부시 포기되었습니다.

제 15 항에 있어서,

(e) 상기 비정질층 중 다른 층에 대해 상기 단계 (c) 및 상기 단계 (d) 를 반복하는 단계를 더 구비하는, 집적회로의 제조 방법.

### 청구항 19.

청구항 19은(는) 설정등록료 납부시 포기되었습니다.

제 1 내지 제 10 항 중 어느 하나의 항에 있어서,

상기 반도체 기판은 실리콘인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 20.

청구항 20은(는) 설정등록료 납부시 포기되었습니다.

제 11 항 내지 제 18 항 중 어느 하나의 항에 있어서,

상기 반도체 기판은 실리콘인, 집적회로의 제조 방법.

### 청구항 21.

청구항 21은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서,

상기 반도체층은 실리콘이고, 상기 원소는 게르마늄이며, 상기 단위 면적당 농도는 실질적으로  $2 \times 10^{14}$  atoms/cm<sup>2</sup>이고, 상기 에너지 레벨은 실질적으로 20KeV 인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

### 청구항 22.

청구항 22은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서, 상기 반도체층은 실리콘이고, 상기 원소는 게르마늄이며, 상기 단위 면적당 농도는 실질적으로  $6 \times 10^{14}$  atoms/cm<sup>2</sup>이고, 상기 에너지 레벨은 실질적으로 40KeV 인, MOSFET의 소오스 드레인 접합을 제조하는 방법.

도면

도면1

도면2a

도면2b

도면3

도면4

도면5