(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5557436号

(P5557436)

(45) 発行日 平成26年7月23日(2014.7.23)

(24) 登録日 平成26年6月13日(2014.6.13)

(51) Int.CI.

H01L 21/60 (2006.01)

F 1

H01L 21/60 311S

請求項の数 6 (全 7 頁)

(21) 出願番号 特願2008-241065 (P2008-241065)

(22) 出願日 平成20年9月19日 (2008.9.19)

(65) 公開番号 特開2009-76915 (P2009-76915A)

(43) 公開日 平成21年4月9日 (2009.4.9)

審査請求日 平成23年9月15日 (2011.9.15)

(31) 優先権主張番号 0757676

(32) 優先日 平成19年9月19日 (2007.9.19)

(33) 優先権主張国 フランス (FR)

(73) 特許権者 502124444

コミッサリア ア レネルジー アトミー

ク エ オ ゼネルジ ザルタナテイヴ

フランス国 エフー 75015 パリ,

バティマン 「ル ポナン テー」,

リュ ルブラン 25

(74) 代理人 100082670

弁理士 西脇 民雄

(72) 発明者 フェンドラー マニュエル

フランス共和国 グルノーブル 3800

O ブルバール マレシャル フォシュ

64

(72) 発明者 エーマニ アブドナセール

フランス共和国 サンテグレブ 3812

O アレ デ グライル 26

最終頁に続く

(54) 【発明の名称】チップ形成方法、及び、チップを基板にポンディングする方法

## (57) 【特許請求の範囲】

## 【請求項 1】

個々のチップを形成する方法であって、

複数の機能性層(40)を、隣接する機能性層(40)がスペースeの間隔で非接触状態で配置されるように支持体(41)上に配列すること、

接着剤(43)を、調整された滴で前記複数の機能性層のそれぞれに付着すること、

拘束基板(44)を前記機能性層のそれぞれに前記接着剤上で加圧の下で配置すること、

それぞれが切断された拘束基板と接着剤と機能性層とを有する複数の单一化されたチップ(45)を形成するように前記複数の機能性層間のスペースeに対応する位置で前記拘束基板(44)を切断すること、

单一化されたチップ(45)を、前記支持体(41)から分離することを含み、

前記拘束基板は、該拘束基板が切断される前に、前記スペースeに対向するように形成された開口(48)を有することを特徴とするチップ形成方法。

## 【請求項 2】

前記機能性層が接着支持体(41)に配列されていることを特徴とする請求項1記載のチップ形成方法。

## 【請求項 3】

前記スペースeが40 μmと500 μmとの間にあることを特徴とする請求項1記載のチップ形成方法。

10

20

**【請求項 4】**

前記機能性層(40)がシリコンで形成されていることを特徴とする請求項1記載のチップ形成方法。

**【請求項 5】**

請求項1乃至4のいずれか1項に記載の個々のチップを形成する方法を実行するため異なる膨張係数の材料から選択された材料によって形成された拘束基板(44)によって半導体読み取り回路(40)を拘束の下で支持体上に配置する方法。

**【請求項 6】**

前記拘束基板の材料が、ゲルマニウム、サファイヤ、BeOから選択されることを特徴とする請求項5記載の方法。

10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、チップを拘束基板にボンディングする方法および異なる膨張係数の材料によって半導体読み取り回路を拘束状態に配置する方法に関する。

**【背景技術】****【0002】**

異質な、換言すると、異なった性質、例えば、異なった膨張係数又はヤング係数を有する二つの部分から成り、熱機械的に信頼性のあるアセンブリを形成することは、バイメタル(二金属)素子構造、又はBCS(Balanced Composite Structure)として知られた構造でも開発を必要とする。このような構造は、拘束基板として知られた基板を、信頼性のあるアセンブリにボンディングすることを特徴としている。

20

**【0003】**

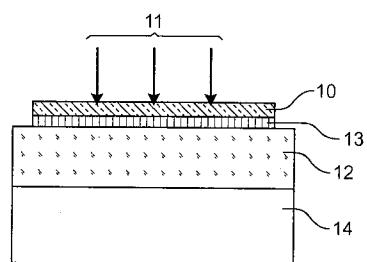

この明細書の末尾に記載された参考文献[1]は、読み取り回路と検出フォーカルプレーン(焦点面)との間を相互に接続するアセンブリを述べている。図1に示されたこのアセンブリは、第一の膨張係数を有し放射線11を検出するようにした半導体の第一の層10と、第二の膨張係数を有する第二の半導体電子回路多重化層12と、二つの第一および第二の層10、12間に配置された第三の相互接続層13と、高い膨張係数を有し第二の層12の下面に結合された拘束基板14とを備えている。この文献は、信頼性のある“ボトムアップ”に形成された構造を述べている。

30

**【0004】**

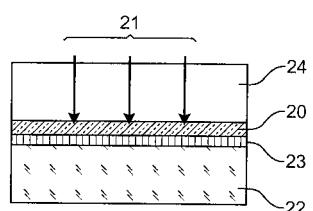

参考文献[2]は、信頼性のある“トップダウン”に形成された構造を述べている。図2に示されているように、この構造は、放射線21を検出する層20と、読み取り層22と、上記二つの層20および層22間に配置された相互接続層23とを備えている。第一の半導体材料に形成された読み取り層22は、機械的基準として機能する。第一の材料に適合し放射線に対して透過である第二の材料の拘束基板24は、検出手段20の上方に配列される。

**【0005】**

これら二つの文献では、拘束基板を信頼があるように形成されたアセンブリにボンディングする構造を特徴としている。

40

**【0006】**

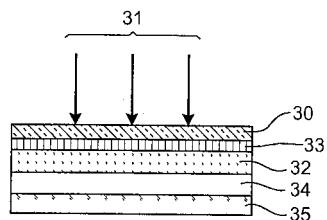

参考文献[3]は、ハイブリッドフォーカルプレーンネットワーク構造を述べている。図3に示すように、この構造は、入力放射線31を検出するようにした半導体の層30と、多重化層32と、二つの層30、32間に配置された相互接続層33とを備えている。検出層30と同様の機械的および幾何学的特性を有する拘束基板34は、層32の下面に結合される。層32と同様な特性を有する補助層35が、バイメタル素子32、34によって発生されるアセンブリの曲率半径を修正するように機能する。BCS構造を形成するこれら三層32、34、35の組み合わせは、アセンブリを信頼性のあるものに形成させることができる。従って、この構造は、信頼性のある“ボトムアップ”に形成される。

**【発明の開示】**

50

**【発明が解決しようとする課題】**

**【0007】**

しかしながら、拘束基板を信頼性のあるアセンブリにボンディングすることは、気泡を有することなく、バイメタル素子効果の利益を十分に得るために、組み立てられる部品間に良好な機械的連結を可能とするような均質な接着剤のフィルム（膜）が形成されなければならない。

**【0008】**

ボンディング技術についての従来技術を開示するいくつかの文献は、面の処理、良好な湿潤および得られるべき強い接着性を可能とする物理的および化学的性質に関するものである。ボンディング方法は、公知技術の分野である。一般に、気泡の不存在およびボンディングの均一性は、ガス排出、真空下でのボンディング、遠心分離、閉塞または高圧の適用によって得られる。このような技術は、最小の粗さまたは最小のボンディング欠陥に対する公差が実質的にゼロになるとき（マイクロ電子の場合に）、大きな面領域に用いるには困難である。10

**【0009】**

その上、このような技術、例えば、最高レベルの清浄度（100以下に分類されるクリーンルーム）を必要とする真空蒸着および分子接着技術は、コスト高になる。

**【0010】**

上記の如き欠点を解消するために、本発明の主題は、小面積単一ボンディングのすべての利点を発展させることによって大面積ボンディングにおけるように個々のチップを共通の基板に集合的にボンディングすることができる低成本の方法である。20

**【課題を解決するための手段】**

**【0011】**

本発明は、個々のチップを形成する方法に関し、この方法は、

複数の機能性層を、隣接する機能性層がスペースeの間隔で非接触状態で配置されるように支持体上に配列すること、

接着剤を、調整された滴で前記複数の機能性層のそれぞれに付着すること、

拘束基板を前記機能性層のそれぞれに前記接着剤上で加圧の下で配置すること、

それぞれが切断された拘束基板と接着剤と機能性層とを有する複数の单一化されたチップを形成するように前記複数の機能性層間のスペースeに対応する位置で前記拘束基板を切断すること。30

单一化されたチップを、前記支持体から分離することを含み、

拘束基板は、該拘束基板が切断される前に、前記スペースeに対向するように形成された開口を有することを特徴とする。

**【0012】**

有益には、スペースeは、40 μmと500 μmとの間にある。機能性層は、シリコンで形成されている。

**【0013】**

本発明は、また、例えば、シリコンの半導体読み取り回路を、上記方法を実施する、異なる膨張係数の材料の基板によって拘束の下で配置する方法に関する。有利には、この材料は、ゲルマニウム、サファイヤ、BeOの中から選択される。40

**【発明を実施するための最良の形態】**

**【0014】**

本発明の方法は、個々のチップを共通の基板に集合ボンディングする方法である。

**【実施例】**

**【0015】**

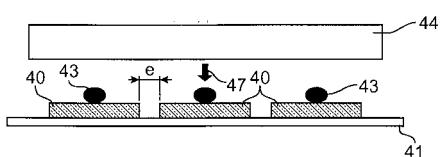

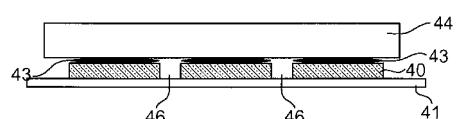

本発明の方法によれば、図4に示されるように、機能性あるいは活性、換言すると、例えば、一体性の読み取り回路として知られた層40を、支持体41に、例えば、接着剤を用いて配列するようにしている。これら機能性の層40が、例えば、これら層を他の回路に接続する接続パッド（例えば、ろう付けバンプ）のための面構造を有する場合には、接50

続パッドは、接着される支持体41に直接接触するようにされる。これら機能性層40は、それらの間が $40\text{ }\mu\text{m}$ と $500\text{ }\mu\text{m}$ との間の範囲のスペースeをもって、隣接した非接触状態で配列されている。

#### 【0016】

次いで、接着剤43の調整された滴がこれら機能性層のそれぞれに付着される。

#### 【0017】

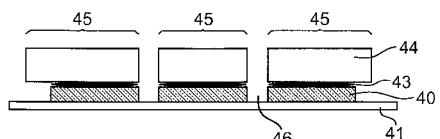

次いで、このようにして形成された組立体の上に、拘束(押圧)基板44が矢印47に示すように搬送され、これによって、図5に示された実施例を得ることができる。

#### 【0018】

次いで、図6に示すように、基板44を切断することによって単一化したチップ45が個々に形成される。次いで、これらチップ45は、支持体41から剥離される。10

#### 【0019】

本発明に係る方法は、支持体41に予め配列された機能性層40の上に大きな寸法の基板44を結合(ボンディング)することによっていくつかのチップ45の同時処理を行うという“大面積”ボンディングの利点を有し、且つ気泡の現出を避けることができる“小面積”ボンディングとして知られた単一ボンディングの利点をも有する。

#### 【0020】

機能性層を、隣接した非接触状態で配列することによって、気泡を局所的にトラップすることができるリザーバのような溝46が機能性層の間に形成されている。従って、機能性層40の外部に向かって放出される気泡は、基板44の全てを覆うことがなく、外部に排出される。20

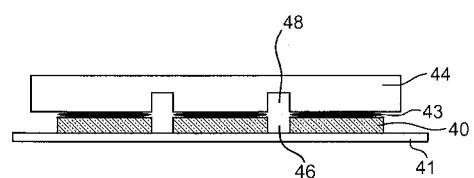

#### 【0021】

溝46の上方に配置された開口48を基板に形成することによって、これらの溝46の容量を大きくすることもできる。かくして、この構造は、図5に示された実施例に代って、図7に示された実施例に示されている。この構造は、特に、スペースeを減少することができるが、同じ接着剤に有効な容量が減少するのを防止することができる。

#### 【0022】

例えば、異なる膨張係数の材料から選択された材料によって形成された拘束基板(44)によって、半導体読み取り回路を拘束状態で支持体上に配置するために本発明の方法を用いてもよい。この場合、上記異なる膨張係数の材料は、半導体読み取り回路の構成要素をハイブリッド化(单一化)させるように構成されている。30

#### 【0023】

これは、例えば、CdHgTe又はCdTe検出器の場合にシリコン上に配置されたゲルマニウム、

CdHgTe又はCdTe検出器の場合にシリコン上に配置されたサファイヤ、

CdHgTe又はCdTe検出器の場合にシリコン上に配置されたBeOである。

#### 【0024】

このような材料は、冷却された赤外放射線(CdHgTe)又はX-線(CdTe)の分野で最も共通に用いられる。これらの材料には、種々の金属、セミコンダクター、セラミック、ガラスおよびポリマーのすべての材料を加えることができ、それらの熱機械的性質は、所定の用途に適合するように設定される。CdHgTeの場合に、包括な例示として、次の材料が引用される:Mo、CuMoCu、FeNiCo、金属のフリット、固体Cd(Zn)Te等。40

#### 【0025】

概述すると、本発明の方法は、バイメタル(二金属)素子(又は文献〔3〕に記載された2以上の層のアセンブリ)の任意の実施例に適用可能であり、膨張係数を適合させるために基板の熱機械性質を変更するようにされている。

#### 【0026】

従って、本発明に係る方法は、バイメタル素子の挙動規則を順守することによって、任意の材料が、他の材料の熱機械性質(挙動)を包囲することを可能にする。

#### 【0027】

50

20

30

40

50

本発明の方法は、チップあるいは材料を、ベースに任意にボンディングすることに、より広く適用することができ、概述すると、例えば、文献〔4〕に記載されているように、光学チップ（InP, GaAs, シリカ）がシリコンアセンブリプラットホーム（シリコン、光学ベンチ）上に搬送される。又、文献〔5〕に記載されているように、チップ（発光のためのGaNチップ、シリコンチップをパッケージ、MCM、又は“マルチチップモジュール”）をベース上のセラミックに移送、カプセル化、あるいはパッケージ化することができる。

#### 【0028】

本発明によれば、利点として、集合、同じバッチのチップに共通な方法の特徴は、

同一厚さおよび性質の接着剤

同一レベルのクロス（架橋）結合

同一のショア硬さ

10

であるボンディング特性について、証明することが容易であることである。

#### 【0029】

参考文献：

〔1〕米国特許4、943、491

〔2〕米国特許5、365、088

〔3〕EP 0 829 907

〔4〕レオ ジー ファインスタンによる“ダイ取り付け方法”（1989 - 電子材料ハンドブック、巻1、213ページ～223ページ、パッケージング、ASMインターナショナル）

20

〔5〕ジョン ダブリュウ ベルダーによる“マルチチップ技術の概説”（1989 - 電子材料ハンドブック、巻1、297ページ～312ページ、パッケージング、ASMインターナショナル）

#### 【図面の簡単な説明】

#### 【0030】

【図1】は、従来技術の実施例を示す図。

【図2】は、従来技術の実施例を示す図。

【図3】は、従来技術の実施例を示す図。

【図4】は、本発明の方法を示す図。

【図5】は、本発明の方法を示す図。

30

【図6】は、本発明の方法を示す図。

【図7】は、本発明の方法を示す図。

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 ググノー アラン

フランス共和国 サセナージュ 38360 シュマン ドゥ ヴィネイ - ラ レジダンス 27

G

(72)発明者 マリオン フランソワ

フランス共和国 サン - マルタン ル ヴィノー 38950 ルート ド クレマンシエール

4480

審査官 関根 崇

(56)参考文献 特開2007-208129(JP,A)

特開2006-108421(JP,A)

特開平04-119645(JP,A)

米国特許第06255140(US,B1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/60

H01L 21/52

H01L 21/301

H01L 23/12

H01L 25/04~18