(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5693450号

(P5693450)

(45) 発行日 平成27年4月1日(2015.4.1)

(24) 登録日 平成27年2月13日(2015.2.13)

(51) Int.Cl.

F 1

H01L 33/48 (2010.01)

H01L 33/60 (2010.01)H01L 33/00 400

H01L 33/00 432

請求項の数 11 (全 13 頁)

(21) 出願番号 特願2011-515089 (P2011-515089)

(86) (22) 出願日 平成21年6月18日 (2009.6.18)

(65) 公表番号 特表2011-526418 (P2011-526418A)

(43) 公表日 平成23年10月6日 (2011.10.6)

(86) 國際出願番号 PCT/DE2009/000857

(87) 國際公開番号 WO2010/000224

(87) 國際公開日 平成22年1月7日 (2010.1.7)

審査請求日 平成24年6月18日 (2012.6.18)

(31) 優先権主張番号 102008030815.3

(32) 優先日 平成20年6月30日 (2008.6.30)

(33) 優先権主張国 ドイツ(DE)

(73) 特許権者 599133716

オスラム オプト セミコンダクターズ

ゲゼルシャフト ミット ベシュレンクテ

ル ハフツング

Osram Opto Semiconduc

tors GmbH

ドイツ連邦共和国、93055 レーゲン

スブルグ、ライプニッツシュトラーゼ 4

Leibnizstrasse 4, D

-93055 Regensburg,

Germany

(74) 代理人 100099483

弁理士 久野 琢也

(74) 代理人 100061815

弁理士 矢野 敏雄

最終頁に続く

(54) 【発明の名称】複数のオプトエレクトロニクス素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のオプトエレクトロニクス素子の製造方法において、

それぞれに1つのコンタクト構造(20)が設けられており、且つ、電磁放射の形成に

適した活性層(16)を半導体層列(15)内に備えている複数の半導体ボディ(14)

を第1の主面(12)上有している半導体ボディ支持体(10)を準備するステップと

、

前記半導体ボディ(14)を覆うことなく、前記コンタクト構造(20)および前記半

導体ボディ支持体(10)の上の領域を少なくとも部分的に覆う平坦な充填構造(42,

44)を前記第1の主面(12)上に形成するステップとを有し、

前記半導体ボディ支持体(10)を準備するステップは、複数の半導体ボディ(14)

を、少なくとも1つのウェハ結合体から個別にまたは一緒に前記半導体ボディ支持体(10)

に運ぶステップを含み、

前記平坦な充填構造を前記半導体ボディの少なくとも1つの側縁に対して距離を空けて

配置し、前記半導体ボディの側方にミラー層を形成し、

少なくとも前記半導体ボディ(14)を覆う構造化されたレジスト層を形成し、構造化

された前記レジスト層の外側に平坦な充填構造を形成し、構造化された前記レジスト層を

除去することにより、平坦な充填構造を形成するステップを実施し、さらに、

前記平坦な充填構造は、前記半導体ボディ(14)の上面と同じ高さで平坦に形成され

ることを特徴とする、複数のオプトエレクトロニクス素子の製造方法。

10

20

**【請求項 2】**

複数の半導体ボディ(14)を複数のウェハ結合体から個別に前記半導体ボディ支持体(10)に運び、前記複数のウェハ結合体から運ばれた前記半導体ボディ(14)は、異なる波長の電磁放射の形成に適した活性層(16)を有する、請求項1記載の方法。

**【請求項 3】**

前記複数の半導体ボディ(14)を自由に選択可能なパターンで前記半導体ボディ支持体上に配置する、請求項1または2記載の方法。

**【請求項 4】**

前記複数の半導体ボディ(14)をウェハ結合体から補助支持体を用いて一緒に前記半導体ボディ支持体(10)に運ぶ、請求項1または2記載の方法。 10

**【請求項 5】**

前記半導体ボディ支持体(10)は半導体材料を含有し、該半導体材料内に保護ダイオードを形成し、該保護ダイオードを前記コンタクト構造の接続面に接続させる、請求項1から4までのいずれか1項記載の方法。

**【請求項 6】**

前記半導体ボディ支持体の上に保護ダイオードを配置し、該保護ダイオードを前記コンタクト構造の接続面に接続させる、請求項1から5までのいずれか1項記載の方法。

**【請求項 7】**

前記半導体ボディ支持体は接続面を有し、該接続面をスルーコンタクトを介して前記半導体ボディ支持体の前記第1の正面側とは反対側の面と接続し、オプトエレクトロニクス素子の表面実装を実施する、請求項1から6までのいずれか1項記載の方法。 20

**【請求項 8】**

前記平坦な充填構造はプラスチックを含む、請求項1から7までのいずれか1項記載の方法。

**【請求項 9】**

前記プラスチックはベンゾシクロブテンを含む、請求項8記載の方法。

**【請求項 10】**

1つまたは複数のオプトエレクトロニクス素子を前記半導体ボディ支持体の分割により個別化する、請求項1から9までのいずれか1項記載の方法。

**【請求項 11】**

複数のオプトエレクトロニクス素子を前記半導体ボディ支持体の分割により個別化し、複数のオプトエレクトロニクス素子から成る結合体を形成し、前記結合体の端部に位置するオプトエレクトロニクス素子をブリッジコンタクトを介して前記結合体の内側に位置するオプトエレクトロニクス素子と接触接続させる、請求項1から10までのいずれか1項記載の方法。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数のオプトエレクトロニクス素子の製造方法に関する。

**【0002】**

製造後に接続支持体上に固定されて接触接続されるべき複数のオプトエレクトロニクス素子を製造するために、各素子の製造のために個別に実施されなければならない一連の個別処理ステップが必要になることが多い。 40

**【0003】**

しかしながら個別処理ステップ、すなわち各素子に対して別々に実施されるステップは、複数の素子に対して同時に実施することができる処理ステップに比べてコストが掛かり、また煩雑である。

**【0004】**

本発明の課題は、簡単に製造することができる複数のオプトエレクトロニクス素子の製造方法を提供することである。 50

**【0005】**

この課題は、以下のステップを有する、複数のオプトエレクトロニクス素子の製造方法によって解決される：

それぞれに1つのコンタクト構造が設けられており、且つ、電磁放射の形成に適した活性層を半導体層列内に備えている半導体ボディを第1の主面上に有している半導体ボディ支持体を準備するステップ、

半導体ボディを覆うことなく、コンタクト構造および半導体ボディ支持体の上の領域を少なくとも部分的に覆う平坦な充填構造を第1の主面上に形成するステップ。

**【0006】**

本発明によれば、個々のオプトエレクトロニクス素子または1つのモジュールに統合される複数のオプトエレクトロニクス素子がウェハレベルの平面に構成される、オプトエレクトロニクス素子の製造コンセプトが提供される。このことは、半導体ボディ支持体上に配置されているオプトエレクトロニクス半導体ボディには充填構造によりケーシングが設けられることを意味する。

10

**【0007】**

このために例えばチップエンベロープが形成され、このチップエンベロープは、セラミックに類似する特性を有する不均一性のプラスチック、例えばエポキシシリコン混合物から成る。しかしながら、プラスチック固体粉末混合物から成る封止材料を使用することも考えられる。充填構造が平坦な層を形成することが製造コンセプトの特徴である。

**【0008】**

20

このことは後続の処理ステップ、例えば半導体ボディの電気的な結線、変換部の被着、または、レンズのような光学素子の形成を容易にする。これらの処理ステップを全てウェハレベル平面で実施することができる、冒頭で述べたような時間の掛かる個別処理ステップを大部分省略することができる。

**【0009】**

別の実施形態においては、平坦な充填構造を形成するステップが以下のように実施される。すなわち、少なくとも半導体ボディを覆う構造化されたレジスト層が形成され、構造化されたレジスト層の外側に平坦な充填構造が形成され、続いて構造化されたレジスト層が除去される。

**【0010】**

30

したがって、ケーシングとして使用される充填構造はリソグラフィ的な製造方法により形成され、これにより半導体ボディの製造時の通常のリソグラフィ的な精度をケーシングエンベロープにも拡張することができる。

**【0011】**

別の実施形態においては、半導体ボディがルミネセンスダイオードチップ、有利には薄膜ルミネセンスダイオードチップとして製造される。

**【0012】**

薄膜ルミネセンスダイオードチップの製造においては、殊に放射を放出する活性層を包含する機能的な半導体層列が先ず成長基板上にエピタキシャルに成長され、続けて新たな支持体が半導体層列の成長基板側とは反対側の表面に取り付けられ、その後、成長基板が除去される。殊に、窒化物化合物半導体のために使用される成長基板、例えば、SiC、サファイアまたはGaNは比較的高価なので、この方法は殊に成長基板を再利用できるという利点を提供する。窒化物化合物半導体から成る半導体層列からのサファイアから成る成長基板の引き剥がしを例えばリフトオフ法によって行うことができる。

40

**【0013】**

殊に、ルミネセンスダイオードチップは、II - V族化合物半導体材料、有利には窒化物化合物半導体を基礎とするエピタキシャル層列を有することができるが、リン化物化合物半導体材料またはヒ化物化合物半導体材料を基礎とするエピタキシャル層列も有することができる。

**【0014】**

50

本発明との関係において「窒化物化合物半導体を基礎とする」とは、活性エピタキシャル層列またはこの層列の内の少なくとも1つの層が窒化物II-V族化合物半導体材料、有利には $\text{Al}_x\text{Ga}_y\text{In}_{1-x-y}\text{N}$ (但し $0 < x < 1, 0 < y < 1$ , 且つ $x + y = 1$ )を含有することを意味している。その際、この材料は必ずしも上述の式に従った数学的に正確な組成を有していなくてもよい。むしろこの材料は、 $\text{Al}_x\text{Ga}_y\text{In}_{1-x-y}\text{N}$ 材料の特徴的な物理特性を実質的に変化させない、1つまたは複数のドーパントならびに付加的な成分を含有していてよい。しかしながら分かり易くするために、僅かな量の他の材料によって部分的に置換されている可能性があるにしても、上述の式には結晶格子( $\text{Al}, \text{Ga}, \text{In}, \text{N}$ )の主要な成分のみが含まれている。

## 【0015】

10

本発明との関係において「リン化物化合物半導体を基礎とする」とは、活性領域、殊に半導体ボディが有利には $\text{Al}_n\text{Ga}_m\text{In}_{1-n-m}\text{P}$ (但し $0 < n < 1, 0 < m < 1$ , 且つ $n + m = 1$ 、有利には $n = 0, n = 1, m = 0$ および/または $m = 1$ )を含有するか、その材料から構成されていることを意味している。その際、この材料は必ずしも上述の式に従った数学的に正確な組成を有していなくてもよい。むしろこの材料は、その物理特性を実質的に変化させない、1つまたは複数のドーパントならびに付加的な成分を含有していてよい。しかしながら分かり易くするために、僅かな量の他の材料によって部分的に置換されている可能性があるにしても、上述の式には結晶格子( $\text{Al}, \text{Ga}, \text{In}, \text{P}$ )の主要な成分のみが含まれている。

## 【0016】

20

本発明との関係において「ヒ化物化合物半導体を基礎とする」とは、活性領域、殊に半導体ボディが有利には $\text{Al}_n\text{Ga}_m\text{In}_{1-n-m}\text{As}$ (但し $0 < n < 1, 0 < m < 1$ , 且つ $n + m = 1$ 、有利には $n = 0, n = 1, m = 0$ および/または $m = 1$ )を含有するか、その材料から構成されていることを意味している。その際、この材料は必ずしも上述の式に従った数学的に正確な組成を有していなくてもよい。むしろこの材料は、その物理特性を実質的に変化させない、1つまたは複数のドーパントならびに付加的な成分を含有していてよい。しかしながら分かり易くするために、僅かな量の他の材料によって部分的に置換されている可能性があるにしても、上述の式には結晶格子( $\text{Al}, \text{Ga}, \text{In}, \text{As}$ )の主要な成分のみが含まれている。

## 【0017】

30

別の実施形態においては、半導体ボディ支持体を準備するステップは、半導体ボディ支持体上に被着される複数の半導体ボディをウェハ結合体から個別に半導体ボディ上に運ぶステップを含む。

## 【0018】

したがって、複数の半導体ボディを備えた半導体ボディ支持体は異なるウェハに由来するオプトエレクトロニクスチップセグメントを収容し、1つの新たな結合体を形成することができる。このことは、種々の半導体ボディの放射特性のばらつき、効率損失などの補償に有利である。つまり例えば、複数の半導体ボディを例えればウェハテスタを用いて事前に検査することができるので、オプトエレクトロニクス素子の放射特性は所期の仕様を満たす。

40

## 【0019】

別の実施形態では、種々の半導体ウェハに由来する半導体ボディを半導体ボディ支持体上に配置し、種々の色印象を有するモジュールまたはRGBモジュールを形成することができる。このために、例えば、従来から公知のピックアンドプレース技術を使用することができる。

## 【0020】

別の実施形態においては、半導体ボディ支持体を準備するステップは、半導体ボディ支持体上に被着される複数の半導体ボディをウェハ結合体から補助支持体を用いて一緒に半導体ボディ上に運ぶステップを含む。

## 【0021】

50

このために例えばフィルムを使用することができ、1つのウェハ上に製造された半導体ボディがこのフィルムに収容され、半導体ボディ支持体上に載置される。

【0022】

本発明の有利な実施形態および発展形態は従属請求項に記載されている。

【0023】

以下では、図面に示された複数の実施例に基づき本発明を詳細に説明する。

【0024】

機能的に同一の作用を有する素子、領域および構造には同一の参照番号を付している。素子、領域または構造が図面において対応している限り、それらに関して必要がなければ後続の各図面では説明しない。

10

【図面の簡単な説明】

【0025】

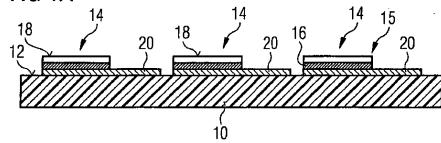

【図1A】オプトエレクトロニクス素子の実施例の概略的な断面図を示す。

【図1B】オプトエレクトロニクス素子の実施例の概略的な断面図を示す。

【図1C】オプトエレクトロニクス素子の実施例の概略的な断面図を示す。

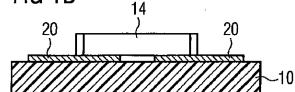

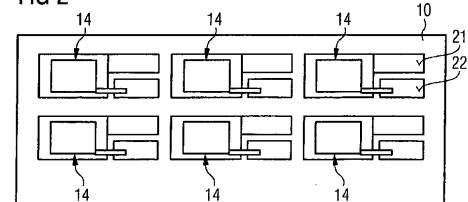

【図2】複数のオプトエレクトロニクス素子の別の実施例の平面図を示す。

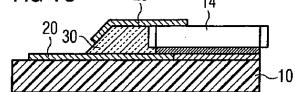

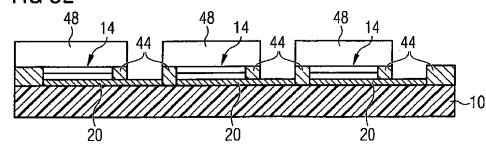

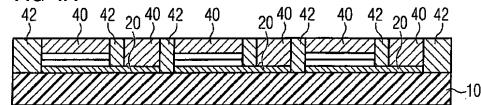

【図3A】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図3B】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

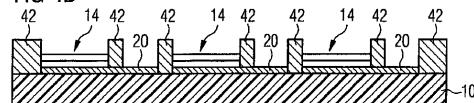

20

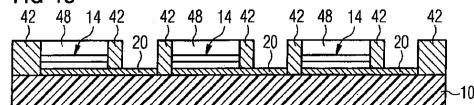

【図3C】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図3D】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図3E】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

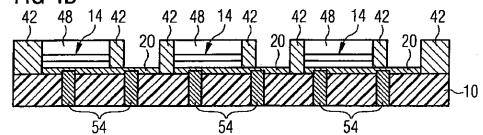

【図4A】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図4B】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

30

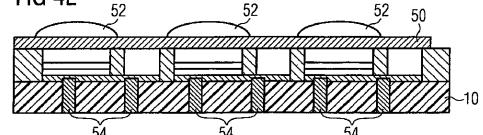

【図4C】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図4D】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図4E】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

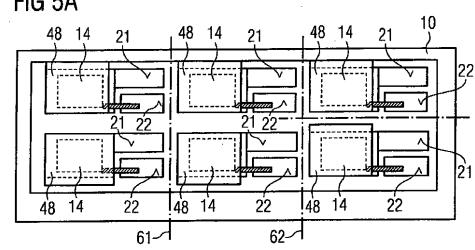

【図5A】オプトエレクトロニクス素子の別の実施例の平面図を示す。

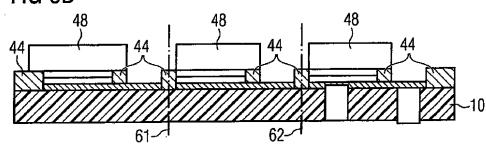

【図5B】図5Aによるオプトエレクトロニクス素子の概略的な断面図を示す。

【図6】オプトエレクトロニクス素子の別の実施例の平面図を示す。

【図7A】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

40

【図7B】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【図8】複数のオプトエレクトロニクス素子の別の実施例の平面図を示す。

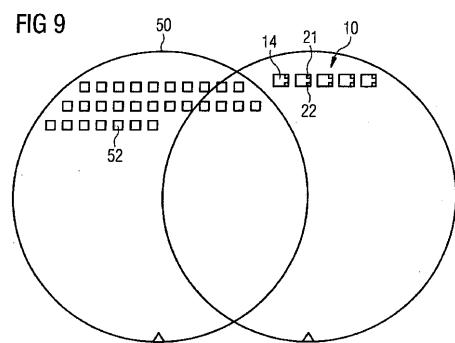

【図9】複数のオプトエレクトロニクス素子の実施例を示す。

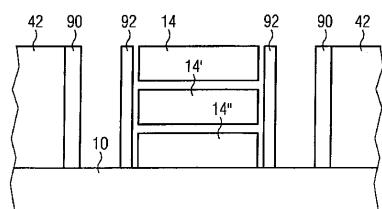

【図10】複数のオプトエレクトロニクス素子を製造するための別の実施例の概略的な断面図を示す。

【0026】

図1Aを参照しながら、以下では本発明による方法の出発点を説明する。図1Aは半導体ボディ支持体10を示し、この半導体ボディ支持体10においては第1の主面12上に

50

複数の半導体ボディ 14 が設けられている。

【0027】

半導体ボディ 14 はそれぞれ 1 つのコンタクト構造 20 を有し、このコンタクト構造 20 は半導体ボディ 14 の電気的な接触接続に適している。コンタクト構造 20 の上に配置されている半導体ボディ 14 は活性層 16 を有し、この活性層 16 は半導体層列 15 内に埋め込まれている。活性層 16 は有利には放射を形成するために構成されている。有利には、それぞれの半導体ボディがルミネセンスダイオード半導体ボディとして構成されている。

【0028】

さらに半導体ボディ 14 は半導体層列 15 を有する。半導体層列 15 は例えば 2 つの半導体層を有することができ、これら 2 つの半導体層の間には活性層 16 が配置されている。これらの半導体層は有利には導電型が異なるものであり、殊に異なる導電型にドープされている (n 導電型または p 導電型)。半導体ボディ 14 はさらに有利にはエピタキシャルに成長されている。

10

【0029】

本導体ボディ 14 のための半導体層構造を、例えば有機金属気相エピタキシャル法によって成長基板上にエピタキシャルに析出することができる。続いて、半導体層構造から例えばエッティングにより半導体ボディを形成することができる。

【0030】

半導体ボディ 14 の上面には放射放出面 18 が形成されており、この放射放出面 18 の面積は実質的に半導体構造の大きさに対応する。半導体ボディ 14 を例えば矩形に構成することができ、この矩形の辺長を広い範囲にわたり変更することができる。つまり一方では 50 μm よりも短い辺長を有する半導体ボディを形成することができるが、他方では 5 mm までの辺長を有する大面積の半導体ボディを使用することもできる。

20

【0031】

この実施例では、半導体層列 15 は例えば約 6 μm の厚さを有しているが、この値を広い範囲で変更することができる。通常の場合、コンタクト構造 20 は、例えばスパッタリングされた金属層からフォトリソグラフィ技術を用いて形成される金属路である。その厚さは通常の場合、数 μm である。

【0032】

30

図 1 A に示されている実施例は、半導体ボディの構造の 1 つのヴァリエーションを表しているに過ぎない。例えば、異なる構成の接触接続によって、すなわち接続支持体 20 を異なる構成で形成することによって、図 1 A による実施例とは異なる他の配置構成も考えられる。

【0033】

つまり図 1 B においては、両方の側面にそれぞれ 1 つのコンタクトを有し、このコンタクトがコンタクト構造 20 と接続されている半導体ボディ 14 が示されている。したがってこれらのコンタクトはこの実施例において対向する面に配置されている。

【0034】

しかしながらまた図 1 C に示されているように、半導体ボディの縁部を介して接触接続を行うことも考えられる。

40

【0035】

このために半導体ボディ 14 は半導体ボディ支持体 10 の上方に配置されており、また一方の面には絶縁材料 30 が設けられている。半導体層列との接続部を絶縁材料 30 の上ないし下に配置することができる。

【0036】

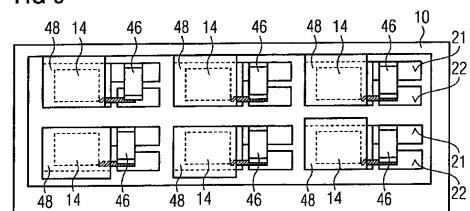

さらに有利には、図 2 に示されているように、半導体ボディ 14 は半導体ボディ支持体 10 上に規則的なパターンに従って配置されている。図 2 に示されている平面図からは、半導体ボディ 14 が例えばマトリクスの形態で配置されていることが見て取れる。

【0037】

50

半導体ボディ 14 を自由に選択できるパターンで半導体ボディ支持体 10 上に配置することができる。多数の半導体ボディ 14 は例えば 1 つのウェハ結合体に由来するものでなく、この場合には半導体ボディ 14 は個別に半導体ボディ支持体 10 上に運ばれる。このために、従来から公知のピックアンドプレース法を使用することができる。

#### 【 0 0 3 8 】

したがって、例えば半導体ボディ支持体 10 の上に配置すべき半導体ボディ 14 をその放射特性に関して事前に選択するために、ウェハ結合体の半導体ボディ 14 を既に製造後に検査することができる。しかしながらまた、例えば電磁放射の形成に適した種々の活性層 16 を有する種々のウェハ結合体の半導体ボディを使用することもでき、それにより半導体ボディ支持体 10 上の半導体ボディ 14 は種々の波長の電磁放射を放出することができる。10

#### 【 0 0 3 9 】

同様に別の実施形態においては、ウェハ結合体の半導体ボディを補助支持体、例えばフィルム、有利には放熱フィルムを用いて半導体ボディの上に運ぶことも可能である。この場合には殊に個別処理ステップを省略することができる。

#### 【 0 0 4 0 】

以下では、図 3 A から 3 E を参照しながら、複数のオプトエレクトロニクス素子を製造するための第 1 の実施例を説明する。この方法では、図 1 A から図 1 C において説明した、半導体ボディ支持体 10 上に配置されている半導体ボディ 14 が出発点となる。20

#### 【 0 0 4 1 】

図 3 A に示されているように、第 1 のステップにおいては、フォトトラック層が被着され、続いて構造化される。フォトトラック層の構造化を例えば従来技術から公知のフォトリソグラフィ的な露光によって実施することができる。構造化の結果、フォトレジスト構造 40 が得られ、このフォトレジスト構造 40 は半導体ボディ 14 ならびにコンタクト構造 20 の一部を覆う。フォトレジスト層は、半導体ボディ 14 の側面にはそれぞれこのフォトレジスト層が覆っていない領域が生じるように構造化される。フォトレジスト層はまた隣接する半導体ボディのコンタクト構造 20 の間においても除去される。20

#### 【 0 0 4 2 】

半導体ボディ支持体 10 に対して多くの材料を使用することができる。つまり、例えば、セラミック基板またはシリコン基板を使用することができる。考えられる別の材料には、酸化マグネシウム、酸化アルミニウム、サファイア、窒化アルミニウムまたは当業者には公知の別の材料が含まれる。30

#### 【 0 0 4 3 】

図 3 B には、充填層を被着し、続いてこの充填層を平坦化するステップが示されている。これにより充填構造が得られ、この充填構造はフォトレジストが除去されている部分に埋められている。平坦化を行うステップによって充填構造 42 はレジスト構造 40 と実質的に同一の高さを有する。充填材料は例えばプラスチックでよい。有利にはベンゾシクロブテンが使用される。

#### 【 0 0 4 4 】

図 3 C に示されている後続のステップにおいては、レジスト構造 40 が除去され、さらなる平坦化ステップが実施される。さらなる平坦化ステップによって充填構造 42 の高さが低減され、これにより半導体ボディ 14 の上面と同じ高さの平坦な充填構造 44 が形成される。40

#### 【 0 0 4 5 】

したがって、他の全ての処理ステップをウェハ結合体のレベルの平坦な系で実施することができる。他の処理ステップには、保護ダイオードの形成、変換部の被着、反射層の形成またはレンズのような光学素子の被着が含まれる。しかしながら、それらの別の処理ステップを必ずしも全て実施する必要はないことを言及しておく。つまり、例えば、変換部を必要としないオプトエレクトロニクス素子、または保護ダイオードが無くとも駆動するオプトエレクトロニクス素子を製造することも可能である。したがって、以下において説50

明する処理ステップは単に例示的なものに過ぎない。

**【0046】**

図3Dには、保護ダイオード46を形成するステップが示されている。この保護ダイオード46は接続支持体20の相応の第1のコンタクト面21ないし第2のコンタクト面22の上に配置される。さらにこの処理ステップにおいては電気的な接続も実施される。

**【0047】**

図3Eには、半導体ボディ14の放射面の上に変換部を形成するステップが示されている。変換層は、例えば、少なくとも1つのルミネセンス変換材料が埋め込まれているシリコン層である。少なくとも1つのルミネセンス変換材料は、例えばYAG:Ceまたは公知のルミネセンス変換材料でよい。

10

**【0048】**

ルミネセンス変換材料によって、例えば、活性層12から放出される、例えば緑色光、青色光または紫外線光である放射の少なくとも一部の波長が白色光を生じさせるように相補的なスペクトル領域に変換される。

**【0049】**

シリコン層をルミネセンス変換材料のためのキャリア層として使用することは、短波長の青色または紫外線の放射に対してシリコンが比較的鈍感であるという利点を有する。このことは殊に、放出される放射が通常は短波長の青色または紫外線のスペクトル領域の成分を少なくとも一部含んでいる、窒化物化合物半導体を基礎とするルミネセンスダイオードチップにとって有利である。択一的に、他の透明な有機材料または無機材料も少なくとも1つのルミネセンス変換材料のためのキャリア層として機能することができる。

20

**【0050】**

別の処理ステップは反射性のコンタクト層としてのコンタクト層の被着を含む。さらに、コンタクト層20と結合層との間にバリア層を配置することもできる。バリア層は例えばTiWNを含有する。殊にバリア層によって、例えばはんだ層である結合層の材料の反射性のコンタクト層への拡散が阻止される。このような材料の拡散は殊に反射性のコンタクト層の反射を劣化させる虞がある。しかしながらこれらのステップは当業者に周知があるので、ここでは詳細には説明しない。

**【0051】**

変換部を例えば支持体フィルムの上に準備し、1つのステップで複数のオプトエレクトロニクス素子のそれぞれの半導体ボディの上に運ぶことができる。したがって、個々のオプトエレクトロニクス素子の時間の掛かる個別処理ステップを省略することができる。変換部48の変換材料に関しては従来技術から種々の製造方法が公知である。

30

**【0052】**

以下では、図4Aから4Eを参照しながら、複数のオプトエレクトロニクス素子を製造するための第2の実施例を説明する。

**【0053】**

図4Aから図4Eによる方法は、充填構造のさらなる平坦化を行うステップが省略される点で前述の方法とは異なる。したがって、レジスト構造は半導体ボディの放射放出面を越えて突出しており、これにより半導体ボディの上方には中空部が生じる。

40

**【0054】**

したがってこの中空部を、図4Cに示されているように、変換部48で充填するために使用することができる。このために有利には、液状の凝集状態で存在し、中空部への充填後に硬化する変換材料が使用される。さらには、放射放出面と変換部との間に空隙を残すか、カバーを設けることが同様に行われている。このことは、紫外線領域の放射を放出するオプトエレクトロニクス素子を使用する際の熱的な利点を有する。

**【0055】**

さらなるステップが図4Dに示されている。この図4Dにおいては、コンタクト構造20のコンタクト面21, 22を第1の主面12側とは反対側の面からスルーコンタクト54(いわゆるバイア)によって接触接続することが示されている。したがって、表面実装

50

に適しているオプトエレクトロニクス素子の製造が可能である。

**【0056】**

図3または図4には示していない別のヴァリエーションは保護ダイオードの形成に関する。殊に、半導体ボディ支持体10としてシリコン基板を使用する場合、例えば適切なドーピングによって保護ダイオードを半導体ボディ10内に直接形成することができる。

**【0057】**

相応の寸法設計によって、すなわちドープされる領域の大きさを適合させることによって、保護ダイオードの電気的な特性をそれぞれの用途に適合させることができる。

**【0058】**

このヴァリエーションは殊に、図3Dに示したような外部保護ダイオードのコストの掛かる実装を省略する。

10

**【0059】**

図4Eには、オプトエレクトロニクス素子の上に光学系を被着するステップが示されている。この実施例において光学系は、支持体50の上に配置されている複数のレンズ52から構成されている。したがって、半導体ボディ支持体10上のオプトエレクトロニクス素子の各々に対して1フレンズ52が1つの処理ステップで形成される。

**【0060】**

以下では、図5Aおよび図5Bを参照しながら、本発明の別の実施例を説明する。図示されている処理ステップは図3Aから図3Eまたは図4Aから図4Eによるステップに統一して行われるものである。

20

**【0061】**

図5Aに示されているように、規則的なパターンで半導体ボディ支持体10上に配置されている複数のオプトエレクトロニクス素子を個別化することができる。

**【0062】**

半導体ボディ10は図5Aの紙面に関して水平方向においても垂直方向においても分割される。図5Aに示されているように、例えば、1つまたは2つのルミネセンスダイオードチップを含むモジュールを形成することができる。

**【0063】**

このために、例えば、図5Bにおいて切断線61および62に基づき概略的に示されているように、隣接する半導体ボディ14間の充填材料の位置で切断が行われる。

30

**【0064】**

図6に基づき、別の実施例における保護ダイオード46の実装を詳細に説明する。保護ダイオード46は例えば表面実装法により第1のコンタクト面21および第2のコンタクト面22上に配置される。保護ダイオード46の被着は有利には、オプトエレクトロニクス素子の個別化の前に実施される。

**【0065】**

以下では、図7Aおよび図7Bを参照しながら、本発明の別のヴァリエーションを説明する。

**【0066】**

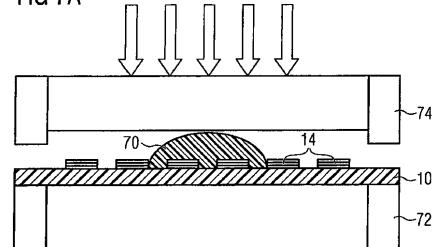

このヴァリエーションは充填材料の被着に関する。充填材料はこの実施例によれば封止材料より成る。このために半導体ボディ支持体10に対して封止材料70が準備される。封止材料を例えば滴の形で落とすことができる。

40

**【0067】**

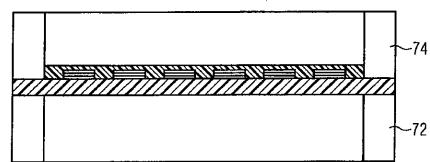

半導体ボディ支持体10は2つのワークピース72と74との間に配置され、これら2つのワークピース72, 74が加熱される。上側のワークピース74は、半導体ボディ支持体10上の半導体ボディ14と接触しないために開口部(キャビティ)を有する。プレスによって封止材料70が半導体ボディ14間に押し付けられる。平坦化ステップを実施した後に、図3Bないし図4Bに基づき説明した、さらなる処理ステップが続けて実施される。

**【0068】**

50

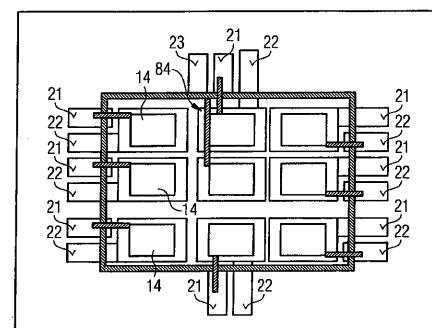

図 8 には別の実施形態が示されており、この実施形態においては複数のオプトエレクトロニクス素子が共通の結合支持体上に被着されている。

#### 【 0 0 6 9 】

図 8 から見て取れるように、外側に配置されている半導体ボディ 1 4 には接続面 2 1 ないし 2 2 がそれぞれ設けられている。この配置構成において内側に設けられている半導体ボディは、その上に配置されているチップの導体路を介して延びるブリッジコンタクト 8 4 によりコンタクトフィールド 2 3 へと案内される。

#### 【 0 0 7 0 】

この実施形態によれば、複数のオプトエレクトロニクス素子から構成されている任意の大きさのモジュールを形成することができる。上述したように、複数の個別処理ステップを実施する必要なく、オプトエレクトロニクス素子を形成することができる。10

#### 【 0 0 7 1 】

このことを、図 9 を参照しながらもう一度概説する。この図 9 には複数のオプトエレクトロニクス素子を含む半導体ボディ支持体 1 0 が示されている。半導体ボディ支持体 1 0 は例えば 6 インチウェハでよい。左側には、ウェハ結合体で製造される複数のレンズが示されている。したがって、例えば半導体ボディ 1 4 の上への光学素子の被着を単一のステップで、半導体ボディ支持体上の複数のオプトエレクトロニクス素子に対して実施することができる。

#### 【 0 0 7 2 】

別の実施例が図 1 0 に示されている。この実施例によれば、例えば赤色、緑色または青色を放射する半導体ボディを形成するために、例えば 3 つの半導体層列から成り、それぞれに異なる活性層が設けられている、いわゆる積層化半導体ボディが使用される。20

#### 【 0 0 7 3 】

これらの半導体ボディは上下に重なって配置されており、その下にはミラー層、拡散バリアおよびはんだ層を配置することができる。この積層体の側縁には例えばパッシベーション層を配置することができる。

#### 【 0 0 7 4 】

さらには、充填材料の側縁に同様にミラー 9 0 を形成することもできる。充填材料の側縁のエッジ角は可変でよい。パッシベーション層 9 2 ないし側縁に配置されるミラーを形成するために、図 3 A から図 3 E ないし図 4 A から図 4 E と同様に実施されるプロセスを実行することができる。30

#### 【 0 0 7 5 】

しかしながらこのプロセスは、例えば図 3 A に示されているようなレジスト層の構造化が、このレジスト層が半導体ボディ 1 4 の側縁も覆うように実施される点において異なる。したがって、半導体ボディ 1 4 と充填構造との間のレジスト構造を除去した後には空隙が生じ、この空隙にパッシベーション層ないしミラーを設けることができる。

#### 【 0 0 7 6 】

本発明は実施例に基づいた説明によって制限されるものではない。むしろ本発明はあらゆる新規の特徴ならびにそれらの特徴のあらゆる組み合わせを含むものであり、これには特に特許請求の範囲に記載した特徴の組み合わせ各々が含まれ、このことはそのような組み合わせ自体が特許請求の範囲あるいは実施例に明示的には記載されていないにしてもあてはまる。40

#### 【 0 0 7 7 】

本願は、ドイツ連邦共和国特許出願 102008030815.3 の優先権を主張するものであり、その開示内容は参考により本願に取り入れられる。

【図 1 A】

FIG 1A

【図 1 B】

FIG 1B

【図 1 C】

FIG 1C

【図 2】

FIG 2

【図 3 E】

FIG 3E

【図 4 A】

FIG 4A

【図 4 B】

FIG 4B

【図 4 C】

FIG 4C

【図 3 A】

FIG 3A

【図 3 B】

FIG 3B

【図 3 C】

FIG 3C

【図 3 D】

FIG 3D

【図 4 D】

FIG 4D

【図 4 E】

FIG 4E

【図 5 A】

FIG 5A

【図 5 B】

FIG 5B

【図 6】

FIG 6

【図 7 A】

FIG 7A

【図 7 B】

FIG 7B

【図 8】

FIG 8

【図 9】

FIG 9

【図 10】

FIG 10

---

フロントページの続き

(74)代理人 100112793

弁理士 高橋 佳大

(74)代理人 100128679

弁理士 星 公弘

(74)代理人 100135633

弁理士 二宮 浩康

(74)代理人 100156812

弁理士 篠 良一

(74)代理人 100114890

弁理士 アインゼル・フェリックス=ラインハルト

(72)発明者 ジークフリート ヘルマン

ドイツ連邦共和国 ノイキルヒエン ハウプトシュトラーセ 24

審査官 村井 友和

(56)参考文献 特開2008-027999(JP,A)

特開2006-108204(JP,A)

特開平11-177138(JP,A)

特開2005-322923(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64