OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 198 229**

(51) Int. Cl.:

**H04M 19/02** (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

(86) Número de solicitud europea: **03006491 .9**

(86) Fecha de presentación : **17.07.1995**

(87) Número de publicación de la solicitud: **1320249**

(87) Fecha de publicación de la solicitud: **18.06.2003**

(54) Título: **Generador de señal de llamada.**

(30) Prioridad: **21.07.1994 US 278471**

(73) Titular/es:

**INTERDIGITAL TECHNOLOGY CORPORATION**

3411 Silverside Road, Concord Plaza

Suite 105, Hagley Building

Wilmington, Delaware 19810, US

(45) Fecha de publicación de la mención BOPI:

**01.11.2007**

(72) Inventor/es: **Estulin, Walter;**

**Huah, Jim J.;**

**Kaewell, John;**

**Kinney, Kevin;**

**Lemmo, Mark A.;**

**Regensburg, Michael W.;**

**Vanderslice, William T., Jr. y**

**Vessal, David**

(45) Fecha de la publicación del folleto de la patente:

**01.11.2007**

(74) Agente: **Elzaburu Márquez, Alberto**

ES 2 198 229 T3

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

## DESCRIPCIÓN

Generador de señal de llamada.

5 Esta invención está relacionada con un método y un aparato de control del consumo de energía de una estación de un sistema de comunicaciones, en el cual se ejerce el control en distintos grados de diferentes estados de funcionamiento de la estación.

## Antecedentes de la invención

10 Ha habido desde hace mucho tiempo un gran interés en contener el consumo de energía eléctrica en circuitos electrónicos que pueden depender de fuentes de alimentación limitadas, tales como baterías o paneles solares. El interés ha sido especialmente acusado en estaciones de sistemas de radioteléfonos que son portátiles o bien están localizados en zonas geográficas que no están servidas adecuadamente por las instalaciones de distribución de energía eléctrica. Tal estación es denominada aquí a menudo una unidad de estación de abonado, o simplemente una unidad de abonado. El interés se ha enfocado incluso más estrechamente a medida que ha crecido la preocupación sobre la necesidad de contener la polución de distintas clases.

20 En el campo de los radioteléfonos, se han hecho varios tipos de esfuerzos para limitar el consumo de energía. Son bien conocidos los transmisores (VOX) que funcionan con voz, en los cuales la presencia o ausencia de una señal real de voz apaga o enciende la fuente de alimentación del transmisor, siendo un ejemplo de ello la patente de Estados Unidos 4.130.731 de D. R. Bolgiano y otros. En otro caso, una unidad de abonado que incluya tal transmisor está siempre encendida durante todos los estados de funcionamiento. Se ha recurrido a diversos esfuerzos de conservación de la energía para habilitar periódicamente, al menos a los circuitos receptores de una unidad de abonado mientras que la unidad está en modo de espera, esperando la disponibilidad de un canal o esperando el inicio de una llamada, siendo algunos ejemplos las patentes de Estados Unidos 4.272.650 de D.R. Bolgiano y otros y la 5.203.020 de H. Sato y otros. Los circuitos de la unidad de abonado en estos últimos sistemas están, en otro caso, siempre encendidos durante el tratamiento real de la señal de llamada. El término "tratamiento de la señal de llamada" se refiere a las operaciones tales como, por ejemplo, amplificación filtrado, codificación/descodificación, interpolación, o modulación con respecto a las señales de cualquier tipo para la comunicación entre estaciones.

25 En la patente de Sato y otros, cuando una unidad de abonado en un sistema de telecomunicaciones móviles está en un lugar donde no es capaz de ser servida en ninguno de los canales del sistema, es alimentada periódicamente para comprobar la disponibilidad de un canal apropiado; y en otro caso, todos los componentes excepto un temporizador están apagados. Cuando se ha encontrado un canal disponible, y mientras se espera el inicio de una llamada, la unidad central de proceso (CPU) y un temporizador están alimentados continuamente mientras que el resto de la unidad es alimentada periódicamente para comprobar el inicio de una llamada. Finalmente, durante la conexión de una llamada, toda la unidad de abonado está alimentada continuamente.

30 40 En otro grupo de sistemas, las unidades de abonado son encendidas o apagadas como un grupo, y se prevén unas disposiciones especiales para encender una unidad de abonado si fuera necesario cuando otras están apagadas. Algunos ejemplos incluyen las patentes de Estados Unidos 4.964.121 de M.A.Moore, 4.509.199 de M.Ichihara y 4.577.315 de S. Otsuka. De forma similar, en la patente de Estados Unidos 4.713.809 de Y. Mizota, se enciende una estación repetidora para un sistema de acceso múltiple por división de tiempos (TDMA), solamente en aquellas ventanas de tiempos TDMA en la cual la unidad de abonado servida por ella está activa.

45 Las unidades de abonado para sistemas de radioteléfono, tales como la unidad de abonado de la patente de Estados Unidos núm. 5.008.900 de D.N Critchlow y otros, han incluido medios para apagar un componente de consumo de energía relativamente alto en un momento seleccionado determinado por la función de la unidad de abonado realizada en ese momento. Por ejemplo, en esa patente de Critchlow y otros, se apaga temporalmente un chip de procesador, incluido en la unidad para controlar los diversos componentes de la unidad, así como para realizar ciertas funciones de tratamiento de la señal, cuando no hay una llamada telefónica en curso. El apagado tiene lugar como respuesta a la ejecución de una instrucción de inactividad en el funcionamiento del programa de la unidad. El funcionamiento normal se reanuda temporalmente como respuesta a una señal de interrupción, y si no hay rutina de servicio a realizar, el procesador vuelve al estado apagado. En otro caso, los componentes de la unidad de abonado aparecen encendidos.

50 55 En la patente de Estados Unidos núm. 4.675.863 de E. Paneth y otros, se hace funcionar un módem en modo semidúplex en una unidad de abonado que funciona en un entorno TDMA. En ese modo, la sección receptora de desmodulación y la sección transmisora de modulación del módem funcionan en momentos diferentes; así, el amplificador de potencia de la sección de radiofrecuencia (RF) está activo durante no más de la mitad del tiempo. Otras componentes de la unidad aparecen funcionando continuamente.

60 La patente de Estados Unidos núm. 5.323.456 (Oprea) describe un botón de llamada controlado digitalmente. Este sistema está destinado al uso con una señal de control desde una línea telefónica u otra línea, generalmente en forma de una señal de LLAMADA estándar de 90 voltios, que está presente en una línea telefónica del Servicio Telefónico Tradicional (POTS). La patente de Estados Unidos núm. 4.477.697 (Judd y otros colaboradores), describe un circuito de llamada telefónica que proporciona distintas frecuencias de llamada. Esto proporciona una llamada personalizada o una llamada distintiva extendida. La patente de Estados Unidos núm. 4.584.576 (Forestier y otros colaboradores),

describe un generador de llamada utilizado para un grupo de líneas de abonado. Los circuitos amplificadores generan los estados de llamada y no llamada deseados. La patente de Estados Unidos n.º 5.001.748 (Burns y otros colaboradores), describe un generador de llamada de potencia menor capaz de superponer una señal de onda sinusoidal analógica sobre una señal de polarización de CC. La patente de Estados Unidos n.º 4.942.600 (Suzuki), describe un circuito para generar una señal ficticia de llamada y una detección de respuesta ficticia de una máquina de facsímil. La generación de timbres de llamada, tonos y cadencia para cargas no conmutadas es conocida como se describe, por ejemplo, en el artículo de Pavelka, *Ringing, Tone and Cadence Requirements for Nonswitched Loads in Digital Central Offices* (Requisitos de llamada, tono y cadencia para cargas no conmutadas en centrales telefónicas digitales), Intelec '88 - Tenth International Telecommunications Energy, IEEE, 30-Oct-1988, páginas 326-333, XP010078375.

Las unidades de abonado, en lugares relativamente difíciles de alcanzar, están equipadas frecuentemente con una fuente de alimentación de reserva que utiliza baterías apoyadas por paneles solares o un cargador de corriente alternativo. A pesar de los esfuerzos de los tipos descritos anteriormente, algunas unidades de abonado en sistemas de comunicaciones inalámbricos TDMA, que tienen la capacidad de ser operados con una alimentación de baterías de reserva con una apropiada facilidad de carga, han tenido que usar múltiples baterías de reserva para suministrar la energía necesaria. En algunas de tales unidades, se ha empleado una pareja de baterías de 15 amperios·hora y 12 voltios y una fuente de carga de cuatro a seis paneles solares.

## Sumario de la invención

De acuerdo con la presente invención, ciertos componentes de circuitos de una unidad de abonado de un sistema TDMA de radioteléfonos son apagados de manera recurrente durante la conexión de una llamada. Las partes apagadas durante distintas ventanas de tiempo de cada trama de tiempo TDMA recurrente no son requeridas para el funcionamiento del tratamiento de la señal en las respectivas ventanas de tiempo de la trama. En otras palabras, hay un mosaico cambiante de partes activas del circuito de una unidad de abonado que son apagadas y encendidas de una ventana de tiempo a otra para limitar dinámicamente el consumo de energía de la unidad.

De acuerdo con un aspecto de la invención la necesidad de circuitos especiales para distribuir señales de control del consumo de energía se reduce empleando los caminos de control o de señal de llamada, según sea apropiado, para distribuir órdenes de control de consumo de energía. Se emplean varias técnicas de implantación del control para reducir la necesidad de circuitos especializados para el control del consumo de energía.

Esas técnicas incluyen, ilustrativamente, la conmutación controlable del camino de corriente de la fuente de alimentación a un componente del circuito, o el control a distancia de la frecuencia de salida de una fuente de reloj para ciertos componentes del circuito sincronizados que son realizados con tecnología de semiconductores en los cuales el consumo de energía es afectado por la velocidad del reloj, o reducir la señal de entrada a un circuito que consume menos energía cuando responde a poca o ninguna señal de entrada, o reducir la corriente de polarización suministrada a un amplificador, o distribuir señales de órdenes a componentes del circuito disponible comercialmente que normalmente están provistos de una conexión de entrada de apagado.

En un modo de realización, los circuitos de la unidad de abonado incluyen una unidad de interfaz de línea para acoplar los componentes del circuito de tratamiento de señales de la unidad de abonado con un terminal telefónico. La unidad de abonado incluye también, en una sola placa de circuitos, junto con la unidad de interfaz de línea y otros componentes del circuito de la unidad de línea, una ranura de expansión, o cabezal de conector, para proporcionar funciones de interfaz con la línea para servicios adicionales del mismo o diferente tipo para compartir la utilización de los circuitos de la unidad de abonado.

Una unidad de abonado de acuerdo con la invención, funciona en un sistema TDMA que incluye una estación de red que proporciona un canal de control por radio (RCC) para comunicarse con unidades de abonado activadas que no están ocupadas con una conexión de llamada. La unidad de abonado utiliza las ventanas de tiempo del sistema TDMA y las disposiciones de sincronización de tramas para encender periódicamente, principalmente solo aquellos componentes del circuito necesarios para tomar muestras del RCC para determinar si hay o no tráfico de llamadas en la unidad. En un modo de realización, no se utiliza más de una ventana de tiempo por trama TDMA con ese fin en el canal RCC. En algunas aplicaciones, es posible utilizar además solamente una ventana de tiempo cada dos tramas o más.

Se conserva energía adicional limitando el circuito de bucle de abonado entre la unidad de abonado servidora y cualquier instrumento de comunicaciones de abonado servido (por ejemplo un teléfono) a una longitud de bucle que es sustancialmente inferior a la longitud de un radio enlace a una estación base a la cual la unidad de abonado acopla el circuito en bucle.

Además, se emplea un controlador de llamada controlado convenientemente, en el cual se puede programar digitalmente una frecuencia de llamada, y la cadencia del sonido o silencio de la llamada y el consumo de energía son controlados por una señal de nivel binario.

El control del nivel de consumo de energía en la unidad de abonado es inhabilitado y habilitado bajo el control de un termostato dentro de la caja de la unidad de abonado, para ayudar a mantener una temperatura mínima predeterminada dentro de la caja.

# ES 2 198 229 T3

La presente invención proporciona un aparato para generar una señal de llamada, de acuerdo con la reivindicación 1.

## Breve descripción de los dibujos

5 Puede conseguirse una comprensión más completa de la invención y de sus diversas características, objetos y ventajas, al considerar la siguiente descripción detallada y las reivindicaciones anexas, junto con los dibujos que se acompañan, en los cuales:

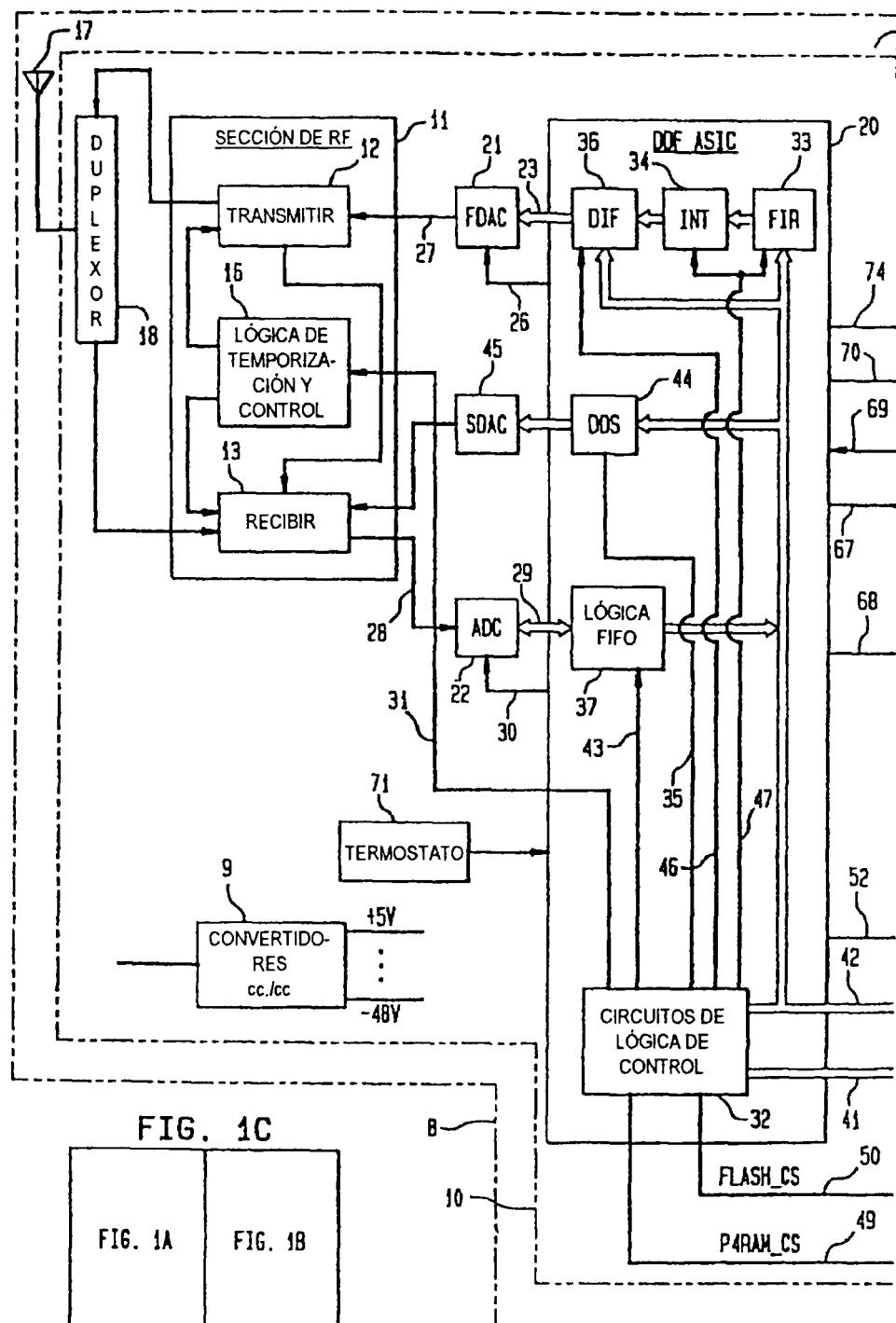

10 Las figuras 1A y 1B tomadas en conjunto como se ilustra en la figura 1C, son un diagrama de bloques y de líneas de una unidad de abonado de acuerdo con la presente invención; y están designadas simplemente como "Fig. 1" cuando se hace referencia a la unidad de abonado completa;

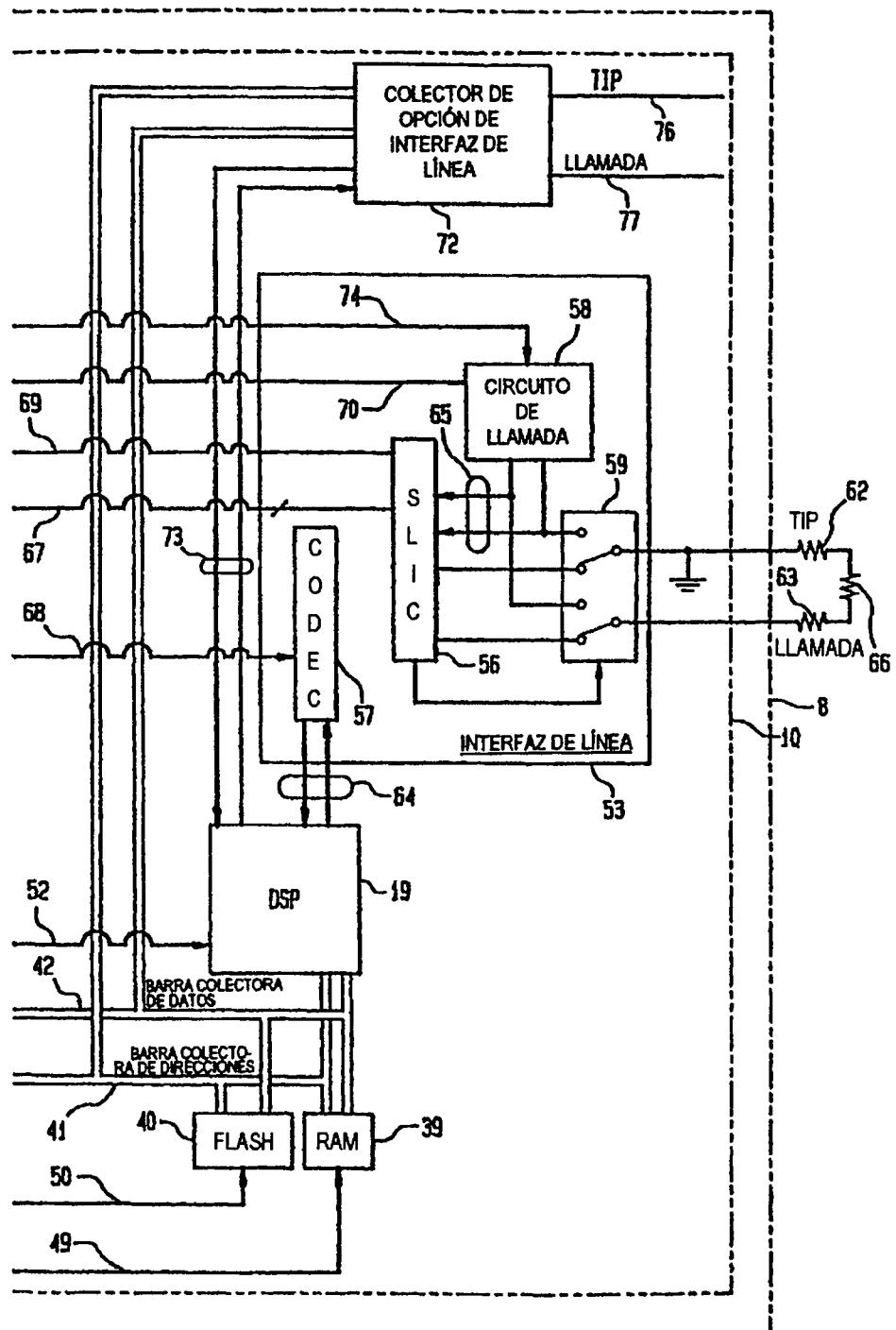

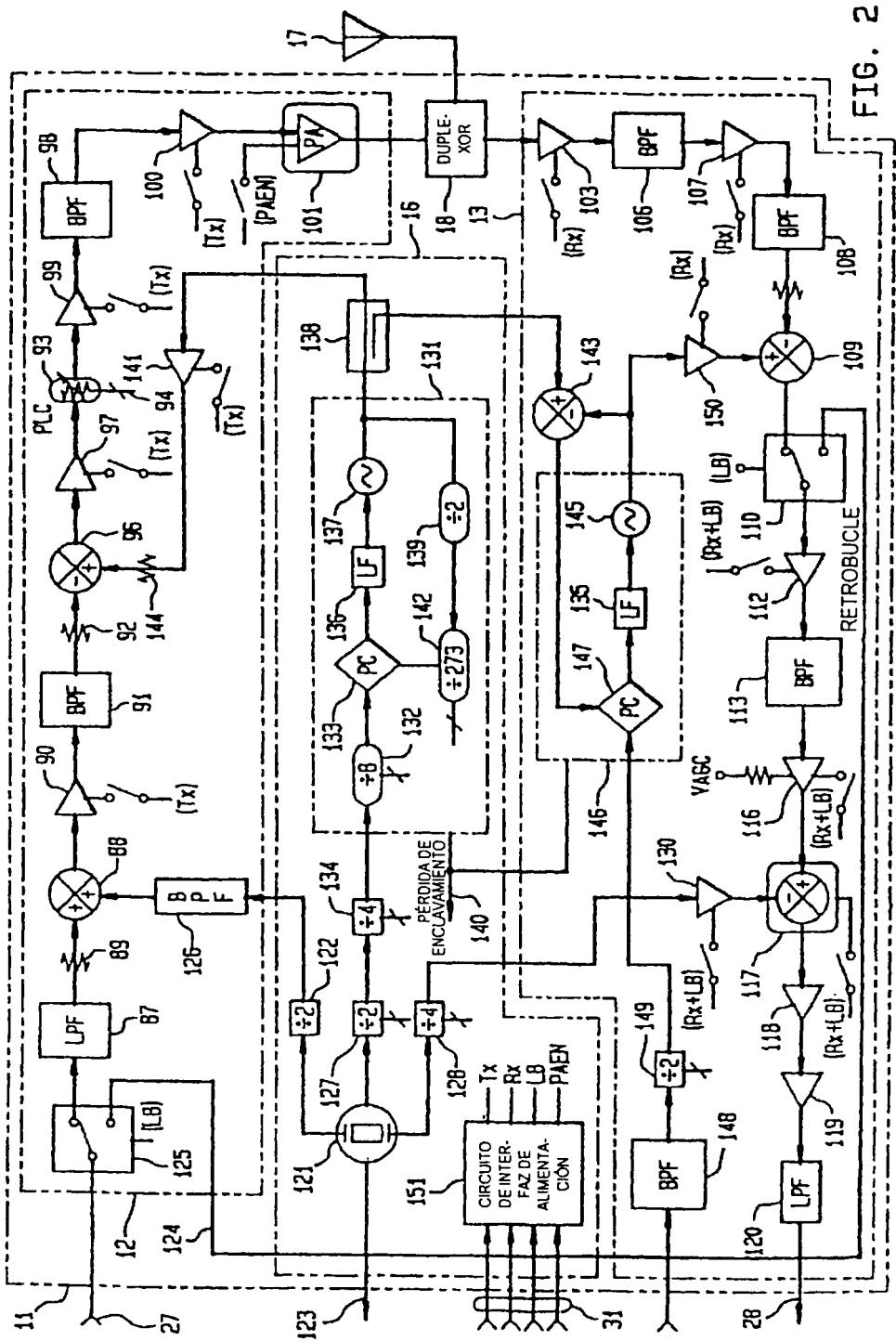

15 la figura 2 es un diagrama de bloques y de líneas de la sección de radiofrecuencia (RF) de la unidad de abonado de la figura 1;

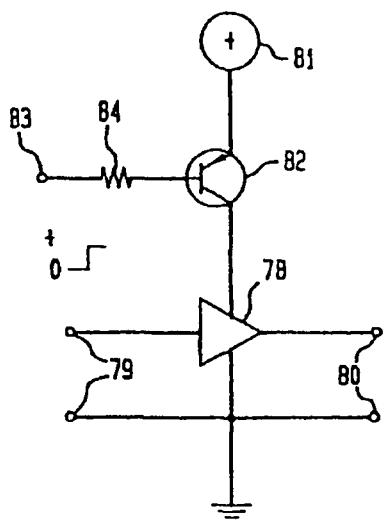

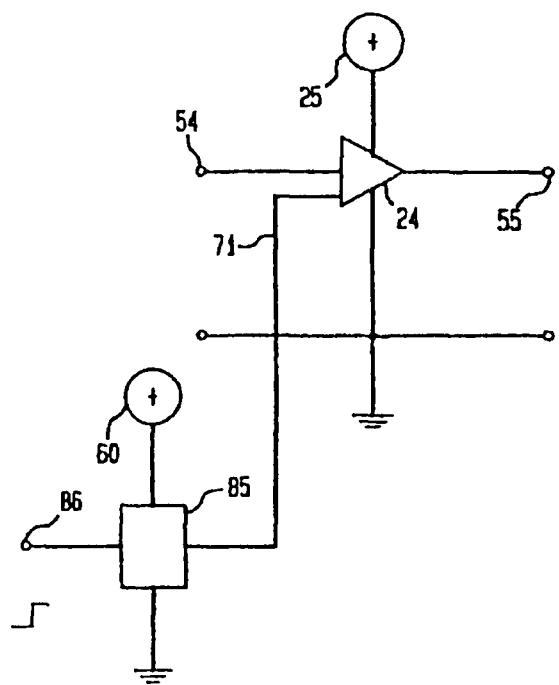

la figura 3 es un diagrama esquemático de un modo de realización de un circuito de control del apagado de la corriente de la fuente de alimentación;

20 la figura 4 es un diagrama esquemático de un circuito de control de apagado de una corriente de polarización;

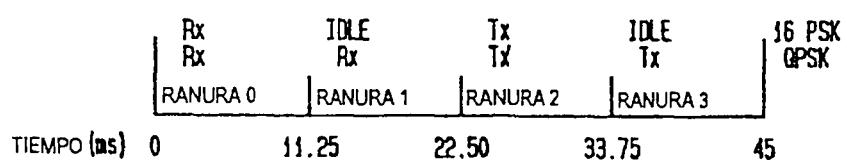

la figura 5 es un diagrama de la estructura de ventanas de la técnica anterior, utilizado en un modo de realización ilustrativo de la unidad de abonado de la figura 1;

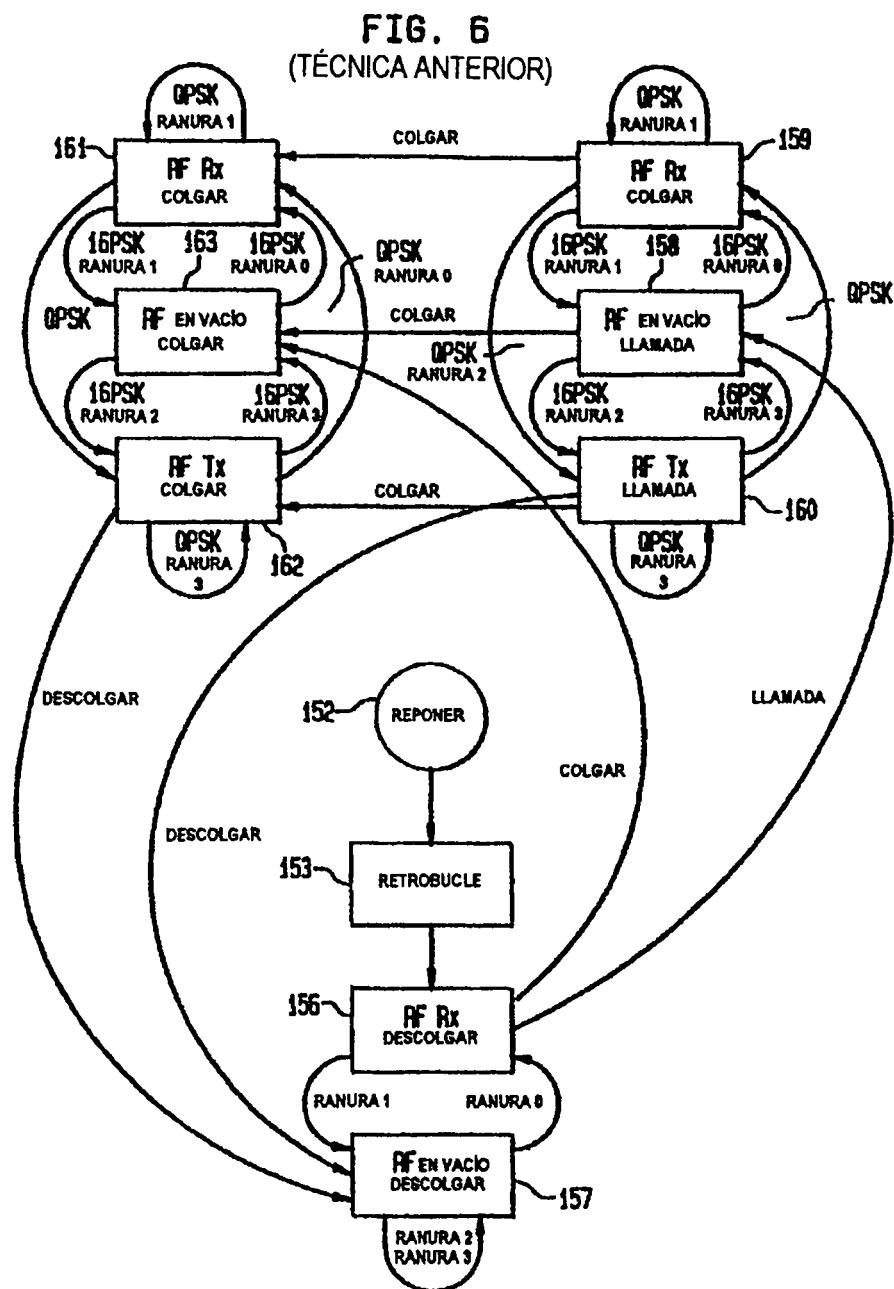

25 la figura 6 es un diagrama de estados que ilustra aspectos de la técnica anterior del funcionamiento TDMA de la unidad de abonado de la figura 1 y que utiliza la estructura de ventanas de la figura 5, tanto para el funcionamiento en modulación por desplazamiento de fases en cuadratura (QPSK) como para el funcionamiento en modulación por desplazamiento de fase de 16 fases (16PSK);

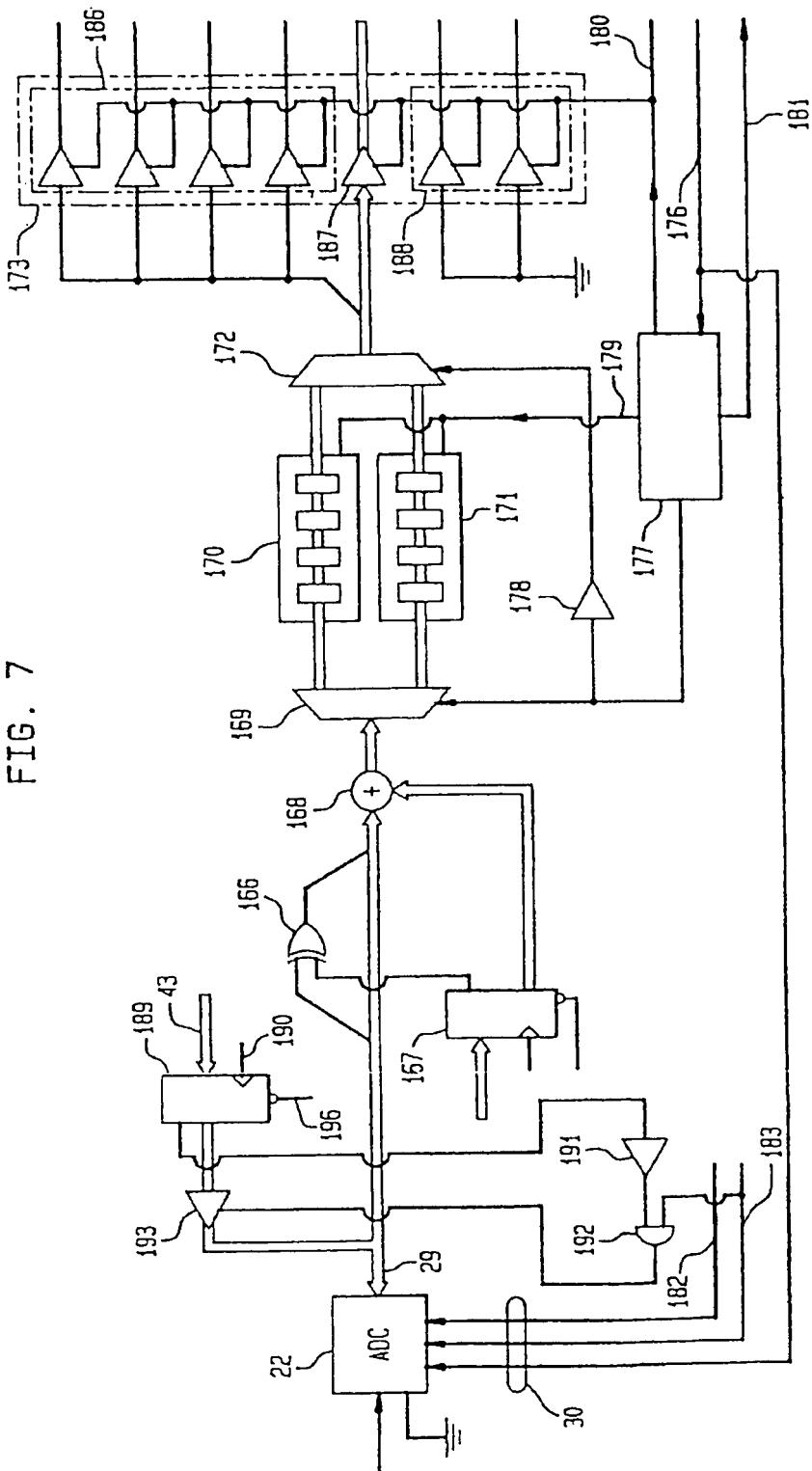

30 la figura 7 es un diagrama de bloques y de líneas de un circuito de interfaz digital en un DDF ASIC de la unidad de abonado en la figura 1;

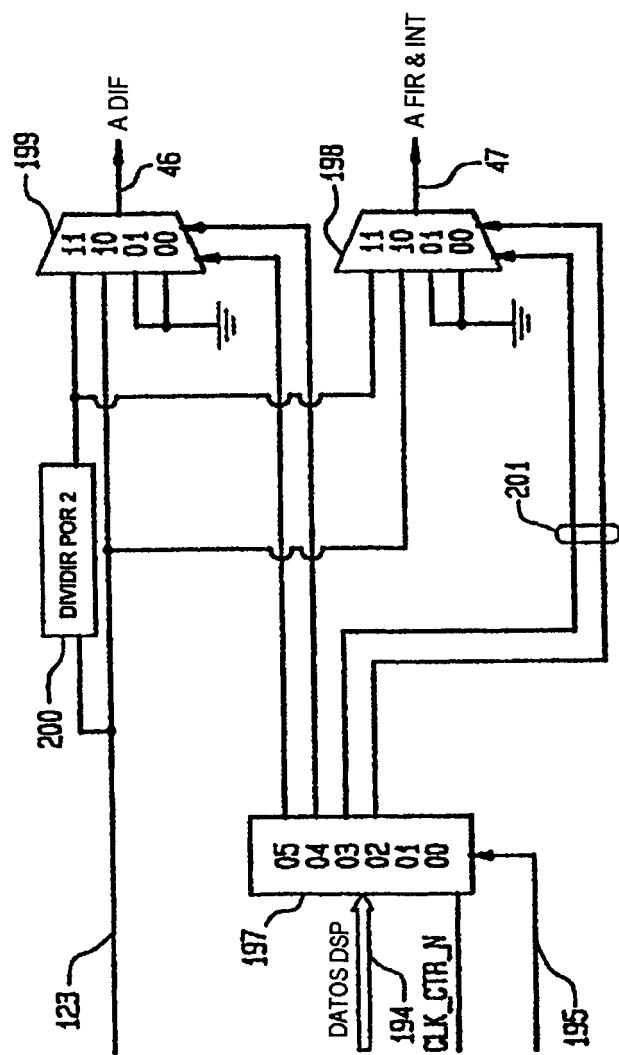

la figura 8 es un diagrama de bloques y de líneas de un circuito de selección del reloj que responde a órdenes en el DDF ASIC de la unidad de abonado de la figura 1;

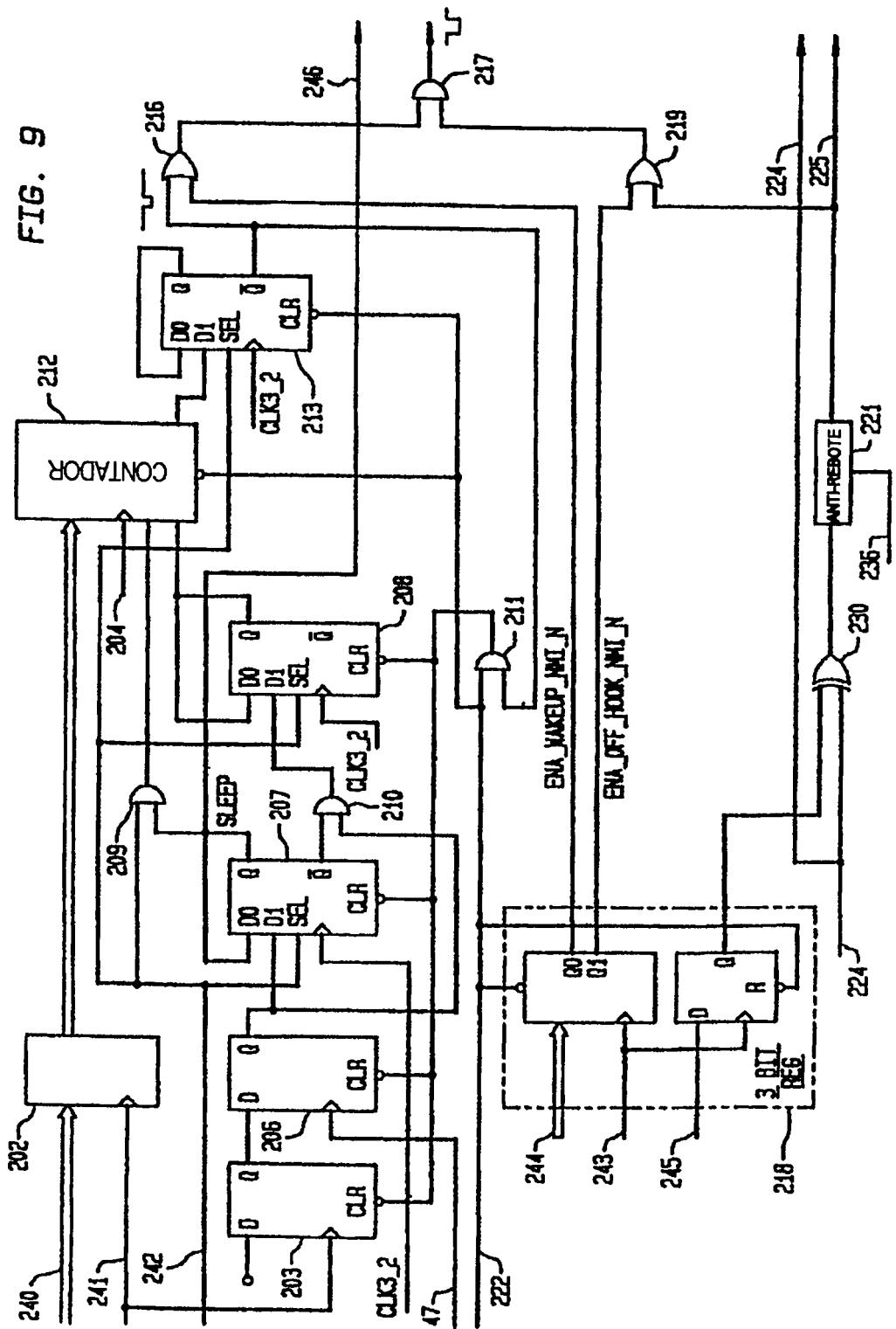

35 la figura 9 es un diagrama de bloques y de líneas de un temporizador de modo inactivo y de la lógica de despertador en el DDF ASIC de la unidad de abonado de la figura 11;

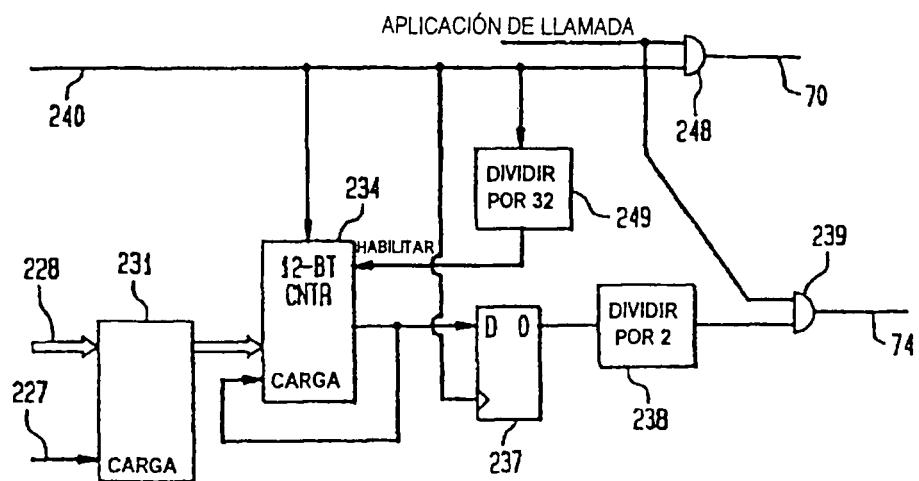

la figura 10 es un diagrama de bloques y de líneas de un circuito para generar dos frecuencias a suministrar a un circuito de llamada en la figura 11; y

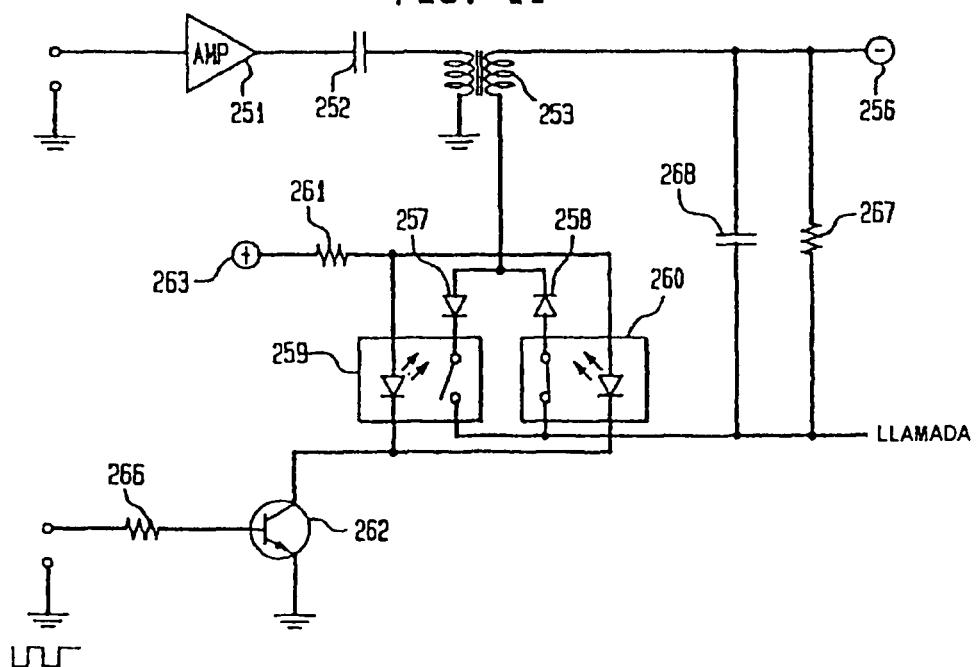

la figura 11 es un diagrama de un circuito de llamada en el circuito de interfaz de línea de la unidad de abonado de la figura 1.

## 45 Definiciones de abreviaturas y siglas

AC: Corriente Alterna

50 ADC: Convertidor Analógico Digital

AGC: Control Automático de Ganancia

ASIC: Circuito Integrado para Aplicaciones Específicas

55 CMOS: Semiconductor de Óxido de Metal Complementario

CODEC: Codificador/Descodificador

60 CODECPD: Señal de Apagado del CODEC

CPU: Unidad Central de Proceso

DAC: Convertidor Digital a Analógico

65 DC: Corriente Continua

DDF: ASIC para realizar funciones DIF, DDS y FIR

# ES 2 198 229 T3

DDS: Síntesis Digital Directa

DIF: IF digital

5 DIFCLK: Reloj Digital de Frecuencia Intermedia

DSP: Procesador de Señal Digital

10 FDAC: Salida DAC para DIF

FIFO: Memoria de Primero en Entrar, Primero en Salir (cola)

FIR: filtrado de Respuesta de Impulso Finito

15 FLASH RAM: RAM no volátil, eléctricamente programable

FLASH\_CS: Señal de selección de chip FLASH

20 IF: Frecuencia Intermedia

IFLPBK: Bucle de retroceso de Frecuencia Intermedia

INT: Interpolador

25 LSB: Bit menos significativo

ms: milisegundo

30 MSB: Bit más significativo

P4RAM\_CS: Señal de selección de chip de RAM de patilla 4

PAEN: Habilitación de Amplificador de Potencia

35 PNP: Transistor de unión que tiene capas de materiales de conductividad p-, n- y tipo-p

PROM: Memoria Programable de Solo Lectura

40 PROM\_CS: Señal de Selección de Chip PROM

PSK: Modulación por Desplazamiento de Fase (Técnica de modulación)

QPSK: Modulación por Desplazamiento de Fase en Cuadratura (técnica de modulación)

45 RAM: Memoria de Acceso Aleatorio

RCC: Canal de Control de Radio

50 RF: Radiofrecuencia

Rx: Recepción

SDAC: DAC para salida del DDS

55 SLIC: Circuito de Interfaz de Línea de Abonado

SLAC: Circuito de Audio del Bucle de Abonado

TDMA: Acceso Múltiple por División de Tiempos

60 T/R: Transmisión o Recepción

Tx: Transmisión

65 VACG: Tensión para el AGC

VOX: Transmisión operada por voz

## Descripción detallada

Por conveniencia en la ilustración, y sin limitaciones, se describe aquí la invención con referencia a la unidad de abonado del sistema de comunicaciones TDMA. Las representaciones en el dibujo de tal unidad están simplificadas

5 para mostrar los aspectos de conservación de energía, siendo conocidos los aspectos subyacentes del tratamiento de señales de radiotelefonía a partir de trabajos de la técnica anterior tales como las patentes de Paneth y otros y de Critchlow y otros referidas anteriormente. Sin embargo, la invención es aplicable a sistemas de radioteléfonos TDMA sin limitarse a un diseño del sistema en particular. La discusión de aspectos de tratamiento de señales de radiotelefonía

10 está incluida aquí solamente en la medida necesaria para facilitar una comprensión de los aspectos de conservación de energía de la invención.

En la figura 1 se muestra un terminal 8 de abonado que incluye una unidad 10 de abonado, del tipo ilustrado en la patente de Critchlow y otros, para un sistema de comunicaciones TDMA tal como el ilustrado en la patente de Paneth y otros. La alimentación de funcionamiento de los componentes del circuito de la unidad 10 es suministrada

15 a partir de una batería (no ilustrada) o de paneles solares (no ilustrados) o de una fuente de alimentación de CA a CC (no ilustrada), por medio de un conjunto de convertidores 9 de CC/CC. Los convertidores del conjunto 9 generan diversas tensiones de salida requeridas por los componentes de circuito de la unidad 10, y en el dibujo se indican ilustrativamente una gama de tensiones que incluyen +5 voltios y -48 voltios. Las diversas tensiones están acopladas a aquellos componentes del circuito de la unidad de abonado de la forma usual por medio de circuitos que no están

20 ilustrados en la figura 1.

Los componentes del circuito de la unidad 10 de abonado incluyen tanto componentes activos como pasivos. Entre los componentes activos del circuito hay un grupo en el cual cada componente tiene al menos una conexión de entrada eléctrica que tiene efecto sobre el consumo de energía, en la cual un cambio predeterminado de la entrada eléctrica

25 origina el correspondiente cambio en el nivel de consumo de energía del componente del circuito. De acuerdo con la invención, esas conexiones de entrada sensibles al consumo de energía están controladas en cada una de las ventanas de tiempo del sistema TDMA para alimentar aquellos componentes del grupo necesarios para el tratamiento de la señal y no alimentar los restantes componentes del grupo.

30 La unidad 10 de abonado de la figura 1 incluye una sección 11 de RF que tiene una parte 12 de transmisión, una parte 13 de recepción y un circuito lógico 16 de sincronización y control. Una antena 17 proporciona el acoplamiento a través de un radioenlace a una estación base (no ilustrada) del sistema TDMA y está acoplada a su vez por medio de un duplexer 18 a las partes de transmisión y recepción de la sección 11 de RF. La unidad 10 de abonado es operada bajo el control de un procesador digital de señales (DSP) 19, es decir, un procesador central programado. Un chip integrado apropiado para el DSP 19 es el TMS320C52 DSP de Texas Instruments Corp. Un circuito integrado específico para la aplicación (ASIC) está acoplado bidireccionalmente con la sección 11 de RF por medio de un convertidor digital a analógico alimentado en DIF (FDAC) 21 (tal como el CXD117M DAC de Sony Corp.) y un convertidor analógico a digital (ADC) 22 (tal como el AD7776 de Analog Devices Corp.) Un bus 23 de bits paralelos y una conexión DIFCLK 26 acoplan los datos de voz de modulación digital y una señal de reloj, respectivamente, desde el DDF ASIC 20 al FDAC 21. La señal del circuito DIFCLK sincroniza el FDAC 21; y durante las ventanas de tiempo TDMA en las que no se requiere el funcionamiento de FDAC, el DIFCLK está apagado para reducir el consumo de energía. Con ese fin, el FDAC 21 está ventajosamente configurado utilizando una tecnología de semiconductores en la cual el consumo de energía está afectado por la velocidad del reloj. Un ejemplo de tal tecnología es la tecnología de semiconductores complementarios de óxido metálico (CMOS). En los circuitos CMOS, la corriente extraída depende de la velocidad a la cual comutan los dispositivos CMOS incluidos; así, si la señal de reloj se interrumpe, la comutación se detiene, y se tiene un resultado de una reducción significativa del consumo de energía. Un efecto similar resulta en los componentes CMOS del circuito que no están sincronizados cuando se impide cambiar a sus señales de entrada, e impidiendo así la comutación de los transistores CMOS. Se aplican señales analógicas de IF desde la salida del FDAC 21 a la parte 12 de transmisión de la sección 11 de RF por medio de un circuito 27.

50 De forma similar, las señales analógicas recibidas de IF son acopladas desde la parte 13 de recepción al ADC 22 por medio de un circuito 28, y la salida digital del ADC es aplicada al DDF ASIC 20 por medio de un circuito bidireccional 29 de bits en paralelo. Ese circuito 29 se emplea también para aplicar señales de control del consumo de energía, y otras señales de control, al ADC 22 desde el DDF ASIC 20, como se describirá posteriormente. Un circuito 30 acopla varias señales de control adicionales al ADC 22 desde el DDF ASIC 20.

Las señales de control del consumo de energía, así como otras señales de sincronismo y control, son aplicadas a la sección 11 de RF y a la lógica 16 de control desde el DDF ASIC 20 por medio de un circuito 31. Ese circuito 31 será descrito con más detalle en conexión con la figura 2, pero para los fines actuales debe observarse que comprende cuatro circuitos para señales utilizadas para implantar el control del consumo de energía en la sección 11 de RF. Esas cuatro señales son Tx (para apagar y encender la parte 12 de transmisión), Rx (para apagar y encender la parte 13 de recepción), PAEN (para habilitar o inhabilitar un amplificador 101 de potencia en la parte 12 de transmisión) e IFLPBK (para controlar un interruptor de bucle de retroceso en la parte 13 de recepción). Una función suplementaria de conversión digital a analógica (no ilustrada en la figura 1), está asociada con una función de control automático de ganancia en la parte 13 de recepción, que será descrita en conexión con la figura 2. La función suplementaria de conversión de digital a analógica se considera incluida en la representación esquemática de la parte 13 de recepción.

El DDF ASIC 20 incluye componentes de circuito que son parte de las secciones de banda base y frecuencia intermedia de la unidad 10 de abonado así como circuitos para realizar las distintas funciones de tratamiento de la señal y de control necesarias para habilitar la cooperación entre la sección 11 de RF, los convertidores 21 y 22, el DSP 19 y los componentes del circuito de banda base no mencionados todavía. De interés específico en conexión con la presente invención son los aspectos de control de consumo de energía que se van a describir. Con ese fin, el DDF ASIC 20 incluye circuitos lógicos 32 de control que supervisan las comunicaciones basadas en registradores entre los componentes del DDF ASIC 20 y otros componentes de la unidad 10 de abonado. Por ejemplo, la información de un circuito fuente, por ejemplo un bus 42 de datos, es cargada en un registrador DDF ASIC en un instante del reloj y después es leída para su circuito de destino en un instante de reloj posterior. Los componentes de los circuitos lógicos

5 32 no están apagados en ningún momento cuando se activa la unidad de abonado. Además, en el DDF ASIC 20, y de interés con fines de control del consumo de energía, hay una sección 33 de FIR del ASIC para filtrar la señal de modulación digital a transmitir, una sección 34 de interpolación (INT) para aumentar la tasa de símbolos de esa señal digital, una sección DIF 36 para realizar la modulación de fase y el primer mezclador para subir la señal digital de banda base a una primera frecuencia intermedia, y un circuito 37 de lógica FIFO de recepción para realizar varias 10 15 funciones como se describirá en conexión con la figura 7.

Diversas funciones de tratamiento de señales de la unidad 10 de abonado requieren distintas frecuencias de la señal, por ejemplo para frecuencias de reloj, frecuencias del oscilador local y frecuencias de referencia, tanto para las operaciones de transmisión como para las de recepción, como es bien sabido en la técnica. El proceso de generar 20 esas frecuencias implica ventajosamente funciones de síntesis digital directa (DDS), también muy conocida en la técnica. En el modo de realización de la figura 1, la sección 36 de DIF realiza ventajosamente la función DDS para los componentes del circuito de la unidad de abonado que están involucrados solamente en operaciones de transmisión. Además, una sección 44 de DDS realiza la función DDS para los componentes del circuito de la unidad de abonado 25 que están involucrados principalmente solo en operaciones de recepción. La salida del DDS 44 está acoplada a través de un DAC alimentado por el DDS (SDAC) 45 a la parte 13 de recepción de la sección 11 de RF. Como al menos un componente del circuito, a describir, de la parte de recepción tiene constantes de tiempo tan largas que debe ser alimentado en todos los momentos de funcionamiento, el DDS es alimentado también durante todos los tiempos de 30 35 40 45 funcionamiento (frente al de inicialización).

Los circuitos lógicos 32 de control responden a señales de direcciones y datos recibida desde el DSP 19 y sus 30 35 40 45 memorias asociadas (es decir, una RAM 39 y una FLASH RAM 40) por medio de un bus 41 de direcciones y un bus 42 de datos para efectuar el control antes mencionado. La información recibida de esa manera por los circuitos 32 les informa del estado operativo del terminal 8 de abonado (por ejemplo, operación de inicio, puesta a cero de parámetros del circuito, desocupado (colgado) mientras espera el inicio de una llamada, llamada, y operación de transmisión/recepción (descolgado) durante una llamada). También se proporcionan datos que indican el modo de funcionamiento (por ejemplo, QPSK o 16PSK). Los circuitos lógicos 32 de control incluyen registradores para la comunicación con los buses 42 y 41 de datos y direcciones y otros componentes del circuito de la unidad 10 de abonado. De aquí viene la caracterización previa de la comunicación entre los circuitos 32 y otros componentes de la unidad de abonado como basada en registradores. Este tipo de comunicación es bien conocida en la técnica. Sin embargo, en la figura 1, esos buses se muestran extendiéndose directamente al bloque que representa los circuitos 32. En la mayoría de los casos, otros circuitos se muestran simplemente extendiéndose hacia o desde el borde del DDF ASIC. Las partes ilustrativas de los circuitos 32 implicadas en el control del consumo de energía basado en ventanas de tiempo serán descritas con más detalle en las figuras 7-10.

Los circuitos lógicos 32 de control utilizan información recibida de los buses 41 y 42 y de otros circuitos, junto 45 50 55 con la información de ventanas de tiempo y tramas generada también en los circuitos 32, para desarrollar las señales adicionales necesarias para el control coordinado de los diversos componentes de la unidad 10 de abonado. Esas señales adicionales incluyen ciertas señales de control del consumo de energía de la unidad 10. Estas últimas señales incluyen las cuatro señales listadas previamente transportadas por el circuito 31 a la sección 11 de RF. Además, un circuito 43 acopla una señal de órdenes de múltiples bits desde los circuitos lógicos 32 la lógica FIFO 37, y la señal incluye un bit de control del nivel de consumo de energía para comunicarlo al ADC 32 al principio y al final de una ventana de tiempo de recepción, como será descrito en conexión con la figura 7. El circuito de lógica FIFO 37 está él mismo continuamente alimentado siempre que la unidad 10 de abonado esté activada.

Los circuitos lógicos 32 de control suministran señales de reloj a los componentes del circuito del DDF ASIC 20. Un circuito 35 acopla señales de reloj continuas al DDS 44. Un circuito 46 acopla señales de reloj seleccionadas, es decir, de interrupción programada, a la sección 36 de DIF, y un circuito 47 acopla otras señales de reloj seleccionadas a la sección 34 de INT y a la sección 33 de FIR, como será descrito en conexión con la figura 8. Apagando y encendiendo las señales de reloj en los circuitos 46 y 47, en las ventanas de tiempo apropiadas, las secciones FIR e INT y la sección 60 DIF, todas ellas realizadas ventajosamente con tecnología CMOS, son eficazmente alimentadas o no para el control del consumo de energía. Cuando los circuitos CMOS no están sincronizados, los transistores CMOS no conmutan y el circuito asume un nivel de consumo de energía cercano a cero.

Los circuitos lógicos 32 incluyen lógica de descodificación de direcciones (no ilustrada) que responde a señales del 65 bus 41 de direcciones para desarrollar señales P4RAM\_CS y FLASH\_CS de selección del chip en los correspondientes conductores designados como 49 y 50, respectivamente, que habilitan los componentes del circuito incluyendo las memorias RAM 39, y la FLASH 40, respectivamente, para su acceso. Los conductores 49 y 50 están normalmente incluidos en el bus 41 de direcciones pero han sido mostrados separadamente con fines ilustrativos del aspecto de

## ES 2 198 229 T3

eliminación de la alimentación de la invención. Como esas memorias están realizadas también con tecnología CMOS, la ausencia de una señal de selección en uno de ellos le impide ser direccionado y de esa manera lo apaga (sin perder la información almacenada) hasta que pueda ser nuevo seleccionado para el direccionamiento.

5 Antes de que el DSP ejecute una instrucción de Desocupado en su programa, con el fin de apagarse él mismo (es decir, pasar a estado durmiente), activa un contador del estado durmiente (figura 9) en los circuitos lógicos 32 de control a través de un registrador con un mapa de memoria en el DDF ASIC 20 y utilizando la dirección DSP y los buses de datos 41 y 42. El DSP 19 habilita entonces el contador para que empiece a contar de la misma manera.

10 Al expiration el intervalo de recuento, o si los circuitos 32 reciben una señal que indica que un abonado servido ha descolgado el teléfono, los circuitos lógico 32 aplican a un circuito 52 una señal de interrupción no enmascarable (NMI) de WAKEUP (despertar) que hace que el DSP 19 active la alimentación y continúe el proceso. Este aspecto se describe con más detalle en conexión con la figura 9.

15 La unidad 10 de abonado incluye una unidad 53 de interfaz de línea, que a su vez incluye componentes de circuito que son encendidos y apagados selectivamente para el control del consumo de energía por señales suministradas desde los circuitos lógicos 32 del DDF ASIC 20. Los componentes principales de la unidad 53 de interfaz de líneas son un circuito 56 de interfaz de línea de abonado (SLIC), un codificador/descodificador (CODEC) 57, (algunas veces denominado un circuito de audio de bucle de abonado (SLAC)), un circuito 58 de llamada, y un relé 59 de llamada. El relé 59 está ilustrado en su posición normal durante una conexión de llamada, y conecta el circuito 58 al bucle de abonado cuando se activa por una señal desde el SLIC 56. El bucle de abonado se representa por las resistencias 62 y 63 de los conductores principal y secundario, respectivamente, y una resistencia 66 que representa el teléfono de abonado. La unidad de abonado es útil para servir a diversos dispositivos de interfaz humana del abonado, es decir, instrumentos de comunicaciones, tales como un teléfono, un módem, o una máquina de facsímil; pero se utiliza aquí el teléfono por conveniencia de la descripción.

25

20 El SLIC 56 proporciona un interfaz eléctrico entre la unidad de abonado y el bucle de abonado, y es ventajosamente un circuito que incluye la capacidad intrínseca de funcionar con distintas tensiones para distintas gamas de resistencia de carga (es decir, de bucles de abonado de teléfono). Por tanto, en una aplicación típica de red cableada, y utilizando el SLIC disponible comercialmente previamente identificado (AMD 79534), la salida de tensión a 30 miliamperios al bucle de abonado era aproximadamente 36 voltios para una resistencia total del bucle de 1200 ohmios, es decir, un consumo de potencia del bucle de 1,08 vatios. Para resistencias más bajas se necesitan tensiones y potencias inferiores.

35 Por otra parte, las aplicaciones para una unidad de abonado incluyen típicamente el montaje de la unidad en un edificio, o muy cerca de él, en el cual esté situado el teléfono del abonado, y el bucle de abonado entre la unidad y el teléfono es típicamente mucho más corto que su enlace por radio entre la unidad de abonado y la estación base que sirve a la unidad de abonado. Dicho de otra manera, el bucle de abonado conectado a la unidad de abonado ilustrada, es típicamente mucho más corto que el bucle de abonado entre una central telefónica y el teléfono del abonado en un sistema cableado. De acuerdo con la presente invención, el bucle de abonado que incluye las resistencias 62, 63 y 40 66 está limitado preferiblemente a una resistencia total muy inferior que la resistencia típica del bucle en un sistema cableado. Por tanto, con el fin de reducir la potencia consumida por el bucle, su resistencia se limita ventajosamente a 500 ohmios, aproximadamente. Eso representa un consumo máximo de potencia en el bucle de alrededor de 0,45 vatios, sin reducir la corriente de funcionamiento disponible para el bucle.

45

40 El SLIC 56 contiene un convertidor de CC-CC que proporciona corriente de bucle constante a resistencias de bucle variables, al tiempo que consume una potencia constante por sí mismo, independientemente de la tensión del bucle, de aproximadamente 450 milivatios (mW). Así, debido a la reducida tensión de salida del SLIC para servir un bucle más corto, y suponiendo que los convertidores 9 tienen una eficacia de alrededor del 85%, la unidad de abonado consume por sí misma en el ejemplo anterior alrededor de 740 mW menos de potencia total. Consecuentemente, hay un ahorro 50 total de energía que es una fracción significativa del requisito de potencia global media de entrada en la unidad de abonado.

55 Las señales de transmisión desde la estación de teléfono del abonado fluyen a través del SLIC 56 y el CODEC 57, y (en forma digital) a través de un circuito bidireccional 64 de interfaz, de señales de comunicaciones, al DSP 19. Tras las funciones de muestreo repetitivo y otras funciones del proceso en el DSP 19, las señales de transmisión continúan hacia la sección 33 de FIR, la sección 34 de INT y la sección 36 de DIF en el DDF ASIC 20, desde el cual fluyen a través del FDAC 21, de la parte 12 de transmisión de la sección 11 de RF, hacia la antena 17. Las señales de recepción interceptadas por la antena 17 fluyen a través de la parte 13 de recepción de la sección 11, del ADC 22, de la lógica 37 de FIFO, del DSP 19 y (a través del circuito 64) del CODEC 57 y del SLIC 56 hacia el teléfono del abonado. El 60 SLIC 56 está provisto de una conexiones 65 de entrada derivadas de la salida del circuito 58 de llamada para habilitar al SLIC 56 para detectar un estado de teléfono descolgado durante la llamada (es decir, durante el estado apagado del SLIC 56). Un conductor 69 que se extiende desde el SLIC 56 acopla la señal detectada de descolgado al DDF ASIC 20 y sus circuitos lógicos 32.

65 El SLIC 56 es ventajosamente un circuito CMOS AM79534 de Advanced Micro Devices, Inc., y es conmutado entre un estado activo y un estado de baja potencia por medio de una palabra de control de múltiples bits proporcionada por el DSP por medio del DDF ASIC 20 (circuitos 32 de control) y una conexión 67. El CODEC 57 es ventajosamente un circuito AMD 7901B de Advanced Micro Devices, Inc., y es conmutado entre un estado activo y un estado inactivo

por medio de una señal SERDAT de múltiples bits sobre un conductor 68 desde los circuitos lógicos 32 del DDF ASIC 20.

Un circuito 70 acopla ilustrativamente una señal de reloj de 80 kilohercios (kHz) y baja tensión desde el DDF ASIC

- 5 20 al circuito 58 de llamada que genera una tensión alta para la llamada. Un circuito 74 acopla una señal RINGFRQ de baja tensión con una baja frecuencia seleccionable (ilustrativamente 20 Hz) al circuito 58 de llamada para generar la frecuencia de la señal de llamada. Las señales de 80 kHz y RINGFRQ son detenidas (es decir, mantenidas a un valor constante de CC) cuando el instrumento del teléfono no produce realmente el sonido de alerta del timbre, por ejemplo durante los “4 segundos de inactividad” de una cadencia de llamada de “2 segundos de activación, 4 segundos de desactivación”. Así, el control del consumo de energía del circuito de llamada y su control operativo son realizados por las mismas señales. Esto es, aún cuando el circuito está en su estado activo de llamada, su alimentación de reloj de la señal de entrada es encendida y apagada periódicamente en la cadencia de llamada mencionada; y eso reduce el consumo de energía. Esto es ventajoso porque, cuando está activo, en un intervalo de llamada de dos segundos el circuito de llamada consume tanta energía como el resto de la unidad 10 de abonado durante alrededor de 3,3 segundos

- 10 15 de funcionamiento en una llamada de voz normal (utilizando modulación 16PSK en funcionamiento semidúplex), u 8,3 segundos de operación en estado desocupado. El relé 59 es activado durante la llamada para conectar las conexiones principal y secundaria del teléfono a la salida del generador 58 de llamada. Esta activación se consigue de forma usual por medio de una salida del SLIC 56, que es controlada por una salida del DDF ASIC 20, que a su vez está controlada por una orden, también en el circuito 67, desde el DSP 19 a través del DDF ASIC 20.

20 También se proporciona una cabecera opcional 72 del interfaz de línea en la unidad 10 de abonado de manera que puedan acomodarse otros servicios dentro de la estructura de tramas de tiempo TDMA, a describir, cuando los niveles de tráfico lo permiten. Ejemplos de tales servicios incluyen, ilustrativamente, la ubicación de una línea de teléfono de abonado normal adicional, o un teléfono de monedas, o un módem de datos, o una máquina de facsímil. Con ese fin, 25 la cabecera 72 está provista de conexiones para el bus 41 de direcciones y el bus 42 de datos, así como un circuito 73 bidireccional para el acoplamiento del interfaz de la señal de comunicaciones con el DSP 19. Se dispone también la conexión de una fuente de alimentación (no ilustrada en la figura 1) para una tensión de alimentación de CC común, tal como 12 voltios, desde el conjunto de convertidores 9 de CC/CC. Los conductores principal y secundario 76 y 77 proporcionan la comunicación con el equipo de servicio del abonado al cual se adapta una tarjeta insertable de servicio opcional (no ilustrada). En la medida en que tal tarjeta opcional requiera una gama particular de tensiones de alimentación distintas a las suministradas desde los convertidores 9, incluirá su propio conjunto de convertidores CC/CC. De forma similar, se proporcionarán señales de control, incluyendo las de control de consumo de energía de los componentes del circuito de la tarjeta opcional, por medio de los buses 42 y 41 de datos y de direcciones a la lógica apropiada de interpretación de órdenes de la tarjeta opcional.

30 35 Cuando se enchufa una tarjeta de circuito de interfaz de línea en el cabezal 72 y se acopla a un bucle de abonado, la unidad de abonado puede funcionar en un modo full-dúplex de QPSK como será descrito en más detalle posteriormente. El término “full-dúplex” según se emplea aquí en el funcionamiento TDMA, tiene una connotación diferente a la connotación tradicional. En el entorno TDMA, el funcionamiento full-dúplex denota el funcionamiento de la unidad de abonado en el cual tanto la parte de transmisión como de la recepción de la unidad están funcionando en una sola ventana de tiempo. Esto permite el funcionamiento full-dúplex más tradicional en el cual ambas partes en una llamada pueden hablar al mismo tiempo, como es el caso también en el funcionamiento semidúplex en TDMA; pero también permite a una sola unidad de abonado servir, por ejemplo, a dos líneas de abonado, es decir, un servicio de línea dual. En el modo de funcionamiento del servicio full-dúplex de línea dual, el consumo de energía de la unidad de abonado completa es mayor que cuando sirve a una sola línea; pero debido a que se comparten partes de la unidad de abonado que están totalmente alimentadas en todos los momentos de funcionamiento, hay un coste de hardware por línea inferior, así como un consumo de energía menor, para la unidad de abonado.

40 45 La capacidad de control del nivel de consumo de energía en el terminal 8 de abonado es útil para ayudar en la regulación de la temperatura interna del terminal. Con ese fin, se acoplaría un termostato 71 a través del DDF ASIC 20 al bus 42 de datos de manera que su estado en circuito abierto o cerrado pueda ser registrado periódicamente en el ASIC y ese estado pueda ser leído por el DSP 19. El termostato está fijado ventajosamente para ser accionado hacia un cambio de estado del circuito cuando la temperatura dentro del terminal 8 de abonado cae por debajo de una temperatura predeterminada, tal como 0° centígrados. Cuando la temperatura cae por debajo de ese nivel, el cambio de estado del circuito del termostato hace que el DSP 19 mantenga las señales de control del nivel de consumo de energía para los circuitos que comutan los circuitos reales de corriente de alimentación de energía, tales como las señales de control suministradas al circuito 31, en sus niveles de consumo de energía de encendido o normales; así, ningún componente del circuito de la unidad de abonado que están controlados de esa manera será apagado hasta que el termostato restaure su anterior estado de circuito. Consecuentemente, el calor generado por los componentes del circuito controlados y totalmente encendidos tenderá a restaurar la temperatura del terminal a un nivel más alto.

50 55 Se hace referencia ahora al diagrama de bloques de la figura 2, que ilustra con más detalle la sección 11 de RF y el nivel de resolución del mosaico de control de consumo de energía. El control de muchos de los componentes de la figura 2 se realiza por la técnica de emplear un interruptor de puerta en el camino en serie de la corriente de los circuitos de la fuente de alimentación para componentes de circuito seleccionados en la sección. Se muestra un ejemplo con más detalle con respecto a un amplificador en la figura 3.

En la figura 3, un amplificador 78 recibe señales de entrada en los terminales 79 y genera señales de salida amplificadas en los terminales 80. Se indica esquemáticamente una fuente de alimentación 81 de tensión positiva mediante un signo mas encerrado en un círculo para representar una fuente de CC que tiene su terminal positivo conectado al circuito ilustrado en el signo mas encerrado en un círculo y su terminal negativo conectado a tierra. La alimentación 81 está conectada al terminal de emisor de un transistor PNP 82 que tiene su terminal de colector conectado a un terminal de fuente de alimentación del amplificador 78, que tiene su otro terminal de alimentación conectado a tierra. El transistor 82 está polarizado para una conducción saturada o bien para no conducción, mediante una señal de control de consumo de energía, es decir, una señal de nivel de CC que es cero o bien positiva, respectivamente, aplicada entre un terminal 83 y tierra a través de la resistencia 84 para polarizar así el terminal de base del transistor. En términos de control del consumo de energía, el transistor 82 está conectado en serie en el camino de alimentación de corriente del amplificador 78 y funciona como un interruptor para encender el amplificador (transistor 82 en conducción saturada) y apagarlo (transistor 82 en no conducción). El uso en la figura 2 de esta técnica para el control del consumo de energía está indicado, por conveniencia de la ilustración, mediante un interruptor abierto en serie en el camino de la fuente de alimentación de un componente de circuito controlado. En la práctica, solamente se utilizan tres interruptores de transistor (no ilustrados, pero incluidos ventajosamente en la representación esquemática de la sección 11 de RF). Cada interruptor está controlado por una de las señales de control del consumo de energía Tx, Rx y LB a describir; y cada interruptor controla una conexión común del bus de fuente de alimentación para dos o más componentes de circuito de la sección 11 de RF que han de tener su fuente de alimentación controlada en base a una ventana de tiempos. Como los interruptores y sus respectivos buses de alimentación controlada son parte así de la representación esquemática de la sección 11 de RF, no serán descritos o referenciados con más detalle.

Volviendo a considerar la figura 2, los componentes del circuito ilustrados aquí y en otros lugares contienen los mismos caracteres de referencia en todas las figuras. Esos componentes serán mencionados para definir el nivel de resolución del mosaico de control del consumo de energía, pero sus interacciones no serán descritas significativamente, ya que son bien conocidas en la técnica, y esas interacciones no comprenden por sí mismas parte alguna de la presente invención. La señal digital IF de salida de la sección 36 de DIF es aplicada, a través del FDAC 21 y el circuito 27, a un primer segmento de IF de la parte 12 de transmisión. En ese segmento, la señal fluye a través de un interruptor 125 de bucle de retroceso, un filtro paso bajo 87 y un atenuador fijo 89 a un primer mezclador 88 para la conversión hacia arriba al segundo nivel de frecuencia intermedia. En ese nivel, las señales fluyen en un segundo segmento de IF a través de un amplificador 90, un filtro paso banda 91 para seleccionar la banda lateral superior y un atenuador fijo 92 a un segundo mezclador 96 que convierte hacia arriba la frecuencia de las señales en la radiofrecuencia apropiada. Las señales de radiofrecuencia en un segmento RF de la parte de transmisión fluyen a través de un amplificador 97, un atenuador programable 93 controlado por un registrador ASIC que puede ser grabado en el DSP a través de las conexiones 94 que son parte del circuito 31 en la figura 1A, un amplificador 99, un filtro paso banda 98, un amplificador 100, y un amplificador 101 de potencia, al duplexor 18.

Las señales de radiofrecuencia recibidas desde el duplexor 18 fluyen en la parte 13 de recepción en un segmento RF que incluye un amplificador 103 de bajo ruido, un filtro paso banda 106, otro amplificador 107 de bajo ruido y un segundo filtro paso banda 108. Un primer mezclador 109 de conversión hacia abajo reduce la frecuencia de la señal a una frecuencia IF y la acopla a un segmento de IF que incluye un interruptor 110 de bucle de retroceso para seleccionar la salida del mezclador 109 o bien una señal de bucle de retroceso en el circuito 124 desde el interruptor 125, un amplificador 112, un filtro de cristal 113 de paso banda para dejar pasar una de las señales seleccionadas por el interruptor 110, y un amplificador 116 de control automático de ganancia. Un segundo mezclador 117 de conversión hacia abajo reduce la señal de IF a una frecuencia de banda base y la acopla a través de una pareja de amplificadores tándem 118 y 119, un filtro paso bajo 120 y un circuito 28, al ADC 22 de la figura 1A.

El circuito 124 está conectado entre los terminales de los interruptores 110 y 125 de bucle de retroceso para proporcionar un camino seleccionable de bucle de retroceso que se emplea para volver a acoplar la señal de IF de transmisión con la sección IF de recepción. Ese camino de bucle de retroceso permite que un programa efectúe una autocalibración del AGC con una señal VAGC al amplificador 116 cuando la unidad de abonado está comenzando a funcionar. El bucle de retroceso se utiliza principalmente para ajustar (es decir, enseñar) a los filtros de ecualización realizados en software del DSP 19, mediante la inserción de modelos conocidos de modulación de IF, para hacer mínima la interferencia entre símbolos originada principalmente por las no linealidades del filtro 113 de cristal, que debe dejar pasar tanto la primera IF de transmisión como a la IF de recepción.

La lógica 16 de control y sincronización de la figura 2 incluye un oscilador 121 que genera, ilustrativamente, una señal de salida de una frecuencia de 43,52 megahercios. Esta salida está acoplada a través de un circuito 123 de salida (no ilustrado en la figura 1A) a los circuitos lógicos 32 de control en el DDF ASIC 20 de la figura 1A, desde el cual se desarrolla el control de tiempos y sincronización. La salida del oscilador 121 es aplicada también a través de un divisor-entre-dos 122 de frecuencias y a un filtro 126 de paso banda como frecuencia de oscilador local, y al primer mezclador 88 en la parte 12 de transmisión. La salida del oscilador 121 es aplicada también al segundo mezclador 117 de conversión hacia abajo por medio de un divisor (128) de frecuencia (división entre cuatro) y a un amplificador 130.

Otra salida más del oscilador 121 es aplicada por medio de un circuito 127 divisor-entre-dos y un circuito 134 divisor-entre-cuatro como una fuente de frecuencia de referencia para un circuito 131 de bucle enclavado en fase (PLL). Las conexiones de conductores tachados ilustrados en los divisores 127, 134 y otros divisores de la figura 2 indican que la razón de las divisiones es fijada ventajosamente mediante puentes de conexión apropiados en conexiones externas de patillas de tales divisores.

El PLL 131 funciona como un multiplicador de frecuencias para recibir una señal de frecuencia relativamente baja (ilustrativamente alrededor de 5 MHz) y generar una señal de frecuencia mayor (ilustrativamente alrededor de 371 MHz) que es utilizada tanto como señal de oscilador local en el mezclador 96 de nivel de radio frecuencia de transmisión, que como fuente de frecuencia de referencia para un PLL 146 de recepción que genera una señal de oscilador local para el mezclador 109 de nivel de radiofrecuencia de recepción. En el circuito 131, la señal del divisor 134 es aplicada a un circuito 132 divisor-entre-8, a un circuito 133 comparador de fase (PC), un filtro 136 en bucle (LF), y un oscilador 137 controlado en tensión (VCO) a la conexión común de un acoplador direccional 138. La salida del VCO 137 es realimentada también a través de un circuito 139 divisor-entre-2 y un circuito 142 divisor-entre-273, a una segunda entrada del circuito PC 133. El PLL 131 y el PLL 146 proporcionan también un indicador de estado LOCK LOSS (pérdida de enclavamiento) en un circuito 140 (no ilustrado en la figura 1A) al DDF ASIC 20. El acoplador direccional 138 conecta la salida del PLL 131 a un amplificador 141, cuya salida es conectada a través de un atenuador fijo 144 a la entrada del oscilador local del segundo mezclador 96 de la sección 12 de transmisión. La salida del PLL 131 es aplicada también a través del acoplador direccional 138 a un mezclador 143 de la parte de recepción donde es mezclada con la salida de un VCO 145 del PLL 146. La salida del mezclador 143 es conectada en el PLL 146 a un comparador 147 de fase que recibe también una señal de frecuencia de referencia desde el SDAC 45 (figura 1A) por medio de un filtro paso bajo 148 y un circuito 149 divisor-entre-dos. La salida del PC 147 es acoplada a través de un filtro 135 en bucle al VCO 145. La salida de ese VCO es acoplada además a través de un amplificador 150 a la entrada del oscilador local del primer mezclador 109 de conversión hacia abajo.

También incluido en la sección de RF hay un circuito 151 de interfaz con la alimentación que comuta los niveles de las cuatro señales del circuito 31 desde los niveles CMOS (alrededor de 5 voltios) hasta los niveles de control de potencia de RF, para generar las señales reales que encienden o apagan los componentes del circuito de la sección 11 de RF. El circuito 151 es una lógica principalmente combinatoria y de cambio de nivel bien conocida que recibe las señales de Tx, Rx, PA ENABLE y LOOP BACK del circuito 31. El circuito 151 genera tres señales de control de energía que son transmisión Tx, recepción Rx y bucle de retroceso LB las cuales, como se ha mencionado en relación con la figura 3, controlan el funcionamiento de los componentes del circuito que han de encenderse o apagarse. El circuito 151 genera también una cuarta señal de control del consumo de energía, PAEN. La señal PAEN controla el funcionamiento del amplificador 101 de potencia que también es encendido o apagado; pero en este caso se emplea también ventajosamente una técnica de control de la corriente de polarización, que se describirá en conexión con la figura 4. Las ventanas de tiempo cuando estas cuatro señales, y otras acciones de control de consumo de energía, están activadas o desactivadas, serán explicadas posteriormente en relación con las Tablas 1 y 2 posteriores y las figuras 5 y 6. Esas cuatro señales son aplicadas, como se ha ilustrado, a las conexiones designadas de manera correspondiente del control de consumo de energía por medio de conductores que no están ilustrados. Así, la señal Tx es aplicada a controlar el consumo de energía de los amplificadores 90, 97, 99, 100 y 141 de la parte de transmisión. La señal PAEN es aplicada al control del consumo de energía del amplificador 101 de potencia y, ventajosamente, alcanza el nivel alto tras alcanzar la señal Tx el nivel alto, y alcanza el nivel bajo antes de que lo alcance la señal Tx para evitar la posibilidad de transmitir frecuencias espurias mientras quedan estables las salidas del mezclador de la parte de transmisión. La señal Rx es aplicada al control del consumo de energía del mezclador 117 y los amplificadores 103, 107, 112, 116, 130 y 150 de la parte de recepción. Finalmente, la señal LB es aplicada a los interruptores 110 y 125 del bucle de retroceso y para controlar el consumo de energía del mezclador 117 y los amplificadores 112, 116 y 130 de la parte de recepción.

Algunos componentes del circuito de la sección 11 de RF están alimentados en todo momento; y, naturalmente, los componentes pasivos del circuito no tienen conexiones con la fuente de alimentación. Los mezcladores 88 y 96 de la parte de transmisión y los mezcladores 109 y 143 de la parte de recepción son pasivos. Los PLL 131 y 146 están siempre encendidos porque tienen constantes de tiempo de funcionamiento relativamente largas en comparación con la duración de una ventana TDMA. Una vez apagados, los PLL requieren casi una ventana de tiempo completa para restablecer un funcionamiento estable totalmente encendido. Los amplificadores 118 y 119 de la parte de recepción, y los divisores 122, 127, 128 y 134 están siempre alimentados en la sección 11 de RF porque consume una cantidad de energía tan pequeña que para controlar su consumo de energía se requerirían más componentes con poca rentabilidad de su valor económico basándose en la conservación de energía. Además, algunas de sus salidas son necesarias para el funcionamiento apropiado de los PLL 131 y 146. Como los PLL 131 y 146 se mantienen encendidos, sus componentes de circuito que generan la señal de entrada, es decir, los divisores 127 y 134, se mantienen encendidos también.

La figura 4 representa un diagrama esquemático simplificado que ilustra una manera de controlar el consumo de energía de un amplificador activando y desactivando su corriente de polarización. Tal control de corriente de polarización es ventajoso, por ejemplo, para amplificadores de potencia porque su corriente de funcionamiento de la fuente de alimentación relativamente alta puede implicar el uso de un transistor de potencia con disipador de calor relativamente costoso para comutar tal corriente. En el diagrama, un amplificador 24 que ha de ser controlado tiene las conexiones normales de la fuente de alimentación representadas por una fuente de tensión 25 puesta a tierra. Las señales de entrada a amplificar son aplicadas al terminal 54. Las señales amplificadas son presentadas en el terminal de salida 55. Una alimentación de corriente constante comutable 85, suministrada desde una fuente adicional 60 de tensión, se emplea como un generador de corriente de polarización. Tales fuentes de corriente constante comutable son bien conocidas en la técnica. La alimentación 85 está conectada a una entrada 71 de corriente de polarización del amplificador 24 para establecer una corriente de polarización que sea suficiente para asegurar la amplificación del mayor nivel de señal previsto en el terminal 54 de entrada. Una conexión 86 de entrada de la alimentación 85 se mantiene con una tensión positiva, ventajosamente ocho voltios en una aplicación, para hacer que la alimentación 85 suministre la suficiente corriente de polarización antes mencionada al amplificador 24, para hacerle que consuma energía en un

primer nivel, o nivel normal, de energía. Cuando la conexión 86 de entrada de la alimentación 85 se mantiene en cero voltios, la salida de corriente de polarización de la alimentación 85 se reduce esencialmente a corriente cero, lo que hace que el amplificador 24 consuma sustancialmente menos energía que en su nivel normal de consumo de energía. La alimentación 85 consume también menos energía en su estado de entrada-cero, salida-cero. Una señal de control de habilitación de la energía es aplicada a la conexión de entrada de la alimentación 85 para hacer que actúe cambiando la corriente de polarización aplicada al amplificador 24. Esta técnica de control de consumo de energía del tipo de corriente de polarización está representada esquemáticamente, por ejemplo, en la figura 2 por una conexión de entrada de polarización que tiene un conductor comutado, tal como el designado por PAEN en el amplificador de potencia 101.

10 La figura 5 es un diagrama de la estructura conocida de ventanas de tiempo para un sistema TDMA, en el cual cada trama TDMA de tiempo recurrente tiene ilustrativamente 45 segundos de duración. Esa trama es la unidad de tiempo básica durante la cual el programa del sistema que se ejecuta en el DSP 19 pasa cíclicamente a través de las operaciones elementales para un estado dado del funcionamiento de la unidad de abonado, como será descrito en más detalle en relación con la figura 6. En un sistema TDMA típico, esta trama de tiempo básica se repite con una frecuencia que es inferior a la frecuencia de Nyquist para una señal de voz típica que se esté procesando, y es mayor que la frecuencia media de los cambios entre funciones de la unidad de abonado, tales como colgado, descolgado y llamada. Cada trama está dividida en cuatro ventanas de tiempo designadas como ventanas 0, 1, 2 y 3; cada ventana de tiempo tiene ilustrativamente una duración de 11,25 milisegundos. Los ahorros de consumo de energía se realizan 15 durante las ventanas de tiempo en las cuales una unidad de abonado está desocupada con todos los componentes del circuito controlables en cuanto a consumo de energía apagados o durante las ventanas de tiempo en las cuales está 20 funcionando solamente con una parte de sus componentes de circuito controlables en cuanto a consumo de energía encendidos y el resto apagados.

25 La manera en la cual la unidad 20 de abonado se desplaza entre sus diversos estados de funcionamiento en relación con la estructura de ventanas de tiempo será descrita en relación con la figura 6, y después se considerarán aquellas operaciones de estado en términos de control de consumo de energía en relación con las Tablas 1 y 2 siguientes. Sin embargo, se consideran en primer lugar dos tipos de funcionamiento de la unidad de abonado. Un primer tipo es la 30 modulación por desplazamiento de fase en cuadratura (QPSK) y un segundo tipo es 16PSK. En el funcionamiento QPSK, una unidad de abonado, funcionando en modo semi-dúplex en un canal de frecuencia dúplex, sirve a una línea de abonado. Como se indica en la figura 5, la unidad de abonado recibe en las ventanas de tiempo 0 y 1 como una 35 ventana de tiempo QPSK y transmite en las ventanas de tiempo 2 y 3, respectivamente, como una ventana de tiempo QPSK. Este doble funcionamiento de ventanas de tiempo es útil para unidades de abonado en lugares de recepción débil, porque conlleva un funcionamiento con relación señal/ruido mayor que el funcionamiento en una sola ventana de tiempo en 16PSK.

40 Otra unidad de abonado podría utilizar el mismo canal para una línea, también en modo semi-dúplex QPSK, recibiendo en las ventanas de tiempo 2 y 3 y transmitiendo en las ventanas de tiempo 0 y 1. Alternativamente, una sola unidad de abonado podría servir a dos líneas funcionando en modo full-dúplex QPSK, cuando ambas líneas están 45 ocupadas en llamadas al mismo tiempo, en el cual se utilizaría la doble ventana de tiempo 0 y 1 para transmitir por la primera línea y recibir por la segunda línea al mismo tiempo. A la inversa, se utilizaría la doble ventana de tiempo 2 y 3 al mismo tiempo para recibir por la primera línea y transmitir por la segunda. Los beneficios de apagar la alimentación basándose en ventanas de tiempo no están disponibles cuando una unidad de abonado funciona en modo full-dúplex en línea dual.

45 En el funcionamiento semi-dúplex de 16PSK, hay más oportunidades para la flexibilidad del funcionamiento y para el ahorro de consumo de energía que en el funcionamiento de QPSK. Se describen algunos ejemplos de posibles configuraciones suponiendo un canal de frecuencia dual. Como se indica en la figura 5, una unidad de abonado, en un servicio de una sola línea, recibe en la ventana de tiempo 0, transmite en la ventana de tiempo 2, y está desocupado 50 en las ventanas de tiempo 1 y 3. Una segunda unidad de abonado podría utilizar el mismo canal para recibir en la ventana de tiempo 1, enviar en la ventana de tiempo 3 y estar desocupado en las ventanas de tiempo 0 y 2. Una unidad de abonado es capaz de servir dos líneas teniendo a una línea de abonado recibiendo en la ventana de tiempo 0 y transmitiendo en la ventana de tiempo 2 y a la otra línea de abonado recibiendo en la ventana de tiempo 1 y transmitiendo en la ventana de tiempo 3. De forma concurrente, otra unidad de abonado puede usar el mismo 55 canal de frecuencia dúplex en modo semidúplex para dos llamadas 16PSK recibiendo en las ventanas de tiempo 2 y 3, respectivamente, y transmitiendo en las ventanas de tiempo 0 y 1, respectivamente. Alternativamente, en el funcionamiento en full dúplex 16PSK con línea dual, una primera línea podría transmitir la voz en la ventana 0 y recibir en la ventana 2, mientras que una segunda línea transmite voz en la ventana 2 y recibe en la ventana 0.

60 Hay también un tercer tipo de funcionamiento cuando la unidad de abonado está en modo de espera de un posible inicio de una llamada y está sintonizada a la frecuencia de un canal dúplex de control de radio (RCC) del sistema TDMA. El RCC está modulado normalmente en modo de modulación binaria por desplazamiento de fase (BPSK), y una línea de abonado funciona también en BPSK cuando está supervisando el RCC. La modulación BPSK es más robusta que la modulación QPSK de doble ventana de tiempo; de esta manera, alcanza fiablemente incluso las regiones 65 remotas que proporcionan el servicio de llamada de abonado con modulación QPSK. Cuando una unidad de abonado QPSK está sintonizada al RCC, y está situada para servir a una sola línea, recibe el RCC en la ventana de tiempo 0 y está desocupada en las otras tres ventanas de tiempo; no obstante, si la unidad es contactada por su estación base (no ilustrada), o si un abonado servido descuelga el teléfono, transmite sus mensajes de reconocimiento necesarios en la

ventana de tiempo 2 para obtener la asignación de un canal de comunicaciones. Cuando un abonado está ocupado en una llamada y la parte distante cuelga el teléfono, la unidad de abonado sigue sintonizada en el canal de voz; así recibe la orden normalmente de colgar por la estación base, fijando apropiadamente uno de los diversos bits de sobrecarga en la señal digital sobre el canal de voz.

5 Cuando una unidad de abonado, funcionando en QPSK o en 16PSK, da servicio a una sola línea, es capaz de realizar el mayor ahorro de consumo de energía basado en ventanas de tiempo. A medida que se añaden líneas adicionales a una unidad de abonado que funcione en 16PSK o en QPSK, el consumo de energía basado en ventanas de tiempo se hace menor porque hay menos oportunidades de ventanas de tiempo para que la unidad de abonado esté desocupada o en un estado de apagado parcial. Además cuando se añaden líneas adicionales a una unidad de abonado, o se añaden unidades de abonado adicionales a un canal, podría ser ventajoso cambiar el modo de funcionamiento del RCC con el fin de asegurar cuando quiera que una línea de abonado ocupada en una llamada cuelgue el teléfono, habrá una ventana de tiempo disponible en la cual la unidad de abonado que da el servicio será capaz de supervisar el RCC. Con ese fin, el RCC puede estar organizado para repetir la transmisión de todos los mensajes de control para las unidades de abonado en cada una de las ventanas de tiempo TDMA de su canal de frecuencia dúplex. Entonces, cualquier unidad de abonado que esté funcionando en el modo de línea dual en full dúplex, puede utilizar, cuando una de las líneas cuelga el teléfono, la ventana de tiempo libre de recepción para estar a la escucha en el RCC y utilizar la correspondiente ventana de tiempo de transmisión para enviar cualquier respuesta apropiada. Como otra alternativa, se podría utilizar la señalización dentro de la banda (“en blanco y a ráfagas”) mediante la sustitución de la información de control del RCC por una ventana de tiempo de voz activa en una trama TDMA, interrumpiendo momentáneamente la conversación de voz.

25 La figura 6 es un diagrama de estado conocido que representa transiciones de la unidad de abonado entre sus diversas funciones, y dentro de las funciones, en relación con la estructura de ventanas de tiempo de la figura 5. La figura 6 contiene tres bucles principales: función de colgar (estados 153, 156 y 157); función de llamada (estados 160, 158 y 159); y función de descolgar (estados 161, 163 y 162). Cuando la unidad 10 de abonado se pone en servicio, se enciende la alimentación y la unidad se inicializa en una función 152 de reposición. Al terminar esa función de reposición, la unidad se desplaza al estado 153 de bucle de retroceso en el cual la señal LB de la figura 2 activa los interruptores 110 y 125 y enciende los amplificadores 112, 116 y 130 para activar la conexión 124 del circuito del bucle de retroceso como se ha indicado en relación con la figura 2. Durante las funciones de reposición y de bucle de retroceso, las ventanas de tiempo no son una preocupación porque no hay utilización del radioenlace. Al terminar la función de aprendizaje del bucle de retroceso, la unidad cambia al estado 156 de recepción con el teléfono colgado (RF Rx Colgado) donde funciona en el modo de recepción durante la ventana de tiempo 0 esperando el inicio de un mensaje de búsqueda desde la estación base, por ejemplo una llamada al abonado servido, o bien una condición de teléfono de abonado descolgado detectada en el SLIC 56 de la figura 1B, por ejemplo una llamada desde el abonado servido. En la ventana de tiempo 1, la unidad 10 cambia a un estado 157 de RF desocupado Colgado, donde funciona en condiciones de bajo consumo de energía, a veces denominado “durmiente” durante las ventanas de tiempo 1, 2 y 3. Al final de la ventana de tiempo 3, la unidad vuelve al estado 156 para recibir cualquier mensaje de búsqueda o a los estados de descolgado que puedan haberse detectado, y continúa pasando cíclicamente a través de los estados 156 y 157 hasta que tiene lugar tal suceso. Pueden realizarse ahorros adicionales de energía manteniendo la unidad de abonado en el modo desocupado, o durmiente, durante siete de las ocho ventanas de tiempo de dos tramas sucesivas en lugar de simplemente tres de las cuatro ventanas de tiempo de cada trama en este bucle de teléfono colgado.

45 Al recibir un mensaje de búsqueda o al detectar una condición de descolgado, la unidad 10 ejecuta cualquier transmisión que sea necesaria para el reconocimiento a la estación base durante la ventana de tiempos 2 (no ilustrada en la figura 6 ni en las Tablas); y suponiendo un mensaje de búsqueda entrante, cambia entonces a un estado 158 de RF desocupado Llamada y comienza a llamar al instrumento telefónico del abonado servido. Por el momento, se supondrá el funcionamiento QPSK; así, en la ventana de tiempo 0 el estado cambia a un estado 159 de RF recepción llamada (RF Rx Llamada) donde permanece la operación hasta el final de la ventana de tiempo 1 para mantener informada a la unidad de abonado de que una parte que llama sigue esperando. En la ventana de tiempo 2, la operación cambia a un estado 160 de RF transmisión llamada (RF Tx Llamada), donde permanece hasta el final de la ventana de tiempo 3 de manera que la ocurrencia de una condición de teléfono del abonado descolgado puede ser transmitida de vuelta a la estación base. En ese momento el funcionamiento cambia al estado 159 de RF Rx Llamada durante las ventanas de tiempo 0 y 1 de la trama siguiente. La operación continúa haciendo ciclos de esta manera hasta que se detecta una condición de teléfono descolgado, y después cambia desde los estados 160 o bien 159 a un estado correspondiente de los estados de descolgado, RF transmisión descolgado (RF Tx Descolgado) 162 o RF recepción Descolgado (RF Rx Descolgado) 161, respectivamente. Si el teléfono del abonado servido no se descolgara nunca en respuesta a la llamada, el funcionamiento expira finalmente y vuelve al estado 157 de RF Desocupado Colgado desde el estado 160 de RF Tx Llamada.

65 Suponiendo que el instrumento telefónico del abonado servido se descuelga, entonces, de una manera similar a las llamadas de QPSK (estados 160 y 159), el funcionamiento pasa cíclicamente entre los estados 162 en las ventanas de tiempo 2 y 3 (unidad de abonado transmitiendo) y 161 en las ventanas de tiempo 0 y 1 (unidad de abonado recibiendo) durante la continuación de la conexión de llamada. Cuando el teléfono del abonado servido se cuelga al final de la comunicación para la cual se estableció la conexión, el funcionamiento vuelve al estado 157 de RF Desocupado Colgado para esperar el inicio de otra llamada.

## ES 2 198 229 T3

El funcionamiento en modo 16PSK es diferente del modo QPSK en cuanto que hay estados 158 y 163 de RF Desocupado en los respectivos bucles de la función de Llamada y Descolgado. La función de Colgado del diagrama de estado no cambia. En el funcionamiento 16PSK del bucle de la función de Llamada, el funcionamiento empieza en el estado 158 de RF Desocupado Llamada. El funcionamiento ilustrado es aplicable a la unidad de abonado que ha sido asignada para utilizar la ventana de tiempo 0 para recibir y la ventana de tiempo 2 para transmitir. Si se entra en el bucle en el estado 158 al final de la ventana de tiempo 3, entonces cambia al estado 159 para la ventana de tiempo 0 y vuelve al estado 158 para la ventana de tiempo 1. Después cambia al estado 160 para la ventana de tiempo 2 y vuelve al estado 158 para la ventana de tiempo 3. El funcionamiento continúa en esos dos bucles secuenciales de función de llamada hasta que expira la operación de llamada, y hay un cambio desde el estado 160 volviendo al estado 157, o hasta que se detecta una condición de descolgar y hay un cambio desde cualquiera de los estados 158, 160 o 159 al estado correspondiente de uno de los estados de función 163, 162 o 161, respectivamente. El funcionamiento continúa en los dos bucles secuenciales de la función de descolgar de una manera similar a la descrita en los bucles de función de Llamada con una duración igual a la de la conexión de la llamada. Cuando se cuelga el teléfono del abonado servido, la operación vuelve al estado 157 de RF Desocupado Colgado para esperar otra llamada.

La descripción anterior de la figura 6 suponía que la llamada iniciada, tras haberse puesto en servicio la unidad 10 de abonado y estar esperando en el bucle de la función de Colgado, se recibía un mensaje de búsqueda. Si la llamada se había iniciado al descolgar el teléfono del abonado servido, el funcionamiento habría sido comutado desde el estado 156 de RF Rx Colgado al estado 163 de RF Desocupado Descolgado y continuaría desde ahí de una forma similar a la ya descrita.

En un modo de realización de la unidad 10 de abonado funcionando con control del consumo de energía basado en ventanas de tiempo, es decir, limitando el consumo de energía de la unidad 10 de abonado como se ha descrito anteriormente, los convertidores 9 de CC/CC de la figura 1A estaban alimentados desde una sola batería de reserva de 12 voltios y 15 amperios que se mantenía cargada por una fuente de alimentación de CA a CC. Alternativamente, los convertidores 9 estaban alimentados por una batería de reserva que se mantenía cargada por hasta dos paneles solares de valor nominal de 12 voltios, 48 vatios de pico.

Se prefiere el funcionamiento de la unidad 10 de abonado en el modo 16PSK semidúplex para conservación de la energía debido a los ahorros de energía realizados con el uso del estado 163 de RF Desocupado Descolgado durante dos ventanas de tiempo de cada trama de función de descolgado, así como a los ahorros realizados por los mosaicos cambiantes de apagado para las ventanas de tiempo de transmisión y recepción. Los ahorros de energía no son tan grandes en el modo de funcionamiento QPSK semidúplex porque hay menos tiempo de desocupación; pero este modo es más robusto en el sentido de la relación señal/ruido; de manera que es útil para unidades de abonado que puedan estar situadas en lugares donde la recepción es relativamente débil en comparación con lugares donde se emplea el funcionamiento 16PSK. El funcionamiento en full dúplex es posible tanto para la operación en QPSK como en 16PSK y ya sea para comunicaciones de datos o de voz. El DSP 19 tiene una amplia capacidad de proceso para manejar el funcionamiento de línea dual porque, por ejemplo, el chip DSP previamente mencionado tiene capacidad para funcionar a veinte millones de instrucciones por segundo (MIPS) aproximadamente, que es alrededor de un treinta por ciento más rápido que lo que se requiere para el funcionamiento con línea dual con respecto a la comunicación por voz. El funcionamiento en full dúplex ofrece los ahorros de energía más pequeños por unidad de abonado debido que a que las señales Tx y Rx deben ser altas, y otras partes correspondientes de la unidad 8 de abonado deben estar encendidas, en todo momento de la duración de una conexión de llamada, es decir, durante los bucles de función de descolgado y de llamada del diagrama de estado de la figura 6. Sin embargo, todavía hay ahorros de energía significativos en base a líneas. Por ejemplo, una unidad de abonado de línea dual realizará ahorros de energía en cualquier momento en que cualquiera de sus líneas servidas no esté ocupada activamente en el tráfico de llamadas. Además, cada unidad de abonado de línea dual puede servir doble número de líneas que podría haber servido como unidad de abonado de una sola línea; y también hay un ahorro de hardware en cuanto que se requieren menos unidades de abonado para un número de líneas dado.

En el funcionamiento del servicio en línea dual, el bucle de descolgado de la figura 6 estaría esencialmente duplicado para una línea servida por la unidad 10 de abonado. La diferencia sería que las posiciones de las ventanas de tiempo del estado RF Tx Descolgado 162 y del estado RF Rx Descolgado 161 del bucle estarían intercambiadas. De forma similar, si ambas líneas estuvieran recibiendo la llamada desde sus respectivos circuitos 58 de llamada al mismo tiempo, sus correspondientes bucles de llamada (que reflejan el funcionamiento del resto de la unidad de abonado en ese momento) serían, para una línea, como se ilustra en la figura 6 y, para la otra línea, serían similares excepto que las posiciones de las ventanas de tiempo en el bucle del estado RF Tx Llamada 160 y en el estado RF Rx Llamada 159 estarían intercambiadas.