(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5554714号

(P5554714)

(45) 発行日 平成26年7月23日(2014.7.23)

(24) 登録日 平成26年6月6日(2014.6.6)

(51) Int.Cl.

F 1

|               |           |               |         |

|---------------|-----------|---------------|---------|

| HO 1 L 21/336 | (2006.01) | HO 1 L 29/78  | 3 7 1   |

| HO 1 L 29/788 | (2006.01) | G 1 1 C 17/00 | 6 2 1 A |

| HO 1 L 29/792 | (2006.01) | G 1 1 C 17/00 | 6 4 1   |

| G 1 1 C 16/04 | (2006.01) | G 1 1 C 17/00 | 6 2 5   |

| G 1 1 C 16/02 | (2006.01) | HO 1 L 27/10  | 4 3 4   |

請求項の数 44 (全 21 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2010-534250 (P2010-534250)  |

| (86) (22) 出願日 | 平成20年11月14日 (2008.11.14)      |

| (65) 公表番号     | 特表2011-503905 (P2011-503905A) |

| (43) 公表日      | 平成23年1月27日 (2011.1.27)        |

| (86) 國際出願番号   | PCT/US2008/083697             |

| (87) 國際公開番号   | W02009/065084                 |

| (87) 國際公開日    | 平成21年5月22日 (2009.5.22)        |

| 審査請求日         | 平成23年11月4日 (2011.11.4)        |

| (31) 優先権主張番号  | 60/987,869                    |

| (32) 優先日      | 平成19年11月14日 (2007.11.14)      |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 12/264,029                    |

| (32) 優先日      | 平成20年11月3日 (2008.11.3)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 309034272<br>インヴェンサンス・コーポレイション<br>アメリカ合衆国 カリフォルニア州 95<br>134、サン・ホセ、オーチャード・パー<br>クウェイ 3025 |

| (74) 代理人  | 100099623<br>弁理士 奥山 尚一                                                                    |

| (74) 代理人  | 100096769<br>弁理士 有原 幸一                                                                    |

| (74) 代理人  | 100107319<br>弁理士 松島 鉄男                                                                    |

| (74) 代理人  | 100114591<br>弁理士 河村 英文                                                                    |

| (74) 代理人  | 100125380<br>弁理士 中村 純子                                                                    |

最終頁に続く

(54) 【発明の名称】可変結合を有する不揮発性プログラマブルメモリに組み込まれた集積回路

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に位置し、少なくとも一つの論理ゲート又は揮発性メモリと関連するトランジスタデバイス用のゲートとして使用される材料から成る浮遊ゲートと、

ソース領域と、

ドレイン領域と、

前記ソース領域と前記ドレイン領域とを結合するnチャネルと

を備え、

前記浮遊ゲートは、前記nチャネルを越えて延在し、前記ドレイン領域のドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレイン領域は、前記ドレイン領域に印加されて前記デバイスをプログラムするプログラム供給電圧を、前記浮遊ゲートと前記ドレイン領域との間にある空間的な容量結合によって前記浮遊ゲートに付与できるように前記重複領域において前記ゲートの大部分に重なり、

さらに前記デバイスは、1ビットを超える情報を前記プログラム供給電圧によって保存できるように構成される、基板上に位置するプログラマブル多状態不揮発性デバイス。

## 【請求項 2】

前記ドレイン領域は、複数のドレイン領域を含んでおり、該複数のドレイン領域のうちの単一のドレイン領域のみが、前記デバイスの状態を決定するために読み取り電圧を受信する、請求項1に記載のプログラマブルデバイス。

10

20

**【請求項 3】**

前記ドレイン領域は、複数のドレイン領域を含んでおり、前記デバイス内に保存された情報量を変化させるためのプログラム操作中に、前記複数のドレイン領域のうちの一部或いは全部にバイアスをかけることができる、請求項 1 に記載のプログラマブルデバイス。

**【請求項 4】**

前記浮遊ゲートは消去可能である、請求項 1 に記載のプログラマブルデバイス。

**【請求項 5】**

前記デバイスは再プログラムできる、請求項 4 に記載のプログラマブルデバイス。

**【請求項 6】**

前記浮遊ゲートは前記ソース領域に印加される消去電圧によって消去可能である、請求項 4 に記載のプログラマブルデバイス。 10

**【請求項 7】**

前記デバイスは、集積回路において別個の各論理回路及び / 又は各メモリ回路に組み込まれたプログラム可能なアレイの一部である、請求項 1 に記載のプログラマブルデバイス。

**【請求項 8】**

前記デバイスは、データ暗号化回路、リファレンス調整 (reference tripping) 回路、製造 ID、又はセキュリティ ID のうちの少なくとも一つと関連する、請求項 7 に記載のプログラマブルデバイス。

**【請求項 9】**

前記空間的な容量結合は、前記基板を覆う前記浮遊ゲートの一部と、前記基板に位置し前記ドレイン領域の一部を含む第 1 トレンチとの間で行われる、請求項 1 に記載のプログラマブルデバイス。 20

**【請求項 10】**

前記基板における一組の第 2 トレンチは組込み型 DRAM として使用される、請求項 9 に記載のプログラマブルデバイス。

**【請求項 11】**

一対のラッチの配列に結合された第 2 プログラマブルデバイスをさらに有し、データやその補数が前記一対のラッチに保存される、請求項 1 に記載のプログラマブルデバイス。

**【請求項 12】**

前記浮遊ゲートの閾値電圧を決定するまでの間に調整される前記ドレイン領域に印加されるバイアス電圧によって、前記ドレイン領域が読み取られる、請求項 1 に記載のプログラマブルデバイス。 30

**【請求項 13】**

前記デバイスは、可変プログラム供給電圧によってマルチレベル状態にプログラムされる、請求項 1 に記載のプログラマブルデバイス。

**【請求項 14】**

電荷蓄積位置としての機能を果たす各不純物を含む材料から成る浮遊ゲートであって、基板上に位置する他の各非プログラマブルデバイス用の絶縁層として利用される、浮遊ゲートと、 40

ソース領域と、

第 1 ドレイン領域及び第 2 ドレイン領域から成るドレイン領域と、

前記ソース領域と前記ドレイン領域とを結合する n チャネルと

を備え、

前記浮遊ゲートは、前記 n チャネルを越えて延在し、前記ドレイン領域のドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレイン領域は、前記ドレイン領域に印加されて前記デバイスをプログラムするプログラム供給電圧を、前記浮遊ゲートと前記ドレイン領域との間にある空間的な容量結合によって前記浮遊ゲートに付与できるように 前記重複領域において前記ゲートの大部分に重なり、 50

さらに、前記デバイスは、複数ビットのデータが前記プログラム供給電圧によって書き込みできるように構成される、基板上に位置するマルチレベルプログラマブルデバイス。

**【請求項 15】**

基板上に位置し、少なくとも一つの論理ゲート又は揮発性メモリと関連するトランジスタデバイス用の相互接続ゲート及び / 又は別のゲートが共用する材料から成る浮遊ゲートと、

ソース領域と、

前記浮遊ゲートの一部分に重なり、少なくとも第 1 ドレイン領域及び第 2 選択可能ドレイン領域を有するドレイン領域と、

前記ソース領域と前記ドレイン領域とを結合する n チャネルと

10

を備え、

前記浮遊ゲートは、前記 n チャネルを越えて延在し、前記ドレイン領域のドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレイン領域と前記浮遊ゲートとの間に空隙的な可変容量結合は、前記重複領域において前記ドレイン領域と前記浮遊ゲートとの間に該可変容量結合を達成するように前記浮遊ゲートに付与される操作電圧として、前記第 1 ドレイン領域及び前記第 2 選択可能ドレイン領域にそれぞれ適用される一つ以上の選択信号によって実現でき、

前記可変容量結合によって、前記第 1 ドレイン領域及び前記第 2 選択可能ドレイン領域からの可変量のチャネル熱電子に前記浮遊ゲートの閾値を恒久的に変更させ、OTP デバイス内にマルチビットデータを保存させる、基板上に位置するマルチレベルワンタイムプログラマブル (MOTP) デバイス。

20

**【請求項 16】**

シリコン基板上にゲート、n 型不純物ソース、及び n 型不純物ドレインを有するマルチレベルプログラマブルメモリデバイスであって、

前記不純物ソースと前記不純物ドレインとを結合する n 型チャネルを備え、

前記ゲートは、前記 n 型チャネルを越えて延在し、前記不純物ドレインのドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記 n 型不純物ドレインは、前記 n 型不純物ドレインに印加されて前記デバイスをプログラムする可変プログラム供給電圧を、前記ゲートと前記 n 型不純物ドレインとの間に空隙的な容量結合によって前記ゲートに付与し、マルチレベル論理状態を前記デバイス内に保存できるように前記重複領域において前記ゲートの大部分に重なり、

30

前記ゲートは、前記デバイスが前記可変プログラム供給電圧によって前記ゲート上に蓄積された電荷量によって画定されるマルチレベルプログラム状態にあるように浮遊ゲートとしての機能に適応し、

さらに、前記浮遊ゲート上の前記電荷は、前記デバイスが再プログラム可能となるよう消去できる、マルチレベルプログラマブルメモリデバイス。

**【請求項 17】**

シリコン基板上にゲート、n 型不純物ソース、及び n 型不純物ドレインを有するマルチレベルワンタイムプログラマブル (MOTP) メモリセルであって、

前記不純物ソースと前記不純物ドレインとを結合する n 型チャネルを備え、

40

前記ゲートは、前記 n 型チャネルを越えて延在し、前記不純物ドレインのドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記 n 型不純物ドレインは、前記 n 型不純物ドレインに印加されて前記セルをプログラムする電圧を空隙的な容量結合によって前記ゲートに付与できるように前記重複領域において前記ゲートの可変部分に重なるように構成され、

前記ゲートは、前記 MOTP セルが前記ゲートの荷電状態によって画定されるプログラム状態にあるように構成され、前記荷電状態は複数のビットのデータに対応する、マルチレベルワンタイムプログラマブルメモリセル。

**【請求項 18】**

基板上に位置し、少なくとも一つの論理ゲート又は揮発性メモリと関連するトランジス

50

タデバイス用のゲートとして使用される材料から成る浮遊ゲートと、

ソース領域と、

第1ドレイン領域及び少なくとも一つの別の第2ドレイン領域と

前記ソース領域と前記ドレイン領域とを結合するチャネルと

を備え、

前記浮遊ゲートは、前記チャネルを越えて延在し、前記ドレイン領域のドレイン接合面

から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレイン領域は、前記ドレイン領域に印加されて前記デバイスをプログラムするプログラム供給電圧を、前記浮遊ゲートと前記ドレイン領域との間にある空間的な容量結合によって前記浮遊ゲートに付与できるように前記重複領域において前記ゲートの大部分に重なり、

10

さらに、前記デバイスは、前記第1ドレイン領域及び前記第2ドレイン領域のうち複数の異なる領域がプログラム及び読み取り作業中にそれぞれ前記ゲートに結合できるように構成される、基板上に位置するプログラマブル不揮発性デバイス。

【請求項19】

前記デバイスはnチャネルである、請求項18に記載のプログラマブルデバイス。

【請求項20】

前記デバイスはpチャネルである、請求項18に記載のプログラマブルデバイス。

【請求項21】

前記デバイスは、プログラム操作中に前記第1ドレイン領域及び前記第2ドレイン領域のうちいずれか一方、或いは両方にバイアスをかけ、或いはいずれにもかけないように構成され、また、前記第1ドレイン領域及び前記第2ドレイン領域のうち一つだけが読み取り操作中にバイアスをかけられるように構成される、請求項18に記載のプログラマブルデバイス。

20

【請求項22】

前記デバイスは、プログラム操作中に前記第1ドレイン領域及び前記第2ドレイン領域のいずれにもバイアスがかからないように、あるいは両方にバイアスがかかるように構成され、また、消去操作中に前記第1ドレイン領域及び前記第2ドレイン領域のうち一方に或いは両方にバイアスがかかるように構成される、請求項18に記載のプログラマブルデバイス。

30

【請求項23】

前記デバイスは、プログラム操作中に前記第1ドレイン領域及び前記第2ドレイン領域のうちいずれか一方、あるいは両方にバイアスかけ、或いはいずれにもかけないように構成され、また、読み取り操作中に前記第1ドレイン領域及び前記第2ドレイン領域はのうちいずれか一方或いは両方にバイアスをかけられるように構成される、請求項18に記載のプログラマブルデバイス。

【請求項24】

前記デバイスは、前記第1ドレイン領域及び前記第2ドレイン領域の前記ゲートに対する結合を変更することによって、プログラム操作、読み取り操作及び/又は消去操作のうち少なくとも一つを操作中に変更できるように構成される、請求項18に記載のプログラマブルデバイス。

40

【請求項25】

前記浮遊ゲートは消去可能である、請求項18に記載のプログラマブルデバイス。

【請求項26】

前記デバイスは再プログラムできる、請求項25に記載のプログラマブルデバイス。

【請求項27】

前記浮遊ゲートは、前記ソース領域に印加される消去電圧によって消去可能である、請求項25に記載のプログラマブルデバイス。

【請求項28】

10

20

30

40

50

前記デバイスは、集積回路において別個の各論理回路及び／又は各メモリ回路に組み込まれたプログラム可能なアレイの一部である、請求項18に記載のプログラマブルデバイス。

【請求項29】

前記デバイスは、データ暗号化回路、リファレンス調整(reference tri

mming)回路、製造ID、及び／又はセキュリティIDのうちの一つと関連する、請求項28に記載のプログラマブルデバイス。

【請求項30】

前記容量結合は前記基板に位置する第1トレンチで行われる、請求項18に記載のプログラマブルデバイス。

10

【請求項31】

前記基板における一組の第2トレンチは組込み型DRAMとして使用される、請求項30に記載のプログラマブルデバイス。

【請求項32】

一対のラッチの配列に結合された第2プログラマブルデバイスをさらに有し、データやその補数が前記一対のラッチに保存される、請求項18に記載のプログラマブルデバイス。

【請求項33】

前記第1ドレイン領域及び／又は前記浮遊ゲートの閾値電圧の閾値電圧を決定するまでの間に調整される前記少なくとも一つの別の第2ドレイン領域のうちの一つに印加されるバイアス電圧によって、前記ドレイン領域が読み取られる、請求項18に記載のプログラマブルデバイス。

20

【請求項34】

前記浮遊ゲートはマルチレベル構造である、請求項18に記載のプログラマブルデバイス。

【請求項35】

前記デバイスは薄膜トランジスタの一部である、請求項18に記載のプログラマブルデバイス。

【請求項36】

前記浮遊ゲートは非平面構造内に配置される、請求項18に記載のプログラマブルデバイス。

30

【請求項37】

前記浮遊ゲートは、前記デバイス以外の少なくとも1つの構造から形成され、電荷蓄積位置として各不純物を含むものである、請求項18に記載のプログラマブルデバイス。

【請求項38】

電荷蓄積位置としての機能を果たす各不純物を含む材料から成る浮遊ゲートであって、基板上に位置する他の各非プログラマブルデバイス用の絶縁層として利用される、浮遊ゲートと、

ソース領域と、

ドレイン領域と

40

前記ソース領域と前記ドレイン領域とを結合するnチャネルと

を備え、

前記浮遊ゲートは、前記nチャネルを越えて延在し、前記ドレイン領域のドレイン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレイン領域は、前記ドレイン領域に印加されて前記デバイスをプログラムするプログラム供給電圧を、前記浮遊ゲートと前記ドレイン領域との間にある空間的な容量結合によって前記浮遊ゲートに付与できるように前記重複領域において前記ゲートの大部分に重なり、

さらに、前記デバイスは、プログラム用の可変閾値をもたらすためのプログラム操作中に、可変プログラム供給電圧を前記ゲートに結合できるように構成される、

50

基板上に位置するプログラマブルデバイス。

【請求項 3 9】

ワンタイムプログラマブル(OTP)デバイスであって、

基板上に位置し、少なくとも一つの論理ゲート又は揮発性メモリと関連するトランジスタデバイス用の相互接続ゲート及び/又は別のゲートが共用する材料から成る浮遊ゲートと、

ソース領域と、

前記浮遊ゲートの一部分に重なり、少なくとも第1ドレン領域と第2選択可能ドレン領域とを有するドレン領域と

前記ソース領域と前記ドレン領域とを結合するnチャネルと

を備え、

前記浮遊ゲートは、前記nチャネルを越えて延在し、前記ドレン領域のドレン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

前記ドレン領域と前記浮遊ゲートとの間にある空間的な可変容量結合は、前記重複領域において前記ドレン領域と前記浮遊ゲートとの間に該可変容量結合を達成するように前記浮遊ゲートに付与されるプログラム電圧として、前記第1ドレン領域と前記第2選択可能ドレン領域とにそれぞれ適用される一つ以上の選択信号によって実現可能であり、

前記可変容量結合によって、前記第1ドレン領域と前記第2選択可能ドレン領域から可変量のチャネル熱電子が、前記浮遊ゲートの閾値を恒久的に変更し、前記OTPデバイスにデータを保存する、基板上に位置するワンタイムプログラマブル(OTP)デバイス。

【請求項 4 0】

少なくとも一つの他の追加論理デバイス又は非OTPメモリデバイスと共にシリコン基板上に組み込まれるワンタイムプログラマブル(OTP)メモリデバイスであって、

a . 浮遊ゲートに空間的に容量的に結合されるドレン領域と、ソース領域と前記ドレン領域とを結合するnチャネルとを有し、前記浮遊ゲートは、前記nチャネルを越えて延在し、前記ドレン領域のドレン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

b . 前記OTPメモリデバイスの任意及びすべての領域と各構造とは、前記少なくとも一つの他の追加論理デバイス又は非OTPメモリデバイスの各構成要素として使用される各対応領域及び構造から単に由来し、

c . 前記浮遊ゲートと前記ドレン領域との間にある空間的な容量結合の量は、前記重複領域において前記ドレン領域と前記浮遊ゲートとの間に該可変容量結合を達成するように、前記ドレン領域に付与されて前記浮遊ゲートに付与される操作電圧によって、少なくとも一つの異なるプログラム、消去、又は読み取りの操作中に変化させることができることを特徴とするメモリデバイス。

【請求項 4 1】

少なくとも一つの他の追加論理デバイス及び/又は非OTPメモリデバイスと共にシリコン基板上に組み込まれるマルチレベルワンタイムプログラマブル(MOTP)メモリセルであって、

a . 浮遊ゲートに空間的に容量的に結合されるドレン領域と、ソース領域と前記ドレン領域とを結合するnチャネルとを有し、前記浮遊ゲートは、前記nチャネルを越えて延在し、前記ドレン領域のドレン接合面から延長しているアクティブ領域に重なる重複領域を有しており、

b . 前記MOTPメモリセルの任意及びすべての領域と各構造は、前記少なくとも一つの他の追加論理デバイス又は非MOTPメモリデバイスの各構成要素として使用される各対応領域及び構造から単に由来し、

c . 前記浮遊ゲートと前記ドレン領域との間にある空間的な容量結合の量は、前記重複領域において前記ドレン領域と前記浮遊ゲートとの間に該可変容量結合を達成するよ

10

20

30

40

50

うに前記浮遊ゲートに付与される、単一MOTPメモリセル内に複数ビットのデータを保存するためのプログラム操作中に印加された電圧によって変更できることを特徴とするメモリセル。

#### 【請求項 4 2】

印加された前記プログラム供給電圧は、前記ソース領域と前記ドレイン領域との間にあ

るトランジスタチャネル領域を流れる電流を生じさせるものである、請求項 1 に記載のプロ

グラマブルデバイス。

#### 【請求項 4 3】

前記空間的な容量結合は、前記浮遊ゲートの下にあるn型ウェル又はn型拡散層の領域

を覆うことにより達成される、請求項 1 に記載のプログラマブルデバイス。 10

#### 【請求項 4 4】

前記デバイスの外部にある別のデバイスを介して前記ドレイン領域に印加される前記プロ

グラム供給電圧を付与することなく、前記デバイスがプログラムされる、請求項 1 に記

載のプログラマブルデバイス。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、複数回プログラム可能である、可変結合を有する不揮発性メモリに関する。

本発明は、特に各電子回路をカスタマイズすることが望ましい各アプリケーションに適用

可能である。 20

#### 【背景技術】

#### 【0002】

ワンタイムプログラマブル(OTP)及びマルチタイムプログラマブル(MTP)メモリは、近年、カスタマイズがデジタル及びアナログ設定の両方において必要とされる多数のアプリケーションでの有效利用を目的として導入されてきている。これらのアプリケーションには、データ暗号化、リファレンス調整(reference trimming)、製造ID、セキュリティID、及び多くの他のアプリケーションが含まれる。それにもかかわらず、OTP及びMTPメモリを組み込むことは、通常、幾つかの追加的な処理ステップを行うことで成り立っている。 30

#### 【0003】

OTPの新しい形式が特許文献1に開示されており、その内容を参考により本願明細書に援用する。当該開示において、OTP(ワンタイムプログラマブル)又はMTP(マルチタイムプログラマブル)メモリセルのいずれかとして動作可能な新しいタイプの单層ポリ不揮発性メモリデバイス構造が開示されている。該デバイス構造は、高度CMOS論理プロセスと完全に互換性があり、最悪の場合、実行するための最小限の追加ステップを必要とする。本デバイス特有の態様は、メモリセル構造の浮遊ゲートがトランジスタの各S/D接合部の一つを通じて電気的に強硬に結合されることであり、一方で、従来の单層ポリ不揮発性メモリセルは、浮遊ゲートに結合するための追加的な相互接続層を必要とするか、又は浮遊ゲートが事実上既存の各電気信号のいずれにも電気的結合をしない或いは最小限電気的結合を行うことを必要とする。 40

#### 【0004】

別の重要な特徴はNMOSデバイス構造で実行されることであるが、従来型の单層ポリOTPは、通常PMOSデバイス構造で実行される。これは、デバイスをウエハ上の他の各nチャネルデバイスと同時に形成できることを意味している。

#### 【0005】

NMOSデバイス構造の別の利点は、該デバイスがEPROMデバイスと同じように機能するということであり、すなわち、デバイスは伝導状態から非伝導状態にプログラムされる。(最も一般的に使用されるPMOS・OTPデバイスは、非伝導状態から伝導状態にプログラムされる。)これにより、PMOSデバイスが製造工場から出て非伝導状態になるのを確認するために、一般にPMOS・OTPデバイスと関連する追加のマスキング 50

ステップの必要性を取り除くことができる。さらに、チャネル熱電子注入 (channel hot electrons injection) を伴うN M O S デバイスのプログラミング機構が自己制御式であるため、チャネル熱電子プログラミングを伴うP M O S の場合とは異なり、本発明におけるプログラミング中のエネルギー消費量は自己制御される。

#### 【 0 0 0 6 】

前述のデバイスのさらなる利点は、多層の機能性は、以下に説明されるように可変電気的結合のさまざまな形式を単に採用することによってとても容易に組み込むことができるという事実である。（単に1ビットではなく）nビット保存できるO T P 及びM T P セルを有する性能は、上述のデバイスに特有のものであると思われる。

#### 【 0 0 0 7 】

特許文献2は、別のN M O S型O T P の導入を開示しており、その内容を参照により本願明細書に援用する。この引用文献におけるデバイスは、チャネル熱正孔注入 (channel hot-hole-injection) によってプログラムされる。当該開示は、チャネル熱正孔注入後にデバイスが伝導状態にプログラムされることを教示している。しかしながら、各発明者が主張する方法によってデバイスが実際に動作するのかどうかは不明確である。すなわち、浮遊ゲートの状態が不明であり、電圧を浮遊ゲートに結合するための有効な手段がないため、チャネル電流が熱正孔注入を誘導し始めるであろうことが明らかでない。N M O S デバイスは、浮遊ゲートの電位がデバイスを作動させるのに十分なときだけ、又はチャネル電流の伝導ができるように閾値電圧が常に初めは低いときだけ、熱正孔注入を開始するようチャネル電流を流す。いずれの状況も確立する唯一の方法は、N M O S の各作動特性を修正するために追加の処理ステップを導入することである。次に、チャネルが初めに導通して各熱正孔が注入されると仮定すると、浮遊ゲート上に注入された各正孔は、該デバイスをより伝導性のあるものにする。そのように、デバイスは、基本的に導電状態から（熱正孔注入用のチャネル電流を流すために）高い導電状態に向かう。これはメモリデバイスにとって最適な動作ではない。

#### 【 0 0 0 8 】

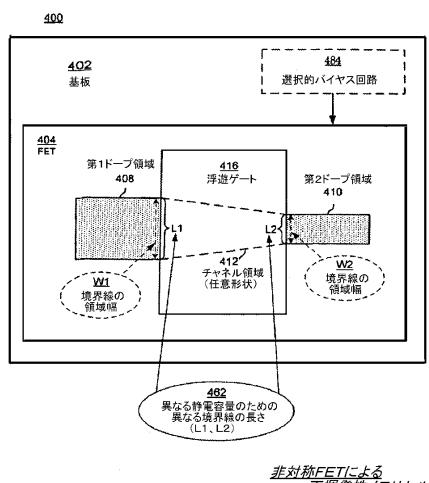

特許文献3（参照により本願明細書に援用する）に記載された別の先行技術のデバイスは、プログラム供給電圧をO T P デバイスの浮遊ゲートの実施形態に供給する課題に対して若干異なった取り組みを説明している。この設計においては、図4に示すように、ドレイン境界線の長さL1をソース側の長さL1に対して増加させることによって、消去可能な浮遊ゲート416に対する結合比を増加させる。該結合比を増加させることによりチャネル電流量が増加すると、その結果、浮遊ゲートへの電荷注入もさらに増加する。しかしながら、このセルの欠点は、セル及びチャネル412は非対称でなければならず、結合は稼働中の各領域の長さの範囲を使用して制御されるだけであるという事実である。これらの制限のために、多層構造にまで拡張可能であるように見えない。さらに、Pチャネルデバイスとして実行されるだけであることは明らかである。

#### 【 0 0 0 9 】

従って、従来技術におけるこれらの欠陥に対処できる浮遊ゲートタイプのプログラマブルメモリが長年に渡って必要とされてきたことは明らかである。

#### 【 0 0 1 0 】

<関連する出願への相互参照>

本出願は、米国特許法第119条(e)項に基づき、2007年11月14日に出願された米国仮特許出願第60/987,869号の利益を主張し、その内容を参照により本願明細書に援用する。本出願は、全て2008年11月3日に出願された米国特許出願番号第12/264029号、第12/264060号及び第12/264076号の利益を主張し、また、当該各出願の一部継続出願であり、それらの内容を参照により本願明細書に援用する。

#### 【 0 0 1 1 】

本出願は、さらに次の各出願、「INTEGRATED CIRCUIT EMBEDDED WITH NON-VOLATILE PROGRAMMABLE MEMORY HAVING VARIABLE COUPLING」（代理人事件番号JONK 2008-4）出

10

20

30

30

40

50

願番号\_\_\_\_\_、「METHOD OF MAKING INTEGRATED CIRCUIT EMBEDDED WITH NON-VOLATILE PROGRAMMABLE MEMORY HAVING VARIABLE COUPLING」(代理人事件番号JONK 2008-5)出願番号\_\_\_\_\_、「METHOD OF OPERATING INTEGRATED CIRCUIT EMBEDDED WITH NON-VOLATILE PROGRAMMABLE MEMORY HAVING VARIABLE COUPLING」(代理人事件番号JONK 2008-6)出願番号\_\_\_\_\_、及びINTEGRATED CIRCUIT EMBEDDED WITH NON-VOLATILE MULTIPLE-TIME PROGRAMMABLE MEMORY HAVING VARIABLE COUPLING(代理人事件番号JONK 2008-7)出願番号\_\_\_\_\_に関連し、当該各出願は全て同日に出願され、参照により本願明細書に援用される。

**【先行技術文献】**

【特許文献】

10

【0012】

【特許文献1】米国特許出願番号第12/264029号明細書

【特許文献2】米国特許第6,920,067号明細書

【特許文献3】米国特許公開公報第2008/0186772号明細書

**【発明の概要】**

**【発明が解決しようとする課題】**

【0013】

それゆえ、本発明の目的は、先行技術における上述の各制限を克服することである。

**【課題を解決するための手段】**

【0014】

20

従って、本発明の第1の態様は、基板上に位置するプログラマブル多状態不揮発性デバイスに関し、該デバイスは、基板上に位置し、論理ゲート及び／又は揮発性メモリと関連するトランジスタデバイス用のゲートとしても使用される材料から成る浮遊ゲートと、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域とを結合するnチャネルとを備え、前記ドレイン領域は、前記ドレインに印加されるデバイス用プログラム供給電圧を容量結合によって前記浮遊ゲートに付与できるように前記ゲートの大部分に重なり、さらに前記デバイスは1ビットを超える情報が前記プログラム供給電圧によって保存できるように構成される。

【0015】

30

この多状態の実施形態においては、前記デバイスは、読み取り操作中に前記ドレイン領域の一部のみが読み取り電圧を受信するように構成されることが望ましい。すなわち、前記デバイス内に保存された情報量を変化させるためのプログラム操作中に、前記ドレイン領域の一部或いは全部にバイアスをかけることができる。場合によっては、前記デバイスは、前記浮遊ゲートの閾値電圧を決定する時間に従って調整される前記ドレイン領域に印加されたバイアス電圧によって読み取ることができる。

【0016】

他の好適な実施形態においては、前記浮遊ゲートは、前記デバイスが再プログラムできるように消去可能である。好適には、前記浮遊ゲートは前記ソース領域に印加される消去電圧によって消去可能であることが好ましい。

【0017】

40

幾つかのアプリケーションにおいて、前記デバイスは、集積回路内で別個の各論理回路及び／又は各メモリ回路に組み込まれたプログラム可能なアレイの一部として一体化できる。そのような回路は、データ暗号化回路、リファレンス調整(reference trimming)回路、製造ID、及び／又はセキュリティID、又はカスタマイズされた不揮発性データを必要とする他の回路のうちの一つであってもよい。

【0018】

幾つかの実施形態では、前記容量結合は前記基板に位置する第1トレンチで行われる。これらのトレンチは、組込み型DRAMアレイの一部であってもよい。結合量は、ゲートの選択的統制(相互接続マスク、ソース／ドレイン拡散マスク又はその両方)に基づいて要望に応じて調整できる。

50

**【 0 0 1 9 】**

他の構造には、一対のラッチの配列に結合された第2プログラマブルデバイスが含まれ、データやその補数が前記一対のラッチに保存される。

**【 0 0 2 0 】**

前記デバイスをマルチレベル状態にプログラムするために、可変プログラム供給電圧を使用することが望ましい。これにより、複数ビットのデータがプログラム供給電圧によって書き込まれる。

**【 0 0 2 1 】**

本発明の別の態様は、基板上に位置するマルチレベルワンタイムプログラマブル（MOTP）デバイスに関し、該デバイスは、基板上に位置して論理ゲート及び／又は揮発性メモリと関連するトランジスタデバイス用の相互接続ゲート及び／又は別のゲートが同様に共用する材料から成る浮遊ゲートと、ソース領域と、前記浮遊ゲートの一部分に重なり、少なくとも第1ドレイン領域及び第2選択可能ドレイン領域を有するドレイン領域とを備え、前記ドレイン領域と前記浮遊ゲートとの間の可変容量結合は、前記第1ドレイン領域及び前記第2ドレイン領域にそれぞれ適用される一つ以上の選択信号によって実現でき、前記可変容量結合によって、前記第1ドレイン領域及び前記第2ドレイン領域からの可変量のチャネル熱電子に前記浮遊ゲートの閾値を恒久的に変更させ、OTPデバイス内にマルチビットデータを保存させる。

10

**【 0 0 2 2 】**

本発明のさらなる態様は、幾つかの実施形態において、前記デバイスは、可変プログラム供給電圧によって浮遊ゲート上に蓄積された電荷量が画定するマルチレベル（マルチビット）プログラム状態であるという事実に関する。

20

**【 0 0 2 3 】**

本発明の他の態様は、上述のマルチレベル不揮発性プログラマブルメモリデバイスを形成する方法に関する。

**【 0 0 2 4 】**

本発明のさらなる他の態様は、上述のマルチレベル不揮発性プログラマブルメモリデバイスを操作する方法に関する。好適な実施形態では、容量結合の量は、前記浮遊ゲートに重なるように選択された複数のN（N > 1）個の独立したドレイン領域を変化させることに基づいて及び／又はプログラム供給電圧レベルを変化させることによって調整できる。

30

**【 0 0 2 5 】**

N = 2 である場合、前記浮遊ゲートの前記閾値は要求に応じて三つ又は四つの異なる値のうちの一つに設定できる。N = 3 である場合、前記浮遊ゲートの前記閾値は、八つの異なる値などのうちの一つに設定できる。前記デバイスの状態を読取るために、読み取り電圧は、前記浮遊ゲートの各閾値状態に対応する時間内に変化する範囲の値になるよう制御されることが望ましい。

**【 0 0 2 6 】**

多状態デバイスは、浮遊ゲートの電圧閾値を変更するチャネル熱電子によってプログラムされ、バンド間トンネリング熱正孔注入によって消去されることが望ましい。幾つかの実施形態では、前記デバイスは、前記第1ドレイン領域及び前記第2ドレイン領域のうち複数の異なる領域がプログラム及び読み取り操作中にそれぞれ前記ゲートに結合できるように構成される。例えば、プログラム操作中に、前記第1ドレイン領域及び前記第2領域のうちいずれか一方、或いは両方にバイアスをかけ、或いはいずれにもバイアスをかけず、また、前記第1領域及び前記第2領域のうち一つだけに読み取り操作中にバイアスをかけることができる。同様に、消去操作中に前記第1領域及び前記第2領域のうち一方に或いは両方にバイアスをかけることができる。

40

**【 0 0 2 7 】**

多状態デバイスの好適な実施形態はnチャネルであるが、pチャネルでも可能である。幾つかのアプリケーションでは、前記浮遊ゲートは、マルチレベル構造として、或いは薄膜トランジスタの一部として実現可能であり、又は非平面構造内に配置することもできる

50

。

### 【0028】

本発明の別の態様は、上記の多状態デバイスと同様の構造的、形成及び操作特性を共有するシングルビットN Vメモリに関する。

### 【0029】

さらなる別の態様は、ワンタイムプログラマブル(OTP)デバイスに関し、該デバイスは、基板上に位置して論理ゲート及び/又は揮発性メモリと関連するトランジスタデバイス用の相互接続ゲート及び/又は別のゲートが同様に共用する材料から成る浮遊ゲートと、ソース領域と、前記浮遊ゲートの一部分に重なり、少なくとも第1ドレイン領域と第2選択可能ドレイン領域とを有するドレイン領域とを備え、前記ドレイン領域と前記浮遊ゲートとの間の可変容量結合は、前記第1ドレイン領域と前記第2ドレイン領域とにそれぞれ適用される一つ以上の選択信号によって実現可能であり、前記可変容量結合によって、前記第1ドレイン領域と前記第2ドレイン領域からの可変量のチャネル熱電子が、前記浮遊ゲートの閾値を恒久的に変更し、前記OTPデバイス内にデータを保存する。

10

### 【0030】

前記OTPデバイスは、上記のマルチレベルデバイスと構造上及び操作上同様に構成することができる。すなわち、容量結合量は、複数のN個(N>1)の独立したドレイン領域又は浮遊ゲートとの重なり合いの大きさを制御/選択すること、又は可変プログラム供給電圧使用することに基づいて調整できる。

20

### 【0031】

デバイスは演算回路内に組み込まれ、処理回路内で他の論理デバイス及び/又はメモリnチャネルデバイスを形成するのに使用されるマスク/C MOS処理によって全て形成されるのが好ましい。場合によっては、不揮発性プログラマブルメモリデバイスは、ダイ/ウエハ用の一つ以上の識別コードを保存するために使用される。

30

### 【0032】

本発明は、多数の異なる実施形態において実行可能であることが詳細な説明から理解されるであろう。さらに、そのような異なる各実施形態が本発明の上述の各目的のうち一つだけ或いは一つ以上を含んでいるであろうということを当業者は容易に認識するであろう。従って、任意の特定の実施形態におけるそのような複数の特性のうち一つ以上が欠けることは、本発明の範囲を限定するものとして解釈されるべきではない。不揮発性メモリアレイとの関連で説明しているが、本教示はあらゆるアプリケーションに使用できることが当業者にとって明らかになるであろう。

### 【図面の簡単な説明】

#### 【0033】

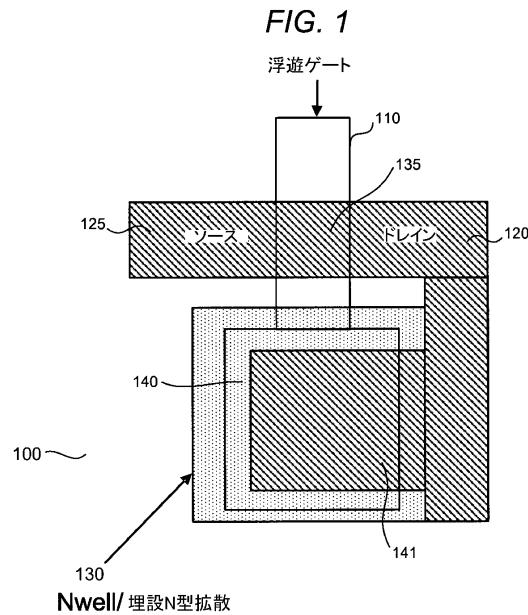

【図1】本発明の不揮発性メモリセルの好適な実施形態の包括図である。

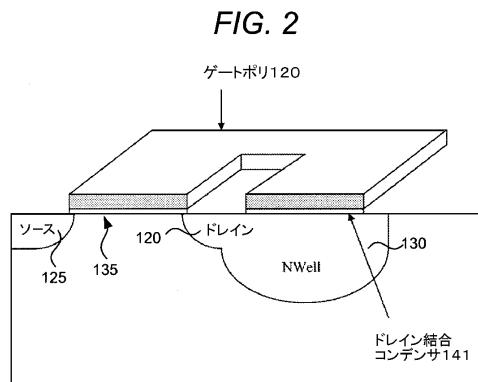

【図2】好適な不揮発性メモリセルの側断面である。

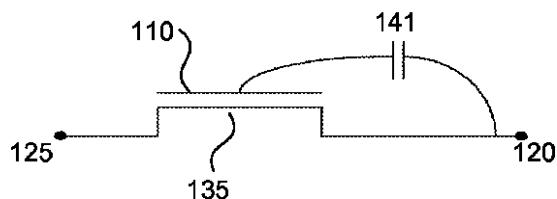

【図3】好適な不揮発性メモリセルの構造の電気的関係性を示す電気回路図である。

【図4】OTPアプリケーション用の浮遊ゲートを使用する先行技術の不揮発性メモリセルを示している。

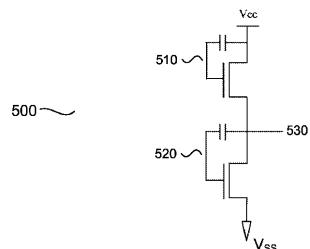

【図5】本発明の各N Vメモリセルと共に構成されたラッチ回路の好適な実施形態を示す電気回路図である。

40

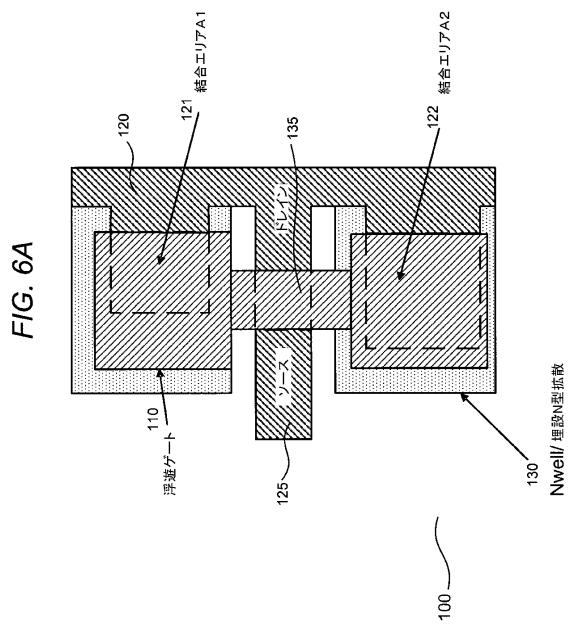

【図6】可変結合を利用する本発明の不揮発性メモリセルの好適な実施形態の包括図である。

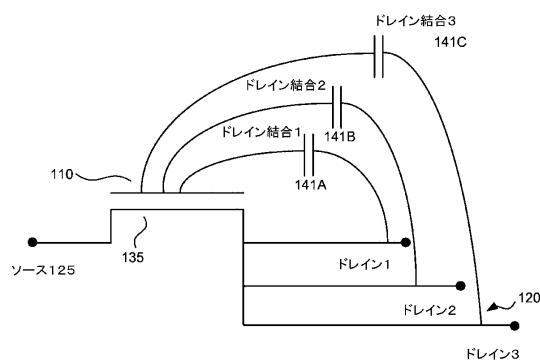

【図7】可変結合を利用する好適な不揮発性メモリセルの各構造の電気的関係性を示す電気回路図である。

### 【発明を実施するための形態】

#### 【0034】

本開示は、可変的な容量結合を利用するOTP(ワンタイムプログラマブル)又はMTP(マルチタイムプログラマブル)メモリセルのいずれかとして動作可能な新しいタイプの不揮発性メモリデバイス構造(単層ポリが好ましい)に関する。好適なデバイス構造は

50

、高度 CMOS 論理プロセスと完全に互換性があり、最悪の場合、実行するための最小限の追加ステップを必要とする。

#### 【0035】

本デバイス特有の態様は、メモリセル構造の浮遊ゲートがトランジスタの不定数の S / D 接合部を通じて電気的に強硬に結合されることであり、一方で、従来の単層ポリ不揮発性メモリセルは、浮遊ゲートに結合するための追加的な相互接続層を必要とするか、又は浮遊ゲートが事実上既存の各電気信号のいずれかにも電気的結合をしない或いは最小限電気的結合を行うことを必要とする。さらに、米国特許公開公報第 2008 / 0186772 号とは異なり、結合比をより具体的かつ正確にすることによって、最終的にプログラムされた  $V_t$  は結合比とドレイン電圧の積に正比例する。<sup>10</sup> 結合比がメモリセルの所望のプログラミング閾値レベル ( $V_t$ ) によって決定又は設定されるように、結合比をより正確に制御できる。これにより、異なる各結合比がプログラムされた異なる  $V_t$  を生み出すので、OTP のマルチレベル版に容易に展開する設計が可能となる。

#### 【0036】

図 1 は、本発明に使用される好適な構造のレイアウトの上面図を示す。図 2 は、デバイス構造の代表的な断面図を示す。これらの図は拡大することを意図したものではなく、デバイスの幾つかの態様を省略することにより明確にしていることが理解されるであろう。

#### 【0037】

本デバイスは、標準的な NMOS トランジスタ 100 を含み、該トランジスタは、デバイスのゲート（好適な実施形態においてポリである）110 が電源に電気的に接続されないように修正される。デバイスのドレイン 120 は、従来型の高度 CMOS プロセスに既に一般的に存在する N 型 well 130 付近で湾曲し、さらに該 N 型 Well 130 によって接合されるのが好ましい。代案として、N-well 130 は、ポリ浮遊ゲートの真下にくるよう導入された n 型拡散層と置き換えることができる。従来型ソース領域 125 が同様に利用される。<sup>20</sup>

#### 【0038】

浮遊ゲートポリ 110 は、標準的なトランジスタチャネル領域 135 を越えて延在し、ドレイン接合面から延長しているアクティブ領域に重なる重複領域 140 を有する。N-well 領域によって囲まれたアクティブ領域部 141 は、浮遊ゲートとの効果的な容量結合としての機能を果たす。従って、ドレイン接合面に印加されるいかなる電圧も浮遊ゲート上に効果的に結合される。<sup>30</sup>

#### 【0039】

図 3 の電気回路図に示すように、ドレインの浮遊ゲートに対する結合比（ゲートチャネル領域のエリアとドレイン延長領域に重なるポリ延長エリアとの比率によって決定される）が十分に高い場合、浮遊ゲートは効果的にドレイン電圧値の割合を高く確保及び有することができる。

#### 【0040】

図 1 及び図 2 に示すように、好適な実施形態の重要な利点は、CMOS プロセスで各 n 型チャネルデバイスをアクティブにするために従来使用される同じ各層から形成されることである。唯一の違いは、ポリ（または場合によっては金属）ゲート層がそのような別に形成された各アクティブデバイスに相互接続されない又はゲート信号に連結されないことがある。ソース / ドレイン用の他の各インプラントも CMOS 従来型プロセスの一部である。それゆえ、ほとんどのアプリケーションにおいて、代替物は処理されるウエハの各関連層用の既存のマスクだけであるため、本発明は追加処理コストなしで集積化できる。<sup>40</sup>

#### 【0041】

このデバイス構造の別の任意の一変形例は、トレンチの側壁上にドレインとゲート間を結合するコンデンサ領域を作成することである。これによって、コンデンサに結合しているドレインとゲート間の領域を大幅に減少させる。このセルエリア内の減少は、製造プロセスを著しく複雑するということを犠牲にして成り立っている。しかしながら、さらに、<sup>50</sup>

本発明が特定の種類のDRAMアーキテクチャ（特に、組込型）と一体化されるアプリケーションにおいては、追加処理コストを回避するためにそのようなメモリ用の従来型処理ステップを組み込むことが可能である。電圧を浮遊ゲートに結合及び所望の結合比を達成するための他の技術が、当業者に明らかになるであろう。

#### 【0042】

浮遊ゲートは単一ポリシリコン層として示されているが、当業者は他の資材も同様に使用可能であることを理解するであろう。例えば、幾つかのアプリケーションにおいては、他の主要な下層の論理/メモリ構造の一部である一方、何らかの浮遊ゲートを作成する目的のためにも利用できる他の各構造/デバイスの構成を利用することが可能であってもよい。この点において、各浮遊ゲートは、各不純物が誘電体層/絶縁層に埋め込まれる/拡散される技術によることも含めて、通常多数の異なる材料から形成可能であることを留意すべきである。10

#### 【0043】

さらに、好適な実施形態がNVMセルを基板上の従来の外側かつ平面のFET構造の一部として示しているが、非平面構造を含む他の形状/アーキテクチャを利用できることが当業者に明らかになるであろう。従って、本発明は、薄膜構造において、基板よりもデバイスの他の各レベルで、マルチゲート（FINFETタイプ）配向及び垂直/非平面構造において各SOI基板内に使用できる。そのような後者の場合、浮遊ゲートは、基板に対して垂直に内蔵及び方向付けられる。

#### 【0044】

デバイス100の好適な操作を説明する。不揮発性デバイス構造は、高度CMOS論理プロセスで実行される従来型I/Oトランジスタの物理的特徴を備えることが好ましい。現時点では、そのようなI/Oトランジスタは名目上3.3Vで動作するが、この値は、製造業の後に続く世代とともに変化するであろうということが理解される。20

#### 【0045】

このタイプのI/Oトランジスタは、通常、70Aの標準的な電気的ゲートの酸化層の厚さを有する0.5Vから0.7Vの閾値電圧である。結合比0.90で浮遊ゲートに結合されるドレインと、デバイスに印加される1.0Vの読み取りドレイン電圧によって、浮遊ゲートはおよそ0.90Vの電圧で効果的に結合されるであろう。これは、プログラムされていないNMOSデバイス100を起動するのに十分であり、チャネル電流は、デバイスの状態を確認する感知回路（sense circuitry）の一般的な手段によって検知できる。特定の結合比や読み取り電圧などはアプリケーションからアプリケーションに変化し、各特性を作用する所望のデバイスに基づいて構成できることが当業者に理解されるであろう。30

#### 【0046】

デバイスは、本来プログラムされていない状態であり、該プログラムされていない状態とは、好適な実施形態において、チャネル領域135を通じてソースとドレインとの間を結合している低抵抗によって特徴づけられる。これは、チャネル領域135を実質的に均一にすることが可能であり、電流の流れが確実であることを意味する。好適な実施形態は対称的なセル/チャネルの形状で示されているが、本発明は、上述の米国特許公開公報第2008/0186772号に示されるような非対称の形状で使用できることが理解されるであろう。40

#### 【0047】

デバイスをプログラム状態にするために、デバイスは、チャネル領域内の各キャリアを減少させ、さらに閾値電圧を増加させることによって遮断されなければならない。このために、6.0Vのドレイン電圧を印加することが可能であり、これによって約5.4Vの電圧を効果的に浮遊ゲートに結合する。このバイアス条件は、デバイスをチャネル熱電子注入体制に設定する。浮遊ゲートに注入された各電子は、デバイスの閾値電圧を効果的に増加させる。1.0Vの後続の読み取り電圧がドレイン上に再び印加される場合、デバイスはその高い閾値電圧の結果、電流を伝導せず、従ってこのデバイスの第二状態が確定さ50

れる。読み取られた各特性と同様に、特定の結合比、プログラム電圧などはアプリケーションからアプリケーションに変化し、各特性を作用する所望のデバイスに基づいて構成できることが当業者に理解されるであろう。

#### 【0048】

上述の従来技術は、浮遊ゲートに対する帶電を解除するためのメカニズムが開示されていないため、主にワンタイムプログラマブルデバイスである。対照的に、本発明の幾つかの実施形態は、マルチタイムプログラムが可能になっている。このために、浮遊ゲートに注入された各電子を除去或いは中和するよう消却作業を導入できる。各電子を除去或いは中和するためのメカニズムは、デバイスの他の非連結接合面125からバンド間トンネリング熱正孔注入によることが好ましい。好適なバイアス条件は次のようになる。非連結接合面(ソース接合面)は、6Vのバイアスが印加されることによって、接合面にバンド間トンネリング電流を誘導させる。バンド間トンネリング電流は熱孔子を浮遊ゲートに注入させ、浮遊ゲート上に保存された各電子を中和させる。従って、デバイスは非伝導又は低伝導状態から伝導状態に(再)プログラムされる。デバイスは、その後、後続の読み取り電圧が読み取り作業中に連結接合面に印加される場合、チャネル電流を流すことができる。低伝導状態から伝導状態にプログラミングすることは、限定作業読出しウィンドウを有することが可能であることが理解されるであろう。10

#### 【0049】

追加的な任意の作業として、消去作業を容易にし、バンド間トンネリング電流を高めるために、浮遊ゲートがより負に帯電されて、ソース接合面を横切るより高いバンド間トンネリング電流をもたらすように、連結接合面を負電圧で供給できる。20

#### 【0050】

従って、各作業特性は以下のようになることが好ましい。

| 作業    | ドレイン       | ソース  | 基板 |

|-------|------------|------|----|

| プログラム | 6.0V       | 0V   | 0V |

| 読み取り  | 1.0V       | 0V   | 0V |

| 消去    | フロート又は Vcc | 6.0V | 0V |

#### 【0051】

幾つかの実施形態では、OTP及びMTPデバイスが浮遊ゲート上に蓄積された電荷の損失に対する十分な耐性を確実に備えるようにさらなる保護を実行できる。このために、デバイスは図5に示すように、一対のラッチ500内に構成でき、そこでデータ及びその補数が該ラッチ内に保存され、その結果保存されたデータ内におけるマージンを効果的に2倍にする。そこに示されるように、上部デバイス510はノード530を第1電圧基準(Vcc)に結合させるが、第2の下部デバイス520は該ノードを第2電圧基準(Vss)に結合させる。上部デバイス浮遊ゲートに帯電させることによって上部デバイス510は非導電状態にプログラムされ、ノード530は下部デバイス520によってVssに確実に引き下げられ、第1論理データ値(0)を示すこととなる。同様に、下部デバイス浮遊ゲートに帯電させることによって、下部デバイス520は非導電状態にプログラムされ、ノード530は上部デバイス510によってVccに確実に引き上げられ、第2論理データ値(1)を示すこととなる。3040

#### 【0052】

本発明の好適な実施形態の別の有用な利点は、最も従来型の各単層ポリOTPは、通常PMOSデバイス構造で実行されるが、本実施例はNMOSデバイス構造で実行されることである。これは、デバイスをウエハ上の他の各nチャネルデバイスと同時に形成できることを意味している。本発明におけるNMOSデバイス構造の別の利点は、該デバイスがEPROMデバイスと同じように機能することであり、すなわち、デバイスは伝導状態から非伝導状態にプログラムされる。対称的に、米国特許公開公報第2008/0186772号の先行技術のタイプのデバイス及び一般に使用される他の各PMOS・OT

P デバイスは、非伝導状態から伝導状態にプログラムされる。従って、本発明の本態様は、PMOS デバイスが製造工場から出て非伝導状態になるのを確認するために一般に PMOS・OTP デバイスと関連する追加のマスキングステップの必要性を取り除くことができる。

#### 【 0 0 5 3 】

さらに、チャネル熱電子注入 (channel hot electrons injection) を伴う NMOS デバイスのプログラミング機構が自己制御式であるため、チャネル熱電子プログラミングを伴う PMOS の場合とは異なり、本発明におけるプログラミング中のエネルギー消費量は自己制御される。

#### 【 0 0 5 4 】

それゆえ、本明細書に示すように、浮遊ゲートの特定の構成は決定的ではない。必要なのは、チャネル伝導を制御するよう構造的及び電気的に構成され、電荷キャリアの電気的ソースに容量的に結合されることだけである。所望のレイアウトまたはマスクに従って、特定の形状に変更可能である。場合によっては、浮遊ゲートを例えば多層構造として実装することが望ましい。さらに、容量結合は使用される各材料の機能であるので、本発明は、浮遊ゲートの構成を要望通り収容するように変更及び特定のプロセスに統合できるよう、大幅な柔軟性を認めている。本教示に従って構築された各セルのアレイは、閾値セルを有する各セルが形成できるように異なる形状や大きさの各浮遊ゲートを備えることができる。

#### 【 0 0 5 5 】

##### 可変結合

本発明の他の実施形態では、デバイス 100 の効果的な結合比は、読み取り、プログラム及び / 又は消去操作の間で異なる、或いは変更することができる。すなわち、図 1 及び図 2 には示されていないが、浮遊ゲートに結合されるドレイン領域 120 は、一つ以上の別々の各サブ領域に分割できる。この詳細を図 6A 及び 6B に示す。各サブ領域 121、122 などは、浮遊ゲートとの重複量が異なるように製造又は制御されることが可能である。そのような一つ以上のサブ領域に対して異なる電圧を選択的に印加することによって、読み取り / プログラム / 消去操作に対して異なる種類の性能が実現可能となる。例えば、超低電力（しかしいくらか遅めの）プログラム又は消去操作があることが望ましい。これは、第 2 タイプ（読み取り）操作中に使用される名目上のエリアよりも小さいそのような第 1 タイプの操作用の結合エリアを作成することによって実現できる。

#### 【 0 0 5 6 】

図 6A 及び図 6B において、可変結合ジオメトリは、ドレイン拡散の大きさを（拡散マスクにおいて）変更し、浮遊ゲートの大きさを一定に保つことによって行われるが、同じ実効性のある結果は、ドレイン拡散を一定に保って浮遊ゲートの大きさを変更することによって実現できることは当業者に明らかになるであろう。例えば、浮遊ゲート領域 122 は、サイズを縮小することによって同じ結果をもたらすことができる。各浮遊ゲートのサイズを調整することによって、各拡散領域を同様に共有することができ、その結果、（他のセル用の）隣接した浮遊ゲート 122' は、ドレイン領域 120 に結合できる。これらの技術の他の組み合わせも同様に使用可能であり、設計 / 性能要求に基づいて選択可能である。

#### 【 0 0 5 7 】

特に、本発明の可変結合の各態様は、PMOS 及び NMOS の OTP 両方に使用可能である。多状態保存、すなわちマルチレベルの OTP の可能性がある浮遊ゲート上に異なる電圧を与えるよう異なる結合比の選択も利用できる。

#### 【 0 0 5 8 】

別の実施形態として、当然ながらプログラム供給電圧を代わりに調整することによってドレイン結合が行われ、特定のセルに印加されたプログラム供給電圧は浮遊ゲートに異なる状態を書き込むように調整される。ドレインは浮遊ゲートに結合されるため、可変プログラム供給電圧は浮遊ゲートに供給されるべきである。例えば、ドレイン電圧は、3、4

10

20

30

40

50

種類以上の異なるレベルを有するように調整できる。これにより異なる形式の可変容量結合をもたらし、該結合は書き込みの観点からはより複雑になるが、幾つかのアプリケーションでは有用となるであろう。

#### 【0059】

NMOS 実行用のマルチレベルOTP の変形例は、当該状態を感知するために印加された異なる各ドレイン電圧を通じて異なるレベルの各浮遊ゲート電圧を使用する場合を除いて、NMOS はオフ状態にプログラムされ、多少オフ状態であることは、十分にオフ状態であることと非常に類似していることを考慮に入れなければならない。しかしながら、そのような状況においては、異なるドレイン電圧は読み取り妨害耐性を不適切に低下させることもあり、ここで交換される可能性がある。

10

#### 【0060】

マルチレベル性能の他の選択肢については、異なるドレインからゲートへのキャパシタンス選択がプログラミング状態を選択するのに（異なる重複エリアを通して）使用されるので、読み取り操作は、多状態のセルを検出するために同じ單一ドレイン重複によって実行できる。例えば、二つの異なるドレイン重複により、合計 2 ビットが実行可能である。そのような実行において、ドレイン 1 は、ドレイン 2 の結合比の数倍（この場合 2 の倍数が好み）の結合比を有するように設定可能である。

#### 【0061】

以下の表が示すように、ドレイン 1 に 0 V の電圧及びドレイン 2 に 6 V の電圧を付与するプログラム供給電圧は、ゲートに付与された第 1 の電荷量に基づいて、セルに第 1 状態を書き込むことになる。代わりに全てのドレインをプログラムする場合、追加された電荷はさらに高くなり、第 2 状態などに対応する。

20

#### 【0062】

合計四つの異なる結合（0（ドレインなし）、1 ×（ドレイン 2）、2 ×（ドレイン 1）、3 ×（ドレイン 1 及びドレイン 2 の両方））が四つの異なる閾値電圧に対応し、それに伴って四つの異なる論理状態がこの単純な配列において達成可能となる。

#### 【0063】

以下の表 2 に示すように、セルの状態を読み取る好適な方法は、ドレイン 1 及びドレイン 2 の両方に読み取り電圧を印加することである。その結果、浮遊ゲート上の電荷量と反比例するセル電流の量が検出される。上述のように、浮遊ゲート上の電荷は、プログラミング中に適用される結合量の一次関数である。従って、セルにおける 0、1 ×、2 × 及び 3 × の状態は読み取り電流との関係によって検出できる。この実施形態において、読み取りドレイン電圧は約 1 ボルトに選択されることが好み。これは、いかなる種類の読み取り妨害又はドレインが引き起こす漏洩を防ぐという利点がある。

30

#### 【0064】

読み取り操作中にデコードを少なくする代替案として、読み取りは、本実施例において最も高い結合比である 2 × ドレインによってドレインノード上で常に行うことができる。そのような場合、全ての四つの異なる状態間で差別化することは可能ではないが、幾つかのアプリケーションにおいては好適なトレードオフとなるかもしれない。

#### 【0065】

同様に表 2 に示すように、マルチレベルセル状態を読み取るさらなる代替手段として、各ドレインのおおの（又は組み合わせ）に徐々に電圧を変更しながらバイアスをかけることによって結集した重複部分からの結合電荷寄与（coupled charge contribution）を決定する。閾値電圧が、セルの状態を確認するための特定の電圧レベルで特定の時間間隔内において達成又はデコードされるまで、ドレインに徐々に（0 からゲートを最も高い閾値状態にするのに十分な任意の目標電圧にまで）増加する電圧でバイアスをかける。従って、全て又は幾つかのドレインはプログラム操作中にバイアスをかけられるが、單一ドレインだけは（上記のように、他のドレインにもバイアスをかけられるが）セルの状態を決定するために読み取り中にバイアスをかけられる必要がある。特定の範囲の読み取りドレイン電圧は、望ましい操作特性などの特定のセル構造に左右され、定期的な検査によって決定で

40

50

きる。また、この実施形態においても、全ての四つの異なる状態の間で差別化をすることは可能ではないが、幾つかのアプリケーションにおいては好適なトレードオフとなるかもしれない。セルをプログラミング及び読取るための他の実施例が当業者に明らかになるであろう。

#### 【 0 0 6 6 】

| 作業    | ドレイン 1                    | ドレイン2                     | ソース    | 基板 |

|-------|---------------------------|---------------------------|--------|----|

| プログラム | 0又は6 V                    | 0又は6 V                    | 0V     | 0V |

| 読み取り  | 1 ボルト(又はMボルト<br>ずつ0~Nボルト) | 1 ボルト(又はMボルト<br>ずつ0~Nボルト) | 0V     | 0V |

| 消去    | フロート又は ~Vcc               | フロート又は ~Vcc               | 6 . 0V | 0V |

10

#### 【 0 0 6 7 】

当然ながら、他の結合比も可能であるが、2の倍数でない異なる比率を選択することによる制約を受け、検出マージン / 差別化は優れていないかもしれない。しかしながら、場合によっては、それぞれの重複部分を任意のより高い / より低い倍率に設定するのが望ましく、それにより任意の出力範囲で二つの隣接する状態間の検出マージンを減少させる効果を持つであろう。しかしながら、検出範囲の感度が不均等である場合、これが好適な選択肢になるであろう（すなわち、4 x と 5 xとの間よりも 1 x と 2 xとの間の差異を検出するほうが容易である場合、又はその逆の場合も同じである）。さらに、場合によっては、奇数の論理状態になる各組み合わせの一つを捨てることによって有効論理状態の数を減少することが望ましい。例えば、マルチビットセルは、単に { 0、ドレイン 1、ドレイン 2 } の三つのプログラムされたドレイン結合を有することができ、{ ドレイン 1 + ドレイン 2 } は無視することとなる。

20

#### 【 0 0 6 8 】

二つの別々の結合比を図 6 A に示し、三つの別々の結合比を図 6 B に示すが、他の分割や結合が本教示に従って実行できることが理解されるであろう。例えば、図 6 B の場合、3 つの異なるレベルの電荷結合を利用することによって 8 つの異なるプログラム状態が実現できる。例えば、1 x、2 x 及び 4 x の結合比を有する各ドレインの異なる組み合わせは統合することが可能であり、又は幾つかの他の比率の組み合わせでもよい。さらに、他の選択は、各状態間のより高いマージンと引き換えに、より少ない各論理状態で行うことができる。本発明の他の変化形が当業者に明らかになるであろう。

30

#### 【 0 0 6 9 】

上記の説明は、提案された各発明の单なる例示的な各実施形態にすぎない。本発明に与えられた保護は、上記の実施形態とは異なる実施形態を同様に含み、適用されるが、該実施形態は本願請求項の範囲内に入るものであることが理解される。

【図1】

【図2】

【図3】

**FIG. 3**

【図4】

**FIG. 4**

先行技術

【図5】

**FIG. 5**

【図 6 A】

【図 6 B】

*FIG. 6B*

## フロントページの続き

|                          |                    |

|--------------------------|--------------------|

| (51)Int.Cl.              | F I                |

| H 01 L 27/115 (2006.01)  | H 01 L 27/10 4 3 3 |

| H 01 L 21/8247 (2006.01) | H 01 L 27/10 4 6 1 |

| H 01 L 27/112 (2006.01)  |                    |

| H 01 L 21/8246 (2006.01) |                    |

| H 01 L 27/10 (2006.01)   |                    |

(31)優先権主張番号 12/264,060

(32)優先日 平成20年11月3日(2008.11.3)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/264,076

(32)優先日 平成20年11月3日(2008.11.3)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/271,647

(32)優先日 平成20年11月14日(2008.11.14)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/271,666

(32)優先日 平成20年11月14日(2008.11.14)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/271,680

(32)優先日 平成20年11月14日(2008.11.14)

(33)優先権主張国 米国(US)

(31)優先権主張番号 12/271,695

(32)優先日 平成20年11月14日(2008.11.14)

(33)優先権主張国 米国(US)

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(72)発明者 リウ , デイヴィッド

アメリカ合衆国・カリフォルニア州 9 4 5 3 9 ・フレモント・ベンボウ ドライブ 4 2 0 6 3

(72)発明者 グロス , ジョン

アメリカ合衆国・カリフォルニア州 9 4 1 1 4 ・サン フランシスコ・18番 ストリート 3

8 8 3

審査官 小山 満

(56)参考文献 特開平05-021809(JP,A)

特開平08-340057(JP,A)

特開2007-067428(JP,A)

特開2005-057106(JP,A)

特開2001-358313(JP,A)

特開2005-038894(JP,A)

特開2004-281971(JP,A)

特開2005-317921(JP,A)

特表2005-533372(JP,A)

特表2003-501806(JP,A)

特表2006-507693(JP,A)

特開2003-197765(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 336

G 11 C 16 / 02

G 11 C 16 / 04

H 01 L 21 / 8246

H 01 L 21 / 8247

H 01 L 27 / 10

H 01 L 27 / 112

H 01 L 27 / 115

H 01 L 29 / 788

H 01 L 29 / 792