(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6364956号

(P6364956)

(45) 発行日 平成30年8月1日(2018.8.1)

(24) 登録日 平成30年7月13日(2018.7.13)

(51) Int.Cl.

F 1

H03F 1/32 (2006.01)

H03F 3/60 (2006.01)H03F 1/32

H03F 3/60

請求項の数 6 (全 8 頁)

(21) 出願番号 特願2014-107357 (P2014-107357)

(22) 出願日 平成26年5月23日 (2014.5.23)

(65) 公開番号 特開2015-222921 (P2015-222921A)

(43) 公開日 平成27年12月10日 (2015.12.10)

審査請求日 平成28年12月8日 (2016.12.8)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 100082175

弁理士 高田 守

(74) 代理人 100106150

弁理士 高橋 英樹

(74) 代理人 100148057

弁理士 久野 淑己

(72) 発明者 金谷 康

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 緒方 寿彦

最終頁に続く

(54) 【発明の名称】 リニアライザ

## (57) 【特許請求の範囲】

## 【請求項 1】

入力端子と分岐点との間に接続された入力伝送線路と、前記分岐点と第1の出力端子との間に接続された第1の出力伝送線路と、前記分岐点と第2の出力端子との間に接続された第2の出力伝送線路とを有する分岐回路と、

前記分岐点に直接的に接続されたアノードと、カソードとを持つダイオードと、

前記ダイオードをバイアスするバイアス回路とを備えることを特徴とするリニアライザ

。

## 【請求項 2】

$Z_d$  は前記ダイオードのインピーダンスであり、

10

$Z_i$  は前記分岐点からみた前記分岐回路の入力インピーダンスであり、

$Z_o$  は前記分岐回路の出力インピーダンスであり、

$Z_d > \frac{Z_i Z_o}{2Z_i + Z_o}$  を満たすことを特徴とする請求項1に記載のリニアライザ。

## 【請求項 3】

前記ダイオードの前記カソードに接続されたインダクタを更に備えることを特徴とする請求項1又は2に記載のリニアライザ。

## 【請求項 4】

前記ダイオードの前記カソードに接続されたピアホールを更に備えることを特徴とする

20

請求項 3 に記載のリニアライザ。

【請求項 5】

前記ダイオードの前記カソードに接続された抵抗を更に備えることを特徴とする請求項 1 又は 2 に記載のリニアライザ。

【請求項 6】

前記ダイオードの前記アノードが前記分岐回路に接続される接続点は、前記入力伝送線路の中央線の延長線から前記入力伝送線路の幅の 3 倍の範囲内で前記延長線からずれていることを特徴とする請求項 1 ~ 5 の何れか 1 項に記載のリニアライザ。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、高周波増幅器に接続され、歪特性を改善するリニアライザに関する。

【背景技術】

【0002】

近年、窒化物半導体（例えば GaN）を用いたトランジスタの研究開発が盛んであり、その応用例として通信用高出力増幅器がある。GaN を用いた増幅器は従来の化合物半導体（例えば GaAs）と比較して高出力化できる。しかし、低い入力電力から利得が緩やかに減少する GaN 特有のソフトコンプレッションにより、特に AMAM 特性（入力レベルを増加させた時の出力レベル特性）が低下する。

【0003】

20

そこで、AMAM 特性を補償するアナログプレディストーションとして、ダイオードを用いたリニアライザが用いられる（例えば、特許文献 1 参照）。特に、GaN 系の増幅器 MMIC はエピ基板が高価なため、回路構成が小さいリニアライザは好ましい。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2012-244545 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

30

しかし、小型ではあるものの、リニアライザを増幅器に単純にカスケード接続すると、リニアライザがない増幅器と比較して回路面積の増加は避けられない。従って、高価なエピ基板の使用面積が大きくなり、コストが増大するという問題がある。

【0006】

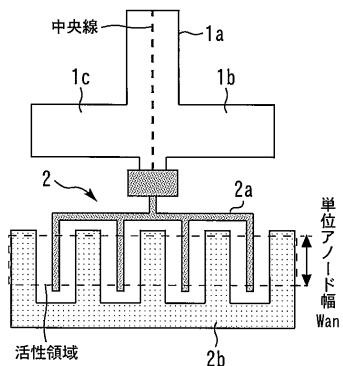

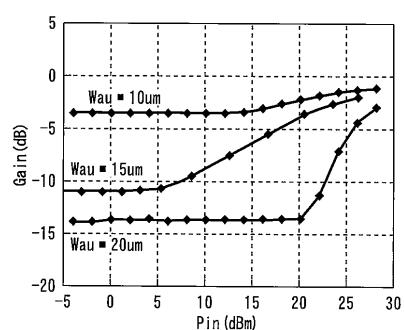

また、GaN-MMIC で使用するリニアライザのダイオードは一般的にショットキーバリアダイオードである。このとき、ダイオードのセルサイズは、単位アノード幅  $W_{a u}$  が短く、フィンガー数が多いセルが望ましい。これには以下の 2 つの理由がある。第 1 に、単位アノード幅  $W_{a u}$  が短いリニアライザの方が、リニアライザの挿入損失を低くしやすいためである。図 12 はリニアライザの AMAM 特性の単位アノード幅  $W_{a u}$  依存性を示す図である。単位アノード幅  $W_{a u}$  が  $20 \mu m$  の場合に最も挿入損失が大きいことが分かる。第 2 に、アノードメタルに過大な電流を流すとアノード電極にエレクトロマイグレーションが発生するため、信頼性の観点からアノードメタルの電流容量に制限がある。これを回避するため、極力、フィンガー数を多くして、フィンガー 1 当たりの電流値を低減させる必要がある。

40

【0007】

一方、単位アノード幅  $W_{a u}$  を決める活性領域の境界はウエハプロセスにおいて制御にくく、単位アノード幅  $W_{a u}$  のばらつきが大きくなる。特に単位アノード幅  $W_{a u}$  が短ければ単位アノード幅全体に対するばらつき量が大きく見えるため、ダイオード特性が大きくばらつき、リニアライザ特性のばらつきが大きくなる。逆に、単位アノード幅  $W_{a u}$  が長ければ全体に対するばらつき量が小さくなるため、特性ばらつきは小さくなる。この

50

ように、製造歩留の観点では、単位アノード幅  $W_{a u}$  は長い方が望しい。従って、挿入損失と製造歩留でトレードオフが発生するという問題がある。

#### 【0008】

本発明は、上述のような課題を解決するためになされたもので、その目的はコストと挿入損失を低減しつつ歩留まりを高くすることができるリニアライザを得るものである。

#### 【課題を解決するための手段】

#### 【0009】

本発明に係るリニアライザは、入力端子と分岐点との間に接続された入力伝送線路と、前記分岐点と第1の出力端子との間に接続された第1の出力伝送線路と、前記分岐点と第2の出力端子との間に接続された第2の出力伝送線路とを有する分岐回路と、前記分岐点に直接的に接続されたアノードと、カソードとを持つダイオードと、前記ダイオードをバイアスするバイアス回路とを備えることを特徴とする。

#### 【発明の効果】

#### 【0010】

本発明では出力側回路が2つであるため、出力側回路が1つの場合と比較して分岐回路のインピーダンス  $Z_c$  は低くなる。このため、高周波信号はダイオードの影響を受け難くなり、ダイオードの挿入損失を低減することができる。従って、挿入損失が大きくなり易い単位アノード幅  $W_{a u}$  が長いダイオードを用いても挿入損失を低減することができる。単位アノード幅  $W_{a u}$  が長いダイオードは特性ばらつきが小さく製造歩留まりが高い。このため、本発明により挿入損失を低減しつつ歩留まりを高くすることができる。

#### 【0011】

また、トーナメント型構成の増幅器では分岐点付近はレイアウトに余裕が出やすい。本発明では分岐点にリニアライザを設けるため、回路面積の増大を抑えつつリニアライザを挿入することができる。従って、高価なエビ基板の使用面積を増大させないため、コストを低減することができる。

#### 【図面の簡単な説明】

#### 【0012】

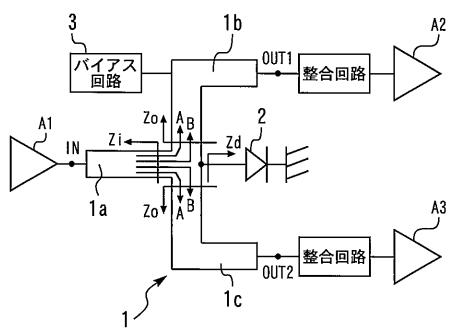

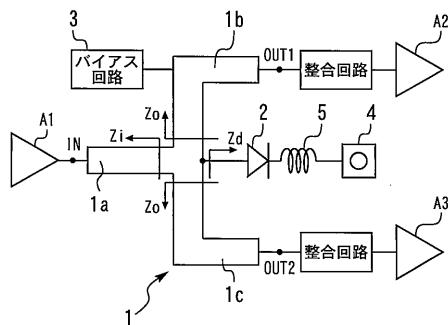

【図1】本発明の実施の形態1に係るリニアライザを示す図である。

【図2】図1のリニアライザの一部を拡大した図である。

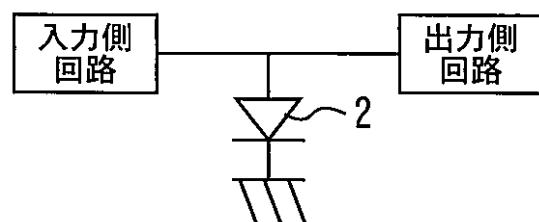

【図3】比較例に係るリニアライザを示すブロック図である。

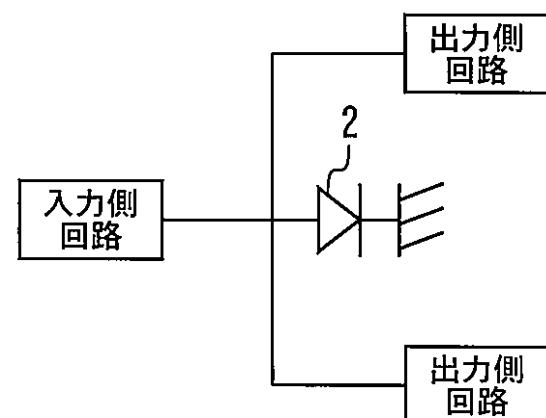

【図4】本発明の実施の形態1に係るリニアライザを示すブロック図である。

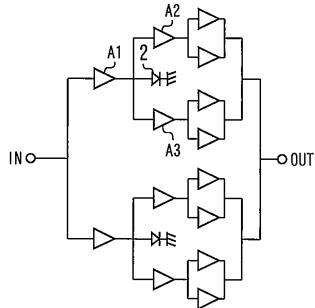

【図5】本発明の実施の形態1に係るリニアライザ付増幅器を示すブロック図である。

【図6】本発明の実施の形態2に係るリニアライザを示す図である。

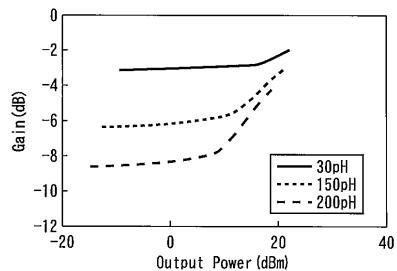

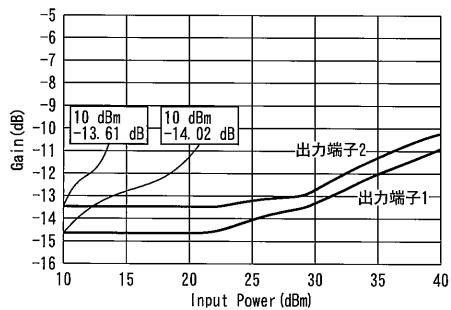

【図7】本発明の実施の形態2に係るリニアライザのAMAM特性を示す図である。

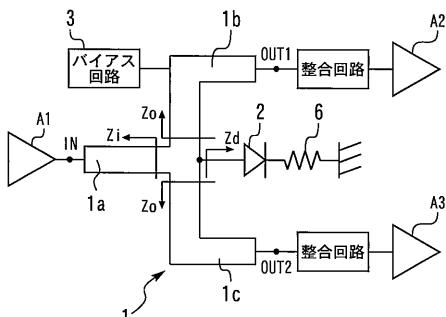

【図8】本発明の実施の形態3に係るリニアライザを示す図である。

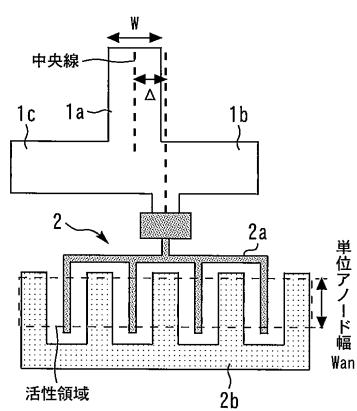

【図9】本発明の実施の形態4に係るリニアライザの一部を拡大した図である。

【図10】本発明の実施の形態4に係るリニアライザのAMAM特性を示す図である。

【図11】本発明の実施の形態4に係るリニアライザ付増幅器を示す図である。

【図12】リニアライザのAMAM特性の単位アノード幅  $W_{a u}$  依存性を示す図である。

#### 【発明を実施するための形態】

#### 【0013】

本発明の実施の形態に係るリニアライザについて図面を参照して説明する。同じ又は対応する構成要素には同じ符号を付し、説明の繰り返しを省略する場合がある。

#### 【0014】

実施の形態1。

図1は、本発明の実施の形態1に係るリニアライザを示す図である。図2は、図1のリニアライザの一部を拡大した図である。前段の増幅器A1と後段の増幅器A2, A3の段間にリニアライザが挿入されている。リニアライザの分岐回路1は入力伝送線路1aと出力伝送線路1b, 1cを有する。入力伝送線路1aは入力端子INと分岐点との間に接続されている。出力伝送線路1bは分岐点と出力端子OUT1との間に接続され、出力伝送

10

20

30

40

50

線路 1 c は分岐点と出力端子 O U T 2 との間に接続されている。

【 0 0 1 5 】

ダイオード 2 のアノードが分岐回路 1 の分岐点に接続され、カソードが接地されている。本実施の形態では入力伝送線路 1 a の中央線の延長線上にダイオード 2 のアノードが接続されている。バイアス回路 3 がダイオード 2 を順方向にバイアスする。ダイオード 2 のアノードフィンガー 2 a とカソードフィンガー 2 b が交互に配置されている。ダイオード 2 の活性領域の幅が単位アノード幅 W a u である。

【 0 0 1 6 】

高周波信号は一般に 2 分岐する線路の内側を通る性質がある。従って、図中において高周波信号は経路 B よりも経路 A を通りやすい。経路 A を通る高周波信号はダイオード 2 を感じずに通過する。リニアライザにより損失が発生するのは高周波信号が経路 B を通る場合である。このような高周波信号の経路は分岐点を基点としたインピーダンスに依存する。

10

【 0 0 1 7 】

ダイオード 2 のインピーダンスが分岐回路 1 のインピーダンスより低い場合、即ち式(1)を満たす場合には、リニアライザの挿入損失が大きくなる。ここで、Z d はダイオード 2 のインピーダンスであり、Z i は分岐点から入力伝送線路側を見たインピーダンスであり、Z o は分岐点から出力伝送線路側を見たインピーダンスである。

$$Z_d < \frac{Z_i Z_o}{2Z_i + Z_o} \quad (1)$$

20

【 0 0 1 8 】

一方、ダイオード 2 のインピーダンスが分岐回路 1 のインピーダンスより高い場合、即ち式(2)を満たす場合には、一部の高周波信号はダイオード 2 を感じずに入力伝送線路 1 a から出力伝送線路 1 b, 1 c に抜けていく。このため、高周波信号はダイオード 2 の影響を受け難くなり、ダイオード 2 の挿入損失を低減することができる。

$$Z_d > \frac{Z_i Z_o}{2Z_i + Z_o} \quad (2)$$

30

【 0 0 1 9 】

図 3 は比較例に係るリニアライザを示すブロック図である。図 4 は本発明の実施の形態 1 に係るリニアライザを示すブロック図である。比較例では出力側回路が 1 つであるが、本実施の形態では出力側回路が 2 つである。このため、式(3)のように比較例と比較して本実施の形態では分岐回路 1 のインピーダンス Z c は低くなる。このため、高周波信号はダイオード 2 の影響を受け難くなり、ダイオード 2 の挿入損失を低減することができる。

$$Z_c = \frac{Z_i Z_o}{Z_i + Z_o} > \frac{Z_i Z_o}{2Z_i + Z_o} \quad (3)$$

40

【 0 0 2 0 】

従って、挿入損失が大きくなり易い単位アノード幅 W a u が長いダイオード 2 を用いても挿入損失を低減することができる。単位アノード幅 W a u が長いダイオード 2 は特性ばらつきが小さく製造歩留まりが高い。このため、本実施の形態により挿入損失を低減しつつ歩留まりを高くすることができる。

【 0 0 2 1 】

図 5 は本発明の実施の形態 1 に係るリニアライザ付増幅器を示す図である。増幅器 A 1 ~ A 3 等がトーナメント型に構成されている場合、分岐点付近にレイアウトの余裕が出やすい。本実施の形態ではこの分岐点にリニアライザを設けるため、回路面積の増大を抑えつつリニアライザを挿入することができる。従って、高価なエピ基板の使用面積を増大させないため、コストを低減することができる。また、リニアライザ付増幅器の設計を容易

50

にすることができる。なお、トランジスタをバランス動作させるために、回路パターンを非対称にしてもよい。また、インピーダンス調整のために、分岐点とアノードの間に伝送線路や抵抗等の受動素子を挿入してもよい。負電圧を印加できるなら分岐点にカソードを接続し、アノードをグランドに接続してもよい。なお、バイアス回路3は、順方向にバイアス可能なものに限らず、逆方向にバイアス可能なものでもよい。また、電源端子を備えるものではなく、抵抗やインダクタを介して接地する回路もバイアス回路3に含まれる。

#### 【0022】

実施の形態2.

図6は、本発明の実施の形態2に係るリニアライザを示す図である。ダイオード2のカソードがビアホール4を介してグランドに接続される。高周波数帯では、ビアホール4のインダクタンスを無視できなくなる。そこで、本実施の形態ではダイオード2のカソードとグランドとの間にインダクタ5を接続する。そして、ビアホール4のインダクタンスをLVHとし、インダクタ5のインダクタンスをLcとして式(4)を満たすように設計する。

$$Z_d + \omega(L_c + L_{vH}) > \frac{Z_i Z_o}{2Z_i + Z_o} \quad (4)$$

#### 【0023】

図7は、本発明の実施の形態2に係るリニアライザのAMAM特性を示す図である。ダイオードのカソードから理想グランドまでのインダクタンス成分をパラメータとしている。100μm基板厚の場合はビアホール4のインダクタンスLVHは30pH程度である。ダイオード2のカソードをビアホール4に直結した場合、通過損失は約3dBであるものの、利得向上が開始してからのダイナミックレンジが殆ど取れない特性となっている。一方、インダクタンスが150, 200pHの場合、利得向上が開始してから一定のダイナミックレンジを確保できる。そこで、例えば200pHのインダクタンスが必要なら、ビアホール4のインダクタンスは30pHであるため、残り170pHのインダクタ5を挿入すればよい。170pHは、一般的なSiC基板を用いた100μm基板厚のGaN-MMICの場合、例えば10GHz帯であれば線路幅10μm, 線路長250μm程度のマイクロストリップ線路で実現できる。なお、AMP特性は示していないが、適切な整合回路設計を行うことにより所望の特性が得られる。

#### 【0024】

実施の形態3.

図8は、本発明の実施の形態3に係るリニアライザを示す図である。ダイオード2のカソードとグランドとの間に抵抗6が接続されている。この抵抗6の抵抗値を含めて適切な整合回路設計を行うことにより所望の特性が得られる。その他の構成及び効果は実施の形態1と同様である。

#### 【0025】

実施の形態4.

図9は、本発明の実施の形態4に係るリニアライザの一部を拡大した図である。ダイオード2のアノードが分岐回路1に接続される接続点は、入力伝送線路1aの中央線の延長線から入力伝送線路1aの幅Wの3倍の範囲内で延長線からずれている。

#### 【0026】

図10は、本発明の実施の形態4に係るリニアライザのAMAM特性を示す図である。すれ量を入力伝送線路1aの幅Wと同じにした。出力端子OUT2での利得の方が出力端子OUT1に比べて約1dB高いことが分かる。

#### 【0027】

図11は本発明の実施の形態4に係るリニアライザ付増幅器を示す図である。このようなトーナメント型3段増幅器においては一般に内側の方が放熱し難い。このため、増幅器A3の利得が増幅器A2に比べて不足し、増幅器A2, A3でアンバランス動作する傾向がある。上下対称な回路のため下側の増幅器でも同様である。

10

20

30

40

50

## 【0028】

また、このアンバランスが3段目に繋がり、3段目でのアンバランス度はさらに大きくなる。これに対して、分岐回路1のパターンを非対称にすることで増幅器A2, A3への入力電力を調整し、バランス動作させることができる。しかし、非対称な分岐回路1のパターンは、時間がかかる電磁界解析をしなければ特性が分からず、開発期間が長くなるという問題がある。これに対して、本実施の形態によれば、ダイオード2の接続位置をずらすだけで入力電力を調整できるため、容易にトランジスタをバランス動作させることができる。なお、本実施の形態ではダイオード2の接続位置のみをずらしたが、それに加えて回路パターンを非対称にしてもよい。

## 【符号の説明】

10

## 【0029】

1 分岐回路、1a 入力伝送線路、1b, 1c 出力伝送線路、2 ダイオード、3 バイアス回路、4 ピアホール、5 インダクタ、6 抵抗、IN 入力端子、OUT1, OUT2 出力端子

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 米国特許第06166604(US, A)

特開2010-233055(JP, A)

特表平07-504069(JP, A)

特開平08-181544(JP, A)

特開2013-223116(JP, A)

米国特許第05282072(US, A)

米国特許第05523716(US, A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/45、3/50 - 3/52、

3/62 - 3/64、3/68 - 3/72