(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4480728号

(P4480728)

(45) 発行日 平成22年6月16日(2010.6.16)

(24) 登録日 平成22年3月26日(2010.3.26)

(51) Int.Cl.

F 1

B81C 99/00 (2010.01)

B81C 5/00

B81C 1/00 (2006.01)

B81C 1/00

H01L 21/301 (2006.01)

H01L 21/78 Q

H01L 21/78 B

H01L 21/78 T

請求項の数 15 (全 21 頁)

(21) 出願番号

特願2007-1227 (P2007-1227)

(22) 出願日

平成19年1月9日(2007.1.9)

(65) 公開番号

特開2008-12654 (P2008-12654A)

(43) 公開日

平成20年1月24日(2008.1.24)

審査請求日

平成21年5月15日(2009.5.15)

(31) 優先権主張番号

特願2006-160927 (P2006-160927)

(32) 優先日

平成18年6月9日(2006.6.9)

(33) 優先権主張国

日本国(JP)

早期審査対象出願

前置審査

(73) 特許権者

000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人

100077931

弁理士 前田 弘

(74) 代理人

100110939

弁理士 竹内 宏

(74) 代理人

100110940

弁理士 嶋田 高久

(74) 代理人

100113262

弁理士 竹内 祐二

(74) 代理人

100115059

弁理士 今江 克実

(74) 代理人

100117581

弁理士 二宮 克也

最終頁に続く

(54) 【発明の名称】MEMSマイクの製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

複数のチップを有する半導体ウェーハにおける前記各チップの所定の領域上に、振動膜を形成する工程(a)と、

前記各チップの前記振動膜上に位置する犠牲層を含む中間膜を前記半導体ウェーハ上に形成する工程(b)と、

前記中間膜上に固定膜を形成する工程(c)と、

前記各チップに貫通孔を形成する工程(d)と、

前記犠牲層を除去して前記振動膜と前記固定膜との間に空隙を設ける工程(e)と、

前記半導体ウェーハの前記固定膜が形成された面とは反対の面にダイシングテープを貼り付けた後、酸化膜又は金属膜が形成されていないスクライブレーンの切断線に沿って、前記固定膜が形成された面側から、前記固定膜が露出した状態で、前記各チップの周囲にレーザ照射を行なうことにより、前記各チップを囲む変質層を形成し、前記半導体ウェーハに外力を加えることにより前記変質層に沿って前記各チップを分離する工程(f)とを備え、

前記犠牲膜を除去して空隙を設ける工程(e)の後に、前記チップを分離する工程(f)が行なわれることを特徴とするMEMSマイクの製造方法。

## 【請求項2】

前記工程(a)において、前記振動膜はポリシリコン(PS)膜を含む層により形成されることを特徴とする請求項1に記載のMEMSマイクの製造方法。

10

20

**【請求項 3】**

前記工程 (a) において、前記振動膜はシリコンナイトライド (SiN) 膜を含む層により形成されることを特徴とする請求項 1 または 2 に記載のMEMSマイクの製造方法。

**【請求項 4】**

前記工程 (a) において、前記振動膜はTEOS膜を含む層により形成されることを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 5】**

前記工程 (a) において、前記振動膜に複数の孔を形成することを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 6】**

前記工程 (c) において、前記固定膜はポリシリコン (PS) 膜を含む層により形成されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 7】**

前記工程 (c) において、前記固定膜はシリコンナイトライド (SiN) 膜を含む層により形成されることを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 8】**

前記工程 (c) において、前記固定膜はTEOS膜を含む層により形成されることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 9】**

前記工程 (c) において、前記固定膜に複数の孔を形成することを特徴とする請求項 1 乃至 8 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 10】**

前記工程 (d) において、前記貫通孔はエッチングにより形成されることを特徴とする請求項 1 乃至 9 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 11】**

前記工程 (d) において、前記貫通孔は前記振動膜を露出するように形成されることを特徴とする請求項 1 乃至 10 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 12】**

前記工程 (d) は、前記工程 (e) の前に行われることを特徴とする請求項 1 乃至 11 のいずれか 1 項記載のMEMSマイクの製造方法。

**【請求項 13】**

前記工程 (e) において、前記半導体ウェーハに対するエッチングにより、前記犠牲層を除去することを特徴とする請求項 1 乃至 12 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 14】**

前記工程 (f) において、前記変質層を前記半導体ウェーハの少なくとも一部に形成することを特徴とする請求項 1 乃至 13 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【請求項 15】**

前記工程 (f) において、前記変質層は多結晶質層として形成されることを特徴とする請求項 1 乃至 14 のいずれか 1 項に記載のMEMSマイクの製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置の製造方法に関し、特に、ダイシングの方法に関する。

**【背景技術】****【0002】**

通常、半導体装置を製造するには、ウェーハ上にトランジスタ等の各種の素子を有する

10

20

30

40

50

多数のチップを形成した後、チップとして個片化するためにダイシングを行なう。このようにダイシングを行なうとき、ウェーハ又は素子が破損し、半導体装置製造の歩留りが低下する原因となることがある。例えば、ブレードダイシングを行なうと、チップの端の部分において欠け（チッピング）が生じる場合がある。これが半導体装置におけるトランジスタ等の各種素子が形成された領域に達すると、半導体装置の機能が破壊されることになる。

#### 【0003】

そこで、このようなダイシングに際する破損を避けるための技術が今までにも検討されてきた。

#### 【0004】

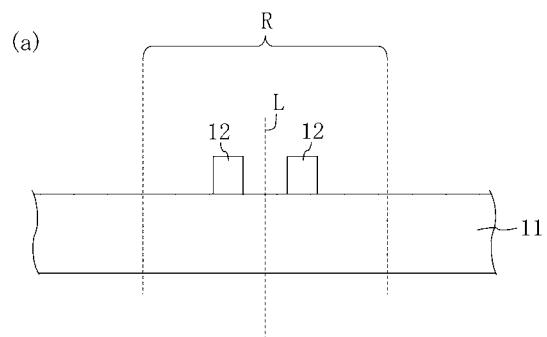

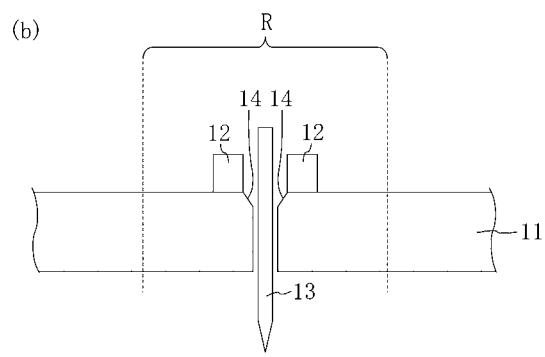

一例として、特許文献1に開示されている半導体ウェーハの切断方法を、図13（a）及び（b）を参照して説明する。

#### 【0005】

図13（a）は、半導体ウェーハ11の一部の断面を示している。特に図示はしていないが半導体ウェーハ11には各種の素子を有するチップが形成されており、スクライプ領域R中の切断線Lにおいて切断（ダイシング）されることにより個片化される。スクライプ領域Rは、チップ同士の間に設けられたダイシングのための領域である。ここで、半導体ウェーハ11上のスクライプ領域Rにおいて、切断線Lの両側には絶縁膜12が設けられている。

#### 【0006】

図13（b）には、半導体ウェーハ11をブレード13によりダイシングした際の様子が示されている。ダイシングは、二つの絶縁膜12の間に位置する切断線Lに沿って行なわれる。このとき、ウェーハ11の表面が欠けた（チッピング形状14が生じた）場合にも、チッピングは絶縁膜12によってストップされる。つまり、絶縁膜12よりも先に進むことは抑えられる。これにより、チッピングによる半導体装置製造の歩留り低下を抑制することができる。

【特許文献1】特許第3500813号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、一般的なダイシングの工程において、半導体ウェーハに形成した構造が脆弱であった場合、その部分が破壊されてしまい、その結果として製造歩留りが極めて悪くなることがある。

#### 【0008】

一般に、ブレードを用いるダイシングは、切断クズの除去等を目的として洗浄液（例えば水）を供給しながら行なわれる。このため、ダイシングの際に半導体ウェーハには水による圧力が加わる。この結果、半導体ウェーハに形成された構造に脆弱な部分が存在すると、そのような部分は水圧によって損傷を受けやすい。

#### 【0009】

特に、半導体装置が中空部分を有する場合、該中空部分を覆うような薄膜は水圧によって容易に破壊されることが考えられる。そこで、このような破壊を回避して、脆弱な部分を有する構造の半導体を実現することが課題となっている。

#### 【0010】

以上に鑑みて、本発明の目的は、中空部分を覆う薄膜のような脆弱な構造を有する半導体装置の確実な製造方法を提供することである。

#### 【課題を解決するための手段】

#### 【0011】

前記の目的を達成するため、本発明の第1の半導体装置の製造方法は、複数のチップを有する半導体ウェーハにおける各チップの所定の領域上に、振動膜を形成する工程（a）と、各チップの振動膜上に位置する犠牲層を含む中間膜を半導体ウェーハ上に形成する工

10

20

30

40

50

程( b )と、中間膜上に固定膜を形成する工程( c )と、半導体ウェーハをブレードダイシングすることにより、各チップを分離する工程( d )と、各チップに対するエッティングにより、犠牲層を除去して振動膜と固定膜との間に空隙を設ける工程( e )とを備える。

#### 【 0 0 1 2 】

本発明の半導体装置の製造方法によると、固定膜が犠牲層上に積層された状態でダイシング行なった後に犠牲層を除去するため、ダイシングの際に固定膜が破壊されるのを抑制することができる。このため、例えば振動膜と固定膜とが空隙を挟んで設けられたMEMS (Micro Electro Mechanical Systems) マイクの構造を有する半導体装置を歩留り良く製造することができる。

#### 【 0 0 1 3 】

尚、工程( d )の前に、固定膜上に保護膜を設ける工程を更に備えることが好ましい。これにより、ダイシングの際の固定膜の破壊を更に確実に抑え、半導体装置製造の歩留りを向上することができる。

#### 【 0 0 1 4 】

また、保護膜は、工程( e )において犠牲層と共に除去されることが好ましい。このようにすると、保護膜を除去するための独立した工程を設けることは不要であり、工程数の増加を抑えて半導体装置を製造することができる。

#### 【 0 0 1 5 】

次に、本発明の第2の発明の半導体装置の製造方法は、複数のチップを有する半導体ウェーハにおける各チップの所定の領域上に、振動膜を形成する工程( a )と、各チップの振動膜上に位置する犠牲層を含む中間膜を半導体ウェーハ上に形成する工程( b )と、中間膜上に固定膜を形成する工程( c )と、半導体ウェーハに対するエッティングにより、犠牲層を除去して振動膜と固定膜との間に空隙を設ける工程( d )と、半導体ウェーハをレーザダイシングすることにより、各チップを分離する工程( e )とを備える。

#### 【 0 0 1 6 】

このようにすると、レーザダイシングは洗浄液の供給無しに行なうダイシング方法であるため、犠牲層が除かれた後に空隙上に設けられている固定膜についてもダイシングの際に破壊されることはない。この結果、振動膜と固定膜とが空隙を挟んで設けられたMEMSマイクの構造を確実に製造することができる。

#### 【 0 0 1 7 】

尚、第2の半導体装置の製造方法に関し、工程( e )において、半導体ウェーハの固定膜が形成された面に表面保護テープを貼り付けた後、半導体ウェーハの他方の面からレーザダイシングを行なうことが好ましい。

#### 【 0 0 1 8 】

このようにすると、表面保護テープにより固定膜を保護してダイシングを行なうことができるため、より確実に固定膜の破壊を抑制することができる。

#### 【 0 0 1 9 】

また、工程( e )において、半導体ウェーハの固定膜が形成された面とは反対の面にダイシングテープを貼り付けた後、固定膜が形成された面からレーザダイシングを行なうことも好ましい。この場合にも、表面保護テープにより固定膜を保護してダイシングを行なうことができる。

#### 【 0 0 2 0 】

以上のように、レーザダイシングは半導体ウェーハのどちらの面から行なうことも可能である。半導体ウェーハのダイシングが行なわれる領域(スクライブレーン)において、半導体ウェーハのいずれかの面に金属膜、拡散層又は酸化膜等が存在するためにレーザが反射され、レーザダイシングが不可能になっている場合がある。しかし、半導体ウェーハのいずれの面の側からレーザを照射してダイシングを行なっても良いため、都合に合わせてレーザを照射する面を選択することができる。

#### 【 0 0 2 1 】

また、第2の半導体装置の製造方法に関し、工程( c )の後で且つ工程( d )の前に、

10

20

30

40

50

半導体ウェーハの固定膜が形成された面に表面保護テープを貼り付けた後、半導体ウェーハの他方の面を研磨する工程を更に備え、工程( d )において、半導体ウェーハの前記他方の面からレーザダイシングを行なうことが好ましい。

【 0 0 2 2 】

このようにすると、半導体ウェーハの固定膜が形成された面とは反対側の面の研磨(バックグラインド)及びダイシングの両方の工程において、表面保護テープにより固定膜を保護することができる。この結果、バックグラインド及びダイシングのために個別にテープを貼り付ける必要が無くなり、工程数を減らすことができる。

【 0 0 2 3 】

また、工程( e )は、各チップの周囲にレーザ照射を行なうことにより、各チップを囲む変質層を形成する工程と、半導体ウェーハに力を加えることにより変質層に沿って各チップを分離する工程とを備えていることが好ましい。

【 0 0 2 4 】

レーザが照射された部分の半導体ウェーハ、中間層及び固定膜において、それぞれの材料が変質して変質層が生じる。変質層は変質する前に比べて物理的強度が低下しており、半導体ウェーハに力を加えると該変質層に沿って切断される。よって、各チップを囲むようにレーザ照射を行なって変質層を設けた後に半導体ウェーハに力を加えることにより、各チップを分離することができる。レーザダイシングは、このようにして行なうことができる。

【 0 0 2 5 】

次に、本発明の第3の半導体装置の製造方法は、複数のチップを有する半導体ウェーハにおける各チップの所定の領域上に、振動膜を形成する工程( a )と、各チップの振動膜上に位置する犠牲層を含む中間膜を半導体ウェーハ上に形成する工程( b )と、中間膜上に固定膜を形成する工程( c )と、半導体ウェーハに対するエッチャリングにより、犠牲層を除去して振動膜と固定膜との間に空隙を設ける工程( d )と、工程( d )の後に、固定膜上に保護膜を設けると共に、半導体ウェーハをブレードダイシングすることにより各チップを分離する工程( e )とを備える。

【 0 0 2 6 】

本発明の第3の半導体装置の製造方法によると、保護膜によって固定膜の破壊を抑制しながら半導体ウェーハをダイシングし、振動膜と固定膜とが空隙を挟んで設けられた構造を有する半導体装置を確実に製造することができる。

【 0 0 2 7 】

尚、第3の半導体装置の製造方法において、工程( e )の後に、各チップをチップホルダーに保持して保護膜を除去する工程を更に備えることが好ましい。このようにすると、保護膜を確実に除去することができる。

【 0 0 2 8 】

また、第3の半導体装置の製造方法において、工程( e )において、半導体ウェーハの固定膜が形成された面とは反対の面にダイシングテープを貼り付けてブレードダイシングを行ない、工程( e )の後に、ダイシングテープに貼り付けられた状態のチップから表面保護膜を除去する工程を更に供えることが好ましい。

【 0 0 2 9 】

このようにすると、保護膜を確実に除去すると共に、各チップをチップホルダーに移す作業は不要となる。

【 0 0 3 0 】

次に、本発明の第4の半導体装置の製造方法は、複数のチップを有する半導体ウェーハにおける各チップの所定の領域上に、振動膜を形成する工程( a )と、各チップの振動膜上に位置する犠牲層を含む中間膜を半導体ウェーハ上に形成する工程( b )と、中間膜上に固定膜を形成する工程( c )と、固定膜、中間膜及び半導体ウェーハに、各チップを囲む溝を固定膜の側から形成する工程( d )と、溝が形成された半導体ウェーハに対するエッチャリングにより、犠牲層を除去して振動膜と固定膜との間に空隙を設ける工程( e )と、

10

20

30

40

50

工程( e )の後に、半導体ウェーハにおける溝を形成した面とは反対側の面を、溝に達するまで研磨することにより前記各チップを分離する工程( f )とを備える。

#### 【 0 0 3 1 】

第4の半導体装置の製造方法によると、まず、固定膜が犠牲層上に積層された状態において、半導体ウェーハの固定膜が形成された面から各チップを囲む溝を形成する。このとき、半導体ウェーハの他の面には達しない溝とする(ハーフカットする)ことにより、それぞれ振動膜等を含むチップが他の面の近傍においてのみ繋がった状態の半導体ウェーハを得る。犠牲層が残った状態でダイシングを行なうのであるから、この工程における固定膜の破壊は抑えられている。

#### 【 0 0 3 2 】

10

次に、このような状態の半導体ウェーハに対してエッティングを行なって犠牲層を除去した後、半導体ウェーハの他の面を研磨(バックグラインド)する。固定膜が形成された面から設けられてる溝に達するまでこのような研磨を行なうことにより、半導体ウェーハの各チップを接続していた部分が除去される。この結果、各チップが切り離され、チップ化される。このようにして、固定膜等の破壊を避けて半導体装置を製造することができる。

#### 【 0 0 3 3 】

また、工程( c )において、溝は、各チップの振動膜から所定の距離を離して形成されることが好ましい。

#### 【 0 0 3 4 】

20

犠牲層を除去するためのエッティングの際、溝の側面から半導体ウェーハがエッティングされ、製造する半導体装置の機能に影響することが考えられる。そこで、このような溝の側面のエッティングを考慮したマージンを含む所定の距離を離すように、溝を振動膜に対して配置する。これにより、溝の側面がエッティングされることによる影響を避けて半導体装置を確実に製造することができる。

#### 【発明の効果】

#### 【 0 0 3 5 】

本発明の半導体装置の製造方法によると、犠牲層上に固定膜を形成した後に犠牲層を除去することにより、空隙上に固定膜が形成された構造を有する半導体装置を製造することができる。ここで、ダイシング後に犠牲層を除去する、ダイシングをレーザにより行なう、固定膜上に保護膜を設ける、又は、ハーフカットの後にバックグラインドを行なうことにより、ダイシングの際に洗浄液の圧力によって固定膜が破壊されるのを抑え、確実に半導体装置を製造することができる。

30

#### 【発明を実施するための最良の形態】

#### 【 0 0 3 6 】

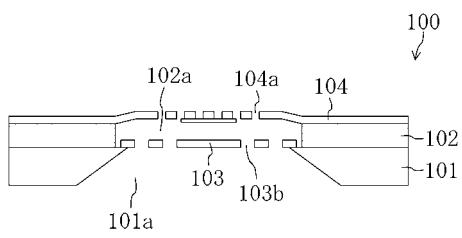

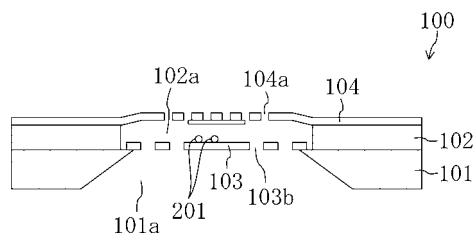

以下、MEMSマイクチップの製造を例として、本発明の実施形態を説明する。まず、MEMSマイクチップとは、図1に示す構造を有する半導体装置である。

#### 【 0 0 3 7 】

図1に示すように、MEMSマイクチップ100は、半導体基板101を用いて形成されている。半導体基板101は貫通孔101aを有すると共に、半導体基板101上には、貫通孔101a上に位置する空隙102aを有する中間膜102が設けられている。また、貫通孔101a上には該貫通孔101aを塞ぐように振動膜103が設けられている。更に、中間膜102上及び空隙102aを覆うように、固定膜104が設けられている。

40

#### 【 0 0 3 8 】

このように、空隙102aは、振動膜103と固定膜104とに挟まれている。また、空隙102a上の部分の固定膜104には音孔104aが設けられていると共に、振動膜103には孔103bが設けられている。つまり、固定膜104における音孔104aは、MEMSマイクチップ100外からの音響をMEMSマイクチップ100内に取り入れる機能を有する。また、振動膜103における孔103bは、貫通孔101a側と気圧を一致させる機能を有する。

50

## 【0039】

このような構造を有するMEMSマイクチップ100において、音孔104aを通じて導入される音波により、振動膜103が振動する。この結果、固定膜104と振動膜103との距離が変化するため、上部電極となる固定膜104と、下部電極となる振動膜103との間の容量の変化を電気信号として取り出すことができる。このようにして、音波を電気信号に変換することができる。

## 【0040】

以下に説明する個々の実施形態においては、MEMSマイクチップ100の製造方法を説明する（但し、本発明がMEMSマイクチップの製造のみに限定されるわけではない）。特に、極めて薄く且つ独立した（他の膜と積層されて補強された構造とはなっていない）部分を有するために脆弱な振動膜103及び固定膜104を形成する方法について詳しく述べる。10

## 【0041】

尚、製造されたMEMSマイクチップ100において、空隙102a内にコンタミネーションが発生している場合がある。

## 【0042】

ここで、コンタミネーションとは、例えばMEMSマイクチップ100の製造工程において生じる半導体ウェーハ101のクズ、ダイシングテープのクズ、ダイシングに用いるブレードの破片等を言う。このようなコンタミネーション201が孔103b又は音孔104aよりも小さい場合、図14に示すように、MEMSマイクチップ100の製造工程中に孔103b又は音孔104aから空隙102a内に入り込み、製造工程が完了した後にも空隙102a内に残ることがある。図14では振動膜103に付着したコンタミネーション201が示されているが、固定膜104、中間膜102の側面又は半導体ウェーハ101の側面に付着することも考えられる。20

## 【0043】

このようなコンタミネーション201が発生すると、MEMSマイクチップ100の性能が劣化する。特に、マイクとしての周波数特性が劣化して必要な品質を得ることができにくくなり、MEMSマイクチップ100製造の歩留りが低下する原因となる。

## 【0044】

尚、振動膜103及び固定膜104が脆弱であること等から、一旦発生したコンタミネーション201を取り除くのは容易ではなく、その発生を防ぐことが望ましい。30

## 【0045】

（第1の実施形態）

以下、本発明の第1の実施形態に係る半導体装置の製造方法について、図面を参照して説明する。

## 【0046】

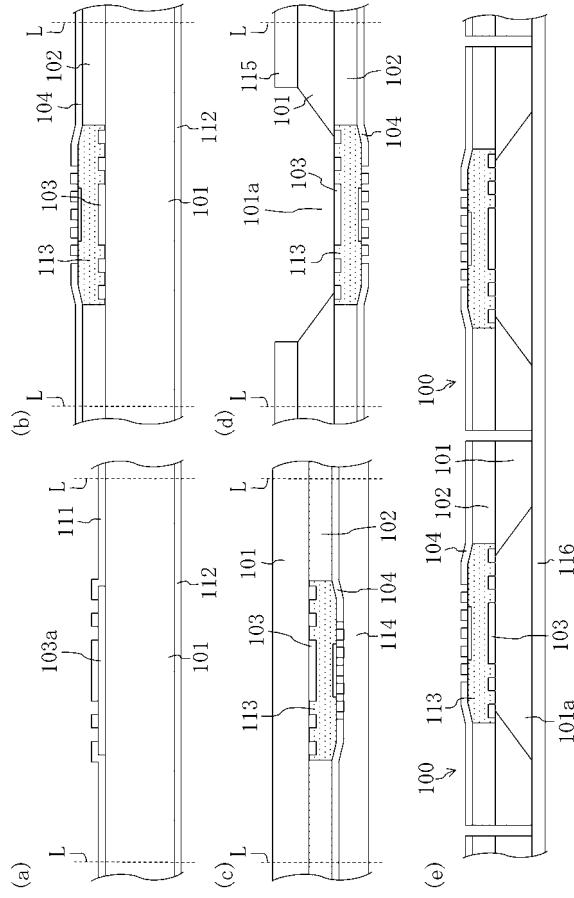

図2(a)～(g)には、本実施形態によるMEMSマイクチップ100の製造方法を示している。

## 【0047】

まず、図2(a)に示すように、半導体ウェーハ101の一方の面（以下、表面と記す）上に、振動膜103に加工するための積層材料膜103aを形成する。積層材料膜103aは、例えば、SiN膜、PS(Poly Silicon)膜TEOS(Tetraethylorthosilicate)膜及びSiN膜が下からこの順に積層した構造であってもよい。40

## 【0048】

次に、積層材料膜103aを覆うように、振動膜103の加工形状に対応したパターンを有し、例えばSiO<sub>2</sub>膜であるエッチングストッパー膜111を形成する。

## 【0049】

尚、積層材料膜103aを形成する際、半導体ウェーハ101における積層材料膜103aを形成したのとは反対側の面（以下、裏面と記す）において、例えば酸化膜112が形成される場合もある。50

**【0050】**

また、図2(a)において、後の工程でダイシングされる位置である切断線Lを示しており、積層材料膜103a一つを含む範囲が切断線Lにおけるダイシングにより一つのチップとなる。図2(a)には一つだけ示しているが、半導体ウェーハ101にはこのような各チップとなる構造を複数同時に形成する。

**【0051】**

この後、エッティングストッパー膜111をマスクとして用いてエッティングを行ない、積層材料膜103aを加工して、図2(b)に示す形状を有する振動膜103を得る。この際、例えば、SiN膜についてフッ素系ガスを用いたドライエッティングを行ない、PS膜についてはフッ酸系溶剤を用いたウェットエッティングを行なえばよい。

10

**【0052】**

次に、図2(b)に示すように、振動膜103上に犠牲層113を有する中間膜102を、半導体ウェーハ101上に形成する。更に、犠牲層113及び中間膜102の上覆うように固定膜104を形成する。

**【0053】**

ここで、犠牲層113は及び中間膜102は例えばBPSG(Boron Phosphorous Silicate Glass)により形成し、また、固定膜104は振動膜103と同一の構成を有する積層膜として形成する。つまり、本実施形態の固定膜104は、SiN膜、PS膜、TEOS膜及びSiN膜が下からこの順に積層した構造である。

**【0054】**

尚、本実施形態のMEMSマイクチップ100において、中間膜102と犠牲層113とは1つの層として一度に形成し、その後、振動膜103上の部分のみを犠牲層113として除去することにより形成している。但し、これに限るものではなく、中間膜102と犠牲層113とを別々に形成することも考えられる。この場合、材料についても異なっていても良い。

20

**【0055】**

次に、図2(c)に示すように、半導体ウェーハ101に対してバックグラインドを行なう。つまり、半導体ウェーハ101の裏面(振動膜103が形成されている面と反対側の面)を研磨し、半導体ウェーハ101の厚さを薄くする。これは、固定膜104上にBG(バックグラインド)テープ114を貼り付けて行なう。BGテープ114としては、例えば、ポリエチレン製テープにアクリル系接着剤を塗布したもの用いても良い。

30

**【0056】**

次に、図2(d)に示すように、半導体ウェーハ101の裏面に、例えばシリコン酸化膜からなるマスク115を形成し、これを用いて半導体ウェーハ101に対するエッティングを行なう。これにより、半導体ウェーハ101に裏面から貫通孔101aが形成され、振動膜103が貫通孔101aに向かって露出することになる。

**【0057】**

次に、半導体ウェーハ101を切断線Lに沿ってダイシングして各チップを分離し、チップ100aを形成する。このためには、半導体ウェーハ101の裏面にダイシングテープ116を貼り付け、ブレードを用いてダイシングする。図2(e)には、チップ100a二つ程度の範囲について、ダイシングした状態が示されている。尚、ダイシングテープ116としては、例えばポリオレフィン製テープにアクリル系接着剤を塗布したもの用いても良い。

40

**【0058】**

このようなダイシングは、切断クズの除去を目的として例えば洗浄用の水を供給しながら行なう。固定膜104は薄い膜であるが、犠牲層113上に積層されているため、供給される水の圧力を受けても容易に破壊されることはない。

**【0059】**

この後、ダイシングテープ116を剥離してチップ100aの状態でエッティング処理を行ない、犠牲層113を除去することにより空隙102aとする。これにより、図1に示

50

すMEMSマイクチップ100の構造を得ることができる。尚、このエッティングの際、エッティング液としてはHFを用いることができる。

#### 【0060】

以上のように、チップ化のためのダイシングを犠牲層113の除去の前に行なうことにより、固定膜104の破壊を抑えることができる。その後、ダイシングの後に犠牲層113を除去すると、振動膜103と固定膜104とが空隙102aを挟んで形成された構造を有する半導体装置(MEMSマイクチップ100)を歩留り良く製造することができる。

#### 【0061】

また、ダイシング工程において生じる切断クズが図14に示したようなコンタミネーション201として空隙102a内に残ることは防がれている。

#### 【0062】

つまり、ダイシングの際、半導体ウェーハ101、中間膜102、ダイシングテープ116等のクズが生じ、また、ダイシングブレードの破片がクズとして生じることもある。このようなクズは、孔103b又は音孔104aよりも小さい場合もあり、仮に犠牲層113が無かったとすると空隙102a内に入り込むことも考えられる。このようにして、図14のようにMEMSマイクチップ100の完成品においてコンタミネーション201が発生すると、装置の品質を劣化させる。

#### 【0063】

しかし、本実施形態の方法によると、ダイシングの際には犠牲層113が残されている。よって、図14に示すコンタミネーション201の発生は防がれている。結果として、MEMSマイクチップ100の品質及びその製造歩留りが向上する。

#### 【0064】

尚、以上に説明した工程においては、固定膜104の形成の後で且つ貫通孔101aの形成の前に、半導体ウェーハ101のバックグラインドを行なっている。しかし、バックグラウンドは、図2(a)に示す振動膜103形成の前に行なっておくことも可能である。この場合は、既に厚さの薄くなった半導体ウェーハ101を用いて図2(a)と同様に振動膜103の形成を行なうことになる。

#### 【0065】

更に、固定膜104の形成の後、先に貫通孔101aの形成を行ない、その後にバックグラウンドを行なってもよい。

#### 【0066】

このように、図2(a)~(e)に示したものとは異なる工程順によりMEMSマイクチップ100を製造することもできる。

#### 【0067】

##### (第1の実施形態の変形例)

次に、第1の実施形態の変形例に係る半導体装置の製造方法を説明する。本変形例では、第1の実施形態の半導体装置の製造方法と比較すると、固定膜104上に保護膜を設けることを特徴とする。これについて、図面を参照して以下に説明する。図3(a)及び(b)は、本変形例における特徴的な工程を示す図である。

#### 【0068】

まず、第1の実施形態と同様に、図2(a)~(d)に説明した工程を行なう。次に、図3(a)に示すように、固定膜104上に保護膜117を形成する。また、半導体ウェーハ101の裏面にダイシングテープ116を貼り付ける。この後、保護膜117と共に半導体ウェーハ101を切断線Lに沿ってブレードダイシングすることにより、図3(b)に示すようにチップ100aを得る。このようにすると、保護膜117により固定膜104の破壊を更に確実に抑制し、MEMSマイクチップ100の製造歩留りを向上することができる。尚、保護膜117は、アクリル等を材料として形成することができる。

#### 【0069】

この後、保護膜117を除去する。これは、ダイシングの後、保護膜117除去のため

10

20

30

40

50

の独立した工程として行なうことも可能である。この場合には、保護膜 117 の除去の後、エッティングにより犠牲層 113 を除去することにより図 1 に示す半導体装置を得ることができる。

#### 【 0070 】

また、独立した工程として保護膜 117 を除去するのに代えて、犠牲層 113 を除去するためのエッティングの際に、保護膜 117 を同時に除去するようにすることも可能である。このようにすると、工程数の増加を抑えて図 1 に示す半導体装置を得ることができる。

#### 【 0071 】

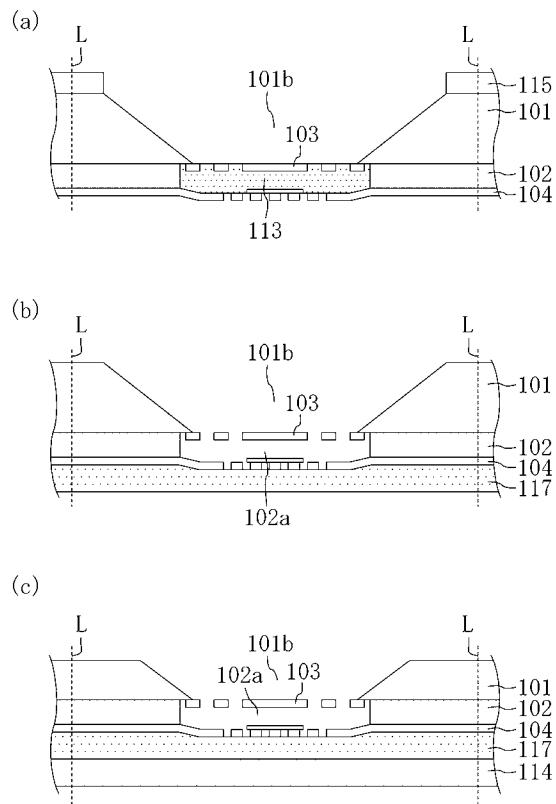

##### ( 第 2 の実施形態 )

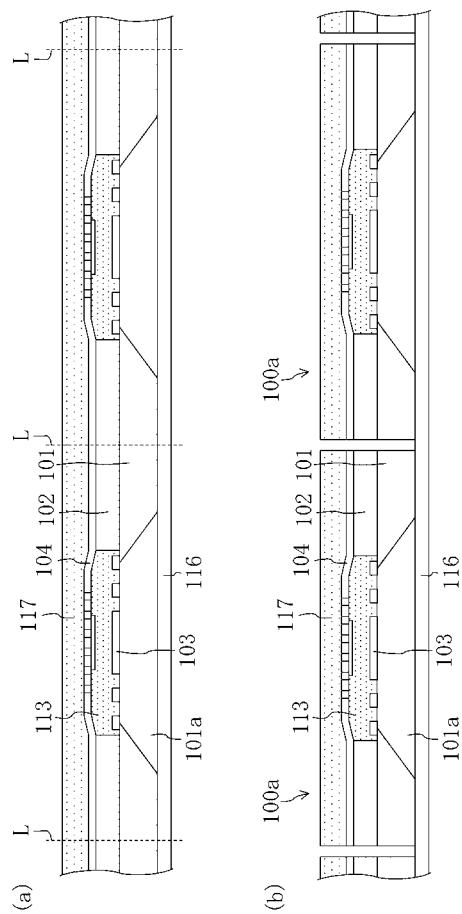

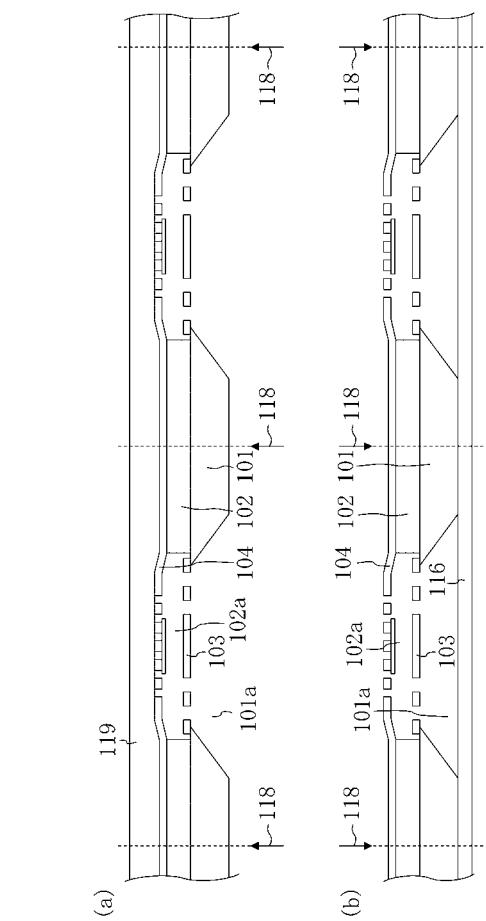

次に、本発明の第 2 の実施形態に係る半導体装置の製造方法について図面を参照して説明する。本実施形態でも、図 1 に示す MEMS マイクチップ 100 を例として説明する。また、犠牲層 113 の除去及びチップ化の工程以外については第 1 の実施形態と同様であるため、本実施形態におけるチップ化の工程について主に説明する。尚、図 4 ( a ) 及び ( b ) と、図 5 ( a ) 及び ( b ) とは、本実施形態における半導体装置の製造工程を説明する図である。

#### 【 0072 】

具体的には、まず、第 1 の実施形態と同様に、図 2 ( a ) ~ ( d ) の工程を行なう。これにより、図 2 ( d ) に示したように、各チップとなる構造を複数有する半導体ウェーハ 101 を得ることができる。

#### 【 0073 】

次に、図 4 ( a ) に示すように、半導体ウェーハ 101 に対してエッティング処理を行なうことにより、ウェーハ状態のまま犠牲層 113 を除去して空隙 102a とする。尚、図 4 ( a ) においても、後にダイシングされる位置である切断線 L を示しており、切断線 L に挟まれた範囲が後にダイシングにより一つのチップとなる。このため、図 4 ( a ) には、半導体ウェーハ 101 のうち、チップ二つ程度の範囲を示していることになる。

#### 【 0074 】

次に、図 4 ( b ) に示すように、半導体ウェーハ 101 の裏面側から切断線 L に沿ってダイシング用のレーザ 118 を照射する。これにより、レーザ 118 を照射された部分 ( 切断線 L の近傍 ) の半導体ウェーハ 101 、中間膜 102 及び固定膜 104 は変質し、物理的強度の低下した変質層 202 となる。

#### 【 0075 】

このため、続いて図 4 ( c ) に示すように半導体ウェーハ 101 の裏面にダイシング用テープを貼り付け、エキスピンドを行なうと、半導体ウェーハ 101 等がレーザ 118 を照射された位置において切断され、チップ化される。ここで、エキスピンドとは、レーザ 118 照射後の半導体ウェーハ 101 に対して面に沿った方向の力を加えるため、ダイシングテープ 116 を広げるように引くことである。図 4 ( c ) では、矢印 F のようにダイシングテープ 116 を引くことを示している。

#### 【 0076 】

以上のようにして、図 1 に示すような MEMS マイクチップ 100 を製造することができる。

#### 【 0077 】

尚、分割された個々のチップについて、周囲に変質層 202 が残されている。照射したレーザの出力が 1 ~ 10 W である場合、残されている変質層 202 の幅 K は、 1 ~ 5 μm 程度となる。

#### 【 0078 】

図 4 ( b ) 及び ( c ) において、レーザが照射された切断線 L の部分の半導体ウェーハ 101 、中間膜 102 及び固定膜 104 が全て変質層 202 となっているように示されている。しかし、より限られた範囲だけが変質層 202 となり、変質されることなく残っている部分があつても良い。図 4 ( c ) のエキスピンドによりチップ 100 が分離される程度に変質層 202 が形成されればよい。

10

20

30

40

50

## 【0079】

また、変質層202とは、代表的には多結晶質層である。つまり、本実施形態の半導体ウェーハ101として単結晶のシリコンからなるウェーハを用いることができ、この場合、レーザ照射を行なった部分の結晶構造が変化して多結晶質層である変質層202となる。

## 【0080】

単結晶のシリコンにおいては、理想的には、全ての原子が規則正しく配列してダイヤモンド格子構造を取っている。これに対して多結晶質層の場合、部分的には原子配列が規則的に配列した結晶構造が見られるが、このような部分的な結晶構造が多数集まつた構造となっており、広い領域に亘る規則正しい配列は有していない。このように、レーザ照射により、原子配列が規則的な配列を有する領域が小さくなる。10

## 【0081】

このような単結晶及び多結晶の違いは、例えば、ラマン分光法等を用いて確認することができる。

## 【0082】

このようなレーザ照射及びエキスパンドによるレーザダイシングは、洗浄水を供給することなく行なわれる。このため、空隙102a上に位置している固定膜104が、洗浄水の圧力等によって破壊されることはない。

## 【0083】

このように、ダイシング前にウェーハ状態で犠牲層113を除去する場合であっても、ダイシングをレーザダイシングとすることにより、洗浄水の圧力によって固定膜104が破壊されることを避けてダイシングを行なうことができる。このため、MEMSマイクチップ100を製造する際の歩留りを向上することができる。20

## 【0084】

尚、レーザ照射の前に、図5(a)のように、固定膜104上に表面保護テープ119を貼り付けても良い。この後、半導体ウェーハ101の裏面からレーザ118を照射する。更に、半導体ウェーハ101の裏面にダイシングテープ116を貼り付け、表面保護テープ119を剥離すると、図4(c)と同様にエキスパンドを行なうことができる。このように表面保護テープ119を用いると、ダイシングの際に固定膜104等が損傷を受けることを防ぎ、更に確実にMEMSマイクチップ100を製造することができる。更に、表面保護テープ119により、空隙102a内へのコンタミネーション201の侵入(図14を参照)を防ぐことができる。30

## 【0085】

また、半導体ウェーハ101に対するエッティング処理により犠牲層113を除去した後、図5(b)に示すように、半導体ウェーハ101の裏面にダイシングテープ116を貼り付けるようにしても良い。この場合、半導体ウェーハ101の表面側からレーザ118を照射する。この後、やはり図4(c)に示すようなエキスパンドを行ない、半導体ウェーハ101をレーザ照射による変質部分において切断し、チップ化することができる。

## 【0086】

このように、レーザ照射については、半導体ウェーハ101の表面側及び裏面側のどちらから行なっても良い。図5(a)及び(b)の場合にもレーザ照射により変質層が生じるが、その図示は省略する。40

## 【0087】

レーザ118を照射する切断線Lにおいて、レーザを入射する面に酸化膜又は金属膜等が存在すると、レーザ118が反射されることがある。このようにレーザの反射が起こる場合、レーザダイシングは困難である。しかし、前記の通り、レーザ照射は半導体ウェーハ101のどちらの面から行なうことも可能である。そのため表面及び裏面のどちらか一方について、酸化膜又は金属膜等の無い面になつていれば、レーザダイシングによるチップ化が可能である。50

**【0088】**

尚、本実施形態におけるそれぞれの構成要素について、いずれも第1の実施形態と同様の材料を用いることができる。エッチングに使用する薬液等についても、第1の実施形態と同様である。

**【0089】**

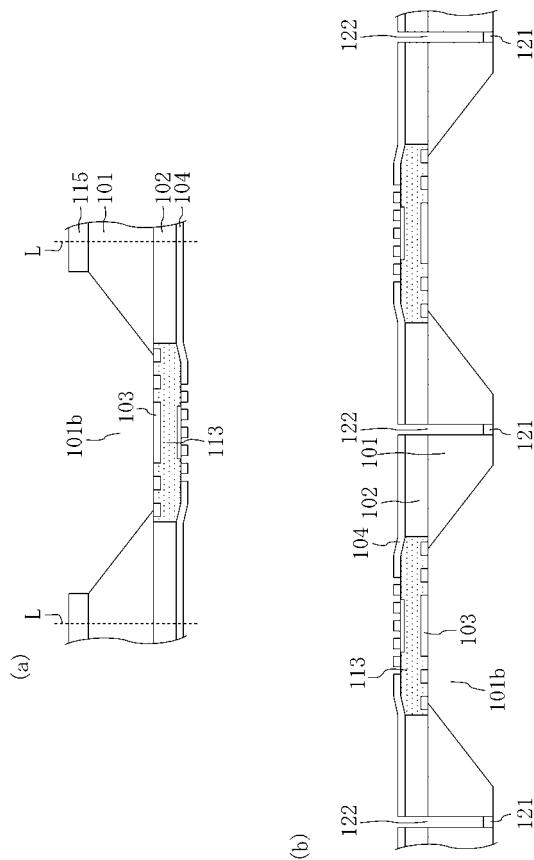

## (第2の実施形態の変形例)

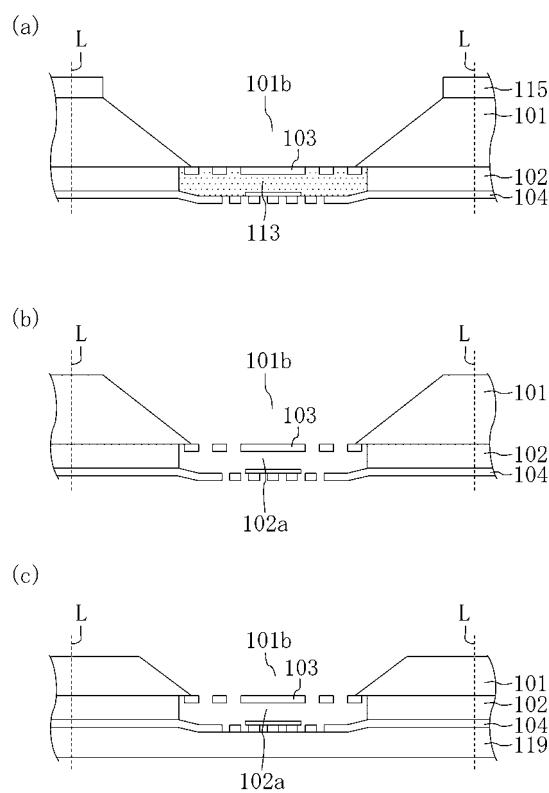

以下に、第2の実施形態の変形例を説明する。図6(a)～(c)は、本変形例に係る半導体装置の製造工程を説明する図である。本変形例では、始めに、第1の実施形態と同様に固定膜104の形成までを行ない、図2(b)に示す構造を得る。

**【0090】**

次に、半導体ウェーハ101の裏面にマスク115を形成し、半導体ウェーハ101に対して裏面からエッチングを行なう。これにより、貫通孔101bが形成され、振動膜103の裏面が貫通孔101bの側に露出する。この様子を図6(a)に示す。

**【0091】**

次に、図6(b)に示すように、エッチングにより犠牲層113を除去して空隙102aとする。続いて、図6(c)に示すように表面保護テープ119を固定膜104上に貼り付けた後、半導体ウェーハ101の裏面を研磨する(バックグラインドを行なう)。これにより、半導体ウェーハ101の厚さが薄くなる。つまり、本変形例を第2の実施形態と比較すると、犠牲層113を除去する工程と、バックグラインドを行なう工程について、順序が逆になっている。

**【0092】**

続いて、図5(a)に示すのと同様のレーザ照射を行なう。これにより、レーザ118を照射された部分が変質して物理的に脆弱になる。更に、図4(c)と同様にダイシングテープ116を貼り付けると共に表面保護テープ119を剥離した後、エキスパンドを行なう。これにより、レーザ118を照射部分において半導体ウェーハ101、中間膜102及び固定膜104が切断され、振動膜103上に空隙102aを挟んで固定膜104が形成された構造を含む個々のチップを得ることができる。

**【0093】**

本変形例によると、表面保護テープ119を用いてバックグラインド及びレーザ照射の二つの工程を行なうことができる。つまり、第2の実施形態の場合のようにバックグラインドに用いたBGテープ114を剥がした後、表面保護テープ119を用いてレーザ照射を行なう場合に比べ、使用するテープの数を減らすことができる。また、テープの貼り付け及び剥離の工程についても減らすことができる。この結果、製造工程の簡略化及びコスト低減が可能である。

**【0094】**

## (第3の実施形態)

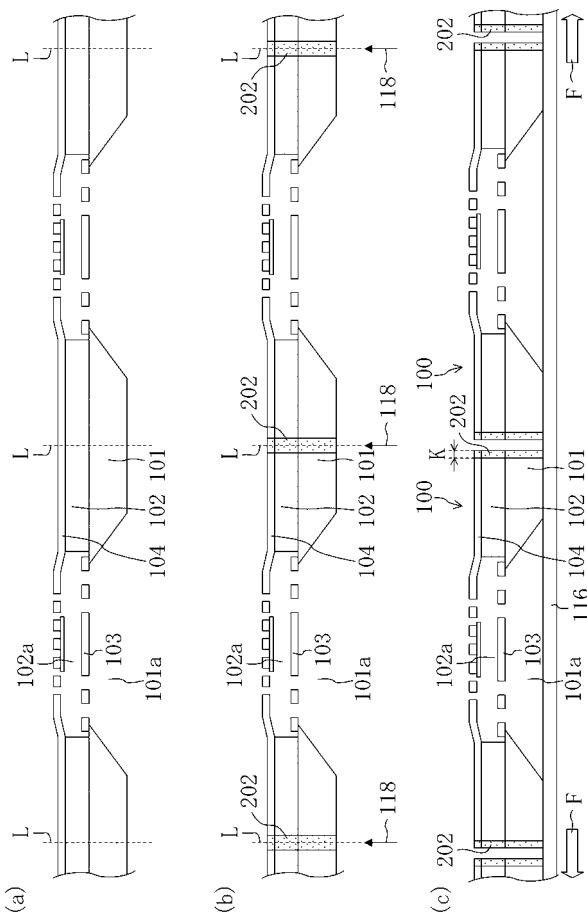

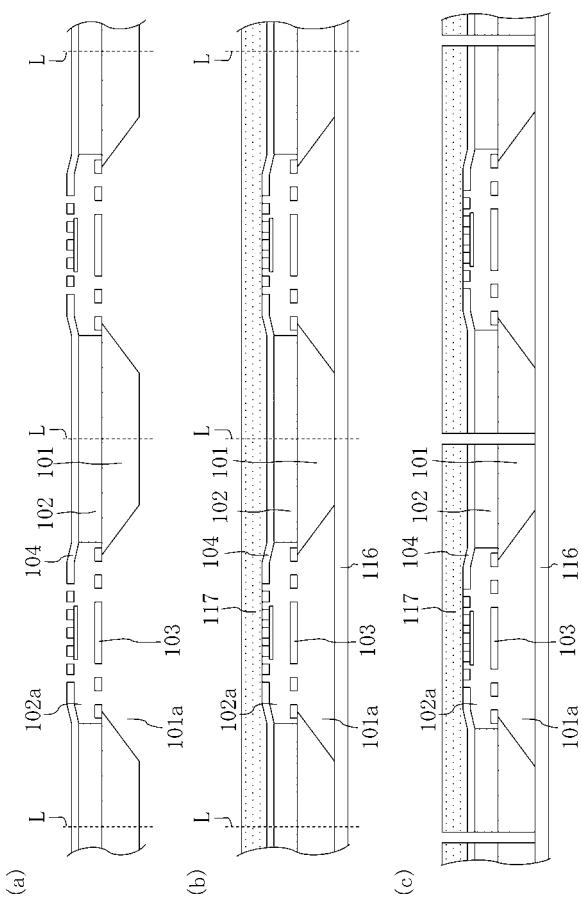

次に、本発明の第3の実施形態に係る半導体装置の製造方法について図面を参照して説明する。本実施形態でも、図1に示すMEMSマイクチップ100を例として説明する。また、犠牲層113の除去及びチップ化の工程以外については第1の実施形態と同様であるため、主として本実施形態におけるチップ化の工程について説明する。尚、図7(a)～(c)と、図8(a)及び(b)とは、本実施形態に係る半導体装置の製造方法を説明する図である。

**【0095】**

具体的には、まず、第1の実施形態と同様に、図2(a)～(d)の工程を行なう。これにより、図2(d)に示したように、振動膜103上に犠牲層113を介して固定膜104が形成された構造を複数有する半導体ウェーハ101を得ることができる。

**【0096】**

次に、図7(a)に示すように、半導体ウェーハ101に対してエッチング処理を行なうことにより、ウェーハ状態のまま犠牲層113を除去して空隙102aとする。尚、図7(a)においても、後にダイシングされる位置である切断線Lを示している。ここでも

10

20

30

40

50

、ダイシングによりチップとなる範囲が二つ程度示されている。

#### 【0097】

次に、図7(b)に示すように、固定膜104上に、保護膜117を形成する。これは、例えば、アクリル等を材料として形成すればよい。更に、半導体ウェーハ101の裏面に、ダイシングテープ116を貼り付ける。

#### 【0098】

続いて、図7(c)に示すように、保護膜117と共に半導体ウェーハ101をブレードダイシングする。このとき、固定膜104上に保護膜117が形成されていることにより、ダイシングに伴う洗浄水の圧力によって固定膜104が破壊されることは抑えられている。

10

#### 【0099】

このようにして、洗浄水の供給を伴うブレードダイシングを用いる場合であっても、保護膜117により固定膜104が破壊されることを抑制しながらダイシングを行ない、チップを得ることができる。

#### 【0100】

このようなダイシングの際、保護膜117が形成されていることにより、図14に示すような空隙102a内におけるコンタミネーション201の発生は防がれている。

#### 【0101】

この後、保護膜117を除去すると、図1と同様のMEMSマイクチップ100を得ることができる。保護膜117の除去のためには、例えば、図8(a)のようにダイシングされたチップをダイシングテープ116から外してチップホルダー120に移し、その後IPA(イソプロピルアルコール)等による洗浄等を行なえばよい。このようにすると、より確実な洗浄を行なうことができる。

20

#### 【0102】

また、保護膜117を除去するための別の方法としては、図8(b)のように、ダイシングテープ116に貼り付けられた状態のままのチップに対してIPA洗浄を行なうことでもできる。この場合、チップをチップホルダーに移す作業が不要であるため、より簡便な工程となる利点がある。

#### 【0103】

以上のようにして、振動膜103上に空隙102aを介して固定膜104が形成された構造を有する半導体装置、具体的にはMEMSマイクチップ100を歩留り良く製造することができる。更に、コンタミネーションの発生が防止されることによる品質及び歩留りの向上も実現する。

30

#### 【0104】

尚、以上に説明した工程では、固定膜104を形成した後にバックグラウンド、その次に貫通孔101aの形成という順序となっている。しかし、第1の実施形態の場合と同様、バックグラウンドは、振動膜103を形成する前に行なっても良い。

#### 【0105】

また、バックグラウンドは、保護膜117の形成後で且つダイシングの前に行なうことでもできる。図9(a)～(c)は、このような場合の工程を説明する図である。

40

#### 【0106】

つまり、図2(b)の構造を形成した後、図9(a)に示すように、半導体ウェーハ101の裏面にマスク115を設けた後、これをマスクとするエッチングにより貫通孔101bを形成する。

#### 【0107】

次に、図9(b)に示すように、固定膜104上に保護膜117を形成する。続いて、保護膜117上にBGテープ114を貼り付け、半導体ウェーハ101のバックグラウンドを行なう。これにより、図9(c)に示すように、半導体ウェーハ101の厚さを裏面から薄くする。続いて、BGテープ114を剥がした後、図7(b)及び(c)と同様に、ダイシングテープ116を貼り付けてブレードダイシングを行なう。保護膜117の除

50

去についても、先に説明した場合と同様である。

**【0108】**

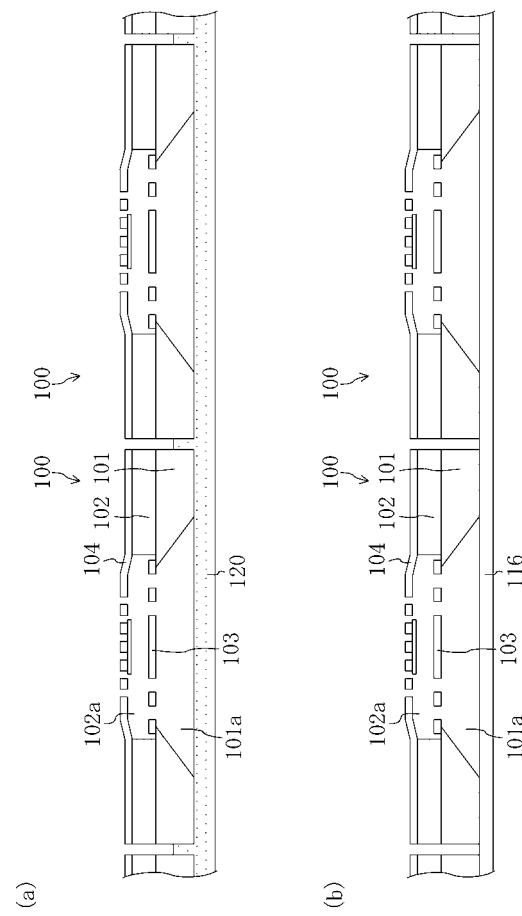

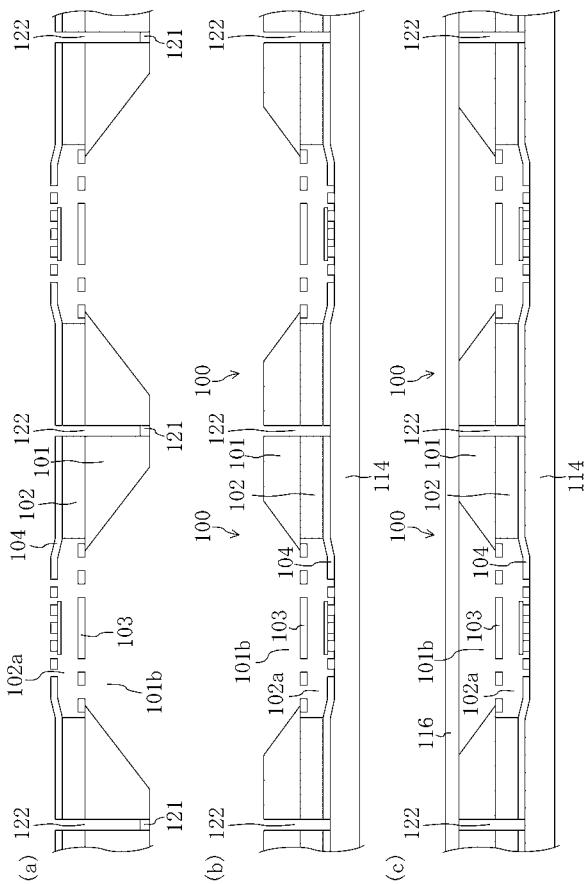

(第4の実施形態)

次に、本発明の第4の実施形態に係る半導体装置の製造方法について、図面を参照して説明する。図10(a)及び(b)と、図11(a)～(c)とは、本実施形態における半導体装置の製造方法を説明する図である。

**【0109】**

本実施形態でも、図1に示すMEMSマイクチップ100を例として説明する。また、犠牲層113の除去及びチップ化の工程以外については第1の実施形態と同様であるため、本実施形態におけるチップ化の工程について主に説明する。

10

**【0110】**

まず、第1の実施形態と同様にして固定膜104の形成までを行ない、図2(b)に示す構造を得る。つまり、半導体ウェーハ101上に振動膜103が形成され、その上に犠牲層113を介して固定膜104が形成された構造である。この時点では、バックグラインドは行なわれていない。

**【0111】**

次に、図10(a)に示すように、半導体ウェーハ101の裏面(振動膜103が形成されているのと反対側の面)にマスク115を形成し、半導体ウェーハ101に対して裏面からエッチングを行なう。これにより、貫通孔101bが形成され、振動膜103の裏面が貫通孔101bの側に露出する。

20

**【0112】**

次に、半導体ウェーハ101の表面からブレードダイシングを行なう。但し、図10(b)に示すように、半導体ウェーハ101の裏面付近において、半導体ウェーハ101の一部を薄い接続部121として残し、表面から溝122を設けるようにブレードダイシングを行なう。この結果、半導体ウェーハ101における各チップとなるべき領域が、半導体ウェーハ101を薄く残した部分である接続部121によって繋がった状態となる。

**【0113】**

このようなブレードダイシングの際、固定膜104は犠牲層113上に積層されているため、洗浄水の圧力によって破壊されることは避けられている。また、犠牲層113が存在するため、ダイシングの際に発生するクズにより図14に示すようなコンタミネーション201が残ることは防がれている。

30

**【0114】**

次に、図11(a)に示すように、溝122の形成された半導体ウェーハ101に対するエッチング処理により、犠牲層113を除去して空隙102aとする。

**【0115】**

続いて、図11(b)に示すように、固定膜104上にBGテープ114を貼り付けた後、半導体ウェーハ101の裏面を研磨する。このようなバックグラインドは、少なくとも、接続部121を削り取って溝122に達するまで行なう。これにより、接続部121によって互いに接続されていた個々のチップとなる領域が切り離され、図1に示すのと同じMEMSマイクチップ100を形成することができる。

40

**【0116】**

この後、図11(c)に示すように、個々のチップの裏面に接するようにダイシングテープ116を貼り付ける。更に、BGテープ114を剥離すると、ダイシングテープ116に対する転写を行なうことができる。

**【0117】**

以上のように、それぞれ振動膜103及び固定膜104を含むチップとなる領域を囲むように、ダイシングによって溝122を半導体ウェーハ101の表面から形成した後、犠牲層113を除去し、更にその後、半導体ウェーハ101の裏面からバックグラインドを行なう。このような方法によると、固定膜104が破壊されるのを抑制しながら、MEMSマイクチップ100のような半導体装置を製造することができる。また、ダイシング工

50

程におけるコンタミネーションの発生を防ぐことにより、品質と製造歩留りの向上とを実現している。

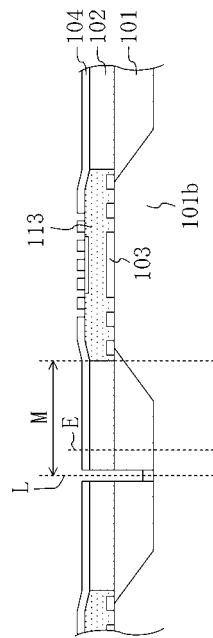

**【0118】**

尚、犠牲層 113 を除去するためのエッチングを行なう際、溝 122 の側面についてもエッチングされ、溝 122 の幅が広くなることがある。例えば、図 12 に示すように、切断線 L から側面侵食位置 E までエッチングされることがある。このようなことが起こると、製造される半導体装置（MEMS マイクチップ 100）の機能に影響するおそれがある。

**【0119】**

そこで、例えば図 12 に示すように、切断線 L から後に空隙 102a となる犠牲層 113 までの距離 M について、エッチング処理により溝 122 の側面の側面がエッチングされる量を予め考慮してマージンを含めた距離としておく。これにより、例えば側面侵食位置 E まで溝 122 の側面がエッチングされた場合にも、製造される半導体装置の機能に影響が及ぶのを避けることができる。

**【0120】**

尚、以上のいずれの実施形態においても、記載した各構成要素の材料等はいずれも例示するものであり、特に限定されない。

**【産業上の利用可能性】**

**【0121】**

本発明に係る半導体装置の製造方法によると、脆弱な構造である部分がダイシングの際に破壊されるのを避けると共に、コンタミネーションを避けて半導体ウェーハのチップ化を行なうことができ、特に、MEMS マイクチップ等の製造に有用である。

**【図面の簡単な説明】**

**【0122】**

【図 1】図 1 は、本発明の各実施形態において形成する半導体装置（MEMS マイクチップ 100）の構造を示す図である。

【図 2】図 2 (a) ~ (e) は、本発明の第 1 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 3】図 3 (a) 及び (b) は、本発明の第 1 の実施形態の変形例に係る半導体装置の製造方法を説明する図である。

【図 4】図 4 (a) ~ (c) は、本発明の第 2 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 5】図 5 (a) 及び (b) は、図 4 (a) ~ (c) に引き続き、本発明の第 2 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 6】図 6 (a) ~ (c) は、本発明の第 2 の実施形態の変形例に係る半導体装置の製造方法を説明する図である。

【図 7】図 7 (a) ~ (c) は、本発明の第 3 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 8】図 8 (a) 及び (b) は、図 7 (a) ~ (c) に引き続き、本発明の第 3 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 9】図 9 (a) ~ (c) は、本発明の第 3 の実施形態に係る半導体装置の製造方法の別の工程を説明する図である。

【図 10】図 10 (a) 及び (b) は、本発明の第 4 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 11】図 11 は、図 10 (a) 及び (b) に引き続き、本発明の第 4 の実施形態に係る半導体装置の製造方法を説明する図である。

【図 12】図 12 は、本発明の第 4 の実施形態に係る半導体装置の製造方法において、切断線 L と犠牲層 113 との距離 M について説明するための図である。

【図 13】図 13 (a) 及び (b) は、ダイシングに関する従来技術を説明するための図である。

10

20

30

40

50

【図14】図14は、MEMSマイクチップ100の空隙102a内に生じる場合があり、本発明において抑制しているコンタミネーション201について説明する図である。

【符号の説明】

【0123】

|      |             |    |

|------|-------------|----|

| 100  | MEMSマイクチップ  |    |

| 100a | チップ         |    |

| 101  | 半導体ウェーハ     |    |

| 102  | 中間膜         |    |

| 102a | 空隙          | 10 |

| 102b | 貫通孔         |    |

| 103  | 振動膜         |    |

| 103a | 積層材料膜       |    |

| 104  | 固定膜         |    |

| 104b | 孔           |    |

| 111  | エッチングストッパー膜 |    |

| 112  | 酸化膜         |    |

| 113  | 犠牲層         |    |

| 114  | BGテープ       |    |

| 115  | マスク         |    |

| 116  | ダイシングテープ    | 20 |

| 117  | 保護膜         |    |

| 118  | レーザ         |    |

| 119  | 表面保護テープ     |    |

| 120  | チップホルダー     |    |

| 121  | 接続部         |    |

| 122  | 溝           |    |

| 201  | コンタミネーション   |    |

| 202  | 変質層         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 内海 勝喜

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 饗川 隆博

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 松浦 正美

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 松島 芳宏

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 馬場 進吾

(56)参考文献 国際公開第2005/083764 (WO, A1)

特開2006-062002 (JP, A)

特開2005-191208 (JP, A)

特開2005-340423 (JP, A)

特開2006-135355 (JP, A)

国際公開第2005/086534 (WO, A1)

特開2006-148175 (JP, A)

特開2005-166728 (JP, A)

特開2006-088268 (JP, A)

特開2005-268752 (JP, A)

特開2006-74025 (JP, A)

特開2006-121465 (JP, A)

特開2006-67547 (JP, A)

(58)調査した分野(Int.Cl., DB名)

B81B 1/00-7/04

B81C 1/00-5/00

H01L 21/78-21/80

H04R 19/00、19/01、19/02、19/04