(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6729523号

(P6729523)

(45) 発行日 令和2年7月22日(2020.7.22)

(24) 登録日 令和2年7月6日(2020.7.6)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>H01L 29/78</b> | <b>(2006.01)</b> | H01L 29/78 | 652H |

| <b>H01L 29/06</b> | <b>(2006.01)</b> | H01L 29/78 | 653A |

| <b>H01L 29/12</b> | <b>(2006.01)</b> | H01L 29/78 | 652P |

|                   |                  | H01L 29/78 | 652N |

|                   |                  | H01L 29/78 | 652T |

請求項の数 10 (全 18 頁) 最終頁に続く

(21) 出願番号

特願2017-166882 (P2017-166882)

(22) 出願日

平成29年8月31日(2017.8.31)

(65) 公開番号

特開2019-46908 (P2019-46908A)

(43) 公開日

平成31年3月22日(2019.3.22)

審査請求日

令和1年10月15日(2019.10.15)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(73) 特許権者 000003207

トヨタ自動車株式会社

愛知県豊田市トヨタ町1番地

(73) 特許権者 000003609

株式会社豊田中央研究所

愛知県長久手市横道41番地の1

(74) 代理人 110001128

特許業務法人ゆうあい特許事務所

(72) 発明者 箕谷 周平

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

トレンチゲート構造を有する炭化珪素半導体装置であって、炭化珪素からなる第1導電型または第2導電型の基板(11)と、前記基板の表面上に形成され、前記基板よりも低不純物濃度とされた第1導電型の第1不純物領域(12)と、

前記第1不純物領域の上に形成された第2導電型の炭化珪素からなるベース領域(18)と、

前記ベース領域の表層部に形成され、前記第1不純物領域よりも高不純物濃度とされた第1導電型の炭化珪素からなる第2不純物領域(19)と、

前記第2不純物領域の表面から前記ベース領域よりも深くまで形成され、一方向を長手方向として形成されたトレンチ(21)の内壁面に形成されたゲート絶縁膜(22)と、前記トレンチ内において、前記ゲート絶縁膜の上に形成されたゲート電極(23)と、を有するトレンチゲート構造と、

前記第2不純物領域に電気的に接続されると共に前記ベース領域に電気的に接続される第1電極(24)と、

前記基板の裏面側に形成され、前記基板と電気的に接続される第2電極(26)と、を備え、

前記第1不純物領域と前記ベース領域との間に形成され、前記第1不純物領域よりも高不純物濃度とされた第1導電型の炭化珪素からなる第1電流分散層(13)と、

10

20

前記第1電流分散層内に形成され、前記第1電流分散層より浅くされると共に一方向を長手方向として延設された第2導電型の炭化珪素からなる複数の第1ディープ層(14)と、

前記第1電流分散層と前記ベース領域との間に形成され、前記トレンチの底部が位置し、第1導電型の炭化珪素からなる第2電流分散層(15)と、

前記第1電流分散層と前記ベース領域との間に形成され、前記ベース領域と繋がると共に前記第1ディープ層と繋がり、かつ前記トレンチから離れて形成された第2導電型の炭化珪素からなる第2ディープ層(17)と、を有し、

前記複数の第1ディープ層は、前記トレンチの長手方向と交差する方向に延設されており、

前記第2ディープ層は、前記第1ディープ層の延設方向と交差する方向に延設されている炭化珪素半導体装置。

#### 【請求項2】

前記複数の第1ディープ層は、隣合う前記第1ディープ層同士が複数箇所で繋がっている請求項1に記載の炭化珪素半導体装置。

#### 【請求項3】

前記第2電流分散層は、前記第1不純物領域よりも高不純物濃度とされている請求項1または2に記載の炭化珪素半導体装置。

#### 【請求項4】

前記第1電流分散層は、当該第1電流分散層の不純物濃度を $y [cm^{-3}]$ とし、隣合う前記第1ディープ層の間に位置する部分における最も狭い部分の長さを $x [\mu m]$ とすると、 $y > 2 \times 10^{16} / x^{1.728}$ とされている請求項1ないし3のいずれか1つに記載の炭化珪素半導体装置。

#### 【請求項5】

前記第1電流分散層は、当該第1電流分散層の不純物濃度を $y [cm^{-3}]$ とし、隣合う前記第1ディープ層の間に位置する部分における最も狭い部分の長さを $x [\mu m]$ とすると、 $y < -2 \times 10^{17} x + 3 \times 10^{17}$ とされている請求項1ないし4のいずれか1つに記載の炭化珪素半導体装置。

#### 【請求項6】

前記トレンチゲート構造が配置されるセル領域(1)と、前記セル領域を囲む外周領域(2)とを有し、

前記第1電流分散層は、前記セル領域のみに形成され、

前記外周領域には、第2導電型の炭化珪素からなるガードリング(27)が形成されている請求項1ないし5のいずれか1つに記載の炭化珪素半導体装置。

#### 【請求項7】

前記トレンチは、<11-20>方向が前記長手方向とされている請求項1ないし6のいずれか1つに記載の炭化珪素半導体装置。

#### 【請求項8】

トレンチゲート構造を有する炭化珪素半導体装置の製造方法であって、

炭化珪素からなる第1導電型または第2導電型の基板(11)を用意することと、

前記基板の表面上に、前記基板よりも低不純物濃度とされた第1導電型の炭化珪素からなる第1不純物領域(12)を形成することと、

前記第1不純物領域上に、前記第1不純物領域よりも高不純物濃度とされた炭化珪素からなる第1導電型の第1電流分散層(13)を形成することと、

前記第1電流分散層にイオン注入を行って熱処理を行うことにより、前記第1電流分散層内に、前記第1電流分散層より浅くされると共に一方向を長手方向とする第2導電型の炭化珪素からなる複数の第1ディープ層(14)を形成することと、

前記第1電流分散層上に、第1導電型の炭化珪素からなる第2電流分散層(15)を形成することと、

前記第1電流分散層上に、前記第1ディープ層と繋がる第2導電型の炭化珪素からなる

10

20

30

40

50

第2ディープ層(17)を形成することと、

前記第2電流分散層および前記第2ディープ層上に、第2導電型の炭化珪素からなるベース領域(18)を形成することと、

前記ベース領域の表層部に、前記第1不純物領域よりも高不純物濃度とされた第1導電型の第2不純物領域(19)を形成することと、

前記第2不純物領域の表面から前記ベース領域を貫通し、かつ底面が前記第2電流分散層内に位置すると共に前記第2ディープ層と離れるように、一方向を長手方向とするトレチ(21)を形成することと、

前記トレチの内壁面にゲート絶縁膜(22)を形成することと、

前記トレチ内において、前記ゲート絶縁膜の上にゲート電極(23)を形成することと、10

前記第2不純物領域および前記ベース領域と電気的に接続される第1電極(24)を形成することと、

前記基板の裏面側に、前記基板と電気的に接続される第2電極(26)を形成することと、を行い、

前記第1電流分散層を形成することでは、前記第1不純物領域にイオン注入を行って熱処理を行うことで前記第1電流分散層を形成し、

前記複数の第1ディープ層を形成することでは、前記トレチの長手方向と交差する方向に前記複数の第1ディープ層を形成し、

前記第2ディープ層を形成することでは、前記第1ディープ層の延設方向と交差する方向に前記第2ディープ層を形成する炭化珪素半導体装置の製造方法。20

#### 【請求項9】

前記基板を用意することでは、セル領域と、前記セル領域を囲む外周領域とを構成可能な前記基板を用意し、

前記第1電流分散層を形成することでは、前記セル領域のみに前記第1電流分散層を形成し、

前記外周領域に、前記セル領域を囲む第1導電型のガードリング(27)を形成する請求項8に記載の炭化珪素半導体装置の製造方法。

#### 【請求項10】

前記第2電流分散層を形成することでは、エピタキシャル成長で前記第2電流分散層を形成し、30

前記ベース領域を形成することでは、エピタキシャル成長で前記ベース領域を形成する請求項8または9に記載の炭化珪素半導体装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、本発明は、トレチゲート構造を有する炭化珪素(以下、SiCという)半導体装置およびその製造方法に関するものである。

##### 【背景技術】

##### 【0002】

従来より、例えば、SiCからなる基板を用いて構成されたSiC半導体装置が提案されている(例えば、特許文献1参照)。すなわち、このSiC半導体装置では、基板上にn型のドリフト層が形成されている。また、ドリフト層の表層部にp型のベース領域が形成され、ベース領域の表層部にn<sup>+</sup>型のソース領域が形成されている。そして、ソース領域およびベース領域を貫通してドリフト層に達するトレチが一方向に延設され、当該トレチの壁面にゲート絶縁膜を介してゲート電極が形成されることでトレチゲート構造が構成されている。また、ベース領域の下方には、トレチの延設方向と交差する方向に沿って複数のp型のディープ層がストライプ状に形成されている。40

##### 【0003】

これによれば、ディープ層とドリフト層との間に構成される空乏層により、高電界がゲ50

ート絶縁膜側に入り難くなるようにできる。このため、このようなSiC半導体装置では、ゲート絶縁膜が破壊されることを抑制できる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2012-169386号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記SiC半導体装置では、ゲート絶縁膜が破壊されることを抑制できるものの、ディープ層とドリフト層との間に構成される空乏層によって電流経路が狭くなり易い。このため、上記SiC半導体装置では、オン抵抗が高くなり易いという問題がある。

【0006】

本発明は上記点に鑑み、ゲート絶縁膜が破壊されることを抑制しつつ、オン抵抗を低減できるSiC半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための請求項1では、トレンチゲート構造を有するSiC半導体装置であって、SiCからなる第1導電型または第2導電型の基板(11)と、基板の表面上に形成され、基板よりも低不純物濃度とされた第1導電型のSiCからなる第1不純物領域(12)と、第1不純物領域の上に形成された第2導電型のSiCからなるベース領域(18)と、ベース領域の表層部に形成され、第1不純物領域よりも高不純物濃度とされた第1導電型のSiCからなる第2不純物領域(19)と、第2不純物領域の表面からベース領域よりも深くまで形成され、一方向を長手方向として形成されたトレンチ(21)の内壁面に形成されたゲート絶縁膜(22)と、トレンチ内において、ゲート絶縁膜の上に形成されたゲート電極(23)と、を有するトレンチゲート構造と、第2不純物領域に電気的に接続されると共にベース領域に電気的に接続される第1電極(24)と、基板の裏面側に形成され、基板と電気的に接続される第2電極(26)と、を備え、第1不純物領域とベース領域との間に形成され、第1不純物領域よりも高不純物濃度とされた第1導電型のSiCからなる第1電流分散層(13)と、第1電流分散層内に形成され、第1電流分散層より浅くされると共に一方向を長手方向として延設された第2導電型のSiCからなる複数の第1ディープ層(14)と、第1電流分散層とベース領域との間に形成され、トレンチの底部が位置し、第1導電型のSiCからなる第2電流分散層(15)と、第1電流分散層とベース領域との間に形成され、ベース領域と繋がると共に第1ディープ層と繋がり、かつトレンチから離れて形成された第2導電型のSiCからなる第2ディープ層(17)と、を有し、複数の第1ディープ層は、トレンチの長手方向と交差する方向に延設されており、第2ディープ層は、第1ディープ層の延設方向と交差する方向に延設されている。

【0008】

これによれば、トレンチよりも深い位置に、第1不純物領域よりも高不純物濃度とされた第1電流分散層と、当該第1電流分散層内に形成された第1ディープ層が配置されている。このため、ゲート絶縁膜に高電界が印加されることを抑制でき、ゲート絶縁膜が破壊されることを抑制できる。

【0009】

また、第1電流分散層は、第1不純物領域より高不純物濃度とされている。このため、第1不純物領域と接するようにディープ層が形成された従来のSiC半導体装置と比較して、第1ディープ層から空乏層が伸びることが抑制され、電流経路が狭くなることが抑制される。したがって、オン抵抗の低減を図ることができる。

【0010】

10

20

30

40

50

そして、第1ディープ層は、第1電流分散層内に形成されている。つまり、第1ディープ層は、第1ディープ層の底部と第1不純物領域との間に第1電流分散層が位置するよう<sup>10</sup>に形成されている。このため、第1ディープ層から延びる空乏層が第1不純物領域側に大きく延び、オン抵抗が増加することを抑制できる。

#### 【0011】

さらに、第2ディープ層は、トレンチと離れた位置に形成されている。このため、第2ディープ層がトレンチと接している場合と比較して、ベース領域を通過したキャリア（例えば、電子）が第2電流分散層に流れる際、第2電流分散層へと流れる経路が狭くなることを抑制できる。したがって、ベース領域と第1ディープ層とを繋ぐ第2ディープ層により、オン抵抗が増加してしまうことを抑制できる。<sup>20</sup>

#### 【0012】

また、請求項8では、トレンチゲート構造を有するSiC半導体装置の製造方法であつて、SiCからなる第1導電型または第2導電型の基板（11）を用意することと、基板の表面上に、基板よりも低不純物濃度とされた第1導電型のSiCからなる第1不純物領域（12）を形成することと、第1不純物領域上に、第1不純物領域よりも高不純物濃度とされたSiCからなる第1導電型の第1電流分散層（13）を形成することと、第1電流分散層にイオン注入を行って熱処理を行うことにより、第1電流分散層内に、第1電流分散層より浅くされると共に一方向を長手方向とする第2導電型のSiCからなる複数の第1ディープ層（14）を形成することと、第1電流分散層上に、第1導電型のSiCからなる第2電流分散層（15）を形成することと、第1電流分散層上に、第1ディープ層と繋がる第2導電型のSiCからなる第2ディープ層（17）を形成することと、第2電流分散層および第2ディープ層上に、第2導電型のSiCからなるベース領域（18）を形成することと、ベース領域の表層部に、第1不純物領域よりも高不純物濃度とされた第1導電型の第2不純物領域（19）を形成することと、第2不純物領域の表面からベース領域を貫通し、かつ底面が第2電流分散層内に位置すると共に第2ディープ層と離れるように、一方向を長手方向とするトレンチ（21）を形成することと、トレンチの内壁面にゲート絶縁膜（22）を形成することと、トレンチ内において、ゲート絶縁膜の上にゲート電極（23）を形成することと、第2不純物領域およびベース領域と電気的に接続される第1電極（24）を形成することと、基板の裏面側に、基板と電気的に接続される第2電極（26）を形成することと、を行い、第1電流分散層を形成することでは、第1不純物領域にイオン注入を行って熱処理を行うことで第1電流分散層を形成し、複数の第1ディープ層を形成することでは、トレンチの長手方向と交差する方向に複数の第1ディープ層を形成し、第2ディープ層を形成することでは、第1ディープ層の延設方向と交差する方向に第2ディープ層を形成する。<sup>30</sup>

#### 【0013】

これによれば、ゲート絶縁膜に高電界が印加されることを抑制しつつ、オン抵抗の低減を図ることのできる半導体装置を製造できる。また、第1電流分散層をイオン注入および熱処理によって形成している。このため、第1不純物領域上にエピタキシャル成長によって第1電流分散層を形成する場合と比較して、第1電流分散層の不純物濃度の制御が容易になり、特性がばらつくことを抑制できる。<sup>40</sup>

#### 【0014】

なお、上記および特許請求の範囲における括弧内の符号は、特許請求の範囲に記載された用語と後述の実施形態に記載される当該用語を例示する具体物等との対応関係を示すものである。

#### 【図面の簡単な説明】

#### 【0015】

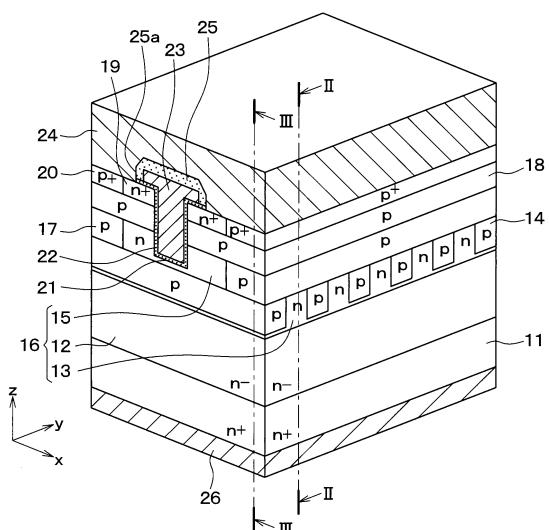

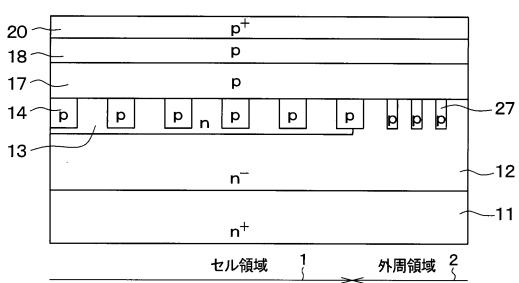

【図1】第1実施形態におけるSiC半導体装置の斜視断面図である。

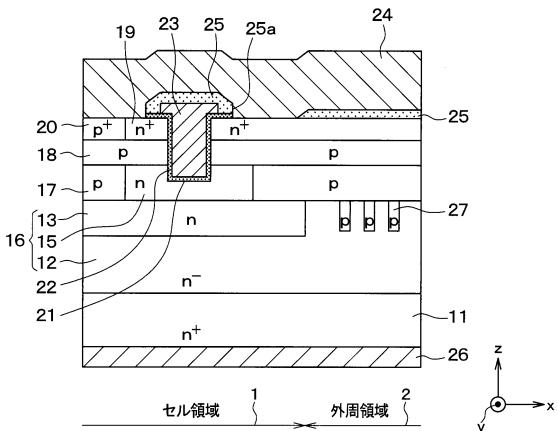

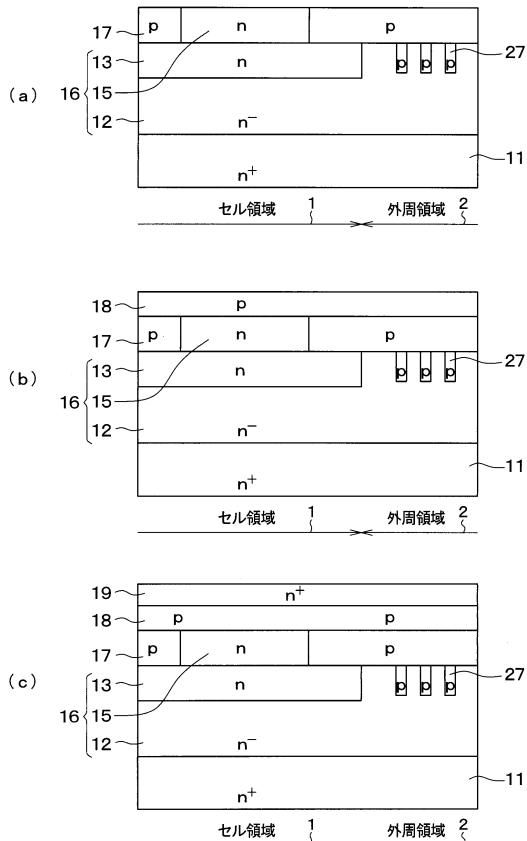

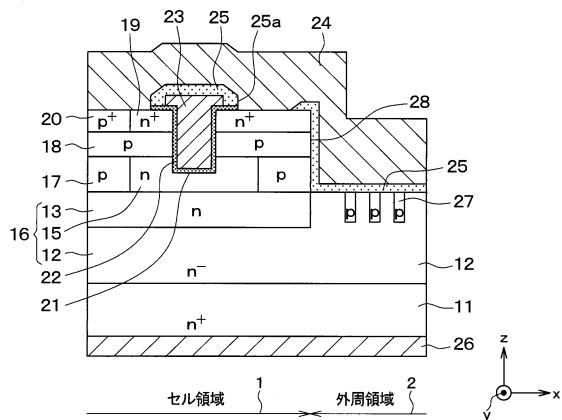

【図2】セル領域および外周領域の断面図である。

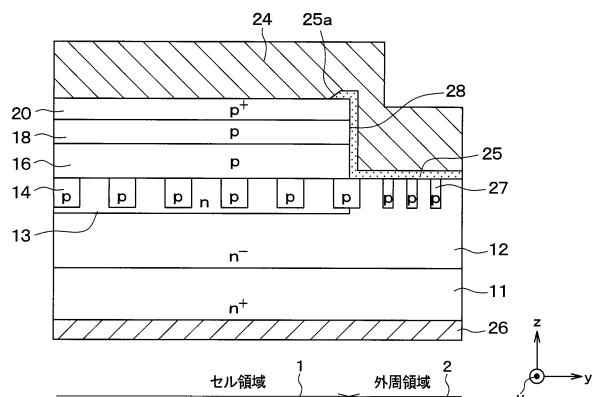

【図3】図2とは異なるセル領域および外周領域の断面図である。

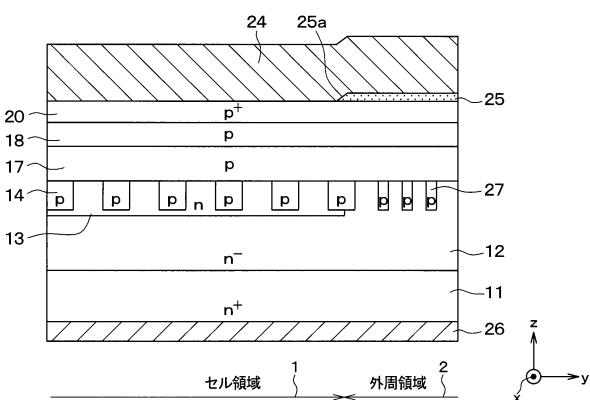

【図4】第1電流分散層の不純物濃度および幅と、第1電流分散層のオン抵抗との関係を

10

20

30

40

50

示すシミュレーション結果である。

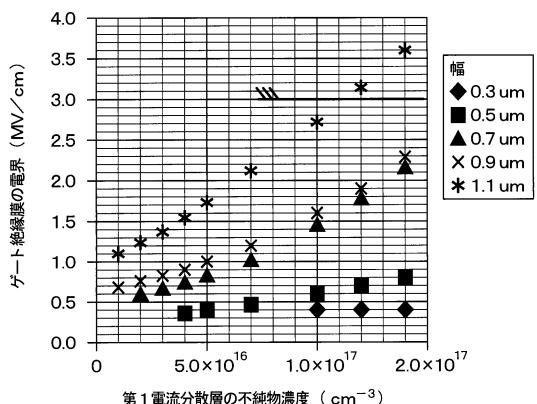

【図5】第1電流分散層の不純物濃度および幅と、ゲート絶縁膜に印加される電界との関係を示すシミュレーション結果である。

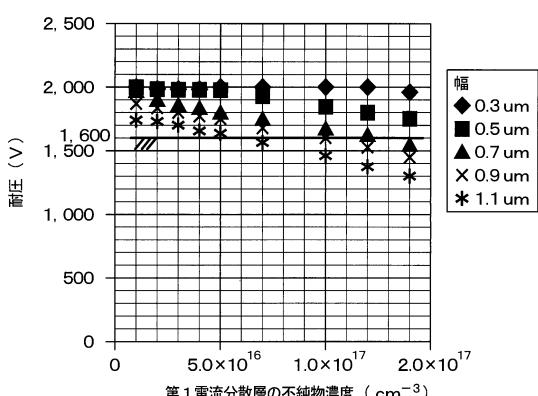

【図6】第1電流分散層の不純物濃度および幅と、耐圧との関係を示すシミュレーション結果である。

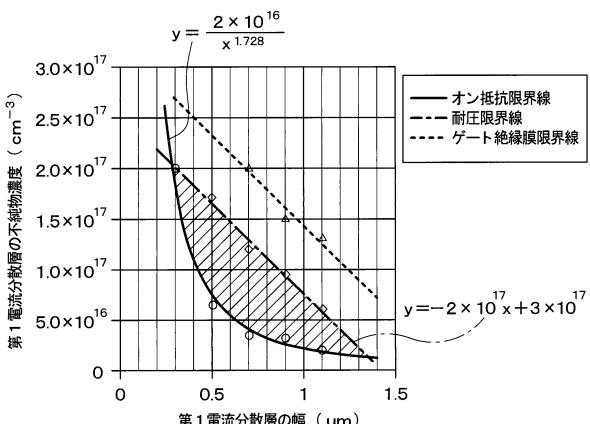

【図7】オン抵抗、ゲート絶縁膜に印加される電界、および耐圧と、第1電流分散層の不純物濃度および幅との関係を示す結果である。

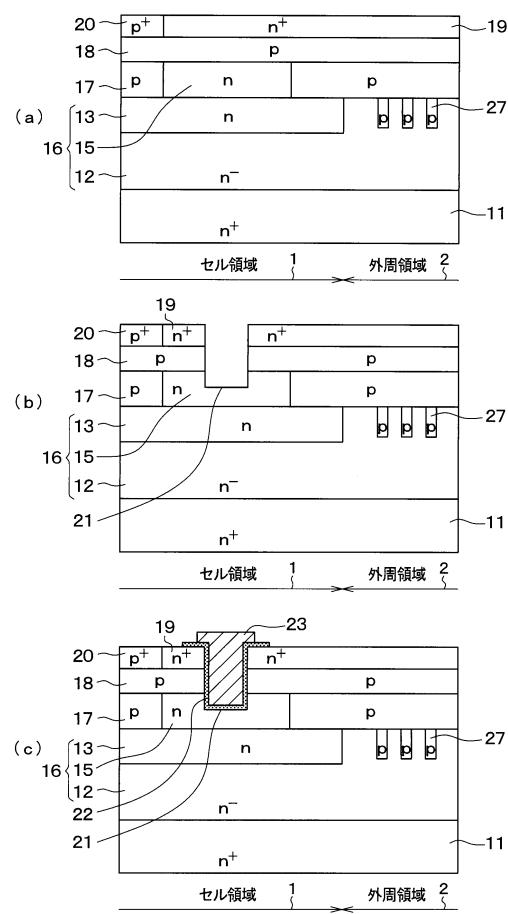

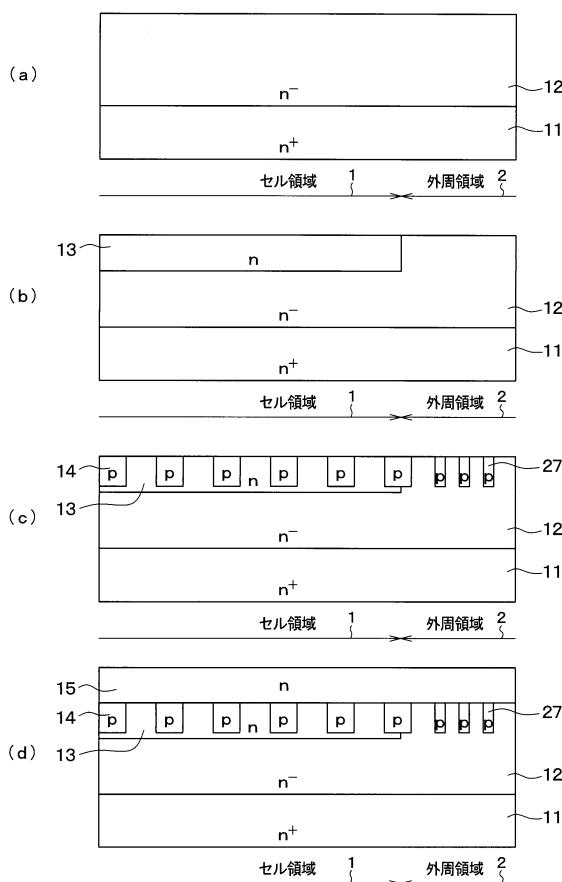

【図8】図2に示すSiC半導体装置の製造工程を示す断面図である。

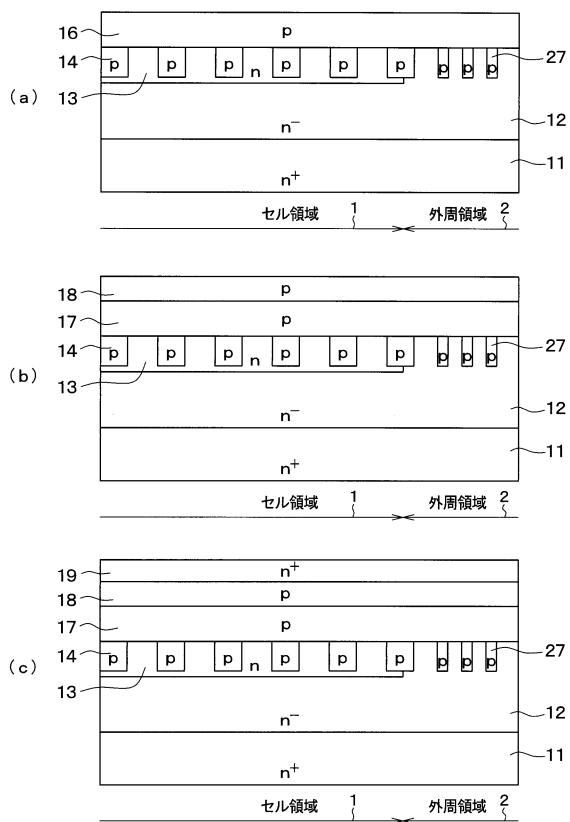

【図9】図8に続くSiC半導体装置の製造工程を示す断面図である。

【図10】図9に続くSiC半導体装置の製造工程を示す断面図である。 10

【図11】図3に示すSiC半導体装置の製造工程を示す断面図である。

【図12】図11に続くSiC半導体装置の製造工程を示す断面図である。

【図13】図12に続くSiC半導体装置の製造工程を示す断面図である。

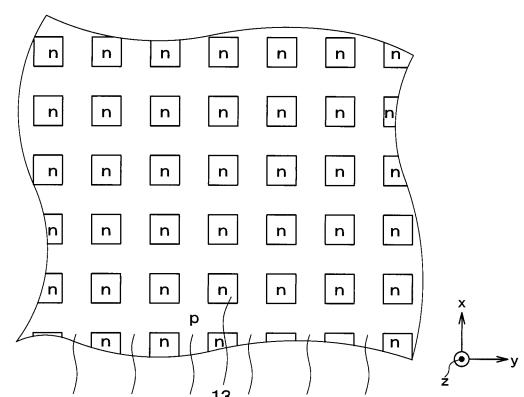

【図14】第2実施形態における第1電流分散層および第1ディープ層の位置関係を示す平面模式図である。

【図15】他の実施形態におけるSiC半導体装置の断面図である。

【図16】他の実施形態におけるSiC半導体装置の断面図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。 20

【0017】

(第1実施形態)

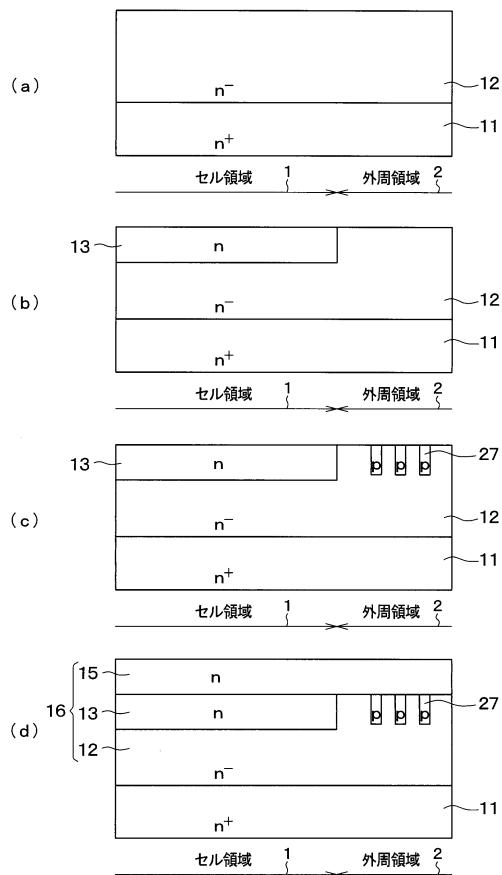

第1実施形態について図1～図3を参照しつつ説明する。本実施形態のSiC半導体装置は、図1～図3に示されるように、反転型のトレンチゲート構造のMOSFETが形成されたセル領域1と、当該セル領域1を囲むように外周耐圧構造が形成された外周領域2とを有する構成とされている。なお、図2中のセル領域1は、図1中のII-II線に沿った断面図に相当し、図3中のセル領域1は、図1中のIII-III線に沿った断面図に相当する。また、図1は、MOSFETのセル領域1における1セル分の斜視断面図である。

【0018】 30

図1～図3に示されるように、SiC半導体装置は、SiCからなる $n^+$ 型の基板11を備えている。本実施形態では、基板11は、例えば、(0001)Si面に対して0～8°のオフ角を有し、窒素やリン等のn型不純物濃度が例えば $1.0 \times 10^{19} / \text{cm}^3$ とされ、厚さが300μm程度とされたものが用いられる。

【0019】

なお、図1～図3では、基板11の面方向をxy平面とし、xy平面における<11-20>方向をy軸方向、y軸方向と直交する方向をx軸方向としている。また、基板11の面方向に対する法線方向をz軸方向としている。

【0020】

基板11の表面上には、窒素やリン等のn型不純物濃度が例えば $5.0 \sim 10.0 \times 10^{15} / \text{cm}^3$ とされ、厚さが10～15μm程度とされたSiCからなる $n^-$ 型層12が形成されている。この $n^-$ 型層12は、不純物濃度が深さ方向において一定であってもよいが、濃度分布に傾斜を付け、 $n^-$ 型層12のうちの基板11側の方が基板11から離れる側よりも高濃度となるようにすると好ましい。例えば、 $n^-$ 型層12は、基板11の表面から3～5μm程度の部分の不純物濃度が $2.0 \times 10^{15} / \text{cm}^3$ 程度他の部分よりも高くなるようにするのがよい。このような構成にすると、 $n^-$ 型層12の内部抵抗を低減でき、オン抵抗を低減することができる。なお、本実施形態では、 $n^-$ 型層12が第1不純物領域に相当している。

【0021】

そして、セル領域1では、 $n^-$ 型層12の表層部に、 $n^-$ 型層12よりも高不純物濃度

10

20

30

40

50

とされた第1電流分散層13が形成されている。第1電流分散層13は、窒素やリン等のn型不純物によって構成され、深さが $0.3 \sim 1.5 \mu\text{m}$ とされている。なお、第1電流分散層13の具体的な不純物濃度については後述する。

#### 【0022】

また、第1電流分散層13は、本実施形態では、セル領域1のみに形成されている。つまり、本実施形態では、n<sup>-</sup>型層12の表層部に第1電流分散層13が形成されている領域がセル領域1とされ、n<sup>-</sup>型層12の表層部に第1電流分散層13が形成されていない領域が外周領域2とされている。

#### 【0023】

第1電流分散層13には、ボロン等のp型不純物濃度が例えば $2.0 \times 10^{17} \sim 2.0 \times 10^{18}$ とされたp型の第1ディープ層14が複数形成されている。本実施形態では、複数の第1ディープ層14は、ストライプ状となるように、それぞれx軸方向に沿って延設され、y軸方向に沿って等間隔に配列されている。

#### 【0024】

また、第1ディープ層14は、第1電流分散層13より浅く形成されている。つまり、第1ディープ層14は、底部が第1電流分散層13内に位置するように形成されている。言い換えると、第1ディープ層14は、n<sup>-</sup>型層12との間に第1電流分散層13が位置するように形成されている。

#### 【0025】

なお、本実施形態では、第1ディープ層14は、後述するようにイオン注入によって形成されるが、イオン注入時におけるフォトリソグラフィーの加工限界を考慮し、y軸方向の長さが $0.3 \mu\text{m}$ 以上となるように形成されている。また、隣合う第1ディープ層14のy軸方向に沿った間隔、つまり隣合う第1ディープ層14で挟まれる第1電流分散層13のy軸方向に沿った幅（以下では、単に第1電流分散層13の幅ともいう）については、後述する。但し、隣合う第1ディープ層14の間隔は、後述する隣合うトレンチ21の間隔よりも狭くされている。

#### 【0026】

第1電流分散層13および第1ディープ層14上には、窒素やリン等のn型不純物濃度が例えば $1.0 \times 10^{16} \sim 5.0 \times 10^{17}$ とされ、厚さが $0.5 \sim 2 \mu\text{m}$ とされた第2電流分散層15が形成されている。なお、本実施形態では、後述するように、n<sup>-</sup>型層12、第1電流分散層13、および第2電流分散層15を含んでドリフト層16が構成されている。

#### 【0027】

また、第2電流分散層15には、当該第2電流分散層15を貫通するように、ボロン等のp型不純物濃度が例えば $2.0 \times 10^{17} \sim 2.0 \times 10^{18}$ とされ、厚さが第2電流分散層15と等しくされた複数の第2ディープ層17が形成されている。本実施形態では、第2ディープ層17は、y軸方向に沿って延設されている。つまり、第2ディープ層17は、各第1ディープ層14と交差する方向に延設されている。そして、各第2ディープ層17は、それぞれ複数の第1ディープ層14と繋がっている。なお、第2ディープ層17は、後述するトレンチ21を挟むように形成されている。つまり、第2ディープ層17は、トレンチ21から離れて形成されている。

#### 【0028】

第2電流分散層15および第2ディープ層17上には、P型のベース領域18が形成されている。そして、ベース領域18の表層部には、n<sup>+</sup>型のソース領域19およびp<sup>+</sup>型のコンタクト層20が形成されている。なお、ソース領域19は、後述するトレンチゲート構造の両側に配置されており、コンタクト層20は、ソース領域19を挟んでトレンチゲート構造と反対側に備えられている。また、本実施形態では、ソース領域19が第2不純物領域に相当している。

#### 【0029】

ベース領域18は、ボロン等のp型不純物濃度が例えば $5.0 \times 10^{16} \sim 2.0 \times 10^{17}$

10

20

30

40

50

$0^{19} / \text{cm}^3$ 、厚さが $2.0 \mu\text{m}$ 程度で構成されている。ソース領域19は、表層部における窒素やリン等のn型不純物濃度（すなわち、表面濃度）が例えば $1.0 \times 10^{21} / \text{cm}^3$ 、厚さが $0.3 \mu\text{m}$ 程度で構成されている。コンタクト層20は、例えば表層部におけるボロン等のp型不純物濃度（すなわち、表面濃度）が例えば $1.0 \times 10^{21} / \text{cm}^3$ 、厚さが $0.3 \mu\text{m}$ 程度で構成されている。

#### 【0030】

また、ベース領域18およびソース領域19を貫通して第2電流分散層15に達すると共に、底面が第2電流分散層15内に位置するように、例えば幅が $1.4 \sim 2.0 \mu\text{m}$ とされたトレンチ21が形成されている。言い換えると、トレンチ21は、第1電流分散層13および第1ディープ層14に達しないように形成されている。つまり、トレンチ21は、当該トレンチ21の底面よりも下方に第1電流分散層13および第1ディープ層14が位置するように形成されている。なお、トレンチ21がベース領域18およびソース領域19を貫通するように形成されているため、ベース領域18およびソース領域19は、トレンチ21の側面と接するように形成されているともいえる。

#### 【0031】

そして、トレンチ21は、内壁面に形成されたゲート絶縁膜22と、ゲート絶縁膜22の表面に形成されたドープトPoly-Siによって構成されるゲート電極23によって埋め込まれている。これにより、トレンチゲート構造が構成されている。特に限定されるものではないが、ゲート絶縁膜22は、トレンチ21の内壁面を熱酸化することで形成され、厚さがトレンチ21の側面側および底部側で共に $100 \text{ nm}$ 程度とされている。

#### 【0032】

本実施形態では、このようにして、トレンチゲート構造が構成されている。また、トレンチ21は、図1中のy軸方向（すなわち、<-1120>方向）を長手方向として延設されている。本実施形態では、このようにトレンチ21が<11-20>方向に延設されることにより、トレンチ21の側壁面である(1-100)面にファセット面が形成されることを抑制できる。また、(1-100)面をチャネルとして用いることができるため、チャネル移動度依存性の影響を低減できる。なお、トレンチ21は、実際には、図1中のx軸方向に沿って複数並べて形成されることでストライプ状とされる。また、上記のソース領域19およびコンタクト層20は、トレンチ21の延設方向に沿って延設されている。

#### 【0033】

ソース領域19およびコンタクト層20の表面やゲート電極23の表面には、ソース電極24やゲート配線（図示せず）が形成されている。なお、本実施形態では、ソース電極24が第1電極に相当している。

#### 【0034】

ソース電極24およびゲート配線は、複数の金属（例えばNi/A1等）にて構成されており、少なくともn型SiC（すなわち、ソース領域19やnドープの場合のゲート電極23）と接触する部分はn型SiCとオーミック接触可能な金属で構成されている。また、ソース電極24およびゲート配線は、少なくともp型SiC（すなわち、コンタクト層20やpドープの場合のゲート電極23）と接触する部分はp型SiCとオーミック接触可能な金属で構成されている。

#### 【0035】

なお、これらソース電極24およびゲート配線は、層間絶縁膜25上に形成されることで電気的に絶縁されている。そして、ソース電極24は、層間絶縁膜25に形成されたコンタクトホール25aを通じてソース領域19およびコンタクト層20と電気的に接続されている。これにより、第1ディープ層14は、コンタクト層20、ベース領域18、第2ディープ層17を介してソース電極24と同電位に維持される。また、ゲート配線は、図1～図3とは別断面において、層間絶縁膜25に形成されたコンタクトホール25aを通じてゲート電極23と電気的に接続されている。

#### 【0036】

10

20

30

40

50

基板 1 1 の裏面側には、基板 1 1 と電気的に接続されるドレイン電極 2 6 が形成されている。なお、本実施形態では、基板 1 1 がドレイン層として機能する。また、本実施形態では、ドレイン電極 2 6 が第 2 電極に相当している。

#### 【 0 0 3 7 】

以上説明したように、セル領域 1 には、n チャネルタイプの反転型のトレンチゲート構造の M O S F E T が構成されている。

#### 【 0 0 3 8 】

外周領域 2 は、図 2 および図 3 に示されるように、n - 型層 1 2 上に、セル領域 1 に形成された第 2 ディープ層 1 7 が延設されている。そして、n - 型層 1 2 の表層部には、第 2 ディープ層 1 7 と繋がると共に、セル領域 1 を囲む複数の P 型のガードリング 2 7 が構成されている。本実施形態では、ガードリング 2 7 は、第 1 電流分散層 1 3 と同じ不純物濃度とされていると共に、同じ深さとされている。なお、外周領域 2 には、上記のように、第 1 電流分散層 1 3 は形成されていない。10

#### 【 0 0 3 9 】

以上が本実施形態における S i C 半導体装置の構成である。次に、上記 S i C 半導体装置の作動について説明する。

#### 【 0 0 4 0 】

まず、上記 S i C 半導体装置は、ゲート電極 2 3 にゲート電圧が印加される前のオフ状態では、ベース領域 1 8 に反転層が形成されない。このため、ドレイン電極 2 6 に正の電圧（例えば、1 6 0 0 V）が印加されたとしても、ソース領域 1 9 からベース領域 1 8 内に電子が流れず、ソース電極 2 4 とドレイン電極 2 6 との間には電流が流れない。20

#### 【 0 0 4 1 】

また、ゲート電極 2 3 にゲート電圧が印加される前の状態では、ドレイン - ゲート間に電界がかかり、ゲート絶縁膜 2 2 の底部に電界集中が発生し得る。しかしながら、上記 S i C 半導体装置では、トレンチ 2 1 よりも深い位置に、第 1 ディープ層 1 4 および第 1 電流分散層 1 3 が備えられている。このため、第 1 ディープ層 1 4 および第 1 電流分散層 1 3 との間に構成される空乏層により、ドレイン電圧の影響による高電界がゲート絶縁膜 2 2 に入り込み難くなる。したがって、本実施形態では、ゲート絶縁膜 2 2 が破壊されることを抑制できる。

#### 【 0 0 4 2 】

そして、ゲート電極 2 3 に所定のゲート電圧（例えば、2 0 V）が印加されると、ベース領域 1 8 のうちのトレンチ 2 1 に接している表面にチャネルが形成される。このため、ソース電極 2 4 から注入された電子は、ソース領域 1 9 からベース領域 1 8 に形成されたチャネルを通った後、第 2 電流分散層 1 5 に流れる。そして、第 2 電流分散層 1 5 に流れた電子は、第 1 電流分散層 1 3 を通過して n - 型層 1 2 に流れ、その後にドレイン層としての基板 1 1 を通過してドレイン電極 2 6 へ流れる。これにより、ソース電極 2 4 とドレイン電極 2 6 との間に電流が流れ、S i C 半導体装置がオン状態となる。なお、本実施形態では、チャネルを通過した電子が第 2 電流分散層 1 5 、第 1 電流分散層 1 3 、および n - 型層 1 2 を通過して基板 1 1 へと流れるため、第 2 電流分散層 1 5 、第 1 電流分散層 1 3 、および n - 型層 1 2 を有してドリフト層 1 6 が構成されているといえる。3040

#### 【 0 0 4 3 】

この際、第 1 ディープ層 1 4 および第 2 ディープ層 1 7 と、第 1 電流分散層 1 3 および第 2 電流分散層 1 5 との間には、逆バイアスが印加された状態となり、空乏層が伸びる。しかしながら、本実施形態では、第 1 電流分散層 1 3 および第 2 電流分散層 1 5 は、n - 型層 1 2 よりも高不純物濃度とされている。このため、ドリフト層と接するようにディープ層が形成された従来の S i C 半導体装置と比較して、第 1 ディープ層 1 4 から延びる空乏層の広がりが抑制される。このため、電流経路が狭くなることが抑制され、オン抵抗の低減を図ることができる。

#### 【 0 0 4 4 】

以上が本実施形態における S i C 半導体装置の作動である。次に、第 1 電流分散層 1 3

の具体的な不純物濃度および幅について説明する。

**【0045】**

まず、図4に示されるように、第1電流分散層13のオン抵抗は、第1電流分散層13の不純物濃度が高くなるほど低くなる。詳しくは、第1電流分散層13のオン抵抗は、 $0.5 \text{ m} \cdot \text{cm}^2$ 以上の範囲では、不純物濃度が高くなるにつれて急峻に低くなり、 $0.5 \text{ m} \cdot \text{cm}^2$ 未満の範囲では、不純物濃度が高くなるにつれて緩やかに低くなる。また、オン抵抗は、第1電流分散層13の幅にも依存し、第1電流分散層13の幅が広くなるほど低くなる。このため、本実施形態では、オン抵抗が $0.5 \text{ m} \cdot \text{cm}^2$ 未満となるよう、第1電流分散層13の不純物濃度および幅が設定されている。

**【0046】**

次に、図5に示されるように、オフ時にゲート絶縁膜22に印加される電界は、第1電流分散層13の不純物濃度が高くなるほど大きくなり、第1電流分散層13の幅が広くなるほど大きくなる。ここで、本実施形態のようなトレンチゲート構造を有するSiC半導体装置では、ゲート絶縁膜22に印加される電界が $3.0 \text{ MV/cm}$ 未満であれば一般的に高信頼性とされている。したがって、本実施形態では、ゲート絶縁膜22に印加される電界が $3.0 \text{ MV/cm}$ 未満となるように、第1電流分散層13の不純物濃度および幅が設定されている。

10

**【0047】**

さらに、図6に示されるように、耐圧は、第1電流分散層13の不純物濃度が高くなるほど低くなり、第1電流分散層13の幅が広くなるほど低くなる。ここで、本実施形態のようなトレンチゲート構造を有するSiC半導体装置では、現状では、 $2000\text{V}$ の耐圧が理論的に最大とされており、 $1600\text{V}$ の耐圧を有すれば十分に高耐圧であるとされている。このため本実施形態では、耐圧が $1600\text{V}$ 以上となるように、第1電流分散層13の不純物濃度および幅が設定されている。

20

**【0048】**

そして、上記図4～図6をまとめると、図7のようになる。具体的には、図7において、ハッチングを施した部分が、図4の第1電流分散層13のオン抵抗、図5のゲート絶縁膜22に印加される電界、図6の耐圧の全てを満たす領域となる。

**【0049】**

このため、本実施形態では、第1電流分散層13の不純物濃度を $y [\text{cm}^{-3}]$ とし、第1電流分散層13の幅を $x [\mu\text{m}]$ とすると、 $2 \times 10^{16} / x^{1.728} < y < -2 \times 10^{17} + 3 \times 10^{17}$ とされている。これにより、本実施形態では、オン抵抗を低減しつつ、ゲート絶縁膜22に印加される電界を低減でき、さらに耐圧が低下することも抑制できる。なお、本実施形態では、複数の第1ディープ層14は、それぞれx軸方向に沿って延設されているため、第1電流分散層13の幅が第1電流分散層13における最も狭い部分の長さに相当する。

30

**【0050】**

次に、本実施形態のSiC半導体装置の製造方法について図8～図13を参照しつつ説明する。なお、図8～図10は、図2に相当する断面図であり、図10～図13は図3に相当する断面図である。

40

**【0051】**

まず、図8(a)および図11(a)示されるように、上記n<sup>+</sup>型の基板11を用意する。そして、この基板11の表面に、SiCからなるn<sup>-</sup>型層12をエピタキシャル成長させる。なお、基板11は、上記セル領域1および外周領域2を構成可能な面積を有するものが用いられる。

**【0052】**

次に、図8(b)および図11(b)に示されるように、n<sup>-</sup>型層12の表面に図示しないマスクを形成し、第1電流分散層13の形成予定領域が開口するようにマスクをフォトリソグラフィー等でパターニングする。具体的には、セル領域1のみが開口するように、マスクをパターニングする。そして、マスク上から窒素またはリン等のn型不純物をイ

50

オン注入と共に熱処理することにより、セル領域1のみに第1電流分散層13を形成する。その後、マスクを除去する。なお、マスクとしては、例えば、LTO(すなわち、Low Temperature oxide)膜等が用いられる。また、本実施形態では、後述の工程でもマスクが用いられるが、各マスクは、例えば、LTO膜等が用いられる。

#### 【0053】

本実施形態では、このように第1電流分散層13をイオン注入によって形成している。このため、第1電流分散層13をエピタキシャル膜で形成する場合と比較して、第1電流分散層13の不純物濃度の制御が容易になり、特性がばらつくことを抑制できる。

#### 【0054】

次に、図8(c)および図11(c)に示されるように、図示しないマスクを形成し、

10 第1ディープ層14およびガードリング27の形成予定領域が開口するようにマスクをフォトリソグラフィー等でパターニングする。そして、マスク上からボロン等のp型不純物をイオン注入すると共に熱処理することにより、第1ディープ層14およびガードリング27を形成する。つまり、本実施形態では、第1ディープ層14およびガードリング27を同じ工程で形成する。

#### 【0055】

なお、第1ディープ層14は、上記のように、ストライプ状であって、第1電流分散層13より浅く形成される。また、第1電流分散層13および第1ディープ層14は、上記のように、 $2 \times 10^{16} / x^{1.728} < y < -2 \times 10^{17} x + 3 \times 10^{17}$ を満たすように形成される。

20

#### 【0056】

続いて、図8(d)および図11(d)に示されるように、n-型層12上に、SiCからなる第2電流分散層15をエピタキシャル成長させる。これにより、n-型層12、第1電流分散層13、第2電流分散層15を有するドリフト層16が構成される。

#### 【0057】

次に、図9(a)および図12(a)に示されるように、図示しないマスクを形成し、第2ディープ層17の形成予定領域が開口するようにマスクをフォトリソグラフィー等でパターニングする。そして、マスク上からボロン等のp型不純物をイオン注入すると共に熱処理することにより、第2ディープ層17を形成する。

#### 【0058】

この際、第2ディープ層17を第1ディープ層14の延設方向と交差する方向に延設する。このため、第2ディープ層17を形成する際に多少の位置ずれがあったとしても、第1ディープ層14と第2ディープ層17とが繋がらないという不具合が発生することを抑制できる。

30

#### 【0059】

次に、図9(b)および図12(b)に示されるように、第2電流分散層15および第2ディープ層17上に、p型不純物層をエピタキシャル成長させることによってベース領域18を形成する。

#### 【0060】

続いて、図9(c)および図12(c)に示されるように、ベース領域18上に、n型不純物層をエピタキシャル成長させることによってソース領域19を形成する。

40

#### 【0061】

そして、図10(a)および図13に示されるように、図示しないマスクを形成し、コンタクト層20の形成予定領域が開口するようにマスクをフォトリソグラフィー等でパターニングする。そして、マスク上からボロン等のp型不純物をイオン注入すると共に熱処理することにより、コンタクト層20を形成する。

#### 【0062】

次に、図10(b)に示されるように、図示しないマスクを形成した後、トレンチ21の形成旅程領域が開口するようにマスクをパターニングする。そして、異方性エッチングを行ってトレンチ21を形成する。具体的には、ソース領域19およびベース領域18を

50

貫通し、第2電流分散層15内に底部が位置するように、トレンチ21を形成する。つまり、トレンチ21の底面より下方に、第1電流分散層13および第1ディープ層14が位置するように、トレンチ21を形成する。なお、異方性エッティングを行った後、必要に応じて等方性エッティングや犠牲層酸化を行うようにしてもよい。

#### 【0063】

次に、図10(c)に示されるように、トレンチ21内を含む場所にゲート絶縁膜22を形成する。具体的には、ウェット雰囲気を用いたパイロジェニック法によるゲート酸化(すなわち、熱酸化)によりゲート絶縁膜22を形成する。続いて、ゲート絶縁膜22の表面にn型不純物をドーピングしたポリシリコン層を例えば600nm程度成膜したのち、トレンチ21内にゲート絶縁膜22およびゲート電極23が残るよう10にエッチバック工程等を行う。これにより、トレンチゲート構造が構成される。

#### 【0064】

その後の工程に関しては、従来と同様であるため図示しないが、簡単に説明すると、まず、層間絶縁膜25を成膜する。そして、ソース領域19の一部およびコンタクト層20が露出するコンタクトホール25aおよびゲート電極23の一部が露出するコンタクトホールを形成する。次に、各コンタクトホール25aを埋め込むように電極材料を成膜した後、当該電極材料をパターニングすることでソース電極24やゲート配線を形成する。また、基板11の裏面側にドレイン電極26を形成する。以上のようにして、本実施形態のSiC半導体装置が製造される。

#### 【0065】

以上説明したように、本実施形態では、トレンチ21よりも深い位置に、n<sup>-</sup>型層12よりも高不純物濃度とされた第1電流分散層13と、当該第1電流分散層13内に形成された第1ディープ層14とを有している。このため、ゲート絶縁膜22に高電界が入り難くなり、ゲート絶縁膜22が破壊されることを抑制できる。

#### 【0066】

また、第1電流分散層13がn<sup>-</sup>型層12よりも高不純物濃度とされているため、ドリフト層と接するようにディープ層が形成された従来のSiC半導体装置と比較して、第1ディープ層14から延びる空乏層の広がりが抑制される。このため、第1ディープ層14によって電流経路が狭くなることが抑制され、オン抵抗の低減を図ることができる。

#### 【0067】

さらに、第1電流分散層13および第1ディープ層14は、トレンチ21よりも深い位置に形成されている。このため、第1ディープ層14を形成する際にアライメントズレ等が発生したとしても、第1ディープ層14とトレンチ21とが接することを抑制できる。

#### 【0068】

また、第1ディープ層14は、第1電流分散層13内に形成されている。つまり、第1ディープ層14は、第1ディープ層14の底部とn<sup>-</sup>型層12との間に第1電流分散層13が位置するように形成されている。このため、第1ディープ層14から延びる空乏層がn<sup>-</sup>型層12側に大きく延び、オン抵抗が増加することを抑制できる。

#### 【0069】

さらに、第2ディープ層17は、第1ディープ層14の延設方向と交差する方向に延設されている。このため、第2ディープ層17を第1ディープ層14の延設方向に沿って延設した場合と比較して、位置ずれ等が発生した場合に第2ディープ層17と第1ディープ層14とが繋がらないという不具合が発生することを抑制できる。つまり、第1ディープ層14がフローティング状態になるという不具合が発生することを抑制できる。

#### 【0070】

また、第2ディープ層17は、第1ディープ層14とベース領域18(つまり、ソース電極24)とを繋ぐ機能を主に発揮するものであり、トレンチ21から離れた位置に形成されている。このため、第2ディープ層17がトレンチ21と接している場合と比較して、ベース領域18に形成されたチャネルを通過した電子が第2電流分散層15に流れる際、第2電流分散層15へと流れる経路が狭くなることを抑制できる。したがって、オン抵

10

20

30

40

50

抗が増加することを抑制できる。

【0071】

さらに、第2電流分散層15は、n<sup>-</sup>型層12よりも高不純物濃度とされている。このため、例えば、第2電流分散層15がn<sup>-</sup>型層12と同じ不純物濃度とされている場合と比較して、第2ディープ層17から延びる空乏層の広がりも抑制される。つまり、第1電流分散層13内の電流経路が狭くなることを抑制できる。したがって、オン抵抗が増加することを抑制できる。

【0072】

また、第1電流分散層13および第1ディープ層14は、第1電流分散層13の不純物濃度をy [cm<sup>-3</sup>]、第1電流分散層13の幅をx [μm] とすると、 $2 \times 10^{16} / x^{1.728} < y < -2 \times 10^{17} x + 3 \times 10^{17}$ となるように形成されている。このため、オン抵抗を低減しつつ、ゲート絶縁膜22に印加される電界を低減でき、さらに耐圧が低下することも抑制できる。

【0073】

さらに、第1電流分散層13は、セル領域1のみに形成されており、外周領域2には形成されていない。このため、外周領域2では、空乏層が広がり易い構成となり、等電位線の間隔が広がり易くなることで電界集中が発生し難い構成とできる。したがって、設計の自由度を向上できる。

【0074】

また、第1電流分散層13は、イオン注入によって形成される。このため、第1電流分散層13をエピタキシャル膜で形成する場合と比較して、第1電流分散層13の不純物濃度の制御が容易になり、特性がばらつくことを抑制できる。

【0075】

(第2実施形態)

第2実施形態について説明する。第2実施形態は、第1ディープ層14の構成を変更したものであり、その他に関しては第1実施形態と同様であるため、ここでは説明を省略する。

【0076】

本実施形態では、図14に示されるように、第1ディープ層14は、x軸方向に沿って複数延設されている。そして、隣合う第1ディープ層14同士は、複数箇所で繋がっている。つまり、本実施形態では、第1ディープ層14は、格子状に形成されているといえる。なお、本実施形態では、第1電流分散層13は、最も狭い部分の長さが上記幅xとなる。つまり、例えば、図14中では、第1電流分散層13は、第1ディープ層14で囲まれる部分の平面形状が正方形とされているが、平面形状が長方形である場合、短辺の長さが上記幅xとなる。

【0077】

以上説明したように、本実施形態では、第1ディープ層14が格子状に形成されている。このため、さらに第1ディープ層14と第2ディープ層17とが繋がらないという不具合が発生することをさらに抑制しつつ、上記第1実施形態と同様の効果を得ることができる。

【0078】

(他の実施形態)

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

【0079】

例えば、上記各実施形態では、第1導電型をn型、第2導電型をp型としたnチャネルタイプのMOSFETを例に挙げて説明したが、各構成要素の導電型を反転させたpチャネルタイプのMOSFETに対しても本発明を適用することができる。また、上記各実施形態では、トレンチゲート構造のMOSFETを例に挙げて説明したが、同様のトレンチゲート構造のIGBTに対しても本発明を適用することができる。IGBTは、上記各実

10

20

30

40

50

施形態に対して基板 1 1 の導電型を n 型から p 型に変更するだけであり、その他の構造や製造方法に関しては上記各実施形態と同様である。

#### 【 0 0 8 0 】

また、上記第 1 実施形態において、外周領域 2 はメサ構造とされていてもよい。すなわち、図 1 5 および図 1 6 に示されるように、外周領域 2 は、ソース領域 1 9 、ベース領域 1 8 を貫通して n - 型層 1 2 に達する凹部 2 8 が形成されたメサ構造とされていてもよい。なお、図 1 5 のセル領域 1 は、図 1 中の II - II 線に沿った断面に相当し、図 1 6 中のセル領域 1 は、図 1 中の III - III 線に沿った断面に相当する。

#### 【 0 0 8 1 】

そして、上記各実施形態において、第 2 ディープ層 1 7 は、複数形成されておらず、1 10 つのみであってもよい。このような SiC 半導体装置としても、1 つの第 2 ディープ層 1 7 が各第 1 ディープ層 1 4 と繋がることにより、上記各実施形態と同様の効果を得ることができます。

#### 【 0 0 8 2 】

さらに、上記各実施形態において、第 1 ディープ層 1 4 は、例えば、y 軸方向に沿って延設されていてもよい。つまり、第 1 ディープ層 1 4 は、第 2 ディープ層 1 7 と同じ方向に延設されていてもよい。また、上記各実施形態において、第 2 電流分散層 1 5 は、例えば、n - 型層 1 2 と同じ不純物濃度とされていてもよい。そして、第 1 電流分散層 1 3 は、外周領域 2 にも形成されていてもよい。

#### 【 0 0 8 3 】

また、上記各実施形態において、コンタクト層 2 0 を形成されていなくてもよい。つまり、ソース電極 2 4 がベース領域 1 8 と接続されていてもよい。

#### 【 0 0 8 4 】

そして、上記各実施形態において、ゲート絶縁膜 2 2 は、熱酸化によらない酸化膜、または窒化膜等を含む構成とされていてもよい。

#### 【 0 0 8 5 】

さらに、上記各実施形態において、ベース領域 1 8 上に p 型不純物層をエピタキシャル成長させることによってコンタクト層 2 0 を形成した後、ソース領域 1 9 を形成するようにもよい。

#### 【 0 0 8 6 】

なお、結晶の方位を示す場合、本来ならば所望の数字の上にバー( - )を付すべきであるが、電子出願に基づく表現上の制限が存在するため、本明細書においては、所望の数字の前にバーを付すものとする。

#### 【 符号の説明 】

##### 【 0 0 8 7 】

1 1 基板

1 2 n - 型層(第 1 不純物領域)

1 3 第 1 電流分散層

1 4 第 1 ディープ層

1 5 第 2 電流分散層

1 7 第 2 ディープ層

1 8 ベース領域

1 9 ソース領域(第 2 不純物領域)

2 1 トレンチ

2 2 ゲート絶縁膜

2 3 ゲート電極

2 4 ソース電極(第 1 電極)

2 6 ドレイン電極(第 2 電極)

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【 四 8 】

【 四 9 】

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 J |

| H 01 L | 29/06 | 3 0 1 M |

| H 01 L | 29/06 | 3 0 1 G |

| H 01 L | 29/06 | 3 0 1 V |

(72)発明者 梶 愛子

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 海老原 康裕

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 永岡 達司

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 青井 佐智子

愛知県長久手市横道41番地の1 株式会社豊田中央研究所内

審査官 棚田 一也

(56)参考文献 特開2015-192027(JP, A)

米国特許出願公開第2014/0021484(US, A1)

国際公開第2014/199465(WO, A1)

特開2008-227356(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 29 / 06

H 01 L 29 / 12