US 20030070106A1

(19) **United States**

(12) **Patent Application Publication**

**Kosuda et al.**

(10) **Pub. No.: US 2003/0070106 A1**

(43) **Pub. Date: Apr. 10, 2003**

(54) **INFORMATION PROCESSING APPARATUS**

(30)

**Foreign Application Priority Data**

(76) Inventors: **Tsukasa Kosuda, Matsumoto-shi (JP); Motomu Hayakawa, Shiojiri-shi (JP)**

Mar. 31, 2000 (JP) ..... 2000-100122

Mar. 31, 2000 (JP) ..... 2000-100123

Mar. 27, 2001 (JP) ..... 2001-91111

Correspondence Address:

**EPSON RESEARCH AND DEVELOPMENT

INC

INTELLECTUAL PROPERTY DEPT

150 RIVER OAKS PARKWAY, SUITE 225

SAN JOSE, CA 95134 (US)**

**Publication Classification**

(51) **Int. Cl.<sup>7</sup> ..... G06F 1/04; G06F 1/06; G06F 1/08**

(52) **U.S. Cl. ..... 713/500**

(57) **ABSTRACT**

By using a CR oscillating circuit and a PLL oscillating circuit selectively, these two oscillating circuits are used as a high frequency, low power consumption, short waiting time for stable oscillation, and low operating voltage oscillating circuit.

(21) Appl. No.: **09/823,137**

(22) Filed: **Mar. 29, 2001**

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7A

FIG. 7B

FIG. 8

FIG. 9

FIG. 12

FIG. 10

51: QUARTZ CRYSTAL OSCILLATING CIRCUIT

FIG. 11

52: CR OSCILLATING CIRCUIT

FIG. 13

258: VOLTAGE GENERATING UNIT

FIG. 19

FIG. 14

261: INPUT INFORMATION PROCESSING UNIT

FIG. 17

FIG. 18

FIG. 20

FIG. 21

FIG. 22

FIG. 23

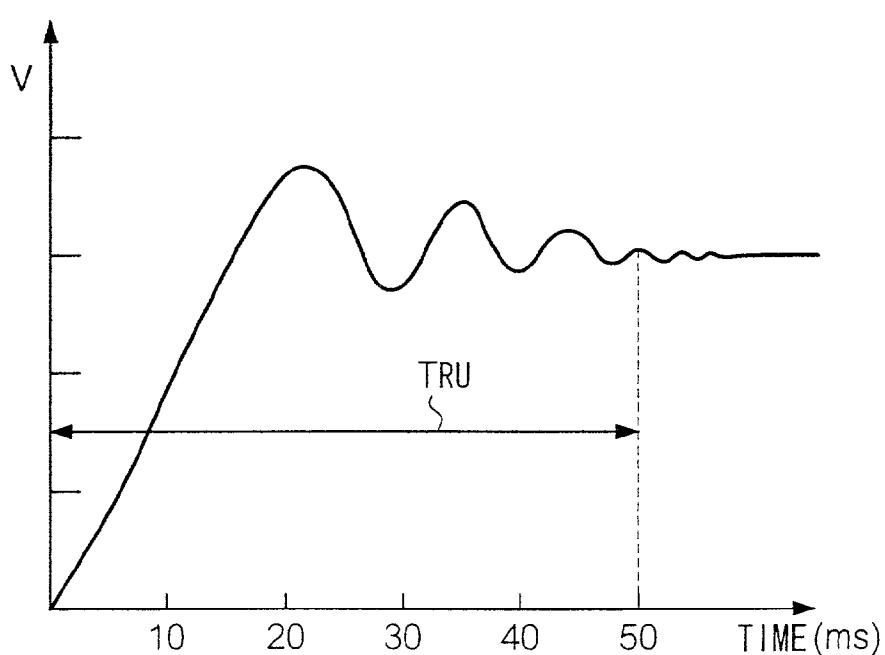

TRU : LOCK UP TIME

FIG. 24

## INFORMATION PROCESSING APPARATUS

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to an information processing apparatus, and more particularly to a technology for reducing power consumption in an information processing apparatus that has an oscillating circuit.

[0003] 2. Description of the Related Art

[0004] A small sized portable electronic apparatus usually works on batteries. Therefore, in order to extend the life of the battery, one-chip microcomputers used in this kind of small sized portable electronic apparatus are desired to be able to operate in low voltage and to be of low power consumption.

[0005] In order to realize this, one-chip microcomputers are usually driven at an operating voltage of around 1 voltage and at an operating frequency of around 32 kHz.

[0006] However, when small sized portable electronic equipment is required to have an information processing capability to some extent, the operating frequency of 32 kHz is not enough for processing information.

[0007] In order to solve this problem, a twin-clock microcomputer that has an oscillating circuit with a low operating frequency of around 32 kHz and an oscillating circuit with a high operating frequency of around 4 MHz is proposed. In this twin-clock microcomputer, when high speed processing is required the microcomputer is driven at a high speed operating frequency, otherwise it is driven at a low speed operating frequency.

[0008] Operating frequency and power consumption is in a roughly proportional relationship, for that reason high speed processing is not desirable from the viewpoint of power consumption.

[0009] However, recently, there is a demand for high speed information processing in small sized portable electronic apparatus, and at the same time much less power consumption is desired.

### SUMMARY OF THE INVENTION

[0010] Accordingly, it is an object of the present invention to provide an information processing apparatus that has capabilities of lowering power consumption and achieving high speed information processing.

[0011] In order to achieve the above mentioned problem, the present invention provides an information processing apparatus comprising: a first oscillating circuit for generating a first clock signal, the first oscillating circuit being capable of operating until a power supply voltage reaches a first lowest operating voltage; a second oscillating circuit for generating a second clock signal, the second oscillating circuit being capable of operating until the power supply voltage reaches a second lowest operating voltage that is higher than the first lowest operating voltage; a switching circuit that, based on the power supply voltage, selects either the first clock signal or the second clock signal to output as a clock signal; and an information processing unit, in synchronism with the clock signal, for performing information processing.

[0012] According to the above configuration, the first oscillating circuit generates the first clock signal and outputs it to the switching circuit.

[0013] The second oscillating circuit generates the second clock signal and outputs it to the switching circuit.

[0014] The switching circuit, based on the power supply voltage, outputs either the first clock signal or the second clock signal as the clock signal.

[0015] By this, the information-processing unit executes various information processing based on the clock signal.

[0016] As a power supply, a normal power supply such as a battery or a constant-voltage regulated power supply such as a voltage regulator may be used.

[0017] Also, the present invention is characterized by providing an information processing apparatus comprising: a first oscillating circuit that generates a first clock signal by using oscillation and has a first oscillation stability time, the first oscillation stability time being a time required for the first oscillating circuit becoming stable from a beginning of the oscillation of the first oscillating circuit; a second oscillating circuit that starts oscillating concurrently with the first oscillating circuit, generates a second clock signal by using oscillation, and has a second oscillation stability time, the second oscillation stability being a time required for the second oscillating circuit becoming stable from a beginning of the oscillation of the second oscillating circuit, and being longer than the first oscillation stability time; a switching circuit for, based on an elapsed time from the beginning of the oscillation, outputting either the first clock signal or the second clock signal as the clock signal; and an information processing unit for, in synchronism with the clock signal, performing information processing.

[0018] By the above configuration, the first oscillating circuit generates the first clock signal and outputs it to the switching circuit.

[0019] The second oscillating circuit generates the second clock signal and outputs it to the switching circuit.

[0020] By this, the information-processing unit executes various information processing based on the clock signal.

[0021] Also, the present invention is characterized by providing a control method for an information processing apparatus, the information processing apparatus comprising: an information processing unit for, based on a clock signal, carrying out various information processing operations; a first oscillating circuit that generates a first clock signal and is able to operate until power supply voltage reaches a first lowest operating voltage, a second oscillating circuit that generates a second clock signal and is able to operate until the power supply voltage reaches a second lowest operating voltage that is higher than the first lowest operating voltage; a switching circuit for, based on the power supply voltage, outputting either the first clock signal or the second clock signal as the clock signal; and the control method comprising: determining power supply voltage; outputting by the switching circuit the first clock signal as the clock signal when the power supply voltage is equal to or higher than the first lowest operating voltage and lower than the second lowest operating voltage; and outputting by the switching circuit the second clock signal as the clock signal when the power supply voltage is higher than the second lowest operating voltage.

[0022] By the above configuration, during determining power supply voltage, power supply voltage is determined.

[0023] During outputting the first clock signal, when the power supply voltage determined during determining power supply voltage is equal to or higher than the first lowest operating voltage and lower than the second lowest operating voltage, the switching circuit outputs the first clock signal as the clock signal.

[0024] During outputting the second clock signal, when the power supply voltage is equal to or higher than the second lowest operating voltage, the switching circuit outputs the second clock signal as the clock signal.

[0025] Also, the present invention is characterized by providing a control program executed by an information processing apparatus, the information processing apparatus comprising: an information processing unit for, based on a clock signal, carrying out various information processing operations; a first oscillating circuit that generates a first clock signal and is able to operate until power supply voltage reaches a first lowest operating voltage, a second oscillating circuit that generates a second clock signal and is able to operate until the power supply voltage reaches a second lowest operating voltage that is higher than the first lowest operating voltage; and a switching circuit for, based on the power supply voltage, outputting either the first clock signal or the second clock signal as the clock signal; and the control program comprising the routines of: determining the power supply voltage; outputting to the switching circuit the first clock signal as the clock signal when the power supply voltage is equal to or higher than the first lowest operating voltage and is lower than the second lowest operating voltage; and outputting to the switching circuit the second clock signal as the clock signal when the power supply voltage is higher than the second lowest operating voltage.

[0026] By the above configuration, the control program makes the information processing apparatus determine power supply voltage, when the power supply voltage is equal to or higher than the first lowest operating voltage and lower than the second lowest operating voltage, makes the switching circuit output the first clock signal as the clock signal, and when the power supply voltage is equal to or higher than the second lowest operating voltage, makes the switching circuit output the second clock signal as the clock signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

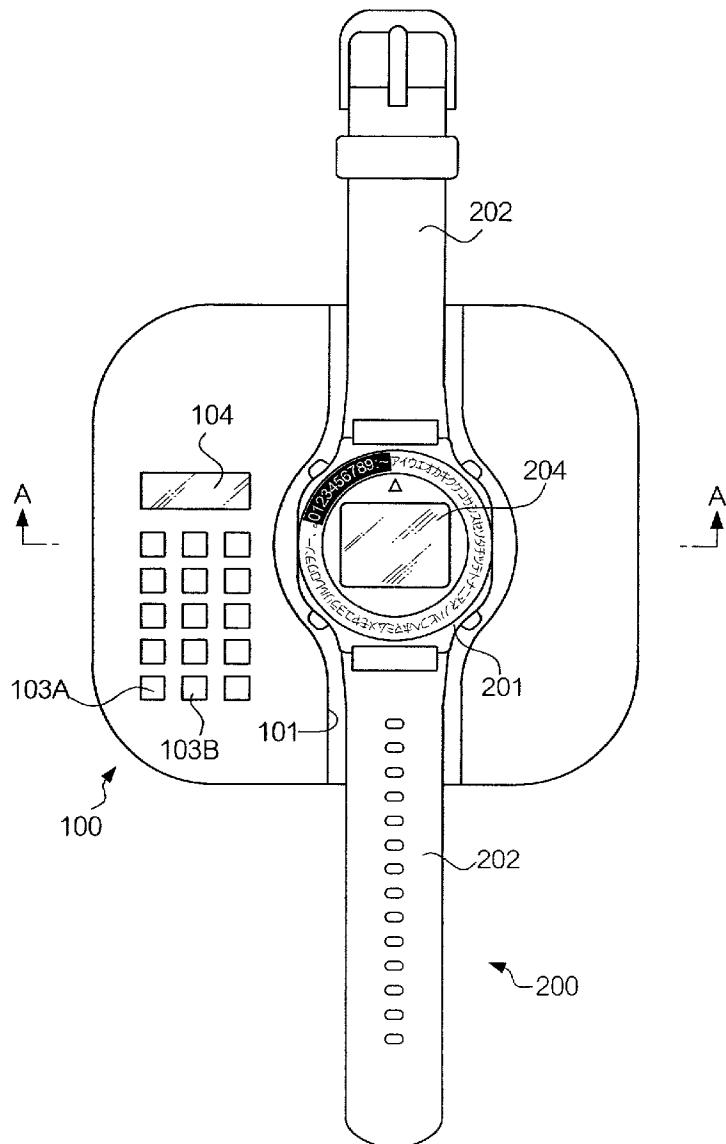

[0027] FIG. 1 is a plan view that shows a configuration of a watch-type information processing apparatus and a station of a first embodiment.

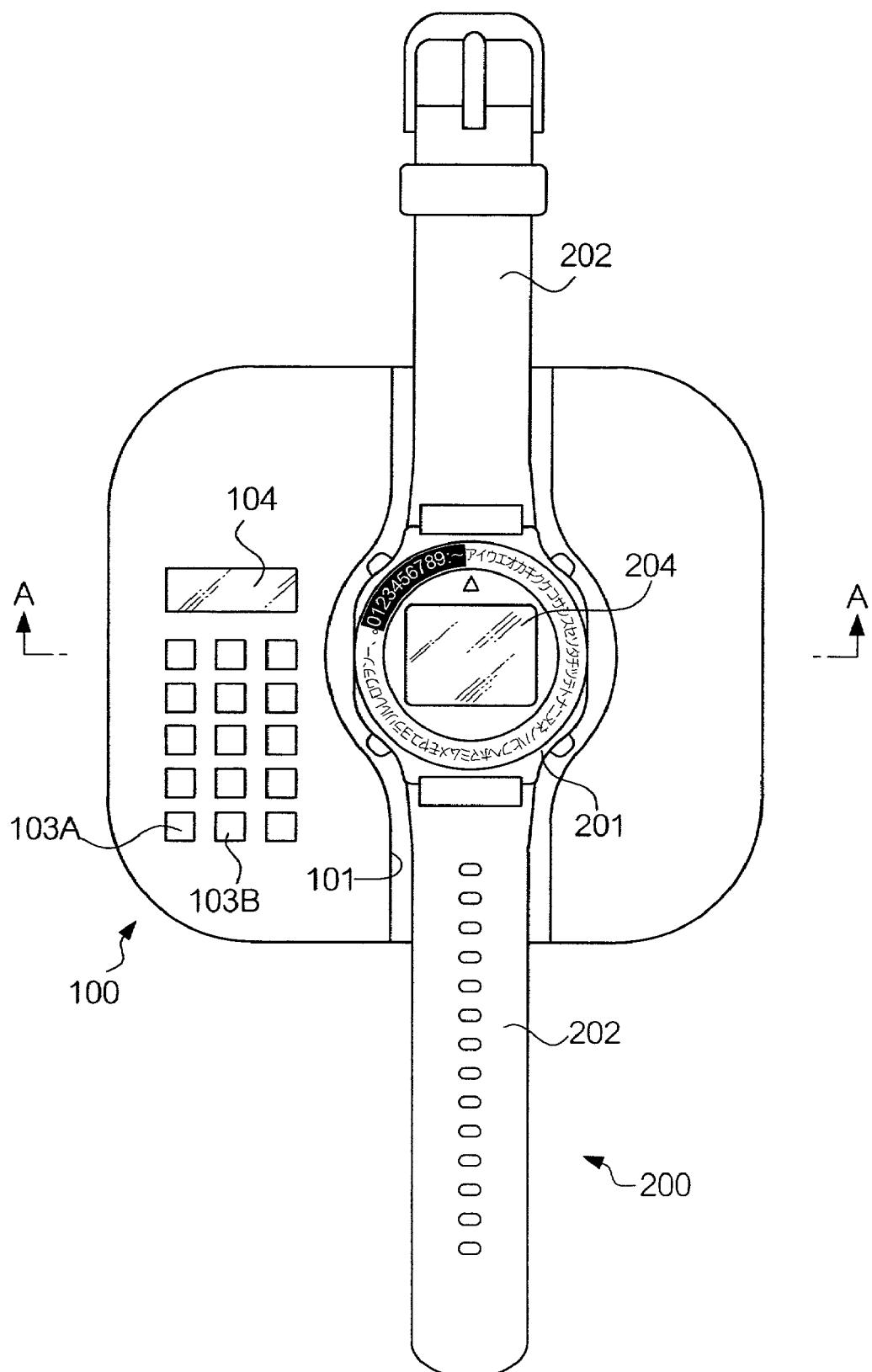

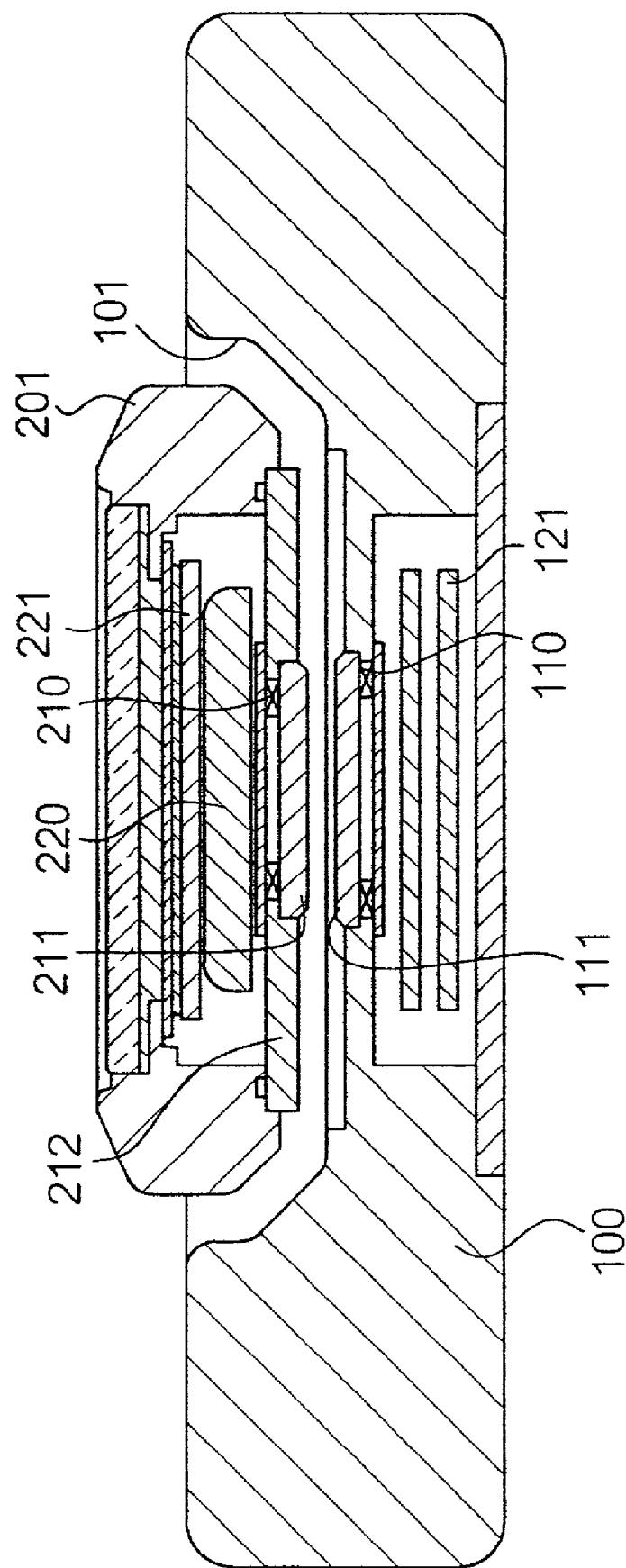

[0028] FIG. 2 is a section view taken on line A-A in FIG. 1.

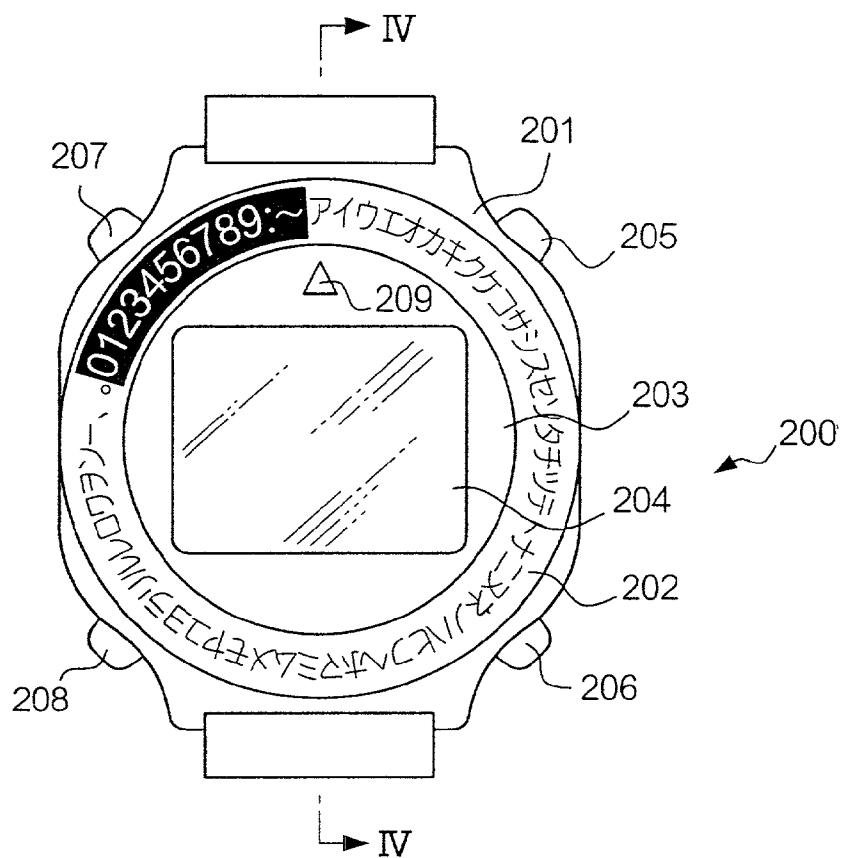

[0029] FIG. 3 is a front view of a watch-type information processing apparatus according to an embodiment of the present invention.

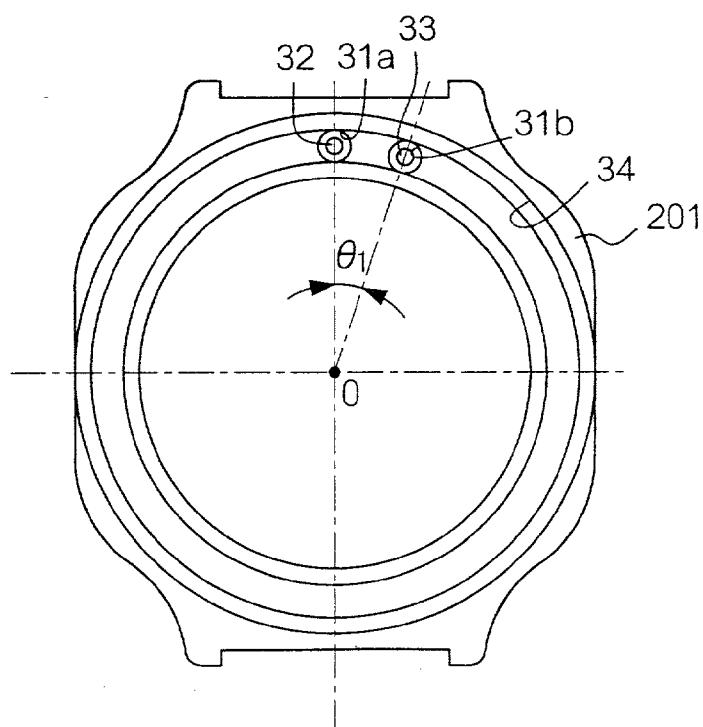

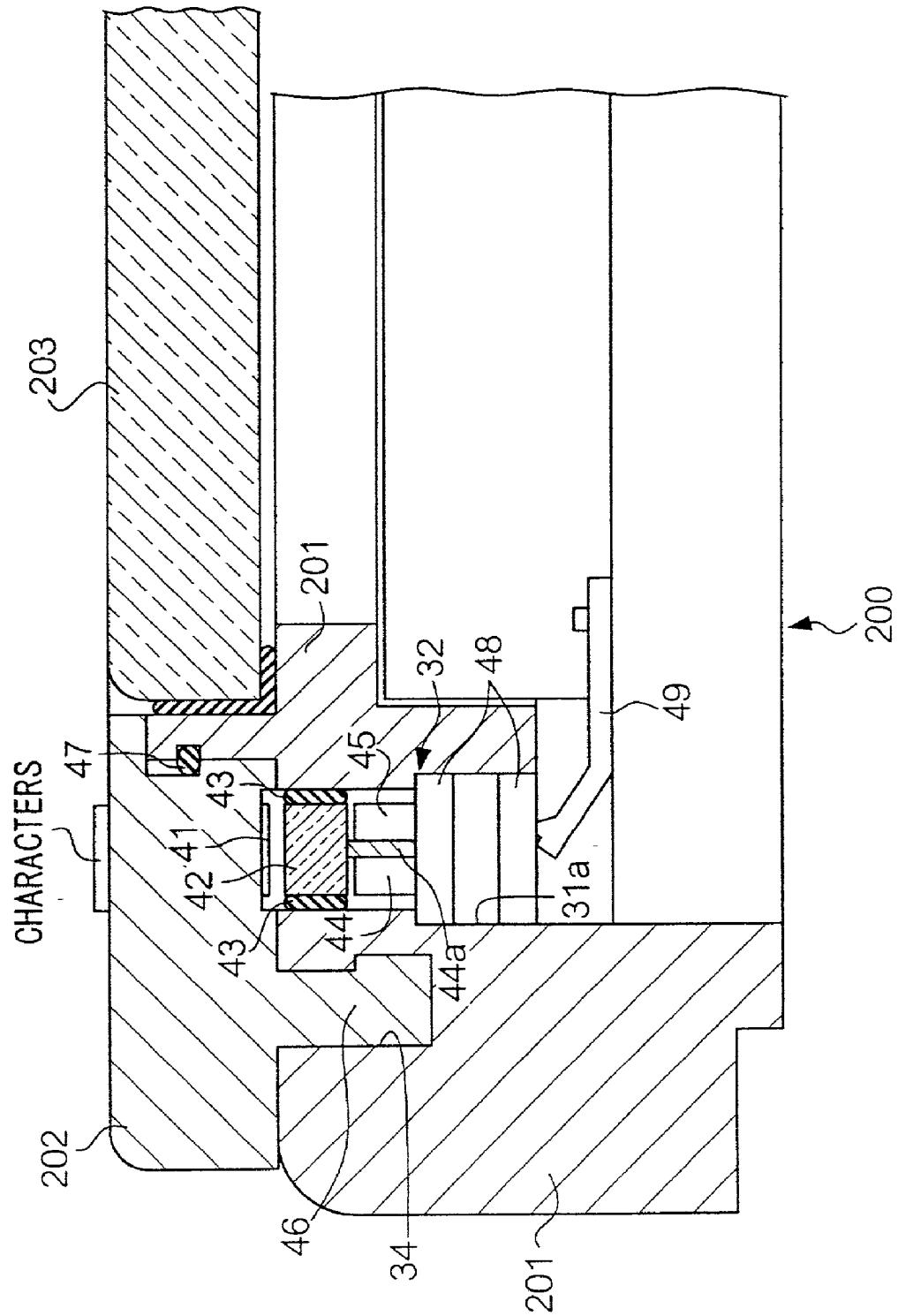

[0030] FIG. 4 is a diagram that shows a state of the information processing apparatus whose turning bezel is removed, FIG. 5 is a section view taken on line IV-IV in FIG. 3.

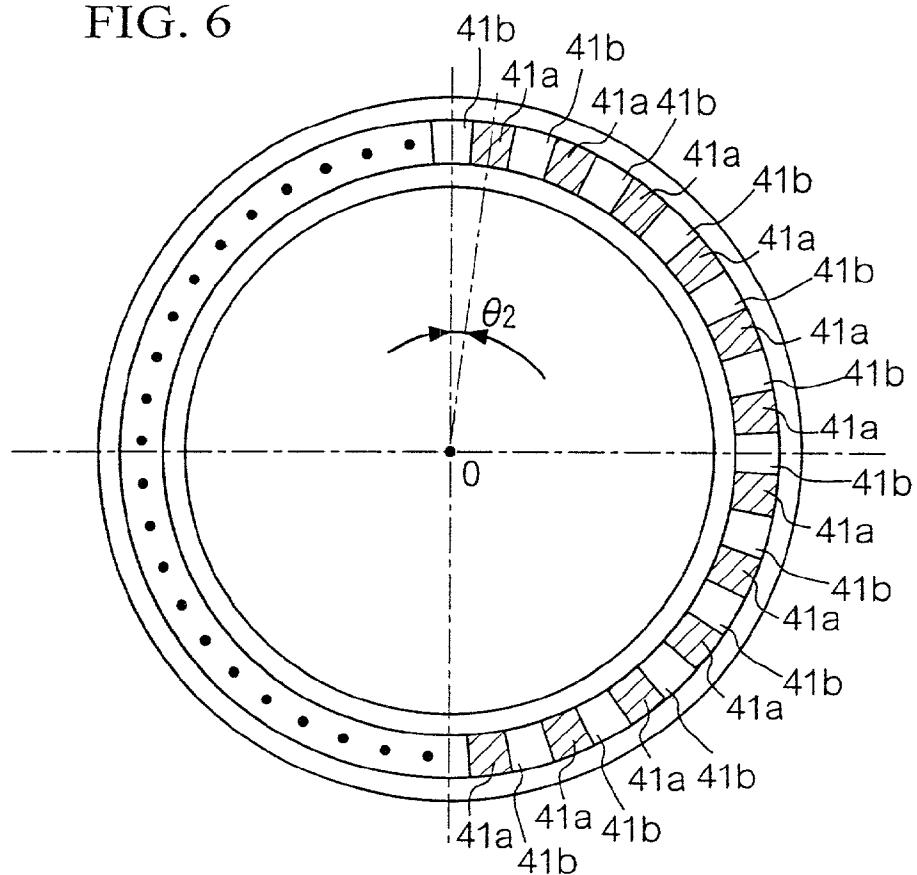

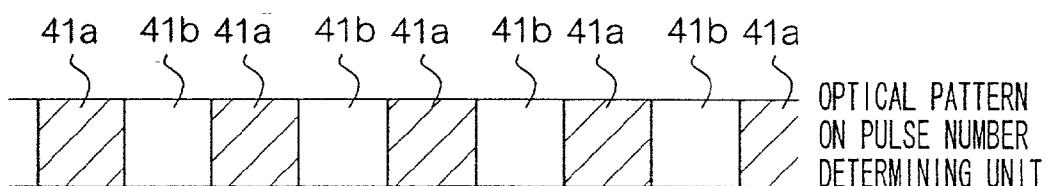

[0031] FIG. 6 is a diagram that shows the underside of the turning bezel.

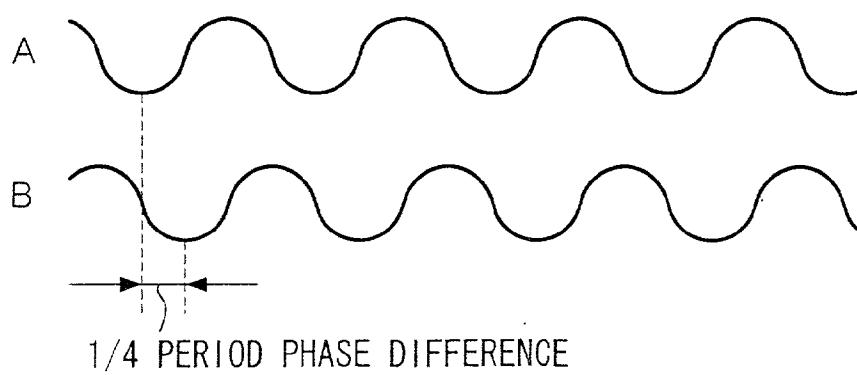

[0032] FIG. 7 is a diagram that explains a relation between an optical pattern made on the turning bezel and a first detection signal or a second detection signal.

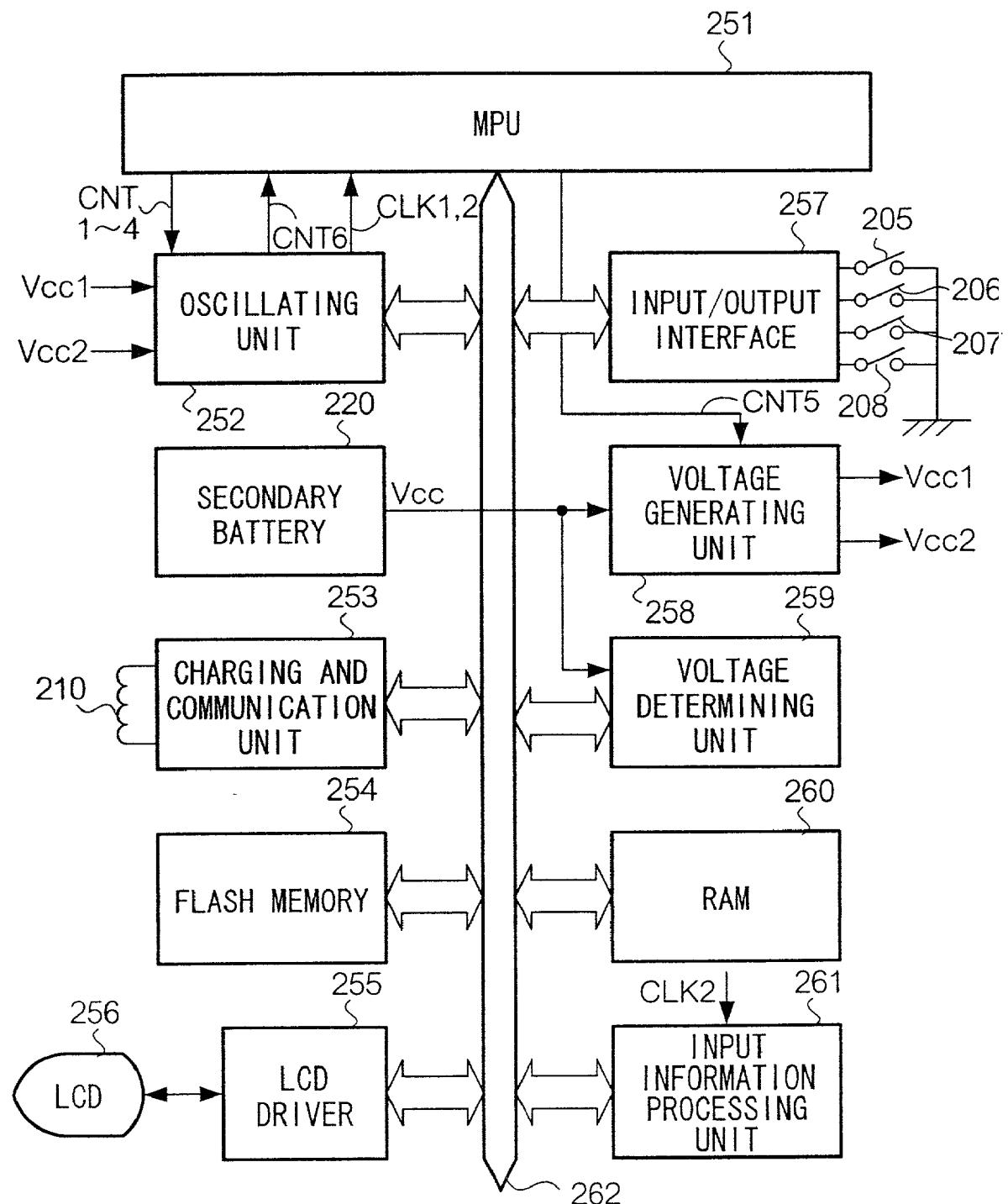

[0033] FIG. 8 is a schematic configuration block diagram of the watch-type information processing apparatus.

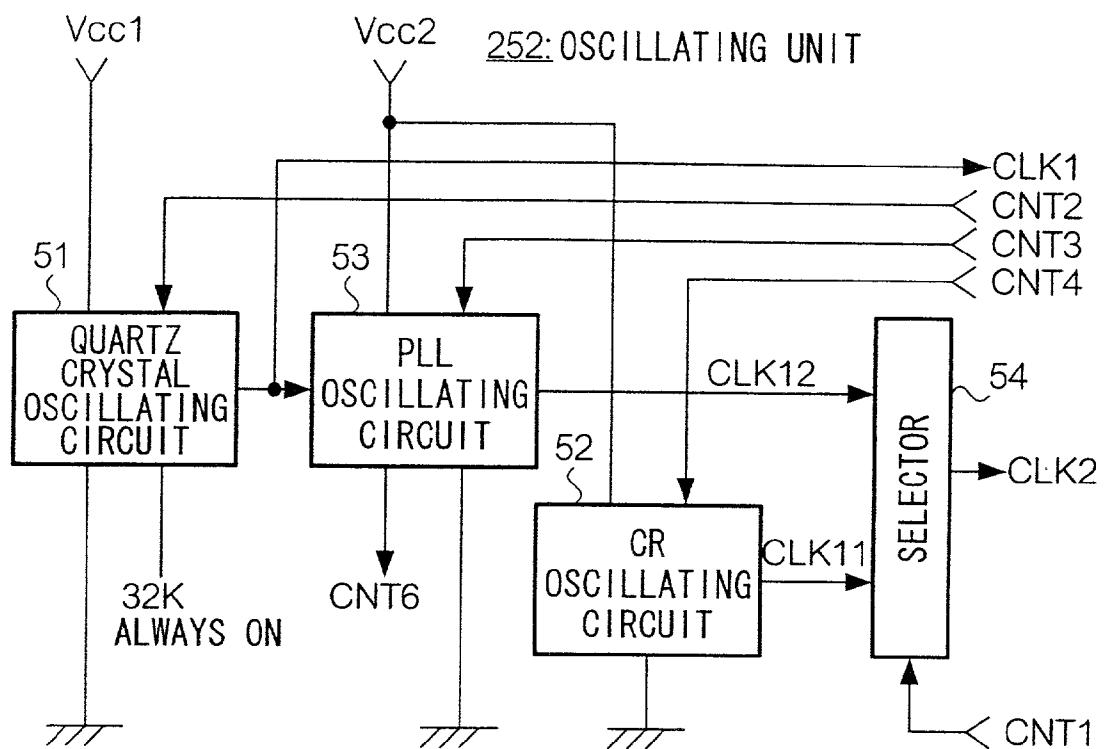

[0034] FIG. 9 is a detailed configuration block diagram of the oscillator unit in the information processing apparatus.

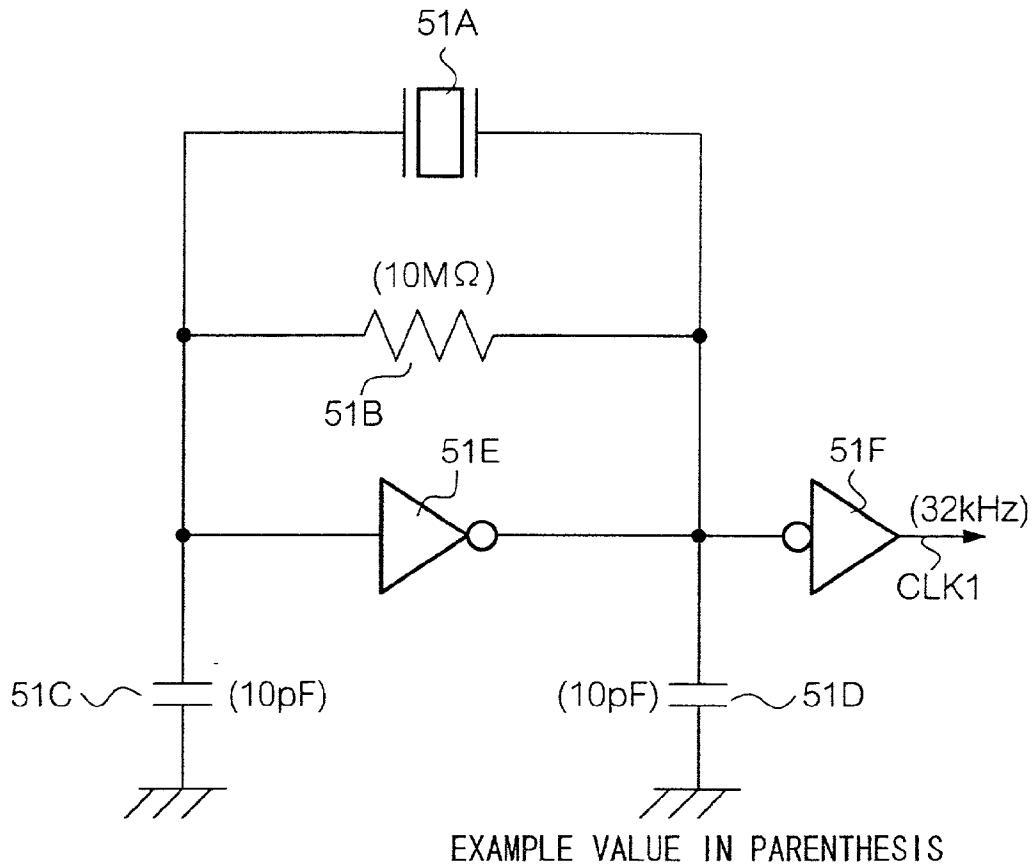

[0035] FIG. 10 is a detailed configuration diagram of the crystal quartz oscillating circuit in the oscillator unit.

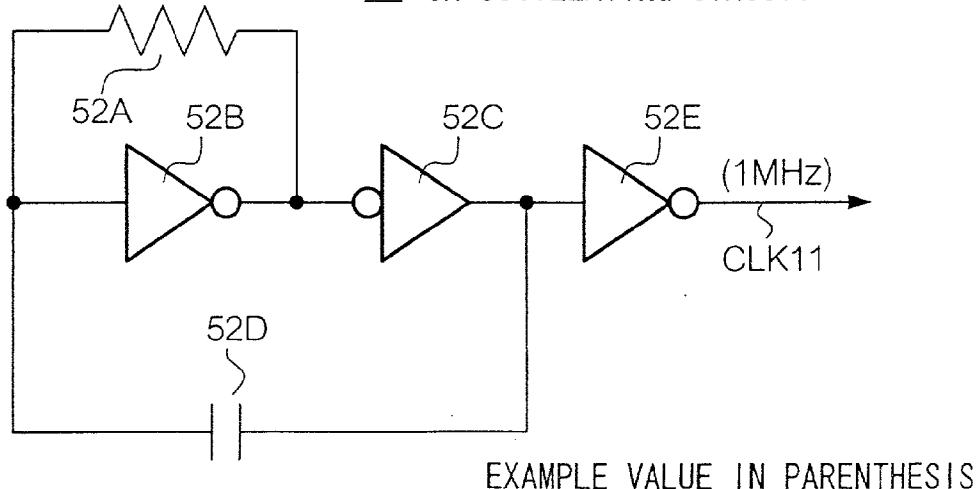

[0036] FIG. 11 is a detailed configuration diagram of the CR oscillating circuit in the oscillator unit.

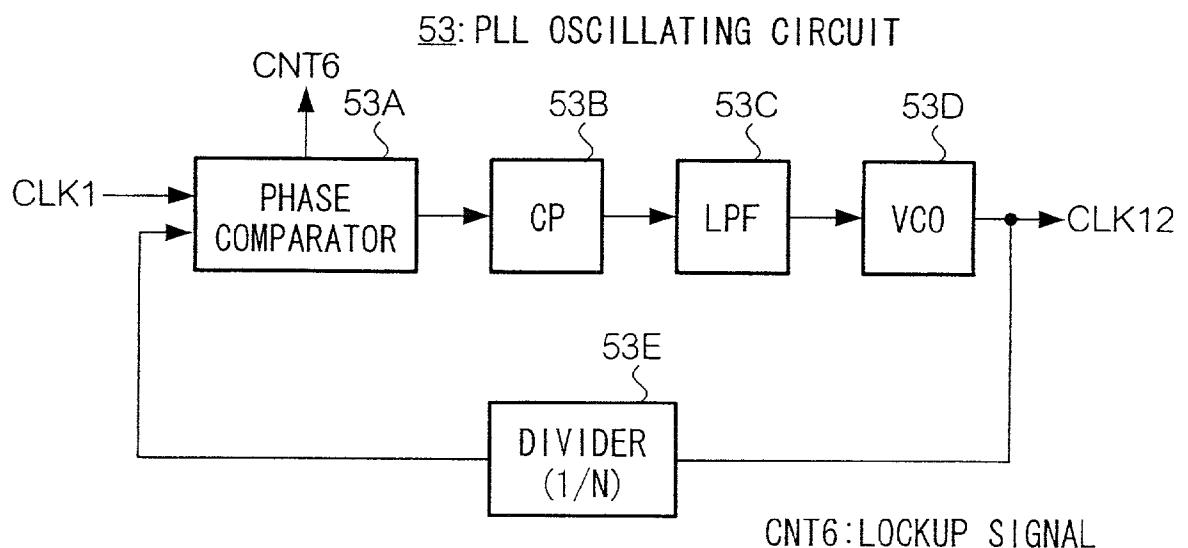

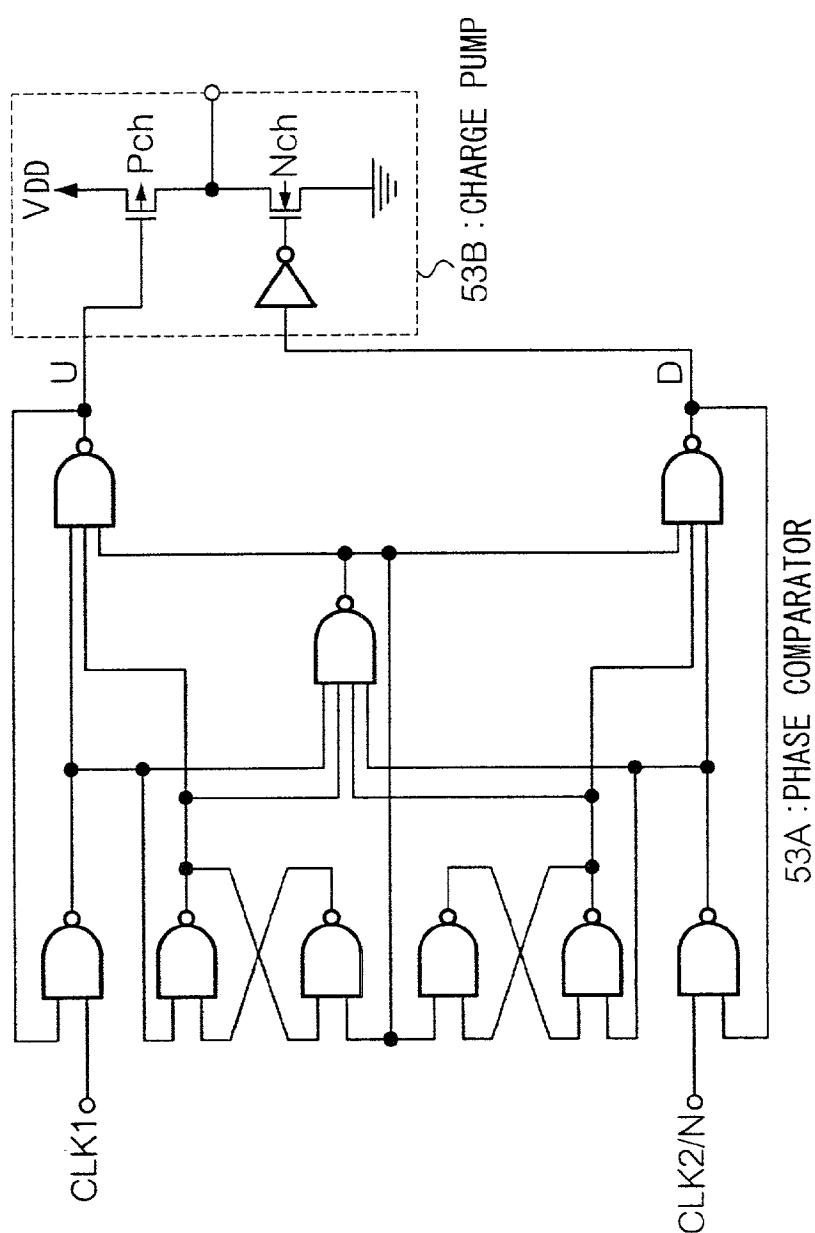

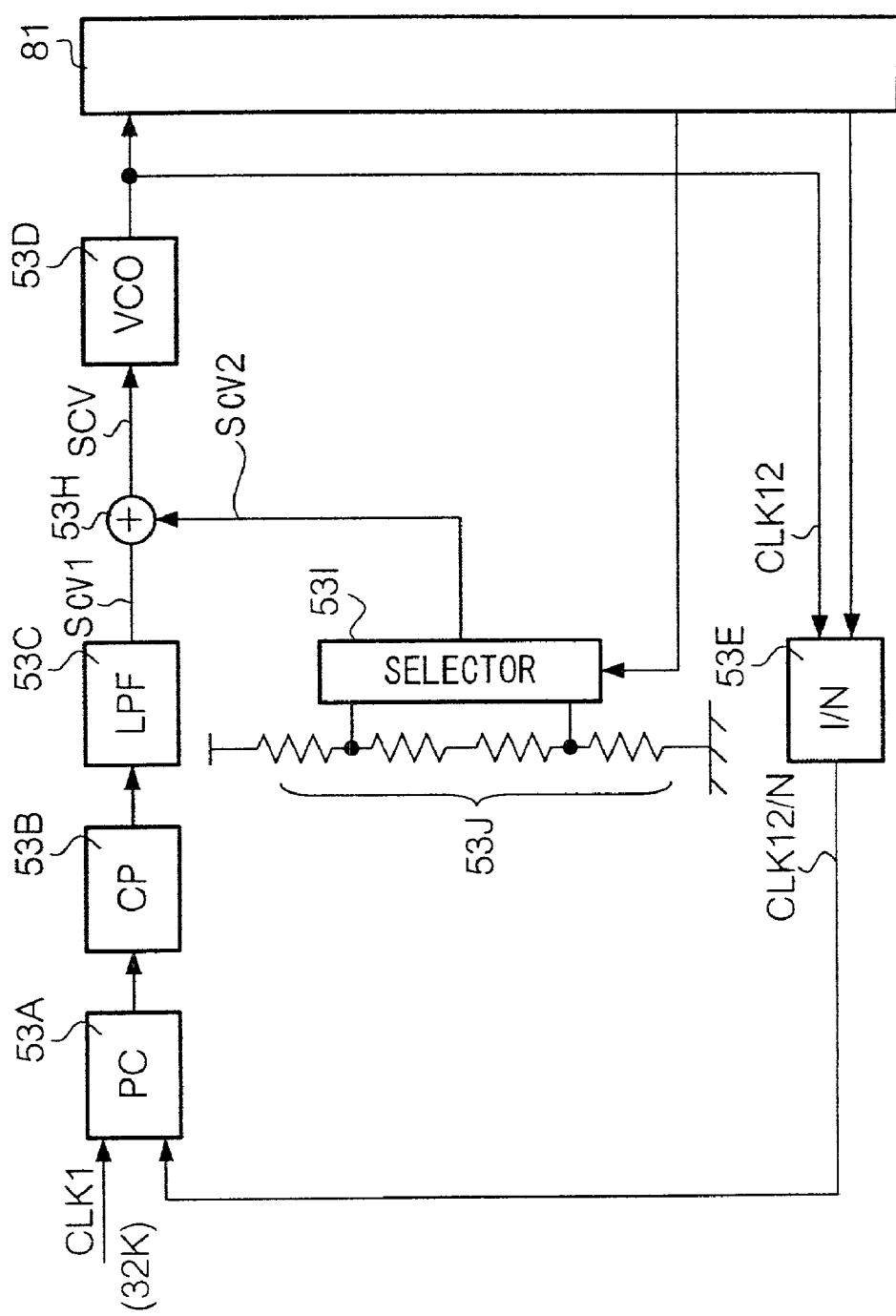

[0037] FIG. 12 is a detailed configuration diagram of the PLL oscillating circuit in the oscillator unit.

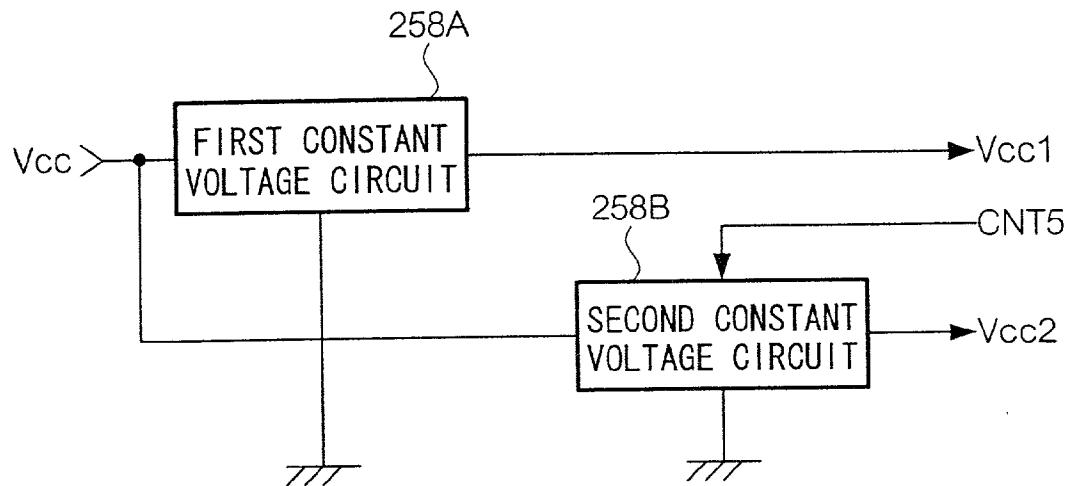

[0038] FIG. 13 is a detailed configuration block diagram of the voltage generating unit in the information processing apparatus.

[0039] FIG. 14 is a detailed configuration block diagram of the input information-processing unit in the information processing apparatus.

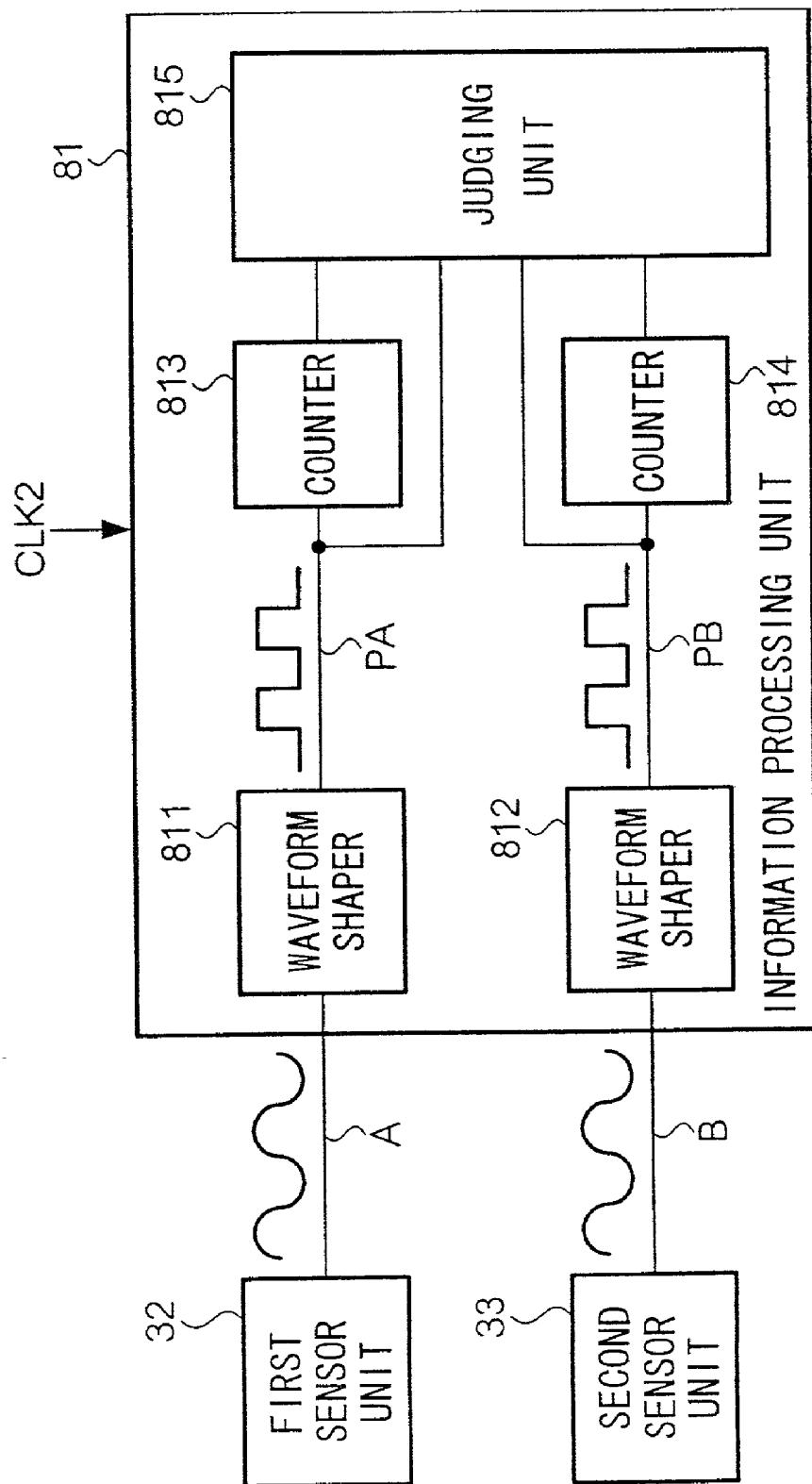

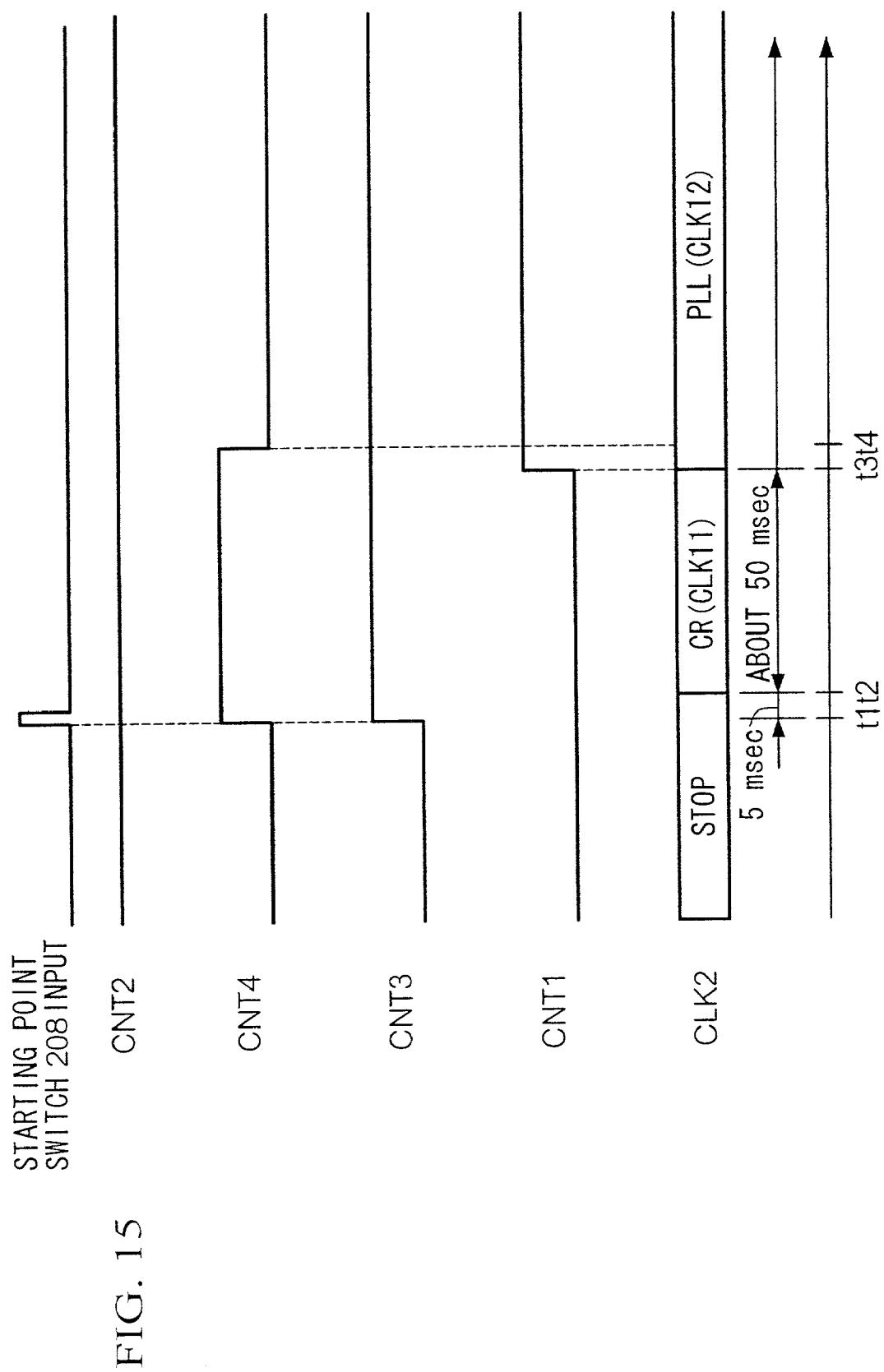

[0040] FIG. 15 is a processing timing chart showing time keeping operation and switching operation of the information processing apparatus.

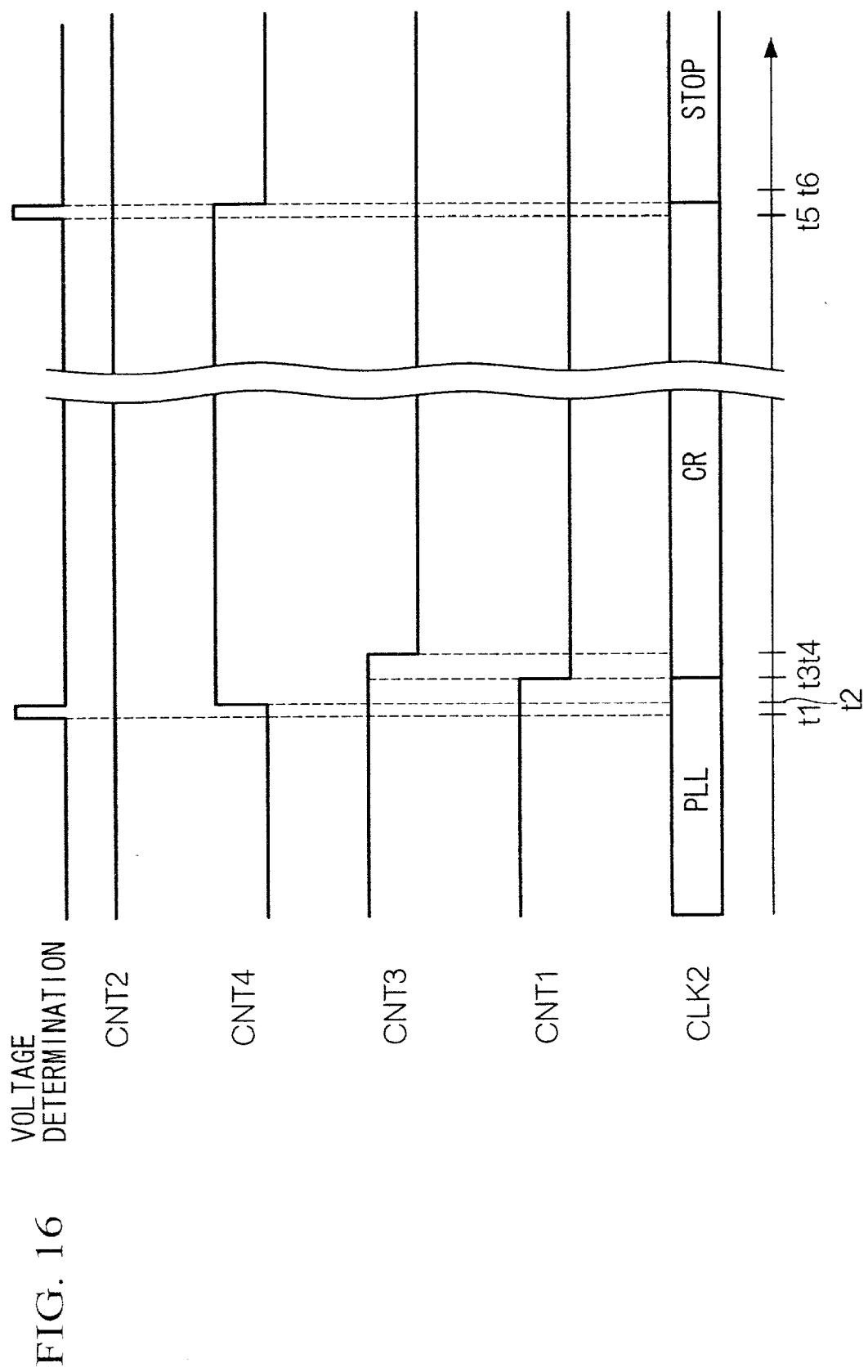

[0041] FIG. 16 is a processing timing chart showing operation of the information processing apparatus when power supply voltage declines.

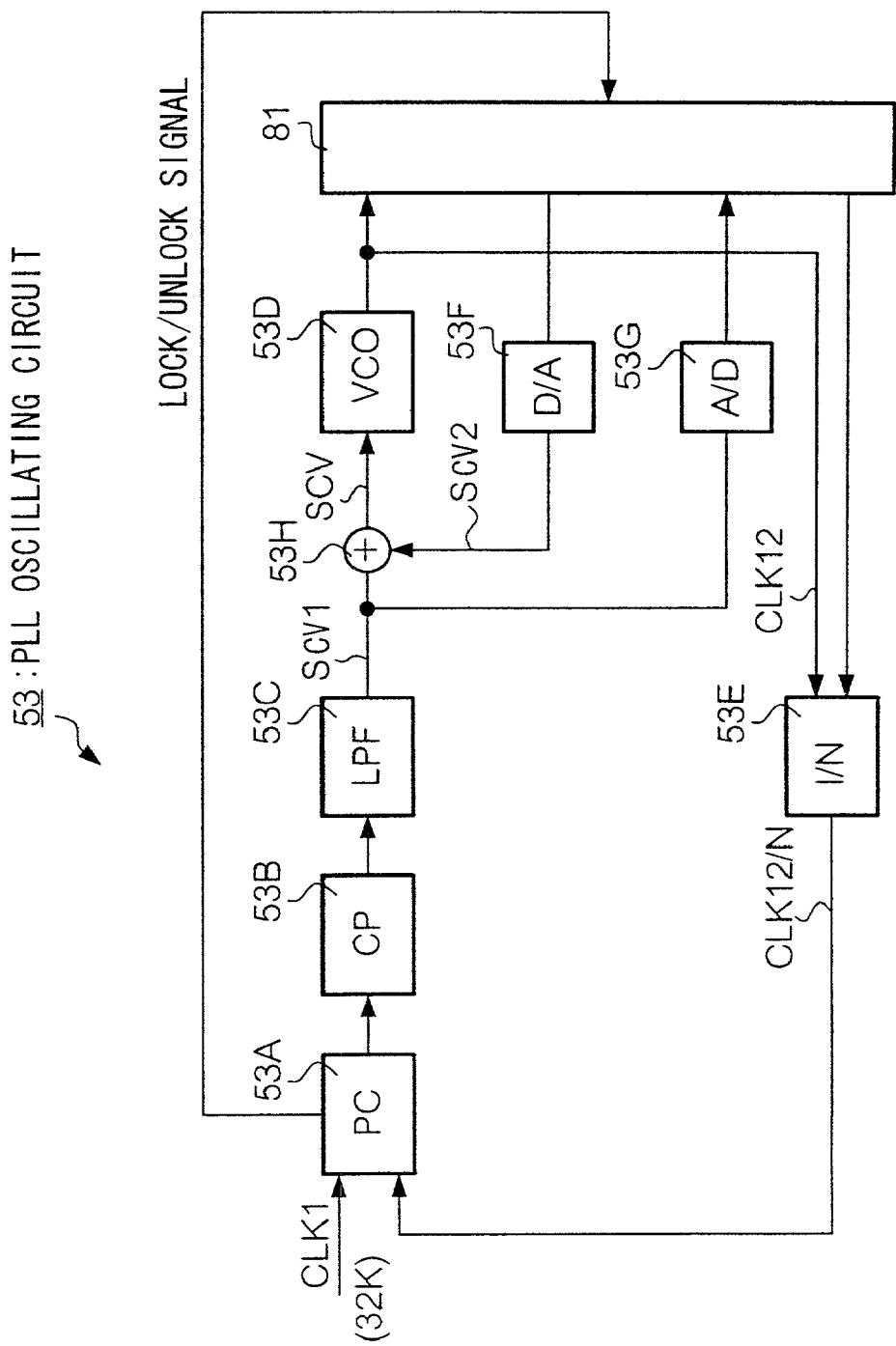

[0042] FIG. 17 is a schematic block diagram of a PLL oscillating circuit of the embodiment.

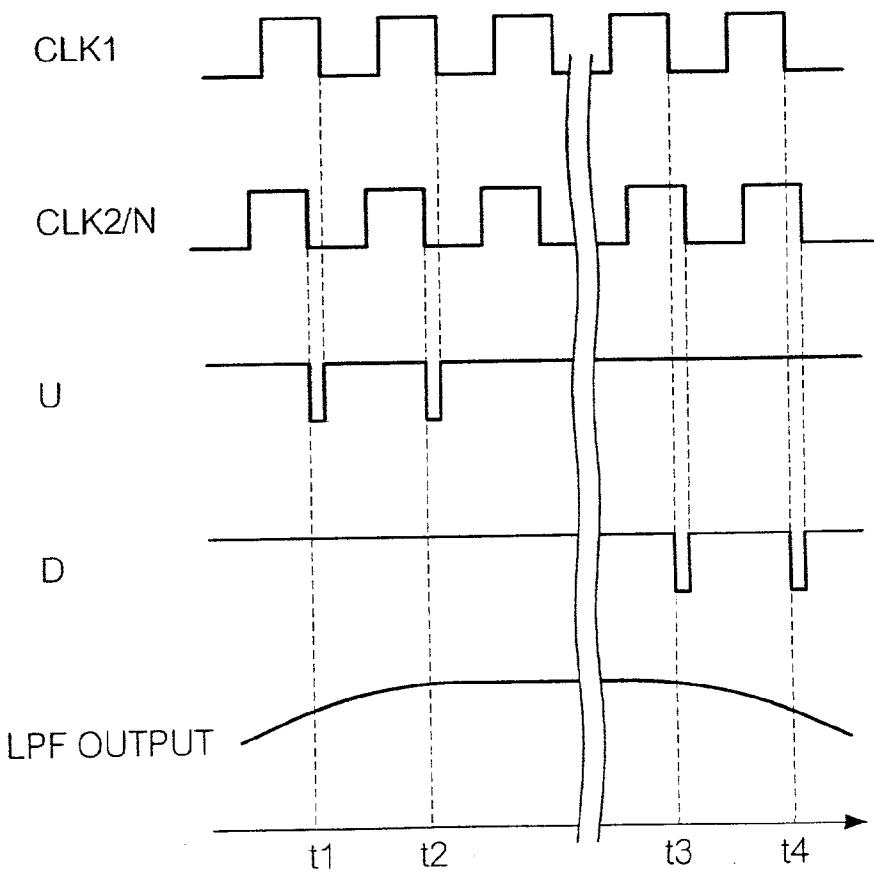

[0043] FIG. 18 is a detailed block diagram of a phase comparator and a charge pump that is connected to latter part of the PLL oscillating circuit.

[0044] FIG. 19 is a timing chart showing the operation of the phase comparator and the charge pump.

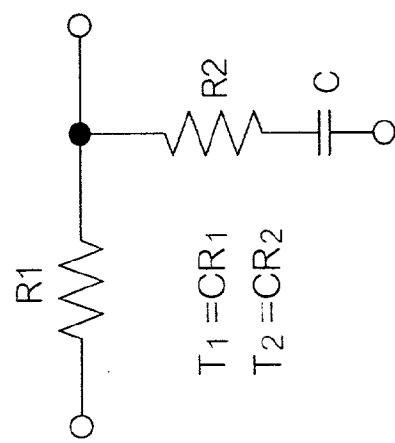

[0045] FIG. 20 is an explanatory diagram of the LPF.

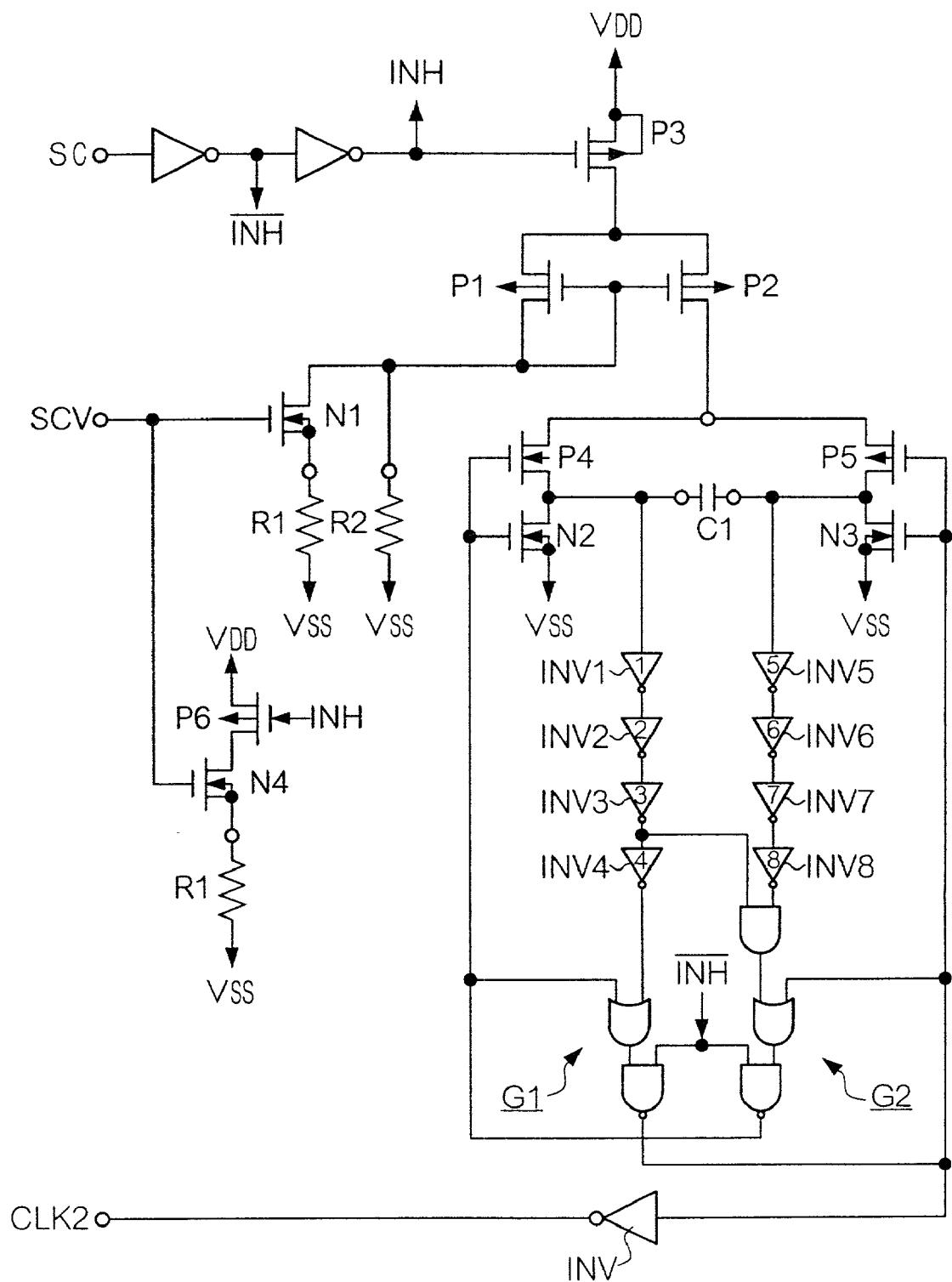

[0046] FIG. 21 is a detailed block diagram of the voltage controlled oscillator (VCO).

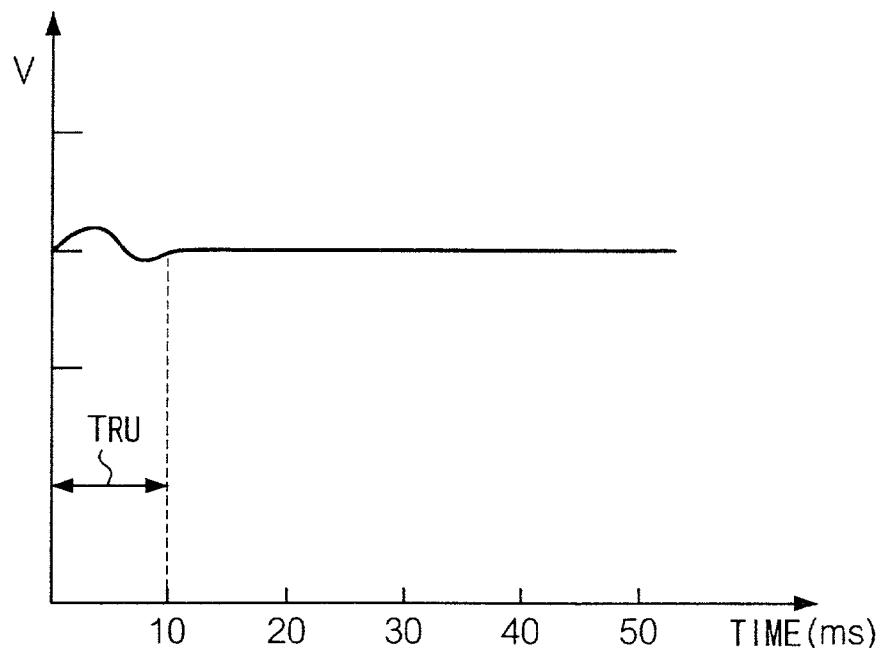

[0047] FIG. 22 is an explanatory diagram for the lockup time of the PLL oscillating circuit of the second embodiment.

[0048] FIG. 23 is an explanatory diagram for the lockup time of the conventional PLL oscillating circuit.

[0049] FIG. 24 is a schematic configuration block diagram of a modification of the second embodiment.

#### DETAILED DESCRIPTION

[0050] With reference to drawings, preferred embodiments of the present invention will be described below.

##### [1] First Embodiment

[0051] [1.1] Configuration of the First Embodiment

[0052] [1.1.1] Mechanical Configuration

[0053] FIG. 1 shows a plan view of a watch-type information processing apparatus and a station according to the first embodiment. In FIG. 1, a watch-type information processing apparatus 200 has a secondary battery as a power

source and receives power from the secondary battery, thereby able to function as a watch and an information processing apparatus. In more detail, the watch-type information processing apparatus 200, when used normal way, is worn on a user's wrist, displays date and time on a display section 204, and has an information-processing function that periodically measures and stores biological information such as pulse rate and heart rate by using sensor (not shown). The station 100 is a device used for charging the secondary battery of the watch-type information processing apparatus 200 and for data transferring with the watch-type information processing apparatus 200. The station 100 has a concave portion 101 which is slightly bigger than the body 201 and a band 202 of the watch-type information processing apparatus 200. The watch-type information processing apparatus 200 is embedded in the concave portion 101.

[0054] The station 100 comprises various input units such as a charge start button 1031 for starting the charging and a transfer start button 1032 for starting the data transferring, and a display unit 104 for carrying out various display.

[0055] FIG. 2 is a section view taken on line A-A in FIG. 1. As shown in FIG. 2, the underside of the body 201 of the watch-type information processing apparatus 200 is closed with a back cover 212. The watch-type information processing apparatus 200 is embedded in the station 100 in a manner by which the back cover 212 and the bottom of the concave portion 101 face each other. In a space inside the back cover of the body 201 is a circuit board 221 and the secondary battery 220 which provides the circuit on the circuit board 221 with power supply voltage. The back cover 212 has an opening which is closed by a cover glass 211. On the surface of the inner part of the cover glass 211, a watch-side coil 210 for data transferring and charging is placed.

[0056] On the other hand, at the bottom of the concave portion 101 of the station 100, there is space accommodating a circuit board 121. The board 121 is connected to the charge start button 103A, the transfer start button 103B, the display unit 104, and a primary battery (not shown). At the roof of the space is an opening which is closed with a cover glass 111. Inside the cover glass, a station-side coil 110 is fixed. The station-side coil 110 faces the watch-side coil 210 of the body through the cover glass 111 of the station 100 and the cover glass 211 of the body.

[0057] In this way, in a case where the watch-type information-processing apparatus 200 is placed in the station 100, the station-side coil 110 is not in physically contact with the watch-side coil 210 because of the cover glasses 111 and 211. However, the coils 110 and 210 are in electromagnetic contact with each other, because the coils are placed in almost parallel.

[0058] The station-side coil 110 and the watch-side coil 210 are of magnetic coreless type in order to avoid magnetization of the watch mechanism section, weight increase of the watch, and exposure of magnetic metal. However, if the invention is applied to an electronic apparatus to which the above matters are not important, coils with magnetic core may be used. However, when signal frequency provided to coil is high enough, a coreless coil works well enough.

[0059] FIG. 3 is a front view of a watch-type information processing apparatus. On the front side (on near side of the drawing sheet) of the body 201, a circle shaped turning bezel

202 is placed so that the turning bezel 202 can slide on the body 201. On the turning bezel 202, characters (such as alphabetic characters, Japanese syllabaries, and/or numeric characters) are placed at regular intervals by printing.

[0060] Inside the turning bezel 202, a cover glass 203 is attached. Below the cover glass 203 (on the far side of the drawing sheet), the display section 204 is fixed that displays information input to the watch-type information processing apparatus 200. On the upper side of the display section 204, an indicator mark 209 is formed by printing or the other method. The indicator mark 209 indicates one of the characters on the turning bezel 202. Around the body 201, a confirmation switch 205, a delete switch 206, a sonant mark switch 207, and a starting point switch 208 are built. These switches may be built on the cover glass 203.

[0061] FIG. 4 is a diagram that shows a state of the information processing apparatus 200 whose turning bezel 202 is removed. FIG. 5 is a section view taken on line IV-IV in FIG. 4. As shown in FIGS. 4 and 5, on the body 201, a gutter 34 is formed along the circle. On the other hand, as shown in FIG. 5, on the undersurface of the turning bezel 202 is formed a protrusive line 46 that protrudes towards inner side of the body. The protrusive line 46 is engaged to the gutter 34 in order to be able to slide. Between the right side of the turning bezel in FIG. 5 and the body 201, an O-ring 47 is built in. The O-ring 47 prevents water and light from entering the inner part of the watch-type information processing apparatus 200.

[0062] As shown in FIG. 4, holes 31a and 31b are formed on the body 201. In the holes 31a and 31b, a first sensor unit 32 and a second sensor unit 33 are placed respectively. In this case, the first sensor unit 32 and the second sensor unit 33 are placed so that the angle between the line from the rotation center O of the turning bezel 202 to the first sensor unit 32 and the line from the rotation center O of the turning bezel 202 to the second sensor unit 33 becomes  $\theta_1$ . Details of the angle  $\theta_1$  will be described later.

[0063] The first sensor unit 32 is placed under (far side of the drawing sheet of FIG. 4) a character indicated by the indicator mark 209 (in FIG. 4, the character is "A").

[0064] As shown in FIG. 5, on the undersurface of the turning bezel 202, optical pattern 41 is formed in a location that corresponds to character on the turning bezel 202. Below the surface where the optical pattern 41 is formed, a sensor cover glass 42 is attached to the body 201. Between the body 201 and the sensor cover glass 42, a packing 43 is put in. By this, it is possible to prevent water and other stuff from entering below the sensor cover glass 42.

[0065] Below the sensor cover glass 42, the first sensor unit 32 is placed. The first sensor unit 32 comprises an light emitting diode (LED) 44, a photodiode 45, a light blocking plate 44a which is placed between the LED 44 and the photodiode 45, and a base plate 48. The LED 44 emits a first detection light L1 to the optical pattern 41. The photodiode 45 receives reflected light. Based on the received first detection light L1, the first sensor unit 32 generates a first detection signal A.

[0066] The second sensor unit 33 comprises an LED, and a photodiode, a light blocking plate, and a base plate, those components being similar to those of the first sensor unit 32.

The LED emits a second detection light **L2** to the optical pattern **41**. The photodiode receives reflected light. Based on the received second detection light **L2**, the second sensor unit **33** generates a second detection signal **B**.

[0067] Below the base plate **48** of the first sensor unit **32**, a contact spring **49** is built. The contact spring **49** electrically connects the first sensor unit **32** and the second sensor unit **33** to a CPU of the watch-type information processing apparatus **200**. Instead of the contact spring **49**, lead wires may be used.

[0068] In this way, the first detection signal and the second detection signal **B** are counted by an information processing unit **81** shown in **FIG. 14** (which is later described). By this, rotation angle and rotation direction of the turning bezel **202** is determined.

#### [0069] [1.1.2] About Optical Pattern

[0070] Next, the optical pattern **41** will be described. **FIG. 6** is a diagram that shows the underside of the turning bezel **202**, the underside functions as a reflective member. As shown in **FIG. 6**, on the underside of the turning bezel **202**, the optical pattern **41** is formed along the circle line, the optical pattern **41** having an alternately repetitive pattern of an absorption region **41a** that absorbs light emitted by the LED **44** and a reflection region **41b** that reflects light emitted by the LED. In this case, a line segment that is from the rotation center **O** to the middle of either an absorption region **41a** or a reflection region **41b** makes an angle of  $\theta_2$  with a line segment that is from the middle of either a neighboring reflection region **41b** or a neighboring absorption region **41a** to the rotation center **O**.

[0071] In this case, if the number of characters formed on the turning bezel **202** is  $n$  ( $n$  is an even number),  $\theta_2 = 360/n(^{\circ})$

[0072] The first sensor unit **32**, when a user turns the turning bezel **202**, alternately reads the absorption region **41a** and the reflection region **41b** of the optical pattern shown in the part (a) of **FIG. 7**, thereby is able to generate the first detection signal **A** which has approximate sinewave form as shown in the part (c) of **FIG. 7**.

[0073] In the same way, the second sensor unit **33** generates the second detection signal **B** which has approximate sinewave form shown in the part (c) of **FIG. 7**.

[0074] In the above case, the absorption region **41a**, the reflection region **41b**, the first sensor unit **32**, and the second sensor unit **33** are placed so that the phase difference becomes a quarter of the wavelength as described later.

#### [0075] [1.1.3] Arrangement of Sensor Unit

[0076] Next, the angle  $\theta_2$  between the first sensor unit **32** and the second sensor unit **33** will be described.

[0077] In this embodiment, the first sensor unit **32** and the second sensor unit **33** are placed so that the angle  $\theta_1$  equals  $\theta_2$  plus  $\pi/2$ . By this, when a user turns the turning bezel **202**, a phase difference of a quarter of the wave length is produced between the first detection signal **A** generated by the first sensor unit **32** and the second detection signal **B** generated by the second sensor unit **33**.

[0078] As shown in **FIG. 7**, when a user turns the turning bezel **202** in a clockwise direction, the second detection signal has an advanced phase of one quarter of the wave-

length to the first detection signal. On the other hand, when a user turns the turning bezel **202** in a counterclockwise direction, the second detection signal has a phase delay of one quarter of the wavelength to the first detection signal. By detecting these phase advance and delay, it becomes possible to determine direction of rotation of the turning bezel **202** as described later.

#### [0079] [1.1.4] Schematic Configuration

[0080] Next, with reference to **FIG. 8**, schematic configuration of the watch-type information processing apparatus **200** will be described. On the circuit board **221** shown in **FIG. 2**, a micro-processing unit (MPU) **251**, an oscillating unit **252**, a charging and communication unit **253**, a flash memory **254**, an LCD driver **255**, an LCD **256**, an input output interface unit **257**, a voltage generating unit **258**, a voltage determining unit **259**, a RAM **260**, an input information processing unit **261** are placed, and a bus **262** is formed to connect the above components. The output voltage of the secondary battery **220** is provided to the voltage generator **258** and the voltage determining unit **259**.

[0081] The micro-processing unit **251** controls the entire watch-type information processing apparatus **200**. When performing this control, the micro processing unit **251** outputs control signals **CNT1**, **CNT2**, **CNT3**, and **CNT4** to the oscillating unit **252**.

[0082] The oscillating unit **252**, based on the control signals **CNT1** to **CNT4**, generates and outputs clock signals **CLK11** and **CLK12**.

[0083] The charging and communication unit **253** is provided with electric power from the station **100** via the watch-side coil **210**, and provides a charging current to the secondary battery **220**. The charging and communication unit **253** also performs data transmission and reception with the station **100** via the watch-side coil **210**.

[0084] The secondary battery **220** stores the charging current provided by the charging and communication unit **253**. The battery voltage is provided to various units as power supply voltage for operation.

[0085] The flash memory **254** is a non-volatile memory that stores displaying pattern data items for displaying various characters, and functions as a character generator.

[0086] The LCD driver **255**, under controls of the micro-processing unit **251**, displays various data items on the display **256**.

[0087] The input output interface unit **257** determines operating conditions of the confirmation switch **205**, the delete switch **206**, the sonant mark switch **207**, and the starting point switch **208**, and performs interface operation between the switches and the micro-processing unit **251**.

[0088] The voltage generating unit **258** receives the power supply voltage **VCC** from the secondary battery **220** and provides power supply voltage **VCC1** for a quartz crystal oscillating circuit and system power supply voltage **VCC2**.

[0089] The voltage determining unit **259** determines voltage of the power supply voltage **VCC** of the secondary battery.

[0090] The RAM **260** temporarily stores various data items.

[0091] The input information-processing unit 261 receives data items input with operation of the bezel 202 and performs data input processing. The data input processing is to provide the input data items to the MPU 251.

[0092] Next, explanations will be given of detailed configurations of the oscillating unit 252, the voltage generating unit 258, and the input information-processing unit 261.

[0093] FIG. 9 is a detailed configuration block diagram of the oscillating unit. The oscillating unit 252 comprises a quartz crystal oscillating circuit 51, a CR oscillating circuit 52, a PLL oscillating circuit 53, and a selector 54.

[0094] The quartz crystal oscillating circuit 51 is a low-speed oscillating circuit and, by receiving the control signal CNT2 and power supply voltage VCC1 for the quartz crystal oscillating circuit, outputs a clock signal CLK1 having low frequency (for example 32 kHz) for time keeping.

[0095] The CR oscillating circuit 52 is a first high-speed oscillating circuit, based on the control signal CNT3, outputs a clock signal CLK11 having high frequency (for example from 1 MHz to 8 MHz) for information processing.

[0096] The PLL oscillating circuit 53 is a second high-speed oscillating circuit, based on the control signal CNT4, outputs a clock signal CLK12 having high frequency (for example from 4 MHz to 16 MHz) for information processing.

[0097] The selector 54, based on the control signal CNT1 from the information processing unit 81 (which is described later), selects either the CR oscillating circuit 52 or the PLL oscillating circuit 53 and outputs the output signal of the selected circuit as a clock signal CLK2.

[0098] In the above case, the clock signal CLK1 from the quartz crystal oscillating circuit 51 is used for time keeping, and the clock signal CLK2 is used for information processing by the information processing unit 81 (which is described later).

[0099] Here, explanation will be given of the configurations of the quartz crystal oscillating circuit 51, the CR oscillating circuit 52, and the PLL oscillating circuit 53.

[0100] The configuration of the quartz crystal oscillating circuit 51 is shown in FIG. 10. The quartz crystal oscillating circuit 51 comprises a first inverter circuit 51E. Between the input terminal and the output terminal of the inverter circuit 51 are connected a quartz oscillator 51A and a resistor 51B in parallel with the first inverter circuit 51E. The quartz oscillator 51A has an oscillating frequency of 32 kHz. The input terminal of the first inverter circuit 51E is connected to the lower voltage side power source (GND) via a capacitor 51C. The output terminal of the first inverter circuit 51E is connected to the lower voltage side power source (GND) via a capacitor 51D. A second inverter circuit 51F amplifies the output signal of the first inverter circuit 51E and outputs the clock signal CLK1 having a frequency of 32 kHz.

[0101] The CR oscillating circuit 52 is shown in FIG. 11. The CR oscillating circuit 52 comprises a first inverter circuit 52B, a second inverter circuit 52C, and a third inverter circuit 52E which are connected in cascade. Between the input terminal and the output terminal of the inverter 52B, a feedback resistor 52A is connected. Between the input terminal of the inverter 52B and the output terminal

of the inverter 52C, a capacitor 52D is connected. The third inverter circuit 52E receives the oscillating signal from the second inverter circuit 52C, amplifies it, and outputs it as clock signal CLK11.

[0102] The PLL oscillating circuit 53 is shown in FIG. 12. The PLL oscillating circuit 53 has a looping formation circuit which is formed by a phase comparator 53A, a charge pump 53B, a low pass filter (LPF) 53C, a voltage controlled oscillator (VCO) 53D, and a divider 53E. The phase comparator 53A compares a phase of the clock signal CLK1 and a phase of the output signal of the divider 53E, and outputs an output signal corresponding to phase difference between them. The charge pump 53B introduces a current into the LPF 53C in response to the output signal of the phase comparator 53A. The LPF 53C selects only lower frequency component of the output signal of the charge pump 53B, and outputs it as a voltage control signal. The VCO 53D oscillates in a frequency corresponding to the voltage control signal output from the LPF 53C, and outputs the clock signal CLK12. The divider 53E divides the frequency of the clock signal CLK12 into an Nth of its frequency.

[0103] In the above configuration, when there is a phase difference between the incoming clock signal CLK1 and the output signal of the divider 53E, synchronization establishment is carried so as to reduce the phase difference and make the output signal of the divider 53E phase-locked with the clock signal CLK1. When the synchronization is established and a state of the PLL oscillating circuit reaches a synchronization maintained state where the output signal of the divider 53E is kept to be in phase-locked with the clock CLK1, the phase comparator 53A outputs a lock-up signal CNT6 having the "H" level indicating the above information.

[0104] Here, advantages and disadvantages of CR oscillating circuits and PLL oscillating circuits will be explained.

[0105] CR oscillating circuits require about four times more power consumption than PLL oscillating circuits do, but the waiting time for constant oscillation of CR oscillating circuits is shorter than that of PLL oscillating circuits. For example, the waiting time for constant oscillation of CR oscillating circuits is about 5 msec. CR oscillating circuits, when used under its upper limited frequency of 1 MHz, is operable at a voltage that is lower than a lower limited voltage for the operation of PLL oscillating circuits (for example until as low as 1.5 V). Hereinafter, for the sake of convenience, a waiting time for constant oscillation of CR oscillating circuits is referred to as a first oscillation stability time, and a lowest limited operating voltage as a first lowest operating voltage.

[0106] On the other hand, PLL oscillating circuits are able to oscillate until at a considerably high frequency with low power consumption. However, PLL oscillating circuits have a long waiting time for constant oscillation (for example 50 msec), and its lowest operating limited voltage is high (for example 2 V). Hereinafter, for the sake of convenience, a waiting time for constant oscillation of PLL oscillating circuits is referred to as a second oscillation stability time, and a lowest limited operating voltage as a second lowest operating voltage.

[0107] Therefore, CR oscillating circuits and PLL oscillating circuits have their merits and demerits. In this embodiment,

ment, by combining advantages of each oscillating circuits, a high-speed oscillating circuit with low power consumption, low operating voltage, and short waiting time for constant oscillation is achieved.

[0108] The voltage generating unit 258, as shown in FIG. 13, comprises a first constant voltage circuit 258A and a second constant voltage circuit 258B. The first constant voltage circuit 258A generates power supply voltage VCC1 for the quartz crystal oscillating circuit from the power supply voltage VCC. The second constant voltage circuit 258B is controlled by the control signal CNT5 and generates the system power supply voltage VCC2 from the power supply voltage VCC.

[0109] Next, with reference to FIG. 14, detail of the input information-processing unit 261 will be described. The input information processing unit 261 comprises the information processing unit 81 which has a counter 813 for counting the number of pulses of the first detection signal A from the first sensor unit 32 and a counter 814 for counting the number of pulses of the second detection signal B from the second sensor unit 33. The first detection signal A and the second detection signal B are changed into detection pulse signals PA and PB by waveform shapers 811 and 812 respectively. These pulses are input to the counters 813 and 814. The input information-processing unit 261 also comprises a judging unit 815 for determining direction of rotational and location of the turning bezel 202 based on the counted values of the counters 813 and 814 and detection pulse signals PA and PB. In this case, the judging unit 815 judges direction of rotation based on, for example, level ("H" or "L") of the detection pulse signal PB at positive edge of the detection pulse signal PA.

[0110] The input information processing unit 261, based on the first detection signal A generated by the first sensor unit 32 and the second detection signal B generated by the second sensor unit 33, generates information data and stores the information data confirmed by a user into the RAM 260.

[0111] In the above case, the information-processing unit 81, by referring to information table on the flash memory 254 generates an information signal. The flash memory 254 stores conversion tables: one of the conversion table is used for converting the output data of the judging unit 815 into a code of character designated by the turning bezel, and one other conversion tables is used for converting the output of the judging unit 815 into a code of image data of the character designated by the turning bezel 202. The flash memory also stores information items corresponding to a location of the turning bezel 202. Based on the information signal, and by using the character generator in the flash memory 254, the LCD driver 255 displays characters and other information on the LCD 256.

[0112] In addition, the information processing unit 81 can process following processing.

[0113] For example, document files made on other personal computer may be transmitted to the apparatus via the charging and communication unit 253 and the station 100, then displayed on the LCD 256.

[0114] When a simple operating system (OS) is installed in the information processing unit 81, simple application programs can be made for the OS. Creatable application programs are for example schedule managing program and

address data managing program. Further, importing and exporting data such as scheduling data and address data from other personal computer can be possible. Data processing such as data addition, data deletion, or data sorting can be possible.

[0115] Next, roles of the starting point switch 208, the confirmation switch 205, the delete switch 206, and the sonant mark switch 207 will be described.

[0116] The starting point switch 208 is a switch that changes the watch-type information processing apparatus into a state of an information input. When the switch 208 is turned on, the counter for the number of pulses in the unit 81 is reset to "0" and the judging unit 815 starts measuring rotation angle and direction of the turning bezel 202 using the first sensor unit 32 and the second sensor unit 33.

[0117] The confirmation switch 205 and the delete switch 206 are used for confirmation and deletion of the information items generated by the information-processing unit 82.

[0118] The sonant mark switch 207 is used for adding a sonant mark when the generated information item by the information-processing unit 81 is a Japanese syllabary and requires a sonant mark. When the generated character is an alphabetic character, the switch 207 is used for switching the character between a capital letter and a small letter.

[0119] The information items generated by the information-processing unit 81 are not limited to character. Instruction codes for such as line feed and mode switching (for example, between time display mode and character input mode) may also be generated by the information processing unit 81. In this case, the information table on the flash memory 254 stores instruction codes for such as line feed and mode switching with correspondence with location of the turning bezel 202. Based on location of the turning bezel 202, the information-processing unit 81 generates instruction codes.

[0120] [1.2] Operation of the Information Processing Unit and the Oscillating Circuit

[0121] Here, by paying an attention to operations of the information-processing unit 81 and the oscillating circuits 51, 51, and 53, an explanation will be given. FIG. 15 is a processing timing chart during time keeping operation and switching operation to information processing.

[0122] [1.2.1] Operation During Time Keeping

[0123] In an initial state, the control signal CNT2 output from the micro-processing unit 251 has the "H" level. The quartz crystal oscillating circuit 51 is in an operating state and outputs the clock signal CLK1 to the information-processing unit 81. The control signal CNT1 has the "L" level. Thereby, the selector 54 selects the CR oscillating circuit 52.

[0124] By this, the information-processing unit 81, based on the clock signal CLK1, performs time keeping operation and displays time on the display unit 104.

[0125] While the information processing unit 81 displays time, the control signals CNT3 and CNT4 have the "L" level, and the CR oscillating circuit 52 and the PLL oscillating circuit 53 are in an inoperative state or a standby state.

[0126] [1.2.2] Shift to the Information Processing Operation

[0127] At time  $t_1$  in FIG. 15, the starting point switch 208 is used and a starting point signal becomes the "H" level. By this, the information-processing unit 81 is switched from time keeping operation to information processing operation.

[0128] By this, the micro processing unit 251 makes the control signals CNT3 and CNT4 to the "H" level so that the CR oscillating circuit 52 and the PLL oscillating circuit 53 start oscillating. In this case, an early stage oscillation stabilization frequency of the CR oscillating circuit 52 is about 1 MHz, and an early stage oscillation stabilization frequency of the PLL oscillating circuit 53 is about 4 MHz.

[0129] By this, the state of the CR oscillating circuit 52 gradually shifts to an oscillation stable state. In the above case, at time  $t_2$  which is 5 msec after beginning of oscillation, the CR oscillating circuit 52 is in an oscillation stable state. The information-processing unit 81 starts its operation using the clock signal CLK12 as the clock signal CLK2.

[0130] On the other hand, at time  $t_2$  (a first oscillation stability time elapsed point: 5 msec elapsed point), the PLL oscillating circuit 53 is in an oscillation non-stable state.

[0131] Subsequently, oscillation frequency of the CR oscillating circuit 52 gradually increases, resulting in around 4 MHz.

[0132] At time  $t_3$  (a second oscillation stability time elapsed point) where 50 msec has elapsed since the time  $t_2$ , the PLL oscillating circuit 53 also enters an oscillation stable state, where oscillation frequency is also around 4 MHz.

[0133] Therefore, the micro-processing unit 251 makes the control signal to the "H" level and changes the selection of the selector 54 to the PLL oscillating circuit 53.

[0134] After this, the information-processing unit 81 operates using the clock signal CLK 12 as the clock CLK2.

[0135] Further, at time  $t_4$ , the micro-processing unit 251 makes the control signal CNT4 to the "L" level and stops oscillation of the CR circuit 52.

[0136] Subsequently, the micro-processing unit 251 gradually raises oscillation frequency of the PLL oscillating circuit 53. By this, the watch-type information apparatus works at a desired high-speed frequency (for example 12 MHz, but in this embodiment 16 MHz).

[0137] [1.2.3] Operation During Declining of the Power Supply Voltage

[0138] FIG. 16 is a processing timing chart when power supply voltage declines. The information-processing unit 81, in a case where information processing is performed in a steady state, uses the clock signal CLK12 which corresponds to oscillation frequency of the PLL oscillating circuit 53 as the clock signal CLK2 as mentioned above.

[0139] However, there can be a case where the declining of the power supply voltage stops the operation of the PLL oscillating circuit 53. That is, when the power supply voltage becomes lower than the second lowest operating voltage, the PLL oscillating circuit 53 cannot operate properly.

[0140] Therefore, the MPU 251, based on the result of the voltage determining unit 259, when the power supply volt-

age declines to a voltage which is higher or equal to the first lowest operating voltage and lower than the second lowest operating voltage, selects the CR oscillating circuit 52. When the power supply voltage further declines to lower than the first lowest operating voltage, the information-processing unit 81 is stopped.

[0141] It is assumed that, in this case, the voltage determining unit 259 determines voltage, for example, every hour on the hour.

[0142] To be concrete, at time  $t_1$  in FIG. 16, the voltage determining unit 259 determines voltage of the secondary battery 220. When the voltage reaches a prescribed switching voltage (for example, in the above case, about 2.2 V), the micro-processing unit 251 starts the CR oscillating circuit 52 by making the control signal CNT4 to the "H" level at time  $t_2$ .

[0143] The micro-processing unit 251 gradually lowers oscillation frequency of the PLL oscillating circuit 53 to around 4 MHz.

[0144] At time  $t_3$ , oscillation frequency of the CR oscillating circuit 52 has already reached 4 MHz. Therefore, the micro-processing unit 251 makes the control signal CNT1 to the "L" level and changes the selection of the selector 54 to the CR oscillating circuit 52.

[0145] Therefore, after this, the information-processing unit 81 operates using the clock signal CLK11 as the clock CLK2. It becomes possible to perform information processing operation until power supply voltage declines to around 1.5 V which is the lowest operating voltage of the CR oscillating circuit 52.

[0146] Further, at time  $t_4$ , the micro-processing unit 251 makes the control signal CNT3 to the "L" level and stops oscillation of the PLL circuit 53.

[0147] Subsequently, the voltage determining unit 259 measures voltage of the secondary battery 220. When the voltage of the secondary battery 220 reaches around 1.5 V which is the lowest operating voltage of the CR oscillating circuit 52, the micro-processing unit 251 notifies this to the user. By this, the micro processing unit 251 urges the user to charge secondary battery or change battery.

[0148] Further, at time  $t_5$  when the voltage determining unit 259 measures voltage of the secondary battery 220, if power supply voltage is lower than 1.5 V, the MPU 251 makes the control signal CNT4 to the "L" level and stops oscillation of the CR oscillating circuit 52 at time  $t_6$ .

[0149] As a result, the information processing unit 81 stops information processing operation and continues to performs time keeping operation until power supply voltage becomes the lowest operating voltage of the quartz crystal oscillating circuit 51 of around 1 V.

[0150] [1.3] Effect of the First Embodiment

[0151] As described above, according to the first embodiment of the present invention, by using CR oscillating circuit and PLL oscillating circuit selectively, it becomes possible to provide a low power-consumption, short waiting-time for stable oscillation, low operating voltage information-processing apparatus.

[0152] In addition, so far, when using software which places a significant burden on the overall performance of the operation such as browser, high-speed clock is required in order to use it without frustration. In this embodiment, by using CR oscillating circuit, when battery voltage declines and PLL oscillating circuit becomes unable to operate, although speed of display becomes slow, displaying is not impossible, and even in very low voltage it becomes possible to continue to display.

[0153] In addition, it becomes possible to start application software from time keeping operation.

[0154] Further, when battery voltage declines considerably, it is possible to operate information-processing unit, thus enabling using application software in a very low battery voltage.

## [2] Second Embodiment

[0155] As described in the explanation for the first embodiment above, PLL oscillating circuit operates at low power consumption even at high frequency, but requires long waiting time for stable oscillation.

[0156] In order to avoid this, following measures are used in conventional PLL oscillating circuit.

[0157] (1) Using two low pass filters (LPF); when starting to use PLL oscillating circuit LPF with small time constant is used, and when oscillation becomes stable LPF with large time constant is used.

[0158] (2) Using two low pass filters (LPF); when one LPF is used, the other LPF is prepared to lock up with other frequency.

[0159] (3) When PLL oscillating circuit has a charge pump for analog/digital conversion of the output signal of phase comparator, increasing a control current for charge pump at starting up PLL oscillating circuit.

[0160] Measures (1) and (2) cannot make lock-up time to zero, and measure (3) makes device configuration complicated and circuit bigger.

[0161] Accordingly, a second embodiment provides shorter lock-up time than the PLL oscillating circuit of the first embodiment does, enabling to shift to higher frequency operation in information processing operation.

[0162] In the following explanation, configuration except PLL oscillating circuit is the same as that of the first embodiment, so mainly PLL oscillating circuit will be described.

[0163] [2.1] Schematic Configuration of the PLL Oscillating Circuit

[0164] A PLL oscillating circuit **53**, as shown in FIG. 17, comprises a phase comparator **53A**, a charge pump **53B**, an LPF **53C**, a voltage controlled oscillator (VCO) **53D**, a D/A converter **53F**, a divider **53E**, an A/D converter **53G**, and an adder **53H**.

[0165] The phase comparator **53A** compares phase of the clock signal CLK1 and phase of the output signal of the divider **53E** and outputs a digital output signal that corresponds to phase difference.

[0166] The charge pump **53B**, based on the output signal of the phase comparator **53A**, outputs a difference voltage that is proportional to the phase difference (frequency difference) of the clock signal CLK1 and a comparison clock signal CLK12/N.

[0167] The LPF **53C** passes only low frequency component of the output signal of the charge pump **53B** and outputs it as a voltage control signal SCV1.

[0168] The VCO **53D**, based on the voltage control signal SCV output from the adder **53H**, controls oscillation frequency of the clock signal CLK12 and outputs it to the divider **53E**.

[0169] The D/A converter **53F** converts a digital signal from the information-processing unit **81** into an offset voltage signal SCV2. The adder **53H** adds the voltage control signal SCV1 to the clock control signal CLK12 to generate the voltage control signal SCV.

[0170] The divider **53E** divides frequency of the clock signal CLK12 into an Nth of its frequency and outputs it to the phase comparator **53A** as a comparison clock signal CLK12/N.

[0171] The A/D converter **53G** A/D converts the output voltage of the LPF **53C** into digital data indicating the output voltage and outputs it to the information-processing unit **81** when the PLL oscillating circuit is locked during examination.

[0172] [2.2] Detailed Configuration of the PLL Oscillating Circuit

[0173] [2.2.1] Phase Comparator and Charge Pump

[0174] FIG. 18 is a detailed block diagram of a phase comparator and a charge pump that is connected to latter part of the PLL oscillating circuit.

[0175] Circuit configurations of the phase comparator **53A** and the charge pump **53B** will not be described in detail since they are widely known. With reference to a timing chart of FIG. 19, operations of these two circuits will be described.

[0176] In the timing chart of the FIG. 19, an output signal U becomes the "L" level when the phase of the comparison clock signal CLK12/N is advanced to that of the clock signal CLK1 or when the frequency of the clock signal CLK12/N is higher than that of the clock signal CLK1. The comparison clock signal CLK12/N is a clock signal obtained by frequency dividing of the clock signal CLK12.

[0177] The output signal D becomes the "L" level when the phase of the comparison clock signal CLK12/N is delayed to that of the clock signal CLK1 or when the frequency of the clock signal CLK12/N is lower than that of the clock signal CLK1.

[0178] When the phase of the comparison clock signal CLK12/N is equal to the phase of the clock signal CLK1 at the rising timing, the both output signals U and D become the "H" level. This state corresponds to a so-called locked state of the PLL oscillating circuit **53**.

[0179] At this state, both a p-channel transistor and an n-channel MOS transistor that comprise the charge pump **53B** become the OFF state, and the output of the charge pump **53B** is put in a high impedance state.

[0180] On the other hand, at time  $t_1$  and  $t_2$  as shown in a timing chart in **FIG. 19**, in a case where the phase of the comparison clock signal CLK12/N is advanced to the phase of the clock CLK1, or where the frequency of the clock signal CLK12 is higher than that of the clock signal CLK1, the output signal U becomes the “L” level during the time interval between the negative edge of the clock signal CLK12/N and the negative edge of the clock signal CLK1. The time interval is proportional to the phase difference or the frequency difference. At this time, the output signal D remains the “H” level.

[0181] In the same way, at time  $t_3$  and  $t_4$  in **FIG. 19**, in a case where the phase of the comparison clock signal CLK12/N is delayed to the phase of the clock CLK1, or where the frequency of the clock signal CLK12 is lower than that of the clock signal CLK1, the output signal D becomes the “L” level during a time period corresponding to the phase difference or the frequency difference. At this time, the output signal U remains the “H” level.

[0182] When these output signals U and D is output from the phase comparator **53A** to the charge pump **53B**, a p-channel transistor becomes ON only while the output signal U has the “L” level, and an n-channel MOS transistor becomes ON only while the output signal D has the “L” level.

[0183] Therefore, the LPF **53C** that is connected to following stage of the charge pump **53B** outputs a direct current voltage corresponding to the phase difference (frequency difference) between the clock signal CLK1 and the comparison clock signal CLK12/N (see **FIG. 19**).

[0184] The above description is about CMOS configured phase comparator. However, the above description may be applied to a bipolar configured phase comparator.

#### [0185] [2.2.2] LPF

[0186] **FIG. 20** shows a detailed configuration of the LPF, and equations of natural angular frequency and dumping factor of the LPF. The LPF **53C** shown in **FIG. 20** is a so-called lag-lead filter, so the LPF **53C** is a conventional LPF. From a viewpoint of operating speed, the LPF **53C** is worse than an active filter with an amplifier, but has enough usefulness when configured in CMOS circuit. When PLL IC is configured with an LPF of CMOS circuit, lockup time can be reduced to around 10 msec.

[0187] In the above case, the natural angular frequency  $\omega_n$  and the dumping factor  $\zeta$  are shown as follows:

$$\begin{aligned}\omega_n &= \sqrt{K_p K_v / (T_1 + T_2) \cdot N} \\ \zeta &= \omega_n / 2 \cdot (T_2 + N / K_p K_v)\end{aligned}$$

[0188] Variables in the above equations are as follows:

[0189]  $K_p$ : gain constant of the phase comparator (V/rad)

[0190]  $K_v$ : gain constant of the voltage controlled oscillator (rad/sec/V)

[0191]  $N$  : divisor of the divider

#### [0192] [2.2.3] Voltage Controlled Oscillator

[0193] **FIG. 21** shows a detailed configuration of voltage controlled oscillator constructed with CMOS. Since the circuit configuration of the voltage controlled oscillator in

**FIG. 21** is widely known, explanation of its configuration will be omitted, and only operation will be described.

[0194] The voltage controlled oscillator **53D** is constructed with CMOS, so input impedance is high and the degree of design freedom of the LPF **53C**, the preceding circuit, increases.

[0195] In **FIG. 21**, when the control signal SC has the “H” level, the p-channel transistor **P3** becomes OFF, thus enabling to stop oscillation.

[0196] When the control signal SC has the “L” level, the voltage controlled oscillator **53D** becomes operating state, and since an n-channel transistor **N1** is constructed in a source follower configuration, if a resistor **R1** has high resistance enough, the drain current of the n-channel transistor **N1** changes in linear relation with the voltage control signal SCV.

[0197] Therefore, currents of the p-channel MOS transistors **P1** and **P2** change in the same manner. As a result, drain currents of the p-channel MOS transistors **P1** and **P2** changes in linear relation with the voltage control signal SCV.

[0198] On the other hand, gates **G1** and **G2** construct a flip-flop circuit, and a p-channel transistor **P4**, an n-channel transistor **N2**, a p-channel transistor **P5**, and an n-channel transistor **N3** work as switches.

[0199] When the output of the gate **G1** has the “L” level, the output if the gate **G2** has the “H” level, the p-channel transistor **P5** and the n-channel transistor **N2** are in ON state, and the p-channel transistor **P4** and the n-channel transistor **N3** are in OFF state.

[0200] Therefore, the input of the inverter **INV** becomes the lower side power supply voltage **VSS**, and electrical potential at the input terminal of the inverter **INV5** rises because the capacitor **C1** is charged by drain current of the p-channel transistors **P2** and **P5**. Further, when output signal levels of the inverter **INV5** to **INV8** is reversed, outputs of the gate **G1** and **G2** that comprise a flipflop circuit are reversed.

[0201] Next, output of the gate **G1** becomes the “H” level, output of the gate **G2** becomes the “L” level, the p-channel transistor **P5** and the N-channel transistor **N2** become to OFF state, and the p-channel transistor **P4** and the n-channel transistor **N3** become to ON state. Therefore, the capacitor **C1** is charged by drain current of the p-channel transistor **P2** and **P4**. Then electrical potential at the input terminal of the inverter **INV1** rises. Then, the output level of the inverters **INV1** to **INV4** is reversed. The same operation repeats after this.

[0202] In this case, the charging current of the capacitor **C1** can be controlled by voltage of the voltage control signal SCV. Therefore, frequency of the clock signal CLK12 is changeable.

[0203] [2.3] Operation of the Information Processing Unit and the Oscillating Circuit

[0204] Here, operations of the information-processing unit **81**, the CR oscillating circuit **52**, and a PLL oscillating circuit **53** will be described.

[0205] [2.3.1] Operation During Keeping Time

[0206] When the information-processing unit 81 displays time, as mentioned above for the first embodiment, the PLL oscillating circuit 53 is in an inoperative state or a standby state under a control of the micro processing unit 259.

[0207] By this, the information-processing unit 81, based on the clock signal CLK1, carries out time keeping operation and displays time on the display unit 204.

[0208] [2.3.2] Shift to the Information Processing Operation

[0209] When the operation of the information processing unit 81 is switched from time keeping operation to information processing operation, the micro processing unit 259 starts oscillation of the PLL oscillating circuit 53 as in the case of the first embodiment.

[0210] In this case, the micro processing unit 259 sets an output voltage data stored in a register (not shown) or a non-volatile memory of flash memory 254 corresponding to an output voltage of the LPF 53C, which output voltage is voltage of during a pre-conducted examination and is voltage when the PLL oscillating circuit 53 is locked.

[0211] By this, the D/A converter 53F generates an offset voltage signal SCV2 that corresponds to an output voltage of the LPF 53C at a pre-conducted examination. The offset voltage signal SCV2 is supplied to the VCO 53D via the adder 53H. As a result, the VCO 53D starts oscillation at a frequency which nearly equals to the frequency at which the PLL oscillating circuit 53 is in lock up state.

[0212] On the other hand, the phase comparator 53A compares the phase of the clock signal CLK1 and the phase of the output signal of the divider 53E and outputs a (digital) output signal corresponding to the phase difference between the above two signals to the charge pump 53B.

[0213] The charge pump 53B, based on the output signal of the phase comparator 53A, outputs a difference voltage proportional to the phase difference (frequency difference) between the clock signal CLK1 and the comparison clock signal CLK12/N to the LPF 53C.

[0214] The LPF 53C passes lower component of the output signal of the charge pump 53B and outputs it as the voltage control signal SCV1.

[0215] As a result, the input terminal of the voltage controlled oscillator (VCO) 53D receives the voltage control signal SCV which is produced by applying the offset voltage signal SCV2 on the voltage control signal SCV1, the clock signal CLK12 having a frequency corresponding to the voltage control signal SCV is generated, and the clock signal CLK12 is output to the information processing unit 81 and the divider 53E.

[0216] The divider 53E divides the clock signal CLK12 output by the voltage controlled oscillator 53D and outputs the divided signal as the comparison clock signal CLK12/N to the phase comparator 53A. Thus, frequency of the clock signal CLK12 output by the voltage controlled oscillator 53D is locked in a desired frequency.

[0217] [2.4] Effect of the Second Embodiment

[0218] As described above, according to the second embodiment, at the beginning of the operation of the PLL

oscillating circuit 53, since the input terminal of the voltage controlled oscillator (VCO) 53D receives the voltage control signal which is produced by applying the offset voltage signal SCV2 on the voltage control signal SCV 1, lockup time TRU of this embodiment (10 msec as shown in FIG. 22) becomes shorter than lockup time of conventional PLL oscillating circuit (50 msec as shown in FIG. 23).

[0219] Therefore, compared to conventional way, it is possible to quickly start information processing operation. Further, from a viewpoint of control program, it is possible to omit waiting time routine that holds operation until the PLL oscillating circuit becomes stable, thereby enabling to ease software development.

[0220] Further, it is possible to improve response in various operation of the information processing apparatus.

[0221] [2.5] Modifications of the Second Embodiment

[0222] [2.5.1] First Modification

[0223] In the above description, the A/D converter 53G determines voltage of the LPF 53C when the PLL oscillating circuit 53 is locked during examination conducted in advance. Then the A/D converter 53G A/D converts the output voltage data that corresponds to this voltage and outputs it to the CPU. However, it is possible to configure as follows. At a prescribed timing (on every predetermined hour, for example), the control voltage input to the voltage controlled oscillator when the PLL oscillating circuit is locked up is A/D converted and set as a new output voltage data, thus, correcting the offset voltage in real-time.

[0224] By this, it is possible to set an offset voltage based on the newest data, to remove errors of environmental factor such as temperature change, and to reach the lock up state more quickly.

[0225] [2.5.2] Second Modification

[0226] In the above description, D/A converter is used for generating the offset voltage signal SCV2. However, as shown in FIG. 24, it is possible to generate a desired offset voltage signal SCV2 by using an externally attached ladder-resistor 53J and selecting a tap location by the selector 53I.

[0227] In addition, if a prescribed voltage is necessary as an offset voltage, it is possible to omit the selector 53I from the above configuration.

[3] Modifications of the Embodiments

[0228] [3.1] First Modification

[0229] In the above description, when a prescribed oscillation stable time has passed, oscillating circuit in use is switched from CR oscillating circuit to PLL oscillating circuit. However, this switching may be carried out based on a signal indicating that PLL oscillating circuit has locked up (in the above-mentioned embodiment, the control signal CNT6 having "H" level).

[0230] [3.2] Second Modification

[0231] In the above description, for a first oscillating circuit, an explanation is given only of a case of a CR oscillating circuit. However, it is possible to use a configuration that comprises a quartz oscillator circuit or a ceramic oscillating circuit on the assumption that it is used until the oscillation of the PLL oscillating circuit becomes stable.

## [0232] [3.3] Third Modification

[0233] In the above description, an explanation is given only of a watch-type information processing apparatus. However, if an information processing apparatus is a twin-clock type information processing apparatus, it is possible to apply the present invention to a personal digital assistant (PDA), a portable information processing apparatus such as a note book type personal computer, or especially a information processing apparatus using a secondary battery.

## [0234] [3.4] Fourth Modification

[0235] In the above explanation, oscillations of CR oscillating circuit and PLL oscillating circuit are started at the same time. However, it is possible to start CR oscillating circuit first and then start PLL oscillating circuit. In this case, from the oscillation of the CR becomes stable to the oscillation of the PLL oscillating circuit becomes stable, the output signal of the CR oscillating circuit is used. After the oscillation of the PLL oscillating circuit becomes stable, the output signal of the PLL oscillating signal is used.

## [0236] [3.5] Fifth Modification

[0237] In the above explanation, one case is explained where a control program for selecting from two oscillating circuits which have different oscillation stability time and operating voltage is stored on memory of the watch-type information processing apparatus.

[0238] However, a program for making an information processing apparatus function in a same way as a watch-type information processing apparatus disclosed in the above embodiments may be stored on a network-connected computer to distribute through a telecommunication line.

[0239] Also, such program may be recorded on a recording medium (such as semiconductor memory, magnetic optical disc, or magnetic disc) readable by a computer to be distributed.

[0240] In this case, as an interface for installing the control program in the information processing apparatus, a conventional connector, optical communication using for example infrared light, or magnetic communication using magnetic connection, may be used.

[0241] Then the program is stored on memory of the information processing apparatus, and the microprocessor executes the program.

## [0242] [3.6] Sixth Modification

[0243] In the above explanation, CR oscillating circuit and PLL oscillating circuit are used selectively based on the operating voltage or the oscillation stability time which is a time required for the oscillation to be stable. Namely, the CR oscillating circuit whose oscillation becomes stable quickly is first used, then the PLL oscillating circuit which consumes small power consumption and can oscillate at a high frequency is used. Also, when the power supply voltage becomes lower than voltage the PLL oscillating circuit can operate at, the CR oscillating circuit which can operate at low voltage is used.

[0244] However, the number of oscillating circuits is not limited to two. The present invention can be applied to a case where more than two oscillating circuits are used. In this case, the selection of the oscillating circuit to be used may

be made by considering, for example, the operating voltage, the oscillation stable time, and the power consumption of these oscillating circuits.

What is claimed is:

1. An information processing apparatus comprising:

a first oscillating circuit for generating a first clock signal, the first oscillating circuit being capable of operating on a power supply voltage equal to or higher than a first lowest operating voltage;

a second oscillating circuit for generating a second clock signal, the second oscillating circuit being capable of operating on the power supply voltage equal to or higher than a second lowest operating voltage that is higher than the first lowest operating voltage;

a switching circuit that, based on the power supply voltage, selects either the first clock signal or the second clock signal to output as a clock signal; and

an information processing unit, in synchronism with the clock signal, for performing information processing.

2. An information processing apparatus according to claim 1, wherein the switching circuit outputs the first clock signal as the clock signal when the power supply voltage is equal to or higher than the first lowest operating voltage and lower than the second lowest operating voltage and outputs the second clock signal as the clock signal when the power supply voltage is equal to or higher than the second lowest operating voltage.

3. An information processing apparatus according to claim 1 or 2, further comprising a power supply voltage measuring circuit for measuring voltage of the power supply.

4. An information processing apparatus comprising:

a first oscillating circuit that generates a first clock signal by oscillation and has a first oscillation stability time, the first oscillation stability time being a time required for frequency of the first clock signal becoming stable from beginning of the oscillation;

a second oscillating circuit that generates a second clock signal by oscillation and has a second oscillation stability time, the second oscillation stability time being a time required for frequency of the second clock signal becoming stable from beginning of the oscillation, and being longer than the first oscillation stability time;

a switching circuit for, based on an elapsed time of the first oscillating circuit from the beginning of the oscillation and an elapsed time of the second oscillating circuit from the beginning of the oscillation, selecting and outputting either the first clock signal or the second clock signal as the clock signal; and

an information processing unit for, in synchronism with the clock signal, performing information processing.

5. An information processing apparatus according to claim 4, wherein the switching circuit selects the first clock signal after the first oscillation stability time has passed until the second oscillation stability time comes, and selects the second clock signal after the second oscillation stability time has passed.

**6.** An information processing apparatus according to claim 1, **2**, **4**, or **5**,

wherein the first oscillating circuit is a CR oscillating circuit, a quartz oscillating circuit, or a ceramic oscillating circuit, and

the second oscillating circuit is a PLL oscillating circuit.

**7.** An information processing apparatus according to claim 3,

wherein the first oscillating circuit is a CR oscillating circuit, a quartz oscillating circuit, or a ceramic oscillating circuit, and

the second oscillating circuit is a PLL oscillating circuit.

**8.** An information processing apparatus according to claim 4,

wherein the first oscillating circuit is a CR oscillating circuit, a quartz oscillating circuit, or a ceramic oscillating circuit,

the second oscillating circuit is a PLL oscillating circuit, and

the switching circuit outputs the first clock signal as the clock signal until the PLL oscillating circuit establishes synchronization, and outputs the second clock signal as the clock signal after the PLL oscillating circuit establishes synchronization and a state of the PLL oscillating circuit reaches a synchronization maintained state.

**9.** An information processing apparatus according to claim 8,

wherein the switching circuit, when the PLL oscillating circuit outputs a lockup signal, detects completion of the synchronization.

**10.** An information processing apparatus according to claim 7, wherein the PLL oscillating circuit comprises:

a voltage controlled oscillator for outputting an oscillation signal having a frequency which corresponds to a voltage control signal;

a phase comparator that compares phase of a reference clock signal and phase of a comparison oscillation signal and outputs a comparison signal;

a low pass filter for passing a lower component of the comparison signal;

a divider for dividing the oscillation signal and outputting the comparison oscillation signal;

an offset voltage generating unit for generating an offset voltage; and

an adder for adding an output signal of the low pass filter and the offset voltage to output the voltage control signal.

**11.** An information processing apparatus according to claim 10, wherein the offset voltage generating unit comprises:

an offset voltage data storage unit for storing an offset voltage data in advance; and

a D/A converter for converting the offset voltage data to the offset voltage.

**12.** An information processing apparatus according to claim 11,

wherein the PLL oscillating circuit further comprises an offset voltage data generating unit for, based on the voltage control signal at a prescribed lockup state of the PLL oscillating circuit, generating the offset voltage data.

**13.** An information processing apparatus according to claim 10, wherein the offset voltage generating unit comprises:

a voltage dividing unit for dividing prescribed power supply voltage to generate a plurality of divided voltage; and

a voltage selection unit for selecting one divided voltage from the plurality of the divided voltage as the offset voltage.

**14.** An information processing apparatus according to claim 10,

wherein the offset voltage generating unit comprises a voltage dividing unit for dividing prescribed voltage to generate the offset voltage.

**15.** An information processing apparatus according to claim 12,

wherein the prescribed lockup state is a state where the PLL oscillating circuit is, when the offset voltage generating unit does not output the offset voltage, locked up so that the oscillation signal has a prescribed frequency.

**16.** An information processing apparatus according to claim 12, wherein the PLL oscillating circuit comprises:

a controlled voltage determining unit for determining voltage of the voltage control signal at a prescribed timing;

an offset data correction unit for, based on a result of determination of the controlled voltage determining unit, correcting the offset voltage to make a new offset voltage.

**17.** In a control method for an information processing apparatus, the information processing apparatus comprising:

an information processing unit for, based on a clock signal, carrying out various information processing operations;

a first oscillating circuit that generates a first clock signal and is able to operate on power supply voltage equal to or higher than a first lowest operating voltage,

a second oscillating circuit that generates a second clock signal and is able to operate on the power supply voltage equal to or higher than a second lowest operating voltage that is higher than the first lowest operating voltage;

a switching circuit for, based on the power supply voltage, outputting either the first clock signal or the second clock signal as the clock signal;

the control method comprising:

determining power supply voltage;

outputting by the switching circuit the first clock signal as the clock signal when the power supply voltage is equal to or higher than the first lowest operating voltage and lower than the second lowest operating voltage; and

outputting by the switching circuit the second clock signal as the clock signal when the power supply voltage is equal to or higher than the second lowest operating voltage.

**18.** In a control method for an information processing apparatus, the information processing apparatus comprising:

a first oscillating circuit that generates a first clock signal by oscillation and has a first oscillation stability time, the first oscillation stability time being a time required for frequency of the first clock signal becoming stable from beginning of the oscillation;

a second oscillating circuit that generates a second clock signal by oscillation and has a second oscillation stability time, the second oscillation stability time being a time required for frequency of the second clock signal becoming stable from beginning of the oscillation, and being longer than the first oscillation stability time;

a switching circuit for, based on an elapsed time from the beginning of the oscillation of the first oscillating circuit and on an elapsed time from the beginning of the oscillation of the second oscillating circuit, selecting to output either the first clock signal or the second clock signal as a clock signal;

an information processing unit for, in synchronous with the clock signal, carrying out information processing operations;

the control method comprising:

outputting the first clock signal as the clock signal after the first oscillation stability time has passed until the second oscillation stability time comes, and the second clock signal as the clock signal after the second oscillation stability time has passed.

**19.** A method for an information processing apparatus according to claims **17** or **18**

wherein the second oscillating circuit is a PLL oscillating circuit with a voltage controlled oscillator that outputs an oscillation signal having frequency corresponding to voltage of a voltage control signal; and

the method further comprising:

applying a prescribed offset voltage to the voltage controlled oscillator as the voltage control signal.

**20.** A method for an information processing apparatus according to claims **19**,