(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-12556

(P2013-12556A)

(43) 公開日 平成25年1月17日(2013.1.17)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/369 (2011.01)

H04N 5/374 (2011.01)

F 1

H01L 27/14

H01L 27/14

H04N 5/335 690

H04N 5/335 740

テーマコード(参考)

4M118

5C024

審査請求 未請求 請求項の数 11 O L (全 26 頁)

(21) 出願番号

(22) 出願日特願2011-143581 (P2011-143581)

平成23年6月28日 (2011.6.28)(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100082131

弁理士 稲本 義雄

(74) 代理人 100121131

弁理士 西川 孝

(72) 発明者 宮波 勇樹

東京都港区港南1丁目7番1号 ソニー株式会社内

F ターム(参考) 4M118 AA01 AB01 BA07 BA14 CA04

CA14 CA24 CB20 DA33 DA34

DA40 DD04 FA06 GA02 GD04

5C024 AX01 CY47 GX03 GX24 GY31

(54) 【発明の名称】 固体撮像装置とその製造方法、および電子機器

(57) 【要約】 (修正有)

【課題】半導体基板内の裏面側に高濃度の不純物領域を形成する裏面照射型の固体撮像装置を提供する。

【解決手段】半導体基板17は、裏面側が光入射面とされ、表面側が回路形成面とされる。接続部23は、裏面側の半導体基板上で生成された信号電荷を半導体基板内に転送するコンタクトプラグ31と接続される接続部であって、裏面側の半導体基板の界面近傍に不純物濃度分布のピークを有する。半導体基板内には、1以上の光電変換部が形成される。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、

前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコントクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、

前記半導体基板内に形成された1以上の第1光電変換部と

を備える固体撮像装置。

**【請求項 2】**

前記光入射面側の前記半導体基板上に積層され、下部電極及び上部電極で挟持された第1色用の第2光電変換部をさらに備え、

前記1以上の第1光電変換部は、前記半導体基板の深さ方向に積層された、第2色用の光電変換部と第3色用の光電変換部とからなり、

前記接続部には、前記第1色用の第2光電変換部で生成された前記信号電荷が供給される

請求項1に記載の固体撮像装置。

**【請求項 3】**

前記接続部は、第1の厚みの半導体層の第1の領域を選択的にエッチングして第2の厚みにした後、不純物をイオン注入することにより形成され、

前記イオン注入後に、エッチングされた前記第1の領域がエピタキシャル成長により前記第1の厚みに埋め戻された後、前記第1の厚みの半導体層が、エピタキシャル成長により第3の厚みにさらに積み増しされて、前記半導体基板とされる

請求項1に記載の固体撮像装置。

**【請求項 4】**

エピタキシャル成長により前記第1の厚みに埋め戻された後、前記第1の厚みの半導体層の、水平方向の位置が前記接続部と異なる第2の領域に、1つの前記第1光電変換部が形成される

請求項3に記載の固体撮像装置。

**【請求項 5】**

前記接続部は、第1の厚みの半導体層の第1の領域に対して、不純物をイオン注入することにより形成され、

前記イオン注入後に、前記第1の厚みの半導体層が、エピタキシャル成長により第2の厚みに積み増しされ、

前記第2の厚みの半導体層が、さらに、エピタキシャル成長により第3の厚みに積み増しされて、前記半導体基板とされる

請求項1に記載の固体撮像装置。

**【請求項 6】**

エピタキシャル成長により前記第2の厚みに積み増しされた後、前記第2の厚みの半導体層の、水平方向の位置が前記接続部と異なる第2の領域に、1つの前記第1光電変換部が形成される

請求項5に記載の固体撮像装置。

**【請求項 7】**

前記不純物濃度分布のピークが、前記裏面側の前記半導体基板の界面から100nm以内の位置にある

請求項1に記載の固体撮像装置。

**【請求項 8】**

第1の厚みの半導体基板の第1の領域に不純物をイオン注入することにより、前記半導体基板の光入射面となる裏面側で生成された信号電荷を前記半導体基板内に転送するコントクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部を形成する接続部形成工程と、

10

20

30

40

50

前記第1の厚みの半導体基板をエピタキシャル成長により第2の厚さまで積み増す第1の半導体層形成工程と、

前記第2の厚みの半導体基板の、前記接続部と水平方向の位置が異なる第2の領域に、第1の波長の光を光電変換する第1の光電変換層を形成する第1の光電変換層形成工程と、

前記第2の厚みの半導体基板を、エピタキシャル成長により、第3の厚みまで積み増す第2の半導体層形成工程と

を含む固体撮像装置の製造方法。

【請求項9】

前記接続部形成工程は、前記第1の厚みより厚い第4の厚みから選択的にエッチングされ前記第1の厚みとされた前記半導体基板の前記第1の領域に不純物をイオン注入することにより、前記接続部を形成し、

前記第1の半導体層形成工程は、前記イオン注入後に、エッチングされた前記第1の領域を、エピタキシャル成長により前記第1の厚みと同じ前記第2の厚さに埋め戻す

請求項8に記載の固体撮像装置の製造方法。

【請求項10】

前記第3の厚みの半導体基板の、前記第1の光電変換層よりも前記裏面側から離れた深さ方向の位置に、第2の波長の光を光電変換する第2の光電変換層を形成する第2の光電変換層形成工程をさらに備える

請求項8に記載の固体撮像装置の製造方法。

【請求項11】

光学レンズで集光された光が入射される固体撮像装置と、

前記固体撮像装置の出力信号を処理する信号処理回路と

を備え、

前記固体撮像装置は、

裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、

前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、

前記半導体基板内に形成された1以上の光電変換部と

を備える電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本技術は、固体撮像装置とその製造方法、および電子機器に関し、特に、半導体基板内の裏面側に高濃度の不純物領域を形成することができるようとする固体撮像装置とその製造方法、および電子機器に関する。

【背景技術】

【0002】

従来の一般的なCCDや、CMOSイメージセンサでは、GRN(緑色)、Red(赤色)、Blue(青色)の画素を平面上に配列させて、各画素から、GRN、Red、またはBlueの光電変換信号を得るような構成が採用されている。GRN、Red、Blueの画素の配列方式には、例えばGRNの2画素とRed及びBlueそれぞれ1画素の組で配列するペイヤー配列などがある。

【0003】

従って、従来のCCDや、CMOSイメージセンサでは、各画素からは单一の色の信号しか得られないため、たとえばGRNの画素においては、隣接するBlueおよびRedの画素の信号から、Blue、Redの信号を補間するデモザイク処理と呼ばれる信号処理を行う必要があった。しかし、このような信号処理を行うと、偽色と呼ばれる画質の劣化を招く。この偽色による画質の劣化を避けるためには、光電変換層を縦方向に3層積層し、1画素から3色の光電変換信号が得られればよい。

10

20

30

40

50

## 【0004】

そこで、例えば、半導体基板上に、GRN、Red、及びBlueの光電変換膜を積層させることにより、1画素で、GRN、Red、及びBlueの光電変換信号を得ることができるようにしたものがある（例えば、特許文献1参照）。

## 【0005】

また、半導体基板上に1色（GRN）の光電変換膜を設け、半導体層に2色（Blue, Red）の光電変換部を設けることにより、1画素で、GRN、Red、及びBlueの光電変換信号を得ることができるようにしたものもある（例えば、特許文献2参照）。

## 【0006】

しかし、上記のいずれの技術も、半導体基板上の配線が形成されている表面に、光電変換層を積層させた構造（表面側の積層型イメージセンサ）になっており、積層された光電変換層の信号電荷が一度半導体層に蓄積されることを特徴としている。その際、積層された光電変換層で得られた信号の電荷を貯める半導体領域に光が入射してしまうと、光電変換層の成分以外の成分による信号が半導体領域の光電変換信号に混入してしまい、混色が生じる。のために、上記のような積層型のイメージセンサでは、積層された光電変換からの信号を蓄積する半導体領域に光が漏れ込まないように、遮光レイヤを形成する必要がある。

10

## 【0007】

しかし、上記のような表面型の積層型イメージセンサでは、遮光レイヤを実現するのは難しい。そこで、本出願人により、裏面照射型で、半導体基板上に、有機光電変換膜からなる1色用の光電変換層を積層し、半導体基板内に、2色用の光電変換層を積層させた構造が提案されている（例えば、特許文献3参照）。この構造においては、有機光電変換膜からの信号電荷を取り出すためのコンタクトプラグと、オーミックコンタクトをとる必要があるため、半導体基板の裏面側の界面近傍に、高濃度の不純物領域を形成する必要がある。

20

## 【先行技術文献】

## 【特許文献】

## 【0008】

【特許文献1】特開2006-222278号公報

30

【特許文献2】特開2006-278446号公報

【特許文献3】特開2011-29337号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0009】

しかしながら、半導体基板の裏面側は製造工程では半導体層の深い領域となるため、高濃度の不純物領域を形成することが難しかった。

## 【0010】

本技術は、このような状況に鑑みてなされたものであり、半導体基板内の裏面側に高濃度の不純物領域を形成することができるようとするものである。

40

## 【課題を解決するための手段】

## 【0011】

本技術の第1の側面の固体撮像装置は、裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、前記半導体基板内に形成された1以上の第1光電変換部とを備える。

## 【0012】

本技術の第1の側面の固体撮像装置においては、裏面側の半導体基板上で生成された信号電荷がコンタクトプラグと接続される半導体基板内の接続部に転送され、接続部では、裏面側の半導体基板の界面近傍が不純物濃度分布のピークとなっている。

50

## 【0013】

本技術の第2の側面の固体撮像装置の製造方法は、第1の厚みの半導体基板の第1の領域に不純物をイオン注入することにより、前記半導体基板の光入射面となる裏面側で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部を形成する接続部形成工程と、前記第1の厚みの半導体基板をエピタキシャル成長により第2の厚さまで積み増す第1の半導体層形成工程と、前記第2の厚みの半導体基板の、前記接続部と水平方向の位置が異なる第2の領域に、第1の波長の光を光電変換する第1の光電変換層を形成する第1の光電変換層形成工程と、前記第2の厚みの半導体基板を、エピタキシャル成長により、第3の厚みまで積み増す第2の半導体層形成工程とを含む。

10

## 【0014】

本技術の第2の側面の固体撮像装置の製造方法においては、第1の厚みの半導体基板の第1の領域に不純物をイオン注入することにより、半導体基板の光入射面となる裏面側で生成された信号電荷を半導体基板内に転送するコンタクトプラグと接続される接続部であって、裏面側の半導体基板の界面近傍に不純物濃度分布のピークを有する接続部が形成され、第1の厚みの半導体基板がエピタキシャル成長により第2の厚さまで積み増しされ、第2の厚みの半導体基板の、接続部と水平方向の位置が異なる第2の領域に、第1の波長の光を光電変換する第1の光電変換層が形成され、第2の厚みの半導体基板が、エピタキシャル成長により、第3の厚みまで積み増しされる。

20

## 【0015】

本技術の第3の側面の電子機器は、光学レンズで集光された光が入射される固体撮像装置と、前記固体撮像装置の出力信号を処理する信号処理回路とを備え、前記固体撮像装置は、裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、前記半導体基板内に形成された1以上の光電変換部とを備える。

20

## 【0016】

本技術の第3の側面の電子機器においては、光学レンズで集光された光が固体撮像装置に入射され、固体撮像装置の出力信号が信号処理回路で処理される。固体撮像装置では、裏面側の半導体基板上で生成された信号電荷がコンタクトプラグと接続される半導体基板内の接続部に転送され、接続部では、裏面側の半導体基板の界面近傍が不純物濃度分布のピークとなっている。

30

## 【発明の効果】

## 【0017】

本技術の第1ないし第3の側面によれば、半導体基板内の裏面側に高濃度の不純物領域を形成することができる。

40

## 【図面の簡単な説明】

## 【0018】

【図1】本技術が適用された第1の実施の形態に係る固体撮像装置の全体を示す概略構成図である。

40

【図2】図1の固体撮像装置の画素の概略平面構成を示す図である。

【図3】画素における要部の概略断面構成を示す図である。

【図4】縦型転送路を説明する図である。

【図5】従来の接続部の形成方法について説明する図である。

【図6】接続部の第1ないし第4の製造方法の概略を説明する図である。

【図7】接続部の第1の製造方法を説明する図である。

【図8】接続部の第2の製造方法を説明する図である。

【図9】接続部の第3の製造方法を説明する図である。

【図10】接続部の第3の製造方法を説明する図である。

50

- 【図11】接続部の第4の製造方法を説明する図である。

【図12】半導体基板の裏面側の製造工程について簡単に説明する図である。

【図13】半導体基板の裏面側の製造工程について簡単に説明する図である。

【図14】半導体基板の裏面側の製造工程について簡単に説明する図である。

【図15】半導体基板の裏面側の製造工程について簡単に説明する図である。

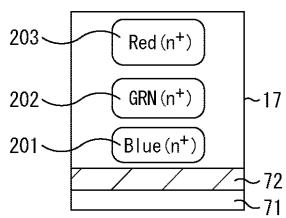

【図16】半導体層に3色用の光電変換部を形成する例を示す図である。

【図17】3層の光電変換層を形成する第1の製造方法を説明する図である。

【図18】層の光電変換層を形成する第2の製造方法を説明する図である。

【図19】本技術が適用された第3の実施の形態に係る電子機器の概略構成図である。

## 【発明を実施するための形態】

10

## 【0019】

以下、本技術を実施するための形態（以下、実施の形態という）について説明する。なお、説明は以下の順序で行う。

## 1. 第1の実施の形態：固体撮像装置

- 1 - 1 全体構成

- 1 - 2 画素の概略平面構成

- 1 - 3 画素の概略断面構成

- 1 - 4 従来の問題

- 1 - 5 第1の製造方法

- 1 - 6 第2の製造方法

- 1 - 7 第3の製造方法

- 1 - 8 第4の製造方法

- 1 - 9 半導体基板の裏面側の製造工程

- 1 - 10 駆動方法

20

## 2. 第2の実施の形態：3色用の光電変換部を半導体層に形成する例

## 3. 第3の実施の形態：電子機器

## 【0020】

## &lt;1. 第1の実施の形態&gt;

まず、本技術が適用された第1の実施の形態に係る固体撮像装置について説明する。

## 【0021】

30

## [1 - 1 固体撮像装置の全体構成]

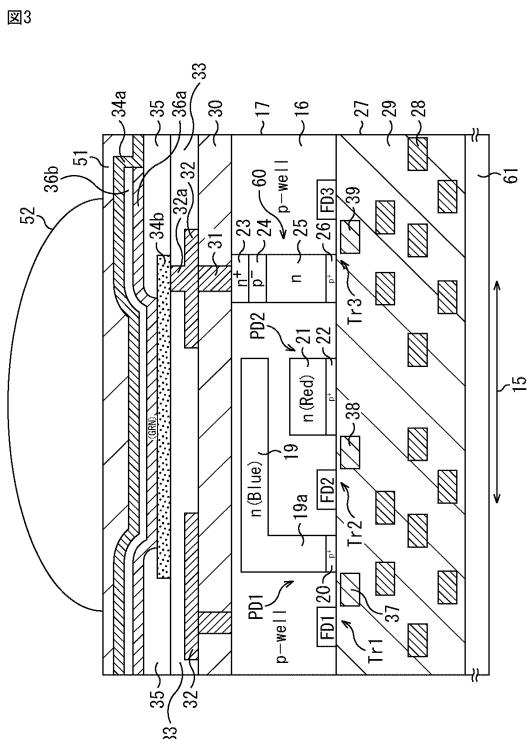

図1は、第1の実施の形態に係る固体撮像装置1の全体を示す概略構成図である。図1の固体撮像装置1は、裏面照射型のCMOS型固体撮像装置である。

## 【0022】

図1の固体撮像装置1は、シリコンからなる基板11上に配列された複数の画素2から構成される画素領域3と、垂直駆動回路4と、カラム信号処理回路5と、水平駆動回路6と、出力回路7と、制御回路8等を有して構成される。

## 【0023】

画素2は、光電変換素子であるフォトダイオードと、複数の画素トランジスタとから構成され、基板11上に、2次元アレイ状に規則的に複数配列される。画素2を構成する画素トランジスタは、転送トランジスタ、リセットトランジスタ、選択トランジスタ、増幅トランジスタで構成される4つの画素トランジスタであってもよく、また、選択トランジスタを除いた3つのトランジスタであってもよい。

## 【0024】

画素領域3は、2次元アレイ状に規則的に複数配列された画素2から構成される。画素領域3は、実際に光を受光し光電変換によって生成された信号電荷を増幅してカラム信号処理回路5に読み出す有効画素領域（図示せず）と、黒レベルの基準になる光学的黒を出力するための黒基準画素領域（図示せず）とから構成されている。黒基準画素領域は、通常は、有効画素領域の外周部に形成される。

## 【0025】

40

50

制御回路 8 は、垂直同期信号、水平同期信号及びマスタクロックに基づいて、垂直駆動回路 4、カラム信号処理回路 5、及び水平駆動回路 6 等の動作の基準となるクロック信号や制御信号などを生成する。そして、制御回路 8 で生成されたクロック信号や制御信号などは、垂直駆動回路 4、カラム信号処理回路 5 及び水平駆動回路 6 等に入力される。

## 【0026】

垂直駆動回路 4 は、例えばシフトレジスタによって構成され、画素領域 3 の各画素 2 を行単位で順次垂直方向に選択走査する。そして、各画素 2 のフォトダイオードにおいて受光量に応じて生成した信号電荷に基づく画素信号を、垂直信号線 9 を通してカラム信号処理回路 5 に供給する。

## 【0027】

カラム信号処理回路 5 は、例えば、画素 2 の列毎に配置されており、1 行分の画素 2 から出力される信号を画素列毎に黒基準画素領域（図示しないが、有効画素領域の周囲に形成される）からの信号によって、ノイズ除去や信号増幅等の信号処理を行う。カラム信号処理回路 5 の出力段には、水平選択スイッチ（図示せず）が水平信号線 10 とのあいだに設けられている。

## 【0028】

水平駆動回路 6 は、例えばシフトレジスタによって構成され、水平走査パルスを順次出力することによって、カラム信号処理回路 5 の各々を順番に選択し、カラム信号処理回路 5 の各々から画素信号を水平信号線 10 に出力させる。

## 【0029】

出力回路 7 は、カラム信号処理回路 5 の各々から水平信号線 10 を通して、順次に供給される信号に対し信号処理を行い出力する。

## 【0030】

## [1-2 画素 2 の概略平面構成]

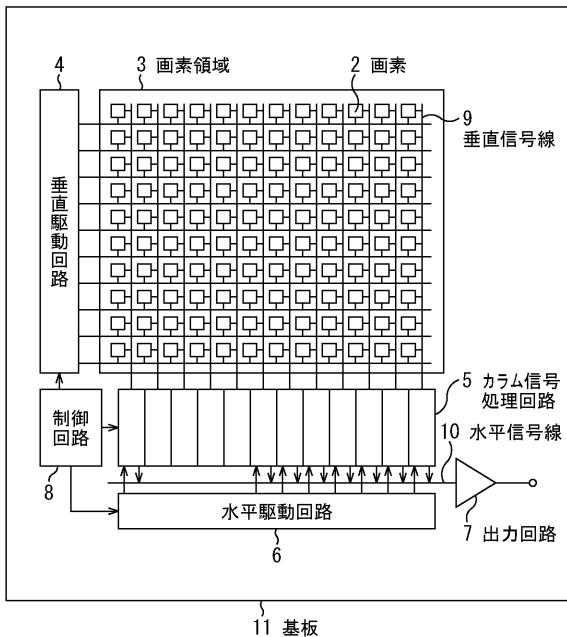

図 2 は、固体撮像装置 1 の画素 2 の概略平面構成を示している。図 2 に示すように、画素 2 は、赤色 (Red)、緑色 (GRN)、青色 (Blue) のそれぞれの波長の光を光電変換する第 1 ないし第 3 光電変換部が 3 層に積層された光電変換領域 15 と、各光電変換部に対応する電荷読み出し部とから構成されている。本実施の形態においては、電荷読み出し部は、第 1 ないし第 3 光電変換部に対応した第 1 ないし第 3 画素トランジスタ Tr A, Tr B, Tr C で構成されている。本実施の形態の固体撮像装置 1 では、画素 2 において縦方向の分光がなされる。

## 【0031】

第 1 ないし第 3 画素トランジスタ Tr A, Tr B, Tr C は、光電変換領域 15 の周辺に形成されており、それぞれ 4 つの MOS 型トランジスタで構成されている。第 1 画素トランジスタ Tr A は、後述する第 1 光電変換部で生成、蓄積された信号電荷を画素信号として出力するもので、第 1 転送トランジスタ Tr 1、リセットトランジスタ Tr 4、増幅トランジスタ Tr 5、及び、選択トランジスタ Tr 6 で構成されている。第 2 画素トランジスタ Tr B は、後述する第 2 光電変換部で生成、蓄積された信号電荷を画素信号として出力するもので、第 2 転送トランジスタ Tr 2、リセットトランジスタ Tr 7、増幅トランジスタ Tr 8、及び、選択トランジスタ Tr 9 で構成されている。第 3 画素トランジスタ Tr C は、後述する第 3 光電変換部で生成、蓄積された信号電荷を画素信号として出力するもので、第 3 転送トランジスタ Tr 3、リセットトランジスタ Tr 10、増幅トランジスタ Tr 11、及び、選択トランジスタ Tr 12 で構成されている。

## 【0032】

リセットトランジスタ Tr 4, Tr 7, Tr 10 は、ソース・ドレイン領域 43, 44 とゲート電極 40 とで構成されている。増幅トランジスタ Tr 5, Tr 8, Tr 11 は、ソース・ドレイン領域 44, 45、ゲート電極 41 とで構成されている。選択トランジスタ Tr 6, Tr 9, Tr 12 は、ソース・ドレイン領域 45, 46 と、ゲート電極 42 とで構成されている。そしてこれらの画素トランジスタ Tr A, Tr B, Tr C においては、フローティングディフュージョン部 FD 1, FD 2, FD 3 が対応するリセットトラン

10

20

30

40

50

ジスタ Tr 4 , Tr 7 , Tr 10 の一方のソース・ドレイン領域 4 3 に接続されている。さらに、フローティングディフュージョン部 FD 1 , FD 2 , FD 3 は、対応する増幅トランジスタ Tr 5 , Tr 8 , Tr 11 のゲート電極 4 1 に接続されている。また、リセットトランジスタ Tr 4 , Tr 7 , Tr 10 と増幅トランジスタ Tr 5 , Tr 8 , Tr 11 とで共通のソース・ドレイン領域 4 4 には、電源電圧配線 V dd が接続されている。また、選択トランジスタ Tr 6 , Tr 9 , Tr 12 の一方のソース・ドレイン領域 4 6 には、選択信号配線 V SL が接続されている。

## 【0033】

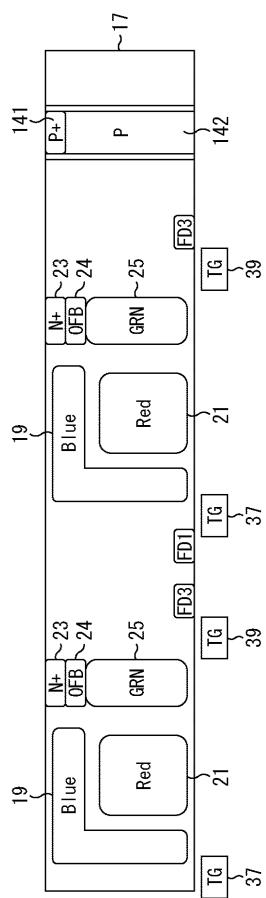

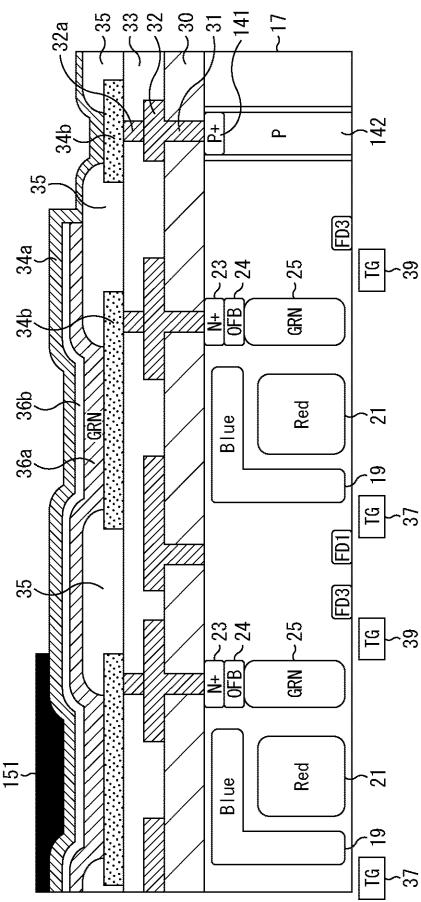

## [1-3 画素 2 の概略断面構成]

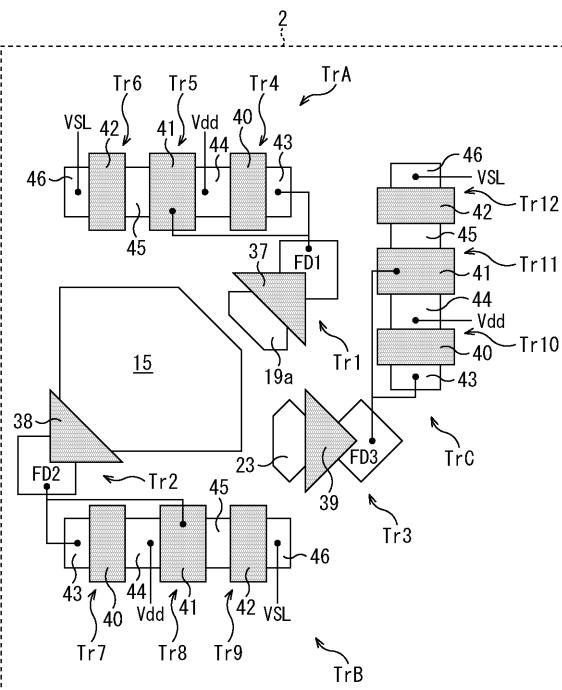

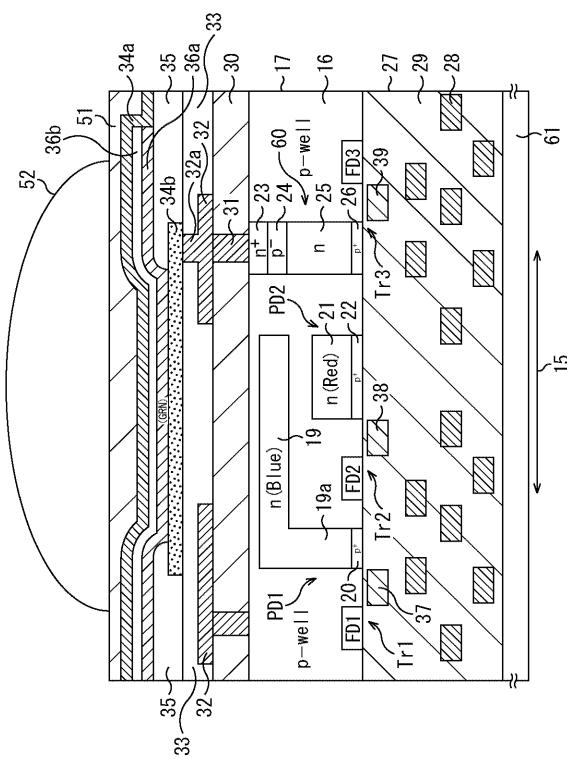

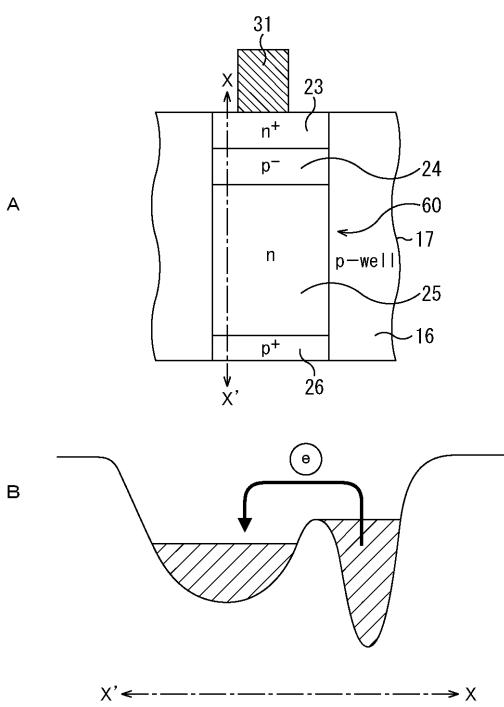

図 3 は、固体撮像装置 1 の画素 2 の概略断面構成を示している。図 3 では、第 1 ないし第 3 画素トランジスタ Tr A , Tr B , Tr C のうち第 1 ないし第 3 転送トランジスタ Tr 1 , Tr 2 , Tr 3 のみ図示し、他の画素トランジスタの図示を省略する。

## 【0034】

本実施の形態の固体撮像装置 1 は、半導体基板 17 の表面側である画素トランジスタが形成された側とは反対側の裏面側から光が入射される裏面照射型の固体撮像装置である。図 3 では、上側が裏面側の受光面側（光入射面側）であり、下側が表面側であり、画素トランジスタや、ロジック回路等の周辺回路などが形成された回路形成面である。

## 【0035】

光電変換領域 15 は、半導体基板 17 に形成される第 1 及び第 2 フォトダイオード PD 1 及び PD 2 からなる第 1 及び第 2 光電変換部と、半導体基板 17 の裏面側に形成された有機光電変換膜 36 a からなる第 3 光電変換部とが光の入射方向に積層された構成とされる。

## 【0036】

第 1 及び第 2 フォトダイオード PD 1 及び PD 2 は、シリコンからなる半導体基板 17 の、第 1 導電型（本実施の形態では p 型とする）の半導体領域からなるウェル領域 16 に形成されている。第 1 フォトダイオード PD 1 は、半導体基板 17 の受光面側に形成された第 2 導電型（本実施の形態では n 型とする）不純物による n 型半導体領域 19 と、その一部が半導体基板の表面側に達するように延長して形成された延長部 19 a を有する。延長部 19 a は、3 層の光電変換部が積層された部分で構成される光電変換領域 15 の周辺に形成されるもので、その延長部 19 a の表面（半導体基板の表面）には、ホール蓄積層となる高濃度の p 型半導体領域 20 が形成されている。また、この延長部 19 a は、第 1 フォトダイオードの n 型半導体領域 19 に蓄積された信号電荷を半導体基板 17 の表面側に抜き出すための抜き出し層として形成されるものである。

## 【0037】

第 2 フォトダイオード PD 2 は、半導体基板 17 の表面側に形成された n 型半導体領域 21 と、その表面側の半導体基板 17 界面に形成されたホール蓄積層となる高濃度の p 型半導体領域 22 とで構成されている。第 1 フォトダイオード PD 1 及び第 2 フォトダイオード PD 2 において、半導体基板 17 の界面に p 型半導体領域 20 及び 22 が形成されることにより、半導体基板 17 界面で発生する暗電流の抑制が図られる。

## 【0038】

受光面から一番離れた領域に形成された第 2 フォトダイオード PD 2 は、赤色の波長の光を光電変換する光電変換部とされる。また、受光面側に形成された第 1 フォトダイオード PD 1 は、青色の波長の光を光電変換する光電変換部とされる。

## 【0039】

図 3 の画素 2 において、緑色の波長の光を光電変換する光電変換部は、裏面側の半導体基板 17 上の有機光電変換膜 36 a により構成されている。有機光電変換膜 36 a には、例えば、ローダーミン系色素、メラシアニン系色素、キナクリドン等を含む有機光電変換材料が用いられる。

## 【0040】

有機光電変換膜 36 a の上面はパッジベーション膜（窒化膜）36 b で覆われ、有機光

10

20

30

40

50

電変換膜36aとパッシベーション膜36bが、上部電極34a及び下部電極34bで挟まれた構成とされている。

【0041】

上部電極34aの上側には平坦化膜51が形成され、平坦化膜51の上にオンチップレンズ52が設けられる。一方、下部電極34bと同一平面で、下部電極34bが形成されていない領域には、下部電極34bのエッジの段差を緩和するための絶縁膜35が設けられる。上部電極34a及び下部電極34bは、光透過性の材料で構成され、例えば、インジウム錫（ITO）膜、酸化インジウム亜鉛膜等の透明導電膜で構成される。

【0042】

本実施の形態では、有機光電変換膜36aの材料を緑色の光を光電変換する材料で構成したが、青色あるいは赤色の波長の光を光電変換する材料で構成し、第1フォトダイオードPD1及び第2フォトダイオードPD2をその他の波長に対応させて構成してもよい。

10

【0043】

例えば、有機光電変換膜36aで青色の光を吸収させる場合には、半導体基板17の受光面側に形成される第1フォトダイオードPD1を、緑色の光を光電変換する光電変換部として設定し、第2フォトダイオードPD2を、赤色の光を光電変換する光電変換部として設定することができる。

【0044】

また、有機光電変換膜36aで赤色の光を吸収させる場合には、半導体基板17の受光面側に形成される第1フォトダイオードPD1を、青色の光を光電変換する光電変換部として設定し、第2フォトダイオードPD2を、緑色の光を光電変換する光電変換部として設定することができる。

20

【0045】

青色の光を光電変換する有機光電変換膜としては、クマリン酸色素、トリス-8-ヒドリキシキノリA1（A1q3）、メラシアニン系色素等を含む有機光電変換材料を用いることができる。また、赤色の光を光電変換する有機光電変換膜としては、フタロシアニン系色素を含む有機光電変換材料を用いることができる。

【0046】

なお、本実施の形態のように、半導体基板17内で光電変換する光を、青色及び赤色とし、有機光電変換膜36aで光電変換する光を緑色と設定することが望ましい。第1及び第2フォトダイオードPD1, PD2間ににおける分光特性を向上させることができるからである。

30

【0047】

上述の有機光電変換膜36aの半導体基板17側に形成される下部電極34bは、絶縁膜33を貫通するコンタクトプラグ32aを介して、遮光膜と配線を兼ねる導電膜32と接続されている。導電膜32には、例えばA1、Ti、W等を用いることができる。そして、導電膜32は、反射防止層30を貫通するコンタクトプラグ31を介して、半導体基板17裏面側から表面側にかけて形成された縦型転送路60の接続部23に接続されている。

【0048】

縦型転送路60は、半導体基板17の裏面側から表面側にかけて縦方向に形成された接続部23、電位障壁層24、電荷蓄積層25、及びp型半導体領域26の積層構造により構成されている。

40

【0049】

接続部23は、コンタクトプラグ31とのオーミックコンタクトのために、高不純物濃度のn型不純物領域により構成されている。電位障壁層24は、低濃度のp型不純物領域からなり、接続部23と電荷蓄積層25間ににおいてポテンシャルバリアを構成する。電荷蓄積層25は、有機光電変換膜36aから転送された信号電荷を蓄積する層であり、接続部23よりも低濃度のn型不純物領域で構成される。半導体基板17の最表面に形成されたp型半導体領域26は、高濃度のp型不純物領域で構成され、これにより半導体基板1

50

7 界面における暗電流の発生が抑制される。

【0050】

図4を参照して、縦型転送路60について説明する。

【0051】

図4Aは、縦型転送路60の拡大図を示し、図4Bは、図4Aにおけるx-x'線上に沿う断面構成図を示している。

【0052】

本実施の形態における縦型転送路60では、図4Bに示すようなポテンシャル勾配が形成される。このため、有機光電変換膜36aからコンタクトプラグ31等を介して接続部23に転送されてきた信号電荷eは、電位障壁層24で形成されるオーバーフローバリア(OFB)を超えて電荷蓄積層25に蓄積されていく。電荷蓄積層25に蓄積された信号電荷eが、半導体基板17の回路形成面となる表面側に読み出されることとなる。

【0053】

そして、半導体基板17の回路形成面となる表面側には、図2で示したように、第1フォトダイオードPD1、第2フォトダイオードPD2及び有機光電変換膜36aに対応する第1ないし第3画素トランジスタTrA, TrB, TrCが構成されている。

【0054】

図3に戻り、第1転送トランジスタTr1は、第1フォトダイオードPD1の延長部19aに隣接する半導体基板17の表面側に形成されたフローティングディフュージョン部FD1と、半導体基板17上にゲート絶縁膜を介して形成された転送ゲート電極37とで構成される。第2転送トランジスタTr2は、第2フォトダイオードPD2に隣接する半導体基板17の表面側に形成されたフローティングディフュージョン部FD2と、半導体基板17上にゲート絶縁膜を介して形成された転送ゲート電極38とで構成される。第3転送トランジスタTr3は、縦型転送路60に隣接する半導体基板17の表面側に形成されたフローティングディフュージョン部FD3と、半導体基板17上にゲート絶縁膜を介して形成された転送ゲート電極39とで構成される。

【0055】

フローティングディフュージョン部FD1、FD2、及びFD3は、いずれもn型の高濃度不純物領域で構成され、転送ゲート電極37ないし39は、例えばポリシリコンで構成される。

【0056】

半導体基板17の表面側には、層間絶縁膜29を介して複数層(本実施の形態では3層)に積層された配線28を有する多層配線層27が形成されている。また、多層配線層27の表面には、製造段階において形成される支持基板61が形成されている。

【0057】

以上のように、本実施の形態の固体撮像装置1では、画素2において縦方向に分光がなされるので、カラーフィルタは構成されていない。

【0058】

[1-4 従来の問題]

図3および図4を参照して説明した画素2の構造において、接続部23は、コンタクトプラグ31とオーミックコンタクトを取る必要があるため、高濃度のn型不純物領域とする必要がある。具体的には、 $1 \times 10^{19}$ ないし $1 \times 10^{20} / \text{cm}^3$ の濃度にする必要がある。

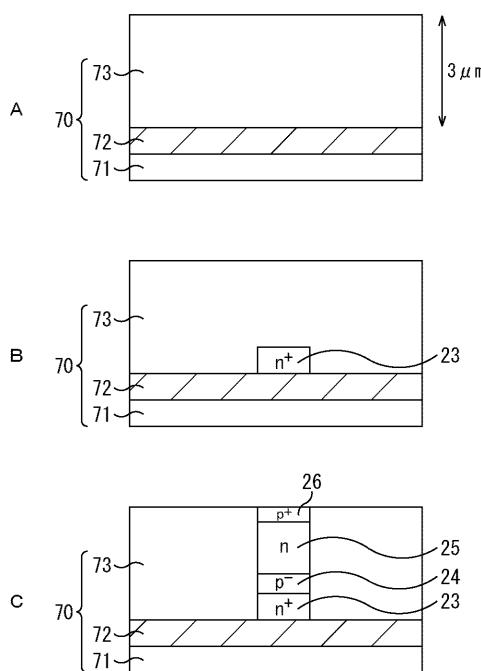

【0059】

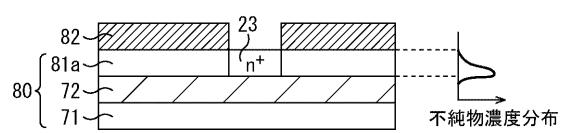

図5を参照して、従来の接続部23の形成方法について説明する。

【0060】

まず、図5Aに示されるようなSOI基板70が用意される。SOI基板70は、シリコンからなる支持基板71上に、BOX層72(埋め込み酸化膜)、及び、シリコンからなる半導体層73が順に積層されて構成される。SOI基板70の半導体層73が、図3の半導体基板17に対応する。半導体層73は、例えば、n型の半導体層とされ、その厚

10

20

30

40

50

みは、例えば、 $3 \mu m$ に形成されている。

【0061】

そして、図5Bに示されるように、SOI基板70の半導体層73のBOX層72界面近傍の深い領域に、n型の不純物を高濃度にイオン注入することで、接続部23が形成される。

【0062】

その後、図5Cに示されるように、電位障壁層24、電荷蓄積層25、p型半導体領域26が、順にイオン注入により形成され、支持基板71およびBOX層72が除去された後、上下に反転された状態が、図3および図4の縦型転送路60に相当する。

【0063】

従来の製造方法では、上述したように、半導体層73のBOX層72界面近傍の深い領域に、n型の不純物を高濃度にイオン注入する必要があるが、半導体層73の深い領域に、不純物濃度分布が急峻になるように接続部23を形成するのは困難であった。

【0064】

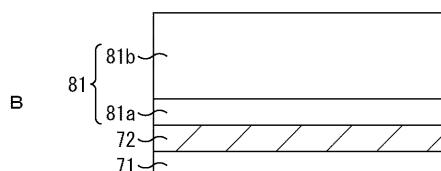

[1-5 第1の製造方法]

そこで、例えば、本実施の形態では、以下の第1ないし第4の製造方法により、高濃度の不純物領域である接続部23が形成される。

【0065】

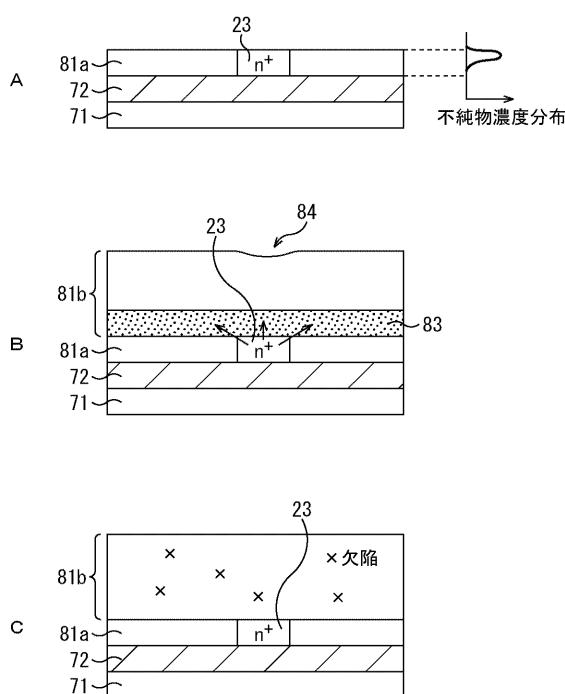

以下に後述する第1ないし第4の製造方法では、最初に、図6Aに示されるように、図5Aの $3 \mu m$ より薄膜の半導体層81aを有するSOI基板80が用意される。SOI基板80は、支持基板71上に、BOX層72と半導体層81aが順に積層されて構成されている。なお、半導体層81aの厚みは、10ないし500nmの範囲内で適宜決定することができる。

【0066】

そして、所定の工程後、図6Bに示されるように、エピタキシャル成長により半導体層81bが積み増しされる。図6Bの半導体層81aと81bとからなる半導体層81が、図5の半導体層73に相当する。本実施の形態では、最初に形成されるときの半導体層81aと81bの導電型は、例えば、第2導電型(n型)であるとする。

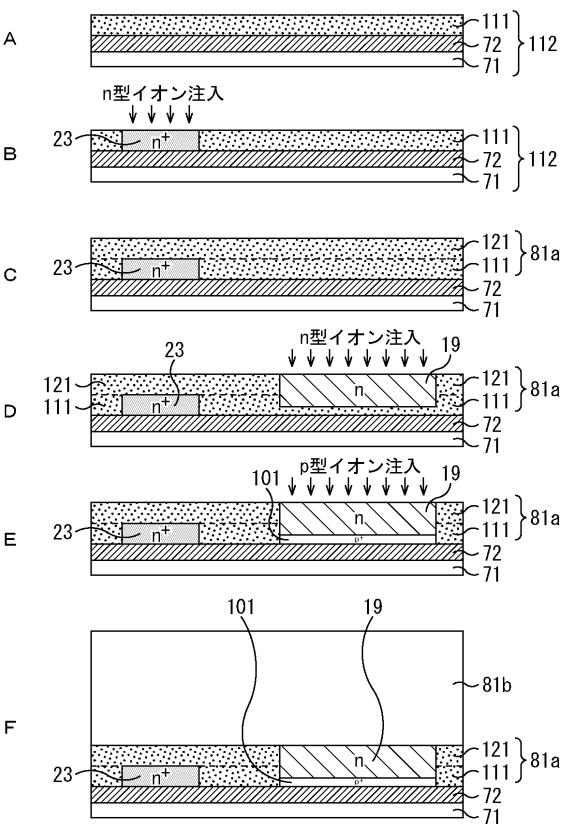

【0067】

図7を参照して、接続部23の第1の製造方法について説明する。

【0068】

第1の製造方法では、薄膜の半導体層81a上の接続部23となる領域が開口するようにレジスト81が形成される。そして、高ドーズ量(Dose量)で照射エネルギーを高くして、イオンの注入深さRp(Projection Range)を、BOX層72界面近傍に設定し、n型不純物を高濃度にイオン注入することで、接続部23が形成される。イオンの注入深さRpは、不純物濃度分布(プロファイル)のピークとなる位置に対応する。第1の製造方法において、薄膜の半導体層81aの厚みは、例えば、200ないし300nmとし、イオンの注入深さRpは、例えば、BOX層72界面から100nm以内の範囲とすることができます。

【0069】

しかし、このような第1の製造方法によれば、高エネルギーのイオンにより接続部23の結晶性を破壊し、回復するのが難しい。また、高エネルギーのイオンがレジスト82にも照射されることにより、レジスト82が硬化し、剥離するのが難しくなる。

【0070】

[1-6 第2の製造方法]

そこで、図8Aに示す第2の製造方法のように、ドーズ量を増加させて、イオンの注入深さRpを、浅く、即ち、薄膜の半導体層81aの表面側に設定して、n型不純物を高濃度にイオン注入することで、接続部23を形成する方法もある。

【0071】

しかし、この場合には、半導体層81bを形成するための高温のエピタキシャル成長により、半導体層81aの表面の不純物濃度が上がる。そのため、図8Bに示されるように

、エピタキシャル成長により形成された活性層である半導体層81bに、オートドープにより活性層が低抵抗化したオードドープ領域83が発生する。この結果、フォトダイオードのポテンシャル設計が難しくなる。さらに、エピタキシャル成長により形成された活性層である半導体層81bの、接続部23の上方部分に局所的な凹み84が発生し、STI(Shallow Trench Isolation)形成時のSiN残が発生してコンタクト形成時の問題になりやすい。

#### 【0072】

一方、オートドープを抑制できる程度の低温のエピタキシャル成長により、半導体層81bを形成した場合には、図8Cに示されるように、半導体層81b自体に結晶欠陥が生じやすい。

10

#### 【0073】

また、オートドープを抑制できる程度に、ドーズ量を少なくした場合には、コンタクト抵抗が増大する。

#### 【0074】

従って、第1及び第2の製造方法は、従来の製造方法よりも、不純物濃度分布が急峻になるように接続部23を形成することはできるが、最良の方法とは言えない。

#### 【0075】

##### [1-7 第3の製造方法]

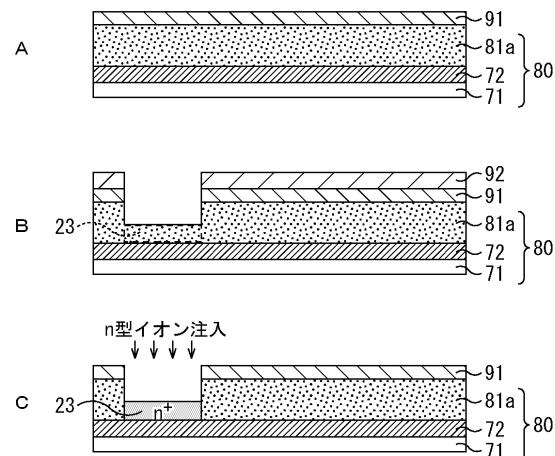

次に、図9および図10を参照して、接続部23の第3の製造方法について説明する。

20

#### 【0076】

最初に、図9Aに示されるように、半導体層81a、BOX層72、及び支持基板71からなるSOI基板80上に、ハードマスクの酸化膜91が成膜される。酸化膜91は、例えば、熱酸化膜やLP-TEOSとすることができる。なお、第3の製造方法において、薄膜の半導体層81aの厚みは、例えば、200ないし300nmとすることができる。

#### 【0077】

次に、図9Bに示されるように、酸化膜91上にレジスト92が塗布された後、半導体層81aの接続部23となる領域が、フォトリソグラフィ及びドライエッチングにより開口される。

#### 【0078】

トレチ（開口部）のエッチングには、例えば、枚葉のドライエッチング装置において、圧力を50ないし150mTorr、RFパワーを500ないし900W、エッチングガスとして、HBr、SF<sub>6</sub>、O<sub>2</sub>のそれぞれを100ないし300sccm、10ないし30sccm、0ないし10sccmとする条件で処理を行うことができる。ドライエッチングの後、ドライエッチングによるシリコンのダメージ除去、つまりシリコン結晶欠陥や不純物を除去する後処理が行われる。この後処理としては、例えば、ダメージレスエッチングのCDE（Chemical Dry Etching）や、アンモニアと過酸化水素水からなるHot SC1犠牲酸化処理とDHF（希フッ酸）処理を追加することが望ましい。

30

#### 【0079】

次に、酸化膜91上のレジスト92が剥離された後、図9Cに示されるように、開口された半導体層81aの接続部23となる領域に、n型の不純物が高濃度にイオン注入され、接続部23が形成される。有機光電変換膜36aからの信号電荷を取り出すためのコンタクトプラグ31とオーミックコンタクトをとる必要があるため、接続部23の不純物濃度は、 $1 \times 10^{19}$ ないし $1 \times 10^{20} / \text{cm}^3$ 程度の濃度とされる。注入されるn型の不純物は、例えば、リン（P）やヒ素（As）とすることができる。

40

#### 【0080】

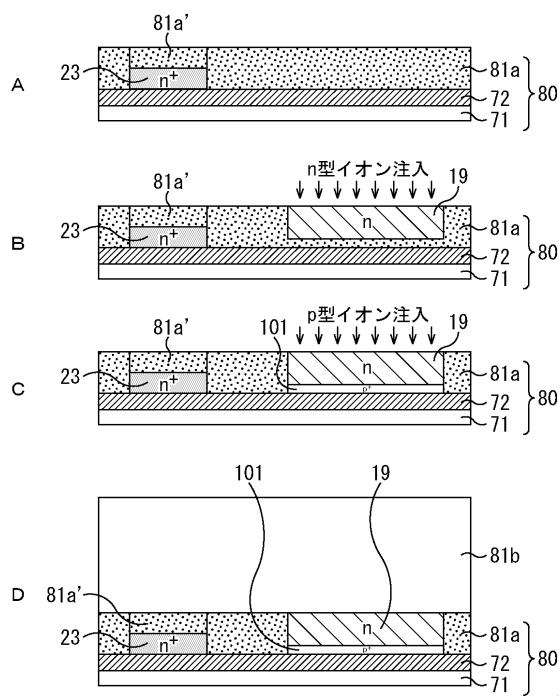

次に、図10Aに示されるように、酸化膜91除去後、イオン注入により形成した接続部23の上のエッチングされた領域のみを選択した選択的低温エピタキシャル成長により、半導体層81a'（シリコン）が形成される。即ち、エッチングされた領域が、選択的低温エピタキシャル成長により、元の半導体層81aの厚みに埋め戻される。ここでの低温エピタキシャル成長の条件としては、例えば、温度を600ないし950、圧力を10Torr

50

ないし760Torr、ジクロロシラン（DCS）の流量を10ないし100sccm、塩化水素（HCl）の流量を10ないし300sccm、水素（H<sub>2</sub>）の流量を10ないし50sImとすることができます。半導体層81a'は、低温のエピタキシャル成長により形成されるため、接続部23の不純物がドープすることはない。「低温」の条件としては、上述のように950以下であることとするが900以下が望ましい。また、上記のジクロロシラン（DCS）の代わりに、SiH<sub>4</sub>、SiH<sub>3</sub>Cl、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>などでもよい。なお、200nmの膜厚の半導体層81a'を、低温のエピタキシャル成長により形成するのに必要な時間は、20分程度である。

#### 【0081】

次に、図10Bに示されるように、半導体層81aの、水平方向の位置が接続部23と異なる領域に、リンまたはヒ素などのn型の不純物がイオン注入され、n型半導体領域19が形成される。このn型半導体領域19が、上述した第1フォトダイオードPD1を構成する。

#### 【0082】

なお、図10Cに示されるように、第1フォトダイオードPD1となるn型半導体領域19とBOX層72との間の半導体層81aの領域に、p型の不純物を高濃度にイオン注入することで、ピニング層101を形成するようにしてもよい。半導体層81aにピニング層101を設けない場合には、支持基板71及びBOX層72が除去された後に成膜される反射防止層30として負の固定電荷を有する膜を用いて、ピニング膜とすることができる。負の固定電荷を持つピニング膜は、例えば、酸化ハフニウム（HfO<sub>2</sub>）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）などである。ピニング層101またはピニング膜により、半導体基板17裏面側の界面にホールの蓄積状態が強化され、暗電流の発生を抑制することができる。

#### 【0083】

そして、最後に、図10Dに示されるように、高温のエピタキシャル成長により、n型の半導体層81bが形成される。高温のエピタキシャル成長によるn型の半導体層81bと、SOI基板80の半導体層81aとを合わせた厚みが、従来の半導体層73と同様の厚み（3μm）になるまで、半導体層81bがエピタキシャル成長される。高温のエピタキシャル成長によりn型の半導体層81bを形成しても、低温のエピタキシャル成長により形成された半導体層81a'で接続部23は覆われているため、高濃度不純物領域である接続部23の不純物がドープすることはない。

#### 【0084】

以上説明した第3の製造方法によれば、例えば、200ないし300nm程度の厚みの半導体層81aをドライエッチングによりさらに薄膜化した上で、イオン注入により接続部23となる高濃度の不純物領域が形成される。そして、形成された高濃度の不純物領域である接続部23の上部が選択的低温エピタキシャル成長により、半導体層81a'（シリコン）が積み増しされた後、高温エピタキシャル成長により、さらに、半導体層81bが積み増しされる。

#### 【0085】

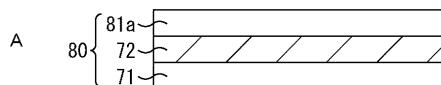

##### [1-8 第4の製造方法]

次に、図11を参照して、接続部23の第4の製造方法について説明する。

#### 【0086】

第4の製造方法では、図11Aに示されるように、BOX層72上に形成されるn型の半導体層111の厚みが、上述したSOI基板80よりも、さらに薄膜であるSOI基板112が用いられる。n型の半導体層111の厚みは、例えば、100nm程度である。

#### 【0087】

そして、図11Bに示されるように、半導体層111の所定の領域に、p型の不純物が高濃度にイオン注入され、接続部23が形成される。有機光電変換膜36aからの信号電荷を取り出すためのコンタクトプラグ31とオーミックコンタクトをとる必要があるため、接続部23の不純物濃度は、 $1 \times 10^{19}$ ないし $1 \times 10^{20} / \text{cm}^3$ 程度の濃度とさ

10

20

30

40

50

れる。注入される p 型の不純物は、例えば、リン (P) やヒ素 (As) である。

【0088】

次に、図 11C に示されるように、高温のエピタキシャル成長により、第 1 フォトダイオード P D 1 となる n 型半導体領域 19 の形成が可能となる厚みまで、具体的には、図 6A で説明した 200 ないし 300 nm の厚みとなるまで、n 型の半導体層 121 が形成される。換言すれば、高温のエピタキシャル成長により積み増しされた半導体層 121 と、半導体層 111 とからなる半導体層によって、図 6A の半導体層 81a が形成される。

【0089】

その後の工程は、上述した第 3 の製造方法と同様である。即ち、図 11D に示されるように、n 型の不純物が高濃度にイオン注入され、第 1 フォトダイオード P D 1 のための n 型半導体領域 19 が形成される。そして、図 11E に示されるように、p 型のイオン注入により、ピニング層 101 が必要に応じて形成され、図 11F に示されるように、高温のエピタキシャル成長により、n 型の半導体層 81b が形成される。

10

【0090】

以上説明した第 4 の製造方法によれば、例えば、100 nm 程度の厚みの半導体層 111 に対して、イオン注入により接続部 23 としての高濃度の不純物領域が形成される。そして、半導体層 111 全面に対して、高温のエピタキシャル成長により半導体層 121 (シリコン) が積み増しされた後、高温のエピタキシャル成長により、半導体層 81b が形成される。

20

【0091】

第 3 及び第 4 の製造方法のいずれにおいても、高濃度の不純物領域である接続部 23 が形成され、BOX 層 72 の界面が接続部 23 で覆われる。そして、形成された接続部 23 が、エピタキシャル成長により積み増した半導体層 81a' または 121 で覆われる。さらに、接続部 23 が半導体層 81a' または 121 で覆われた状態から、高温のエピタキシャル成長によりさらに半導体層 81b が形成される。従って、オートドープを抑制することができる。

20

【0092】

また、薄く形成された半導体層 81a に対して、コンタクトプラグ 31 とオーミックコンタクトをとる必要がある接続部 23 や、第 1 フォトダイオード P D 1 となる n 型半導体領域 19 を形成するためのイオン注入を行うことができるので、BOX 層 72 の界面近傍に不純物濃度分布 (プロファイル) のピーク Rp が存在する高濃度不純物領域の形成が可能となる。即ち、従来の 3 μm 程度の厚みの半導体層 73 でいうところの深い領域に、不純物濃度分布 (プロファイル) のピーク Rp が存在する接続部 23 と n 型半導体領域 19 を形成することができる。これにより、オートドープの抑制とコンタクト抵抗の低減を両立させることができる。また、接続部 23 以外の結晶性も改善することができ、白点、暗電流特性を改善することができる。

30

【0093】

なお、不純物濃度分布 (プロファイル) のピーク Rp が存在する BOX 层 72 の界面近傍とは、具体的には、電位障壁層 24 より界面側であり、BOX 层 72 の界面から 100 nm 以内を意味する。

40

【0094】

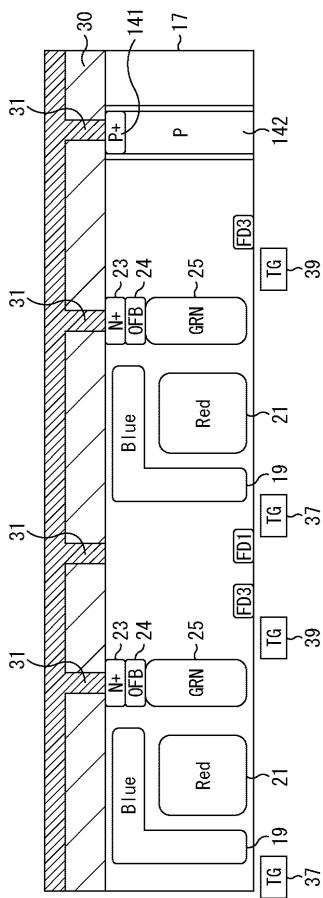

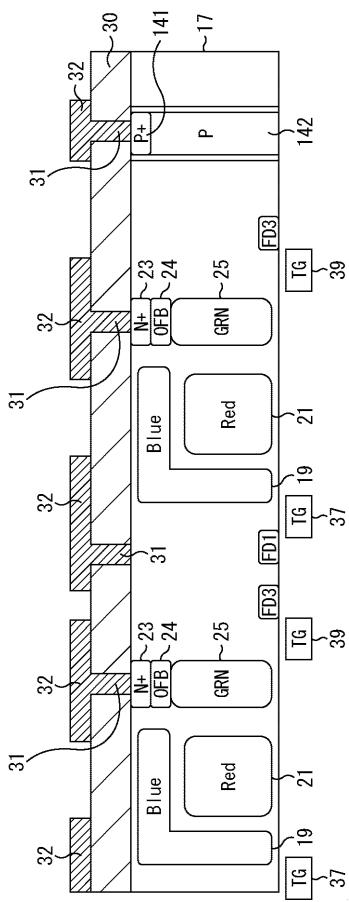

[1-9 半導体基板の裏面側の製造工程]

図 12 ないし図 15 を参照して、光入射面となる半導体基板 17 の裏面側の製造工程について、簡単に説明する。

【0095】

図 12 は、半導体層 81a と 81b とからなる半導体基板 17 に、第 2 フォトダイオード P D 2 となる n 型半導体領域 21 、縦型転送路 60 を構成する電位障壁層 24 及び電荷蓄積層 25 等を形成し、素子反転して、支持基板 71 と BOX 层 72 が除去された状態を示している。

【0096】

50

なお、図12ないし図15において、図3と対応する部分については同一の符号を付してあるので、その説明は省略する。また、図12ないし図14は概略の構成であるので、図3では図示されているが、図12ないし図15では図示されていないものもある。

#### 【0097】

一方、図12の接続部141とコンタクトプラグ142は、図3では図示されていないので簡単に説明する。接続部141は、最終的に、上部電極34a(図3)と接続される。上部電極34aは、ホールを引き抜くので、接続部141は、高濃度のp型の不純物領域で構成される。また、コンタクトプラグ142は、半導体基板17を貫通し、上部電極34aに所定の電位を与えるための表面側の回路と接続されている。コンタクトプラグ142は、p型の不純物領域で構成することができる。

10

#### 【0098】

図12の状態の後、図13に示されるように、半導体基板17の裏面側に反射防止層30が形成され、接続部23および接続部141の上部にコンタクトホールが形成される。そして、形成されたコンタクトホールに導電膜を埋め込むことで、コンタクトプラグ31が形成されるとともに、反射防止層30の上面にも同一の導電膜が積層される。

#### 【0099】

反射防止層30の上面に積層された導電膜は、図14に示されるように、遮光したい領域だけを残すように加工され、遮光膜32となる。従って、遮光膜32は、配線を兼用したものとなり、コンタクトプラグ31の材料をそのまま遮光膜32として残すことで、工程を増やすことなく、コンタクトプラグ31と遮光膜32を形成することができる。コンタクトプラグ31及び遮光膜32となる導電膜には、バリアメタル膜としてチタン(Ti)と窒化チタン(TiN)の積層膜、コンタクトホールに埋め込む金属材料としては、タンゲステン(W)を用いることが好ましい。

20

#### 【0100】

次に、図15に示されるように、遮光膜32上に絶縁膜33が形成され、CMP(chemical mechanical polishing: 化学的機械研磨)を用いて、絶縁膜33が平坦化される。

#### 【0101】

そして、平坦化された絶縁膜33のうち、遮光膜32かつコンタクトプラグ31の上部が開口され、そこにコンタクトプラグ32aが形成された後、下部電極34bと、そのエッジの段差を緩和するための絶縁膜35が形成される。この絶縁膜35は、全面に成膜した後に、テーパ形状を持ち、下部電極34bの表面を露出するようなエッティングを行うことで形成される。

30

#### 【0102】

次に、緑色の光を光電変換する有機光電変換膜36a、パッシベーション膜36b、及び上部電極34aが積層される。このとき、有機光電変換膜36aとパッシベーション膜36bは、下部電極34bおよび絶縁膜35の上部の全面に形成されるが、上部電極34aは、図15で有機光電変換膜36aとパッシベーション膜36bが形成されている一部の領域のみ形成される。そして、一部の領域のみに形成された上部電極34aをハードマスクとして、有機光電変換膜36aとパッシベーション膜36bが、図15で示される領域のみにエッティングされる。その後、上部電極34aの残りの領域、即ち、図15右端の接続部141に接続する下部電極34bとその両側の絶縁膜35の上面の上部電極34aが、形成される。また、黒基準画素領域の画素については、さらに、遮光膜151も形成される。

40

#### 【0103】

##### [1-10 駆動方法]

次に、固体撮像装置1の駆動方法について説明する。駆動方法については、図2及び図3を用いて説明する。

#### 【0104】

有機光電変換膜36aの受光面側に形成された上部電極34aには、固定の負電圧VLが印加され、コンタクトプラグ31に接続されている下部電極34bに電荷蓄積時におい

50

て、電圧  $V_L$  よりも高い電圧  $V_H$  が印加されている。電圧  $V_H$  はオーバーフロー・バリアの電位によって決定される。

#### 【0105】

電荷蓄積時において、1つの画素2に光が入射すると、緑の波長の光は、緑の波長光に吸収特性を有する有機光電変換膜36aにおいて光電変換され、有機光電変換膜36aにおいて電子・ホール対が形成される。この光電変換により生成された電子・ホール対のうち、信号電荷となる電子が、高い電圧  $V_H$  が印加されている下部電極34bに引かれ、コントラクトプラグ31を通って接続部23に転送される。そして、接続部23の飽和電荷量を超えた信号電荷は、電位障壁層24を超えて、電荷蓄積層25にオーバーフローされ、電荷蓄積層25において蓄積される。このとき、ホールは負電圧  $V_L$  が印加された上部電極34aに引かれ、図示しない所要の配線を通じて排出される。また、本実施形態例においては、下部電極34bには高い電圧  $V_H$  が印加されているので、半導体基板17の裏面側界面に暗電流が発生するバイアス電圧の極性に相当する。しかしながら、反射防止層30において酸化ハフニウムなどを用いることにより半導体基板17裏面にホールが励起された状態とされる。このため、下部電極34bに印加する電圧  $V_H$  に起因して半導体基板17界面に発生する暗電流を抑制することができる。

10

#### 【0106】

また、青色の波長の光は、受光面に近い半導体基板17内に形成された第1フォトダイオードPD1に吸収され光電変換される。これにより、青色の光に対応する信号電荷が第1フォトダイオードPD1のn型半導体領域19に蓄積される。赤色の波長の光は、受光面から深さ方向に深い半導体基板17内に形成された第2フォトダイオードPD2に吸収され光電変換される。これにより、赤色の光に対応する信号電荷が第2フォトダイオードPD2のn型半導体領域21に蓄積される。

20

#### 【0107】

そして、電荷蓄積が終了した後、第1ないし第3転送トランジスタTr1, Tr2, Tr3の転送ゲート電極37, 38, 39に所望の転送パルスが印加されることにより、電荷の読み出しが開始される。第1転送トランジスタTr1では、第1フォトダイオードPD1のn型半導体領域19に蓄積された青色の光に対応する信号電荷が延長部19aを通ってフローティングディフュージョン部FD1に読み出される。また、第2転送トランジスタTr2では、第2フォトダイオードPD2のn型半導体領域21に蓄積された赤色の光に対応する信号電荷がフローティングディフュージョン部FD2に読み出される。また、第3転送トランジスタTr3では、縦型転送路60の電荷蓄積層25に蓄積された緑色の光に対応する信号電荷がフローティングディフュージョン部FD3に読み出される。

30

#### 【0108】

そして、それぞれの信号電荷がそれぞれのフローティングディフュージョン部FD1, FD2, FD3に読み出されることによる電位変化が増幅トランジスタTr5, Tr8, Tr11によって増幅され、画素信号とされて図示しない垂直信号配線に読み出される。垂直信号配線に読み出されるタイミングは、選択トランジスタTr6, Tr9, Tr12によって決定される。

40

#### 【0109】

信号電荷の読み出し、転送後は、リセットトランジスタTr4, Tr7, Tr10によって、フローティングディフュージョン部FD1, FD2, FD3に読み出された信号電荷がリセットされる。

#### 【0110】

本実施の形態によれば、有機光電変換膜36aで生成された信号電荷を半導体基板17に形成した縦型転送路60において、接続部23から電荷蓄積層25内に縦方向にオーバーフローさせて転送し、電荷蓄積層25内に蓄積することができる。このような縦方向のオーバーフロー構造を有する縦型転送路60の形成は、上述したように、イオン注入のエネルギーによって精密に制御できるため、横方向のオーバーフロー構造よりも製造し易く、プロセスの制御性を向上させることができる。また、縦型転送路60は、半導体基板1

50

7の裏面側から表面側にかけて縦方向に形成されるため、画素サイズの増大を伴うことがなく、有機光電変換膜36aで生成された信号電荷を半導体基板17の裏面側から表面側に読み出すことができる。

【0111】

また、電荷蓄積層25は転送ゲート電極39に近接して形成できることから、電荷蓄積層25からフロー・ティング・ディフュージョン部FD3への転送にも有利な構成である。さらに、裏面照射型の固体撮像装置であるため、受光面となる半導体基板17の裏面側には多層配線層27が形成されないので、有機光電変換膜36aと半導体基板17に形成された第1及び第2フォトダイオードPD1, PD2とを近い距離に形成できる。これにより、有機光電変換膜36aと第1及び第2フォトダイオードPD1, PD2の距離が遠い場合に発生するF値による色毎の感度変動の影響も低減することができる。

10

【0112】

本実施の形態では、図2に示すような画素2の構成としたが、各画素トランジスタを複数の画素で共有する例としてもよい。

【0113】

<2. 第2の実施の形態>

[3色用の光電変換部を半導体層に形成する例]

上述した第1の実施の形態では、裏面照射型で半導体基板17上に1色用の光電変換層(有機光電変換膜36a)と、半導体基板17内に2色用の光電変換層(第1及び第2フォトダイオードPD1, PD2)とからなる構造が採用された。

20

【0114】

しかしながら、上述した第1ないし第4の製造方法のように、エピタキシャル成長により半導体層を積み増す方法によれば、図16に示されるような3色用(3層)の光電変換層201ないし203を半導体基板17内に形成することも可能である。

【0115】

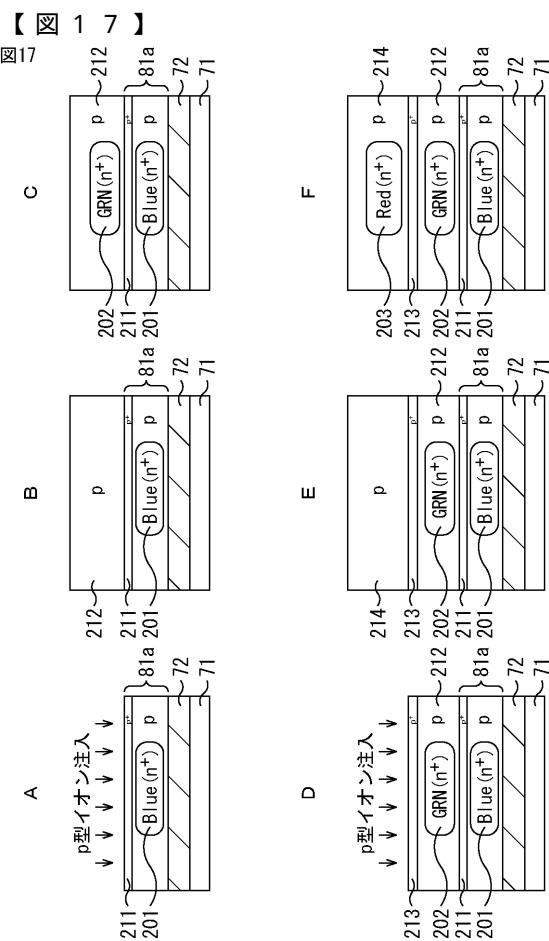

図17は、半導体基板17内に3層の光電変換層を形成する第1の製造方法を示している。

【0116】

青色の光電変換層201を形成するまでの工程、即ち、SOI基板80の半導体層81aに、n型の不純物領域として青色の光電変換層201を形成するまでの工程は、上述した第3および第4の製造方法と同様であるので、その説明は省略する。

30

【0117】

そして、n型の高濃度不純物領域として青色の光電変換層201が形成された半導体層81aに対して、図17Aに示されるように、ホウ素(B)などのp型の不純物のイオン注入が行われ、p型の高濃度不純物領域211が形成される。このp型の高濃度不純物領域211は、その上部に形成される緑色の光電変換層202と電気的に絶縁させ、混色を防止するためのものである。

【0118】

次に、図17Bに示されるように、エピタキシャル成長によりn型の半導体層212が積み増しされて形成され、そこに、p型の不純物がイオン注入されることで、半導体層212が、低濃度のp型の不純物領域とされる。

40

【0119】

次に、図17Cに示されるように、n型の不純物が高濃度にイオン注入されることにより、緑色の光電変換層202が形成される。

【0120】

そして、図17Dに示されるように、図17Aと同様に、緑色の光電変換層202と、その上部に形成される赤色の光電変換層203とを電気的に絶縁させるp型の高濃度不純物領域213がイオン注入により形成される。

【0121】

さらに、図17Eに示されるように、エピタキシャル成長によりn型の半導体層214

50

が積み増しされて形成され、そこに、p型の不純物がイオン注入されることで、半導体層214が、低濃度のp型の不純物領域とされる。

【0122】

そして、図17Fに示されるように、n型の不純物が高濃度にイオン注入されることにより、赤色の光電変換層203が形成される。

【0123】

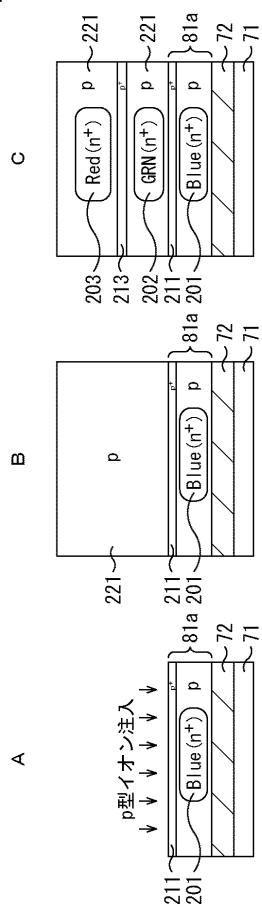

図18は、半導体基板17内に3層の光電変換層を形成する第2の製造方法を示している。

【0124】

図18Aに示される青色の光電変換層201を形成するまでの工程は、図17Aを参照して説明した方法と同様である。

【0125】

次に、図18Bに示されるように、エピタキシャル成長により、緑色と赤色の光電変換層202および203を形成可能な程度の厚みとなるまで、n型の半導体層221が積み増しされて形成され、そこに、p型の不純物がイオン注入されることで、半導体層221が低濃度のp型の不純物領域とされる。

【0126】

以下、図17Cないし図17Fを参照して説明した方法と同様の方法で、順次、緑色の光電変換層202、p型の高濃度不純物領域213、赤色の光電変換層203が形成され、図18Cに示されるように、3色の光電変換層201、202、および203が形成される。

【0127】

以上のように、エピタキシャル成長により半導体層を積み増す方法によって、3層の光電変換層を半導体基板17内に形成することも可能である。エピタキシャル成長により半導体層を積み増し、複数の光電変換層を半導体基板17内に形成する方法は、上述した裏面照射型の固体撮像装置のほか、表面照射型の固体撮像装置であっても適用可能である。

【0128】

上述した実施の形態では、第1に、SOI基板80, 112の予め形成された半導体層81a, 111に、高濃度の不純物をイオン注入して、接続部23およびn型半導体領域19が形成される。そして、第2に、エピタキシャル成長により半導体層81bが積み増しされる。これにより、半導体層の光入射面から浅い領域に、不純物濃度分布のピークRpを有する高濃度不純物領域を形成することができる。

【0129】

なお、上述した実施の形態では、半導体基板としてSOI基板(80, 112)を採用した例について説明した。しかし、BOX層72に代わりに、ホウ素(B)やアンチモン(Sb)などのドープ層でもよい。また、ドープ層がなくてもよい。

【0130】

また、上述した実施の形態では、半導体層の光入射面から浅い領域にある高濃度不純物領域の例として、接続部23およびn型半導体領域19を説明したが、その他の領域にも適用できることは言うまでもない。例えば、上部電極34aと接続される接続部141(図15)や、画素領域3以外の周辺回路のコンタクトの形成にも適用することができる。

【0131】

さらに、上述した実施形態では、電子を信号電荷としたもので、第1導電型をp型、第2導電型をn型としているが、本技術は正孔を信号電荷とする固体撮像装置にも適用することができる。すなわち、第1導電型をn型とし、第2導電型をp型として、前述の各半導体領域を逆の導電型の半導体領域で構成することができる。

【0132】

また、本技術は、可視光の入射光量の分布を検知して画像として撮像する固体撮像装置への適用に限らず、赤外線やX線、あるいは粒子等の入射量の分布を画像として撮像する固体撮像装置にも適用可能である。また、広義の意味として、圧力や静電容量など、他の

10

20

30

40

50

物理量の分布を検知して画像として撮像する指紋検出センサ等の固体撮像装置（物理量分布検知装置）全般に対して適用可能である。

【0133】

さらに、本技術は、画素部の各単位画素を行単位で順に走査して各単位画素から画素信号を読み出す固体撮像装置に限られるものではない。画素単位で任意の画素を選択して、当該選択画素から画素単位で信号を読み出すX-Yアドレス型の固体撮像装置に対しても適用可能である。なお、固体撮像装置はワンチップとして形成された形態であってもよいし、画素部と、信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール状の形態であってもよい。

【0134】

また、本技術は、固体撮像装置への適用に限られるものではなく、撮像装置にも適用可能である。ここで、撮像装置とは、デジタルスチルカメラやビデオカメラ等のカメラシステムや、携帯電話機などの撮像機能を有する電子機器のことを言う。なお、電子機器に搭載される上記モジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

10

【0135】

<3. 第3の実施の形態>

次に、第3の実施形態に係る電子機器について説明する。

【0136】

図19は、本技術が適用された第3の実施の形態に係る電子機器300の概略構成図である。

20

【0137】

図19の電子機器300は、上述した第1の実施形態における固体撮像装置1を電子機器（カメラ）に用いており、固体撮像装置1と、光学レンズ310と、シャッタ装置311と、駆動回路312と、信号処理回路313とを有する。

30

【0138】

光学レンズ310は、被写体からの像光（入射光）を固体撮像装置1の撮像面上に結像させる。これにより固体撮像装置1内に一定期間当該信号電荷が蓄積される。シャッタ装置311は、固体撮像装置1への光照射期間および遮光期間を制御する。駆動回路312は、固体撮像装置1の転送動作およびシャッタ装置311のシャッタ動作を制御する駆動信号を供給する。駆動回路312から供給される駆動信号（タイミング信号）により、固体撮像装置1の信号転送を行う。信号処理回路313は、各種の信号処理を行う。信号処理が行われた撮像信号は、メモリなどの記憶媒体に記憶され、あるいはモニタに出力される。

【0139】

本実施の形態の電子機器300では、固体撮像装置1において画素サイズを微細化及び転送効率が向上されるので、画素特性が向上する。固体撮像装置1を適用できる電子機器300としては、カメラに限られるものではなく、デジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置に適用可能である。

30

【0140】

本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

40

【0141】

なお、本技術は以下のよう構成も取ることができる。

(1)

裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、

前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、

前記半導体基板内に形成された1以上の第1光電変換部と

を備える固体撮像装置。

50

( 2 )

前記光入射面側の前記半導体基板上に積層され、下部電極及び上部電極で挟持された第1色用の第2光電変換部をさらに備え、

前記1以上の第1光電変換部は、前記半導体基板の深さ方向に積層された、第2色用の光電変換部と第3色用の光電変換部とからなり、

前記接続部には、前記第1色用の第2光電変換部で生成された前記信号電荷が供給される

前記(1)に記載の固体撮像装置。

( 3 )

前記接続部は、第1の厚みの半導体層の第1の領域を選択的にエッチングして第2の厚みにした後、不純物をイオン注入することにより形成され、

前記イオン注入後に、エッチングされた前記第1の領域がエピタキシャル成長により前記第1の厚みに埋め戻された後、前記第1の厚みの半導体層が、エピタキシャル成長により第3の厚みにさらに積み増しされて、前記半導体基板とされる

前記(1)または(2)に記載の固体撮像装置。

( 4 )

エピタキシャル成長により前記第1の厚みに埋め戻された後、前記第1の厚みの半導体層の、水平方向の位置が前記接続部と異なる第2の領域に、1つの前記第1光電変換部が形成される

前記(3)に記載の固体撮像装置。

( 5 )

前記接続部は、第1の厚みの半導体層の第1の領域に対して、不純物をイオン注入することにより形成され、

前記イオン注入後に、前記第1の厚みの半導体層が、エピタキシャル成長により第2の厚みに積み増しされ、

前記第2の厚みの半導体層が、さらに、エピタキシャル成長により第3の厚みに積み増しされて、前記半導体基板とされる

前記(1)乃至(4)のいずれかに記載の固体撮像装置。

( 6 )

エピタキシャル成長により前記第2の厚みに積み増しされた後、前記第2の厚みの半導体層の、水平方向の位置が前記接続部と異なる第2の領域に、1つの前記第1光電変換部が形成される

前記(5)に記載の固体撮像装置。

( 7 )

前記不純物濃度分布のピークが、前記裏面側の前記半導体基板の界面から100nm以内の位置にある

前記(1)乃至(6)のいずれかに記載の固体撮像装置。

( 8 )

第1の厚みの半導体基板の第1の領域に不純物をイオン注入することにより、前記半導体基板の光入射面となる裏面側で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部を形成する接続部形成工程と、

前記第1の厚みの半導体基板をエピタキシャル成長により第2の厚さまで積み増す第1の半導体層形成工程と、

前記第2の厚みの半導体基板の、前記接続部と水平方向の位置が異なる第2の領域に、第1の波長の光を光電変換する第1の光電変換層を形成する第1の光電変換層形成工程と、

前記第2の厚みの半導体基板を、エピタキシャル成長により、第3の厚みまで積み増す第2の半導体層形成工程と

を含む固体撮像装置の製造方法。

10

20

30

40

50

( 9 )

前記接続部形成工程は、前記第1の厚みより厚い第4の厚みから選択的にエッティングされ前記第1の厚みとされた前記半導体基板の前記第1の領域に不純物をイオン注入することにより、前記接続部を形成し、

前記第1の半導体層形成工程は、前記イオン注入後に、エッティングされた前記第1の領域を、エピタキシャル成長により前記第1の厚みと同じ前記第2の厚さに埋め戻す

前記(8)に記載の固体撮像装置の製造方法。

( 10 )

前記第3の厚みの半導体基板の、前記第1の光電変換層よりも前記裏面側から離れた深さ方向の位置に、第2の波長の光を光電変換する第2の光電変換層を形成する第2の光電変換層形成工程をさらに備える

10

前記(8)または(9)のいずれかに記載の固体撮像装置の製造方法。

( 11 )

光学レンズで集光された光が入射される固体撮像装置と、

前記固体撮像装置の出力信号を処理する信号処理回路と

を備え、

前記固体撮像装置は、

裏面側が光入射面とされ、表面側が回路形成面とされた半導体基板と、

前記裏面側の前記半導体基板上で生成された信号電荷を前記半導体基板内に転送するコンタクトプラグと接続される接続部であって、前記裏面側の前記半導体基板の界面近傍に不純物濃度分布のピークを有する接続部と、

20

前記半導体基板内に形成された1以上の光電変換部と

を備える電子機器。

【符号の説明】

【0142】

1 固体撮像装置, 2 画素, 3 画素領域, 16 ウエル領域, 17 半導

体基板(半導体層), 19 n型半導体領域, 20 p型半導体領域, 21 n型

半導体領域, PD1 第1フォトダイオード, PD2 第2フォトダイオード, 2

3 接続部, 34a 上部電極, 34b 下部電極, 36a 有機光電変換膜,

36b パッシベーション膜, 31 コンタクトプラグ, 32 遮光膜, 32a

コンタクトプラグ, 300 電子機器, 310 光学レンズ, 313 信号処理回

路

30

【図1】

図1

1 固体撮像装置

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5【図6】

図6【図7】

図7【図8】

図8【図9】

図9

【図 1 0】

図10

【図 1 1】

図11

【図 1 2】

図12

【図 1 3】

図13

【図14】

【 図 1 6 】

【 図 1 5 】

【 図 1 7 】

【図18】

図18

【図19】

図19