(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 697 31 936 T2 2005.06.23

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 854 611 B1

(21) Deutsches Aktenzeichen: 697 31 936.9

(96) Europäisches Aktenzeichen: 97 310 656.0

(96) Europäischer Anmeldetag: 30.12.1997

(97) Erstveröffentlichung durch das EPA: 22.07.1998

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 15.12.2004

(47) Veröffentlichungstag im Patentblatt: 23.06.2005

(51) Int Cl.<sup>7</sup>: H04L 12/44

H04L 12/40, H04L 12/56

(30) Unionspriorität:

**774605 30.12.1996 US**

(84) Benannte Vertragsstaaten:

**DE, FR, GB**

(73) Patentinhaber:

**Compaq Computer Corp., Houston, Tex., US**

(72) Erfinder:

**Walker, William J., Houston, Texas 77070, US;

Kotzur, Gary B., Spring, Texas 77388, US; Hareski,

Patricia E., Houston, Texas 77070, US; Mayer, Dale

J., Houston, Texas 77070, US; Witkowski, Michael

L., Tomball, Texas 77375, US**

(74) Vertreter:

**Grünecker, Kinkeldey, Stockmair &

Schwanhäusser, 80538 München**

(54) Bezeichnung: **Netzwerkkoppelfeld mit Mehrfachbusarchitektur**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung**

**[0001]** Die vorliegende Erfindung betrifft das Gebiet von Netzwerk-Vorrichtungen und insbesondere einen Netzwerkschalter mit einer Mehrfachbus-Architektur.

**[0002]** Es gibt viele verschiedene Arten von Netzwerken und Netzwerksystemen, die sich in Dateien und Ressourcen teilen oder anderweitig eine Kommunikation zwischen zwei oder mehr Computern ermöglichen. Netzwerke können auf der Basis verschiedener Merkmale und Funktionen kategorisiert werden, z. B. Nachrichtenkapazität, Bereich, über den die Knoten verteilt sind, Knoten- oder Computertypen, Knotenbeziehungen, Architektur oder Struktur basierend auf Kabeltyp und Datenpaketformat, Zugriffsmöglichkeiten usw. Zum Beispiel bezieht sich der Bereich eines Netzwerks auf die Entfernung, über die die Knoten verteilt sind, z. B. Lokale Netzwerke (LANs) in einem Büro oder einer Etage eines Gebäudes, Weitbereichs-Netzwerke (WANs), die eine Hochschulanlage, eine Stadt oder einen Staat überspannen, Globale Netzwerke (GANs), die nationale Grenzen überspannen, usw.

**[0003]** Die Struktur eines Netzwerks bezieht sich im Allgemeinen auf die verwendete Verkabelung oder Medien und Medienzugang sowie die Paketstruktur der über die Medien zu sendenden Daten. Verschiedene Strukturen sind üblich, einschließlich Ethernet, das Koaxialkabel, verdrillte Kabelpaare oder faseroptische Kabel zum Betrieb bei 10 Megabit pro Sekunde (Mbps) (z. B. 10Base-T, 10Base-F) verwendet, oder schnelles Ethernet, das bei 100 Mbps (100Base-T, 100Base-FX) arbeitet. ARCnet (Attached Resource Computer Network) ist eine relativ billige Netzwerkstruktur, die Koaxialkabel, verdrillte Kabelpaare oder faseroptische Kabel zum Betrieb bei 2.5 Mbps verwendet. Tokenring-Topologien verwenden spezielles IBM-Kabel oder faseroptisches Kabel zum Betrieb bei 1–16 Mbps. Natürlich sind viele andere Arten von Netzwerken bekannt und verfügbar.

**[0004]** Jedes Netzwerk enthält im Allgemeinen zwei oder mehr Computer, oft als Knoten oder Stationen bezeichnet, die durch ausgewählte Medien oder verschiedene andere Netzwerk-Vorrichtungen miteinander verbunden sind, um die Daten zwischen den Knoten weiterzuleiten, zu übertragen, zu wiederholen, zu übersetzen, zu filtern usw. Der Begriff "Netzwerk Vorrichtung" betrifft gewöhnlich die Computer und ihre Netzwerk-Schnittstellenkarten (NICs) sowie verschiedene andere Vorrichtungen auf dem Netzwerk, z. B. Repeater, Brücken, Schalter, Router, Brouter, um einige Beispiele zu nennen. Ein Netzwerk, das entsprechend einem gegebenen Kommunikationsprotokoll arbeitet, kann unter Verwendung von einem oder mehreren Repeatern, Brücken oder Schaltern erweitert werden. Ein Repeater ist eine Hardware-Vorrichtung, die auf der physikalischen Schicht arbeitet und jedes empfangene Paket an jeden anderen Port weitersendet. Eine Brücke arbeitet auf der Datenverbindungsschicht des OSI-Referenzmodells und erhöht die Effizienz durch Filtern von Paketen, um die Menge an unnötiger Paketausbreitung auf jedem Netzwerksegment zu verringern.

**[0005]** Ein Netzwerkschalter funktioniert ähnlich, doch effizienter, wie eine Multiport-Brücke, die eine Vielzahl von Ports zum Verbinden mit mehreren ähnlichen Netzwerken zum Dirigieren des Netzwerkverkehrs unter den Netzwerken enthält. Ein Netzwerkschalter umfasst gewöhnlich eine mit den Ports über einen Bus verbundene Schaltmatrix und einen Speicher, um Netzwerksdaten, z. B. Ethernet-Pakete oder dergleichen, vorübergehend zu speichern. Gewöhnlich ist ein erhebliches Verarbeitungsvermögen erforderlich, um den Verkehr zu dirigieren und andere Aufgaben durchzuführen, z. B. Initialisierung, Konfigurierung, statistische Überwachung und Netzwerk-Verwaltung, um einige Beispiele zu nennen. Die Netzwerk-Verwaltung umfasst die Speicherverwaltung, Ausführung des Spannbaum-Algorithmus nach dem IEEE (Institute of Electrical and Electronics Engineers) 802.1 Standard, Unterhaltung und Verwaltung der Verwaltungs-Informationsbasis-(MIB) oder MIB II Struktur usw.

**[0006]** Typische Schalter-Architekturen weisen einen Primärbus für allen Netzwerk- und Prozessorverkehr auf. Solche Overhead-Funktionen benötigen wenigstens einen mit dem Bus verbundenen Prozessor oder dergleichen, um die Ports, die Schalterstruktur und den Speicher zu überwachen und zu verwalten. Die Overhead-Funktionen benötigen erhebliche Prozessorzeit und Busbandbreite, die mit dem normalen Netzwerkverkehr in Konflikt geraten, wodurch die Leistung des Schalters verlangsamt und verschlechtert wird. Eine solche Leistungsverschlechterung führt oft zu einer bedeutsamen Zahl von fallen gelassenen Paketen, besonders bei starker Belastung.

**[0007]** Es besteht der Wunsch, einen Netzwerkschalter mit verbesserter Kapazität bereitzustellen, um den Netzwerkverkehr auch bei starker Belastung zu handhaben. Es ist daher erwünscht, einen Netzwerkschalter bereitzustellen, der den Netzwerkverkehr handhaben kann, während er auch Netzwerk-Overhead-Funktionen, z. B. Initialisierung, Konfigurierung, Überwachung und Netzwerk-Verwaltung, durchführt.

**[0008]** WO 9613922 A offenbart ein Computernetzwerk-Schaltsystem mit einem Schaltstruktur-Schaltkreis, der eine Vielzahl von Ports umfasst, die mit einem entsprechenden einer Vielzahl von LAN-Segmenten verbunden sind. Der Schaltstruktur-Schaltkreis dient zum Empfangen von Anforderungen für Datenübertragungsoperationen von der Vielzahl von Ports und zum Priorisieren der Anforderungen während einer Synchronisationsperiode. Es wird offenbart, dass jedes LAN-Segment nach einem unterschiedlichen LAN-Kommunikationsprotokoll arbeiten kann.

**[0009]** Gemäß US-A-5546385 wird ein Netzwerkschalter bereitgestellt, der umfasst: eine Vielzahl von Netzwerkports zum Empfangen und Senden von Daten, wobei jeder umfasst: eine Netzwerk-Schnittstelle, eine Datenbus-Schnittstelle und eine Prozessorport-Schnittstelle, wobei der Netzwerkschalter weiter einen Datenbus, der mit der Datenbus-Schnittstelle jedes der Vielzahl von Netzwerk-Ports verbunden ist, einen Prozessor, der mit einem Prozessorbus verbunden ist, der mit der Prozessorport-Schnittstelle jedes der Vielzahl von Netzwerkports verbunden ist, und einen Speicher umfasst, der mit einem Speicherbus verbunden ist.

**[0010]** Die vorliegende Erfindung ist gekennzeichnet durch einen Schalter-Manager, der mit dem Datenbus, dem Prozessorbus und einem weiteren Prozessorbus verbunden ist, der mit jedem der Vielzahl von Netzwerkports verbunden ist, und mit dem Speicherbus verbunden ist, um den Datenfluss zwischen der Vielzahl von Netzwerkports und dem Speicher zu steuern und dem Prozessor zu ermöglichen, auf jeden der Vielzahl von Netzwerk-Ports und den Speicher zuzugreifen, wobei der Speicher-Manager umfasst:

eine Datenbus-Schnittstelle, die mit dem Datenbus verbunden ist und umfasst:

eine Abfragelogik, die periodisch abfragt, um den Status jedes der Vielzahl von Netzwerk ports zu bestimmen, und

eine Steuerlogik, die mit der Abfragelogik verbunden ist, wobei die Steuerlogik den Datenfluss zwischen der Vielzahl von Netzwerkports, dem Prozessor und einer Speicherbus-Schnittstelle steuert,

wobei die Speicherbus-Schnittstelle mit dem Speicherbus und der Datenbus-Schnittstelle verbunden ist, und

eine Prozessorbus-Schnittstelle, die mit dem Prozessorbus, der Datenbus-Schnittstelle und der Speicherbus-Schnittstelle verbunden ist.

**[0011]** Auf diese Weise hat der Prozessor direkten und unabhängigen Zugriff auf die Netzwerk ports zur Überwachung, Bestimmung des Status, Konfiguration und Verwaltung, ohne wertvolle Bandbreite des Datenbusses zu verbrauchen.

**[0012]** Die Datenbus-Schnittstelle enthält vorzugsweise Empfangs- und Sendepuffer zum Übertragen von Daten, wenigstens eine Zustandsmaschine zum periodischen Abfragen der Ports, um ihren Status zu bestimmen, und Steuerlogik zum Steuern des Datenflusses zwischen den Ports und zwischen den Ports und dem Speicher. Die Speicherbus-Schnittstelle kann eine Speichersteuerung zum Steuern von Speicherzyklen des Speichers und einen Arbitr umfassen, um den Zugriff auf den Speicher durch die Speichersteuerung zu steuern. Die Speicherbus-Schnittstelle kann auch eine Empfangssteuerung zum Steuern des Datenflusses von der Datenbus-Schnittstelle zum Speicher und eine Sendesteuerung zum Steuern des Datenflusses vom Speicher zu der Datenbus-Schnittstelle enthalten. Die Speicherbus-Schnittstelle kann weiter eine Auffrischungssteuerung zum Aufrechterhalten des Zustands des Speichers über den Speicherbus enthalten, um so den Prozessor von Auffrischungsfunktionen zu befreien.

**[0013]** Der Prozessorbus kann einen zwischen den Schalter-Manager und den Prozessor geschalteten Prozessorabschnitt und einen zwischen den Schalter-Manager und jeden der Ports geschalteten Portabschnitt enthalten. Die Prozessorbus-Schnittstelle des Schalter-Managers kann eine Prozessor-Schnittstelle, die mit dem Prozessor durch den Prozessorabschnitt des Prozessorbusses verbunden ist, und eine Port-Schnittstelle enthalten, die mit der Prozessor-Schnittstelle und mit jedem der Netzwerkports durch den Portabschnitt des Prozessorbusses verbunden ist. Die Prozessor- und Portbusabschnitte können die gleiche Größe haben. In der gezeigten und hierin beschriebenen Ausführung weisen jedoch die Prozessor und Portabschnitte des Prozessorbusses verschiedene Breiten auf, wo die Prozessor-Schnittstelle eine Zustandsmaschine enthält, die Zyklen zwischen den Prozessor- und Portabschnitten des Prozessorbusses übersetzt. Jeder der Netzwerkports kann einen oder mehr Statistik-Zähler zum Verfolgen des Status und Betriebs seines entsprechenden Ports enthalten, wobei die Zähler verbunden und daher für den Portabschnitt des Prozessorbusses ohne weiteres verfügbar sind. Auf diese Weise hat der Prozessor unabhängigen und vollständigen Zugriff auf jeden der Ports zum Durchführen von Overhead-Funktionen während des Betriebs, ohne Aktivitäten auf dem Datenbus zu stören.

**[0014]** Die Prozessorbus-Schnittstelle kann ferner dem Prozessor gestatten, auf den Datenbus und den Speicher durch die Speicherbus-Schnittstelle zuzugreifen. Das heißt, die Prozessorbus-Schnittstelle enthält geeig-

nete Sende- und Empfangspuffer und eine erste Steuerung zum Steuern des Datenflusses zwischen der Prozessorbus-Schnittstelle und der Datenbus-Schnittstelle und eine zweite Steuerung zum Steuern des Datenflusses zwischen der Prozessorbus-Schnittstelle und der Speicherbus-Schnittstelle.

[0015] Bei der hierin beschriebenen einzelnen Ausführung eines erfindungsgemäßen Netzwerkschalters umfasst die Vielzahl von Netzwerkports eine Gruppe von Ports, die entsprechend einem ersten mit dem ersten Datenbus verbundenen Protokoll arbeiten, und eine zweite Gruppe von Ports, die entsprechend einem zweiten Protokoll arbeiten. Ein zweiter Datenbus wird zum schnittstellenmäßigen Verbinden der zweiten Gruppe von Ports bereitgestellt, und eine Brückenvorrichtung ist zwischen den ersten und den zweiten Datenbus geschaltet. In der gezeigten Ausführung arbeitet die erste Gruppe von Ports entsprechend dem Ethernet-Standard bei 10 Mbps, während die zweite Gruppe entsprechend dem Ethernet-Standard bei 100 Mbps arbeitet, obwohl einzusehen ist, dass die vorliegende Erfindung nicht auf ein bestimmtes Protokoll oder Datenübertragungsgeschwindigkeit begrenzt ist.

[0016] Ein erfindungsgemäßes Netzwerksystem umfasst eine Vielzahl von Netzwerken, wobei jedes wenigstens eine Datenvorrichtung zum Senden und Empfangen von Datenpaketen und einen Netzwerkschalter, wie oben beschrieben, enthält, der mit den Netzwerken zum Übertragen der Datenpakete verbunden ist.

[0017] Die vorliegende Erfindung kann besser verstanden werden, wenn die folgende ausführliche Beschreibung der bevorzugten Ausführung in Verbindung mit den folgenden Zeichnungen in Betracht gezogen wird. Inhalt der Zeichnungen:

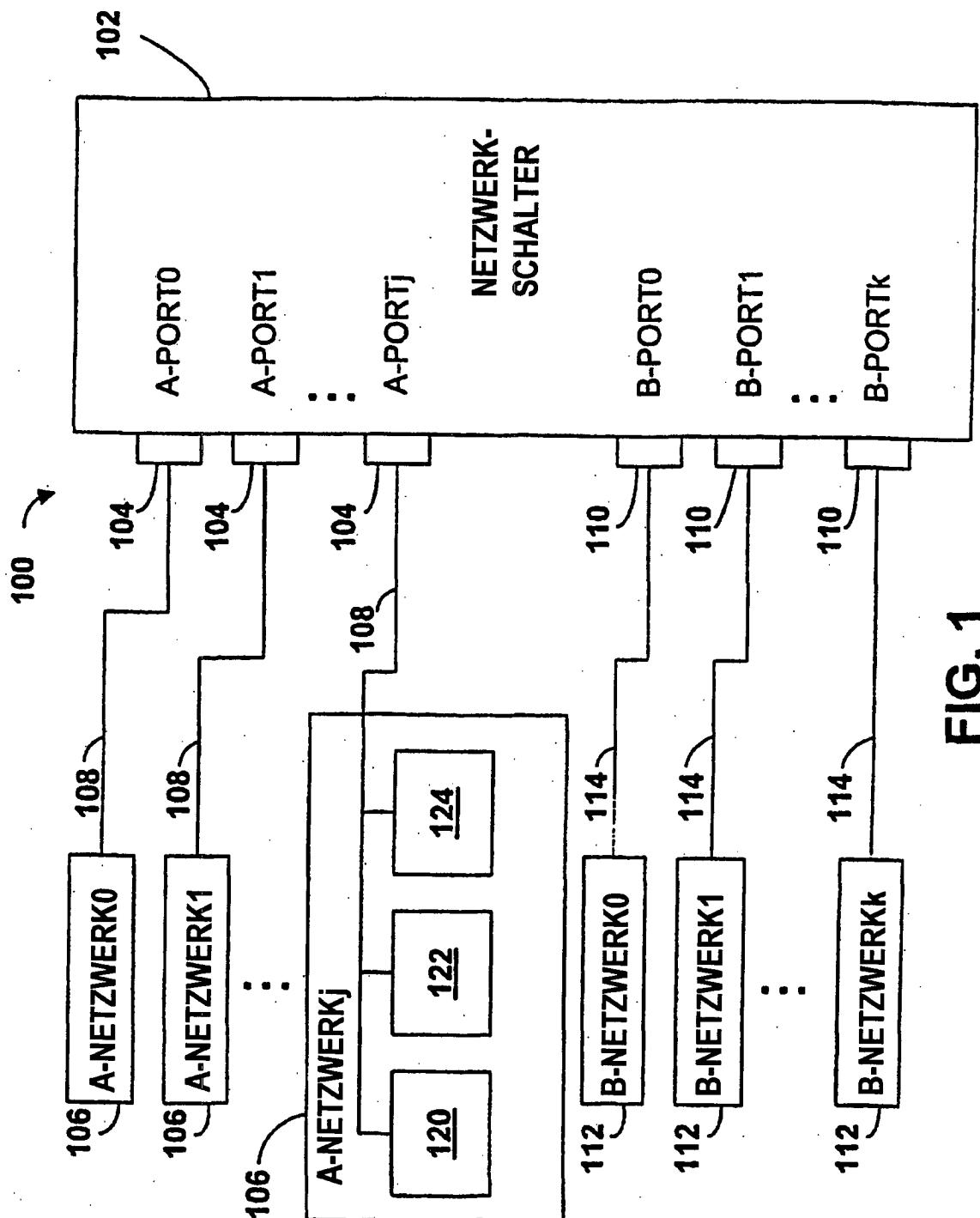

[0018] [Fig. 1](#) ist ein vereinfachtes Schaltbild eines Netzwerksystems, das einen erfindungsgemäßen Netzwerkschalter enthält.

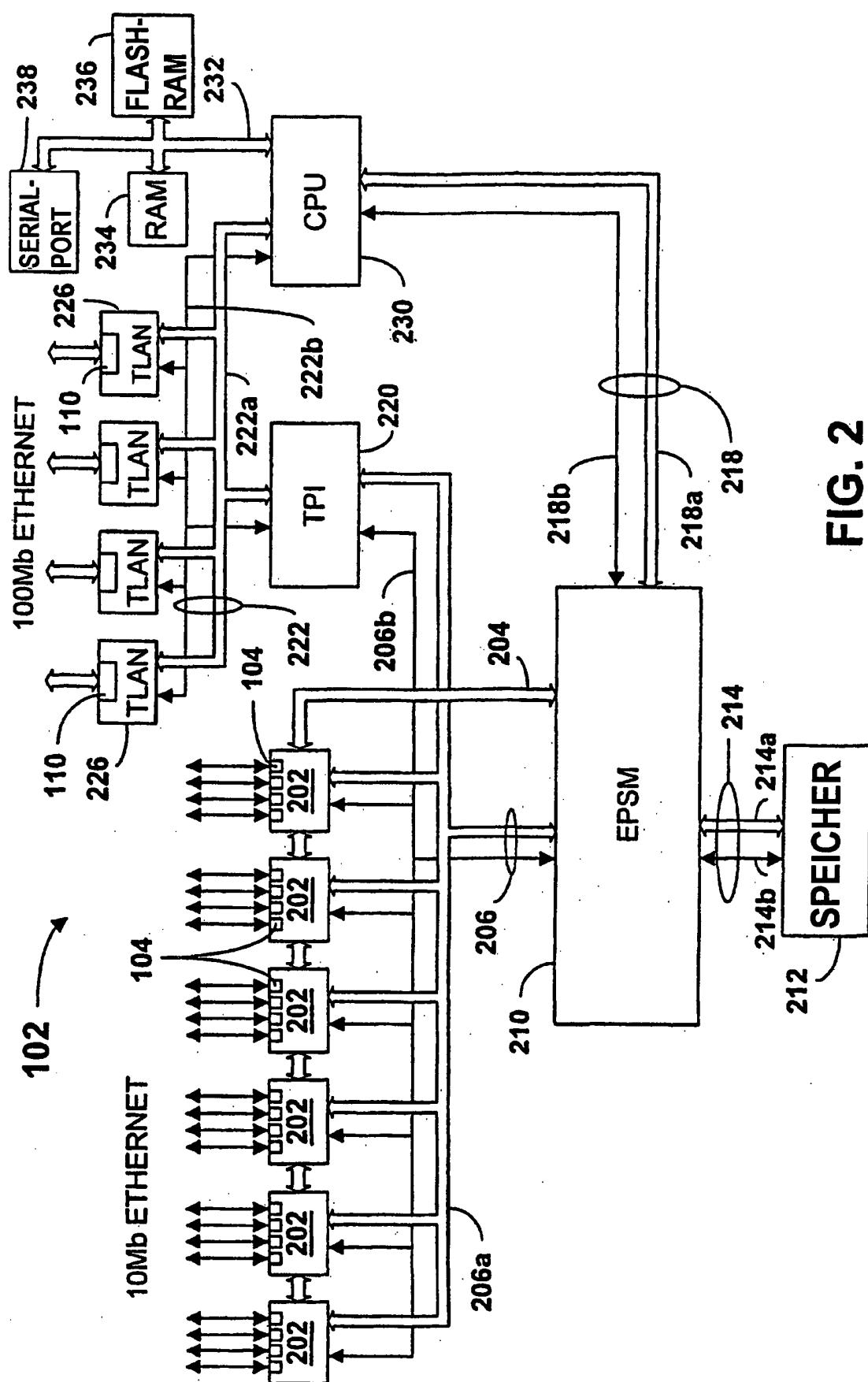

[0019] [Fig. 2](#) ist ein genaueres Blockschaltbild des Netzwerkschalters von [Fig. 1](#).

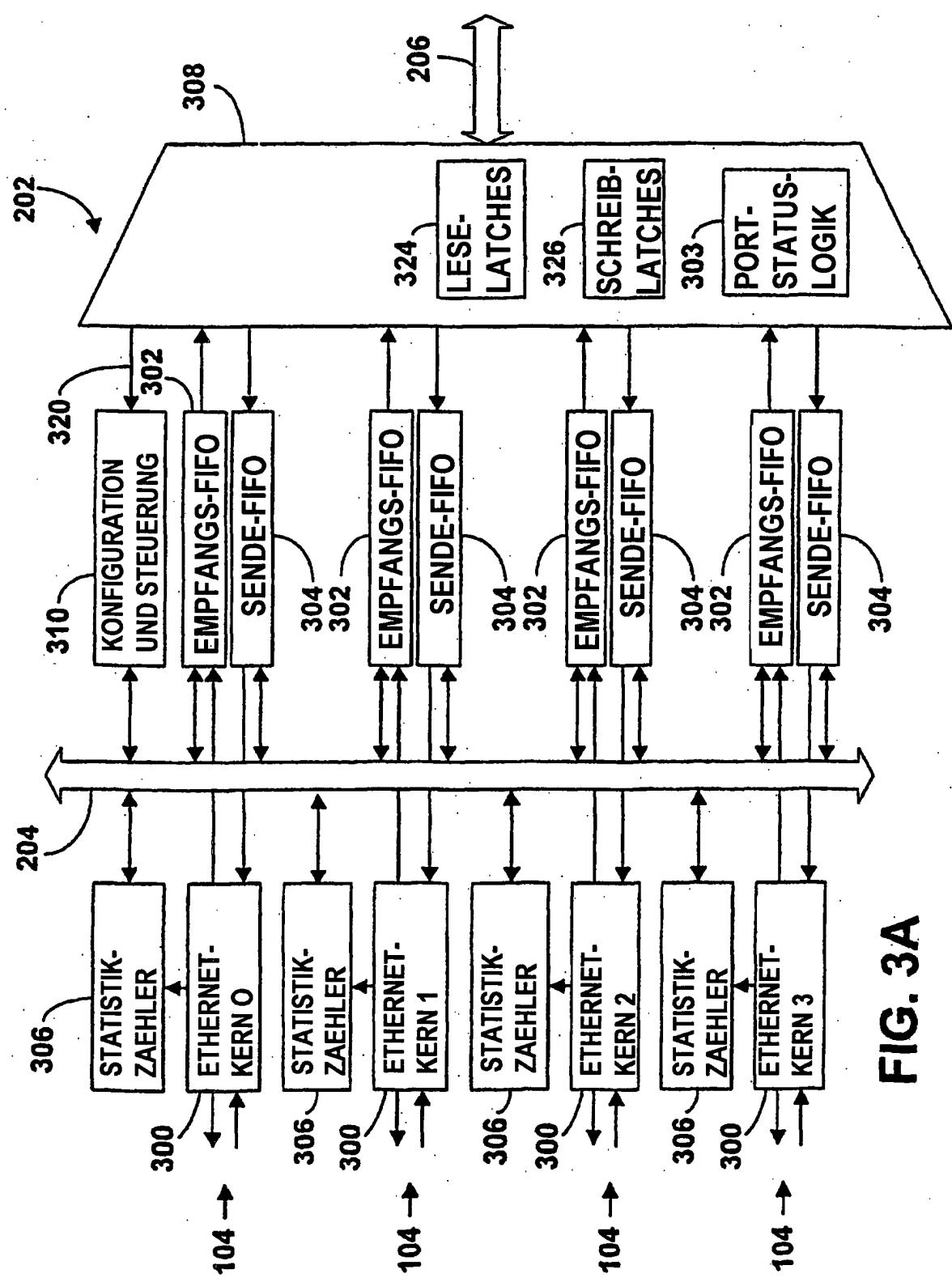

[0020] [Fig. 3A](#) ist ein Blockschaltbild einer exemplarischen Vierfach-Kaskaden-Vorrichtung von [Fig. 2](#) zur Implementierung der Ports des Netzwerkschalters.

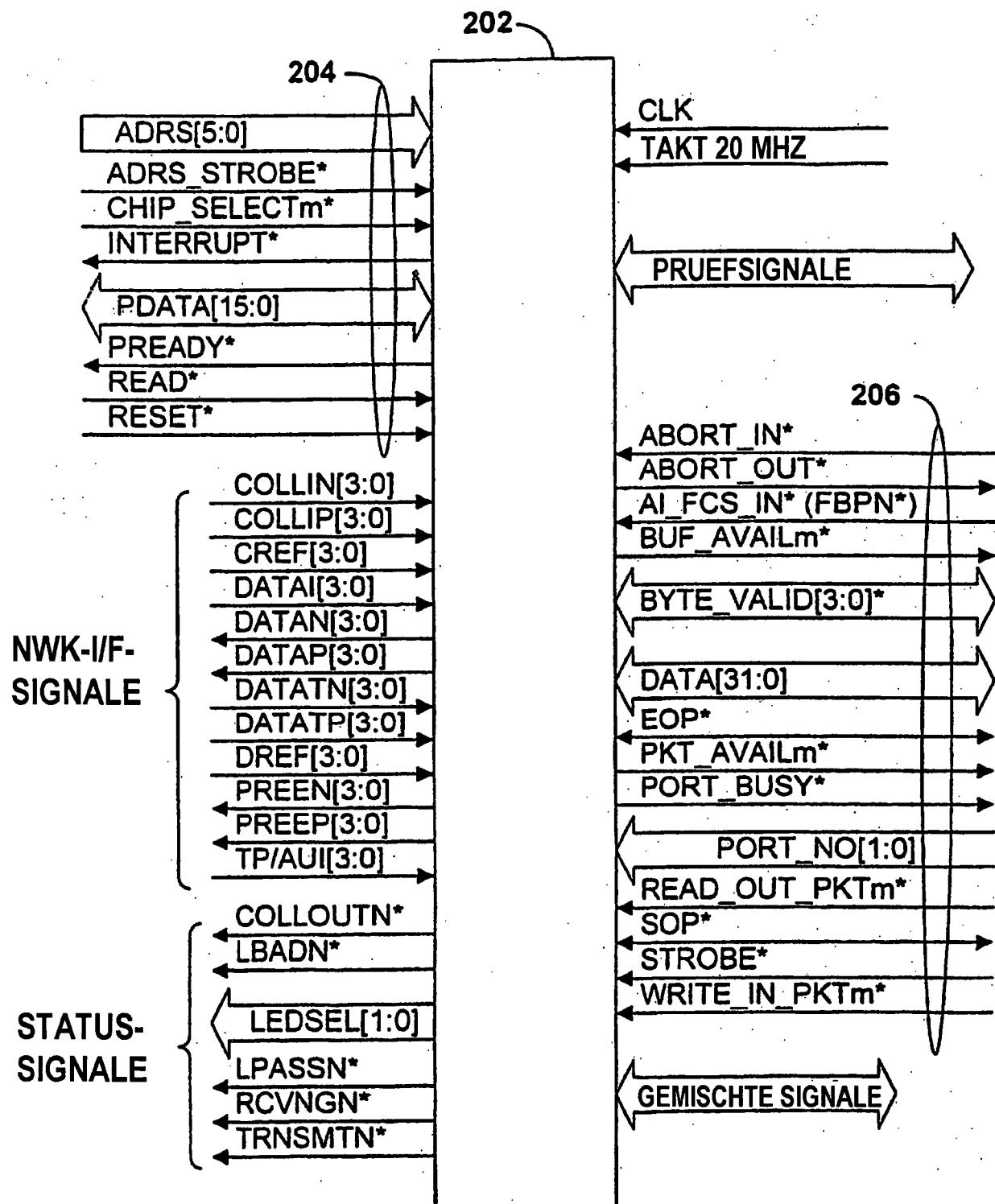

[0021] [Fig. 3B](#) ist ein Diagramm, das die Signale der in [Fig. 3A](#) gezeigten einzelnen Vierfach-Kaskaden-Vorrichtung veranschaulicht.

[0022] [Fig. 3C](#) ist ein exemplarisches Timing-Diagramm, das das Prozessor-Lesetiming der Vierfach-Kaskaden-Vorrichtung von [Fig. 3A](#) veranschaulicht.

[0023] [Fig. 3D](#) ist ein exemplarisches Timing-Diagramm, das das Prozessor-Schreibtiming der Vierfach-Kaskaden-Vorrichtung von [Fig. 3A](#) veranschaulicht.

[0024] [Fig. 3E](#) ist ein exemplarisches Timing-Diagramm, das das Prozessor-Burst-Lesezugriffstimering der Vierfach-Kaskaden-Vorrichtung von [Fig. 3A](#) veranschaulicht.

[0025] [Fig. 3F](#) ist ein exemplarisches Timing-Diagramm, das eine Pufferstatusabfrage jedes der Ports von [Fig. 3A](#) veranschaulicht.

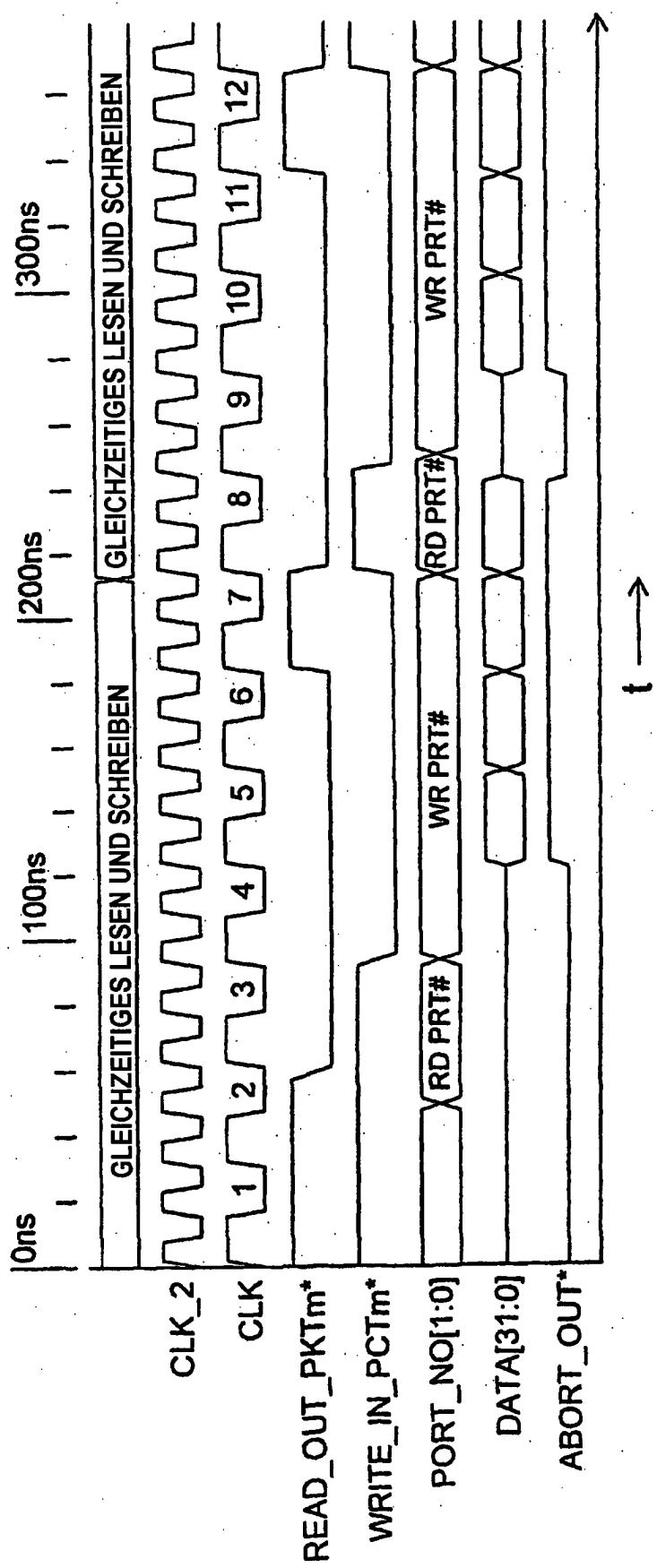

[0026] [Fig. 3G](#) ist ein exemplarisches Timing-Diagramm, das einen gleichlaufenden Lese- und Schreibzyklus auf dem HSB von [Fig. 2](#) veranschaulicht.

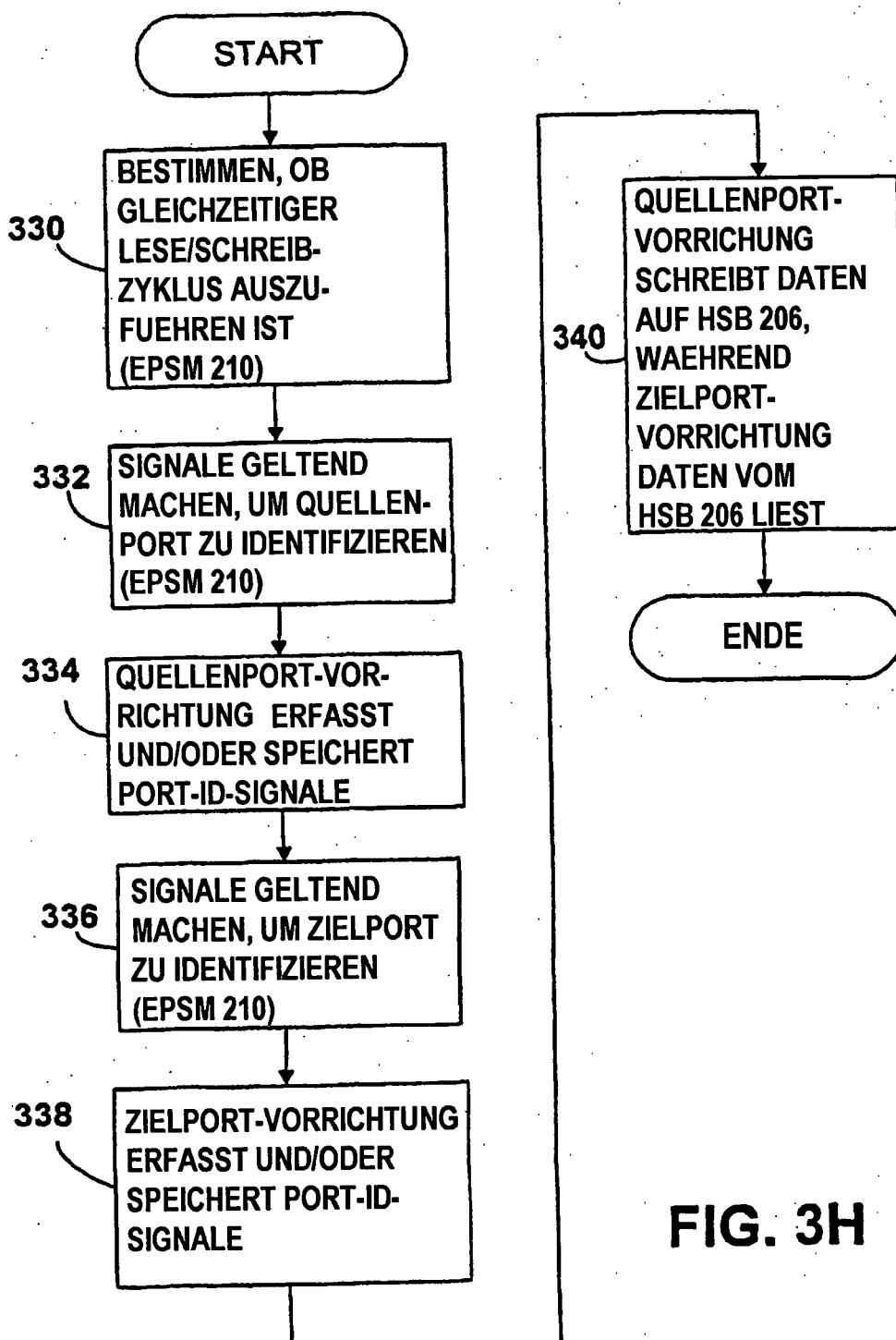

[0027] [Fig. 3H](#) ist ein Flussdiagramm, das eine Prozedur zum Ausführen eines gleichlaufenden Lese- und Schreibzyklusses auf dem HSB von [Fig. 2](#) veranschaulicht.

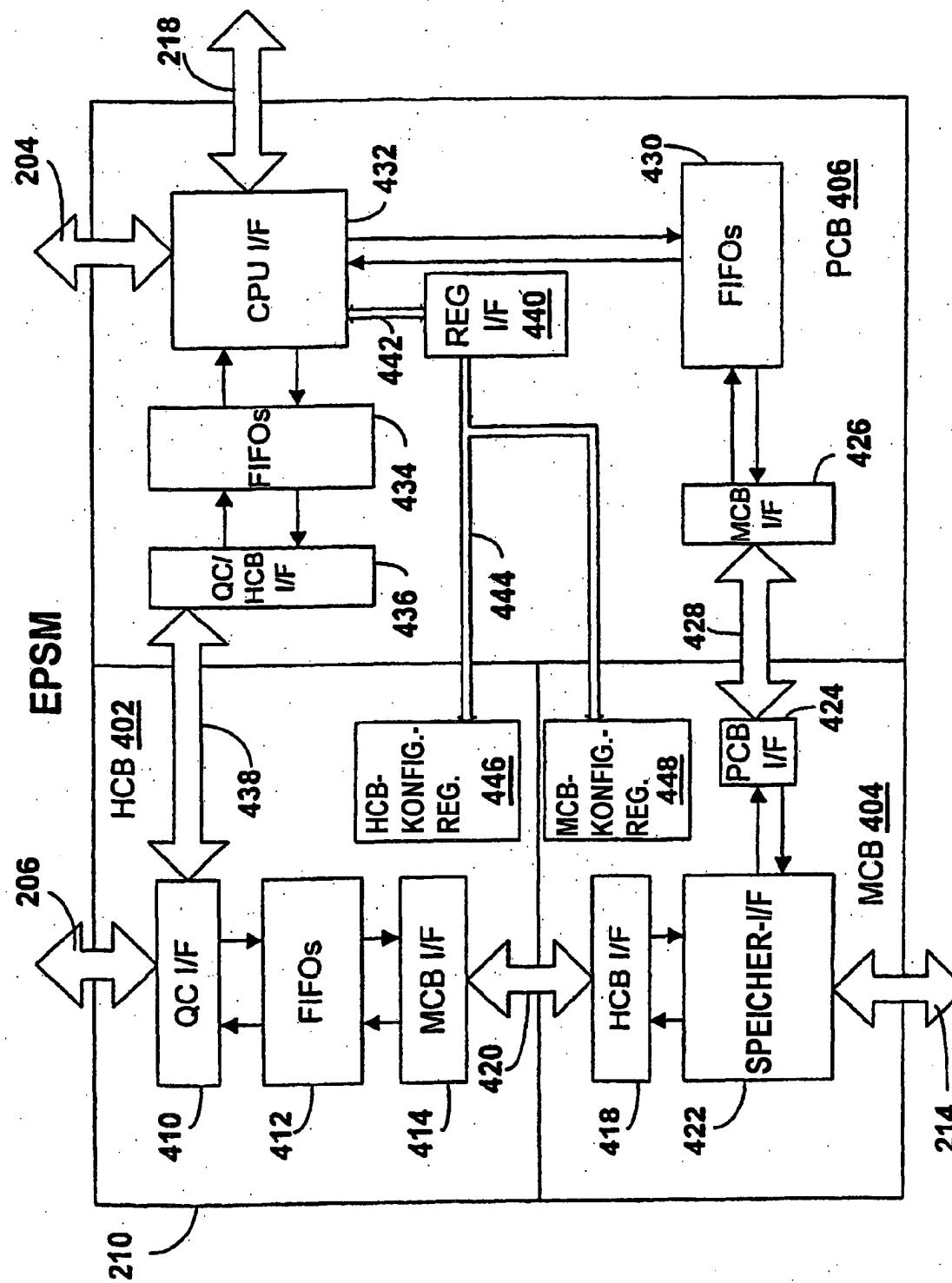

[0028] [Fig. 4](#) ist ein Blockschaltbild des Schalter-Managers von [Fig. 2](#).

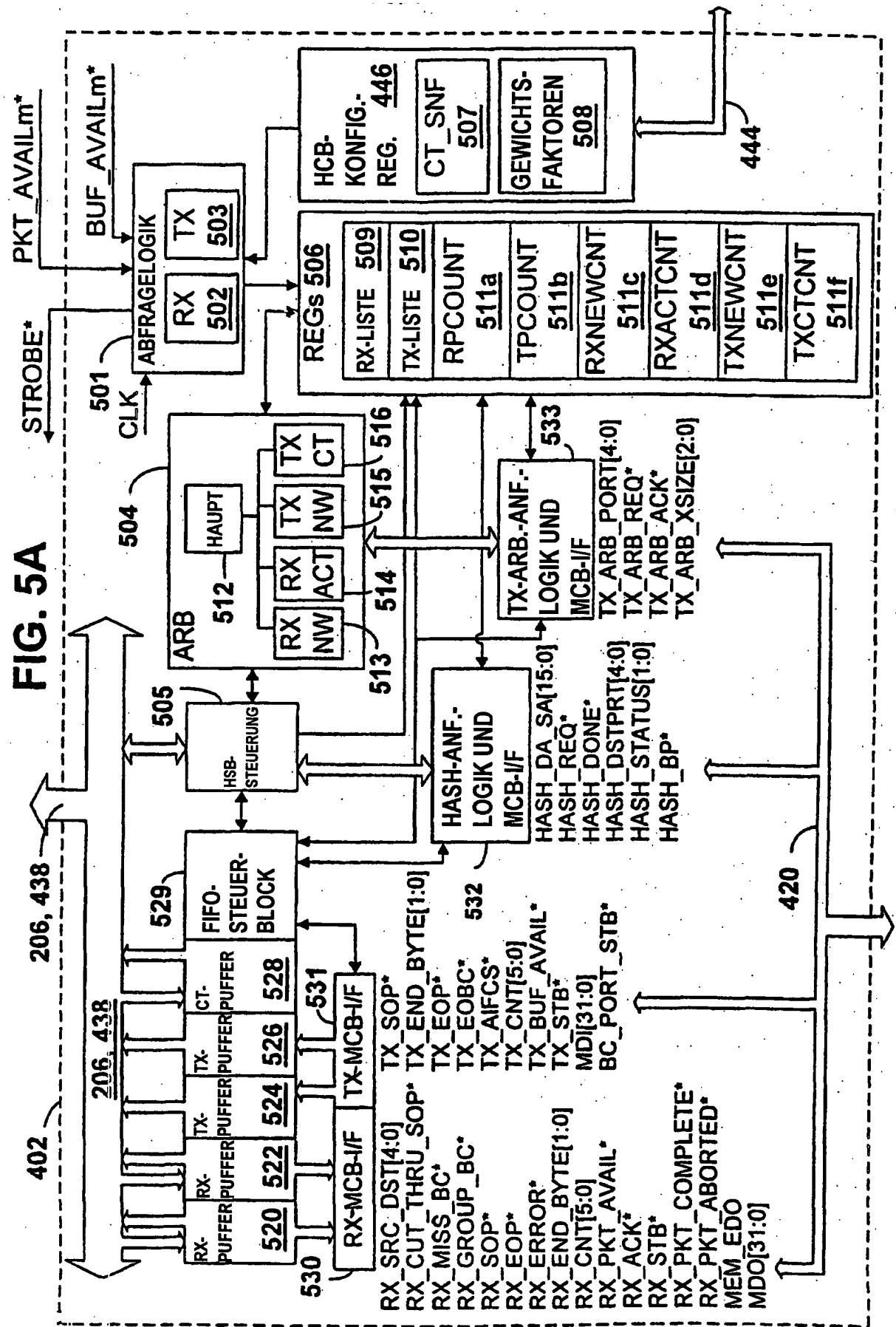

[0029] [Fig. 5A](#) ist ausführlicheres Blockschaltbild des Bussteuerungsblocks von [Fig. 4](#).

[0030] [Fig. 5B](#) ist ein Diagramm, das Puffer in dem Speicher des Bussteuerungsblocks von [Fig. 5A](#) veranschaulicht.

[0031] [Fig. 5C](#) ist ein Zustandsdiagramm, das die Arbeitsweise der Empfangsabfrage-Zustandsmaschine in dem Bussteuerungsblock von [Fig. 5A](#) veranschaulicht.

[0032] [Fig. 5D](#) ist ein Zustandsdiagramm, das die Arbeitsweise der Sendeabfrage-Zustandsmaschine in dem Bussteuerungsblock von [Fig. 5A](#) veranschaulicht.

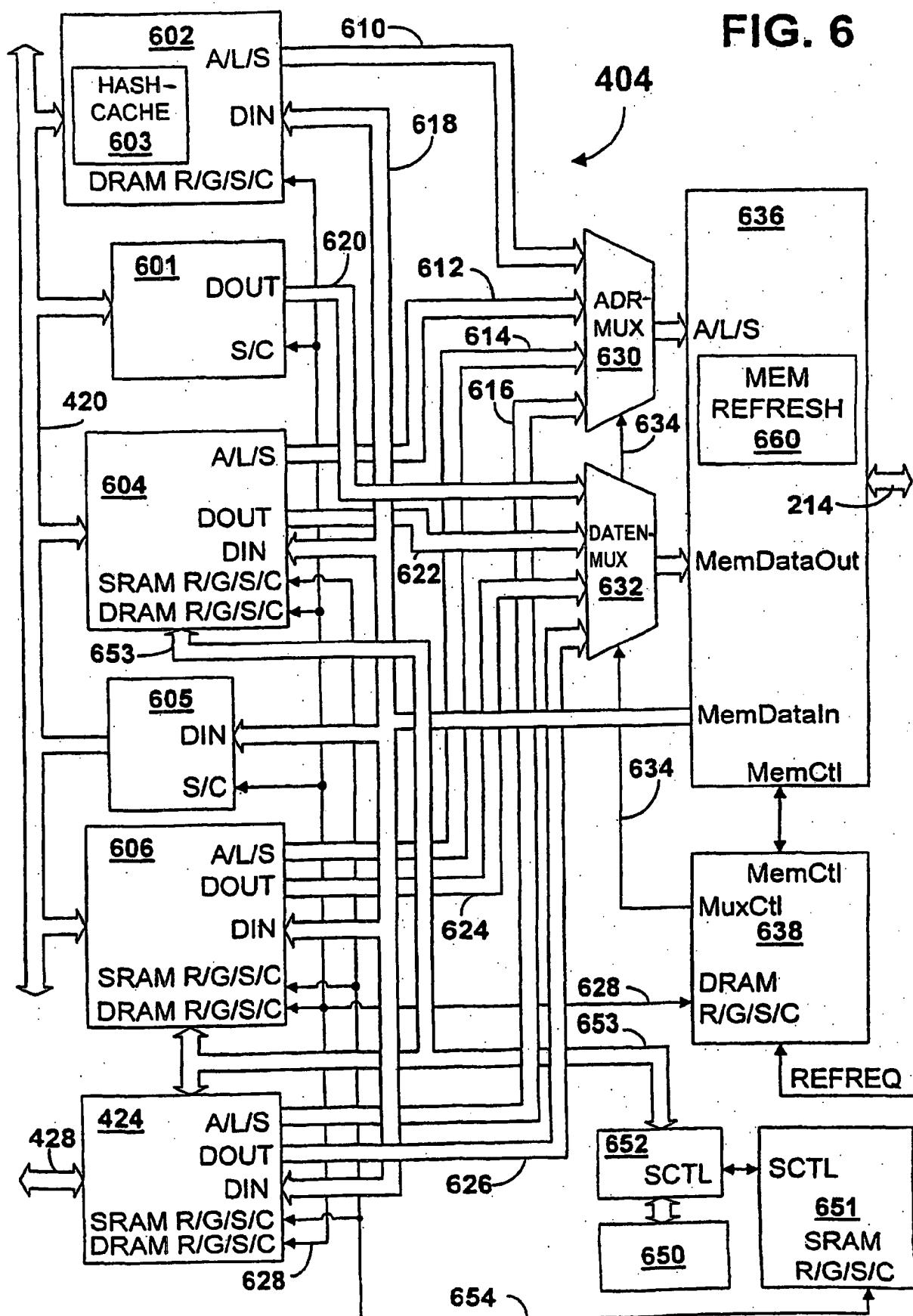

[0033] [Fig. 6](#) ist ein ausführlicheres Blockschaltbild des Speichersteuerungsblocks von [Fig. 4](#).

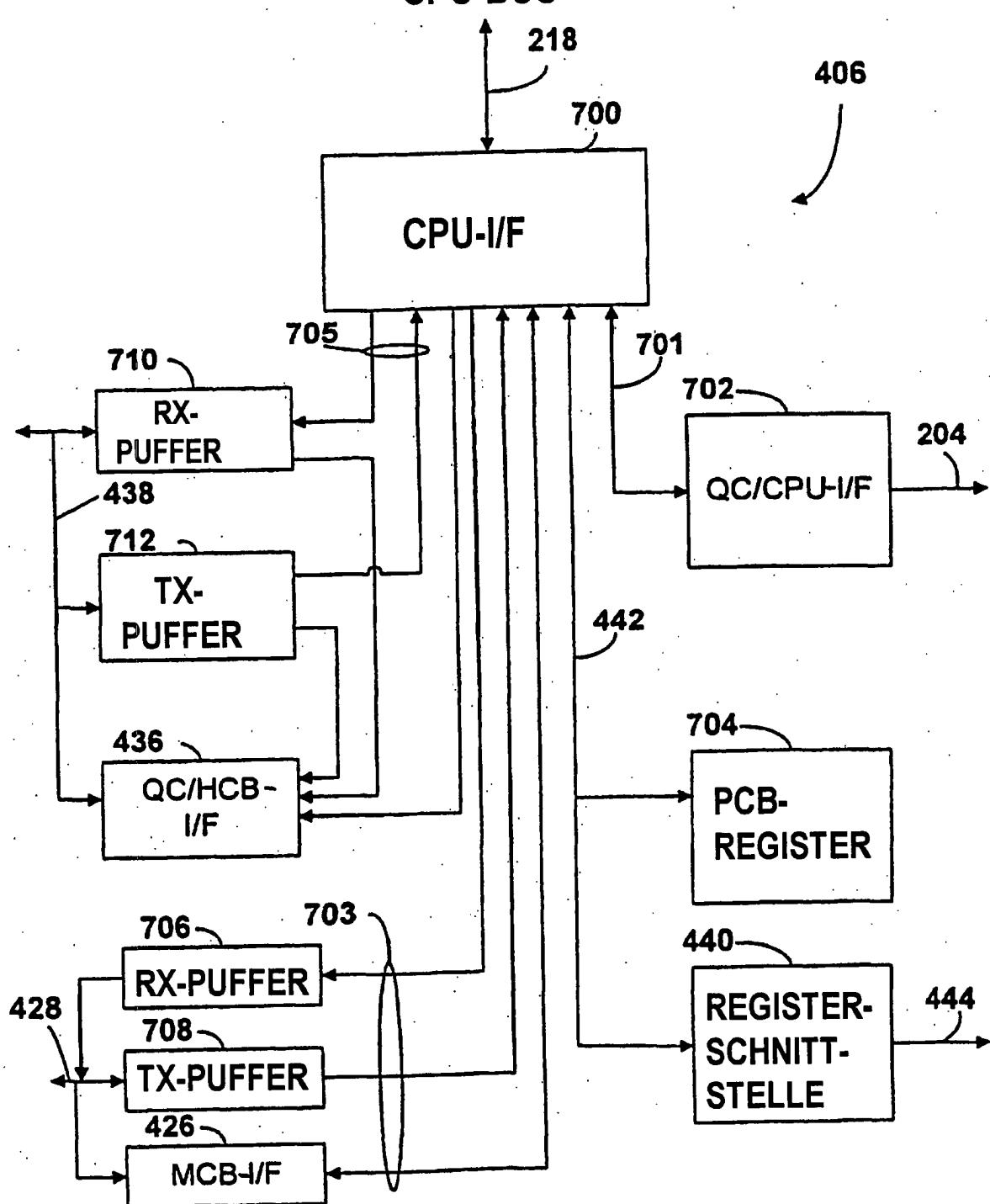

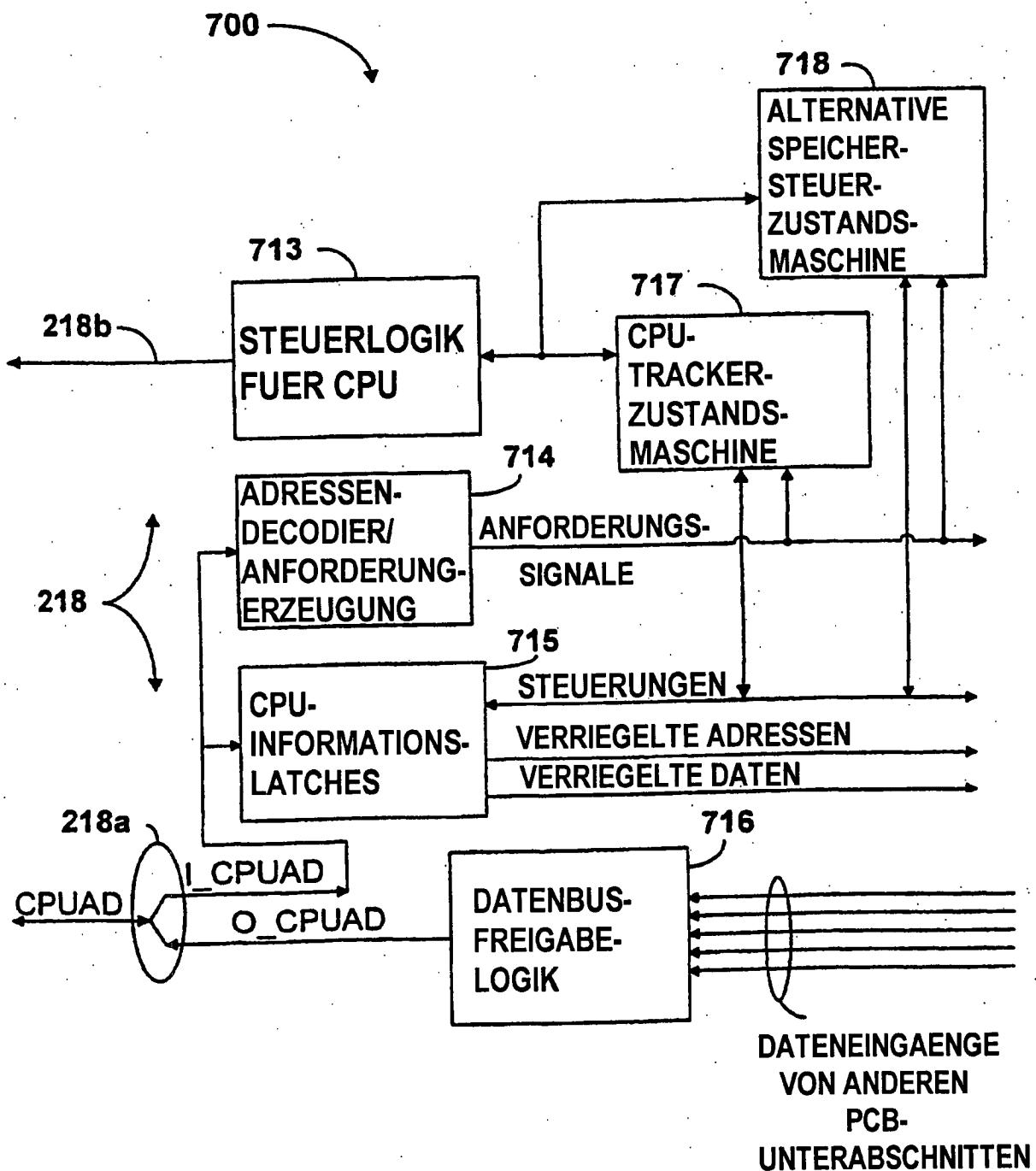

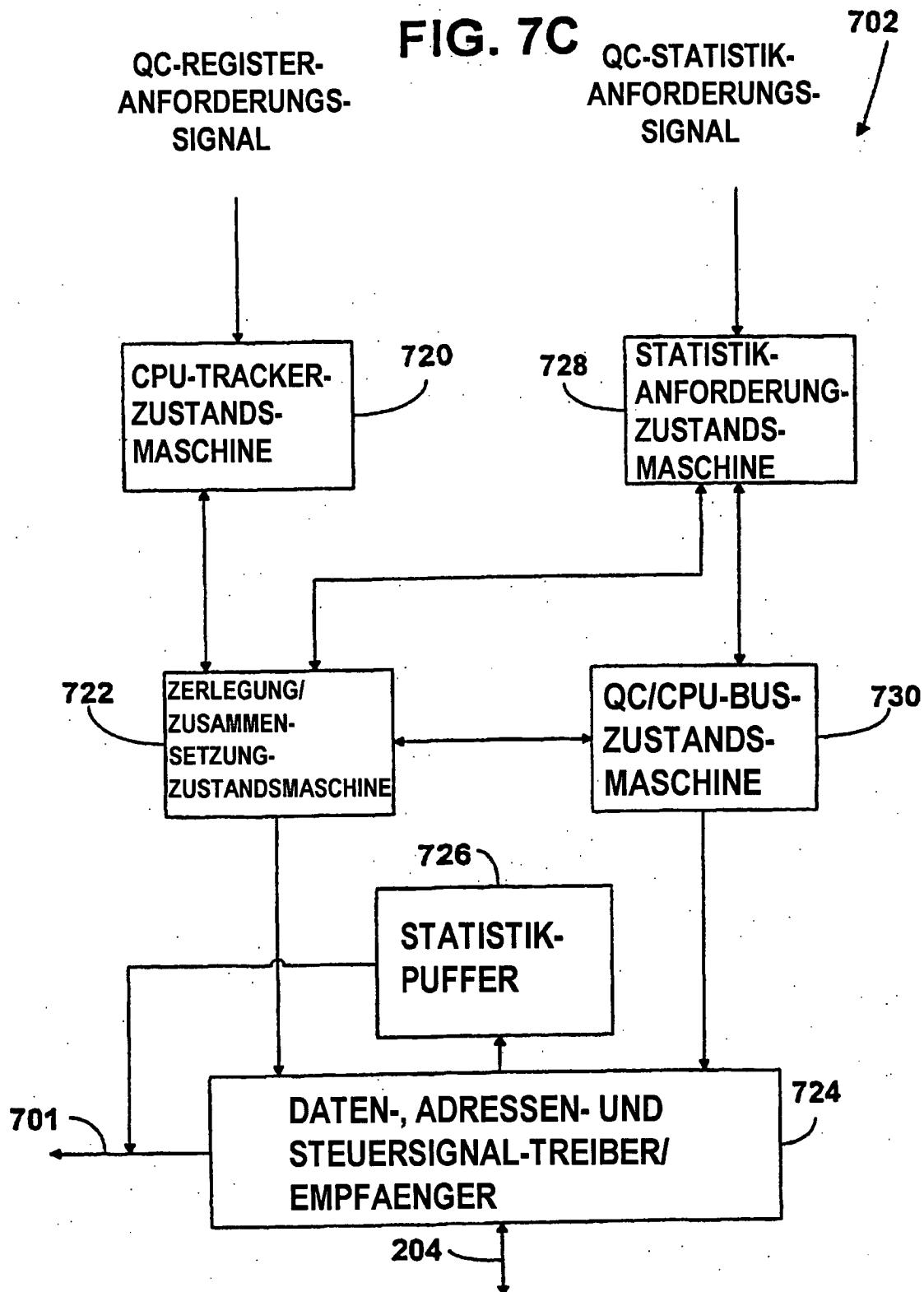

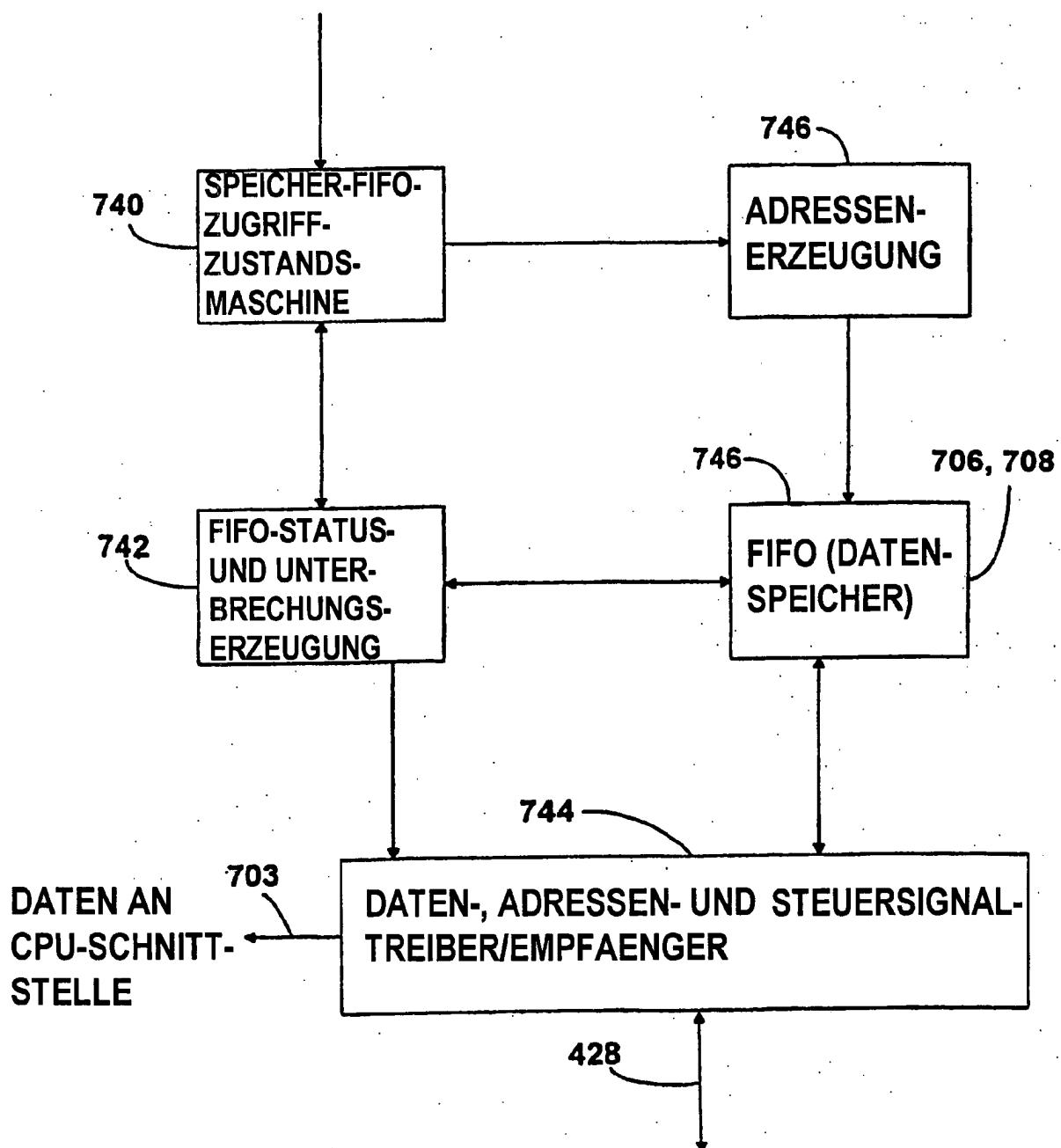

[0034] [Fig. 7A](#)–[Fig. 7E](#) sind ausführlichere Blockschaltbilder des Prozessorsteuerungsblocks von [Fig. 4](#).

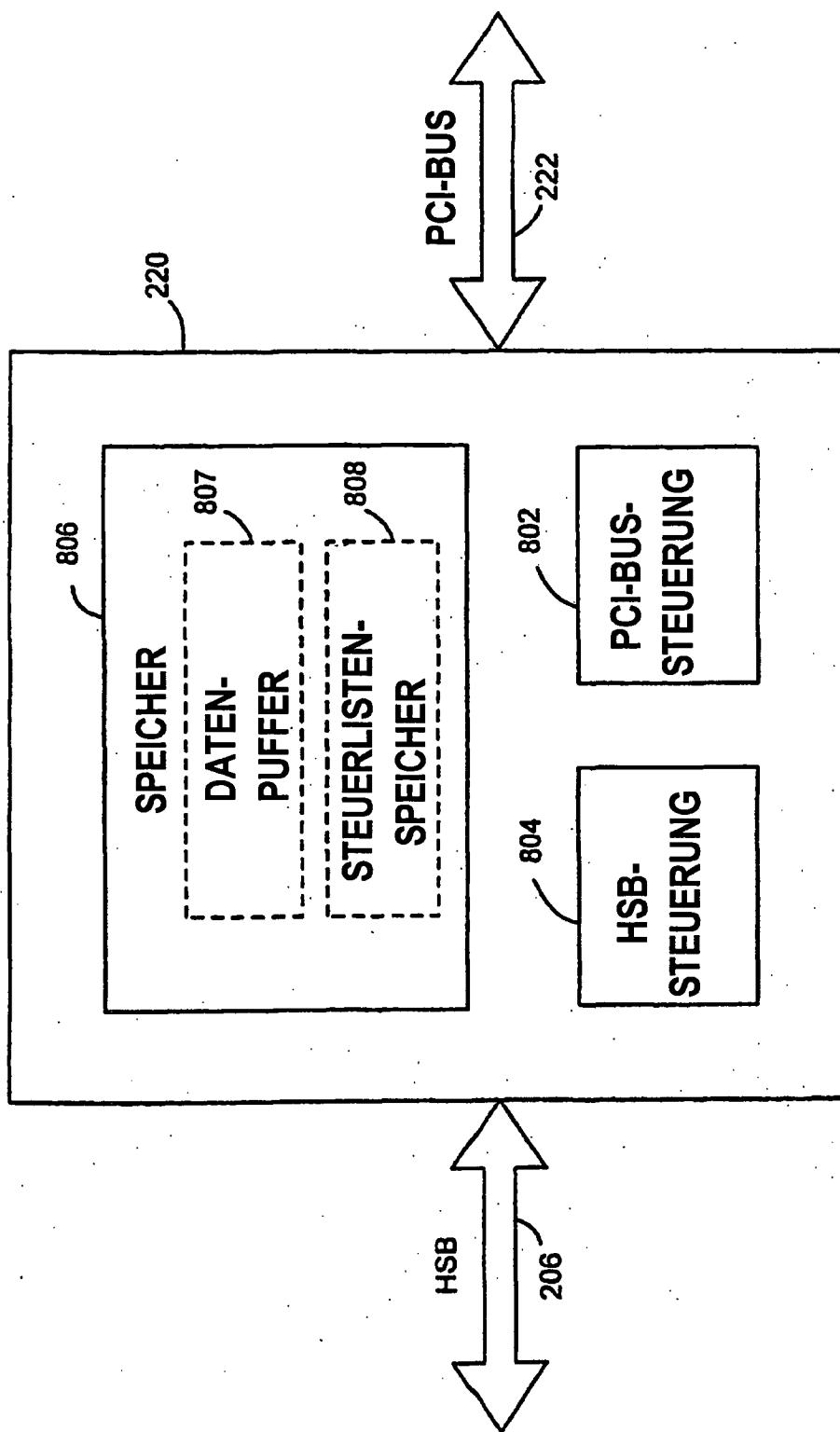

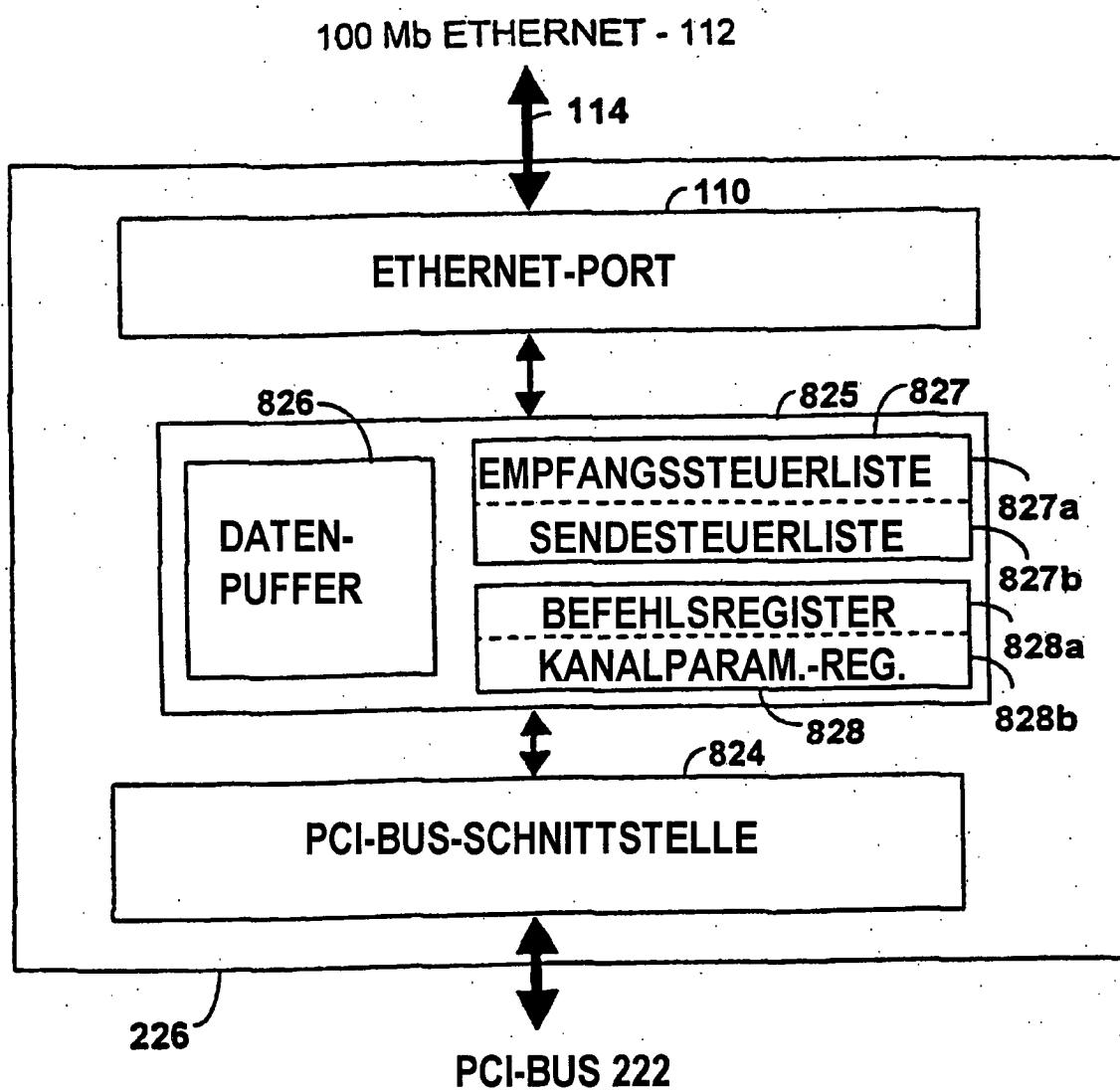

[0035] [Fig. 8A](#) ist ein vereinfachtes Blockschaltbild der Thunder-LAN-Portschnittstelle (TPI) von [Fig. 2](#).

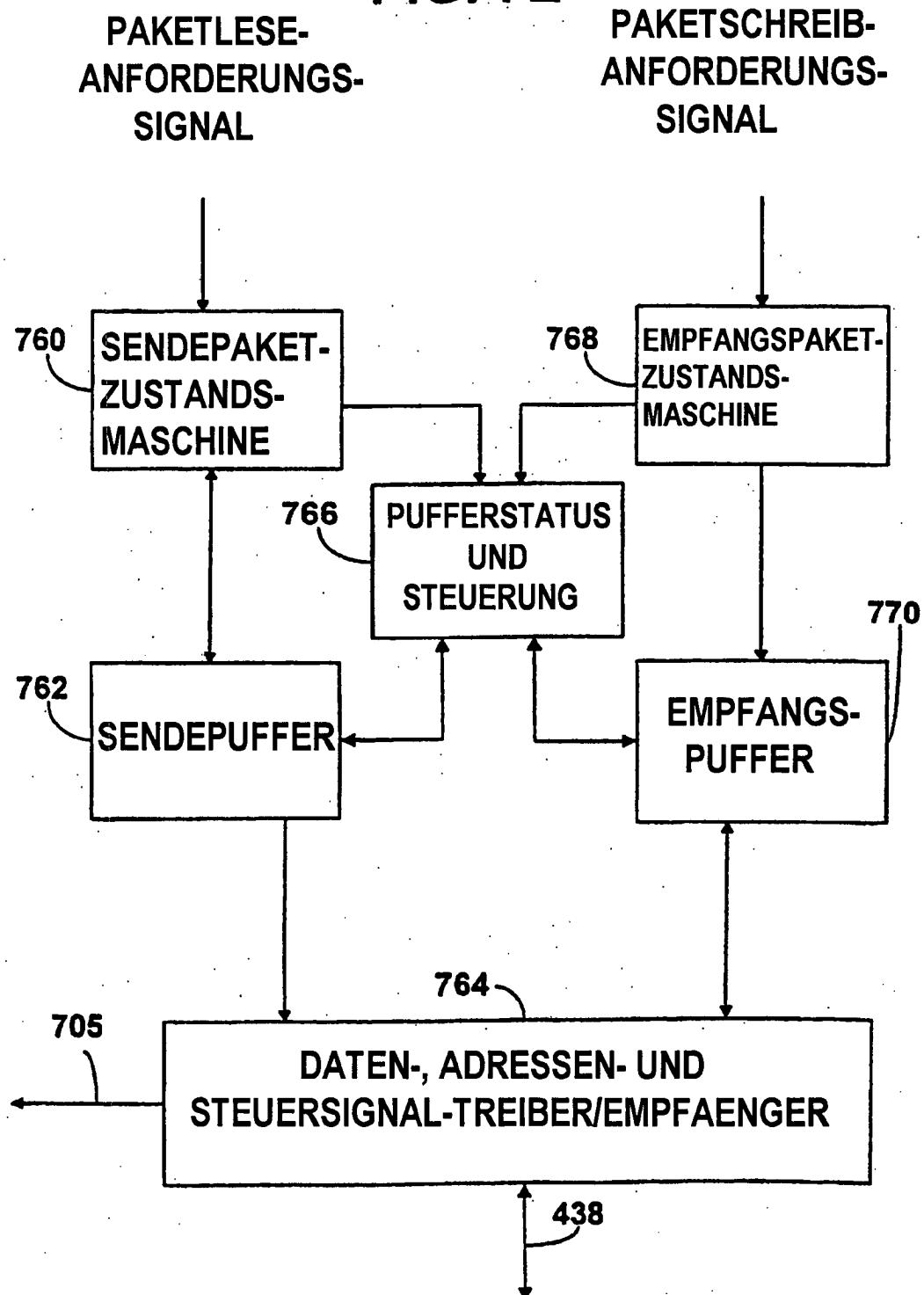

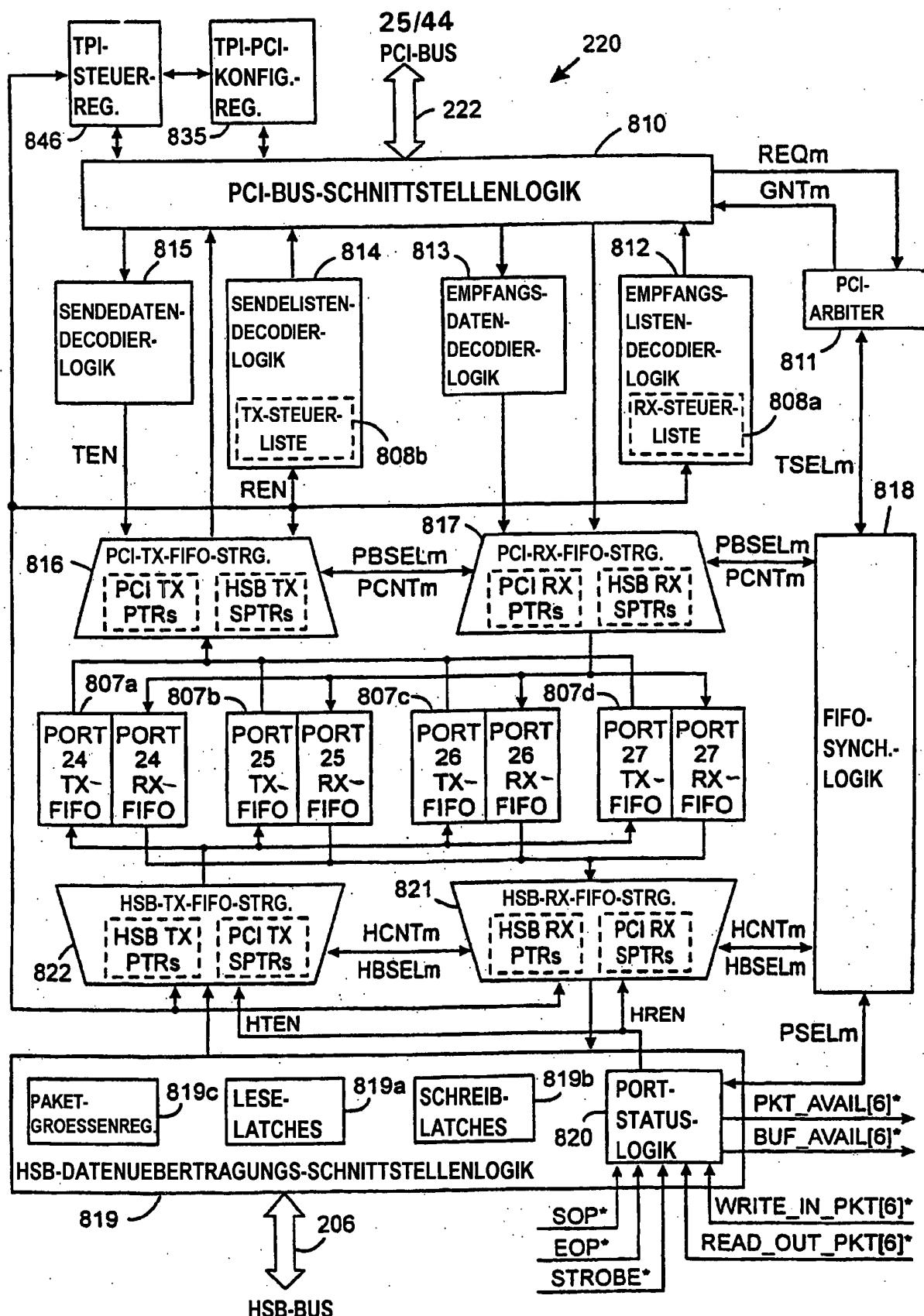

[0036] [Fig. 8B](#) ist ein ausführlicheres Blockschaltbild der TPI.

[0037] [Fig. 8C](#) ist ein Blockschaltbild, das die Konfiguration und Funktionalität jedes der Thunder-LANs (TLANs) von [Fig. 2](#) veranschaulicht.

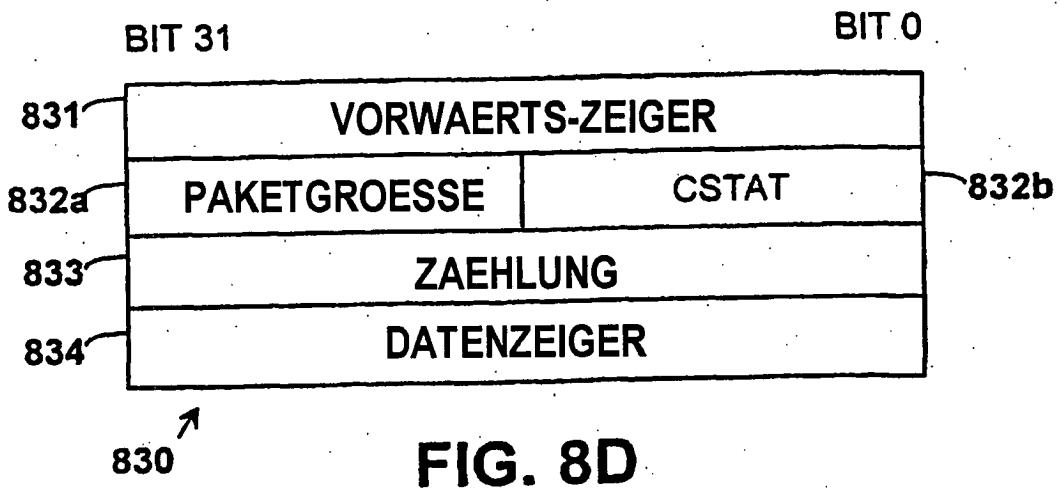

[0038] [Fig. 8D](#) ist ein Diagramm, das das allgemeine Format einer Steuerliste zum Ausführen durch jedes der TLANs veranschaulicht.

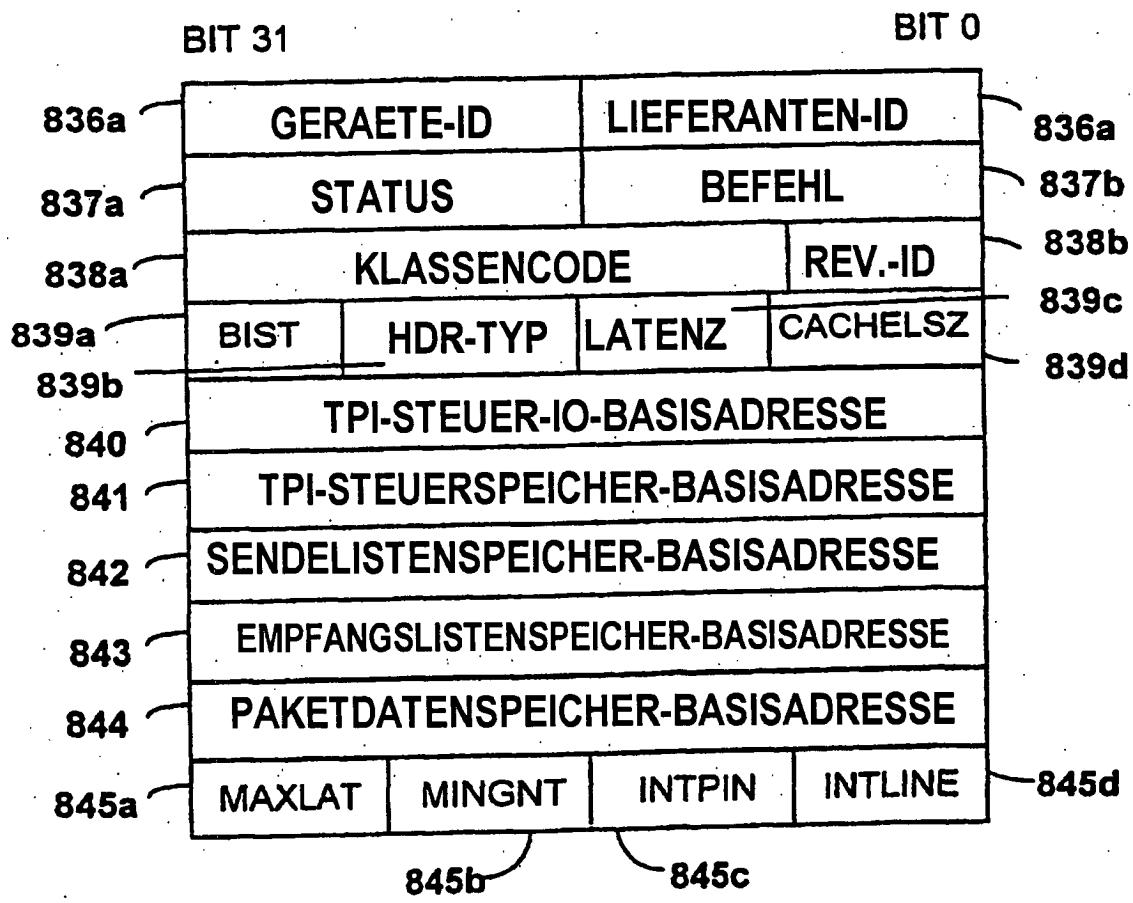

[0039] [Fig. 8E](#) ist ein Diagramm, das eine Definition von TPI-Peripheriekomponenten-Verbindungs-(PCI)Konfigurationsregistern veranschaulicht, die von der mit dem PCI-Bus von [Fig. 2](#) verbundenen TPI verwendet werden.

[0040] [Fig. 8F](#) ist ein Diagramm, das die Definition der von der TPI verwendeten TPI-Steuerregister veranschaulicht.

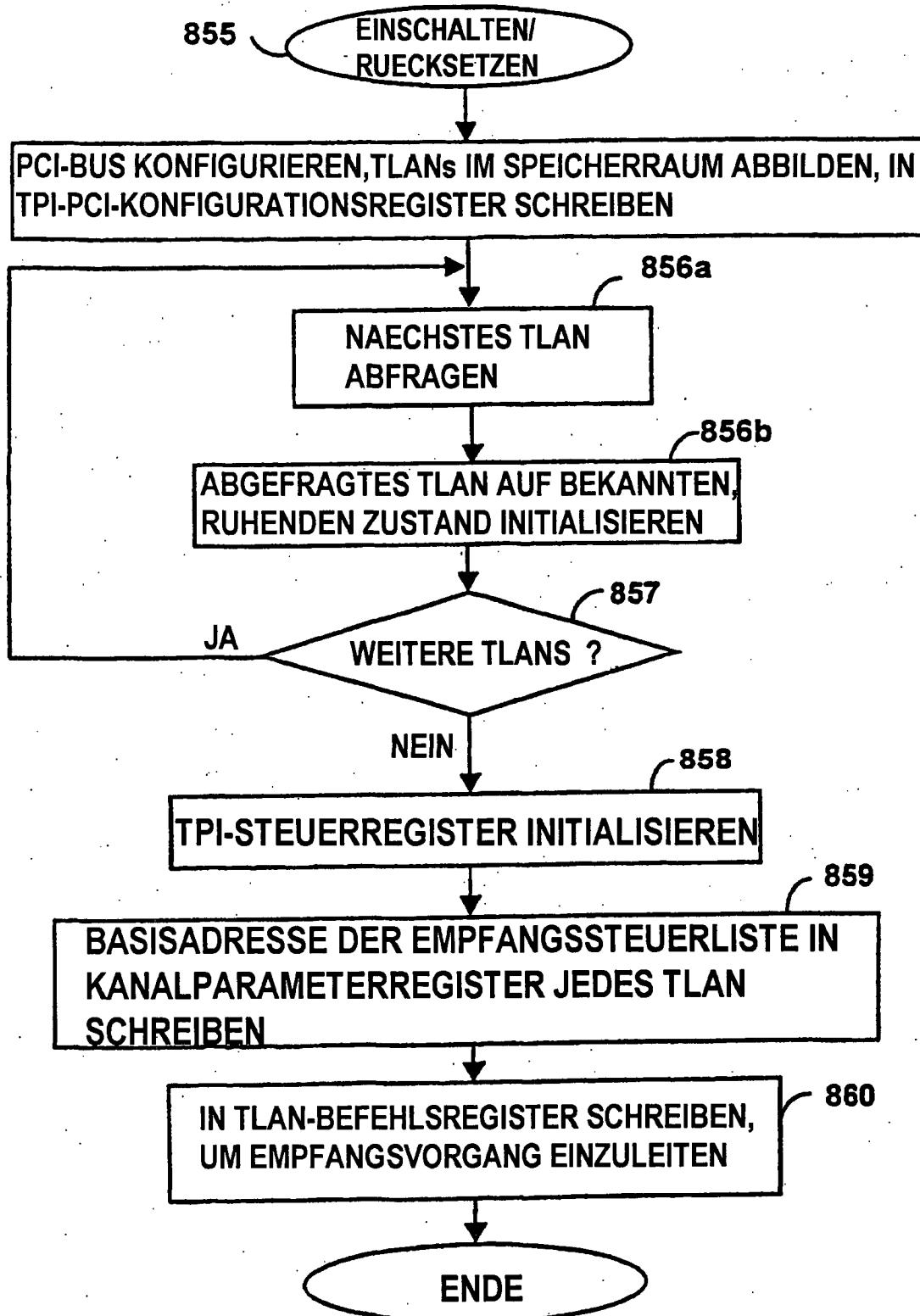

[0041] [Fig. 8G](#) ist ein Flussdiagramm, das PCI-Initialisierungsoperationen der CPU von [Fig. 2](#) veranschaulicht.

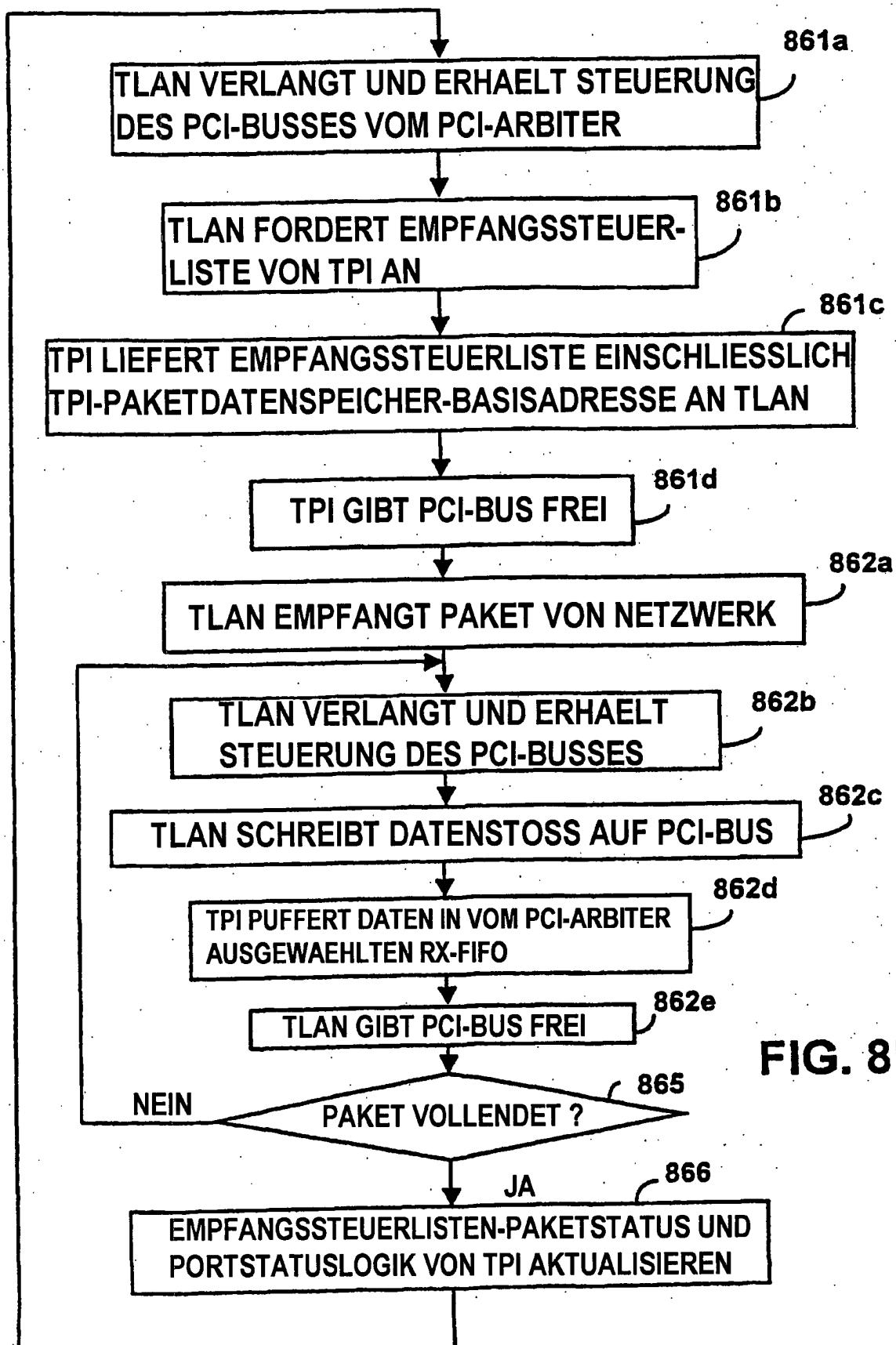

[0042] [Fig. 8H](#) ist ein Flussdiagramm, das eine Empfangsoperation für jedes der TLANs veranschaulicht.

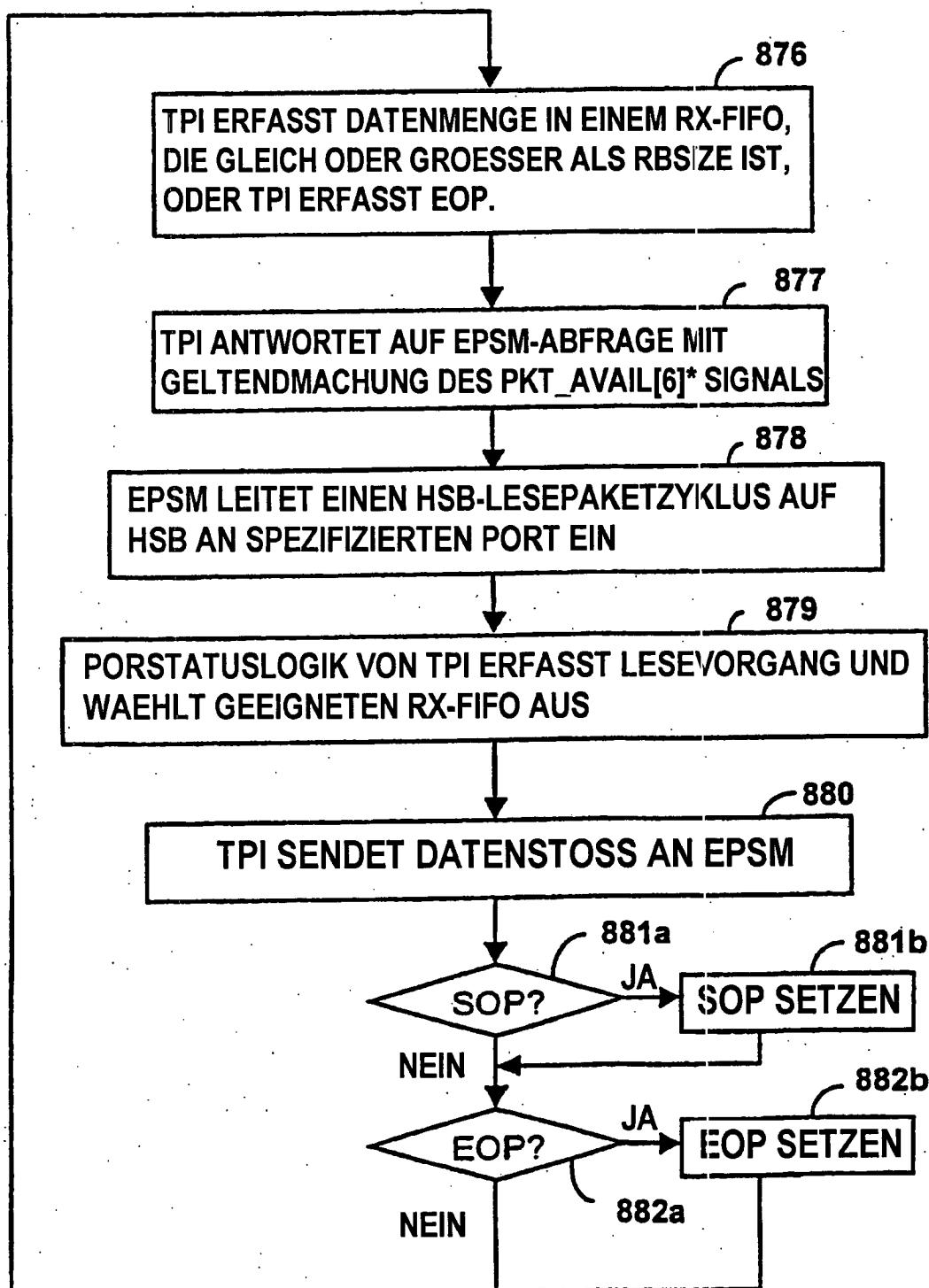

[0043] [Fig. 8I](#) ist ein Flussdiagramm, das einen Empfangsdaten-Übertragungsvorgang über den Hochgeschwindigkeitsbus (HSB) von [Fig. 2](#) veranschaulicht.

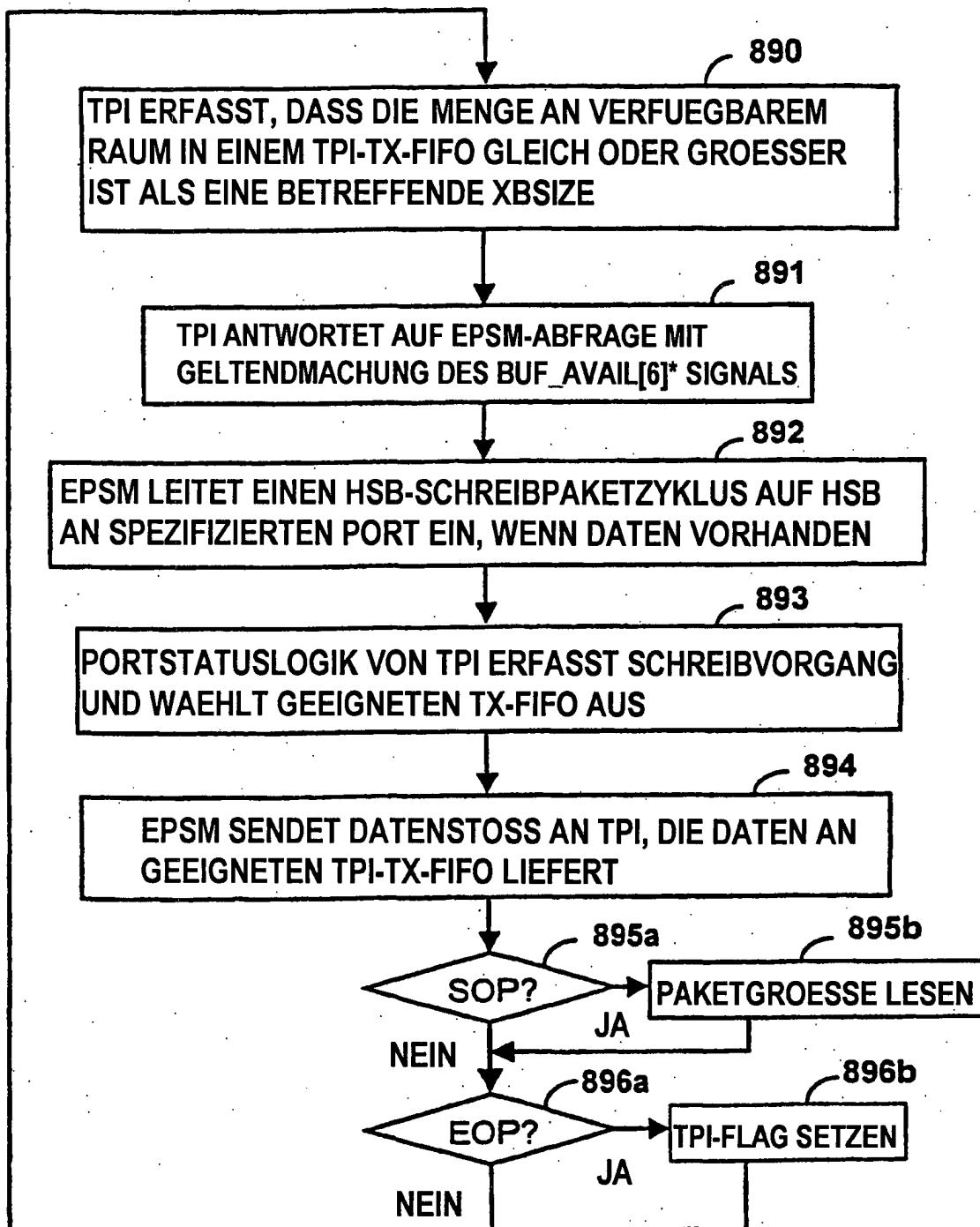

[0044] [Fig. 8J](#) ist ein Flussdiagramm, das einen Sendedaten-Übertragungsvorgang über den HSB veranschaulicht.

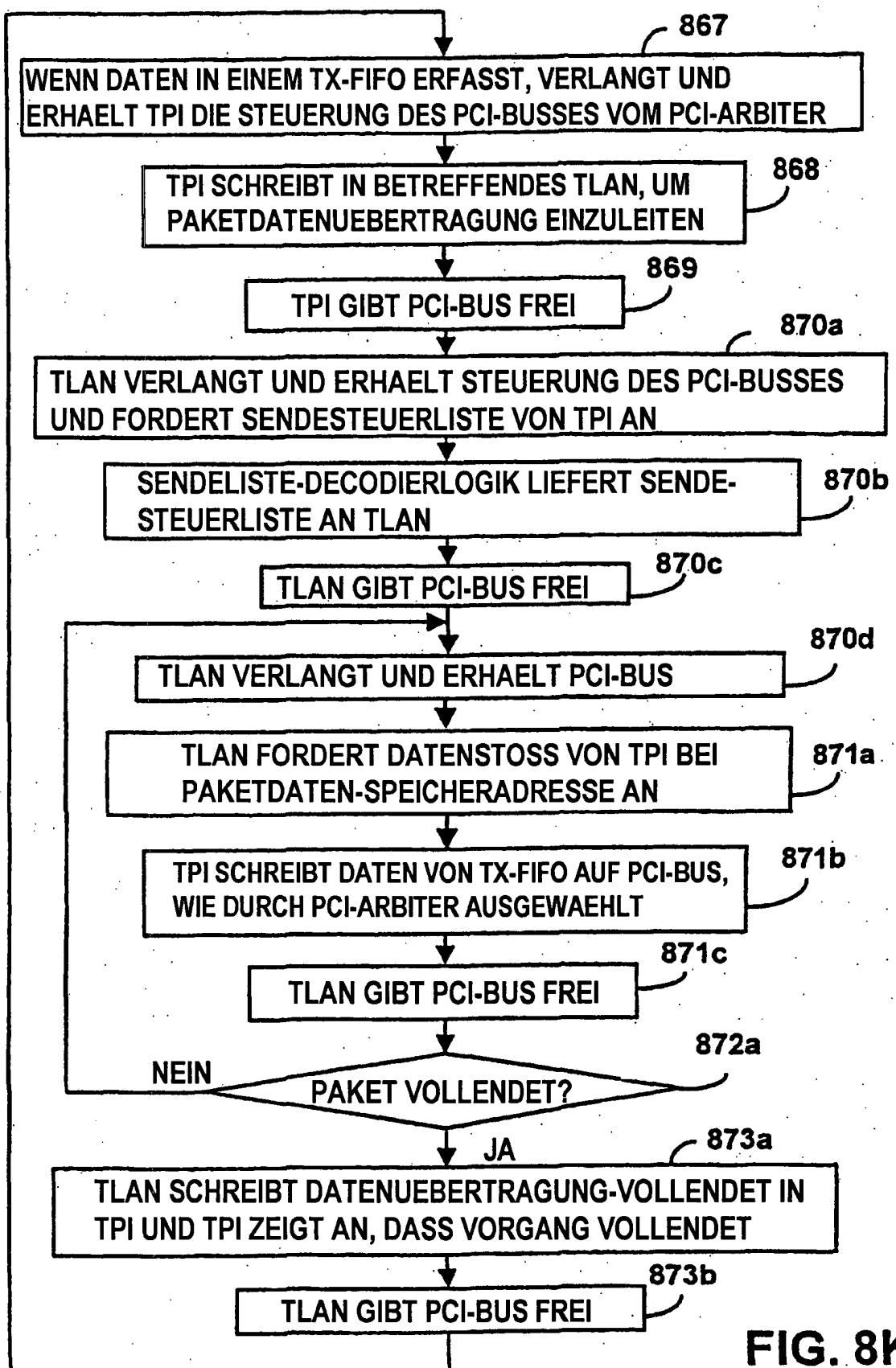

[0045] [Fig. 8K](#) ist ein Flussdiagramm, das einen Sendevorgang für jedes der TLANs veranschaulicht.

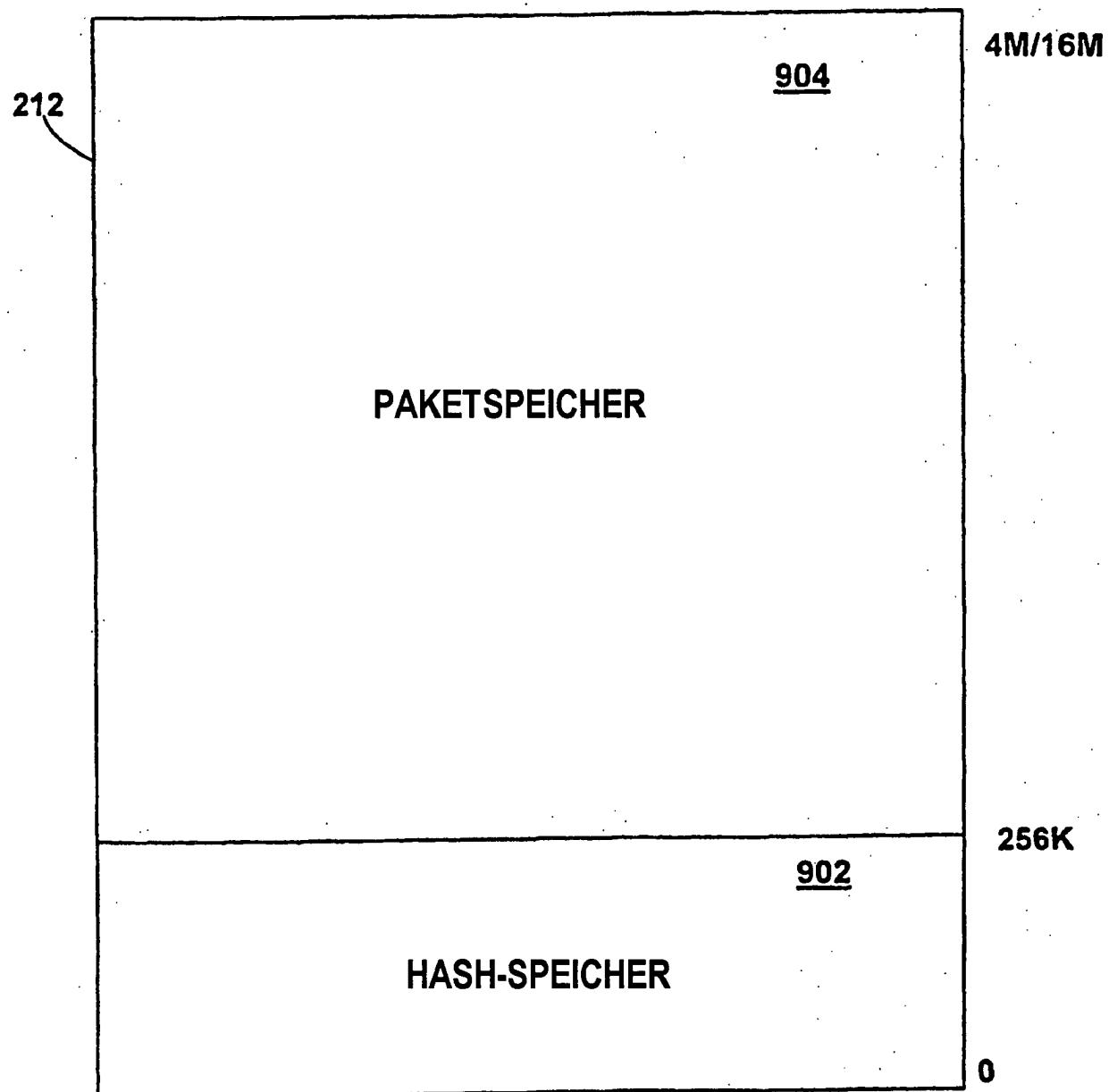

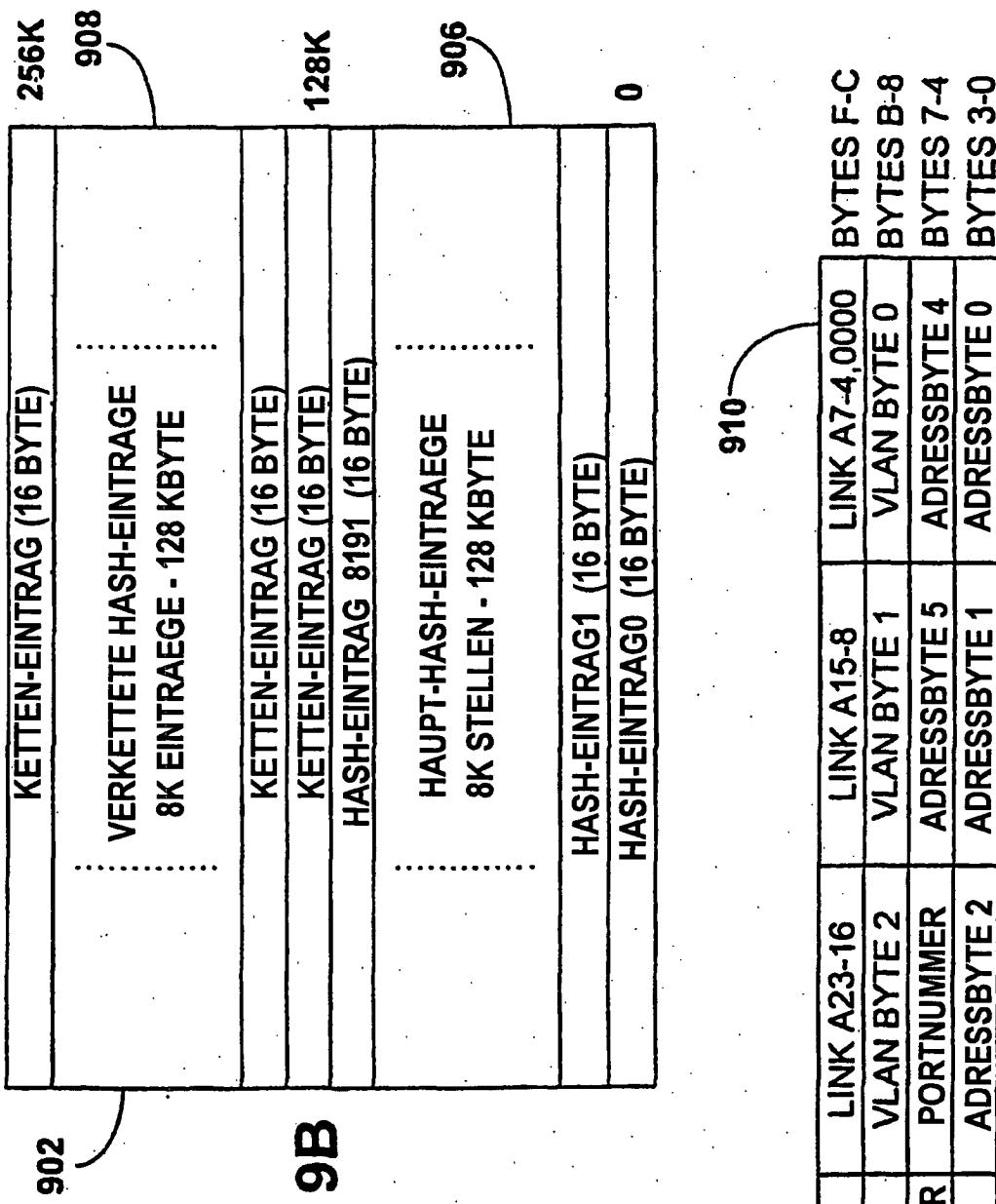

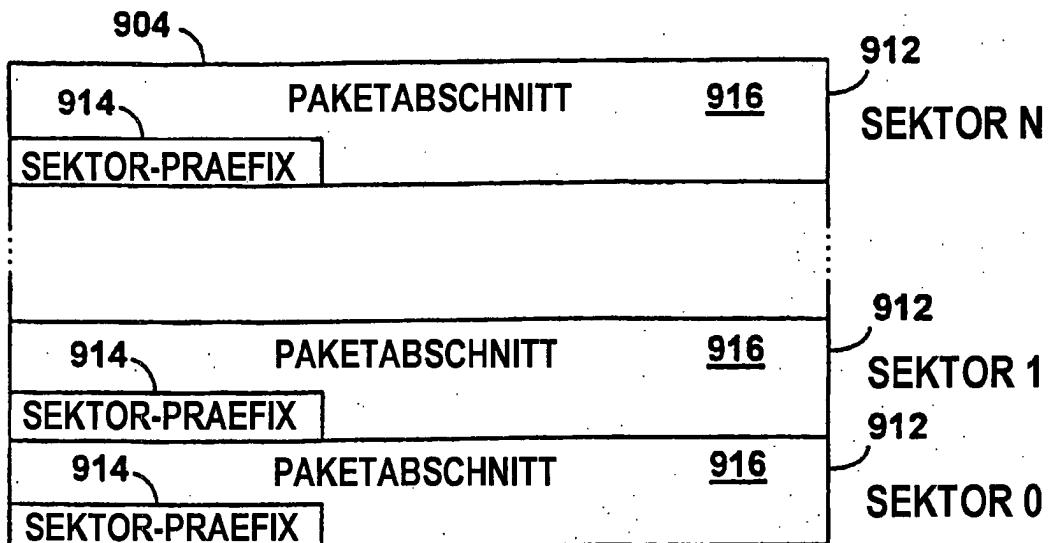

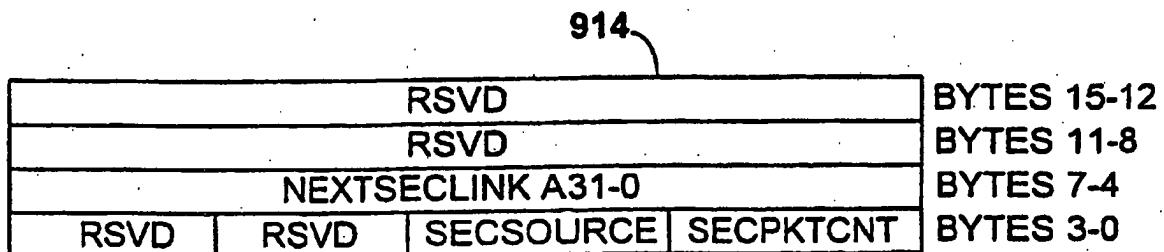

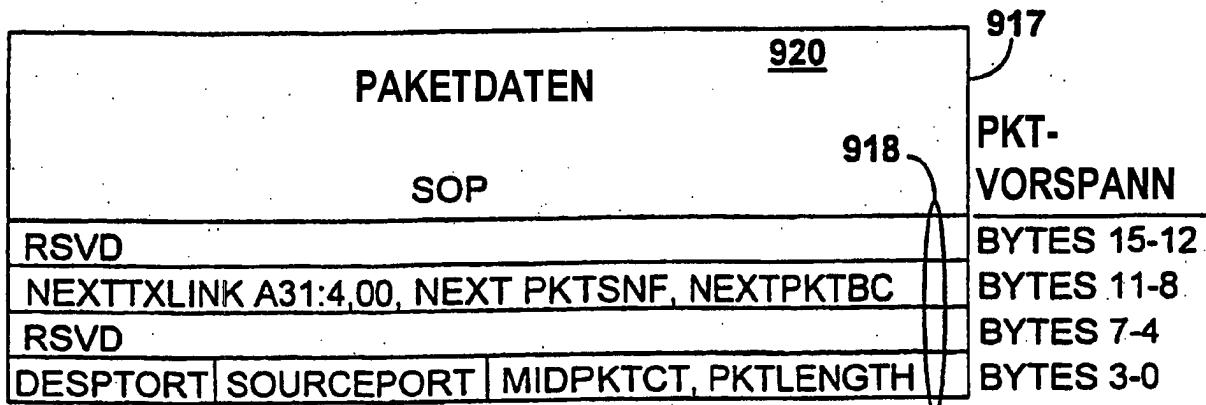

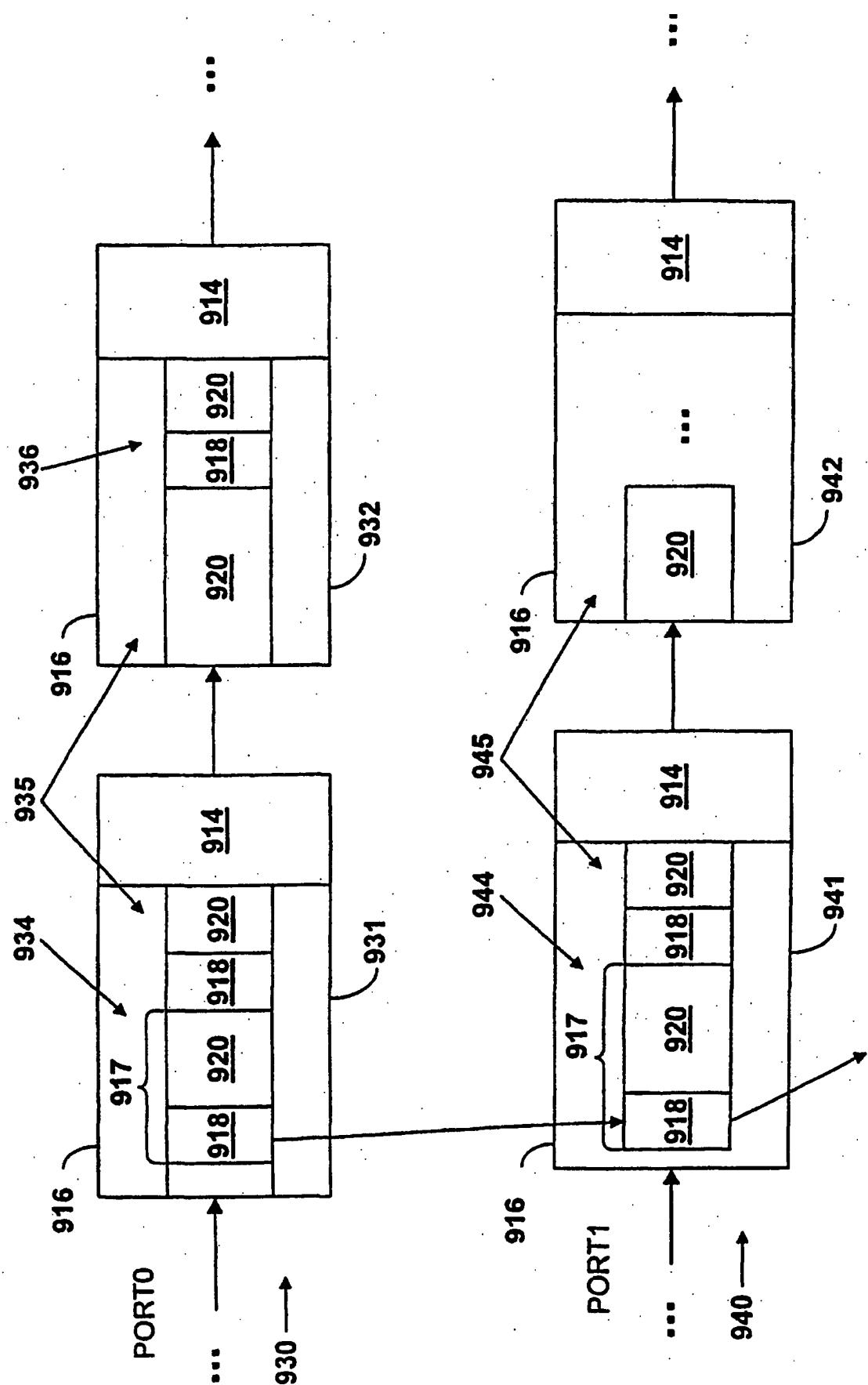

[0046] [Fig. 9A](#)–[Fig. 9H](#) sind Blockschaltbilder, die die Organisation des Speichers von [Fig. 2](#) veranschaulichen.

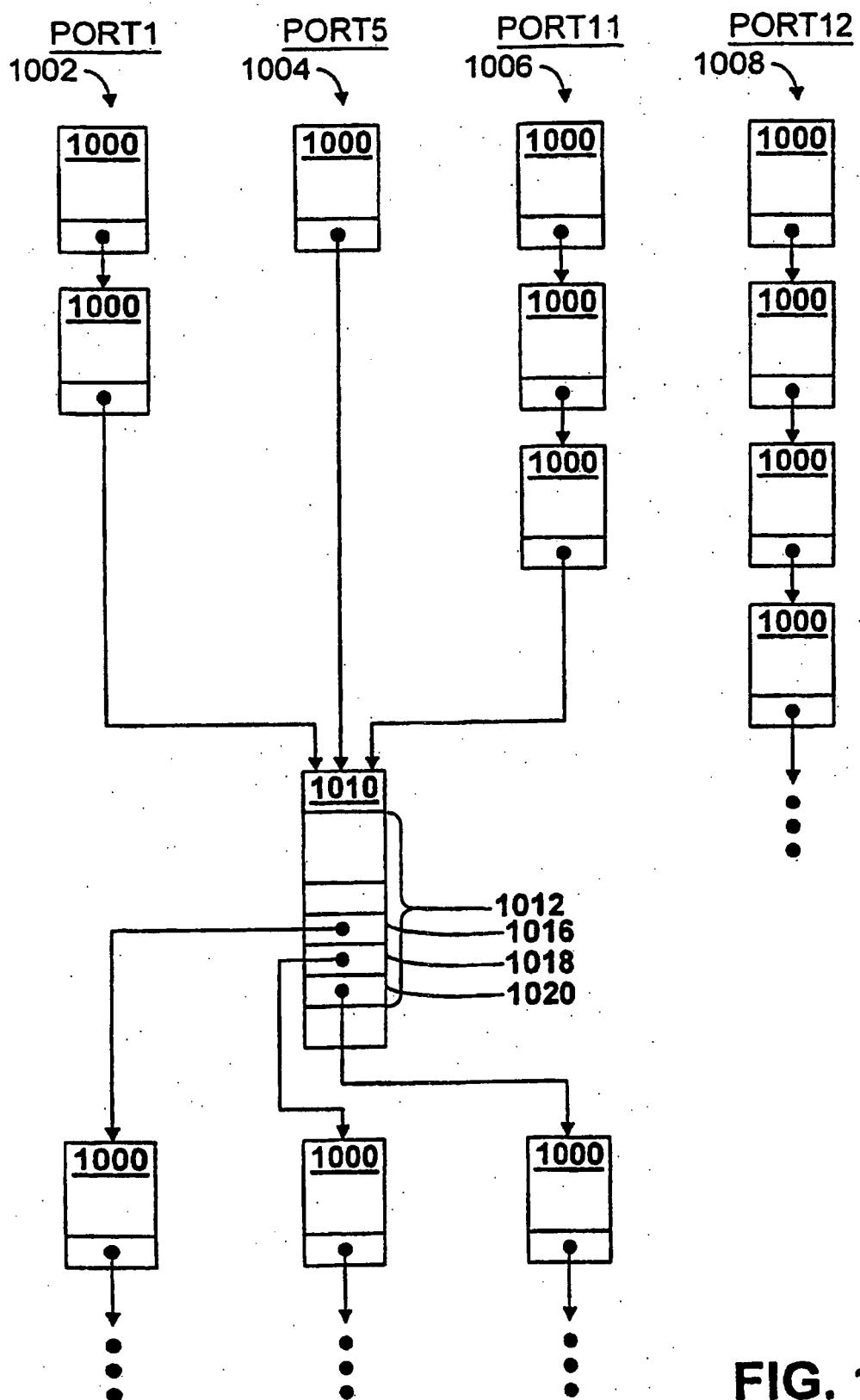

[0047] [Fig. 10](#) ist ein exemplarisches Blockschaltbild, das mehrere Sendepaketstrecken, die ein Rundsendepaket einschließen, veranschaulicht.

[0048] [Fig. 11A](#) und [Fig. 11B](#) sind Blockschaltbilder, die die Organisation des statischen Speichers von [Fig. 6](#) veranschaulichen.

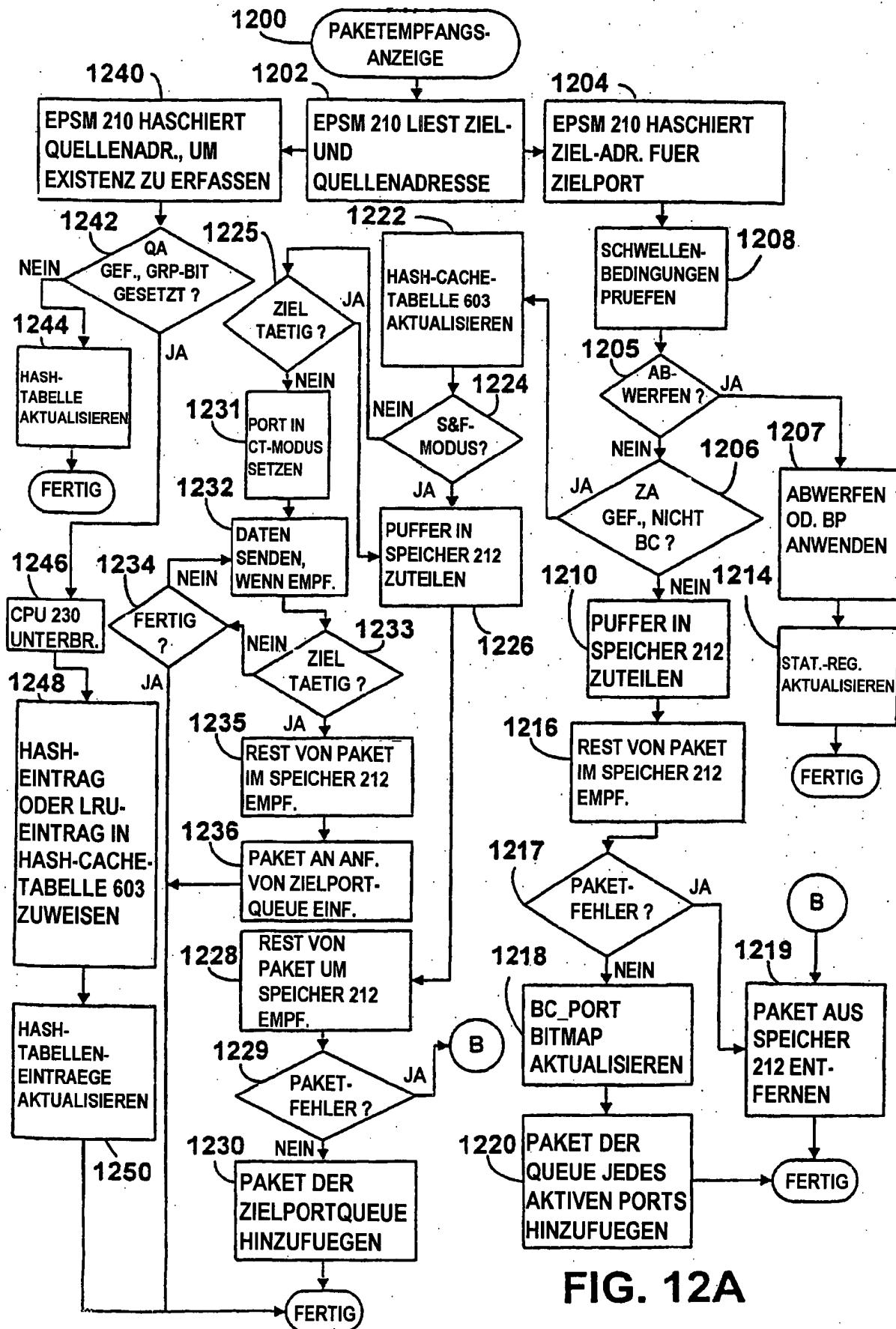

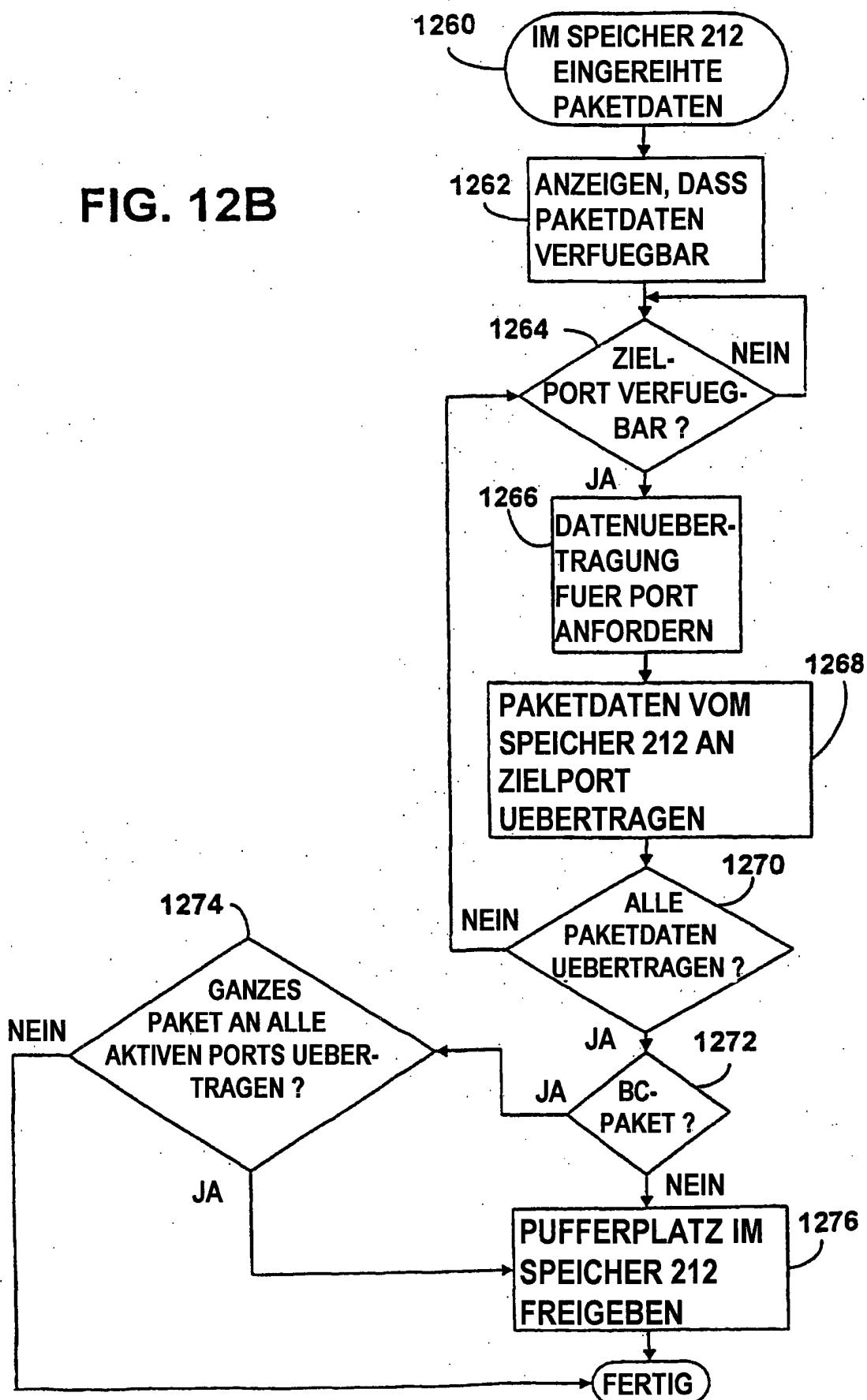

[0049] [Fig. 12A](#) ist ein Flussdiagramm, das die allgemeine Arbeitsweise des Netzwerkschalters von [Fig. 2](#) zum Empfangen von Datenpaketen im Speicher und zum Senden von Datenpaketen in einer Durchschalt-Betriebsart veranschaulicht.

[0050] [Fig. 12B](#) ist ein Flussdiagramm, das die allgemeine Arbeitsweise des Netzwerkschalters von [Fig. 2](#) zum Senden von Datenpaketen aus dem Speicher veranschaulicht.

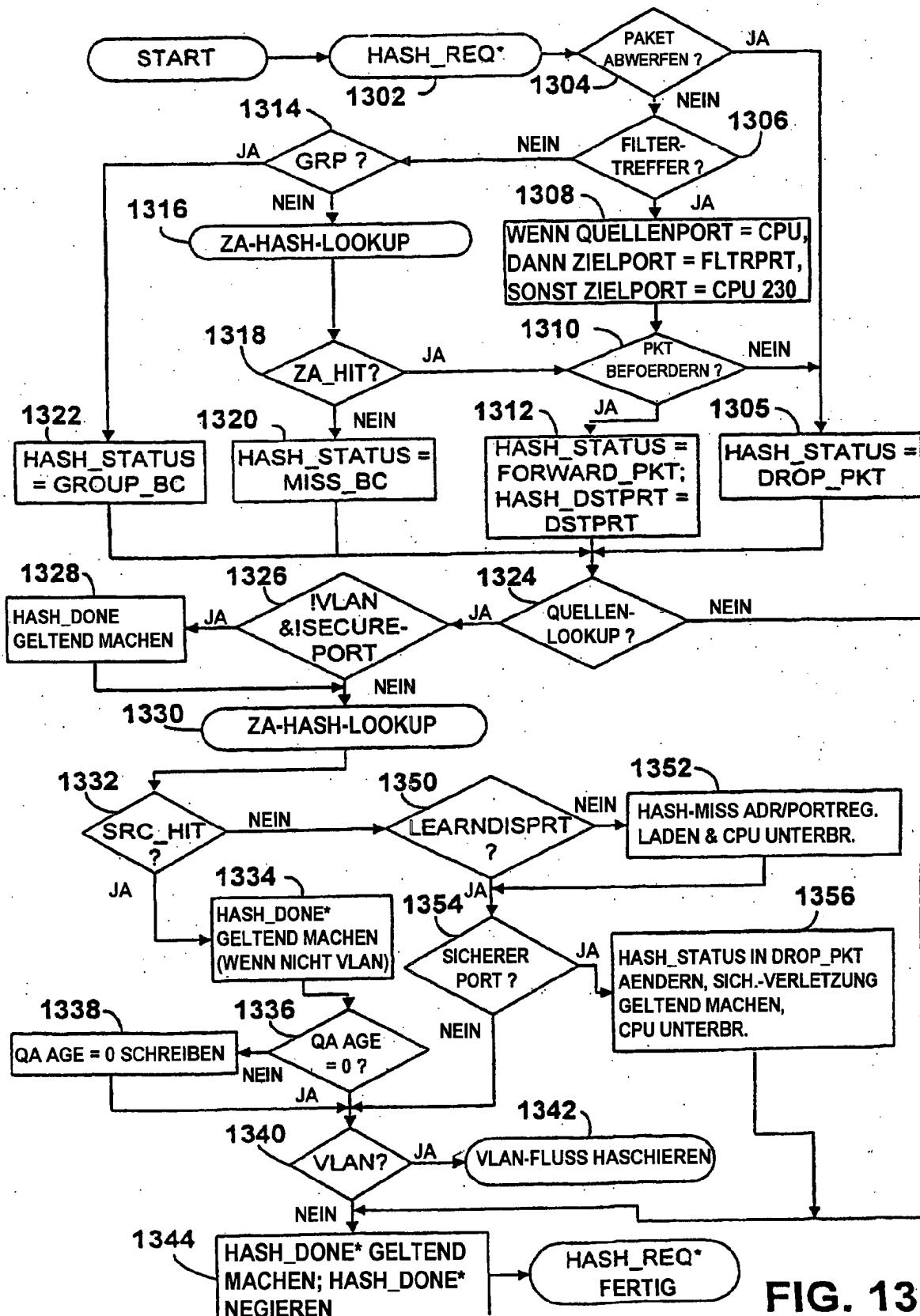

[0051] [Fig. 13](#) ist ein Flussdiagramm, das eine Hash-Lookup-Operation des Schalter-Managers von [Fig. 2](#) veranschaulicht.

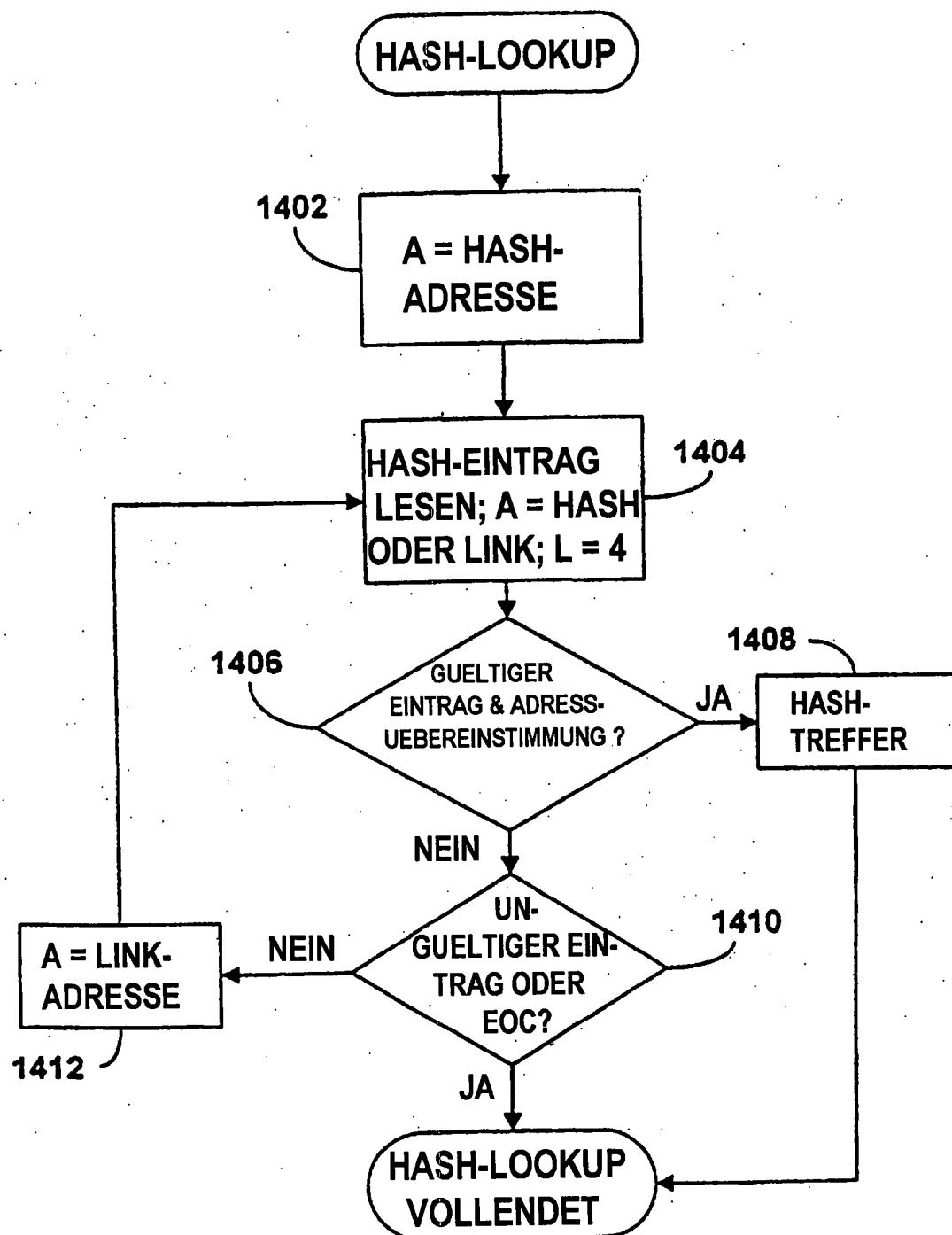

[0052] [Fig. 14](#) ist ein Flussdiagramm, das eine Hash-Lookup-Operation zum Suchen von Hash-Tabelleneinträgen im Speicher von [Fig. 2](#) veranschaulicht.

[0053] [Fig. 1](#) zeigt ein vereinfachtes Netzwerkdiagramm eines Netzwerks **100**, das einen nach der vorliegen-

den Erfindung implementierten Netzwerkschalter **102** enthält. Der Netzwerkschalter **102** umfasst einen oder mehr "A" Ports **104**, jeweils zum Verbinden und Kommunizieren mit einem von mehreren "A" Netzwerken **106** durch ein geeignetes Mediensegment **108**. Jedes Mediensegment **108** ist irgendeine Art von Medium, z. B. ein verdrilltes Kabel oder faseroptisches Kabel usw. Die Ports **104** ermöglichen bidirektionale Kommunikation oder Datenfluss zwischen dem Netzwerkschalter **102** und jedem der Netzwerke **106**. Ein solcher bidirektionaler Datenfluss ist entsprechend einer von mehreren Betriebsarten, z. B. Halbduplex oder Vollduplex. Wie in [Fig. 1](#) gezeigt, gibt es " $j$ " + 1 Netzwerke **106**, die einzeln mit A-Netzwerk0, A-Netzwerk1, ..., A-Netzwerk $j$  bezeichnet sind, wo jedes Netzwerk **106** mit dem Netzwerkschalter **102** durch einen entsprechenden der  $j + 1$  Ports **104**, einzeln bezeichnet mit A-Port0, A-Port1, ..., A-Port $j$ , verbunden ist. Der Netzwerkschalter **102** kann jede gewünschte Zahl von Ports **104** zum Verbinden mit bis zu einer zugehörigen Zahl von Netzwerken **106** enthalten. Bei der hier beschriebenen Ausführung ist  $j$  eine Ganzzahl gleich 23 für insgesamt 24 Ports zum Verbinden von bis zu Netzwerken **106**, wobei diese Ports kollektiv als Ports **104** oder einzeln als Ports Port0, Port1, Port2, ..., Port23 bezeichnet werden.

**[0054]** In ähnlicher Weise umfasst der Netzwerkschalter **102** weiter einen oder mehr "B" Ports **110**, jeder zum Koppeln an ein und Verbinden mit einem "B" Netzwerk **112** durch ein geeignetes Mediensegment **114**. Jedes Mediensegment kann wieder jede Art von Medium zum Verbinden von Netzwerk-Vorrichtungen sein, z. B. ein verdrilltes Kabelpaar ein faseroptisches Kabel usw. Die Ports **110** sind ebenfalls bidirektional, um einen Datenfluss zwischen dem Netzwerkschalter **102** und den Netzwerken **112** in einer ähnlichen Weise wie für die Ports **104** beschrieben zu ermöglichen. In der gezeigten Ausführung gibt es " $k$ " + 1 Ports **110**, einzeln bezeichnet mit B-Port0, B-Port1, ..., B-Port $k$ , zum Verbinden von bis zu  $k + 1$  Netzwerken, bezeichnet mit B-Netzwerk0, B-Netzwerk1, ..., B-Netzwerk $k$ . Der Netzwerkschalter **102** kann jede gewünschte Zahl von Ports **110** zum Verbinden mit bis zu einer zugehörigen Zahl von Netzwerken **112** enthalten. In der gezeigten spezifischen Ausführung ist  $k$  eine Ganzzahl gleich 3 für insgesamt 4 Ports **110** zum Verbinden von bis zu vier Netzwerken **112**. Die "A" Typ Ports und Netzwerke arbeiten bei einem unterschiedlichen Netzwerkprotokoll und/oder Geschwindigkeit als die "B" Typ Ports und Netzwerke. In der gezeigten spezifischen Ausführung arbeiten die Ports **104** und Netzwerke **106** entsprechend dem Ethernet-Protokoll bei 10 Megabit pro Sekunde (Mbps), während die Ports **110** und Netzwerke **112** entsprechend dem Ethernet-Protokoll bei 100 Mbps arbeiten. Die Ports B-Port0, B-Port1, ..., B-Port3 werden hier kollektiv als die Ports **104** und einzeln als Port24, Port25, ..., Port27 bezeichnet.

**[0055]** Die Netzwerke **106** und **112** enthalten eine oder mehr Datenvorrichtungen oder Datenendgeräte (DTE), die die Eingabe oder Ausgabe von Daten erlauben, oder jede Art von Netzwerk-Vorrichtung, um eine oder mehr Datenvorrichtungen miteinander zu verbinden. Jedes der Netzwerke, z. B. A-Netzwerk0 oder B-Netzwerk1, usw, kann daher einen oder mehr Computer, Netzwerk-Schnittstellenkarten (NICs), Workstations, Datei-Server, Modems, Drucker oder jede andere Vorrichtung enthalten, die Daten in einem Netzwerk empfängt oder sendet, z. B. Repeater, Schalter, Router, Hubs, Konzentratoren usw. Zum Beispiel sind, wie in [Fig. 1](#) gezeigt, mehrere Computersysteme oder Workstations **120**, **122** und **124** mit dem entsprechenden Segment **108** von A-Netzwerk $j$  verbunden. Die Computersysteme **120**, **122** und **124** können miteinander oder mit anderen Vorrichtungen von anderen Netzwerken durch den Netzwerkschalter **102** kommunizieren. Jedes Netzwerk **106** und **112** stellt daher eine oder mehrere durch ein oder mehrere Segmente verbundene Datenvorrichtungen dar, wobei der Netzwerkschalter **102** Daten zwischen irgendwelchen zwei oder mehr Datenvorrichtungen in jedem der Netzwerke **106** und **112** überträgt.

**[0056]** Der Netzwerkschalter **102** empfängt gewöhnlich Information von Datenvorrichtungen, die mit jedem der Ports **104** und **110** verbunden sind, und leitet die Information an einen oder mehr der anderen Ports **104** und **110**. Der Netzwerkschalter **102** filtert auch die Information durch Wegwerfen oder sonstwie Ignorieren von Information, die von einer Datenvorrichtung in einem Netzwerk **106** oder **112** empfangen wird und nur für Datenvorrichtungen in diesem gleichen Netzwerk bestimmt ist. Die Daten oder Information sind in der Form von Paketen, wo die einzelne Form jedes Pakets von dem durch ein gegebenes Netzwerk unterstützten Protokoll abhängt. Ein Paket ist ein vordefinierter Block von Bytes, der gewöhnlich aus Vorspann, Daten und Nachspann besteht, wobei das Format eines gegebenen Pakets von dem Protokoll abhängt, das das Paket erzeugte. Der Vorspann enthält gewöhnlich eine Zieladresse, die die Zieldatenvorrichtung identifiziert, und Quellenadresse, die eine Datenvorrichtung identifiziert, die das Paket hervorbringt, wobei die Adressen typisch Medienzugangssteuer-(MAC)Adressen sind, um die Einmaligkeit in der Industrie zu sichern. Ein für eine Zielvorrichtung bestimmtes Paket wird hierin als ein Unicast-Paket bezeichnet. Der Vorspann enthält weiter ein Gruppenbit, das angibt, ob das Paket ein für mehrfache Zielvorrichtungen bestimmtes Multicast- oder Broadcast-(BC)Paket ist. Wenn das Gruppenbit auf logisch eins (1) gesetzt wird, wird es als ein Multicast-Paket betrachtet, und wenn alle Zieladressenbits auch auf logisch 1 gesetzt sind, ist das Paket ein BC-Paket. Zu Zwecken der vorliegenden Erfindung werden jedoch Multicast- und BC-Pakete gleich behandelt und werden im Folgenden als BC-Pakete

bezeichnet.

**[0057]** [Fig. 2](#) zeigt ein genaueres Blockschaltbild des Netzwerkschalters **102**. In der gezeigten Ausführung enthält der Netzwerkschalter **102** sechs ähnliche Vierfach-Steuerungs- oder Vierfach-Kaskaden-(QC)Vorrichtungen **202**, wobei jede vier der Ports **104** einschließt. Die QC-Vorrichtungen **202** können in jeder gewünschten Weise implementiert werden, z. B. als in ein einziges ASIC-(anwendungsspezifische integrierte Schaltung) Gehäuse integriert oder als getrennte integrierte Schaltungs-(IC)Chips, wie gezeigt. In der gezeigten Ausführung arbeitet jeder Port **104** bei 10 Mbps bei Halbduplex für einen Gesamtdurchsatz von 20 Mbps pro Port bei Voll-duplex. Dies ergibt insgesamt 480 Mbps für alle sechs der QC-Vorrichtungen **202** bei Vollduplexbetrieb. Jede der QC-Vorrichtungen **202** enthält vorzugsweise eine mit einem QC/CPU-Bus **204** verbundene Prozessor-Schnittstelle und eine mit einem Hochgeschwindigkeitsbus (HSB) **206** verbundene Bus-Schnittstelle. Der HSB **206** enthält einen Datenabschnitt **206a** und verschiedene Steuer- und Statussignale **206b**. Der HSB **206** ist ein 32-Bit 33 MHz Bus zum Übertragen von über ein Gigabit von Daten pro Sekunde.

**[0058]** Der HSB **206** und der QC/CPU-Bus **204** sind weiter mit einem Ethernet-Paketschalter-Manager (EP-SM) **210** verbunden, der in der gezeigten Ausführung als ASIC implementiert ist, obwohl die vorliegende Erfindung nicht auf eine bestimmte physikalische oder logische Implementierung begrenzt ist. Der EPSM **210** ist weiter mit einem Speicher **212** durch einen 32-Bit Speicherbus **214** verbunden, der einen Daten- und Adressenabschnitt **214a** und Steuersignale **214b** enthält. Der Speicher **212** enthält vorzugsweise 4 bis 16 Megabyte (MB) an dynamischem Direktzugriffspeicher (DRAM), obwohl, wenn gewünscht, mehr Speicher abhängig von den Bedürfnissen der einzelnen Anwendung hinzugefügt wird. Der EPSM **210** unterstützt jede von wenigstens drei verschiedenen Arten von DRAMs zur Implementierung des Speichers **212**, einschließlich schneller Seitenmodus-(FPM)Einzel-Inline-Speichermodule (SIMMs), die mit etwa 60 Nanosekunden (NS) arbeiten, Erweiterte Datenausgabe-(EDO)Modus DRAM SIMMs oder Synchronmodus- DRAM SIMMs. Sychrone DRAMs benötigen gewöhnlich einen 66 MHz Takt zum Erreichen einer Stoßdatenrate von 66 MHz oder 266 MB pro Sekunde. EDO DRAMs können mit entweder einem 33 oder 66 MHz Takt arbeiten, erreichen aber eine maximale Stoßdatenrate von 33 MHz oder 133 MB pro mit jeder Taktrate. FPM DRAMs können auch mit einem 33 oder 66 MHZ Takt arbeiten und erreichen eine maximale Stoßrate von 16 MHZ oder 64 MB pro Sekunde mit einem 33 MHz Takt und eine Stoßrate von 22 MHz oder 88 MB pro Sekunde mit einem 66 MHz Takt.

**[0059]** Der Speicherbus **214** umfasst einen Speicherdatenbus MD[31:0], Datenparitätssignale MD\_PAR[3:0], Reihen- und Spaltenadresssignale MA[11:0], ein Schreibfreigabesignal MWE\*, Bankauswählsignale RAS[3:0]\*/SD\_CS\*[3:0], die entweder Reihensignale für FPM DRAM und EDO DRAM oder Chipauswahlen für synchrone DRAM sind, Speicherbyte-Steuersignale CAS[3:0]\*/SD\_DQM[3:0], die Spaltensignale für FPM und EDO oder DQM für synchrone DRAM sind, ein Reihensignal SD\_RAS\* nur für synchrone DRAM, ein Spalten-signal SD\_CAS\* nur für synchrone DRAM, ein Serial-Eingang-SIMM/DIMM-Anwesenheits-Erfassungssignal PD\_SERIAL\_IN und ein Parallel-Eingang-SIMM/DIMM-Anwesenheits-Erfassungssignal PD\_LOAD\*.

**[0060]** Der HSB **206** ist mit einer Thunder LAN (TLAN) Portschnittstelle (TPI) **220** verbunden, die weiter mit einem Peripheriekomponenten-Verbindungs-(PCI) Bus **222** verbunden ist, der Daten und Adresssignale **222a** und zugehörige Statussignale **222b** umfasst. Der PCI-Bus **222** ist mit vier TLANS **226** verbunden, die in jeder gewünschten Weise implementiert werden können. Die TLANS **226** sind vorzugsweise die TNTE100 ThunderLAN™ PCI Ethernet™ Controller, hergestellt von Texas Instruments, Inc, (TI), wo jedes einen der Ports **110** einschließt. Für den EPSM **210** arbeitet die TPI **220** in einer ähnlichen Weise auf dem HSB **206** als eine andere QC-Vorrichtung **202** zum Anschließen von vier Ports. Der EPSM **210** "sieht" daher effektiv sieben (7) Vierfach-Portvorrichtungen. In Bezug auf den PCI-Bus **220** emuliert die TPI **220** einen Standard-PCI-Bus in dem erforderlichen Ausmaß zum richtigen Betrieb der TLANS **226**, die normalerweise mit PCI-Speichervorrichtungen verbunden sind. Der PCI-Bus **222** muss daher nicht voll PCI-kompatibel sein. Der PCI-Bus **222** ist mit einem Prozessor oder zentralen Verarbeitungseinheit (CPU) **230** verbunden, die mit einem lokalen Prozessorbus **232** zum Verbinden der CPU **230** mit dem lokalen RAM **234**, einem lokalen Flash-RAM **236** und, wenn gewünscht, mit einer seriellen Portschnittstelle **238** verbunden ist. Die serielle Portschnittstelle **238** ist vorzugsweise ein UART oder dergleichen. In der gezeigten Ausführung ist die CPU eine 32-Bit, 33 MHz i960RP CPU von Intel, obwohl die CPU **230** jeder andere geeignete Prozessor sein kann.

**[0061]** Die CPU **230** handhabt gewöhnlich die Initialisierung und Konfigurierung der TPI **220** und des EPSM **210** beim Einschalten des Netzwerkschalters **102**. Die CPU **230** überwacht und gewinnt auch Statistiken und verwaltet und steuert die Funktionen der verschiedenen Vorrichtungen des Netzwerkschalters **102** während des Betriebs. Die CPU **230** aktualisiert ferner die Hash-Tabellendaten im Speicher **212** durch den EPSM **210**. Der EPSM **210** steuert jedoch den Zugriff auf den Speicher **212** und führt die DRAM-Auffrischungszyklen durch, um dadurch Auffrischungsoperationen von der CPU **230** zu entfernen. Andernfalls würde die CPU **230**

6–8 Buszyklen benötigen, um jeden Auffrischungszyklus durchzuführen, was wertvolle Prozessor-Ressourcen verbrauchen würde. Die CPU **230** agiert auch als ein zusätzlicher Netzwerkport für verschiedene Zwecke und wird hierin oft als Port28 bezeichnet. Die Ports **104**, **110** und die CPU **230** schließen daher kollektiv die Ports Port0–Port28 ein.

**[0062]** Die CPU **230** ist weiter mit dem EPSM **210** durch einen CPU-Bus **218** verbunden, der einen Adress- und Datenabschnitt **218a** und zugehörige Steuer- und Statussignale **218b** umfasst. Der Adress- und Datenabschnitt **218a** wird vorzugsweise zwischen Adress- und Datensignale gemultiplext. Insbesondere umfasst der CPU-Bus **218** einen Adress/Daten-Bus CPU\_AD[31:0], einen Adress-Strobe CPU\_ADS\* von der CPU **230**, Datenbyte-Freigaben CPU\_BE[3:0], ein Lese/Schreib-Auswählsignal CPU\_WR\*, einen Burst-Letzte-Daten-Strobe CPU\_BLAST\*, ein Daten-Bereit-Signal CPU\_RDY\* und wenigstens ein CPU-Unterbrechungssignal CPU\_INT\*. In dieser Offenbarung bezeichnen normale Signalnamen anders als Daten- und Adresssignale positive Logik, wo das Signal als geltend gemacht betrachtet wird, wenn es hoch ist oder auf logisch eins (1) ist, und Signalnamen gefolgt von einem Stern (\*) bezeichnen negative Logik, wo das Signal als geltend gemacht betrachtet wird, wenn es tief ist oder auf logisch null (0) ist: Die Funktions-Definition ist im Allgemeinen einfach und gewöhnlich durch den Signalnamen bestimmbar.

**[0063]** [Fig. 3A](#) ist ein Blockschaltbild einer exemplarischen QC-Vorrichtung **202** zur Implementierung von vier der Ports **104**, wobei die Vorrichtung sechsmal dupliziert ist, um die 24 Ports Port0–Port23 zu implementieren. Eine bestimmte Vorrichtung ist der L64381 Quad Cascade Ethernet Controller von LSI Logic Corporation (LSI). Eine verbesserte Vorrichtung ist der QE110 Quad Cascade Ethernet Controller, auch von LSI, der zusätzliche Merkmale und Fähigkeiten enthält, wie hierin beschrieben. Es wird jedoch angemerkt, dass die vorliegende Erfindung nicht auf eine bestimmte Vorrichtung zum Implementieren der Ports **104** begrenzt ist. In der gezeigten Ausführung enthält jede QC-Vorrichtung **202** einen Ethernet-Kern **300** für jeden der Ports **104**, wo der Ethernet-Kern **300** voll synchron ist und eine Medien-Zugriffssteuerung, einen Manchester-Coder/Decoder und verdrillte Paar/AUI (Attachment Unit Interface) Transceiver enthält. Jeder Ethernet-Kern **300** ermöglicht bidirektionale Kommunikation mit einem verbundenen Netzwerk **106** auf einem entsprechenden Segment **108**, und jeder ist mit einem entsprechenden 128-Bit Empfangs-FIFO (First-in-First-out) **302** und einem 128-Bit Send-FOFO **304** verbunden. Jeder Ethernet-Kern **300** ist auch mit einem Block von Statistik-Zählern **306** verbunden, wo jeder Block von Statistik Zählern **306** 25 Zähler zum Bereitstellen von On-Chip-Wartung enthält. Die Zähler in jedem Block von Statistik-Zählern **306** erfüllen vorzugsweise die Forderungen des einfachen Netzwerk Verwaltungsprotokolls (SNMP). Jeder der FIFOs **302**, **304** ist weiter mit Busschnittstellenlogik **308** verbunden, die mit dem HSB **206** verbunden ist, um bidirektionalen Datenfluss zwischen jeder QG-Vorrichtung **202** und dem EPSM **210** zu ermöglichen. Jede QC-Vorrichtung **202** enthält Konfigurations- und Steuerlogik **310**, die programmierbares Konfigurieren ermöglicht, wie z. B. Einfügen von Quellenadressen, Einfügen einer Rahmenprüfsequenz (FCS), sofortiges Neusenden bei Kollision, Busübertragungsgröße und Sendepuffer-Schwellengröße.

**[0064]** Die Konfigurations- und Steuerlogik **310** und alle Blöcke von Statistik-Zählern **306** und die FOFOs **302**, **304** sind mit dem QC/CPU-Bus **204** verbunden. Der EPSM **210** stellt eine getrennte Schnittstelle zwischen dem CPU-Bus **218** und dem QC/CPU-Bus **204** bereit. Auf diese Weise hat die CPU **230** vollen Zugang, um die Aktivitäten jeder der QC-Vorrichtungen **202** und somit jedes der Ports **104** zu initialisieren, zu überwachen und zu modifizieren. Der QE110 Quad Cascade Ethernet Controller enthält eine zusätzliche Verbindung **320** zwischen der Konfigurations- und Steuerlogik **310** zum Erfassen eines Rückstau-Anzeichens, um eine Hemmungssequenz geltend zu machen, um ein gerade gesendetes Paket zu beenden, wenn das Rückstau-Anzeichen rechtzeitig empfangen wird. Das Rückstau-Anzeichen ist vorzugsweise ein auf dem HSB **206** ausgeführter Rückstau-Zyklus, obwohl jedes von mehreren Verfahren benutzt werden kann, um einen Rückstau anzuzeigen, z. B. ein getrenntes Signal oder dergleichen.

**[0065]** Es wird angemerkt, dass die Hemmungssequenz während der ersten 64 Bytes des Datenpakets gesendet werden sollte, das an einem Port empfangen wird, als "früh" oder rechtzeitig zu betrachten ist. Die ersten 16 Byte (4 DWORDs) sind nötig, bevor eine später beschriebene Hash-Lookup-Prozedur durch den EPSM **210** durchgeführt wird. Jedes Datenbit wird in etwa 100 ns über Ethernet 10Base-T übertragen; sodass die ersten 16 Byte in etwa 13 µs übertragen werden. 64 Byte werden in etwa 51 µs empfangen, sodass der Netzwerkschalter **102** etwa 38 µs hat, um die ersten 16 empfangenen Bytes zu übertragen, die Hashing-Prozedur durchzuführen, den Rückstau-Zyklus auszuführen und schließlich die Hemmungssequenz geltend zu machen. Da ein Hash-Lookup etwa 1–2 µs braucht, um zu vollenden, ist fast immer genug Zeit vorhanden, um die Hemmungssequenz rechtzeitig zu senden. Das rechtzeitige Geltendmachen der Hemmungssequenz ist jedoch nicht garantiert, sodass die Möglichkeit besteht, dass Pakete infolge einer Schwellenverletzungsbedingung fallen gelassen werden. Wenn der Rückstau-Zyklus spät ausgeführt wird, weist der Port den Rückstau-Zyklus zu-

rück, und der Netzwerkschalter **102** lässt das Paket fallen, wenn er außerstande ist, das Paket anzunehmen. Der Netzwerkschalter kann dieses Paket annehmen, da eine Schwellenbedingung ein frühes Anzeichen ist und daher Speicher vorhanden sein kann, um das Paket zu speichern.

**[0066]** Wenn der Rückstau-Zyklus in einer rechtzeitigen Weise ausgeführt wird, und wenn der Port in Halbduplex arbeitet, macht die Konfigurations- und Steuerlogik **310** als Reaktion einen Kollisionsbefehl an einem der Ethernet-Kerne **300** eines angegebenen Ports **104** geltend. Der Ethernet-Kern **300**, der den Kollisionsbefehl empfängt, macht dann die Hemmungssequenz geltend, um ein Paket zu beenden, das durch diesen Port **104** empfangen wird. Wenn der Rückstau-Zyklus in dem 64-Byte Fenster ausgeführt wird, zeigt der Port dem EPSM **210** an, dass der Rückstau-Zyklus für diesen Port ausgeführt wird, durch Geltendmachen eines Abort-Signals **ABORT\_OUT\*** auf dem HSB **206**. Wenn der Rückstau-Zyklus außerhalb des 64-Byte Fensters liegt und daher nicht rechtzeitig geltend gemacht wird, wird das **ABORT\_OUT\*** Signal nicht geltend gemacht, und der EPSM **210** lässt das Paket fallen. EPSM **210** lässt das Paket meistens fallen, wenn ein Versuch, Rückstau geltend zu machen, fehlschlägt. Obwohl erwünscht ist, so wenig Pakete wie möglich zur maximalen Effizienz fallen zu lassen, wird ein fallen gelassenes Paket schließlich auf höheren Netzwerkstufen in der hervorbringenden Datenvorrichtung erfasst und ist daher für den Gesamtbetrieb des Netzwerksystems **100** nicht fatal. Die hervorbringende Vorrichtung erkennt, dass das Paket fallen gelassen wurde und sendet ein oder mehr Pakete einschließlich des fallen gelassenen Pakets neu.

**[0067]** Die Busschnittstellenlogik **308** enthält vorzugsweise Lese-Latches **324** und Schreib-Latches **326** zur Implementierung eines gleichlaufenden Lese- und Schreibzyklusses auf dem HSB **206**, wie weiter unten beschrieben. Diese Latches speichern PORT\_NO[1:0] Signale, die auf dem HSB **206** bei bestimmten Zyklen eines ersten Taktsignals (CLK\_1) geltend gemacht werden. Das Signal CLK\_1 ist der Haupttakt für den HSB **206** und arbeitet in der gezeigten Ausführung typisch bei etwa 30–33 MHz. Da das Signal CLK\_1 der Haupttakt ist, wird es im Folgenden einfach als CLK-Signal bezeichnet. Ein zweites Taktsignal CLK\_2 wird auch für die Schnittstelle zum Speicher **212** verwendet und arbeitet bei der doppelten Frequenz des CLK-Signals oder bei etwa 60–66 MHz.

**[0068]** [Fig. 3B](#) ist ein Diagramm, das die Signale der in [Fig. 3A](#) gezeigten einzelnen Vierfach-Kaskaden-Vorrichtung **202** veranschaulicht. Die Signale sind in mehrere Funktions- und Busabschnitte geteilt, die mit dem QC-Bus **204** verbundene Prozessor-Schnittstellensignale, mit den vier Ports **104** verbundene Netzwerk-Schnittstellensignale, Statussignale, Takt- und Prüfsignale, mit dem HSB-Bus **206** verbundene Bus-Schnittstellensignale und gemischte Signale umfassen.

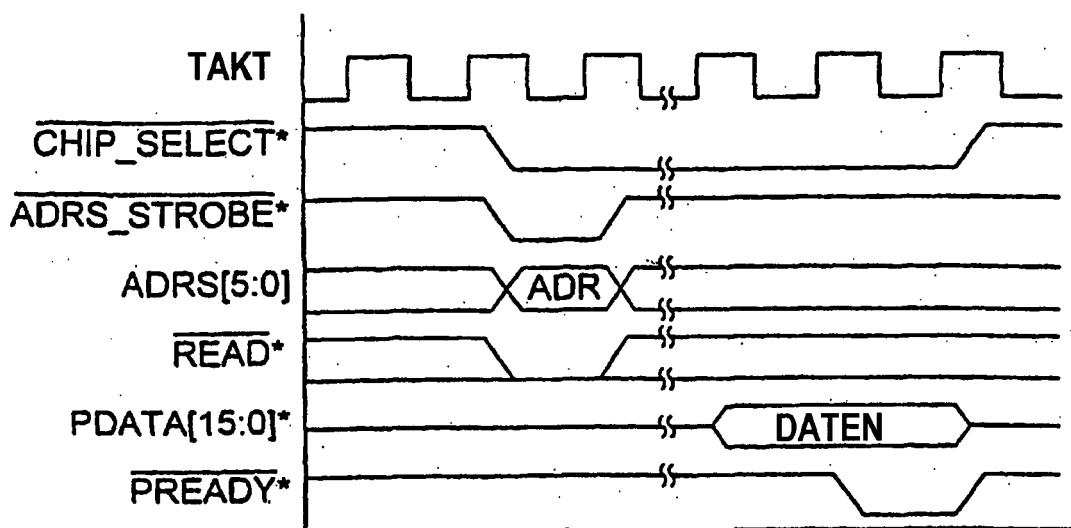

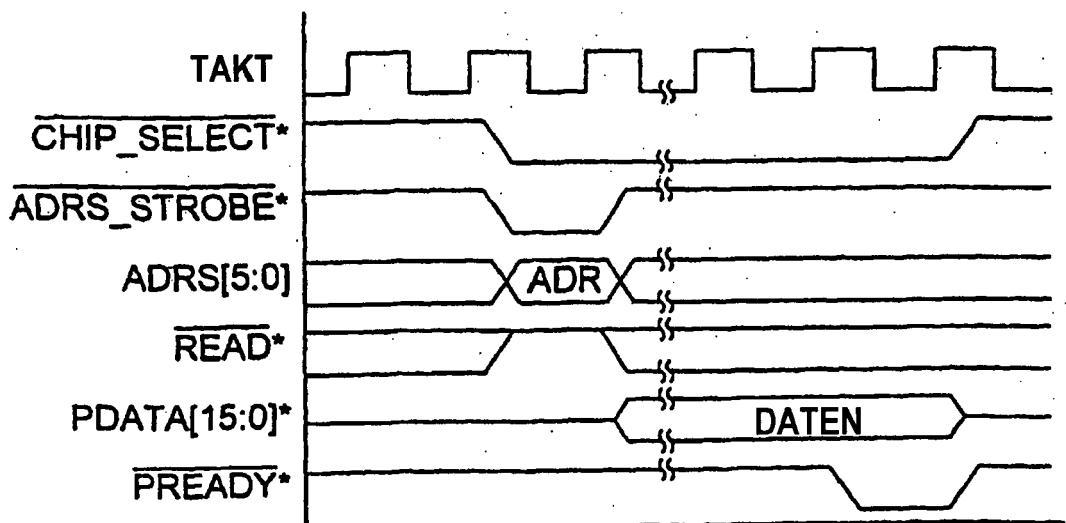

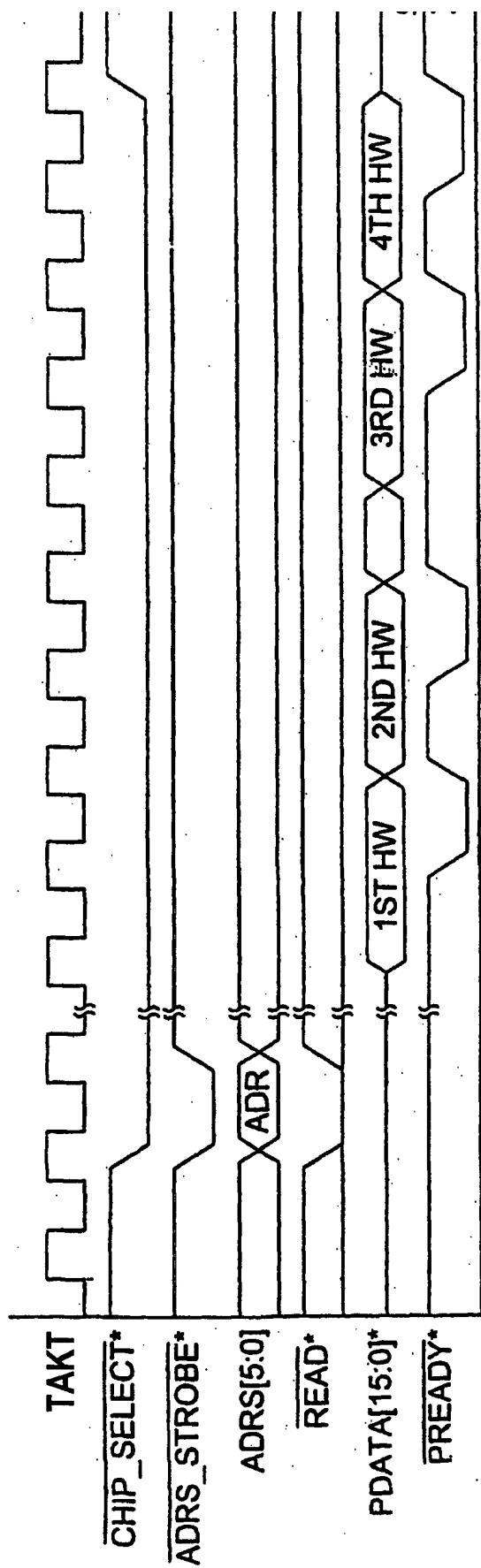

**[0069]** Den QC-Bus **204** betreffend schreibt der EPSM **210** Daten in die Register und Zähler **306, 310** der QC-Vorrichtung **202** durch Datensignale PDATA[15:0] und liest Daten daraus aus. Das Signal READ\* wird für einen Schreibvorgang hoch und für einen Lesevorgang tief gesetzt. Das einzelne Register in der QC-Vorrichtung **202** durch eine auf ADR[5:0] Signalen geltend gemachte Adresse bestimmt. Geltendmachen eines Adress-Strobesignals ADRS\_STROBE\* zusammen mit dem entsprechenden der mehreren Chipauswählsignalen CHIP\_SELECTm\* veranlasst die QC-Vorrichtung **202**, die ADRS-Signale zu speichern. Ein an den Signalnamen angehängtes "m" bezeichnet gewöhnlich mehrfache Signale eines einzelnen Typs. Zum Beispiel gibt es sechs getrennte CHIP\_SELCT[5:0]\* Signale, jedes zum Adressieren einer betreffenden der sechs QC-Vorrichtungen **202**. Ein Signal PREADY\* wird durch die QC-Vorrichtung **202** für einen Zyklus eines CLK-Signals während eines Schreibzyklusses nach der steigenden CLK-Flanke, auf der die verlangten Daten gespeichert werden, tief geltend gemacht. Für einen Schreibzyklus macht die QC-Vorrichtung **202** PREADY\* für einen CLK-Zyklus tief geltend, nachdem sie Daten auf den PDATA-Bus gelegt hat.

**[0070]** [Fig. 3C](#) ist ein exemplarisches Timing-Diagramm, das einen Prozessor-Lesezyklus für eine QC-Vorrichtung **202** veranschaulicht, und [Fig. 3D](#) ist ein exemplarisches Timing-Diagramm, das einen Prozessor-Schreibzyklus veranschaulicht. [Fig. 3D](#) ist ein exemplarisches Timing-Diagramm, das einen Prozessor-Stoßlesezugriffszyklus für eine QC-Vorrichtung **202** veranschaulicht. Diese Timing-Diagramme sind nur exemplarisch und werden gezeigt, um eine allgemeine Funktionalität und nicht ein bestimmtes Timing oder bestimmte Signaleigenschaften zu veranschaulichen.

**[0071]** Zurück auf [Fig. 3B](#) verweisend umfassen die Netzwerk-Schnittstellensignale die negativen und positiven Kollisionsschwellensignale, das Kollisionsbezugssignal, das serielle Daten-Ein-Signal, die negativen und positiven Manchester-codierten Datensignale, die positiven und negativen Datenschwellensignale, das Datenschwellenbezugssignal, die positiven und negativen Präemphasesignale und die Verdrillte-Paar/AUI-Modusauswählsignale für jeden der mit [3:0] bezeichneten vier Ports der QC-Vorrichtung **202**. Jede QC-Vorrichtung empfängt das CKL-Signal und hat einen CLOCK\_20 MHz Eingang, der ein 20 MHz Taktsignal empfängt, um

80, 20 und 10 MHz interne Taktsignale zur Verwendung durch die Ports **104** zu erzeugen. Jeder Ethernet-Kern **300** erfasst eine auf dem entsprechenden Segment **108** auftretende Kollision und sendet eine Hemmungssequenz entsprechend dem Ethernet CSMA/CD-(Carrier Sense Multiple Access/Collision Detect) Verfahren.

**[0072]** Die mit dem HSB **206** verbundenen Busschnittstellensignale betreffend beendet eine QC-Vorrichtung vorzeitig ein ganzes Paket durch Geltendmachen des Signals ABORT\_OUT\*. Der EPSM **210** beendet vorzeitig den laufenden Buszyklus durch Geltendmachen eines Abortsignals ABORT\_IN\*. In einer Ausführung sind die QC-Vorrichtungen **202** QE110 Vorrichtungen, die ersonnen sind, dem EPSM **210** zu ermöglichen, ein Paket, das empfangen wird, vorzeitig zu beenden, durch Ausführen eines Rückstau-Zyklusses auf dem HSB **206**. Dieser einzelne Typ von Rückstau-Fähigkeit ist ein "Paket für Paket" oder dynamischer "pro Port" Rückstau, der das Rückweisen eines Pakets erlaubt, das an einem Port empfangen wird. L64381-Vorrichtungen umfassen ein Selbseinfügungs-Rahmenprüfsequenzsignal (AI\_FCS\_IN\*), das werter unten beschrieben wird. QE110-Vorrichtungen ersetzen das AI\_FCS\_IN\* Signal mit einem Signal FBPNI\*, das benutzt wird, um die gleichen Funktionen wie das Siggnal AI\_FCS\_IN\* auszuführen, aber auch benutzt wird, um einen Rückstau-Zyklus und eine erhöhte Paketflut anzuzeigen. Natürlich können alternative Verfahren verwendet werden, um den hierin beschriebenen dynamischen Rückstau zu implementieren. Das heißt, der EPSM **210** macht das Signal FBPNI\* während eines Lesezyklusses geltend, um einen Rückstau-Anforderungszyklus auszuführen. Wenn das Signal ABORT\_OUT\* durch die entsprechende QC-Vorrichtung **202** während der Datenphase des Lesezyklusses geltend gemacht wird, dann wurde die Rückstau-"Anforderung" durch die QC-Vorrichtung **202** gewährt, die dann eine Hemmungssequenz geltend macht, um das Paket vorzeitig zu beenden. Wenn das Signal ABORT\_OUT\* nicht geltend gemacht wird, lässt der EPSM **210** das Paket fallen.

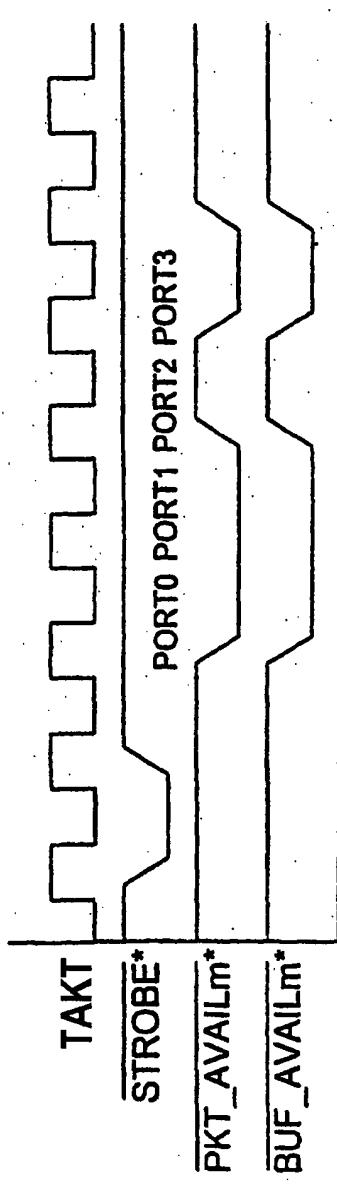

**[0073]** Der EPSM **210** macht ein Status-Strobesignal STROBE\* an allen QC-Vorrichtungen **202** und der TPI **220** geltend, die alle mit dem Status ihrer vier Ports **104** oder **110** (im Fall der TPI **220**) in gemultiplexter Weise auf Signale PKT\_AVAILm\* und BUF\_AVAILm\* antworten, wenn das Signal STROBE\* auf der steigenden Flanke des CLK-Signals geltend gemacht wird. Es gibt ein getrenntes Signal für jede QC-Vorrichtung **202**, einen Satz für die TPI **220** und einen ähnlichen Satz für die CPU **230**, die für einige Operation als ein weiterer Port agiert. Das heißt, die Signale PKT\_AVAILm\* und BUF\_AVAILm\* enthalten Signale PKT\_AVAIL[5:0]\* und BUF\_AVAIL[5:0]\* für die QC-Vorrichtungen, Signale TPI\_PKT\_AVAIL\* und TPI\_BUF\_AVAIL\*, andernfalls als PKT\_AVAIL[6]\* und BUF\_AVAIL[6]\* bezeichnet, für die TPI **220** und Signale PCB\_PKT\_AVAIL\* und PCB\_BUF\_AVAIL\*, andernfalls als PKT\_AVAIL[7]\* und BUF\_AVAIL[7]\* bezeichnet, die der CPU **230** entsprechen, für insgesamt 8 Signale pro Signaltyp.

**[0074]** Auf diese Weise umfasst der HSB **206** Signale PKT\_AVAIL[0]\* und BUF\_AVAIL[0]\* für die erste QC-Vorrichtung **202**, um auf die vier Ports Port0–Port3 zuzugreifen, der HSB **206** umfasst Signale PKT\_AVAIL[1]\* und BUF\_AVAIL[1]\* für die nächste QC-Vorrichtung **202**, um auf die nächsten vier Ports Port0–Port7 zuzugreifen, usw., die TPI **220** umfasst Signale PKT\_AVAIL[6]\* und BUF\_AVAIL[6]\*, um auf die Ports Port24–Port27 zuzugreifen, und der EPSM **210** enthält interne Signale PKT\_AVAIL[7]\* und BUF\_AVAIL[7]\* für die CPU **230**. Bis zu vier Bits werden auf jedem der Signale entsprechend den vier Ports, getrennt durch jeweilige Zyklen des CLK-Signals, gemultiplext.

**[0075]** Als Reaktion auf das STROBE\* Signal enthält die Busschnittstellenlogik **308** Portstatuslogik **303** zum Multiplexen von vier Statusbits auf einem betreffenden der BUF\_AVAIL[5:0]\* Signale, um anzuzeigen, ob jeder von ihnen entsprechenden Sende-FIFOs **304** für den betreffenden Port genug freien Raum zur Verfügung hat, um Daten zu speichern. Die Portstatuslogik **303** ist entweder für alle vier Ports, wie gezeigt, zentralisiert oder ist unter den Ports verteilt. Die Bestimmung von freiem Raum erfolgt entsprechend einem Konfigurationsregister in der Busschnittstellenlogik **308**, das eine Busübertragungsfeldgröße (TBUS) speichert, die vorzugsweise durch die CPU **230** zu 16, 32 oder Bytes konfiguriert wird. In ähnlicher Weise enthält als Reaktion auf das STROBE\* Signal die TPI **220** ähnliche Portstatuslogik **820** ([Fig. 8B](#)), die mit dem HSB **206** zum Multiplexen von vier Statusbits auf dem BUF\_AVAIL[6]\* Signal, um anzuzeigen, ob jeder ihrer internen Sende-FIFOs, unten beschrieben, genug freien Raum hat, um Daten für die entsprechenden der TLANS **226** für die jeweiligen Ports Port24–Port27 zu speichern. Für die CPU **230** oder Port28 macht ein PCB **406** ([Fig. 4](#)) in dem EPSM **210** ein einzelnes Statusbit auf dem BUF\_AVAIL[7]\* Signal geltend, um anzuzeigen, ob ein interner PCB-Sende-FIFO in dem EPSM **210** verfügbaren Raum hat, um Daten für die CPU **230** zu speichern.

**[0076]** In einer ähnlichen Weise multiplext als Reaktion auf das STROBE\* Signal die Portstatuslogik **303** der Busschnittstellenlogik **308** in jeder QC-Vorrichtung **202** vier Statusbits auf einem entsprechenden der PKT\_AVAIL[5:0]\* Signale, die anzeigen, ob jeder ihrer Empfangs-FIFOs **302** für den betreffenden Port genug Daten entsprechend dem TBUS-Wert hat, um empfangene Daten für eine Busübertragung auf dem HSB **206** zu übertragen. Desgleichen multiplext die TPI **220** vier Statusbits auf dem PKT\_AVAIL[6]\* Signal, das anzeigt,

ob ihre internen Empfangs-FIFOs genug Daten von den betreffenden Ports Port23–Port27 empfangen haben, um sie auf dem HSB **206** zu übertragen. Für die CPU **230** macht der PCB **406** im EPSM **210** ein einzelnes Statusbit auf dem PKT\_AVAIL[7]\* Signal geltend, um anzugeben, ob ein interner PCB-Empfangs-FIFO im EPSM **210** genug Daten von der CPU **230** für eine HSB **206** Busübertragung empfangen hat.

**[0077]** [Fig. 3F](#) ist ein exemplarisches Timing-Diagramm, das eine Pufferstatusabfrage der QC-Vorrichtung **202** und der TPI **220**, einschließlich Geltendmachung des STROBE\* Signals durch den EPSM **210** und Antwort durch jede der QC-Vorrichtungen **202** auf das Geltendmachen jeweiliger PKT\_AVAILm\* und BUF\_AVAILm\* Signale durch die TPI **220** veranschaulicht. Die Verweise auf Port0, Port1, Port2 und Port3 in [Fig. 3F](#) sind die vier betreffenden Ports einer bestimmten QC-Vorrichtung **202** oder der TPI **220**. Der PCB **406** antwortet in einer ähnlichen Weise, außer dass sein Port für alle vier Phasen aktiv ist. Das STROBE\* Signal ist pegelgetriggert und daher auf der ersten steigenden Flanke des CLK-Signals tief gesampt. Es wird angemerkt, dass das Timing-Diagramm von [Fig. 3F](#) nur exemplarisch ist und gezeigt wird, um die allgemeine Funktionalität und nicht ein bestimmtes Timing oder bestimmte Signaleigenschaften zu veranschaulichen. Zum Beispiel ist das STROBE\* Signal periodisch und wird typischerweise für mehr als einen CLK-Zyklus im Betrieb der gezeigten Ausführung tief geltend gemacht.

**[0078]** Wieder auf [Fig. 3B](#) verweisend wird das PORT\_BUSY\* Signal benutzt, um anzugeben, ob der jeweilige Port im Halbduplexmodus sendet oder empfängt, oder wenn der Port im Vollduplexmodus sendet. Lese-datensignale READ\_OUT\_PKT[5:0]\* werden von dem EPSM **210** geltend gemacht, um eine betreffende QC-Vorrichtung **202** zu informieren, Daten von einem betreffenden Empfangs-FIFO **302** auf die Datensignale DATA[31:0] zu legen. In einer ähnlichen Weise werden Schreibdatensignale WRITE\_IN\_PKT[5:0] durch den EPSM **210** geltend gemacht, um eine betreffende QC-Vorrichtung **202** zu informieren, Daten von den Datensignalen DATA[31:0] in einen betreffenden Sende-FIFO **304** zurückzugewinnen. Auch werden ähnliche Signale PCG\_RD\_OUT\_PKT\*, PVB\_WR\_IN\_PKT\* und TPI\_RFAD\_OUT\_PKT\*, TPI\_WRITE\_IN\_PKT\* für die TPI **220** bzw. die CPU **230** eingeschlossen. Alle Lese- und Schreibsignale werden kollektiv als READ\_OUT\_PKTm\* bzw. WRITE\_IN\_PKTm\* bezeichnet. Die PORT\_NO[1:0] Bits geben an, welcher einzelne Port **104** für einen auf dem HSB **206** ausgeführten Zyklus adressiert wird.

**[0079]** Ein Signal SOP\* gibt den Start des Pakets an, wenn der Anfang oder Vorspann eines Pakets auf dem HSB **206** übertragen wird. Das AI\_FCS\_IN\* Signal wird typischerweise mit dem SOP\* und einem der WRITE\_IN\_PKTm\* Signale geltend gemacht, um eine L64381-Vorrichtung (für eine Implementierung der QC-Vorrichtungen **202**) zu veranlassen, automatisch einen CRC-(zyklische Redundanzprüfung)Wert aus den Daten in dem Paket zu berechnen und den CRC in das FCS-Feld des Pakets einzufügen. Eine QE110 Vorrichtung ersetzt das AI\_FCS\_IN\* Signal mit dem FBPN\* Signal, wie früher beschrieben, für zusätzliche Funktionen. Ein Signal EOP\* bezeichnet das Ende des Pakets, wenn die letzte Datenübertragung eines Datenpakets auf dem HSB **206** übertragen wird. BYTE\_VALID[3:0]\* Signale geben an, welche Bytes in dem gegenwärtigen Wort auf den DATA-Signalen gültig sind. Es wird angemerkt, dass ein Datenpaket für ein einzelne Übertragung auf dem HSB **206** gewöhnlich zulang ist, sodass jeder Buszyklus eine Datenmenge kleiner als oder gleich dem TBUS-Wert überträgt.

**[0080]** Man wird erkennen, dass jede QC-Vorrichtung **202** jeden ihrer vier Port als 10Base-T Ethernet-Ports betreibt. Man wird weiter erkennen, dass der EPSM **210** Zugang hat, um alle Register der QC-Vorrichtungen **202** durch den QC-Bus **204** zu lesen und zu beschreiben. Ferner liest der EPSM **210** Daten aus allen Empfangs-FIFOs **320** und schreibt Daten in alle Sende-FIFOs **304** durch den HSB **206**.

**[0081]** [Fig. 3G](#) ist ein exemplarisches Timing-Diagramm, das einen gleichzeitigen Lese- und Schreibzyklus auf dem HSB **206** veranschaulicht. Der obere Teil des Timing-Diagramms bezeichnet den Zyklustyp, wo zwei gleichlaufende Lese- und Schreibzyklen einer nach dem anderen ausgeführt werden. Die Signale CLK, CLK\_2, STROBE\*, READ\_OUT\_PKTm\*, WRITE\_IN\_PKTm\*, PORT\_NO[1:0], DATA[31:0] und ABORT\_OUT\* sind auf einer Y Achse (oder Vertikalachse) über Zeit geplottet, die auf einer X-Achse (oder Horizontalachse) des Timing-Diagramms geplottet ist. Es gibt zwei verschiedene Typen von gleichzeitigen Lese- und Schreibzyklen, die abhängig von der einzelnen Ausführung durchgeführt werden. Für den ersten, allgemeinen Typ von gleichzeitigen Zyklen werden, wenn die QC-Vorrichtungen **202** mit den QE110 Vorrichtungen, die die Latches **324**, **326** enthalten, implementiert sind, gleichzeitige Lese- und Schreibzyklen ohne weitere Verbesserung durchgeführt. Alternativ, wenn die QC-Vorrichtungen **202** mit den L64381 Vorrichtungen implementiert sind, werden externe Latches und Auswahllogik (nicht gezeigt) hinzugefügt, um die PORT\_NO Signale zu speichern, wenn auf dem HSB **206** geltend gemacht. Ein zweiter, spezieller Typ von gleichzeitigen Lese- und Schreibzyklen wird mit den L64381 Vorrichtungen ohne weitere Verbesserung durchgeführt, aber nur, wenn die PORT\_NO Signale gleich sind und nur, wenn die QC-Vorrichtungen **202** verschieden sind.

**[0082]** Der EPSM **210** bestimmt den Typ des auszuführenden Zyklusses, z. B. Lesen, Schreiben, gleichzeitiges Lesen und Schreiben, Rückstau usw. Ein Lesezyklus wird gewöhnlich durch Geltendmachung eines der READ\_OUT\_PKTm\* Signale angegeben, und ein Schreibzyklus wird gewöhnlich durch Geltendmachung eines der WRITE\_IN\_PKTm\* Signale angegeben. Ein gleichzeitiger Lese- und Schreibzyklus wird durch gleichzeitige Geltendmachung eines READ\_OUT\_PKTm\* Signals und eines WRITE\_IN\_PKTm\* Signals angegeben. Der EPSM **210** führt einen gleichzeitigen Lese- und Schreibzyklus zwischen Ports unter bestimmten Bedingungen durch, z. B. nur wenn beide Ports konfiguriert sind, um im Durchschalt-(CT)Modus, unten ausführlicher beschrieben, zu arbeiten.

**[0083]** Während des gleichzeitigen Zyklusses macht der EPSM **210** eines der READ\_OUT\_PKTm\* Signale am Anfang des dritten CLK-Zyklusses tief geltend, um eine der QC-Vorrichtungen oder die TPI **220** anzugeben, und macht die geeignete Portnummer auf den PORT\_NO[1:0] Signalen während des dritten CLK-Zyklusses geltend, um einen der vier Ports der durch das geltend gemachte READ\_OUT\_PKTm\* Signal identifizierten QC-Vorrichtung **202** anzugeben. Die durch das bestimmte READ\_OUT\_PKTm\* Signal identifizierte QC-Vorrichtung **202** speichert die PORT\_NO[1:0] Signale im dritten CLK-Zyklus, um den einzelnen Port, der gelesen wird, zu bestimmen. Zum Beispiel sind die QE110 Vorrichtungen, die die QC-Vorrichtungen **202** implementieren, mit den Lese-Latches **324** konfiguriert, um die Signale PORT\_NO[1:0] zu speichern. Außerdem enthält die TPI **220** ähnliche Lese-Latches **819b** ([Fig. 8B](#)), um die PORT\_NO[1:0] Signale im dritten CLK-Zyklus zu speichern, wenn durch das READ\_OUT\_PKT[6]\* Signal angegeben. Alternativ werden externe Latches für diesen Zweck verwendet, wenn die QC-Vorrichtungen **202** mit den L64381 Vorrichtungen implementiert sind. An diesem Punkt ist der identifizierte einzelne Port PORT0–PORT27 als der Quellenport für einen Lesezyklus auf dem HSB **206** bezeichnet worden.

**[0084]** Der EPSM **210** macht eines der WRITE\_IN\_PKTm\* Signale am Anfang des vierten CLK-Zyklusses tief geltend, um die gleiche oder irgendeine andere der QC-Vorrichtungen **202** oder die TPI **220** zu bezeichnen, und macht die geeignete Portnummer auf den PORT\_NO[1:0] Signalen während des vierten CLK-Zyklusses geltend, um einen der vier Ports der Vorrichtung zu bezeichnen, die durch das geltend gemachte WRITE\_IN\_PKTm\* Signal bezeichnet wird. Die durch das einzelne WRITE\_IN\_PKTm\* Signal identifizierte QC-Vorrichtung speichert die PORT\_NO[1:0] Signale im vierten CLK-Zyklus, um den einzelnen Port, in den geschrieben wird, zu bestimmen. Zum Beispiel sind die QE110 Vorrichtungen, die die QC-Vorrichtungen **202** implementieren, mit den Schreib-Latches **326** konfiguriert, um die Signale PORT\_NO[1:0] im vierten CLK-Zyklus zu speichern. Außerdem enthält die TPI **220** ähnliche Schreib-Latches **819b**, ([Fig. 8B](#)), um die PORT\_NO[1:0] Signale im vierten CLK-Zyklus zu speichern, wenn durch das WRITE\_IN\_PKT[6]\* Signal angegeben. In dieser Weise wird irgendein anderer der Ports Port0–Port27 als der Zielport für einen Schreibzyklus auf dem HSB **206** bezeichnet, wobei der Schreibzyklus zur gleichen Zeit wie der gerade angegebene Lesezyklus stattfindet. Die Quellen- und Zielports können auf der gleichen QC-Vorrichtung oder zwei Ports der TPI **220** sein, oder können zwischen verschiedenen QC-Vorrichtungen **202** liegen. Ein gleichzeitiger Lese- und Schreibzyklus wird jedoch zwischen einem der Ports **104** der QC-Vorrichtungen **202** und einem der Ports **110** der TPI **220** in der gezeigten Ausführung wegen der Unterschiede in der Datenübertragungsgeschwindigkeit nicht durchgeführt.

**[0085]** In den folgenden Zyklen des CLK-Signals werden Paketdaten gleichzeitig übertragen oder aus dem Quellenport gelesen und über den HSB **206** direkt in den Zielport geschrieben, ohne in dem EPSM **210** oder dem Speicher **212** gespeichert zu werden. Die Datenübertragung erfolgt in Zyklen 5, 6, 7 und 8 zum Übertragen mehrerer Bytes abhängig von der Ausführung. Zum Beispiel werden bis zu 64 Bytes für L64381 Vorrichtungen übertragen, und bis zu 256 Bytes werden für QE110 Vorrichtungen übertragen. Obwohl vier CLK-Zyklen für die Datenübertragung gezeigt werden, kann die Datenübertragung mit einem, zwei oder vier CLK-Zyklen abhängig davon stattfinden, wie viele Daten übertragen werden. Für neue Pakete wird zuerst ein normaler Lesezyklus durchgeführt, um die Quellen- und Ziel-MAC-Adressen in den EPSM **210** zu bringen, der dann eine weiter unten beschriebene Hashig-Prozedur durchführt, um die Zielportnummer, wenn bekannt, zu bestimmen. Sobald die Zielportnummer bekannt ist, und wenn es nur einen Zielport gibt, kann eine gleichzeitige Lese- und Schreib-Operation für jeden Abschnitt oder den ganzen Rest des Pakets, wie gewünscht, durchgeführt werden.

**[0086]** Der spezielle Typ des gleichzeitigen Lese- und Schreibzyklusses wird durchgeführt, wenn die PORT\_NO Signale gleich sind, aber zwischen zwei verschiedenen Ports und daher zwischen zwei verschiedenen QC-Vorrichtungen **202**. [Fig. 3G](#) zeigt auch diesen Fall, außer dass die PORT\_NO Signale während des ganzen Zyklusses unverändert bleiben. Die Latches **324**, **326** sind nicht erforderlich, da die PORT\_NO Signale unverändert bleiben, sodass dieser Typ von Bleizeitigem Zyklus zwischen zwei verschiedenen L64391 Vorrichtungen ohne externe Latches oder Auswahllogik durchgeführt werden kann. Der EPSM **210** bestimmt, dass

die PORT\_NO Signale zwischen den Quellen- und Zielports gleich sind, und dass zwei verschiedene QC-Vorrichtungen **202** involviert sind, und lässt dann den gleichzeitigen Zyklus, wie gezeigt, laufen.

**[0087]** Wein [Fig. 3G](#) gezeigt, findet eine zweite, gleichzeitige Lese- und Schreibübertragung im sechsten CLK-Zyklus statt, wo die PORT\_NO[1:0] Signale dann im siebten, achtten und neunten Zyklus mit dem Lese-Modus, der Leseportnummer und der Schreibportnummer geltend gemacht werden. Als Reaktion wird ein READ\_OUT\_PKTm\* Signal für den siebten Zyklus deaktiviert. Desgleichen wird ein WRITE\_IN\_PKTm\* Signal für den achtzen Zyklus deaktiviert. Dieser zweite, gleichzeitige Zyklus ist entweder eine Fortsetzung des ersten gleichzeitigen Zyklusses zum Bereitstellen von fortlaufenden und aufeinanderfolgenden Daten des gleichen Pakets, oder kann der Beginn eines gänzlich verschiedenen Pakets sein. Die Quellen- und Zielports sind für fortgesetzte Daten für das gleiche Paket die gleichen. Entweder der Quellenport, der Zielport oder beide können jedoch im zweiten, gleichzeitigen Zyklus zum Übertragen von Daten für ein unterschiedliches Paket verschieden sein.

**[0088]** [Fig. 3H](#) ist ein Flussdiagramm, das eine Prozedur zum Ausführen eines gleichzeitigen Lese- und Schreibzyklusses auf dem HSB **206** veranschaulicht. In einem ersten Schritt **330** stellt der EPSM **210** fest, ob ein gleichzeitiger Lese- und Schreibzyklus auf dem HSB **206** zwischen einem Quellenport und einem Zielport ausgeführt werden kann. Im nächsten Schritt **332** macht dann der EPSN **210** die geeigneten Signale geltend, um den Quellenport zu identifizieren. Dies wird durch Geltendmachung der Quellen- oder "Lese"-Portnummer mittels der PORT\_NO Signale auf dem HSB **206** und durch Geltendmachung des geeigneten READ\_OUT\_PKTm\* Signals durchgeführt. Im nächsten Schritt **334** erfasst oder speichert die identifizierte Quellenport-Vorrichtung die Identifikationssignale. In dem speziellen gleichzeitigen Zyklus ohne Latches erfasst die QC-Vorrichtung **202** das READ\_OUT\_PKTm\* Signal und dann die PORT\_NO Signale auf dem HSB **206** und beginnt, sich auf einen Lesezyklus vorzubereiten. In den allgemeinen gleichzeitigen Zyklen, die Latches verwenden, speichert die angegebene QC-Vorrichtung **202** oder die TPI **220** in Schritt **334** die Leseportnummer und beginnt, sich auf einen Lesezyklus vorzubereiten.

**[0089]** Im nächsten Schritt **336** macht der EPSM **210** die geeigneten Signale geltend, um den Zielport zu identifizieren. Für den speziellen gleichzeitigen Zyklus macht der EPSM **210** das geeignete WRITE\_IN\_PKTm\* Signal geltend und bewahrt die gleichen PORT\_NO Signale. Für den allgemeinen Fall macht der EPSM **210** auch die Ziel- oder "Schreib"-Portnummer auf dem HSB **206** zusammen mit dem geeigneten WRITE\_IN\_PKTm\* Signal im nächsten Schritt **336** geltend. Im nächsten Schritt **338** erfasst oder speichert die identifizierte Zielport-Vorrichtung die Identifikationssignale. In dem speziellen Zyklus ohne Latches erfasst die angegebene QC-Vorrichtung **202** das WRITE\_IN\_PKTm\* Signal und dann die PORT\_NO Signale auf dem HSB **206** und beginnt, sich auf einen Schreibzyklus vorzubereiten. Für den allgemeinen Fall speichert die angegebene QC-Vorrichtung **202** oder die TPI **220** die Ziel- oder Schreibportnummer im nächsten Schritt **338**. Schließlich stellt im nächsten Schritt **340** der angegebene Quellenport die Daten auf dem HSB **206** bereit, während der angegebene Zielport die Daten aus dem HSB **206** in einem gleichzeitigen Lese- und Schreibzyklus liest.

**[0090]** Die gleichzeitige Lese- und Schreib-Operation ist der schnellste Typ von Datenübertragungszyklus, da nur ein einziger Buszyklus für jede Übertragung von Paketdaten benötigt wird. Wie weiter unten beschrieben, benötigt eine normale CT-Betriebsart wenigstens zwei Übertragungen, eine von dem Quellenport zu dem EPSM **210** und eine andere von dem EPSM **210** zu dem Zielport, was zwei getrennte Zyklen auf dem HSB **206** für die gleichen Daten benötigt. Ein gleichzeitiger Lese- und Schreibzyklus benötigt eine einzige direkte Übertragung auf dem HSB **206** für die gleichen Daten, wodurch die Bandbreite des HSB **206** erhöht wird. Andere, langsamere Modi werden bereitgestellt, einschließlich mehrerer Interim-CT- und Speichern-und-Weiterleiten-(SnF)Modi, wo Paketdaten in den Speicher **212** geschrieben werden, bevor sie zu dem Zielport übertragen werden.

**[0091]** [Fig. 4](#) zeigt ein vereinfachtes Blockschaltbild des EPSM **211**, das den Datenfluss und Konfigurationsregister veranschaulicht. Der EPSM **210** enthält drei Hauptabschnitte, einschließlich eines HSB-Steuerungsblocks (HCB) **402**, eines Speicher-Steuerungsblocks (MCB) **404** und eines Prozessor-Steuerungsblocks (PCB) **406**. Eine QC-Schnittstelle **410** verbindet den HSB **206** und den HCB **402** des EPSM **210**. Ein Satz von Puffern oder FIFOs **412** ist mit der anderen Seite der QC-Schnittstelle **410** verbunden, wo die FIFOs **412** weiter unten beschriebene Empfangs-, Sende- und Durchschalt-FIFOs umfassen. Die andere Seite der FIFOs (ausschließlich eines CT-Puffers, [Fig. 5A](#)) ist mit dem MCB **404** durch eine MCB-Schnittstelle **414** verbunden, die mit einer HCB-Schnittstelle **418** in dem MCB **404** durch einen geeigneten Bus **420** verbunden ist. Die HCB-Schnittstelle **418** ist weiter mit einer Speicherschnittstelle **422** verbunden, die mit dem Speicher **212** durch den Speicherbus **214** verbunden ist. Die Speicherschnittstelle **422** ist weiter mit einer Seite einer PCB-Schnitt-

stelle **424** verbunden, deren andere Seite mit einer Seite einer MCB-Schnittstelle **426** in dem PCB **406** durch einen geeigneten MCB-Bus **428** verbunden ist. Die andere Seite der MCB-Schnittstelle **426** ist mit einer Seite eines Satzes von FIFOs **430** verbunden, die weiter mit einer CPU-Schnittstelle **432** in dem PCB **406** verbunden sind. Die CPU-Schnittstelle **432** ist mit dem QC/CPU-Bus **204** und mit dem CPU-Bus **218** verbunden. Die CPU-Schnittstelle **432** ist weiter mit einer Seite eines zweiten Satzes FIFOs **434** in dem PCB **406** verbunden, deren andere Seite mit einer QC/HCB-Schnittstelle **436** verbunden ist. Die andere Seite der QC/HCB-Schnittstelle **436** ist mit der QC-Schnittstelle **410** über einen geeigneten HCB-Bus **438** verbunden.

**[0092]** Es wird angemerkt, dass die Signale PCB\_BUF\_AVAIL\*, PCG\_PKT\_AVAIL\*, PCB\_RD\_OUT\_PKT\* und PCB\_WR\_IN\_PKT\* des HCB-Busses **438**, die mit dem PCB **406** und der CPU **230** verbunden sind, in den Signalen BUF\_AVAILm\*, PKT\_AVAILm\*, READ\_OUT\_PKTm\* und WRITE\_IN\_PKTm\* enthalten sind. In der gezeigten Ausführung ist der HCB-Bus **438** ähnlich dem HSB **206** und ist im Wesentlichen eine interne Version des HSB **206** im EPSM **210**. Der PCB **406** verhält sich in ähnlicher Weise wie jeder der Ports **104** und die TPI **220** zu dem HCB **402**. Auf diese Weise arbeitet die CPU **230**, durch die Funktion des PCB **406**, als ein zusätzlicher Port (Port28) zu dem HCB **402**.

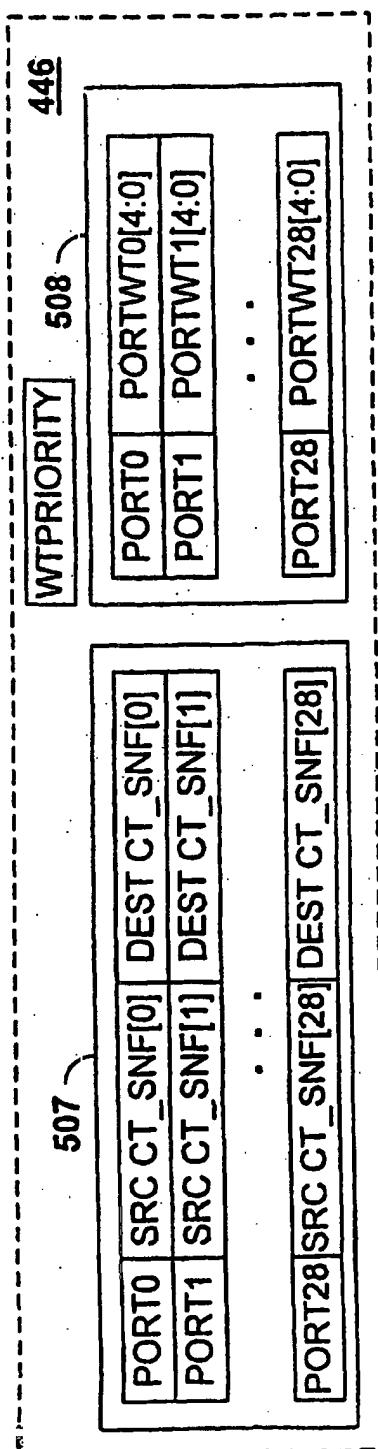

**[0093]** Die CPU-Schnittstelle **432** ist mit einer Registerschnittstelle **440** durch einen Bus **442** verbunden, wo die Registerschnittstelle **440** weiter mit einem Registerbus **444** verbunden ist. Der Registerbus **444** ist mit einem Satz von HCB-Konfigurationsregistern **446** in dem HCB **401** und einem Satz von MCB-Konfigurationsregistern **448** in dem MCB **404** verbunden. In dieser Weise initialisiert und programmiert die CPU **230** die Register in den HCB- und MCB-Konfigurationsregistern **446** und **448** durch die CPU-Schnittstelle **432** und die Registerschnittstelle **440**.

**[0094]** Die MCB-Konfigurationsregister **448** werden benutzt, eine wesentliche Menge mit den Ports und dem Speicher **212** verbundener Konfigurationsinformation zu speichern. Zum Beispiel enthalten die MCB-Konfigurationsregister **448** Port-Statusinformation, die angibt, ob jeder in einem lernenden (LRN), weiterleitenden (FWD), blockierten (BLK), zuhörenden (LST) oder abgeschalteten (DIS) Zustand ist, Speichersektorinformation, Busbenutzungsinformation des Speicherbusses **214**, Zahl fallen gelassener Pakete, Hash-Tabelleninformation, Speicherschwellen, BC-Schwellen, Identifikation von sicheren Ports, wenn vorhanden, Speichersteuerinformation, MCB-Unterbrechungsquellenbits, Unterbrechungsmaskierungsbits und Abfragequellenbits usw.

**[0095]** Die Beschreibung des EPSM **210** veranschaulicht, dass die CPU **230** Zugriff auf die QC-Vorrichtungen und den Speicher **212** für Konfigurations- und Steuerzwecke hat. Obwohl der Hauptdatenfluss mit dem HSB **206** mit dem EPSM **210** durch die FIFOs **412** und den Speicher **212** ist, findet ein Datenfluss auch zwischen dem HSB **206** und der CPU **230** durch den HCB-Bus **438** und zugehörige FIFOs und Schnittstellen des EPSM **210** statt.

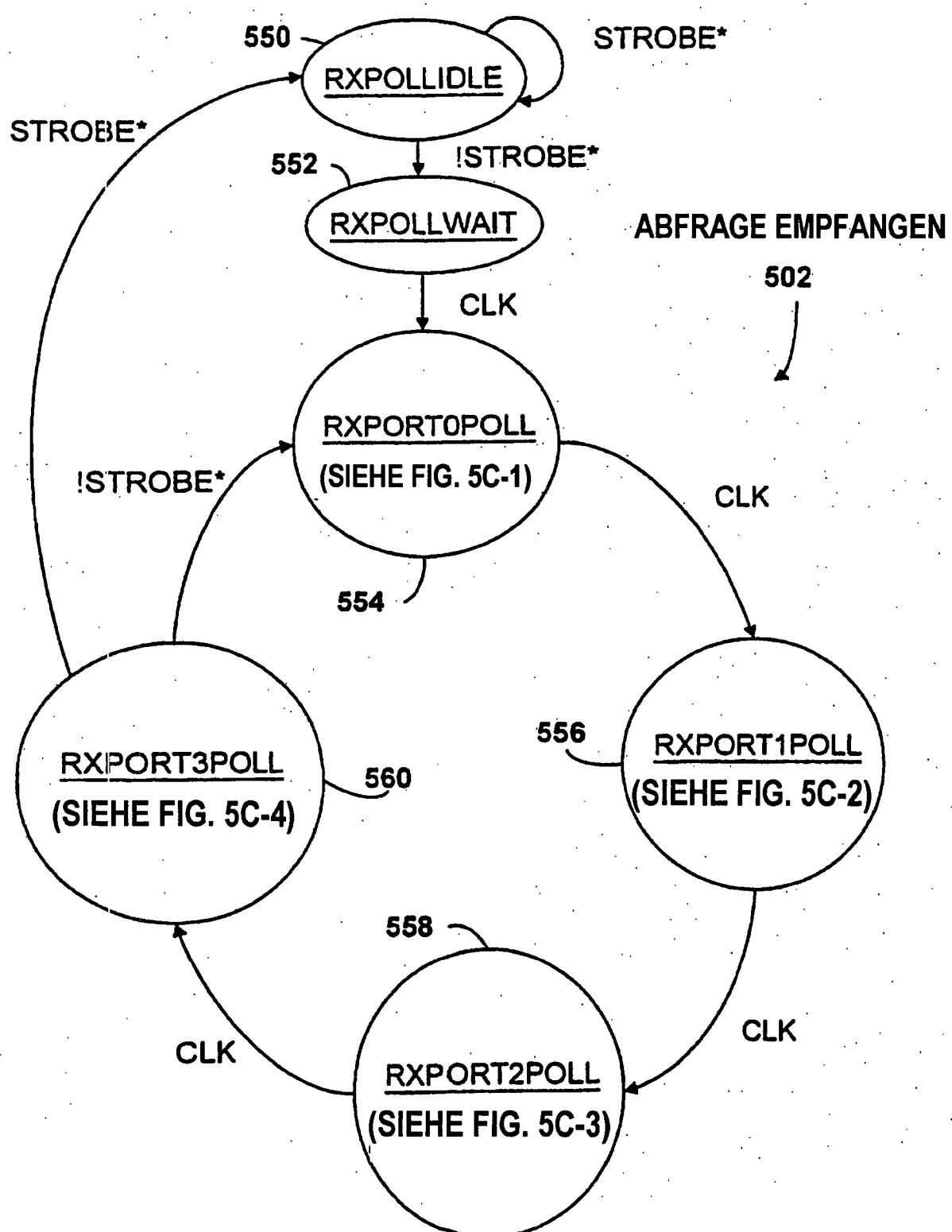

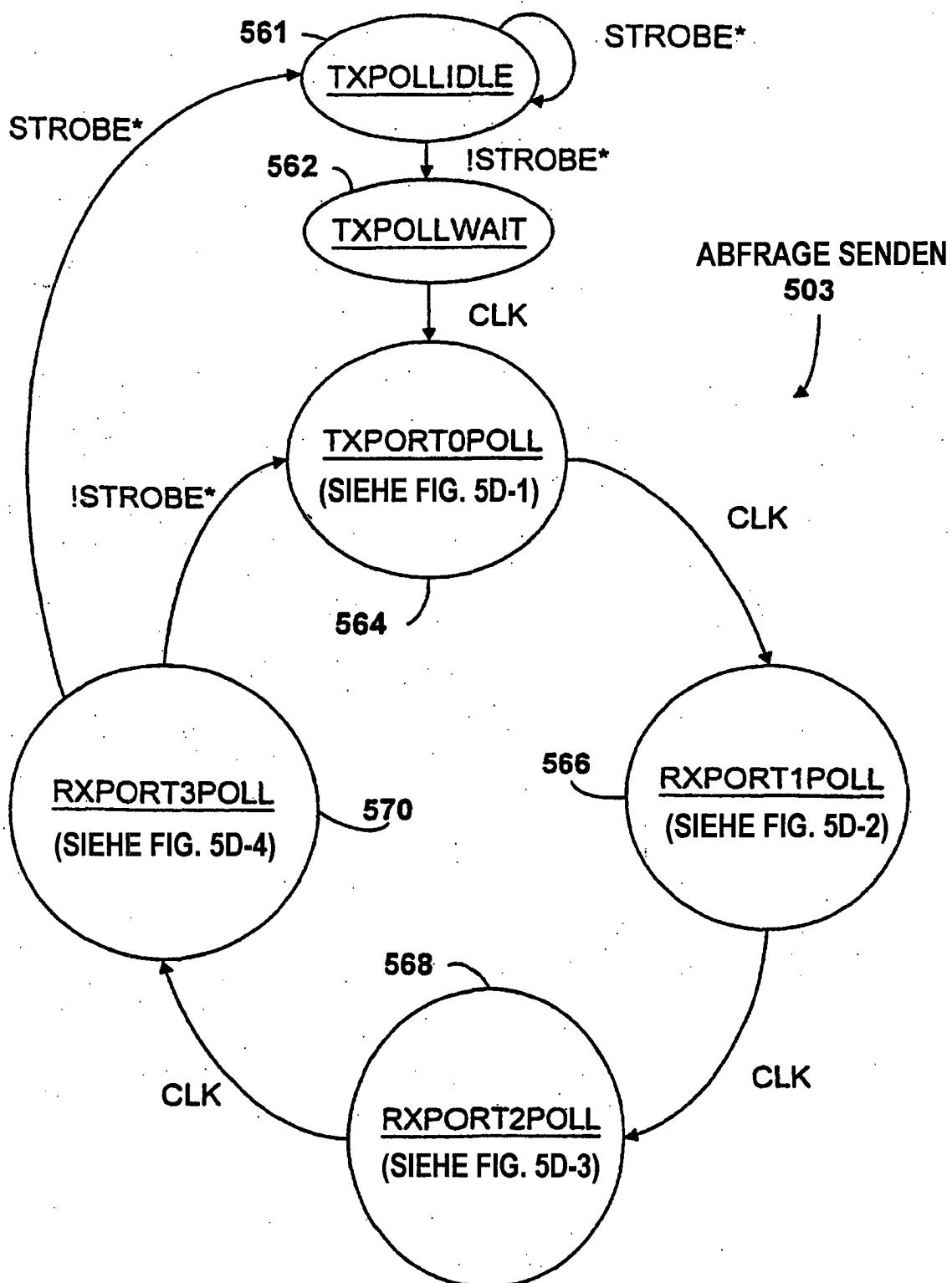

**[0096]** [Fig. 5A](#) zeigt ein ausführlicheres Blockschaltbild des HCB **402**. Der HCB-Bus **438** ist eine interne Version des HSB **206** zum Verbinden des PCB **406**, wo beide Busse **206**, **438** kollektiv als der HSB **206** bezeichnet werden. Eine Abfragelogik **501** ist mit dem HSB **206**, mit einem Satz von lokalen Registern **506** und mit HCB-Konfigurationsregistern **446** verbunden. Die Abfragelogik **501** empfängt das CLK-Signal und macht periodisch das STROBE\* Signal an den QC-Vorrichtungen **202** und der TPI **220** zum Abfragen der Ports **104**, **110** und des PCB **406** geltend. Die Abfragelogik **501** überwacht dann die gemultiplexten PKT\_AVAIL\_m\* und BUF\_AVAILm\* Signale von den QC-Vorrichtungen und der TPI **220**, wobei die jede QC-Vorrichtung **202** und die TPI **220** den Status ihrer vier Ports **104** bzw. **110** liefert, wie vorher beschrieben. Die TPI **220** antwortet mit den Signalen PKT\_AVAIL[6]\* und BUF\_AVAIL[6]\*, und der PCB **406** antwortet mit den Signalen PKT\_AVAIL[7]\* und BUF\_AVAIL[7]\*.

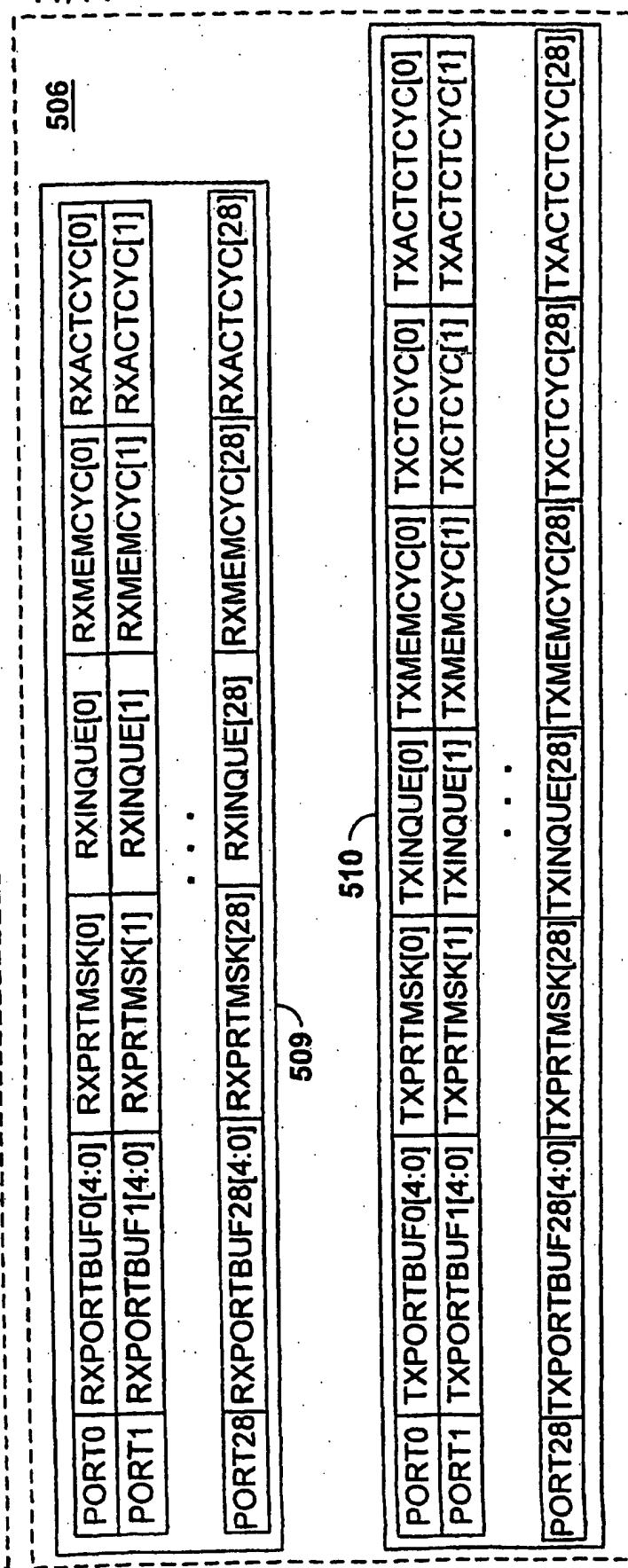

**[0097]** Die Abfragelogik **501** enthält eine Empfangs-(RX)Abfragezustandsmaschine **502**, die die PKT\_AVAILm\* Signale durchsieht und eine Empfangsliste **509** in den Registern **506** aktualisiert. In einer ähnlichen Weise enthält die Abfragelogik **501** eine Sende-(TX)Abfragezustandsmaschine **503**, die die BUF\_AVAILm\* Signale durchsieht und eine Sendeliste **510** in den Registern **506** aktualisiert. Wenn ein WT-PRIORITY-Flag in den HCB-Konfigurationsregistern **446** durch die CPU **230** gesetzt wird, verwenden die RX-Abfragezustandsmaschine **502** und die TX-Abfragezustandsmaschine **503** einen Satz von Gewichtsfaktoren **508** in den HCB-Konfigurationsregistern **446** zum Programmieren der Empfangsliste **509** bzw. der Sendeliste **510**, wie weiter unten beschrieben. Die HCB-Konfigurationsregister **446** enthalten auch einen Satz von CT\_SnF-Registern **507**, die von der CPU **230** programmiert werden, um die gewünschte Betriebsart zwischen CT und SnF zu bestimmen, wenn der entsprechende Port entweder ein Quellen- oder ein Zielport ist.

**[0098]** Die Register **506** werden in jeder gewünschten Weise abhängig von der Implementierung des EPSM

**210** implementiert, z. B. als Latches, Flipflops, statische RAMs (SRAM), DRAMs usw., und umfassen eine Vielzahl von Status- und Steuerregistern oder Puffern. Die Empfangsliste **509** enthält eine Vielzahl von Registerwerten, die den relativen Empfangsstatus und die Priorität jedes Ports anzeigen. Desgleichen enthält die Sendeliste **510** ein Vielzahl von Registerwerten, die den relativen Sendestatus und die Priorität jedes Ports anzeigen. Ein PRCOUNT-Register **511a** speichert eine PRCOUNT-Nummer, die von der RX-Abfragezustandsmaschine **502** verwendet wird, um jedem Port eine relative Empfangspriorität zuweisen, wenn Paketdaten durch diesen Port von einer externen Netzwerk-Vorrichtung empfangen werden. Alternativ verwendet die RX-Abfragezustandsmaschine **502** einen entsprechenden Gewichtsfaktor von den Gewichtsfaktoren **508**. Desgleichen speichert ein TP-COUNT-Register **511b** eine TPCOUNT-Nummern die von der TX-Abfragezustandsmaschine **503** verwendet wird, um jedem Port eine relative Sendepriority zuzuweisen, wenn Paketdaten zum Senden durch diesen Port an eine externe Netzwerk-Vorrichtung vorhanden sind und der Fort Raum hat, um Daten zum Senden zu empfangen. Alternativ verwendet die TX-Abfragezustandsmaschine **502** einen entsprechenden Gewichtsfaktor von den Gewichtsfaktoren **508**. Relative Arbitrations-Zählwerte RXNEWCNT, RXACTCNT, TXNEWCNT und TXCTCNT werden in Registern RXNEWCNT **511c**, RXACTCNT **511d**, TXNEWCNT **511e** und TXCTCNT **511f** gespeichert.

**[0099]** Der HCB **402** enthält Arbitrationslogik **504**, die die Daten in den Registern **506** und **446** durchsieht, um die Typen der auf dem HSB **206** ausgeführten Zyklen zu bestimmen. Eine HSB-Steuerung **505** steuert jeden auf dem HSB **206** ausgeführten Zyklus zum Steuern des Datenflusses zwischen dem EPSM **210** und dem HSB **206**. Die HSB-Steuerung **505** ist mit den Registern **506** zum Modifizieren von Statusbits verbunden. Die HSB-Steuerung **505** empfängt eine Angabe des Typs jedes Zyklusses von der Arbitrationslogik **504**. Die Arbitrationslogik **504** enthält eine Haupt-Arbiter **512**, der mit vier Arbitern verbunden ist, die einen Neupaketempfangs-(RX NW)Arbiter **513**, einen Empfangaktiv-(RX ACT)Arbiter **514**, einen Neupaketsende-(TX NW)Arbiter **515** und einen Sende-Durchschall-(TX CT)Arbiter **516** umfassen. Der Hauptarbiter **512** wählt gewöhnlich zwischen dem RX NW-Arbiter **513**, dem RX ACT-Arbiter **514**, dem TX NW-Arbiter **515** und dem TX CT-Arbiter **516** aus, wo jeder Arbiter schlichtet, um den nächsten Zyklus zu definieren. Der Hauptarbiter **512** verwendet nach Wunsch jedes annehmbare Prioritätsschema. In der gezeigten Ausführung verwendet der Hauptarbiter **512** z. B. ein Umlauf-Prioritätsschema.

**[0100]** Die FIFOs **412** werden in jeder gewünschten Weise implementiert. In der gezeigten Ausführung implementieren zwei Empfangspuffer RX BUFS **529**, **522** einen RXFIFO, wo Daten aus einem Puffer gelesen werden, während sie in den anderen geschrieben werden, und umgekehrt. Auch werden zwei Sendepuffer TX-BUFS **524**, **526** bereitgestellt und arbeiten in einer ähnlichen Weise wie die RXBUFs **510**, **522**. Die FIFOs **412** enthalten auch wenigstens einen Durchschalt-Puffer CTBUF **528**. Die RXBUFs **520** und **522** sind beide 64-Byte Puffer, die je eine bidirektionale Datenschnittstelle mit dem HSB **206** zum Datenfluss in jeder Richtung und eine unidirektionale Schnittstelle zum Liefern von Daten an den MCB **404** durch eine RXMCB-Schnittstelle **530** enthalten. Die TXBUFs **524**, **526** sind beide 64-Byte Puffer, die zwischen den HSB **206** und einer TXMCB-Schnittstelle **531** geschaltet sind. Die TXBUFs **524**, **526** empfangen Daten von dem MCG **404** durch die TXMCB-Schnittstelle **531** und liefern Daten an den HSB **206**. Der CTBUF **528** ist ein 64-Byte Puffer mit einer bidirektionalen Schnittstelle mit dem HSB **206**. Ein FIFO-Steuerblock **529** ist mit den Registern **506**, der HSB-Steuerung **505**, den RXBUFs **520** **522**, den TXBUFs **524**, **526**, dem CTBUF **528**, der RXMCB-Schnittstelle **530** und der TXMCB-Schnittstelle **531** zum Steuern des Datenflusses durch die FIFOs **520**, **522**, **524**, **526** verbunden, um bestimmte durch die RX, TXMCB-Schnittstellen **530** und **531** geltend gemachte Statussignale zu erfassen und bestimmte Bits in den Registern **506** zu setzen, wie unten weiter beschrieben.

**[0101]** Der Bus **420** enthält eine Vielzahl von Daten- und Steuersignalen zum Verbinden des HSB **402** mit dem MCB **404** durch die RX, TXMCB-Schnittstellen **530**, **531**, Hash-Anforderungslogik und MCB-Schnittstelle (bezeichnet als HASH REQ LOGIC) **532** und Sende-Arbiter-Anforderungslogik und MCB-Schnittstelle (bezeichnet als TX ARB REQ LOGIC) **533**. Die HSB-Steuerung **505** kopiert den Vorspann jedes neuen Pakets von einem der Ports Port0–Port28 in einen der RXBUFs **520**, **522** und auch in die HASH REG LOGIC **532**. Der Vorspann beträgt wenigstens drei DWORDs (je 32 Bit), die sowohl die Quellen- als auch Ziel-MAC-Adressen enthalten. Die HASH REQ LOGIC **532** verlangt, dass die Hashing-Prozedur durch den MCB **404** ausgeführt wird, und setzt geeignete Bits in den Registern **506**. Die Hashing-Prozedur wird durchgeführt, um die geeignete Aktion zu bestimmen, die für das Paket zu ergreifen ist.

**[0102]** In der gezeigten Ausführung macht nach Empfangen des Vorspanns eines neuen Pakets die HASH REG LOGIC **532** ein Signal HASH\_REQ\* am MCB **404** geltend und multiplext die 48-Bit MAC-Ziel- und Quellenadressen und eine 8-Bit Quellenportnummer auf HASH\_DA\_SA[15:9] Signale. Der MCB **404** erfasst das HASH\_REQ\* Signal, führt die Hashing-Prozedur durch und macht ein Signal HASH\_DONE an der HASH REQ LOGIC **532** geltend. Der MCB **404** macht auch Signale HASH\_DSTPRT[4:0], HASH\_STATUS[1:9] und ein Si-

gnal HASH\_BP\*, wenn angebracht, geltend. Die HASH\_STATUS[1:0] Signale bezeichnen eines von vier Ergebnissen, die 00b (b bezeichnet eine Binärzahl) = DROP\_PKT, um das Paket fallen zu lassen, 01b = GROUP\_BC für ein Rundsende-(BC)Paket, 10b = MISS\_BC für einen unbekannten Zielport und daher ein BC-Paket, und 11b = FORWARD\_PKT, das ein Unicast-Paket an einen einzelnen Zielport bezeichnet, umfasst. Wenn HASH\_STATUS[1:0] = FORWARD\_PKTn werden die HASH\_DSTPRT[4:0] Signale geltend gemacht, wobei eine binäre Portnummer den Zielport für das Paket bezeichnet. Das HASH\_BP\* Signal wird geltend gemacht, um Rückstau anzudeuten, wenn Rückstau freigegeben und anwendbar ist, infolge einer Schwellenüberlaufbedingung im Speicher **212**, wie durch den MCB **404** festgestellt.

**[0103]** Bestimmte Schwellenwerte werden für den ganzen Speicher **212**, für einzelne Typen von Paketen (z. B. BC-Pakete) und auf einer Port-für-Port-Basis festgelegt. Wenn ein Schwellenwert erreicht wird, sodass ein anderes an den Speicher **212** geliefertes Paket eine Schwellenbegrenzung verletzen würde, entscheidet der Netzwerkschalter **102**, ob das Paket fallen zu lassen ist. Die sendende Vorrichtung erkennt schließlich, dass das Paket fallen gelassen wird, und sendet das Paket neu. Wenn bestimmte Schwellenbedingungen verletzt werden, wird Rückstau freigegeben, und wenn der Quellenport im Halbduplexmodus arbeitet, wird das HASH\_BP\* Signal geltend gemacht.

**[0104]** Die HASH\_REQ\_LOGIC **532** erfasst das HASH\_BP\* SIGNAL und stellt fest, ob HASH\_STATUS[1:0] = DROP\_PKT, z. B. die Quellen- und Zielports sind die gleichen. Wenn HASH\_STATUS[1:0] = DROP\_PKT, ist keine weitere Aktion nötig, da das Paket fallen zu lassen ist. Wenn HASH\_STATUS[1:0] nicht gleich DROP\_PKT ist, stellt die HASH REQ LOGIC **532** fest, ob HASH\_STATUS[1:0] = FORWARD\_PKT und das Paket im CT-Modus durch den CT BUF **528** zu übertragen ist, um dadurch möglicherweise den Speicher **212** zu umgehen. Wenn der Zielport beschäftigt ist, oder wenn HASH\_STATUS[1:0] nicht angibt, das Paket fallen zu lassen oder das Paket weiterzuleiten, weist die HASH REQ LOGIC **532** die HSB-Steuerung an, einen Rückstau-Zyklus auf dem Port, der Daten empfängt, auszuführen.