(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-148995

(P2019-148995A)

(43) 公開日 令和1年9月5日(2019.9.5)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |       |  |

|------------------------------|------------|-------------|-------|--|

| <b>G06F 17/50</b> (2006.01)  | G06F 17/50 | 658K        | 5B046 |  |

| <b>H01L 21/822</b> (2006.01) | G06F 17/50 | 658T        | 5F038 |  |

| <b>H01L 27/04</b> (2006.01)  | H01L 27/04 | D           | 5F064 |  |

| <b>H01L 21/82</b> (2006.01)  | H01L 21/82 | C           |       |  |

審査請求 未請求 請求項の数 14 O L (全 10 頁)

|           |                            |          |                                                 |

|-----------|----------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2018-33347 (P2018-33347) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号           |

| (22) 出願日  | 平成30年2月27日 (2018.2.27)     | (71) 出願人 | 317011920<br>東芝デバイス&ストレージ株式会社<br>東京都港区芝浦一丁目1番1号 |

|           |                            | (74) 代理人 | 100108855<br>弁理士 蔵田 昌俊                          |

|           |                            | (74) 代理人 | 100103034<br>弁理士 野河 信久                          |

|           |                            | (74) 代理人 | 100075672<br>弁理士 峰 隆司                           |

|           |                            | (74) 代理人 | 100153051<br>弁理士 河野 直樹                          |

最終頁に続く

(54) 【発明の名称】半導体集積回路の設計装置及び設計方法

(57) 【要約】 (修正有)

【課題】クロックバッファを効果的にゲーティングできるように、クロックゲーティング回路を適切に設定できる半導体集積回路の設計装置を提供する。

【解決手段】クロック信号により動作する論理回路に対して、当該クロック信号の供給を制御するクロックゲーティング回路を設定する機能を有し、コンピュータシステムにより構成される半導体集積回路の設計装置であって、検出機能と、算出機能と、分割機能と、設定機能とを実現するプロセッサを備えた構成である。検出機能は、クロックゲーティング回路に対して、イネーブル信号を出力するイネーブルの論理組み合わせを検出する。算出機能は、論理組み合わせの各論理要素の遅延時間を算出する。分割機能は、遅延時間に基づいて、論理組み合わせを各論理要素に分割する。設定機能は、分割された各論理要素のそれぞれに合わせて、クロックゲーティング回路を設定する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

クロック信号により動作する論理回路に対して、当該クロック信号の供給を制御するクロックゲーティング回路を設定する機能を有し、コンピュータシステムにより構成される半導体集積回路の設計装置であって、

クロックゲーティング回路に対して、イネーブル信号を出力するイネーブルの論理組み合わせを検出する検出手段と、

前記論理組み合わせの各論理要素の遅延時間を算出する算出手段と、

前記遅延時間に基づいて、前記論理組み合わせを前記各論理要素に分割する分割手段と、

分割された前記各論理要素のそれぞれに合わせて、クロックゲーティング回路を設定する設定手段と、

を具備する半導体集積回路の設計装置。

**【請求項 2】**

前記検出手段は、

前記論理組み合わせから出力される前記イネーブル信号を抽出し、

前記論理組み合わせの各論理要素として、それぞれの出力が前記イネーブル信号を出力するアンドゲートの各入力となる構成の前記論理組み合わせを検出する、請求項 1 に記載の半導体集積回路の設計装置。

**【請求項 3】**

前記検出手段は、

前記論理組み合わせから出力される前記イネーブル信号を抽出し、

前記論理組み合わせの各論理要素として、それぞれの入力が同一であり、それぞれの出力が前記イネーブル信号を出力するアンドゲートの各入力となる構成の前記論理組み合わせを検出する、請求項 1 に記載の半導体集積回路の設計装置。

**【請求項 4】**

前記分割手段は、

前記遅延時間に基づいて、前記論理組み合わせから、相対的に遅延の大きさに従って前記各論理要素に分割する、請求項 1 から 3 のいずれか 1 項に記載の半導体集積回路の設計装置。

**【請求項 5】**

前記論理回路において、前記クロック信号を生成する手段が階層的に最上位側である場合に、

前記設定手段は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の小さい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記論理回路の上位側に設定する請求項 1 から 4 のいずれか 1 項に記載の半導体集積回路の設計装置。

**【請求項 6】**

前記論理回路はクロック信号の入出力を行うクロックバッファを含み、

前記設定手段は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の小さい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記クロックバッファの上流側に設定する、請求項 1 から 4 のいずれか 1 項に記載の半導体集積回路の設計装置。

**【請求項 7】**

前記設定手段は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の大きい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記クロックバッファの下流側に設定する、請求項 6 に記載の半導体集積回路の設計装置。

**【請求項 8】**

10

20

30

40

50

クロック信号により動作する論理回路に対して、当該クロック信号の供給を制御するクロックゲーティング回路を設定する機能を有し、コンピュータシステムにより実現される半導体集積回路の設計方法であって、

クロックゲーティング回路に対して、イネーブル信号を出力するイネーブルの論理組み合わせを検出する処理と、

前記論理組み合わせの各論理要素の遅延時間を算出する処理と、

前記遅延時間に基づいて、前記論理組み合わせを前記各論理要素に分割する処理と、

分割された前記各論理要素のそれぞれに合わせて、クロックゲーティング回路を設定する処理と、

を実行する半導体集積回路の設計方法。

10

#### 【請求項 9】

前記検出する処理は、

前記論理組み合わせから出力される前記イネーブル信号を抽出し、

前記論理組み合わせの各論理要素として、それぞれの出力が前記イネーブル信号を出力するアンドゲートの各入力となる構成の前記論理組み合わせを検出する、請求項 8 に記載の半導体集積回路の設計方法。

#### 【請求項 10】

前記検出する処理は、

前記論理組み合わせから出力される前記イネーブル信号を抽出し、

前記論理組み合わせの各論理要素として、それぞれの入力が同一であり、それぞれの出力が前記イネーブル信号を出力するアンドゲートの各入力となる構成の前記論理組み合わせを検出する、請求項 8 に記載の半導体集積回路の設計方法。

20

#### 【請求項 11】

前記分割する処理は、

前記遅延時間に基づいて、前記論理組み合わせから、相対的に遅延の大きさに従って前記各論理要素に分割する、請求項 8 から 10 のいずれか 1 項に記載の半導体集積回路の設計方法。

#### 【請求項 12】

前記論理回路において、前記クロック信号を生成する手段が階層的に最上位側である場合に、

30

前記設定する処理は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の小さい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記論理回路の上位側に設定する請求項 8 から 11 のいずれか 1 項に記載の半導体集積回路の設計方法。

#### 【請求項 13】

前記論理回路はクロック信号の入出力をを行うクロックバッファを含み、

前記設定する処理は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の小さい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記クロックバッファの上流側に設定する、請求項 8 から 11 のいずれか 1 項に記載の半導体集積回路の設計方法。

40

#### 【請求項 14】

前記設定する処理は、

分割された前記各論理要素の中で、前記遅延時間に基づいて相対的に遅延の大きい論理要素からのイネーブル信号を入力とするクロックゲーティング回路を、前記クロックバッファの下流側に設定する、請求項 13 に記載の半導体集積回路の設計方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明の実施形態は、半導体集積回路の設計装置及び設計方法に関する。

50

## 【背景技術】

## 【0002】

一般的に、LSI (large scale integrated circuit) 等の半導体集積回路の設計では、消費電力削減のために、クロックゲーティング (clock gating) 回路を設定 (挿入) する手法が採用されている。クロックゲーティング回路は、イネーブル信号に応じて、例えば、論理回路の構成要素であるフリップフロップ (flip-flop) に対して、非動作時にはクロック信号の供給を停止するように制御する。

## 【0003】

通常では、半導体集積回路の設計では、EDA (electronic design automation) ツールや論理合成ツール等を使用する設計装置が使用されて、イネーブルの論理によるイネーブルのタイミングを考慮して、クロックゲーティング回路の設定が行われる。このため、クロックゲーティング回路はクロックバッファの下流側に設定される可能性がある。

10

## 【先行技術文献】

## 【特許文献】

## 【0004】

## 【特許文献1】特許第5368941号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

半導体集積回路の設計において、有効な消費電力削減を実現するためには、クロックバッファをイネーブルの論理により効果的にゲーティングできるように、クロックゲーティング回路をクロックバッファの上流側に設定 (挿入) することが望ましい。

20

## 【0006】

そこで、目的は、半導体集積回路の設計において、クロックバッファを効果的にゲーティングできるように、クロックゲーティング回路を適切に設定できる半導体集積回路の設計装置を提供することにある。

## 【課題を解決するための手段】

## 【0007】

本実施形態の半導体集積回路の設計装置、クロック信号により動作する論理回路に対して、当該クロック信号の供給を制御するクロックゲーティング回路を設定する機能を有し、コンピュータシステムにより構成される半導体集積回路の設計装置であって、検出手段と、算出手段と、分割手段と、設定手段とを備えた構成である。前記検出手段は、前記クロックゲーティング回路に対して、イネーブル信号を出力するイネーブルの論理組み合わせを検出する。前記算出手段は、前記論理組み合わせの各論理要素の遅延時間を算出する。前記分割手段は、前記遅延時間に基づいて、前記論理組み合わせを前記各論理要素に分割する。前記設定手段は、分割された前記各論理要素のそれぞれに合わせて、前記クロックゲーティング回路を設定する。

30

## 【図面の簡単な説明】

## 【0008】

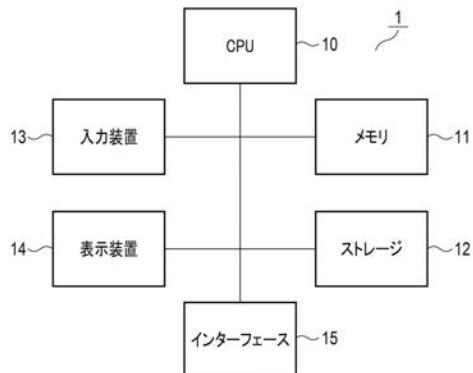

【図1】実施形態に関する半導体集積回路の設計装置の構成を説明するためのブロック図。

40

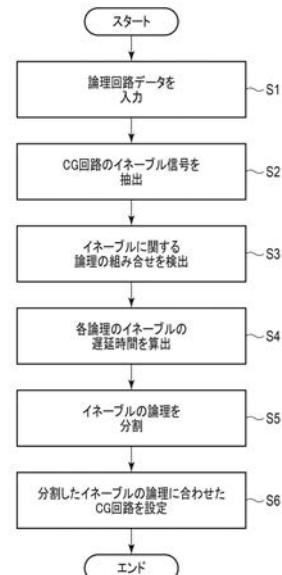

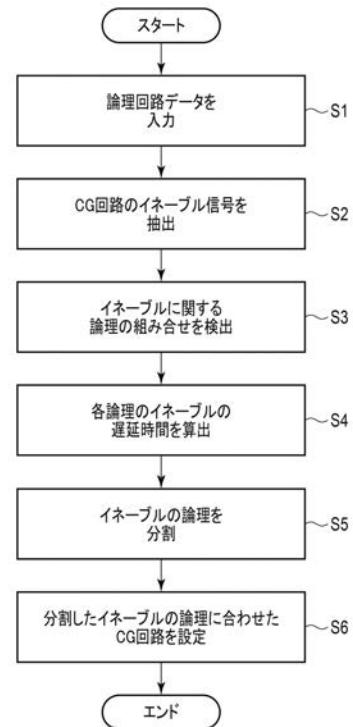

【図2】実施形態に関する設計装置の処理を説明するためのフローチャート。

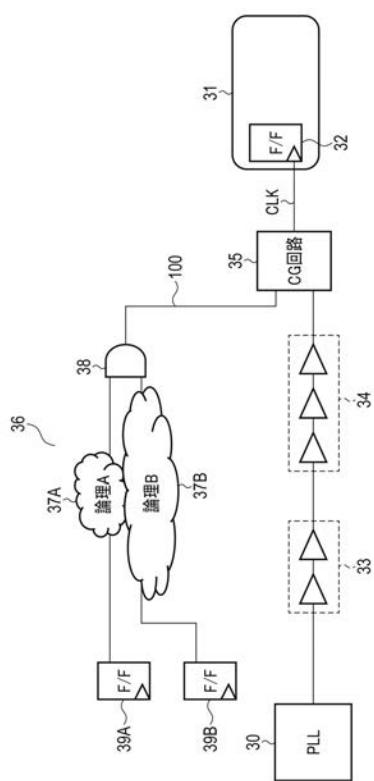

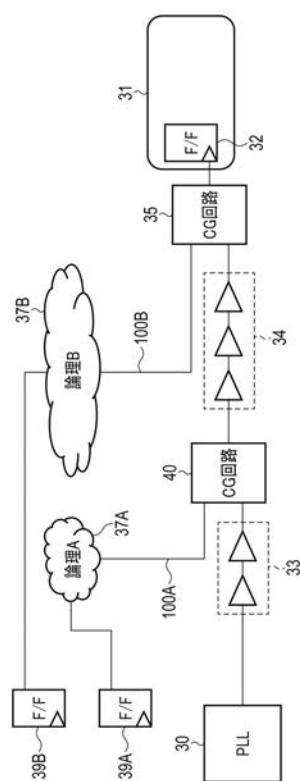

【図3】実施形態に関する論理回路データの一例を示す図。

【図4】実施形態に関する設計方法による設計結果の一例を示す図。

【図5】実施形態の変形例に関する論理回路データの一例を示す図。

【図6】実施形態の変形例に関する設計方法による設計結果の一例を示す図。

## 【発明を実施するための形態】

## 【0009】

以下図面を参照して、実施形態を説明する。

## [設計装置の構成]

50

図1は、本実施形態に関する半導体集積回路の設計装置の構成を説明するためのブロック図である。図1に示すように、本設計装置1は、コンピュータシステムにより構成されており、プロセッサ(CPU)10と、メモリ11と、ストレージ12と、入力装置13と、表示装置14と、インターフェース15と、を有する構成である。

#### 【0010】

CPU10は、メモリ11から読み出したプログラムにより、後述するように、半導体集積回路の設計において、本実施形態に関するクロックゲーティング(clock gating)回路の設定処理を実行する。メモリ11は、CPU10が実行するプログラムや各種データを保持する、RAM(random access memory)やフラッシュメモリ等を含む。

#### 【0011】

ストレージ12は外部記憶装置であり、半導体集積回路の自動設計用ソフトウェアを保存している。自動設計用ソフトウェアには、例えばEDA(electronic design automation)ツールや、論理合成ツール等が含まれる。本実施形態では、CPU10が実行するプログラムは、例えば論理合成ツールに含まれており、ストレージ12からメモリ11にコードされる。

#### 【0012】

入力装置13は、オペレータの操作により、データやコマンドを入力する。表示装置14は、CPU10の制御により、論理回路データや設計結果をディスプレイに表示する。インターフェース15は、LAN(local area network)等の通信系を介して、ソフトウェアやデータを入出力する。

#### [設計装置の動作]

図2は、本設計装置1の処理を説明するためのフローチャートである。本実施形態は、LSI等の半導体集積回路の自動設計において、消費電力削減のためのクロックゲーティング回路(CG回路)の設定(挿入)処理に関する。

#### 【0013】

図2に示すように、CPU10は、CG回路を挿入する、設計対象の論理回路データを入力すると(S1)、CG回路の設定処理を実行する。図3は、設計対象の論理回路データの一例を示す図である。

#### 【0014】

図3に示すように、当該論理回路データは、例えば、階層的に最上位(先端)のクロック生成回路30と、最下位(末端)の論理回路ブロック31を有する論理回路を示すデータである。クロック生成回路30は、PLL(phase-locked loop)を含み、クロック信号(CLK)を生成する。論理回路ブロック31は、当該クロック信号(CLK)により動作するフリップフロップ(flip-flop:F/F)32を含む。

#### 【0015】

クロック生成回路30により生成されるクロック信号(CLK)は、複数のクロックバッファ33,34により、論理回路ブロック31に伝送される。クロックバッファ33,34は、クロック信号の分配や、クロックスキュー(clock skew)調整等の機能を有する。ここで、論理回路ブロック31に含まれるF/F32は、CG回路35により、クロックバッファ34から出力されるクロック信号(CLK)の供給を制御される。

#### 【0016】

CG回路35は、イネーブルの論理組み合わせ36により生成されるイネーブル信号100によるイネーブルのタイミングに応じてゲーティングし、F/F32に対するクロック信号(CLK)の供給を制御する。通常では、CG回路35は、アンド(AND)ゲート及びラッチ回路を含み、統合クロックゲーティング回路(Integrated Clock gating:ICG)とも呼ばれる。

#### 【0017】

イネーブルの論理組み合わせ36は、例えば、複数(ここでは2個)のイネーブル論理(A,B)を構成するイネーブル論理回路37A,37B、及びアンド(AND)ゲート38を含む。各イネーブル論理回路37A,37Bは、異なるフリップフロップ(F/F)

10

20

30

40

50

) 39A, 39Bからの出力を各入力とし、各出力が同一のアンドゲート38の入力となる構成である。

**【0018】**

図2に戻って、CPU10は、図3に示すような論理回路データを入力すると(S1)、CG回路35のイネーブル信号100を抽出する(S2)。さらに、CPU10は、抽出したイネーブル信号100に基づいて、CG回路35のイネーブルの論理の組み合わせ36に含まれる各イネーブル論理回路37A, 37Bを検出する(S3)。

**【0019】**

次に、CPU10は、検出した各イネーブル論理回路37A, 37Bの遅延時間を算出する(S4)。CPU10は、算出した遅延時間に基づいて、例えば相対的に遅延が小さいイネーブル論理回路37Aと、相対的に遅延が大きいイネーブル論理回路37Bとを識別する。

**【0020】**

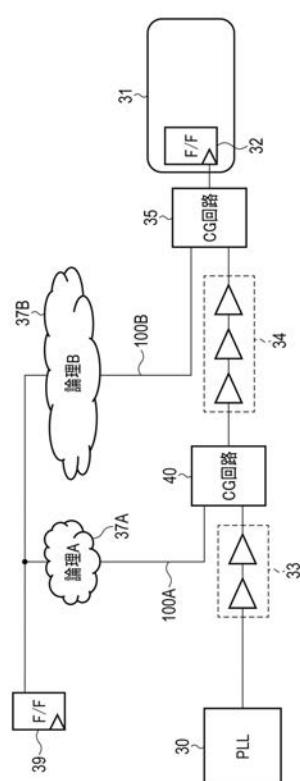

ここで、図4は、図3の論理回路データに対して、CG回路の設定処理を実行した後の設計結果の一例を示す図である。図4に示すように、CPU10は、イネーブルの論理の組み合わせ36から、遅延が小さいイネーブル論理回路37Aと、遅延が大きいイネーブル論理回路37Bとを分割する(S5)。

**【0021】**

CPU10は、分割したイネーブル論理回路37A, 37Bに合わせて、CG回路の設定処理を実行する(S6)。具体的には、図4に示すように、CPU10は、末端の論理回路ブロック31の近傍に挿入されるCG回路35と、クロックバッファ34の上流側(入力側)に挿入されるCG回路40を設定する。ここでは、CG回路40は、階層的に上位側に設定される。また、CG回路35は、クロックバッファ34の下流側(出力側)で、階層的に下位側に設定される。

**【0022】**

末端のCG回路35は、遅延が大きいイネーブル論理回路37Bからのイネーブル信号100Bによるイネーブルのタイミングに応じて、クロックバッファ34からのクロック信号(CLK)の供給を制御する。即ち、CG回路35は、イネーブル論理が「1」であればクロック信号(CLK)をF/F32に供給し、イネーブル論理が「0」であればクロック信号(CLK)の供給を停止する。

**【0023】**

従って、末端の論理回路ブロック31の非動作時には、クロック信号(CLK)の供給が停止されるため、F/F32を含む論理回路ブロック31における消費電力を削減できることになる。

**【0024】**

一方、クロックバッファ34の上流側に挿入されるCG回路40は、遅延が小さいイネーブル論理回路37Aからのイネーブル信号100Aによるイネーブルのタイミングに応じて、クロックバッファ33からのクロック信号(CLK)の供給を制御する。即ち、CG回路40は、イネーブル論理が「1」であればクロック信号(CLK)をクロックバッファ34に供給し、イネーブル論理が「0」であればクロック信号(CLK)の供給を停止する。

**【0025】**

従って、イネーブル論理回路37Aのイネーブル論理が「0」の場合に、末端のCG回路35によるクロック信号(CLK)の供給が停止する前に、クロックバッファ34に対するゲーティングにより、クロック信号(CLK)の供給が停止される。これにより、クロックバッファ34の消費電力を削減できることになる。

**【0026】**

以上のように本実施形態によれば、設計対象の論理回路において、イネーブルの論理組み合わせを、遅延が小さいイネーブルの論理と、遅延が大きいイネーブルの論理とに分割し、それぞれのイネーブル信号を入力とする各CG回路を設定(挿入)することができる

。

## 【0027】

即ち、図4に示すように、設計対象の論理回路において階層的に末端の論理回路ブロック31の近傍に設定するCG回路35と共に、クロックバッファ34の上流側にCG回路40を設定することができる。CG回路40は、遅延が小さいイネーブルの論理（論理回路37A）のイネーブルのタイミング（イネーブル信号100A）に応じて、クロックバッファ34をゲーティングする。これにより、クロックバッファ34は、イネーブル信号100Aの論理が「0」の場合に、クロック信号(CLK)の供給が停止される。従って、末端のF/F32の消費電力の削減に加えて、クロックバッファ34の消費電力を削減できるため、消費電力の効果的な削減を実現することができる。10

## 【0028】

換言すれば、本実施形態によれば、設計対象の論理回路において、前述したように、分割したイネーブルの論理のそれぞれに対応する各CG回路を設定（挿入）することにより、ゲーティングされるクロックバッファを増大することが可能となる。このため、結果的に、クロック信号(CLK)の供給を停止できるクロックバッファを増大できるため、効果的な消費電力の削減を実現することができる。20

## [変形例]

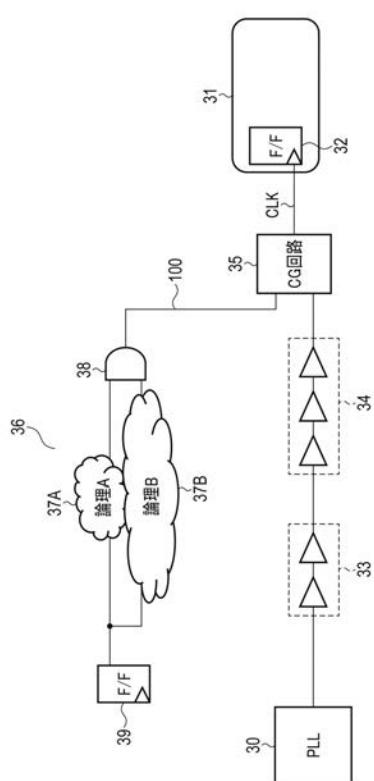

図5及び図6は、本実施形態の変形例を説明するための図である。図5は、本変形例の設計対象の論理回路データの一例を示す図である。図6は、本変形例の設計結果の一例を示す図である。20

## 【0029】

なお、本変形例においても、半導体集積回路の設計装置の構成は、図1に示す本実施形態の場合と同様であるため、図示を含む説明を省略する。また、設計装置の動作及び効果も、図2に示す本実施形態の場合と同様であるため、図示を含む説明を省略する。

## 【0030】

図5に示すように、本変形例の設計対象の論理回路では、前述したように、CG回路35は、イネーブルの論理組み合わせ36により生成されるイネーブル信号100によるイネーブルのタイミングに応じてゲーティングされる。これにより、CG回路35は、F/F32に対するクロック信号(CLK)の供給を制御する。30

## 【0031】

イネーブルの論理組み合わせ36は、複数のイネーブル論理(A, B)を構成するイネーブル論理回路37A, 37B、及びアンド(AND)ゲート38を含む。ここで、各イネーブル論理回路37A, 37Bは、同一のフリップフロップ(F/F)39からの出力を各入力とし、各出力が同一のアンドゲート38の入力となる構成である。なお、他の構成については、図3に示す本実施形態の場合と同様であるため、含む説明を省略する。

## 【0032】

次に、図6に示すように、本変形例の設計結果は、前述したように、イネーブルの論理の組み合わせ36から、遅延が小さいイネーブルの論理A（論理回路37A）と、遅延が大きいイネーブルの論理B（論理回路37B）とが分割される。さらに、末端の論理回路ブロック31の近傍にはCG回路35が設定されて、クロックバッファ34の上流側にはCG回路40が設定されている。40

## 【0033】

ここで、各イネーブル論理回路37A, 37Bは、同一のフリップフロップ(F/F)39からの出力を各入力とし、各出力が同一のアンドゲート38の入力となる構成である。なお、他の構成については、図4に示す本実施形態の場合と同様であるため、含む説明を省略する。

## 【0034】

なお、本実施形態及び変形例は、設計対象の論理回路は、階層的に最下位（末端）の論理回路ブロック31が1個である場合について設定したが、当然ながら、複数の論理回路ブロック31が存在する場合にも適用可能である。50

## 【0035】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【符号の説明】

## 【0036】

- 1 … 設計装置、 10 … プロセッサ（CPU）、 11 … メモリ、 12 … ストレージ、

13 … 入力装置、 14 … 表示装置、 15 … インターフェース、

30 … クロック生成回路、 31 … 論理回路ブロック、

32, 39, 39A, 39B … フリップフロップ（FF）、

33, 34 … クロックバッファ、 35, 40 … クロックゲーティング回路（CG回路）

、

36 … イネーブルの論理組み合わせ。

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(74)代理人 100189913

弁理士 鵜飼 健

(72)発明者 佐藤 宏則

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

(72)発明者 村岡 寛昭

東京都港区芝浦一丁目1番1号 東芝デバイス&ストレージ株式会社内

F ターム(参考) 5B046 AA08 BA04 GA01 JA01

5F038 CD06 CD09 DF08 EZ09 EZ20

5F064 BB03 BB19 EE47 EE54 HH06