(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-219856

(P2008-219856A)

(43) 公開日 平成20年9月18日(2008.9.18)

| (51) Int.Cl.                  | F 1          | テーマコード (参考) |

|-------------------------------|--------------|-------------|

| <b>H03K 17/06 (2006.01)</b>   | H03K 17/06   | C 5 J 0 5 5 |

| <b>H03K 17/687 (2006.01)</b>  | H03K 17/687  | G 5 J 0 5 6 |

| <b>H03K 19/0944 (2006.01)</b> | H03K 19/0944 | A           |

審査請求 未請求 請求項の数 5 O L (全 12 頁)

(21) 出願番号 特願2007-296351 (P2007-296351)

(22) 出願日 平成19年11月15日 (2007.11.15)

(31) 優先権主張番号 特願2007-26745 (P2007-26745)

(32) 優先日 平成19年2月6日 (2007.2.6)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

(74) 代理人 100115691

弁理士 藤田 篤史

最終頁に続く

(54) 【発明の名称】半導体スイッチ

## (57) 【要約】

【課題】低電圧電源を用いた半導体スイッチにおいて中間電位付近の電圧を出力する際に、オン抵抗の増大やリーコンデンサの発生により、動作速度の低下と、出力電圧の精度低下などが課題となる。

【解決手段】階調発生回路100とアナログスイッチ回路111とバックゲート電圧制御回路122とを有し、階調発生回路100の電圧を入力するアナログスイッチ回路111のNチャネルMOSトランジスタ112及びPチャネルMOSトランジスタ113の各々のバックゲート電圧を、階調発生回路100と等しい構成であるバックゲート電圧制御回路122から供給する。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

複数の階調電圧を発生する階調発生回路と、

各々前記複数の階調電圧のうちの1つの階調電圧を選択する複数のアナログスイッチ回路を有する階調セレクタ回路と、

前記階調セレクタ回路の動作を制御するスイッチ制御回路とを備えた半導体スイッチであって、

前記複数のアナログスイッチ回路の各々は、前記複数の階調電圧のうちの選択すべき階調電圧に接続されたソースを持つMOSトランジスタを有し、

前記スイッチ制御回路は、

前記MOSトランジスタのオン・オフを制御するように当該MOSトランジスタのゲート電圧を供給するタイミング制御回路と、

前記MOSトランジスタのソース電圧とほぼ等しい電圧を前記MOSトランジスタのバックゲート電圧として供給するバックゲート電圧制御回路とを有することを特徴とする半導体スイッチ。

## 【請求項 2】

請求項1記載の半導体スイッチにおいて、

前記バックゲート電圧制御回路は、前記MOSトランジスタのソース・バックゲート間のPN接合を順方向にバイアスしない電圧を前記MOSトランジスタのバックゲート電圧として供給することを特徴とする半導体スイッチ。

## 【請求項 3】

請求項1記載の半導体スイッチにおいて、

前記バックゲート電圧制御回路は、前記階調発生回路と同様の内部構成を有することを特徴とする半導体スイッチ。

## 【請求項 4】

請求項3記載の半導体スイッチにおいて、

前記階調発生回路及び前記バックゲート電圧制御回路の各々は、H側電源とL側電源との間に接続された抵抗ストリング回路を有することを特徴とする半導体スイッチ。

## 【請求項 5】

請求項3記載の半導体スイッチにおいて、

前記階調発生回路及び前記バックゲート電圧制御回路の各々は、H側電源とL側電源との間に直列に接続された電流源と抵抗ストリング回路とダイオードとを有することを特徴とする半導体スイッチ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、半導体スイッチに関し、特に、オン抵抗を低く抑え、小型、安価で、スイッチング応答に優れた半導体スイッチに関するものである。

## 【背景技術】

## 【0002】

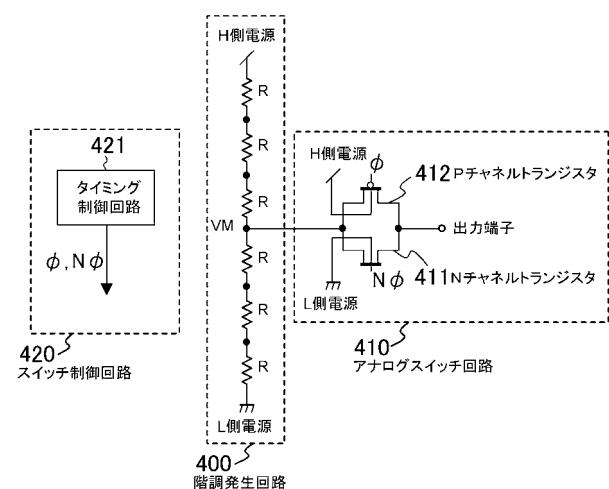

半導体スイッチの従来技術について図6を用いて説明する。図6に示す半導体スイッチは、階調電圧を発生する階調発生回路400、アナログスイッチ回路410、スイッチ制御回路420から構成され、階調発生回路400の任意の階調電圧VMを、アナログスイッチ回路410を介して出力端子に伝達する。

## 【0003】

アナログスイッチ回路410は、一般的に、図6に示すようにPチャネルMOSトランジスタ412とNチャネルMOSトランジスタ411の並列接続で構成されており、PチャネルMOSトランジスタ412とNチャネルMOSトランジスタ411のソース及びドレインがそれぞれ共通接続されている。また、アナログスイッチ回路410をオン／オフさせる電圧はスイッチ制御回路420から供給され、PチャネルMOSトランジスタ41

10

20

30

40

50

2のゲート端子に接続されるHIGHレベルもしくはLOWレベルの信号を とすると、NチャネルMOSトランジスタ411のゲート端子に接続される信号N<sub>1</sub>は、信号のHIGHレベルとLOWレベルを反転させた信号となる。また、NチャネルMOSトランジスタ411のバックゲート端子、すなわち、Pウェルは、最低電位L側電源に接続され、PチャネルMOSトランジスタ412のバックゲート端子、すなわち、Nウェルは、最高電位であるH側電源に接続される。

#### 【0004】

この従来のCMOS構造のアナログスイッチ回路410は、信号N<sub>1</sub>のHIGHレベルの電圧がNチャネルMOSトランジスタ411のゲート端子に与えられると、NチャネルMOSトランジスタ411が導通状態となると同時に、信号N<sub>2</sub>のLOWレベルの電圧がPチャネルMOSトランジスタ412のゲート端子に与えられ、PチャネルMOSトランジスタ412も導通状態となる。したがって、アナログスイッチ回路410は、導通(ON)状態となり、階調電圧VMが出力端子へ伝達される。

10

#### 【0005】

次に信号N<sub>1</sub>のLOWレベルの電圧がNチャネルMOSトランジスタ411のゲート端子に与えられると、NチャネルMOSトランジスタ411が遮断状態となると同時に、信号N<sub>2</sub>のHIGHレベルの電圧がPチャネルMOSトランジスタ412のゲート端子に与えられ、PチャネルMOSトランジスタ412も遮断状態となる。したがって、アナログスイッチ回路410は、遮断(OFF)状態となり、階調電圧VMは出力端子へ伝達されない。

20

#### 【0006】

ここで、PチャネルMOSトランジスタ412に供給される電圧のうち、ソース電圧よりもバックゲート電圧が低いとPチャネルMOSトランジスタ412のソースであるPウェルとバックゲートであるNウェル間に存在するPN接合にリーク電流が発生するため、PチャネルMOSトランジスタ412のバックゲート電圧はソース電圧以上の電圧が望ましく、従来技術ではPチャネルMOSトランジスタ412のバックゲート電圧は最高電位であるH側電源に接続されている。同様にNチャネルMOSトランジスタ411においても供給される電圧のうち、ソース電圧よりもバックゲート電圧が高いとソースであるNウェルとバックゲートであるPウェル間に存在するPN接合にリーク電流が発生するため、NチャネルMOSトランジスタ411のバックゲート電圧はソース電圧以下の電圧が望ましく、従来技術ではNチャネルMOSトランジスタ411のバックゲート電圧は最低電位であるL側電源に接続されている。

30

#### 【0007】

しかしながら、従来技術では、アナログスイッチ回路410における各々のMOSトランジスタ411, 412のソース電極の電位とバックゲート電極の電位との間に電位差が生じる。そのため、基板バイアス効果によってMOSトランジスタ411, 412のしきい値電圧が上昇する。そして、アナログスイッチ回路410の入力電圧VMが中間電位付近のアナログ電圧である場合に特に基板バイアス効果の影響が大きくなり、アナログスイッチ回路410のオン抵抗が高くなる。また、中間電位付近ではアナログスイッチ回路410のゲート端子を駆動するゲート・ソース間電圧自体が小さくなる。

40

#### 【0008】

通常、MOSトランジスタは、ゲート・ソース間の電位差が、しきい値電圧よりも大きくなるとオンするが、このようにゲート・ソース間電圧が小さく、しきい値電圧が大きくなると、オン抵抗が高くなり、信号の伝達が困難となる。これにより、動作速度が低下し、アナログスイッチ回路410の出力端子から出力される電圧精度の誤差が大きくなる。更に、MOSトランジスタ411, 412のゲート・ソース間の電位差が、しきい値電圧を上回らない場合はアナログスイッチ回路410がオンしない状態となる。

#### 【0009】

上記問題を回避するには、MOSトランジスタのサイズ変更、低しきい値電圧化、及びディプレッション型のMOSトランジスタを用いる方法があるが、リーク電流の増大やチ

50

ップコスト上昇の原因となる（特許文献1参照）。

【特許文献1】特開2003-338745号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

基板バイアス効果は、トリプルウェル構造など、深さ方向に複数のウェルが存在するプロセスで構成されるMOSトランジスタにおいて、チップの面積増大を招くもののMOSトランジスタのソース端子とバックゲート端子を接続し、等電位とすることで、対策できるようになる。

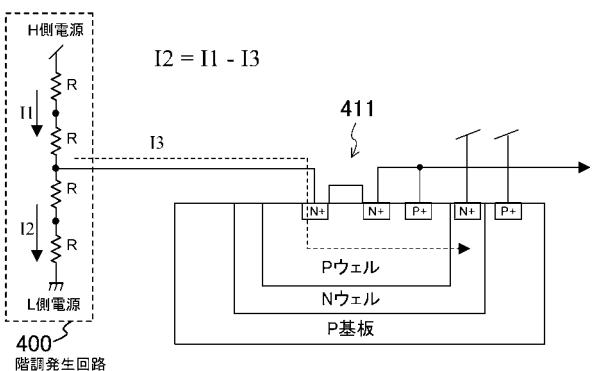

【0011】

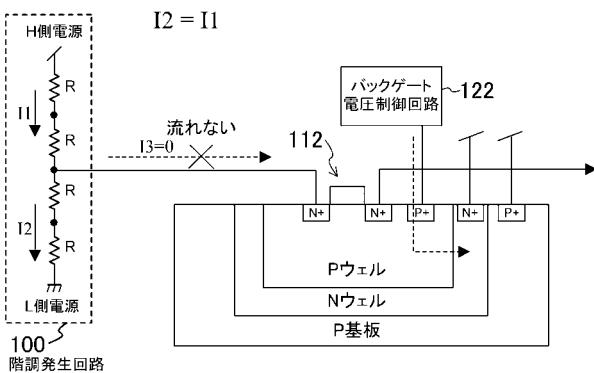

しかしながら、図7に示すようにトリプルウェル構造にてMOSトランジスタのソース端子とバックゲート端子を接続したとしても、NチャネルMOSトランジスタ411のバックゲートとなるPウェルとそのPウェルの外側に位置するNウェルがPN接合の逆バイアスを形成しており、このPN接合に逆バイアスリーク電流I3が発生する。不図示のPチャネルMOSトランジスタ412についても当該PチャネルMOSトランジスタのバックゲートとなるNウェルとそのNウェルの外側に位置するPウェルがPN接合の逆バイアスを形成しており、逆バイアスリーク電流が発生する。これらの逆バイアスリーク電流は、PN接合の接合間電位差が高くなるにつれて増大する。近年の微細プロセスにおいては基板電流やホットキャリアの影響により、リーク電流はより顕著になってきている。

【0012】

逆バイアスリーク電流I3はアナログスイッチ回路410の接続先である階調発生回路400から供給され、本来、階調発生回路400に流れる電流は、H側電源からL側電源へ分岐することなく流れることが望ましいが（I2=I1）、逆バイアスリーク電流I3が階調発生回路400からアナログスイッチ回路410に分流することによりI2=I1-I3となる結果、階調発生回路400における抵抗分圧による階調電圧に誤差が生じ、アナログスイッチ回路410の出力端子から出力される電圧の精度が低下する。

【0013】

したがって、本発明の目的は、半導体スイッチにおいて、MOSトランジスタのしきい値電圧が高いプロセスや低電圧での回路設計が必要な場合においても、オン抵抗が低く、更に微細化プロセスであっても、リーク電流を防止でき、高速動作及び出力電圧の高精度化を実現することにある。

【課題を解決するための手段】

【0014】

上記目的の達成を図るために、本発明の半導体スイッチは、アナログスイッチ回路を構成するMOSトランジスタのソース・バックゲート間の電圧を低く保つことにより、基板バイアス効果の影響を受けにくく、オン抵抗の低い半導体スイッチを実現でき、出力電圧の精度の高い動作を実現できるものである。

【0015】

具体的に説明すると、本発明に係る半導体スイッチは、複数の階調電圧を発生する階調発生回路と、各々前記複数の階調電圧のうちの1つの階調電圧を選択する複数のアナログスイッチ回路を有する階調セレクタ回路と、前記階調セレクタ回路の動作を制御するスイッチ制御回路とを備えた半導体スイッチであって、前記複数のアナログスイッチ回路の各々は、前記複数の階調電圧のうちの選択すべき階調電圧に接続されたソースを持つMOSトランジスタを有し、前記スイッチ制御回路は、前記MOSトランジスタのオン・オフを制御するよう当該MOSトランジスタのゲート電圧を供給するタイミング制御回路と、前記MOSトランジスタのソース電圧とほぼ等しい電圧を前記MOSトランジスタのバックゲート電圧として供給するバックゲート電圧制御回路とを有することを特徴とするものである。

【発明の効果】

【0016】

10

20

30

40

50

本発明により、半導体スイッチにおいて、オン抵抗が低く、リーク電流を防止でき、高速動作及び出力電圧の精度の高い動作を実行することができる。

【発明を実施するための最良の形態】

【0017】

《第1の実施形態》

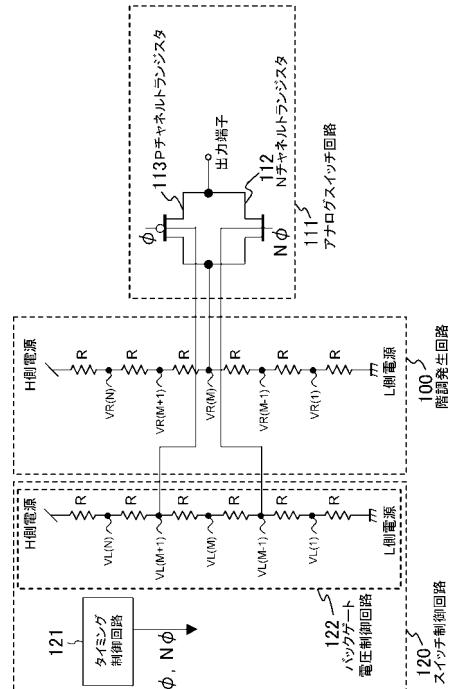

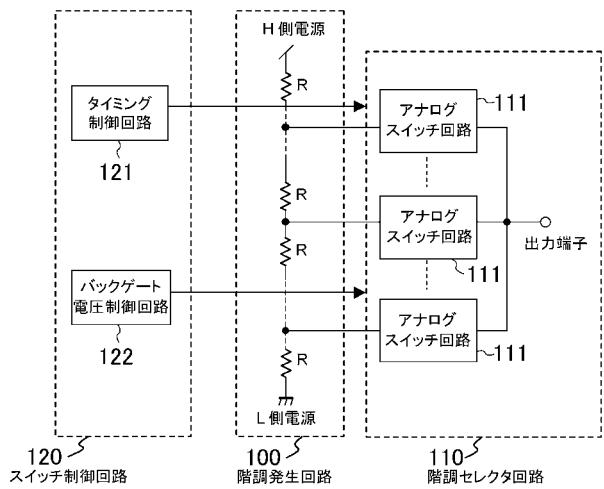

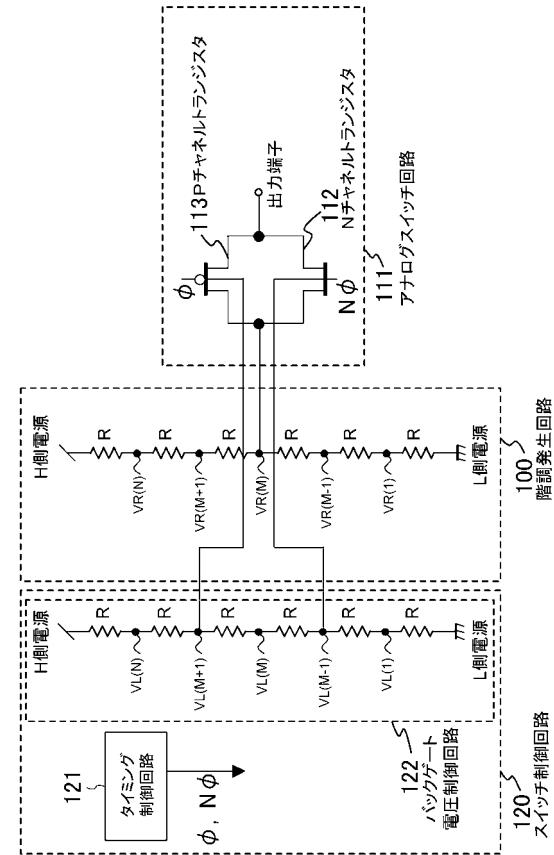

本発明の第1の実施形態による半導体スイッチについて、図1と図2を参照しながら説明する。本第1の実施形態の半導体スイッチは、階調発生回路100と階調セレクタ回路110とスイッチ制御回路120から構成され、スイッチ制御回路120は、タイミング制御回路121とバックゲート電圧制御回路122から構成される。

【0018】

ここで、階調発生回路100は、H側電源とL側電源との間に、複数の抵抗素子Rを直列に接続した抵抗ストリング回路で構成されている。抵抗素子Rの個数をN個とすると、抵抗間の接続点に発生する階調電圧の個数はN-1個となる。H側電源とL側電源の電圧、抵抗素子Rの大きさ及び数は、半導体スイッチの用途に基づいて設計により決定される。階調セレクタ回路110は、複数個のアナログスイッチ回路111により構成され、複数個のアナログスイッチ回路111は、入力側を階調発生回路100の各抵抗素子R間の接続点にそれぞれ接続されており、出力側は階調セレクタ回路110の出力端子に接続されている。

【0019】

図2では、アナログスイッチ回路111の1つの回路図のみを表示し、バックゲート電圧制御回路122を階調発生回路100と同様の抵抗ストリング回路で構成している。図2において、アナログスイッチ回路111はNチャネルMOSトランジスタ112とPチャネルMOSトランジスタ113とが並列接続された構成であり、PチャネルMOSトランジスタ113のゲート信号がLOWレベルであり、NチャネルMOSトランジスタ112のゲート信号NがHIGHレベルである場合にストリング抵抗の1つの接続点から供給される電圧、例えばVR(M)が出力端子に伝達される。逆に、PチャネルMOSトランジスタ113のゲート信号がHIGHレベルであり、NチャネルMOSトランジスタ112のゲート信号NがLOWレベルである場合には、入力側の電圧VR(M)は出力端子に伝達されない。MOSトランジスタ112, 113のゲート端子に接続されるゲート信号とその反転信号Nとは、スイッチ制御回路120のタイミング制御回路121により供給される。

【0020】

バックゲート電圧制御回路122は、H側電源とL側電源との間に、抵抗素子Rを直列に接続したストリング抵抗により構成されており、抵抗素子の個数をN個とすると、抵抗間の接続点に発生する階調電圧の個数はN-1個となる。ここで、バックゲート電圧制御回路122の抵抗間の接続点に発生する階調電圧を低電圧側から順にVL(1)、VL(2)、…、VL(N)とし、低電圧側から数えた任意のM番目の階調電圧をVL(M)、M-1番目の階調電圧をVL(M-1)、M+1番目の階調電圧をVL(M+1)とする。同様に、階調発生回路100の抵抗間の接続点に発生する階調電圧を低電圧側から順にVR(1)、VR(2)、…、VR(N)とし、低電圧側から数えた任意のM番目の階調電圧をVR(M)、M-1番目の階調電圧をVR(M-1)、M+1番目の階調電圧をVR(M+1)とする。

【0021】

バックゲート電圧制御回路122と階調発生回路100のそれぞれの抵抗値と抵抗数を等しいものとすると、双方の低電位からM番目の電圧VR(M)とVL(M)は等しい電圧となる。階調電圧VR(M)を入力とするアナログスイッチ回路111において、アナログスイッチ回路111を構成するPチャネルMOSトランジスタ113のバックゲート端子にはバックゲート電圧制御回路122のVL(M+1)電位を接続し、アナログスイッチ回路111を構成するNチャネルMOSトランジスタ112のバックゲート端子にはバックゲート電圧制御回路122のVL(M-1)電位を接続する。

10

20

30

40

50

## 【0022】

上記のように、階調発生回路100とバックゲート電圧制御回路122とを等しい構成とすることにより、半導体の製造過程において製造ばらつきが発生した場合においても、階調発生回路100とバックゲート電圧制御回路122の各階調電圧 $V_L(M)$ と $V_R(M)$ とはH側電源とL側電源の電圧の抵抗分圧により決定するため、 $V_L(M)$ と $V_R(M)$ はほぼ等しい値となり、PチャネルMOSトランジスタ113のバックゲート電圧 $V_L(M+1)$ はPチャネルMOSトランジスタ113のソース電位 $V_R(M)$ より高い電圧となり、NチャネルMOSトランジスタ112のソース端子よりも低い電圧となる。よって、NチャネルMOSトランジスタ112とPチャネルMOSトランジスタ113のソース・バックゲート間のPN接合の順方向リーキを確実に防止できるとともに、基板バイアス効果の影響を受けにくく、オン抵抗の小さい半導体スイッチを実現できる。

10

## 【0023】

このとき、抵抗の製造ばらつきが小さい場合は、NチャネルMOSトランジスタ112のバックゲートを $V_L(M)$ に接続し、PチャネルMOSトランジスタ113のバックゲートを $V_L(M)$ に接続してもよい。

## 【0024】

また、図3に示されるように、MOSトランジスタのバックゲートからバックゲートの外周のウェルに流れ込む電流、例えばNチャネルMOSトランジスタ112であればPウェルからNウェルに流れ込むPN接合逆バイアスリーク電流は、階調発生回路100から供給されるのではなく、バックゲート電圧制御回路122から供給されるため、 $I_2 = I_1$ となる結果、階調発生回路100の電圧ずれを引き起こすことなく階調電圧を出力端子に伝達できる。なお、PチャネルMOSトランジスタ113の場合にNウェルからPウェルに流れ込む逆バイアスリーク電流もバックゲート電圧制御回路122から供給されるが、図示を省略する。

20

## 【0025】

## 《第2の実施形態》

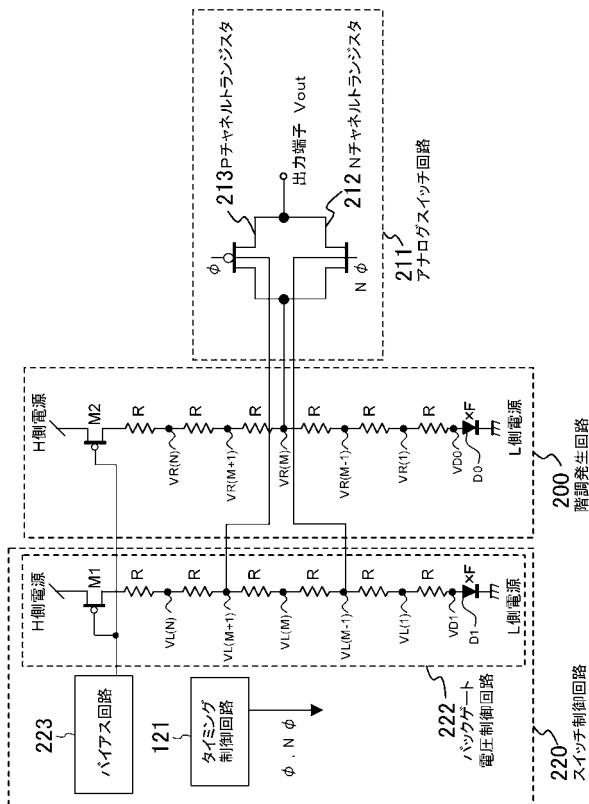

本発明の第2の実施形態による半導体スイッチについて図4を参照しながら説明する。第2の実施形態の半導体スイッチはアナログスイッチ回路211とスイッチ制御回路220と階調発生回路200から構成される。また、スイッチ制御回路220はタイミング制御回路121とバックゲート電圧制御回路222とバイアス回路223から構成される。

30

## 【0026】

ここで、タイミング制御回路121は第1の実施形態と同じ構成であるため、図1及び図2と同様の構成部分については同一の符号を付して、その詳細な説明を省略する。

## 【0027】

階調発生回路200はH側電源とL側電源の間にPチャネルMOSトランジスタM2と、複数個の抵抗素子Rと、ダイオードD0とが直列接続された構成となる。また、バックゲート電圧制御回路222はH側電源とL側電源の間にPチャネルMOSトランジスタM1と、複数個の抵抗素子Rと、ダイオードD1とが直列接続された構成となる。なお、ダイオードD0は、並列に接続されたF個のダイオードから構成され、ダイオードD1においても、並列に接続されたF個のダイオードから構成される。PチャネルMOSトランジスタM1とPチャネルMOSトランジスタM2のゲート電圧は共通接続されており、バイアス回路223に接続されている。

40

## 【0028】

上記構成は、第1の実施形態に記載された半導体スイッチを使用したバンドギャップリファレンス回路であり、アナログスイッチ回路211の出力端子には電源電圧と周囲温度に依存しない基準電圧が出力される。

## 【0029】

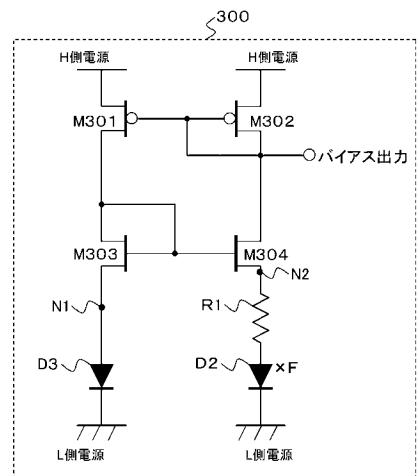

図5に、図4中のバイアス回路223の具体的な回路構成を示す。図5のバイアス回路300は、第1のカレントミラー回路を構成するPチャネルMOSトランジスタM301及

50

びM302と、第2のカレントミラー回路を構成するNチャネルMOSトランジスタM303及びM304と、NチャネルMOSトランジスタM303のソースとL側電源に接続されたダイオードD3と、NチャネルMOSトランジスタM304のソースとL側電源間に直列に接続された抵抗素子R1及びダイオードD2とから構成される。

【0030】

なお、ダイオードD2は、並列に接続されたF個のダイオードから構成される。ダイオードD3及びダイオードD2の接合総面積をそれぞれS1、S2とし、その面積比S2/S1をFとする。以上のように構成されたバンドギャップリファレンス回路について、以下にその動作を説明し、バンドギャップリファレンス回路の出力電圧である基準電圧の電圧式を求める。

10

【0031】

ここで前提として、バイアス回路300の第1のカレントミラー回路を構成するPチャネルMOSトランジスタM301及びM302のゲート長及びゲート幅の大きさは等しく、第2のカレントミラー回路を構成するNチャネルMOSトランジスタM303及びM304のゲート長及びゲート幅の大きさは等しいものとする。

【0032】

ボルツマン定数をk、絶対温度をT、電子の電荷量をqとすると、PチャネルMOSトランジスタM302のソース・ドレイン間電流I2は、

$$I_2 = (kT/q) \cdot LN(F) / R_1 \dots (1)$$

20

で表される。ここで、演算記号LNはeを底とする自然対数である。この電流I2は電源電圧に依存せず、物理定数、抵抗値R1並びにダイオードD3及びダイオードD2の接合総面積比Fによって決定される。

【0033】

バイアス回路223(300)のバイアス出力はバックゲート電圧制御回路222のPチャネルMOSトランジスタM1と階調発生回路200のPチャネルMOSトランジスタM2のゲート端子に接続されており、バイアス回路223(300)のPチャネルMOSトランジスタM302と階調発生回路200のPチャネルMOSトランジスタM2とバックゲート電圧制御回路222のPチャネルMOSトランジスタM1はカレントミラーを構成している。

30

【0034】

よって、PチャネルMOSトランジスタM302とPチャネルMOSトランジスタM1とPチャネルMOSトランジスタM2のゲート長がそれぞれ等しく、ゲート幅がそれぞれ等しいとすると、PチャネルMOSトランジスタM302に流れる電流I2と等しい電流がPチャネルMOSトランジスタM1とPチャネルMOSトランジスタM2に流れる。

【0035】

ここで階調発生回路200の複数の抵抗素子の抵抗値をR、個数をN個とし、L側電源から数えたM番目の階調電圧をVR(M)、ダイオードD0の順方向電圧をVD0とすると、VR(M)は、

$$VR(M) = (M \cdot R / R_1) \cdot (kT/q) \cdot LN(F) + VD_0 \dots (2)$$

40

で表される。

【0036】

また、バックゲート電圧制御回路222の複数の抵抗素子の抵抗値をR、個数をN個とし、L側電源から数えたM番目の階調電圧をVL(M)、ダイオードD1の順方向電圧をVD1とすると、VL(M)は、

$$VL(M) = (M \cdot R / R_1) \cdot (kT/q) \cdot LN(F) + VD_1 \dots (3)$$

40

で表される。

【0037】

また、バックゲート電圧制御回路222におけるL側電源から数えたM-1番目の階調出力VL(M-1)は、

$$VL(M-1) = [(M-1) \cdot R / R_1] \cdot (kT/q) \cdot LN(F) + VD_1 \dots$$

50

( 4 )

で表され、バックゲート電圧制御回路 222 における L 側電源から数えた M + 1 番目の階調出力  $V_L(M+1)$  は、

$$V_L(M+1) = [(M+1) \cdot R / R_1] \cdot (kT/q) \cdot LN(F) + VD1 \dots \quad (5)$$

で表せる。

【 0 0 3 8 】

アナログスイッチ回路 211 の P チャネル MOS トランジスタ 213 のバックゲートには  $V_L(M+1)$  が接続され、アナログスイッチ回路 211 の N チャネル MOS トランジスタ 212 のバックゲートには  $V_L(M-1)$  が接続される。 10

【 0 0 3 9 】

また、  $VR(M)$  の電圧をアナログスイッチ回路 211 を介して出力端子  $V_{out}$  に出力するので、

$$V_{out} = VR(M) = [(M \cdot R) / R_1] \cdot (kT/q) \cdot LN(F) + VD0 \dots \quad (6)$$

で表される。

【 0 0 4 0 】

出力電圧  $V_{out}$  の温度特性は、

$$V_{out} / T = VR(M) / T = [(M \cdot R) / R_1] \cdot (k/q) \cdot LN(F) + VD0 / T \dots \quad (7)$$

で表される。 20

【 0 0 4 1 】

また、バックゲート電圧制御回路 222 の階調電圧  $V_L(M)$  の温度特性は、

$$V_L(M) / T = [(M \cdot R) / R_1] \cdot (k/q) \cdot LN(F) + VD1 / T \dots \quad (8)$$

で表される。

【 0 0 4 2 】

ここで、ダイオードの順方向電圧  $VF$  の温度依存性は  $-2 \text{ mV/}^{\circ}\text{C}$  であることが知られており、(7)式の右辺がゼロとなるような階調発生回路 200 とスイッチ制御回路 220 の抵抗素子  $R$  の個数  $M$ 、抵抗値  $R$ 、抵抗値  $R_1$ 、接合総面積比  $F$  の定数を選択することで、周囲温度に依存しない  $VR(M)$ 、 $V_L(M)$  及び出力電圧  $V_{out}$  を得ることができる。例えば、 $R_1 = 5.0 \text{ k}\Omega$ 、 $R = 5.0 \text{ k}\Omega$ 、 $M = 11$  とし、接合面積比  $F$  を 8 とすると、 $VR(M)$ 、 $V_L(M)$ 、 $V_{out}$  の温度特性は  $-0.3 \text{ mV/}^{\circ}\text{C}$  となる。 30

【 0 0 4 3 】

以上のように本実施形態の半導体スイッチによれば、回路構成及び、(2)、(4)、(5)式から明らかなように P チャネル MOS トランジスタ 213 のソース端子よりバックゲート端子の方が高電位であり、N チャネル MOS トランジスタ 212 のソース端子よりバックゲート端子の方が低電位となるため、アナログスイッチ回路 211 において、N チャネル MOS トランジスタ 212 と P チャネル MOS トランジスタ 213 のソース・バックゲート間の PN 接合の順方向リークを確実に防止できる。また、(7)、(8)式から明らかなように、バックゲート電圧制御回路 222 の階調電圧  $V_L(M)$  と階調発生回路 200 の階調電圧  $VR(M)$  とが共に等しい温度依存性と電源電圧依存性を持つので、周囲温度や電源電圧が変動しても  $V_L(M)$  と  $VR(M)$  の電圧のずれが小さく、基板バイアス効果の影響を低減することが可能となる。PN 接合逆バイアスリーク電流は、階調発生回路 200 から供給されるのではなく、バックゲート電圧制御回路 222 から供給されるため、階調発生回路 200 の電圧ずれを引き起こすことなく、出力電圧の精度の高い動作を実行することができる。 40

【 0 0 4 4 】

なお、低しきい値電圧化を実現するにあたって、H 側電源と L 側電源間電圧以下の耐压を持つ MOS トランジスタを用いて、半導体スイッチを構成することで、低オン抵抗、高

10

20

30

40

50

速スイッチングが可能である。

【0045】

また、上記第1及び第2の実施形態では、PチャネルMOSトランジスタとNチャネルMOSトランジスタとを並列接続したアナログスイッチ回路を用いていたが、PチャネルMOSトランジスタのみで構成されるアナログスイッチ、又はNチャネルMOSトランジスタのみで構成されるアナログスイッチを用いても同様の効果を得ることができる。

【0046】

また、上記第1及び第2の実施形態で用いられた抵抗素子として、各々半導体プロセスで製造可能な抵抗素子である、ポリシリコンを用いた抵抗素子、拡散抵抗を用いた抵抗素子、ウェル抵抗を用いた抵抗素子を用いても同様の効果を得ることができる。

10

【0047】

また、上記第2の実施形態で用いたダイオードは半導体プロセスで製造可能なPN接合を有する素子であればよく、例えばMOSトランジスタのソース及びドレイン端子とバックゲート端子との間のPN接合を利用して同様の効果を得ることができる。

【産業上の利用可能性】

【0048】

本発明は、半導体スイッチに有用であり、特に階調発生回路や電源回路を構成する半導体スイッチに特に有用である。

【図面の簡単な説明】

【0049】

【図1】本発明に係る半導体スイッチの全体構成を示すブロック図である。

20

【図2】本発明の第1の実施形態に係る半導体スイッチの詳細構成図である。

【図3】図2中のNチャネルMOSトランジスタにトリプルウェル構造を採用した場合の断面図である。

【図4】本発明の第2の実施形態に係る半導体スイッチの詳細構成図である。

30

【図5】図4中のバイアス回路の具体例を示す回路図である。

【図6】従来の半導体スイッチの構成例を示す回路図である。

【図7】図6中のNチャネルMOSトランジスタにトリプルウェル構造を採用した場合の断面図である。

【符号の説明】

【0050】

100, 200, 400 階調発生回路

110 階調セレクタ回路

111, 211, 410 アナログスイッチ回路

112, 212, 411 NチャネルMOSトランジスタ

113, 213, 412 PチャネルMOSトランジスタ

120, 220, 420 スイッチ制御回路

121, 421 タイミング制御回路

122, 222 バックゲート電圧制御回路

223, 300 バイアス回路

D0, D1, D2, D3 ダイオード

M1, M2, M301, M302 PチャネルMOSトランジスタ

M303, M304 NチャネルMOSトランジスタ

R, R1 抵抗素子

VR(1) ~ VR(N), VL(1) ~ VL(N) 階調電圧

40

, N アナログスイッチ回路のオン/オフ制御信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 關 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 串間 貴仁

大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内

(72)発明者 小島 友和

大阪府門真市大字門真1006番地 パナソニック半導体システムテクノ株式会社内

F ターム(参考) 5J055 AX02 BX17 CX01 DX13 DX14 DX22 DX74 DX82 EX07 EY03

EY21 EZ12 FX13 FX32 GX01 GX07

5J056 AA00 BB02 BB49 DD28 EE04 FF06