(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4653735号

(P4653735)

(45) 発行日 平成23年3月16日(2011.3.16)

(24) 登録日 平成22年12月24日(2010.12.24)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 613A |

| HO1L 21/8238 | (2006.01) | HO1L 27/08 | 321D |

| HO1L 27/092  | (2006.01) | HO1L 27/08 | 331E |

| HO1L 27/08   | (2006.01) | HO1L 29/58 | G    |

| HO1L 29/49   | (2006.01) | HO1L 29/78 | 617M |

請求項の数 2 (全 8 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2006-509809 (P2006-509809)  |

| (86) (22) 出願日 | 平成16年4月8日(2004.4.8)           |

| (65) 公表番号     | 特表2006-523037 (P2006-523037A) |

| (43) 公表日      | 平成18年10月5日(2006.10.5)         |

| (86) 國際出願番号   | PCT/US2004/010814             |

| (87) 國際公開番号   | W02004/093182                 |

| (87) 國際公開日    | 平成16年10月28日(2004.10.28)       |

| 審査請求日         | 平成19年4月9日(2007.4.9)           |

| (31) 優先権主張番号  | 10/410,043                    |

| (32) 優先日      | 平成15年4月9日(2003.4.9)           |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (72) 発明者  | アデトゥトゥ、オルブンミ オー.<br>アメリカ合衆国 78729 テキサス州<br>オースティン パートリッジ ベンド<br>ドライブ 12919                                 |

最終頁に続く

(54) 【発明の名称】デュアルメタルゲート構造を形成するためのプロセス

## (57) 【特許請求の範囲】

## 【請求項 1】

デュアルメタルゲート構造を形成するためのプロセスであって、

第1領域と第2領域とを有し、前記第1領域はN型を有し、前記第2領域はP型を有する半導体基板を提供するステップと、

前記半導体基板の前記第1領域と前記第2領域とを覆う誘電体層を形成するステップであって、前記誘電体層は酸窒化シリコン又は酸化シリコンからなるステップと、

前記誘電体層上に設けられ、前記半導体基板の前記第1領域を覆う第1メタル含有層を形成するステップであって、前記第1メタル含有層は窒化チタンからなるステップと、

前記第1メタル含有層と前記誘電体層とを覆うと共に、前記半導体基板の前記第2領域上に設けられた前記誘電体層の一部と直接接する第2メタル含有層を形成するステップであって、前記第2メタル含有層は窒化タンタルシリコンからなるステップと、

前記第2メタル含有層上にパターン化されたマスキング層を形成するステップと、

前記パターン化されたマスキング層を用いて前記第2メタル含有層をドライエッチングし、第2ゲート層を形成すると共に前記第1メタル含有層上に第1ゲート層の上部を形成するステップと、

前記第1ゲート層の上部をマスクとして用いて前記第1メタル含有層の少なくとも一部をウェットエッチングし、前記第1ゲート層の下部を形成するステップであって、前記ウェットエッチングは、硫酸及び過酸化水素の水溶液を用いたピラニア洗浄であるステップと

10

を備えるプロセス。

【請求項 2】

デュアルメタルゲート構造を形成するためのプロセスであって、

第1領域と第2領域とを有し、前記第1領域はN領域であり、前記第2領域はP領域である半導体基板を提供するステップと、

前記半導体基板の前記第1領域と前記第2領域とを覆うゲート誘電体層を形成するステップであって、前記ゲート誘電体層は酸窒化シリコン又は酸化シリコンからなるステップと、

前記ゲート誘電体層上に設けられ、前記半導体基板の前記第1領域を覆う第1メタル含有層を形成するステップであって、前記第1メタル含有層は窒化チタンからなるステップと、

前記第1メタル含有層と前記ゲート誘電体層とを覆うように設けられ、前記半導体基板の前記第2領域を覆う前記ゲート誘電体層の一部と直接接する第2メタル含有層を形成するステップであって、前記第2メタル含有層は窒化タンタルシリコンからなるステップと、

前記第2メタル含有層上にパターン化されたマスキング層を形成するステップと、

前記パターン化されたマスキング層を用いて前記第2メタル含有層をドライエッチングし、第2ゲート層を形成すると共に前記第1メタル含有層上に第1ゲート層の上部を形成するステップと、

前記パターン化されたマスキング層を用いて前記第1メタル含有層の少なくとも一部をウェットエッチングし、前記第1ゲート層の下部を形成するステップであって、前記ウェットエッチングは、硫酸及び過酸化水素の水溶液を用いたピラニア洗浄であるステップとを備えるプロセス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メタルゲートを用いた集積回路の製造に関し、より詳しくは、異なる構造のメタルゲートを用いた集積回路の製造に関する。

【背景技術】

【0002】

半導体デバイスの縮小化が進み、従来のポリシリコンゲートでは不十分になりつつある。一つの問題として、相対的に高い固有抵抗が挙げられ、別の問題として、ポリシリコンゲートとゲート誘電体との境界近傍においてポリシリコンゲート中に含まれるドーパントの減少が挙げられる。ポリシリコンに関するこれらの欠陥を克服するため、その代替物としてメタルゲートが要求されている。PチャンネルトランジスタとNチャンネルトランジスタとに要求される機能のため、PチャンネルトランジスタとNチャンネルトランジスタとに用いられるメタルの仕事関数はそれぞれ異なるべきである。これにより、二種類のメタルを、ゲート誘電体の直上に設けられるメタルとして使用することが可能になる。これに対する有効なメタルは、一般に、堆積やエッチングを容易に行うことができない。有効な二種類のメタルとしては、Pチャンネルトランジスタ用として窒化チタンが知られ、Nチャンネルトランジスタ用として窒化タンタルシリコンが知られている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

しかしながら、これらの材料に対し通常用いられるエッチング液は、ゲート誘電体とシリコン基板とに対して十分に選択的でないため、シリコン基板に溝が形成されてしまうおそれがある。このことは、Pチャンネル活性領域において、窒化タンタルシリコンの下に窒化チタンが設けられているために生じる。Pチャンネル活性領域上における窒化タンタルシリコンの除去のためのエッチング処理では、その後のエッチングによりNチャンネル領域内のゲート誘電体を露出させるため、窒化チタンを露出させなければならない。この

10

20

30

40

50

ため、窒化チタンのエッティングは、ソース／ドレインが形成されるNチャンネル活性領域に露出しているゲート誘電体に対しても適用されてしまう。このような窒化チタンのエッティングにより、露出しているゲート誘電体が除去されてしまい、ソース／ドレインの形成される基部となるシリコンに溝が形成されてしまう虞がある。

【課題を解決するための手段】

【0004】

従って、上述した課題を解決することの可能なデュアルゲートトランジスタの製造プロセスが求められている。

【発明を実施するための最良の形態】

【0005】

本発明は、一例として記載され、添付図面により制限されるものではない。添付図面では、同じ参照番号が同じ要素を示している。

図中の要素が明瞭化及び簡略化のために示され、実寸で図示される必要のないことは当業者にとって明らかである。例えば、本発明の実施形態に対する理解をより深めるため、図中の要素のうち、いくつかの寸法が、他の要素に比べて誇張されている。

【0006】

一実施態様において、半導体デバイスは、Pチャンネルゲート層を有し、同Pチャンネルゲート層は、第1メタルと、同第1メタル上に第2メタルとを備えている。また、半導体デバイスは、Nチャンネルゲート層を有し、同Nチャンネルゲート層は、ゲート誘電体と直接接する第2メタルを備えている。Nチャンネルゲート層、及びPチャンネルゲート層の一部には、ドライエッティングによるエッティング処理が施される。Pチャンネルゲート層は、ウェットエッティングにより仕上げられる。ウェットエッティングは、ゲート誘電体と第2メタルとの両方に対して極めて選択的である。そのため、Nチャンネルトランジスタは、Pチャンネルゲート層のエッティング仕上げによる影響を受けない。このことは、図面と以下の説明とを参照することによって一層理解される。

【0007】

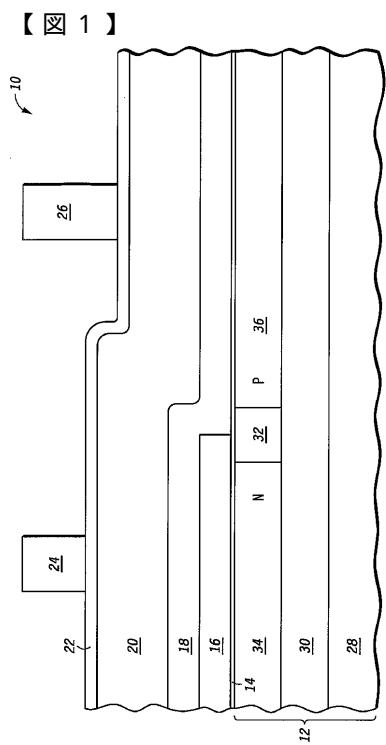

図1に示すように、半導体デバイス10は、SOI基板12（シリコンオンインシュレータウェーハ）、SOI基板12の表面の直上にゲート誘電体14、窒化チタン層16、窒化タンタルシリコン層18、ポリシリコン層20、シリコンを多く含む窒化シリコンからなる反射防止膜（ARC）層22、及び、パターン化されたフォトトレジスト部24, 26を備えている。SOI基板12は、シリコン基板28、絶縁層30、N領域34、絶縁領域32、及びP領域36を備えている。絶縁層30は、酸化シリコンであることが好ましいが、別の絶縁材料であってもよい。また、SOI基板の代わりに、バルクシリコン基板を用いてもよい。層16は、P領域36上ではなく、N領域34上に設けられ、ゲート誘電体14と直接接している。層18は、層16とP領域36とを有するSOI基板12上に設けられている。層20は層18上に設けられ、層22は層20上に設けられている。Pチャンネルゲート層が形成されるN領域34上には、パターン化されたフォトトレジスト部24が部分的に設けられている。同様に、Nチャンネルゲート層が形成されるP領域36上には、パターン化されたフォトトレジスト部26が部分的に設けられている。

【0008】

ここに至って、ゲート誘電体14を貫通しないようなドライエッティングが実施される。層16, 18の厚みは5nmであることが好ましいが、3nmに小さくしてもよく、5nmより大きくしてもよい。トランジスタのゲート長の決定に用いられるパターン化されたフォトトレジスト部24, 26の幅は、メタル層16, 18の厚みの約10倍に相当する50nmであることが好ましい。絶縁領域32の幅は、パターン化されたフォトトレジスト部24, 26の幅とほぼ同等である。これらの寸法は、使用される特殊技術によって小さくすることもでき、大きくすることもできる。例えば、リソグラフィー技術によれば、製造時に、パターン化されたフォトトレジスト部24, 26のための最小寸法が、50nmか、或いは、100nmと同等の値にのみ制限される。ところが、層16, 18の厚みは、やはり5nmのままであり、ARC層22の厚みは20nmであることが好ましい。

10

20

30

40

50

## 【0009】

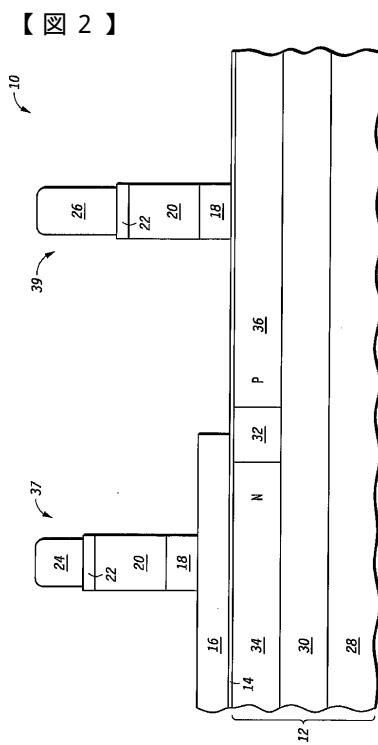

図2に示すように、ドライエッティングを実施した結果、N領域34上とP領域36上には、それぞれゲート層37, 39が形成される。ゲート誘電体14は、ゲート層39により覆われた部分を除いてP領域36上に露出されている。N領域34上の層16は、ゲート層37により覆われた部分を除いて露出されている。パターン化されたフォトレジスト部24, 26は侵食されてもよい。ゲート層37, 39は、共に、ARC層22の部分と、層20の部分と、層18の部分とを備えている。

## 【0010】

図2に示されるゲート層37, 39を形成する際のドライエッティングは、3段階のエッティング工程を通じて実施されることが好ましい。第一段階では、窒化シリコンARC層22のエッティングを対象としており、ハロゲンベースの反応性イオンエッティング(RIE)を用いることが好ましい。続いて、ハロゲンベースのRIEにより層20のエッティングが行われる。層20のエッティングに続いて、ハロゲンベースのRIEにより層18のエッティングが行われる。これらのエッティングでは、これらの種類の層を対象とした従来のエッティングが行われる。窒化チタンのエッティングは、通常、RIEにより行われ、この場合もハロゲンベースのRIEである。これに伴う困難性として、窒化チタンがゲート誘電体に対して十分選択的でないことが挙げられる。この場合、ゲート誘電体は酸窒化シリコンであることが好ましい。酸窒化シリコンは、酸化シリコンよりも高い誘電率を有し、その上、ハロゲンベースのRIEエッティングに対する耐性も高いが、窒化チタンを必要な厚みにエッティングするまでの間、該エッティングにより貫通されることを回避するのに十分な抵抗力を有してはいない。ハロゲンベースのRIEエッティングには多少の違いがあり、最終的には、実際にエッティングされる層に応じて経験的に決められている。これらの材料を対象とするエッティングは従来通りであり、慣習的な方法により決められている。酸化シリコンがゲート誘電体として用いられると、同じようなエッティングの問題が生じてしまい、実際には、より悪くなることすらある。なぜなら、層16, 18に用いられる金属含有材料をエッティング対象とした通常のドライエッティングは、酸窒化シリコンを対象とした場合よりも酸化シリコンに対して更に選択的ではないためである。

## 【0011】

処理のためには、窒化チタンの厚みを薄くすることが望ましい。しかしながら、次に形成されるトランジスタのチャンネルを制御する仕事関数の決定のため、窒化チタンの厚みを十分に確保することが望ましい。ゲート誘電体は、3.9より大きい誘電率を有することが好ましい。一般には、NチャンネルトランジスタゲートとPチャンネルトランジスタゲートとに対する最適な仕事関数は、それぞれ、シリコンのエネルギー・バンドのバンド端、即ち、4.1電子ボルト(eV)と5.2eVとであると考えられている。このことは、バルクシリコンと、部分空乏層型SOIとの両方に対しても当てはまる。実際に、これを実現することは困難であるが、好ましくは、Nチャンネルメタルゲートは、4.4eV以下の仕事関数を有するべきであり、Pチャンネルメタルゲートは、本実施形態の部分空乏層型SOI基板又はバルク半導体基板に対して4.6eVよりも大きい仕事関数を有するべきである。窒化チタン層16は、4.65eVの仕事関数を有し、窒化タンタルシリコン層18は、4.4eVの仕事関数を有している。仕事関数の差異をより小さくするほど、完全空乏層型SOI基板に対しては要求を満たすものとなり得る。

## 【0012】

従って、層16をエッティングするため、従来のRIEエッティングを用いる代わりに、ウェットエッティングが用いられている。ウェットエッティングは、硫酸及び過酸化水素の水溶液を用いたピラニア洗浄であることが好ましい。このためには、他のウェットエッティングについても有効であろう。ピラニア洗浄は、製造設備の入手が容易であり、そのため利用方法や制御方法がよく理解されていることから、とりわけ有効である。このピラニア洗浄は、酸化シリコン、並びに、窒化タンタルシリコン及び酸窒化シリコンの両方に対し極めて選択的である。従って、ピラニア洗浄に曝される層16が除去されるまでの間、層18とゲート誘電体14についても最低限度のエッティングがなされる。このことは、ゲート

10

20

30

40

50

誘電体 14 が酸化シリコンの場合にも当てはまる。

【0013】

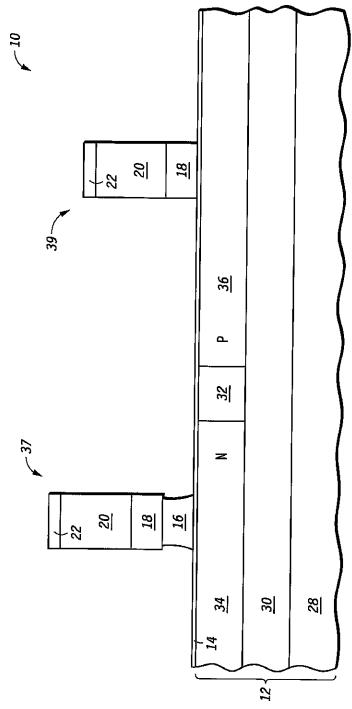

ピラニア洗浄の適用結果を図3に示す。これは、完成したゲート層37と、ゲート層39の最小変化とを示している。パターン化されたフォトレジスト部24, 26は、ピラニア洗浄時に除去される。ウェット洗浄による材料の除去では、縦方向と横方向とを共にエッティングする等方性のエッティングが行われる。従って、ゲート層37の一部を構成する層18の下部から層16が部分的に除去されて層16のアンダーカットが生じる。こうしたアンダーカットは、一般に、エッティングされる層の厚みよりも大きくない。この場合、層16の好ましい厚みは5nmであり、そのため、層16と層18との境界に生じるアンダーカットの量は約5nmとなり得る。この値は、ゲート長の約10%に相当し、ゲート誘電体14に近づくほどアンダーカットの量は小さくなる。図3には、従来の方法でトランジスタが形成され、完成した状態のゲート層37, 39が示されている。

【0014】

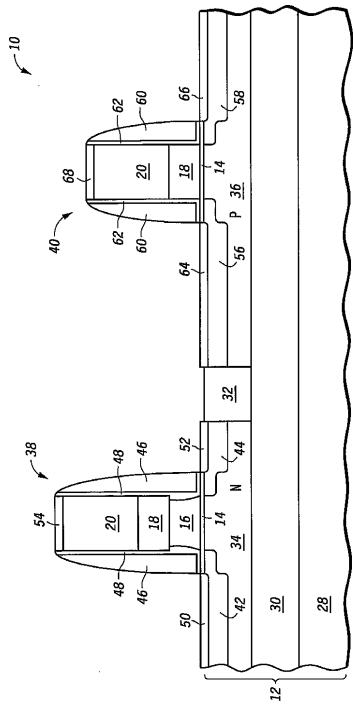

図4には、ゲート層37, 39を用いて完成した状態のトランジスタ38, 40が示されている。ARC層22は、両ゲート層37, 39から除去されており、従来の方法によつて、トランジスタ38, 40を形成することができる。トランジスタ38は、ソース/ドレイン42, 44、側壁スペーサ46、ライナー48、及びケイ化物領域50, 52, 54を有するPチャンネルトランジスタである。ケイ化物領域50, 52は、それぞれ、ソース/ドレイン42, 44と接触した状態で、それらの直上に形成されている。同様に、ケイ化物領域54は、図3に示されるゲート層37の一部を構成する層20と接触した状態で、同層20の直上に形成されている。トランジスタ40は、ソース/ドレイン56, 58、側壁スペーサ60、ライナー62、及びケイ化物領域64, 66を有するNチャンネルトランジスタである。ケイ化物領域64, 66は、それぞれ、ソース/ドレイン56, 58と接触した状態で、それらの直上に形成されている。

【0015】

上述した仕様において、本発明は、特定の実施態様について述べられている。しかしながら、特許請求の範囲に記載される本発明の技術的範囲から逸脱しないで、種々の変更を行うことが可能であることは当業者にとって明らかである。例えば、図1に示すデバイス構造の代替案としては、濃度勾配を有する单一材料を含む合金又は積層されたデバイス構造の上部に設けられる導体に対するものがある。また、二つの異なる層16, 18は、本明細書にて特定されたものと異なる材料であつてもよい。これら二つの層は、実際には同じ材料からなるものの、所望の仕事関数差を得るために材料の割合を異ならせるようにしてもよい。更に、P領域36内にて、層18の直上に層16を設けるため、同層18を最初に堆積するようにしてもよい。その結果、図2～図4に示されるようにPチャンネルゲート層が両メタル層を有する代わりに、Nチャンネルゲート層が両メタルを有することになる。代替案の別の例として、デバイス構造の上部に設けられるポリシリコン層を、例えばタンクステン等のシート抵抗の低い材料に変更してもよい。つまり、本明細書及び図は、限定的な意義よりもむしろ説明的な意義とみなすべきであり、そのような全ての変更は、本発明の技術的に範囲に含まれている。

【0016】

有利点と、問題に対する解決策とについて、特定の実施態様に関して説明してきた。しかしながら、有利点、問題に対する解決策、及び、全ての利点又は解決策を生じさせるか或いは一層明確にすることのできる全ての要素は、幾つかの又は全ての特許請求の範囲に重要な、必要な、又は、本質的な特徴或いは要件と解釈するべきではない。本明細書で用いられる「備える」や「からなる」といった用語、又は全ての変更例は、非排他的の包含をカバーするためのもので、列挙された要素からなるプロセス、方法、物品、又は装置は、それらの要素のみを含むものではなく、本明細書には明確に列挙されていない他の要件を含むこともできる。

【図面の簡単な説明】

【0017】

10

20

30

40

50

【図1】プロセスの連続的な段階における本発明の第1実施形態に係る半導体デバイスの断面図。

【図2】プロセスの連続的な段階における本発明の第1実施形態に係る半導体デバイスの断面図。

【図3】プロセスの連続的な段階における本発明の第1実施形態に係る半導体デバイスの断面図。

【図4】プロセスの連続的な段階における本発明の第1実施形態に係る半導体デバイスの断面図。

FIG.1

FIG.2

【図3】

FIG.3

【図4】

FIG.4

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01)

(72)発明者 ルコースキー、エリック ディ .

アメリカ合衆国 7 8 6 6 4 テキサス州 ラウンド ロック フラワー ヒル ドライブ 3 0

1 6

(72)発明者 サマベダム、スリカンス ピー .

アメリカ合衆国 7 8 7 2 8 テキサス州 オースティン ベルナーディーノ コブ 2 9 1 3

(72)発明者 マルチネス、アルトウーロ エム . ジュニア

アメリカ合衆国 7 8 7 2 7 テキサス州 オースティン ケリース ファーム レーン 1 3 0

0 0

審査官 綿引 隆

(56)参考文献 特開2002-359295 (JP, A)

特開2002-083812 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 21/8238

H01L 27/08

H01L 27/092

H01L 29/423

H01L 29/49

H01L 29/786