(10) DE 103 10 552 B4 2014.01.23

(12)

## Patentschrift

(21) Aktenzeichen: 103 10 552.2

(51) Int Cl.: H01L 29/78 (2006.01)

(22) Anmelddatum: 11.03.2003

H01L 21/336 (2006.01)

(43) Offenlegungstag: 30.09.2004

(45) Veröffentlichungstag

der Patenterteilung: 23.01.2014

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

**Infineon Technologies AG, 81669, München, DE**

(56) Ermittelter Stand der Technik:

**APPELS, J. A.; VAES, H. M. J.: High voltage thin layer devices (RESURF devices). In: Electron Devices Meeting, 25, 1979, S. 238 - 241. - ISSN 0000-0238. <http://dx.doi.org/10.1109/IEDM.1979.189589>**

(74) Vertreter:

**Schoppe, Zimmermann, Stöckeler, Zinkler & Partner, 82049, Pullach, DE**

(72) Erfinder:

**Krumbein, Ulrich, Dr., 83026, Rosenheim, DE;

Taddiken, Hans, Dr., 81737, München, DE**

(54) Bezeichnung: **Feldeffekttransistor und Halbleiterchip mit diesem Feldeffekttransistor**

(57) Hauptanspruch: Feldeffekttransistor mit:

einem Substrat (30) mit einer Dotierung eines ersten Leitfähigkeitstyps;

einem Drainbereich (50, 52, 54) in dem Substrat (30) mit einer Dotierung eines zweiten, zu dem ersten Leitfähigkeits-

typ entgegengesetzten Leitfähigkeits-

typs;

einem Sourcebereich (40) in dem Substrat (30), der von dem Drainbereich (50, 52, 54) lateral beabstandet ist, mit

einer Dotierung des zweiten Leitfähigkeits-

typs;

einem Kanalbereich (98) in dem Substrat (30), der zwi-

schen dem Sourcebereich (40) und dem Drainbereich (50,

52, 54) angeordnet ist; und

einer Mehrzahl von Abschnitten (102) mit einer Dotierung

des zweiten Leitfähigkeits-

typs, die mit dem Drainbereich (50, 52, 54) in elektrischem Kontakt sind und sich ausge-

hend von dem Drainbereich (50, 52, 54) in einer ersten

Richtung senkrecht zu einer Oberfläche (32) des Substrats

(30) in das Substrat (30) erstrecken, wobei die Abschnitte (102) in lateraler Richtung durch Zwischenräume (104),

die unmittelbar an den Drainbereich (50, 52, 54) angrenzen und eine Dotierung des ersten Leitfähigkeits-

typs aufweisen, voneinander beabstandet sind, so dass unterhalb

des Drainbereichs (50, 52, 54) in lateraler Richtung alter-

nierend Gebiete (102, 104) mit dem ersten Leitfähigkeits-

typ und mit dem zweiten Leitfähigkeits-

typ angeordnet sind,

wobei der Drainbereich einen hochdotierten Drainteilbereich (50) und einen niedrig dotierten Drainteilbereich (52,

54) mit einem oder mehreren Drainabschnitten aufweist, in

dem oder in denen eine Dotierungskonzentration in Rich-

tung zu dem Kanalbereich (98) kontinuierlich oder stufen-

weise abnimmt, und

wobei die Abschnitte (102) nur unter dem hochdotierten

Drainteilbereich (50) und dem niedrig dotierten Drainteil-

bereich (52, 54) angeordnet sind, so dass eine minimale

Drainspannung, ab der sich eine Drain-Substrat-Kapazität

nicht mehr ändert, reduziert ist.

## Beschreibung

**[0001]** Die vorliegende Erfindung bezieht sich auf einen Feldeffekttransistor mit einer reduzierten kapazitiven Kopplung zwischen Drain und Substrat sowie auf einen Halbleiterchip mit diesem Feldeffekttransistor.

**[0002]** Für zahlreiche Großsignalanwendungen werden LDMOS-Transistoren bzw. LDMOS-Feldeffekttransistoren (LDMOS = lateral diffused metal oxide semiconductor = lateral diffundierter Metalloxidfeldeffekttransistor) verwendet, beispielsweise für Leistungsverstärker für Basisstationen, Handsets, Mobiltelefone etc. Die Ausgangskapazität eines LDMOS-Feldeffekttransistors ist von der Drainspannung bzw. von der Spannung zwischen der Drain bzw. dem Drainbereich einerseits und dem oft mit einem Bezugspotential verbundenen Substrat andererseits abhängig.

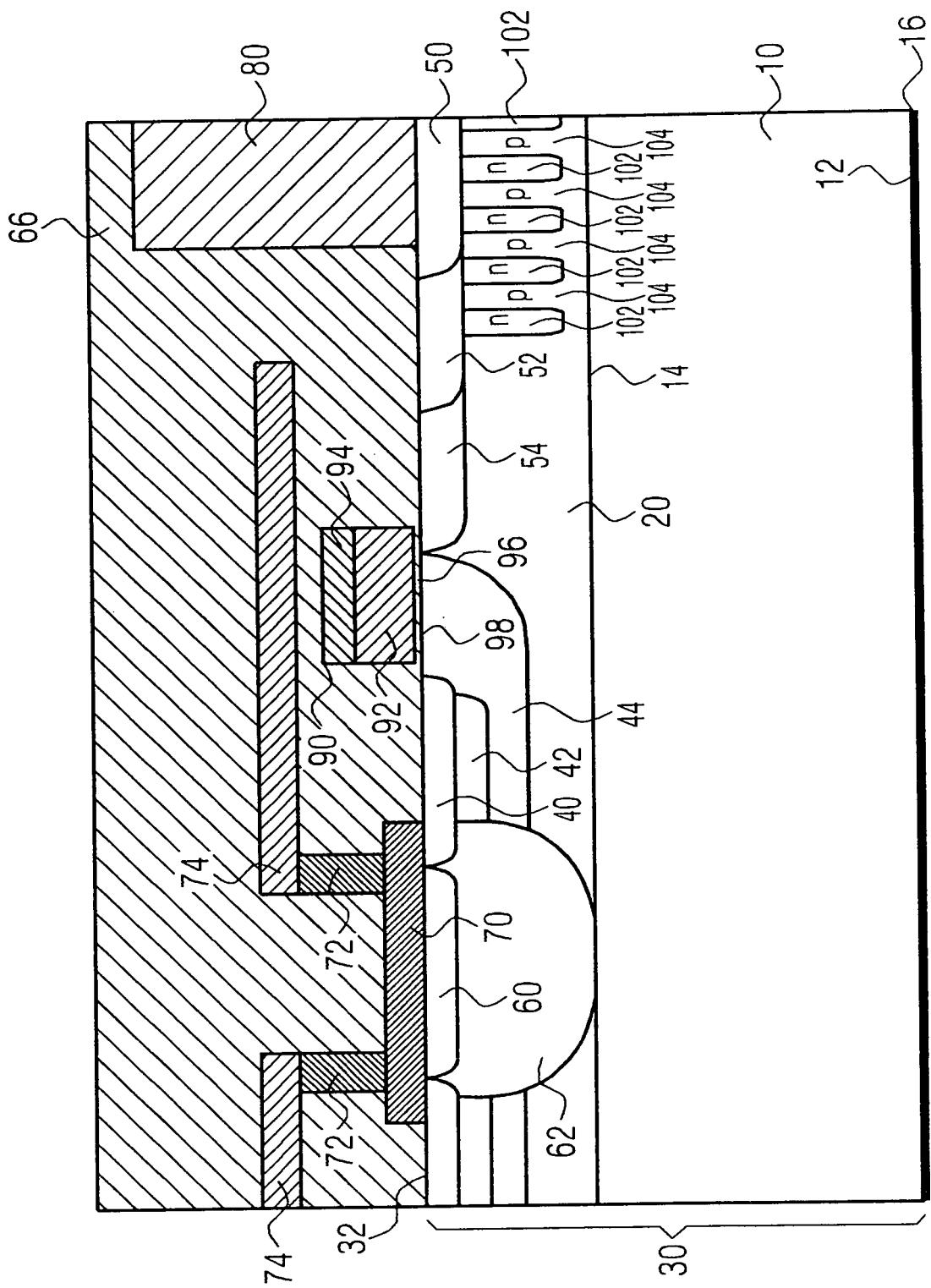

**[0003]** Fig. 3 ist eine schematische Darstellung eines vertikalen Schnitts durch einen herkömmlichen LDMOS-Feldeffekttransistor. Ein p-dotiertes Grundsubstrat **10** weist eine erste, untere Oberfläche **12** und eine zweite, obere Oberfläche **14** auf. An der unteren Oberfläche **12** weist das Grundsubstrat **10** einen Rückseitenkontakt in Form einer Metallbeschichtung **16** auf. Auf der oberen Oberfläche **14** des Grundsubstrats **10** ist mittels eines epitaktischen Verfahrens, beispielsweise mittels CVD-Epitaxie (CVD = chemical vapor deposition = chemische Dampfphasenabscheidung), eine p-dotierte Epitaxieschicht **20** erzeugt. Das Grundsubstrat **10** und die Epitaxieschicht **20** bilden zusammen ein Bauelementsubstrat **30** mit einer Oberfläche **32**, die gleichzeitig eine von dem Grundsubstrat **10** abgewandte Oberfläche der Epitaxieschicht **20** ist.

**[0004]** In bzw. auf der Epitaxieschicht **20** sind der Feldeffekttransistor bzw. seine Halbleiterfunktionselemente angeordnet. Ein Sourcebereich **40** wird durch einen n<sup>+</sup>-dotierten Bereich an bzw. direkt unter der Oberfläche **32** gebildet. An einer von der Oberfläche **32** abgewandten Seite des Sourcebereichs **40** schließt sich ein p-dotierter Enhance-Bereich **42** an. An einer von dem Sourcebereich **40** und der Oberfläche **32** abgewandten Seite des Enhance-Bereichs **42** schließt sich ein p-dotierter Body-Bereich **44** an, der jedoch im Gegensatz zum Enhance-Bereich **42** mindestens in einer Richtung eine größere Ausdehnung als der Sourcebereich **40** aufweist und damit auch seitlich bzw. lateral an den Sourcebereich **40** und den Enhance-Bereich **42** sowie an die Oberfläche **32** angrenzt.

**[0005]** Lateral von dem Sourcebereich **40** beabstandet, jedoch lateral an den Body-Bereich **44** angrenzend, ist an der Oberfläche **32** ein Drainbereich angeordnet, der in diesem Ausführungsbeispiel aus drei

Drainteilbereichen **50**, **52**, **54** mit unterschiedlich hoher Dotierungskonzentration gebildet ist. Ein erster Drainteilbereich **50**, der den größten Abstand zum Sourcebereich **40** aufweist, ist n<sup>+</sup>-dotiert. In Richtung zum Sourcebereich **40** schließt sich an den ersten Drainteilbereich **50** ein zweiter Drainteilbereich **52** an, dessen Dotierungskonzentration niedriger als die des ersten Drainteilbereichs **50** ist. An den zweiten Drainteilbereich **52** schließt sich ein dritter Drainteilbereich **54** an, der an den Body-Bereich **44** angrenzt und eine niedrigere Dotierungskonzentration aufweist als der zweite Drainteilbereich **52**. Der zweite Drainteilbereich **52** und der dritte Drainteilbereich **54** werden zusammen auch als Resurf-Bereich (Resurf = reduced surface field = reduziertes Oberflächenfeld) bezeichnet.

**[0006]** An eine vom Drainbereich **50**, **52**, **54** abgewandte Seite des Sourcebereichs **40** schließt sich ein p<sup>+</sup>-dotierter Bereich **60** an der Oberfläche **32** an. Zwischen dem p<sup>+</sup>-dotierten Bereich **60** und dem Grundsubstrat **10** bzw. dessen oberer Oberfläche **14** erstreckt sich ein p-dotierter Sinker **62**, der die elektrische Leitfähigkeit zwischen dem p<sup>+</sup>-dotierten Bereich **60** und dem Grundsubstrat **10** erhöht.

**[0007]** An einer von dem Sourcebereich **40**, dem Enhance-Bereich **42** und dem Body-Bereich **44** abgewandten Seite des p<sup>+</sup>-dotierten Bereichs **60** und des Sinkers **62** schließen sich lateral weitere Strukturen **40'**, **42'**, **44'** an, bei denen es sich beispielsweise um einen weiteren Sourcebereich, einen weiteren Enhance-Bereich und einen weiteren Body-Bereich oder aber um die in Form eines offenen oder geschlossenen Bogens oder Rahmens um den p<sup>+</sup>-dotierten Bereich **60** und den Sinker **62** lateral herumgeführten Sourcebereich **40**, Enhance-Bereich **42** und Body-Bereich **44** handelt.

**[0008]** Auf der Epitaxieschicht **20** sind eingebettet in eine Dielektrikumsschicht **66** elektrisch leitfähige Strukturen aus Metallen oder anderen elektrischen Leitern angeordnet. Eine Sourcemetallisierung **70** grenzt an den Sourcebereich **40** und den p<sup>+</sup>-dotierten Bereich **60** an und kontaktiert dieselben bzw. ist mit denselben elektrisch leitfähig verbunden. Durchgangsleiter **72** verbinden die Sourcemetallisierung **70** elektrisch leitfähig mit lateral überlappenden bzw. teilweise vertikal über der Sourcemetallisierung **70** angeordneten Abschirmleitern **74**, die Bestandteil einer darüberliegenden Metallisierungsebene sind.

**[0009]** Eine Drainmetallisierung **80** grenzt an den am höchsten dotierten ersten Drainteilbereich **50** und ist mit diesem elektrisch leitfähig verbunden.

**[0010]** Über dem Abschnitt des Body-Bereichs **44**, der an die Oberfläche **32** angrenzt, ist ein Gate **90** aus einer dotierten Polysiliziumschicht **92** und einer Silizidschicht **94** angeordnet. Das Gate **90** bzw. die

Polysiliziumschicht **92** desselben ist von der Oberfläche **32** bzw. von dem dem Gate **90** wesentlichen gegenüberliegenden Body-Bereich **44** durch eine dünne Isolierschicht **96** (Gateoxid) räumlich beabstandet und elektrisch isoliert.

**[0011]** Bei Anlegen einer positiven Spannung an das Gate **90** bildet sich in dem dem Gate **90** gegenüberliegenden Body-Bereich **44** nahe der Oberfläche **32** eine dünne leitfähige Schicht, der sogenannte Kanal, aus. Der Bereich, in dem sich der Kanal bei Anlegen der positiven Spannung ausbildet, wird im Folgenden als Kanalbereich **98** bezeichnet.

**[0012]** Zwischen dem Drainbereich **50, 52, 54** einerseits und angrenzenden Bereichen der Epitaxieschicht **20** andererseits liegt ein pn-Übergang vor. An diesem bildet sich eine Raumladungszone bzw. eine Verarmungszone aus, deren Dicke bzw. deren Ausdehnung senkrecht zu dem pn-Übergang von der Höhe der anliegenden Drainspannung bzw. von der Potentialdifferenz zwischen dem Drainbereich **50, 52, 54** einerseits und dem Substrat **10** andererseits abhängig ist. Der gesperrte pn-Übergang zwischen dem Drainbereich **50, 52, 54** und dem Substrat **10** bildet gleichzeitig einen Kondensator, dessen Kapazität von der Dicke der genannten Raumladungszone und damit von der Drainspannung abhängt.

**[0013]** Wie oben bereits erwähnt, erschwert die von der Drainspannung abhängige Ausgangskapazität bzw. Kapazität zwischen dem Drainbereich **50, 52, 54** und dem Substrat **10** die Anpassung einer Schaltung, die mit dem Feldeffekttransistor verbunden ist, an denselben. Bisher musste diese von der Drainspannung abhängige Ausgangskapazität des Feldeffekttransistors hingenommen werden.

**[0014]** Die DE 100 52 170 C2 betrifft ein Halbleiterbauelement mit einem Substrat, in dem ein MOS-Transistor gebildet ist. Dieser umfasst einen Drain-Bereich, zwei Source-Bereiche und zwei Gate-Elektroden. Zwischen dem Drain-Bereich und den unterhalb der Source- und Gate-Bereiche gebildeten Kanalzonen ist ein Driftbereich ausgebildet. Ferner ist eine n-Epitaxieschicht vorgesehen, in der eine Vielzahl von Gräben gebildet sind, die mit einem p-leitenden Material aufgefüllt sind.

**[0015]** Die DE 101 22 364 A1 und die DE 100 12 610 A1 beschreiben vertikale Transistorstrukturen, bei denen ein Drain-Bereich auf einer Rückseite eines Substrats gebildet ist, wobei sich lateral oder vertikal erstreckende Halbleiterbereiche wechselnden Leitungstyps zwischen einer Oberfläche des Substrats, in der der Source-Bereich gebildet ist, und dem Drain-Bereich angeordnet sind.

**[0016]** In dem Artikel „High voltage thin layer devices“ von J. A. Appels u. a. in IEEE, International

electronic device meeting 1979, Seiten 238–241 wird eine Resurf-Diode beschrieben.

**[0017]** Die Aufgabe der vorliegenden Erfindung besteht darin, einen Feldeffekttransistor mit einer von der Drainspannung unabhängigen Kapazität zwischen einem Drainbereich und einem Substrat zu schaffen.

**[0018]** Diese Aufgabe wird durch einen Feldeffekttransistor gemäß Anspruch 1 oder gemäß Anspruch 2 gelöst.

**[0019]** Gemäß einer bevorzugten Ausgestaltung schafft die vorliegende Erfindung einen Halbleiterchip mit dem erfindungsgemäßen Feldeffekttransistor.

**[0020]** Die vorliegende Erfindung beruht auf der Idee, unterhalb des Drainbereichs einen Bereich zu schaffen, der aufgrund seiner räumlichen Struktur bereits bei niedrigen Drainspannungen eine vollständige Verarmung innerhalb einer möglichst dicken, jedoch von der Drainspannung unabhängigen Schicht bewirkt, so dass bei höheren Drainspannungen keine oder keine wesentliche Veränderung der Dicke der Verarmungszone mehr auftritt. Dies wird beispielsweise dadurch erreicht, dass der Bereich eine oder mehrere Säulen oder Lamellen aufweist bzw. die Form einer oder mehrerer Säulen oder Lamellen mit einer Dotierung aufweist, deren Ladungsträgertyp gleich dem des Drainbereichs und zu dem des Substrats entgegengesetzt ist. Die Dicke der Säulen bzw. Lamellen und die Abmessungen der zwischen diesen verbleibenden Bereiche des entgegengesetzten dotierten Substrats sind so (klein) gewählt, dass bereits bei einer möglichst niedrigen Drainspannung Raumladungszenen erzeugt werden, welche die Säulen bzw. Lamellen und die Zwischenräume zwischen denselben vollständig erfüllen.

**[0021]** Ein wesentlicher Vorteil der vorliegenden Erfindung besteht darin, dass ab einer vorbestimmten minimalen Drainspannung, bei der die Raumladungszenen, wie erwähnt, sowohl die Säulen oder Lamellen des Bereichs als auch das Substratmaterial in deren Umgebung vollständig erfüllen, die räumliche Ausdehnung und insbesondere die Dicke dieser Verarmungszone im wesentlichen nur noch von der Geometrie dieser Säulen oder Lamellen und nicht mehr von der Drainspannung abhängt. Die Kapazität zwischen dem Drainbereich und dem Substrat ist dann von der Drainspannung weitgehend unabhängig. Dies ermöglicht eine einfache, unaufwendige und effiziente Hochfrequenzanpassung einer Schaltung, in der der erfindungsgemäße Feldeffekttransistor verwendet wird, an den Feldeffekttransistor.

**[0022]** Bevorzugte Weiterbildungen der vorliegenden Erfindung sind in den Unteransprüchen definiert.

**[0023]** Nachfolgend werden bevorzugte Ausführungsbeispiele der vorliegenden Erfindung mit Bezug auf die beiliegenden Figuren näher erläutert. Es zeigen:

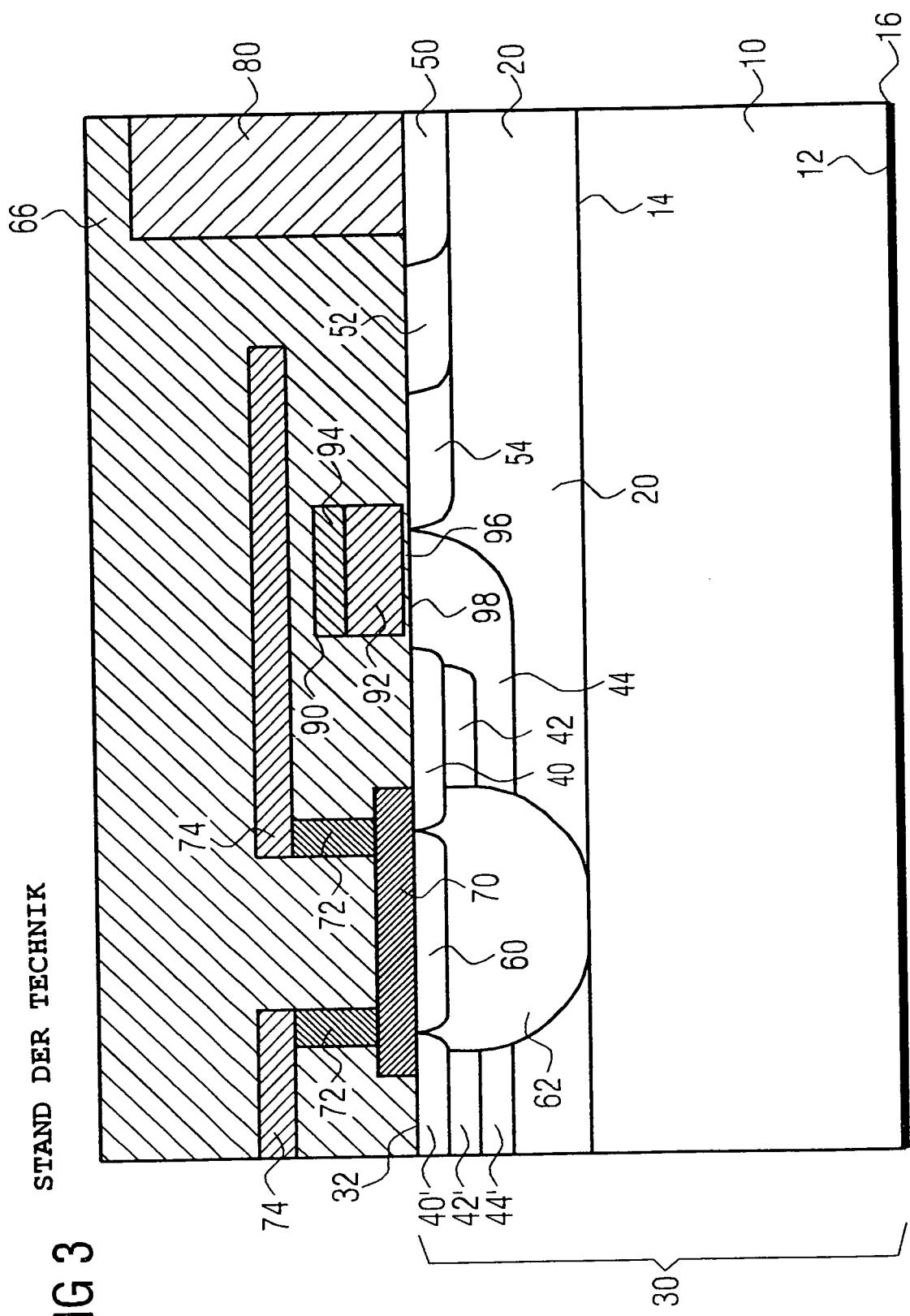

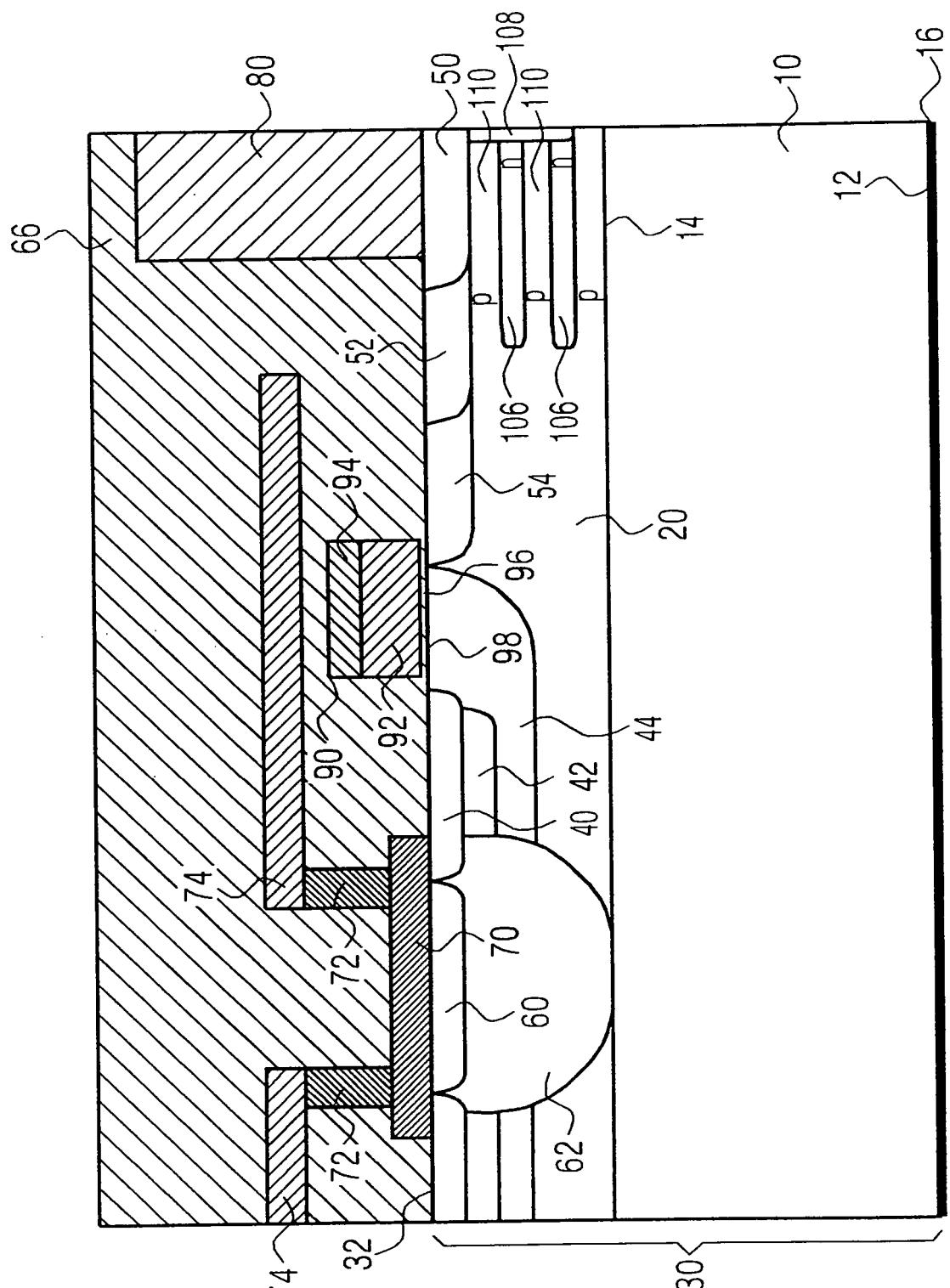

**[0024]** **Fig.** 1 ein schematische Schnittdarstellung eines Feldeffekttransistors gemäß einem ersten Ausführungsbeispiel der vorliegenden Erfindung;

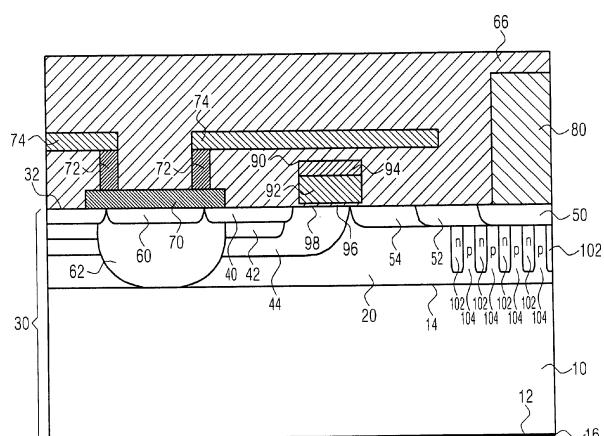

**[0025]** **Fig.** 2 eine schematische Schnittdarstellung eines Feldeffekttransistors gemäß einem zweiten Ausführungsbeispiels der vorliegenden Erfindung; und

**[0026]** **Fig.** 3 eine schematische Schnittdarstellung eines herkömmlichen Feldeffekttransistors.

**[0027]** **Fig.** 1 ist eine schematische Darstellung eines vertikalen Schnitts durch einen Feldeffekttransistor gemäß einem ersten bevorzugten Ausführungsbeispiel der vorliegenden Erfindung. Dieser Feldeffekttransistor unterscheidet sich von dem oben anhand der **Fig.** 3 beschriebenen herkömmlichen Feldeffekttransistor dadurch, dass unter dem Drainbereich **50, 52, 54** und insbesondere unter den beiden höherdotierten Drainteilbereichen **50, 52** ein Bereich aus einer Mehrzahl von Säulen **102** angeordnet ist, der wie der Drainbereich **50, 52, 54** n-dotiert ist. Die n-dotierten Säulen **102** sind senkrecht zu der Oberfläche **32** der Epitaxieschicht **20** angeordnet und grenzen unmittelbar an den Drainbereich **50, 52, 54** an, so dass sie mit demselben elektrisch leitfähig verbunden sind. Die Säulen **102** haben einen möglichst kleinen Durchmesser und einen möglichst kleinen gegenseitigen bzw. lateralen Abstand bzw. möglichst schmale Zwischenräume **104**. Dadurch wird bewirkt, dass beim Anlegen einer Drainspannung und damit beim Anlegen einer Spannung zwischen den n-dotierten Säulen **102** und dem sie umgebenden p-dotierten Material der Epitaxieschicht **20** in Sperrrichtung die von den Grenzflächen zwischen den Säulen **102** und dem umgebenden Material an der Epitaxieschicht ausgehenden Raumladungszonen möglichst schnell bzw. bei einer möglichst geringen Drainspannung die Säulen **102** und die Zwischenräume **104** zwischen den Säulen **102** vollständig ausfüllen.

**[0028]** Die Länge der Säulen **102** ist vorzugsweise so gewählt, dass sie einen geringen vertikalen Abstand von der oberen Oberfläche **14** des Grundsubstrats **10** aufweisen, der näherungsweise die gleiche Größe hat wie der Abstand zwischen den Säulen **102** und der Durchmesser der Säulen **102**. Beim Anlegen der oben beschriebenen minimalen Drainspannung wird damit die Epitaxieschicht **20** unter den am höchsten dotierten Drainteilbereichen **50, 52** vollständig verarmt. Wenn die Drainspannung ausgehend von der minimalen Drainspannung weiter erhöht wird, wächst die Verarmungszone nur noch minimal in vertikaler Richtung. Das von der Drainspannung ab-

hängige Wachstum der Verarmungszone wird ferner stark eingeschränkt, wenn das Grundsubstrat **10** eine hohe Dotierungskonzentration oder zumindest eine wesentlich höhere Dotierungskonzentration als die Epitaxieschicht **20** aufweist. Bei dem in **Fig.** 1 dargestellten Ausführungsbeispiel des erfindungsgemäß Feldeffekttransistors ist die Kapazität zwischen dem Drainbereich **50, 52, 54** und dem Substrat **10** somit näherungsweise die Kapazität eines entsprechenden Kondensators mit einem Plattenabstand, der weitestgehend unabhängig von der Drainspannung konstant ist und der Dicke der Epitaxieschicht **20** abzüglich der Dicke bzw. der vertikalen Abmessung des Drainbereichs **50, 52, 54** entspricht. Die Kapazität zwischen dem Drainbereich **50, 52, 54** und dem Substrat **10** ist somit klein und näherungsweise konstant.

**[0029]** Die vorliegende Erfindung bewirkt somit eine Nivellierung der Ausgangskapazität im Bereich der Sperrsicht und insbesondere im Bereich der Sperrsicht, die sich zwischen Drain und Substrat ausbildet.

**[0030]** Gemäß einer Variante des ersten Ausführungsbeispiels der vorliegenden Erfindung sind anstelle der Säulen **102** Lamellen bzw. Platten unterhalb des Drainbereichs **50, 52, 54** angeordnet, die an denselben angrenzen und sich in vertikaler Richtung näherungsweise bis zu der oberen Oberfläche **14** des Grundsubstrats **10** erstrecken. Die **Fig.** 1 kann auch so interpretiert werden, dass die sichtbaren Strukturen **102** Querschnittsflächen dieser Lamellen bzw. Platten sind. Anstelle mehrerer Lamellen oder Platten ist alternativ nur eine Lamelle vorgesehen sein, die lateral die Form einer Spirale aufweist.

**[0031]** **Fig.** 2 ist eine schematische Darstellung eines vertikalen Schnitts durch einen Feldeffekttransistor gemäß einem zweiten Ausführungsbeispiel der vorliegenden Erfindung. Das zweite Ausführungsbeispiel unterscheidet sich von dem anhand der **Fig.** 1 dargestellten ersten Ausführungsbeispiel dadurch, dass anstelle der vertikalen Säulen oder Lamellen bzw. Platten **102** horizontale bzw. parallel zu der Oberfläche **32** der Epitaxieschicht **20** angeordnete n-dotierte Säulen bzw. Stäbe oder Platten bzw. Lamellen **106** vorgesehen sind, die über einen weiteren n-dotierten, jedoch vertikal ausgerichteten, stab-, säulen-, platten- oder lamellenförmigen Verbindungsreich **108** mit dem Drainbereich **50, 52, 54** geometrisch und elektrisch leitfähig verbunden sind. Die Stäbe oder Platten **106** des zweiten Ausführungsbeispiels sowie Zwischenräume **110** zwischen denselben sind vorzugsweise ähnlich oder gleich dimensioniert wie die Säulen oder Lamellen **102** des ersten Ausführungsbeispiels und weisen dieselbe Funktion auf.

**[0032]** Den Ausführungsbeispielen aus den **Fig. 1** und **Fig. 2** ist gemein, dass der aus den Säulen, Stäben, Lamellen oder Platten gebildete Bereich **102**, **106**, **108** zumindest entlang einer Schnittebene einen kammförmigen Querschnitt aufweist. Bei der vertikalen Ausrichtung der Säulen oder Lamellen **102**, wie sie das anhand des **Fig. 1** dargestellte erste Ausführungsbeispiel aufweist, ist vorzugsweise eine Mehrzahl oder eine Vielzahl von Säulen oder Lamellen **102** oder aber eine einzige lateral spiralförmige Lamelle **102** vorgesehen, damit die erzeugte Verarmungszone eine möglichst große laterale Ausdehnung aufweist, die vorzugsweise näherungsweise der lateralen Ausdehnung zumindest der höherdotierten Drainbereiche **50**, **52** entspricht. Im Falle der horizontal ausgerichteten Strukturen des anhand der **Fig. 2** dargestellten zweiten Ausführungsbeispiels ist eine Platte **106** mit entsprechender lateraler Ausdehnung ausreichend, um die oben beschriebenen Vorteile der vorliegenden Erfindung zu realisieren. Eine Mehrzahl paralleler Platten **106** ist jedoch vorteilhaft, da sie eine entsprechend dickere Verarmungszone bewirkt. Eine einzelne horizontale bzw. zu der Oberfläche **32** parallele Platte **106** weist keinen kammförmigen Querschnitt auf. Beiden beschriebenen Ausführungsbeispielen und ihren Varianten ist jedoch gemein, dass sie eine alternierende Anordnung von Gebieten bzw. alternierende Gebiete mit entgegengesetzten Leitfähigkeitstypen erzeugen.

**[0033]** Ein Feldeffekttransistor gemäß der vorliegenden Erfindung wird vorzugsweise durch ein Verfahren hergestellt, dessen Verfahrensschritte teilweise einem herkömmlichen Herstellungsverfahren entsprechen. Insbesondere wird zunächst ein Grundsubstrat, beispielsweise ein monokristallines Siliziumsubstrat erzeugt, indem beispielsweise eine entsprechende Scheibe aus einem gezogenen Siliziumeinkristall geschnitten und ihre Oberflächen poliert werden. Auf die obere Oberfläche **14** des Grundsubstrats **10** wird die Epitaxieschicht **20** aufgewachsen. Die vertikal ausgerichteten Säulen oder Lamellen **102** des ersten Ausführungsbeispiels werden vorzugsweise erzeugt, indem in die fertiggestellte Epitaxieschicht **20** Löcher bzw. Gräben geätzt werden, die mit Silizium aufgefüllt werden, dessen Dotierung einen Leitfähigkeitstyp aufweist, der zum Leitfähigkeitstyp des Substrats **10** und insbesondere der Epitaxieschicht **20** entgegengesetzt ist. Alternativ wird zunächst nur eine Teilschicht der Epitaxieschicht **20** erzeugt, die den Bereich der zukünftigen Säulen bzw. Lamellen **102** umfasst. Nach dem Erzeugen der Säulen oder Lamellen **102** wird eine weitere Teilschicht der Epitaxieschicht **20** aufgebracht, in der später der Drainbereich **50**, **52**, **54** angeordnet sein wird.

**[0034]** Alternativ werden die Säulen oder Lamellen **102** nach dem Erzeugen der Epitaxieschicht **20** durch Implantation von Dotieratomen durch eine entsprechende Maske hindurch erzeugt.

**[0035]** Alternativ wird die Epitaxieschicht **20** in mehreren Teilschichten erzeugt, in denen jeweils Teilstücke der Säulen bzw. Lamellen **102** durch Implantation erzeugt werden, wobei diese Teilstücke lateral ausgerichtet sind und zusammen die Säulen bzw. Lamellen **102** bilden.

**[0036]** Horizontale Strukturen, wie sie in dem anhand der **Fig. 2** dargestellten zweiten Ausführungsbeispiel vorliegen, werden vorzugsweise erzeugt, indem die Epitaxieschicht **20** in mehreren Teilschichten aufgebracht wird, wobei die horizontalen Stäbe bzw. Balken oder Platten **106** durch Implantation von Dotieratomen oder durch Ätzen entsprechender Gräben oder Ausnehmungen und Auffüllen derselben mit dotiertem Silizium erzeugt werden.

**[0037]** Die Erzeugung des Drainbereichs **50**, **52**, **54**, des Sourcebereichs **40**, des Enhance-Bereichs **42**, des Body-Bereichs **44**, des p<sup>+</sup>-dotierten Bereichs **60** und des Sinkers **62** erfolgen vorzugsweise ebenso wie die Erzeugung der Leiterstrukturen **70**, **72**, **74**, **80** und des Gates **90** ähnlich wie bei herkömmlichen Feldeffekttransistoren.

**[0038]** Die vorliegende Erfindung wurde für einen LDMOS-Feldeffekttransistor mit n-dotierten Source- und Drainbereichen **40**, **50**, **52**, **54** und einem p-dotierten Body-Bereich **44** in einer p-dotierten Epitaxieschicht **20** auf einem p-dotierten Grundsubstrat **10** beschrieben. Die vorliegende Erfindung ist jedoch für alle Arten von Feldeffekttransistoren, insbesondere laterale Feldeffekttransistoren in allen Arten von Halbleitersubstraten mit und ohne Epitaxieschicht realisierbar.

## Patentansprüche

1. Feldeffekttransistor mit:

einem Substrat (**30**) mit einer Dotierung eines ersten Leitfähigkeitstyps;

einem Drainbereich (**50**, **52**, **54**) in dem Substrat (**30**) mit einer Dotierung eines zweiten, zu dem ersten Leitfähigkeitstyp entgegengesetzten Leitfähigkeitstyps;

einem Sourcebereich (**40**) in dem Substrat (**30**), der von dem Drainbereich (**50**, **52**, **54**) lateral beabstandet ist, mit einer Dotierung des zweiten Leitfähigkeitstyps;

einem Kanalbereich (**98**) in dem Substrat (**30**), der zwischen dem Sourcebereich (**40**) und dem Drainbereich (**50**, **52**, **54**) angeordnet ist; und

einer Mehrzahl von Abschnitten (**102**) mit einer Dotierung des zweiten Leitfähigkeitstyps, die mit dem Drainbereich (**50**, **52**, **54**) in elektrischem Kontakt sind und sich ausgehend von dem Drainbereich (**50**, **52**, **54**) in einer ersten Richtung senkrecht zu einer Oberfläche (**32**) des Substrats (**30**) in das Substrat (**30**) erstrecken, wobei die Abschnitte (**102**) in lateraler Richtung durch Zwischenräume (**104**), die unmittelbar an den Drainbereich (**50**, **52**, **54**) angrenzen und

eine Dotierung des ersten Leitfähigkeitstyps aufweisen, voneinander beabstandet sind, so dass unterhalb des Drainbereichs (50, 52, 54) in lateraler Richtung alternierend Gebiete (102, 104) mit dem ersten Leitfähigkeitstyp und mit dem zweiten Leitfähigkeitsotyp angeordnet sind,

wobei der Drainbereich einen hochdotierten Drainteilbereich (50) und einen niedrig dotierten Drainteilbereich (52, 54) mit einem oder mehreren Drainabschnitten aufweist, in dem oder in denen eine Dotierungskonzentration in Richtung zu dem Kanalbereich (98) kontinuierlich oder stufenweise abnimmt, und wobei die Abschnitte (102) nur unter dem hochdotierten Drainteilbereich (50) und dem niedrig dotierten Drainteilbereich (52, 54) angeordnet sind, so dass eine minimale Drainspannung, ab der sich eine Drain-Substrat-Kapazität nicht mehr ändert, reduziert ist.

2. Feldeffekttransistor mit:

einem Substrat (30) mit einer Dotierung eines ersten Leitfähigkeitstyps;

einem Drainbereich (50, 52, 54) in dem Substrat (30) mit einer Dotierung eines zweiten, zu dem ersten Leitfähigkeitstyp entgegengesetzten Leitfähigkeitstyps;

einem Sourcebereich (40) in dem Substrat (30), der von dem Drainbereich (50, 52, 54) lateral beabstandet ist, mit einer Dotierung des zweiten Leitfähigkeitsotyps;

einem Kanalbereich (98) in dem Substrat (30), der zwischen dem Sourcebereich (40) und dem Drainbereich (50, 52, 54) angeordnet ist;

einem Verbindungsabschnitt (108) mit einer Dotierung des zweiten Leitfähigkeitstyps, der mit dem Drainbereich (50, 52, 54) in elektrischem Kontakt ist und sich ausgehend von dem Drainbereich (50, 52, 54) in einer ersten Richtung senkrecht zu einer Oberfläche (32) des Substrats (30) in das Substrat (30) erstrecken; und

einer Mehrzahl von Abschnitten (106) mit einer Dotierung des zweiten Leitfähigkeitstyps, die mit dem Verbindungsabschnitt (108) in elektrischem Kontakt sind und sich ausgehend von dem Verbindungsabschnitt (108) in einer zweiten Richtung parallel zu der Oberfläche (32) des Substrats (30) unter den Drainbereich (50, 52, 54) erstrecken, wobei die Abschnitte (106) in der ersten Richtung voneinander durch Zwischenräume (110), die unmittelbar an den Verbindungsabschnitt (108) angrenzen und eine Dotierung des ersten Leitfähigkeitstyps aufweisen, beabstandet sind, so dass unterhalb des Drainbereichs (50, 52, 54) entlang der ersten Richtung ausgehend von dem Drainbereich (50, 52, 54) alternierend Gebiete mit dem ersten Leitfähigkeitstyp und mit dem zweiten Leitfähigkeitsotyp angeordnet sind,

wobei der Drainbereich einen hochdotierten Drainteilbereich (50) und einen niedrig dotierten Drainteilbereich (52, 54) mit einem oder mehreren Drainabschnitten aufweist, in dem oder in denen eine Dotierungskonzentration in Richtung zu dem Kanalbereich (98) kontinuierlich oder stufenweise abnimmt, und

wobei die Abschnitte (106) nur unter dem hochdotierten Drainteilbereich (50) und dem niedrig dotierten Drainteilbereich (52, 54) angeordnet sind, so dass eine minimale Drainspannung, ab der sich eine Drain-Substrat-Kapazität nicht mehr ändert, reduziert ist.

3. Feldeffekttransistor gemäß Anspruch 1 oder 2, bei dem die Mehrzahl der Abschnitte (102; 106) so ausgebildet ist, dass bei Anliegen einer vorbestimmten Drainspannung der an den Drainbereich (50, 52, 54) angrenzende Abschnitt des Substrats (30) vollständig verarmt.

4. Feldeffekttransistor gemäß einem der Ansprüche 1 bis 3, bei dem das Substrat (30) ein Grundsubstrat (10) mit einer Oberfläche (14) und eine auf die Oberfläche (14) des Grundsubstrats (10) epitaktisch aufgewachsene Epitaxieschicht (20) aufweist, wobei der Sourcebereich (40), der Drainbereich (50, 52, 54) und der Kanalbereich (98) in der Epitaxieschicht (20) angeordnet sind, und wobei die Mehrzahl der Abschnitte (102; 106) zwischen dem Drainbereich (50, 52, 54) und dem Grundsubstrat (10) angeordnet sind.

5. Feldeffekttransistor gemäß einem der Ansprüche 1 bis 4, wobei der Feldeffekttransistor ein LD-MOS-Feldeffekttransistor ist.

6. Halbleiterchip mit einem Feldeffekttransistor gemäß einem der Ansprüche 1 bis 5.

Es folgen 3 Seiten Zeichnungen

## Anhängende Zeichnungen

1

**FIG**

FIG 2

FIG 3

STAND DER TECHNIK