US 20060157079A1

### (19) United States (12) Patent Application Publication (10) Pub. No.: US 2006/0157079 A1

### (10) Pub. No.: US 2006/0157079 A1 (43) Pub. Date: Jul. 20, 2006

### Kim et al.

(54) METHOD FOR CLEANING SUBSTRATE SURFACE

(76) Inventors: Jeong-Ho Kim, Sungnam-shi (KR); Gil-Gwang Lee, Kwangmyung-shi (KR)

> Correspondence Address: HAYES, SOLOWAY P.C. 3450 E. SUNRISE DRIVE, SUITE 140 TUCSON, AZ 85718 (US)

- (21) Appl. No.: 11/385,391

- (22) Filed: Mar. 21, 2006

### **Related U.S. Application Data**

(60) Continuation of application No. 10/850,261, filed on May 20, 2004, which is a continuation-in-part of application No. 10/831,252, filed on Apr. 23, 2004, which is a division of application No. 10/038,553, filed on Jan. 4, 2002, now abandoned.

### (30) Foreign Application Priority Data

| Jan. 8, 2001  | (KR) |  |

|---------------|------|--|

| Dec. 14, 2001 | (KR) |  |

### **Publication Classification**

### (57) **ABSTRACT**

There is provided a surface cleaning apparatus and method using plasma to remove a native oxide layer, a chemical oxide layer, and a damaged portion from a silicon substrate surface, and contaminants from a metal surface. A mixture of  $H_2$  and  $N_2$  gas is used as a first processing gas. By absorbing potential in a grounded grid or baffle between a plasma generator and a substrate, only radicals are passed to the substrate, and HF gas is used as a second processing gas. Thus a native oxide layer, a chemical oxide layer, or a damaged portion formed on the silicon substrate during etching is removed in annealing step with  $H_2$  flow. The environment of a chamber is maintained constant by introducing a conditioning gas after each wafer process. Therefore, process repeatability is improved.

FIG. 1

## PRIOR ART

## PRIOR ART

.

.

FIG. 5A

FIG. 5D

Patent Application Publication Jul. 20, 2006 Sheet 7 of 11 US 2006/0157079 A1

FIG.6A

FIG.6B

1

### METHOD FOR CLEANING SUBSTRATE SURFACE

### CROSS REFERENCE TO RELATED APPLICATION

[0001] This application is a continuation of co-pending U.S. application Ser. No. 10/850,261, filed May 20, 2004, which is, in turn, a continuation-in-part of co-pending U.S. application Ser. No. 10/831,252, filed Apr. 23, 2004 which is, in turn, a divisional of U.S. application Ser. No. 10/038, 553, filed Jan. 4, 2002.

### PRIORITY

**[0002]** This application claims priority to an application entitled Method of Manufacturing Semiconductor Integrated Circuit and Apparatus Thereof filed in the Korean Industrial Property Office on Jan. 8, 2001 and assigned Serial No. 2001-1018, and to an application entitled Apparatus and Method for Dry Surface Cleaning Using Plasma filed in the Korean Industrial Property Office on Dec. 14, 2001 and assigned Serial No. 2001-79425, the contents of both of which are hereby incorporated by reference.

### BACKGROUND OF THE INVENTION

[0003] 1. Field of the Invention

**[0004]** The present invention relates generally to a surface cleaning apparatus and method using plasma, and in particular, to a surface cleaning apparatus and method for, using plasma, removing a native oxide layer resulting from reaction between oxygen in the air and a silicon, silicide or metal surface in fabrication of an integrated circuit such as semiconductor device or TFT (Thin Film Transistor) LCD (Liquid Crystal Display), an oxide layer chemically formed on the silicon surface during processing, a damaged portion on the silicon surface, or contaminants on the silicon surface and the sidewalls of a contact hole.

### [0005] 2. Description of the Related Art

[0006] In general, metalization is needed to connect devices formed on an underlying silicon substrate by a metal layer in fabrication of an integrated circuit such as a semiconductor, TFT LCD, or FPD (Flat Panel Display). Formation of a contact hole is requisite for the metalization. The contact hole is formed usually by dry-etching an oxide layer using plasma. In the course of forming the contact hole, the underlying silicon, silicide or metal surface is exposed. After the dry etch, a damaged portion is formed due to ion impact from the plasma, and contaminants including materials dissociated from etching gases and etched materials stick to a silicon surface and sidewalls. Because the damaged portion and contaminants may increase contact resistance or leakage current that is deadly adverse to device characteristics, they are removed by dry cleaning or wet cleaning during fabrication of an integrated circuit. Aside from the damaged portion and contaminants, a native oxide layer is formed due to reaction between oxygen in the air and the silicon, silicide or metal surface. Therefore, the native oxide layer should also be removed by dry cleaning or wet cleaning before deposition of a conductive material after the contact hole is formed.

[0007] In addition, an oxide layer can be chemically formed by reaction between the silicon surface and a mixed solution of  $H_2O_2$ ,  $HSO_4$ , and deionized water used for

post-etch processing. The oxide layer influences subsequent steps and deteriorates electrical connection characteristics, thereby degrading the characteristics of a resulting semiconductor or TFT LCD circuit.

**[0008]** Along with the decrease of CD (Critical Dimension) in an integrated circuit, a self-aligned contact (SAC) has recently been used widely. During an SAC etch, an etch stopper layer made of a silicon nitride layer is exposed. Thus, either sidewalls formed of a silicon oxide layer or the nitride layer should not be etched during surface cleaning in order to prevent short between an electrode surrounded by the nitride film and a conductive material filling the contact hole as well as minimizing leakage current.

**[0009]** Even if the silicon substrate surface underlying the contact hole is not closed, a gate, a polysilicon electrode for a capacitor, or a connection line can be exposed. In this case, a damaged portion, an oxide layer, or contaminants should be removed as in the case where the silicon substrate surface is exposed.

**[0010]** A metal is used for a gate electrode or bit lines of a memory when necessary. The top portion of the metal is exposed during etching a contact hole. Similarly, contaminants on the metal and sidewalls must be removed and much attention should be paid to the removal because etched metal components are contained in the contaminants and are difficult to remove.

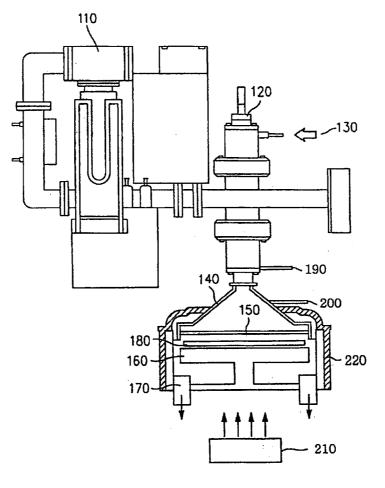

[0011] FIG. 1 is a schematic view of a conventional fluorine acid spray apparatus. Referring to FIG. 1, the conventional fluorine acid spray apparatus is comprised of a fluorine acid solution 10, a heating chamber 20, a substrate 30, a substrate mount 40, a fluorine solution tank 50 filled with a fluorine acid solution 60, and fluorine acid supply pipes 70 and 80. To prevent formation of a native oxide layer, oxygen is preliminarily removed by forming a fluorine layer on a silicon surface to react with the oxygen. Specifically, a fluorine acid layer is formed on a silicon surface by generating fluorine acid vapor using the fluorine acid spray apparatus and hardened by heat. Oxygen introduced into an etching device to etch the fluorine acid layer-having substrate or oxygen remaining in the etching device reacts chemically with the fluorine acid layer on the surface of the substrate and thus the oxygen is removed.

**[0012]** Despite the advantage of simplicity in device configuration and concept, however, the above conventional technology has a shortcoming in that it is difficult to effectively control fine process parameters.

**[0013]** UV (UltraViolet) light and ozone  $(O_3)$  can be used for surface cleaning. That is, a silicon surface is oxidized by reaction between silicon and  $O_3$  dissociated by UV light and the oxide layer is removed by wet etch. However, oxidation takes a long time, leading to slow processing accurately.

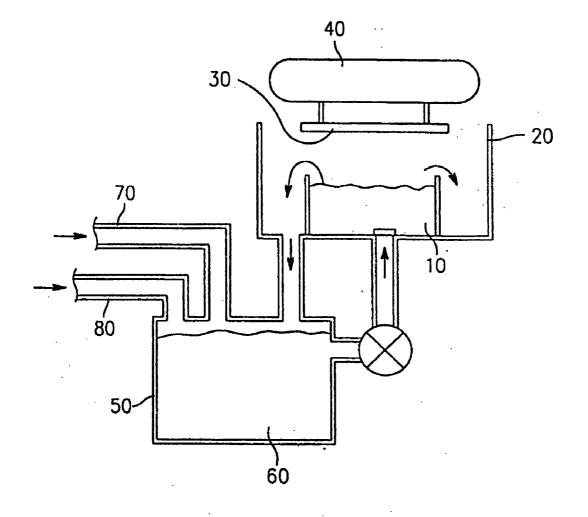

[0014] FIG. 2 is a schematic view of a conventional plasma etching apparatus. plasma is generated in a plasma generator 100 by introducing  $H_2$  and  $N_2$  through a first processing gas inlet 90 and then NF<sub>3</sub> is introduced through a second processing gas inlet 110, thereby etching a silicon substrate 120 in a chamber 140 with gases exhausted through an outlet 130.

[0015] The  $NF_3$  gas as a main processing gas accelerates plasma dissociation and activation, so that excess fluorine

atoms and ions involved in the etching are generated. As a result, the silicon surface is over-etched deeper than a damaged portion, or a BPSG (Borophosphosilicate glass) oxide layer or a nitride layer that must avoid etching may also be etched. This is due to a a low selection ratio between native oxide etch rate and etch rate of silicon, BPSG or nitride when NF<sub>3</sub> is used.

**[0016]** Another feature in which an inert gas such as Ar as a first processing gas shows a slow etch rate.

**[0017]** Therefore, it is required to provide improved cleaning method other than a conventional wet or dry etching method as described above.

### SUMMARY OF THE INVENTION

**[0018]** It is, therefore, an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing a native oxide layer or a chemical oxide layer formed on a silicon surface before growth of a gate oxide layer for the purpose of preventing deterioration of the characteristics of the gate oxide layer.

**[0019]** It is also an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing a native oxide layer/a chemical oxide layer, a damaged portion, and contaminants from a silicon surface exposed during etching an oxide layer before salicidation (CoSi or NiSi formation) in order to prevent the increase of contact resistance and leakage current.

**[0020]** It is also an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing a native oxide layer/a chemical oxide layer, a damaged portion, and contaminants from a silicon surface exposed during etching an oxide layer for formation of a contact hole in order to prevent the increase of contact resistance and leakage current.

**[0021]** It is also an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing a native oxide layer and contaminants from a silicide surface exposed during etching a oxide layer for formation of a contact hole in order to prevent the increase of contact resistance and leakage current.

**[0022]** It is also an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing contaminants such as polymers on the sidewalls of a contact hole and the upper surface of an underlying metal layer when the contact hole is etched for connection to the metal layer.

**[0023]** It is also an object of the present invention to provide a surface cleaning apparatus and method using plasma, for removing a native oxide layer/a chemical oxide layer, a damaged portion, and contaminants from an etched silicon surface before the formation of STI (shallow trench insulation) in order to prevent the increase of leakage current.

**[0024]** It is a further object of the present invention to provide a surface cleaning apparatus and method using plasma, for growing good quality epitaxial silicon by removing a native oxide layer or a chemical oxide layer from a silicon surface prior to the epitaxial silicon growing process in fabrication of an integrated circuit.

**[0025]** It is still another object of the present invention to provide a surface cleaning apparatus and method using plasma, for growing good quality hemispherical grains (HSGs) by removing a native oxide layer or a chemical oxide layer from an underlying silicon surface in an HSG silicon formation process.

**[0026]** It is yet another object of the present invention to provide a surface cleaning apparatus and method using plasma, for improving process uniformity.

**[0027]** The foregoing and other objects of the present invention can be achieved by providing a surface cleaning apparatus and method using plasma. According to one aspect of the present invention, the surface cleaning apparatus using plasma has a chamber that can be maintained in a vacuum state, a substrate mount in the chamber, for mounting a silicon substrate, a first processing gas inlet for introducing a carrier gas into the chamber to generate and maintain plasma, a plasma generator for forming plasma out of the first processing gas, a filter between the plasma generator and the substrate mount, for passing only radicals to the substrate, and a second processing gas inlet between the plasma generator and the filter, for introducing a second processing gas into the chamber.

**[0028]** Preferably, the plasma generator uses a microwave generator as an energy source for plasma generation.

[0029] Preferably, a wall heat jacket is also provided for maintaining the walls of the chamber at a predetermined temperature to concentrate the radicals on the surface of the substrate to achieve a high etch rate by preventing deposition of the radicals and formation of a byproduct layer with the radicals. Particularly, chamber wall temperature between  $50^{\circ}$  C. and  $120^{\circ}$  C. makes surface cleaning speed 2-3 times more than normal cleaning environments.

**[0030]** Preferably, the filter is grounded, or a grid or baffle with a square-wave or sine-wave AC (alternating current) voltage applied is used as the filter.

**[0031]** More preferably, a third processing gas inlet is further provided for introducing a conditioning gas into the chamber to maintain a constant and controlled environment of the chamber after processing each wafer.

**[0032]** According to another aspect of the present invention, in the surface cleaning method using plasma, for removing a damaged portion and an unwanted oxide layer formed during etching for a contact hole on a silicon substrate having at least one layer including an insulation layer, a polymer layer is first formed on the oxide layer. The polymer layer and the oxide layer are removed by annealing wherein the components of the polymer layer are decomposed and combined with the components of the oxide layer and excited and removed, and the damaged portion of the surface of the silicon substrate is removed.

[0033] Preferably, in the polymer layer formation step, plasma is formed by introducing a first processing gas containing  $H_2$  and  $N_2$ , only radicals are passed to the silicon substrate by filtering the plasma, and a second processing gas containing a halogen element is introduced.

[0034] Preferably, the second processing gas is HF.

**[0035]** Preferably, the polymer layer and the oxide layer are removed by annealing using a UV lamp or IR lamp, or by annealing in a heat chamber.

[0036] Preferably, the annealing gas is  $H_2$ . Flow of  $H_2$  during annealing reduces time to remove the polymer layer and the oxide layer and at the same time passivates the surface of silicon, silicide or metal with hydrogen bonds, which extends the allowable time period prior to subsequent step. Preferable flow rate of  $H_2$  is 10 sccm and 5,000 sccm.

**[0037]** Preferably, the damaged portion of the silicon substrate surface is removed by annealing in a heat chamber.

**[0038]** More preferably, the damaged portion removal step is performed in-situ in the same chamber as the polymer layer and the oxide layer are removed.

**[0039]** According to a further aspect of the present invention, in the surface cleaning method using plasma for fabrication of an integrated circuit in a surface cleaning apparatus having a chamber that can be maintained in a vacuum state, a substrate mount for mounting a silicon substrate, a first processing gas inlet for introducing a carrier gas for generation and maintenance of plasma, a plasma generator, a filter for passing only radicals to the substrate, and a second processing gas inlet, the first processing gas is introduced into the chamber, plasma is formed out of the first processing gas is introduced into the chamber, and then a third processing gas is introduced into the chamber, and then a third processing gas is introduced into the chamber to maintain the environment of the chamber constant after processing each wafer.

[0040] Preferably, the first processing gas contains  $H_2$  and  $N_2$ .

**[0041]** Preferably, the filter is grounded or receives an AC voltage.

**[0042]** Preferably, the second processing gas contains a halogen element.

[0043] More preferably, the second processing gas is HF.

**[0044]** Preferably, the third processing gas contains at least one of H, F, O and N containing gas.

[0045] Preferably, the annealing gas is at least one of  $H_2$ ,  $N_2$  or Ar.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0046]** The above and other objects, features and advantages of the present invention will become more apparent from the following detailed description when taken in conjunction with the accompanying drawings in which:

**[0047] FIG. 1** is a schematic view of a conventional fluorine acid spray device;

**[0048] FIG. 2** is a schematic view of a conventional plasma etching apparatus:

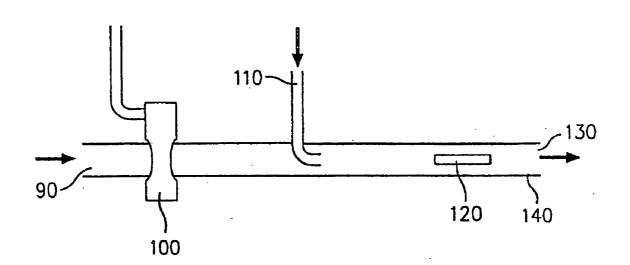

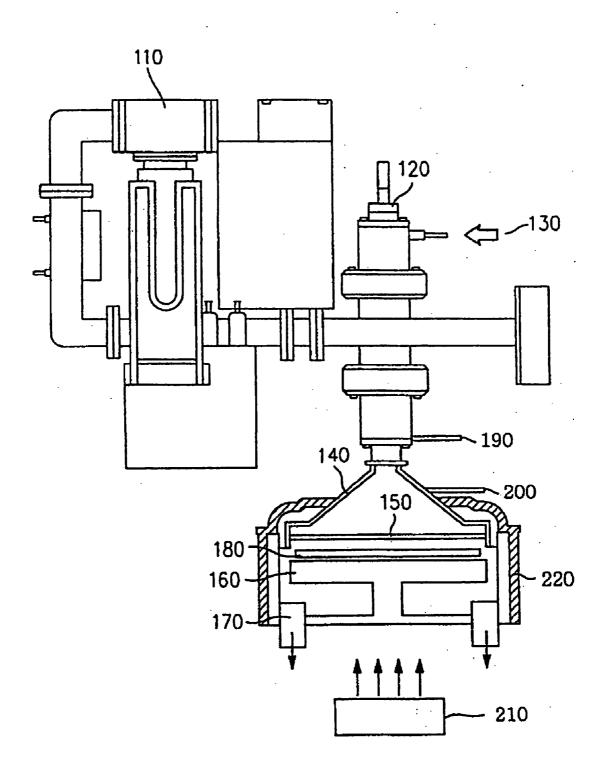

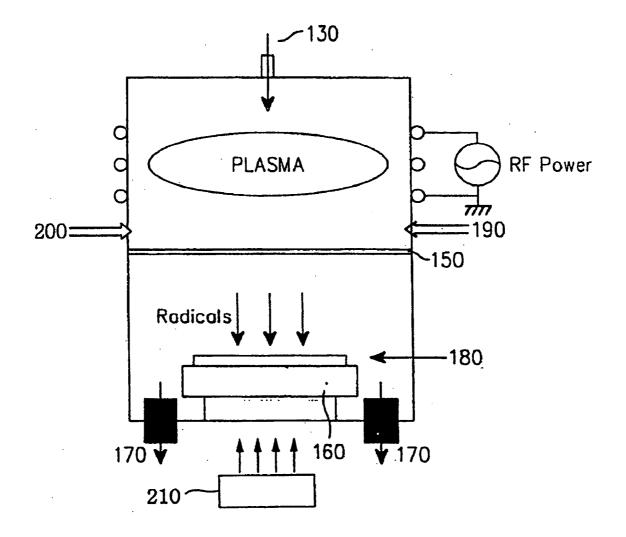

**[0049] FIG. 3** is a schematic view of an embodiment of plasma etching apparatus according to the present invention;

**[0050] FIG. 4** is a schematic view of another embodiment of the plasma etching apparatus according to the present invention;

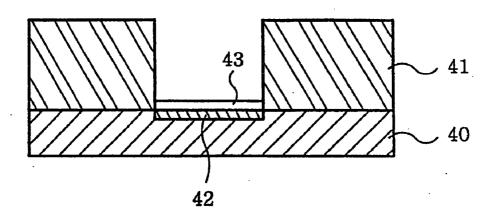

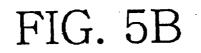

**[0051] FIGS. 5A** to **5**E are sectional views sequentially illustrating an embodiment of a process of removing a native oxide layer and a damaged portion of a silicon substrate surface; and

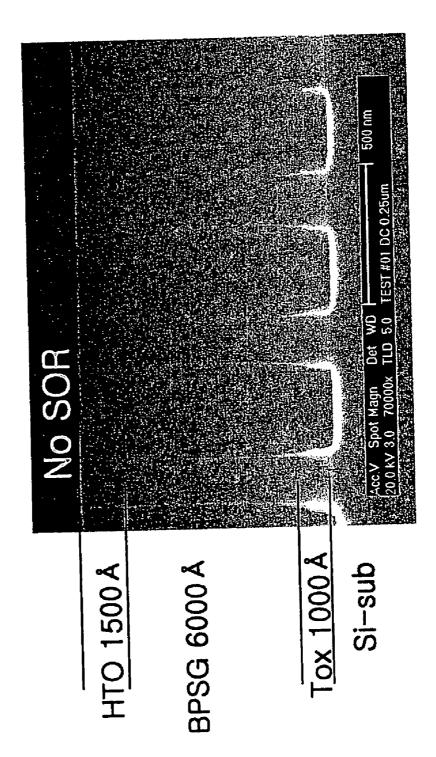

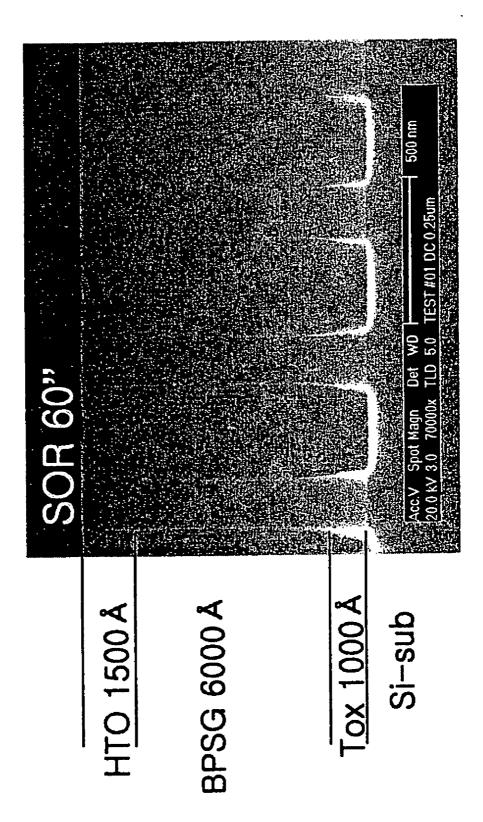

**[0052] FIGS. 6A and 6B** are SEM (Scanning Electro Microscope) images illustrating contact profiles.

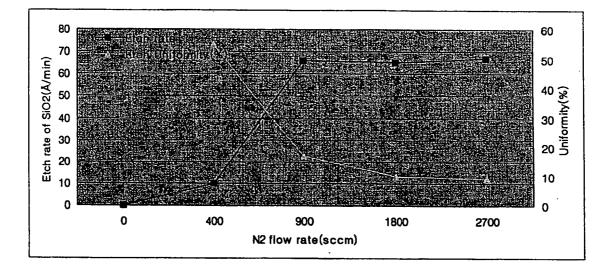

**[0053]** FIG. 7 is a graph illustrating etch rate and uniformity according to a  $N_2$  flow rate at constant  $H_2$  flow rate.

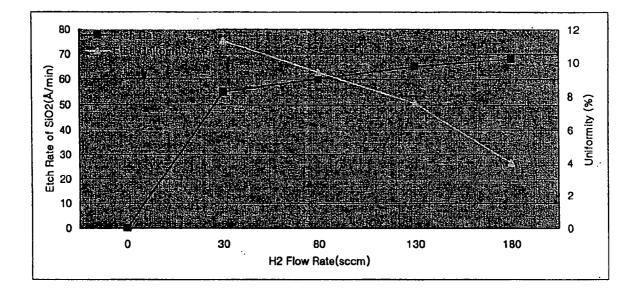

[0054] FIG. 8 is a graph illustrating etch rate and uniformity according to a  $H_2$  flow rate at constant  $N_2$  flow rate.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

**[0055]** Preferred embodiments of the present invention will be described herein below with reference to the accompanying drawings. In the following description, well-known functions or constructions are not described in detail since they would obscure the invention in unnecessary detail.

[0056] FIG. 3 illustrates the structure of an embodiment of plasma etching apparatus according to the present invention. The plasma etching apparatus performs dry cleaning using a microwave plasma. Referring to FIG. 3, after a silicon substrate 180 is mounted on a substrate mount 160 under a chamber 140 that can be maintained in a vacuum state, a mixture gas of N2 and H2 is introduced through a first processing gas inlet 130. The mixture gas of  $N_2$  and  $H_2$ serves as a carrier gas for generating and maintaining plasma. Subsequently, plasma is generated by operating a microwave source module 110 and a plasma applicator 120 and HF gas is introduced through a second processing gas inlet 190. A fluorine-containing halogen element, or a halogen compound such as HCl, BCl<sub>3</sub>, or ClF<sub>3</sub> may be a substitute for HF. The plasma passes through a filter 150, while moving down toward the substrate 180. The filter 150, being a grounded baffle or grid, absorbs potential so that only radicals reach the silicon substrate 180. A heater 210 for annealing, where in the damaged portion of the silicon substrate surface is removed by annealing in a heat chamber. A wall heat jacket 220 maintains the walls of the chamber 140 at an appropriate temperature to prevent the radicals from sticking to the walls of the chamber 140 and forming a byproduct layer and to concentrate the radicals on the surface of the silicon substrate for a high etch rate 180. H, O, N or F containing gas as a conditioning gas is introduced through a third processing gas inlet 200 to maintain the environment inside the chamber 140 constant and thus increase etch reproducibility after etching. The conditioning gas is H, F, O or N containing gas, or a mixture of the gases.

[0057] The used processing gases are exhausted through an outlet **170**.

**[0058] FIG. 4** illustrates the structure of another embodiment of the plasma etching apparatus according to the present invention. The plasma etching apparatus performs dry cleaning using a remote plasma. Referring to **FIG. 4**, this plasma etching apparatus is similar to the plasma etching apparatus using a microwave plasma except that RF power is supplied to generate plasma. The plasma etching apparatus is well known to those skilled in the field and thus its description is avoided here.

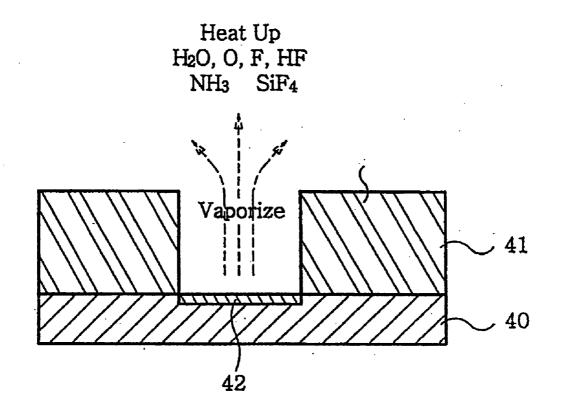

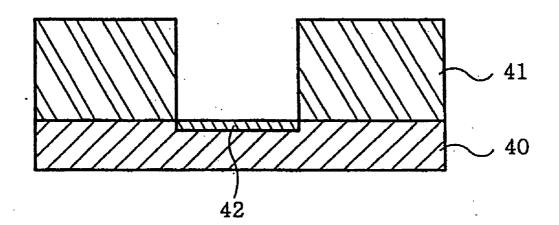

**[0059] FIGS. 5A** to **5**E are sectional views sequentially illustrating a process of removing a native oxide layer and a damaged portion of a silicon substrate surface according to an embodiment of the present invention.

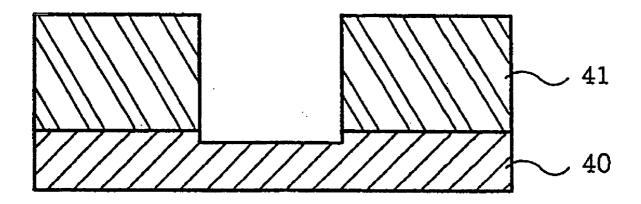

[0060] FIG. 5A illustrates the step of forming an interlayer insulation layer 41 on a silicon substrate 40 and then forming a contact hole by etching the interlayer insulation layer 41 in a contact area. The surface of the silicon substrate 40 exposed in the contact area is damaged during the etching. As a result, a damaged portion 42 and a native oxide layer 43 are sequentially formed on the silicon substrate 40. Since the native oxide layer 43 and the damaged portion 42 increase contact resistance or leakage current and as a result, deteriorates device characteristics, they must be removed.

[0061] FIG. 5B illustrates the step of forming an NxHyFz polymer layer 44 or a byproduct on the native oxide layer 43, the interlayer insulation layer 41 and the sidewalls of a contact hole using plasma generated out of  $H_2$  and  $N_2$  gas, and HF gas as a second processing gas. By grounding a grid or baffle for filtering the plasma, or applying AC voltage, only radicals in the plasma reach the substrate surface.

**[0062] FIG. 5C** illustrates the step of removing the polymer layer **44** by annealing. As the components of the polymer layer **44** are decomposed by annealing, the decomposed component are combined with the components of the underlying native oxide layer **43** to form  $N_2O$ , F, HF, NH<sub>3</sub>, SiF<sub>4</sub>, etc and then removed. Annealing temperature is between 120 and 400° C. Preferably, the annealing gas is at least one of H<sub>2</sub>, N<sub>2</sub> or Ar. Particularly, annealing using H<sub>2</sub> gas terminates Si substrate surface. Instead of heat annealing, the polymer layer or byproduct can be removed by annealing using a UV lamp or IR (InfraRed) lamp radiation.

**[0063] FIG. 5D** illustrates the step of performing hydrophobic cleaning on the silicon substrate surface after the native oxide layer **43** is removed by annealing.

**[0064] FIG. 5E** illustrates the step of removing the silicon damaged portion **42** in-situ in the same chamber. The silicon damaged portion **42** can be removed using a remote plasma of at least one of HF/H<sub>2</sub>, HF/O<sub>2</sub>, NF<sub>3</sub>/O<sub>2</sub>, SF<sub>6</sub>/O<sub>2</sub>, and CF<sub>4</sub>/O<sub>2</sub> or appropriately combining a gas such as NF<sub>3</sub>, CF<sub>4</sub>, and C<sub>2</sub>F<sub>2</sub>, a gas such as O<sub>2</sub>, CO<sub>2</sub>, NO<sub>2</sub>, and N<sub>2</sub>, and an inert gas such as He, Ne, Xe, and Ar. When removing the silicon damaged portion of a silicon substrate caused during processing including metal etching such as etching for formation of a metal contact window, it is more effective to use a remote plasma including Cl, like HCl, ClF<sub>3</sub> and so on.

**[0065]** A table shown below is a comparison between the present invention using HF as a second processing gas and the conventional technology using NF<sub>3</sub> as a second processing gas when a mixture gas of  $H_2$  and  $N_2$ . is a first processing gas. As seen from the table, the present invention is much improved in etch rate (Å/min), silicon substrate roughness (RMS: nm), and metal contamination.

| Items<br>Etch Rate (Å/min) |    | HF       | NF <sub>3</sub> | Reference |

|----------------------------|----|----------|-----------------|-----------|

|                            |    | 42       | 30              | _         |

| Selectivity of Oxide to    |    | >8       | >6              |           |

| Nitride (or Si-sub)        |    |          |                 |           |

| SI Surface Roughness       |    | 0.2803   | 0.3623          | 0.1043    |

| (RMS: nm)                  |    |          |                 |           |

| Metal                      | Al | 7.91E+10 | 4.38E+12        | 3.44E+09  |

| Contamination              | Cr | 1.79E+09 | 5.36E+09        | 1.79E+09  |

| (/cm <sup>3</sup> )        | Fe | 3.98E+10 | 1.43E+11        | 1.66E+09  |

|                            | Ni | 1.60E+09 | 9.61E+09        | 1.60E+09  |

[0066] FIG. 6A illustrates a contact profile before removing a native oxide layer and FIG. 6B illustrates a contact profile during processing the native oxide layer for 60 seconds. There are little changes in the contact profiles in terms of CD and substrate damage.

[0067] FIG. 7 is a graph illustrating etch rate and uniformity according to a  $N_2$  flow rate at constant  $H_2$  flow rate. Here, a gas pressure is 5 Torr and Microwave power is at 600 W and a flow rate of  $H_2$  is 30 sccm (standard cubic centimeter per minute) and a flow rate of HF (second processing gas) is 48 sccm. If  $N_2$  flow is zero, an etch rate of SiO<sub>2</sub> (Å/min) is negligible. An etch rate of SiO<sub>2</sub> (Å/min) increases as  $N_2$  flow rate increases. After  $N_2$  flow rate reaches 900 sccm, an etch rate is saturated. Similar trends can be found from pressure in the range of 0.1 Torr to 50 Torr, Microwave power in the range of 100 W to 2000 W, HF flow in the range of 5 sccm to 500 sccm. Uniformity improves as  $N_2$  flow rate increases and at 1,800 sccm of  $N_2$  flow rate it is about 10% with the current process kit.

**[0068] FIG. 8** is a graph illustrating etch rate and uniformity according to a  $H_2$  flow rate at constant  $N_2$  flow rate. Here, a gas pressure is 5 Torr and Microwave power is at 600 W and a flow rate of  $N_2$  is 1,800 sccm (standard cubic centimeter per minute) and a flow rate of HF (second processing gas) is 48 sccm. If there is no  $H_2$  flow, an etch rate of SiO<sub>2</sub> (Å/min) is negligible. An etch rate of SiO<sub>2</sub> (Å/min) increases as  $N_2$  flow rate increases. Similar trends can be found from pressure in the range of 0.1 Torr to 50 Torr, Microwave power in the range of 100 W to 2000 W, HF flow in the range of 5 sccm to 500 sccm. Uniformity improves as  $H_2$  flow rate increases with the current process kit.

**[0069]** Out of **FIG. 7** and **FIG. 8**, it is found that in order to obtain greater than 50 (Å/min) etch rate of  $SiO_2$  a combination of at least 500 sccm flow rate of  $N_2$  and at least a 20 sccm flow rate of  $H_2$  is preferable.

[0070] Particularly, surface cleaning speed 2-3 times more than normal cleaning environments is acquired by maintaining chamber wall temperature between  $50^{\circ}$  C. and  $120^{\circ}$  C. during whole cleaning process including a step of plasma generating, polymer forming and annealing. Maintaining the chamber wall temperature between  $50^{\circ}$  C. and  $120^{\circ}$  C. during whole cleaning process also prevents the formation of contaminant particles on wall.

[0071] In accordance with the present invention as described above, (1) deterioration of the characteristics of a gate oxide layer is prevented by removing a native oxide layer or a chemical oxide layer formed on a silicon surface before growth of the gate oxide layer; (2) the increase of contact resistance and leakage at a contact are prevented by removing a native oxide layer or a chemical oxide layer formed on a silicon surface exposed after etching for a contact hole and a portion of the silicon surface damaged during etching; (3) metal contact resistance is reduced by removing organic contaminants such as polymers existing at the boundary between the sidewalls of a contact and an underlying metal during etching the metal contact hole; (4) good quality epitaxial silicon is grown by removing a native oxide layer or a chemical oxide layer from a silicon surface in an epitaxial silicon growing process; (5) good quality HSGs are grown by removing a native oxide layer or a chemical oxide layer from a silicon surface in an HSG silicon forming process; and (6) process uniformity is improved by introducing a conditioning gas after processing each wafer and thus maintaining the environment of a chamber constant.

**[0072]** While the invention has been shown and described with reference to certain preferred embodiments thereof, it will be understood by those skilled in the art that various changes in form and details may be made therein without departing from the spirit and scope of the invention as defined by the appended claims.

1-22. (canceled)

**23**. A method for cleaning native oxides, chemical oxides or damaged portions thereon off a surface of a substrate using plasma, the method comprising the steps in sequence of:

- A. introducing a first processing gas which is a mixture of H<sub>2</sub> and N<sub>2</sub> gas into a first inlet of a cleaning apparatus;

- B. generating and maintaining a plasma of said first processing gas in a plasma generating space in said cleaning apparatus.

- C. adding a second processing gas of HF gas into a second inlet in said cleaning apparatus in which said second gas is activated to HF radicals by said plasma of first gas;

- D. forming a polymer layer of NxHyFz that is a byproduct of said first gas, said second gas and said materials on said surface of said substrate; and

- E. removing said polymer layer by annealing said substrate to clean said surface of said substrate.

**24**. The method of claim 23, wherein  $H_2$  is used as an annealing gas in step E.

**25**. The method of claim 23, wherein said  $H_2$  gas is introduced in step A at a flow rate of above 20 sccm, said  $N_2$  gas is introduced in step A at a flow rate of above 500 sccm, and said plasma is generated using Microwave power in the range of 100 W to 2000 W.

**26**. The method of claim 25, wherein said HF gas is introduced in step C at a flow rate of 5 sccm to 500 sccm.

**27**. The method of claim 23, wherein gas pressure of said first processing gas is maintained in a range of 0.1 Torr to 50 Torr.

**28**. The method of claim 23, wherein said annealing is performed using a UV lamp or IR lamp.

**29**. The method of claim 23, wherein a gas pressure of 0.1 Torr to 50 Torr is maintained in step A.

**30**. The method of claim 23, wherein a wall temperature of said cleaning apparatus is maintained at between 50° C. and 120° C.

**31**. The method of claim 23, wherein  $H_2$ ,  $N_2$  or Ar is used as an annealing gas in step E.

**32**. The method of claim 23, wherein said annealing step E is performed with a flow of  $H_2$  gas at 10 sccm and 5,000 sccm at a temperature between 120° C. and 400° C.

**33**. A surface cleaning method using plasma for removing a native oxide layer formed on a semiconductor substrate during an etching process in which a contact hole is formed in a semiconductor substrate having at least one layer including an insulation layer, the method comprising the steps in sequence of:

- A. generating a plasma from a first processing gas which is a mixture of  $H_2$  and  $N_2$ ;

- B. introducing HF gas into said plasma;

- C. contacting said semiconductor substrate with said plasma from step B whereby to form a polymer layer of

NxHyFz on said insulation layer and said native oxide layer formed on said substrate; and

D. removing said polymer layer and said natural oxide layer by annealing wherein components of said polymer layer are decomposed and combined with the components of said natural oxide layer and removed.

34. The method of claim 33, wherein said annealing step

D is performed using  $H_2$ ,  $N_2$  or Ar as an annealing gas.

**35**. The method of claim 33, wherein said annealing step D is performed with a flow of  $H_2$  at 10 sccm and 5,000 sccm at temperature between 120° C. and 400° C.

**36**. The method of claim 33, wherein said method is performed in a cleaning apparatus in which a wall thereof is maintained at a temperature of between  $50^{\circ}$  C. and  $120^{\circ}$  C.

**37**. A surface cleaning method for cleaning native oxides off a surface of a silicon substrate wafers used for fabrication of an integrated circuit in a surface cleaning apparatus having a chamber that can be maintained in a vacuum state, a substrate mount for mounting said silicon substrate, a first processing gas inlet for introducing a first processing gas inlet for he substrate, a second processing gas inlet for introducing a silicon the apparatus, and a third processing gas inlet for introducing a third processing gas into the apparatus to maintain the environment of the chamber constant after processing each wafer, the method comprising the steps in sequence of:

- A. introducing a first processing gas of a mixture of  $H_2$ and  $N_2$  into said chamber via said first processing gas inlet;

- B. forming plasma of said first processing gas using the plasma generator;

- C. introducing a second processing gas of HF into said chamber via said second processing gas inlet;

- D. forming on said surface of said substrate a polymer layer of NxHyFz that is a by-product of said first gas, said second gas and materials of a surface of said substrate;

- E. removing said polymer layer and said natural oxide layer by annealing wherein components of said polymer layer are decomposed and combined with components of said natural oxide layer and removed; and

- F. introducing said third processing gas into said chamber to maintain the environment of said chamber.

**38**. The method of claim 37, wherein said  $H_2$  gas is introduced in step A at a flow rate above 20 sccm, said  $N_2$  gas is introduced in step A at a flow rate above 500 sccm, said plasma as generated in step B using Microwave power in the range of 100 W to 2000 W, said HF is introduced in step C at a flow rate of 5 sccm to 500 sccm.

**39**. The method of claim 37, wherein said polymer layer and said natural oxide layer are removed by annealing using a UV lamp or IR lamp.

**40**. The method of claim 37, further comprising a step E1 of removing a damaged portion of the surface of said substrate after said step E of removing said polymer layer and said natural oxide layer by annealing with a flow of  $H_2$ .

**41**. The method of claim 37, wherein a wall temperature of said chamber is maintained at between  $50^{\circ}$  C. and  $120^{\circ}$  C.

\* \* \* \* \*