(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-49437

(P2014-49437A)

(43) 公開日 平成26年3月17日(2014.3.17)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H05B 37/02</b> (2006.01) | H05B 37/02 | J 2H193     |

| <b>G02F 1/133</b> (2006.01) | G02F 1/133 | 535 3KO73   |

| <b>G09G 3/34</b> (2006.01)  | G09G 3/34  | J 5C006     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20  | 641A 5C080  |

| <b>G09G 3/36</b> (2006.01)  | G09G 3/20  | 611G        |

審査請求 有 請求項の数 12 O L (全 14 頁) 最終頁に続く

(21) 出願番号 特願2012-273471 (P2012-273471)

(22) 出願日 平成24年12月14日 (2012.12.14)

(31) 優先権主張番号 10-2012-0096323

(32) 優先日 平成24年8月31日 (2012.8.31)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー ディスプレイカンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

ウィーテロ 128

(74) 代理人 100109726

弁理士 園田 吉隆

(74) 代理人 100101199

弁理士 小林 義教

(72) 発明者 アン, ヨンファン

大韓民国 136-775, ソウル,

ソンブック, チョンヌン 4ドン, プ

ンリム アパートメント, 129-15

10

最終頁に続く

(54) 【発明の名称】バックライトユニットの光源駆動装置及び方法

## (57) 【要約】

【課題】本発明は光源ドライバの設計を単純化しそのサイズを小さくすることができ、ひいては製品単価を下げることができるバックライトユニットの光源駆動装置及び方法を提供する。

【解決手段】本発明に係るバックライトユニットの光源駆動装置は光源と、入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするためにPWM制御とPWMカウント制御を時系列的に組み合わせ前記光源の明るさ調整のための出力ディミング信号のディミング値を段階的に下げる光源ドライバを備え、前記出力ディミング信号のディミング値は、第1期間で前記PWM制御によって第1ディミング値まで下がった後、前記第1期間に続く第2期間で前記PWMカウント制御によって前記第1ディミング値より低い第2ディミング値まで下がることを特徴とする。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

光源と、

入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするために PWM 制御と PWM カウント制御を時系列的に組み合わせて前記光源の明るさ調整のための出力ディミング信号のディミング値を段階的に下げる光源ドライバを備え、

前記出力ディミング信号のディミング値は、

第 1 期間で前記 PWM 制御によって第 1 ディミング値まで下がった後、前記第 1 期間に続く第 2 期間で前記 PWM カウント制御によって前記第 1 ディミング値より低い第 2 ディミング値まで下がることを特徴とするバックライトユニットの光源駆動装置。10

**【請求項 2】**

前記光源ドライバは前記待機モードでのローディミングを可能とするために前記 PWM 制御及び PWM カウント制御とともにアナログディミング制御を時系列的にさらに組み合わせ前記出力ディミング信号のディミング値を段階的に下げることを特徴とする請求項 1 記載のバックライトユニットの光源駆動装置。

**【請求項 3】**

前記出力ディミング信号のディミング値は、

前記第 1 期間と前記第 2 期間の間の第 3 期間において前記アナログディミング制御によって、前記第 1 ディミング値と前記第 2 ディミング値の間の第 3 ディミング値に制御されることを特徴とする請求項 2 記載のバックライトユニットの光源駆動装置。20

**【請求項 4】**

前記出力ディミング信号のディミング値は、

前記第 1 期間より前の第 3 期間において前記アナログディミング制御によって前記第 1 ディミング値より高い第 3 ディミング値に制御されることを特徴とする請求項 2 記載のバックライトユニットの光源駆動装置。

**【請求項 5】**

前記出力ディミング信号のディミング値は、

前記第 2 期間に続く第 3 期間において前記アナログディミング制御によって前記第 2 ディミング値より低い第 3 ディミング値に制御されることを特徴とする請求項 2 記載のバックライトユニットの光源駆動装置。30

**【請求項 6】**

前記光源ドライバは、

前記出力ディミング信号のディミング値を前記第 1 ディミング値まで下げるために前記出力ディミング信号の PWM デューティを調整し、

前記出力ディミング信号のディミング値を前記第 2 ディミング値まで下げるために前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、

前記カウントされた PWM パルスの一部をオフにし、

前記出力ディミング信号のディミング値を前記第 3 ディミング値まで下げるために光源駆動電流を調整することを特徴とする請求項 3 乃至 5 の内いずれか一項記載のバックライトユニットの光源駆動装置。40

**【請求項 7】**

入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするために PWM 制御と PWM カウント制御を時系列的に組み合わせ出力ディミング信号のディミング値を段階的に下げる段階と、

前記出力ディミング信号によって光源を駆動させ前記光源の明るさを調整する段階を含み、

前記出力ディミング信号のディミング値は、

第 1 期間で前記 PWM 制御によって第 1 ディミング値まで下がった後、前記第 1 期間に引き継いだ第 2 期間で前記 PWM カウント制御によって前記第 1 ディミング値より低い第50

2ディミング値まで下がることを特徴とするバックライトユニットの光源駆動方法。

【請求項 8】

前記出力ディミング信号のディミング値を段階的に下げる段階では、前記 PWM 制御及び PWM カウント制御とともにアナログディミング制御を時系列的にさらに組み合わせることを特徴とする請求項 7 記載のバックライトユニットの光源駆動方法。

【請求項 9】

前記出力ディミング信号のディミング値は、

前記第1期間と前記第2期間の間の第3期間において前記アナログディミング制御によって、前記第1ディミング値と前記第2ディミング値の間の第3ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

10

【請求項 10】

前記出力ディミング信号のディミング値は、

前記第1期間より前の第3期間において前記アナログディミング制御によって前記第1ディミング値より高い第3ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

【請求項 11】

前記出力ディミング信号のディミング値は、

前記第2期間に続く第3期間において前記アナログディミング制御によって前記第2ディミング値より低い第3ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

20

【請求項 12】

前記出力ディミング信号のディミング値を段階的に下げる段階は、

前記出力ディミング信号のディミング値を前記第1ディミング値まで下げるために前記出力ディミング信号の PWM デューティを調整する段階と

前記出力ディミング信号のディミング値を前記第2ディミング値まで下げるために前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、前記カウントされた PWM パルスの一部をオフにする段階と、

前記出力ディミング信号のディミング値を前記第3ディミング値まで下げるために光源駆動電流を調整する段階を含むことを特徴とする請求項 9 乃至 11 の内いずれか一項記載のバックライトユニットの光源駆動方法。

30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に光を照射するバックライトユニットに関し、特に、バックライトユニットの光源駆動装置及び方法に関する。

【背景技術】

【0002】

液晶表示装置は軽量、薄型、低消費電力駆動などの特徴によってその応用範囲が徐々に広くなっている傾向にある。この液晶表示装置はノートパソコン (PC) のようなポータブルコンピュータ、事務自動化機器、オーディオ/ビデオ機器、屋内外広告表示装置などに利用されている。液晶表示装置の大部分を占めている透過型液晶表示装置は液晶層に印加される電界を制御しバックライトユニットから入射される光をデータ電圧によって調節して画像を表示する。

40

【0003】

バックライトユニットの光源では冷陰極蛍光ランプ (Cold Cathode Fluorescent Lamp、CCFL) のような蛍光ランプが使われて来たが最近には既存蛍光ランプに比べて消費電力、重さ、輝度などで多くの長所を有する発光ダイオード (Light Emitting Diode : 以下 'LED' と称する) が採用されている。複数の LED は光源ドライバによってその明るさが制御される。光源ドライバは LED の明るさを制御するためにパルス幅変造 (Pulse Width Modulation、以下 "PWM" と称する) 方式を利用する。PWM 方式で、出力ディ

50

ミング信号のデューティ比は入力 PWM 信号のデューティ比と同一であるが、出力ディミング信号の周波数は入力 PWM 信号の周波数と異なりに独立的に制御可能である。通常的な出力ディミング周波数は 10 kHz 以上で非常に高い。

#### 【0004】

液晶表示装置は正常な画像表示のためのノーマルモード以外に、消費電力低減のための待機モードを並行して使っている。待機モードの下で液晶表示装置は動作に必要な最小限の電源のみを活性化し、特に出力ディミング信号のデューティ比はあらかじめ決まった値（例えば、0.02%）以下に大きく下げられる。

#### 【0005】

ところが、PWM 方式を利用した従来の光源駆動装置によれば、待機モードで具現される 0.02% 以下の出力ディミング値計算のために最小 13 ビット以上の演算ロジックが必要で光源ドライバに対する設計が複雑である。さらに、20 kHz 程度の早い出力ディミング周波数帯域で 0.02% 位の低い出力ディミング値具現のためには 100 MHz 以上の基準クロックが必要であるが、従来の光源ドライバはこの基準クロックに合わせて演算データが処理されるように設計されなければならず、その構成が複雑になる。光源ドライバの設計が複雑になるほど光源ドライバのサイズが大きくなつて製品単価が上がる。

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

本発明の目的は、待機モードで必要な出力ディミング値を比較的少ない演算ロジックと低い基準クロックで具現するようにしたバックライトユニットの光源駆動装置及び方法を提供することにある。

20

#### 【課題を解決するための手段】

#### 【0007】

前記目的を達成するために、本発明のバックライトユニットの光源駆動装置は光源と入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするために PWM 制御と PWM カウント制御を時系列的に組み合わせて前記光源の明るさ調整のための出力ディミング信号のディミング値を段階的に下げる光源ドライバを備え、前記出力ディミング信号のディミング値は、第 1 期間で前記 PWM 制御によって第 1 ディミング値まで下がった後、前記第 1 期間に引き継いだ第 2 期間で前記 PWM カウント制御によって前記第 1 ディミング値より低い第 2 ディミング値まで下げられることを特徴とする。

30

#### 【発明の効果】

#### 【0008】

前述したように、本発明は PWM 方式と PWM カウント方式を時系列的に組み合わせるかまたは、PWM 方式及び PWM カウント方式にアナログディミング方式さらに時系列的に組み合わせることで、比較的少ない演算ロジックと低い基準クロックでローディミングを具現することができる。これによって本発明は光源ドライバの設計を単純化しそのサイズを小さくすることができる、ひいては製品単価を下げることができる。

40

#### 【図面の簡単な説明】

#### 【0009】

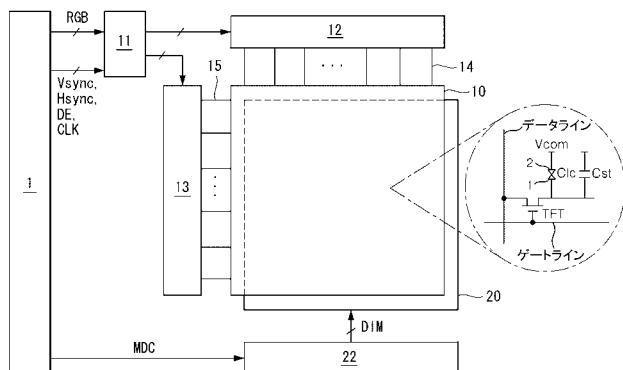

【図 1】本発明の実施の形態に係る液晶表示装置を示す図である。

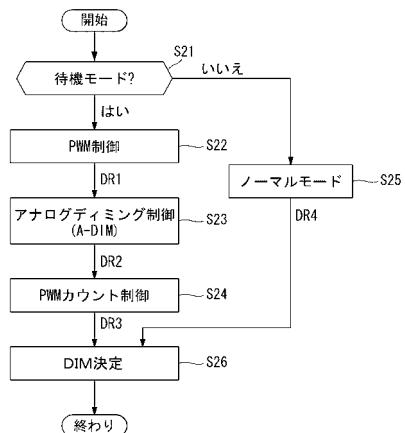

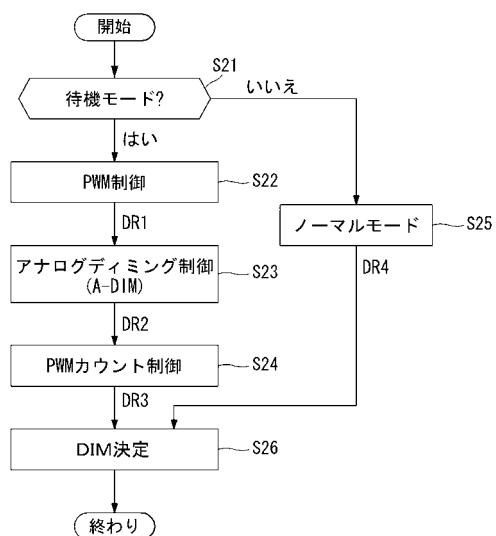

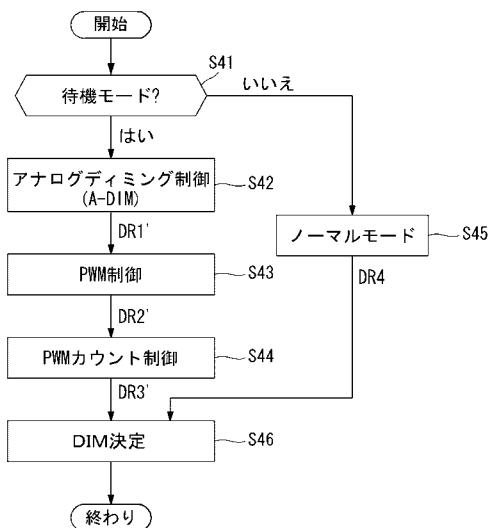

【図 2】ローディミング具現のための光源ドライバ動作手順の一例を示す図である。

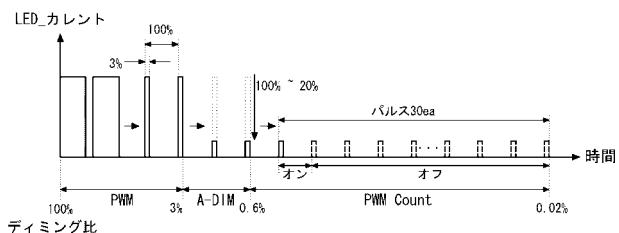

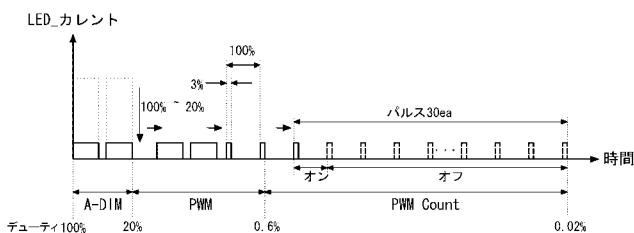

【図 3】図 2 の動作による出力ディミング値の制御コンセプトを示す図である。

【図 4】ローディミング具現のための光源ドライバ動作手順の他の例を示す図である。

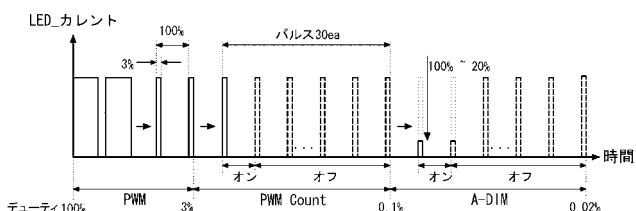

【図 5】図 4 の動作による出力ディミング値制御コンセプトを示す図である。

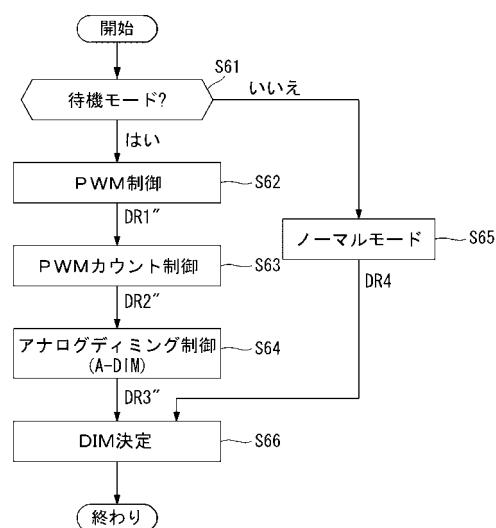

【図 6】ローディミング具現のための光源ドライバ動作手順のまた他の例を示す図である。

。

【図 7】図 6 の動作による出力ディミング値制御コンセプトを示す図である。

#### 【発明を実施するための形態】

50

## 【0010】

前記目的外に本発明の他の目的及び特徴は添付した図を参照した実施の形態の説明を通じ明確になる。

## 【0011】

以下、図1乃至図7を参照し本発明の望ましい実施の形態に対して詳しく説明する。

## 【0012】

図1は本発明の実施の形態に係る液晶表示装置を示す。

## 【0013】

図1を参照すれば、本発明の実施の形態に係る液晶表示装置は液晶表示パネル10、液晶表示パネル10に光を照射するバックライトユニット20、バックライトユニット20の光源を駆動するための光源ドライバ22、液晶表示パネル10のデータライン14を駆動するためのソースドライバ12、液晶表示パネル10のゲートライン15を駆動するためのゲートドライバ13、タイミングコントローラ11及びホストシステム1を備える。10

## 【0014】

液晶表示パネル10は二枚のガラス基板の間に液晶層が形成される。この液晶表示パネル10の下部ガラス基板には複数のデータライン14と複数のゲートライン15が交差される。データライン14とゲートライン15の交差構造によって液晶表示パネル10には液晶セル(C1c)がマトリックス形態に配置される。液晶表示パネル10の下部ガラス基板にはデータライン14、ゲートライン15、薄膜トランジスタ(TFT)、薄膜トランジスタ(TFT)に接続された液晶セル(C1c)の画素電極1、及びストレージキャパシター(Storage Capacitor, Cst)などが形成される。20

## 【0015】

液晶表示パネル10の上部ガラス基板上にはブラックマットリックス、カラーフィルター及び共通電極2が形成される。共通電極2はTN(Twisted Nematic)モードとVA(Vertical Alignment)モードのような垂直電界駆動方式で上部ガラス基板上に形成され、IPS(In Plane Switching)モードとFFS(Fringe Field Switching)モードのような水平電界駆動方式で画素電極1とともに下部ガラス基板上に形成される。液晶表示パネル10の上部ガラス基板と下部ガラス基板それぞれには偏光板が附着し液晶と接する内面に液晶のプレチルト角を設定するための配向膜が形成される。30

## 【0016】

バックライトユニット20は光源ドライバ22によって駆動される複数の光源を含み液晶表示パネル10に光を照射する。光源ではその制限がないが、消費電力、重さ、輝度などで多くの長所を有するLEDが選択されることが望ましい。バックライトユニット20は光源チャンネルが導光板の側面と対向するように配置されるエッジ型バックライトユニットに具現されることができまた、光源が拡散板の下に配置される直下型バックライトユニットに具現されることもできる。エッジ型バックライトユニット20は光源チャンネルから発生された光を導光板とその上に積層された複数の光学シートを利用して均一な面光源に変換し液晶表示パネル10に光を照射する。直下型バックライトユニット20は光源から発生された光を拡散板とその上に積層された複数の光学シートを通じて均一な面光源に変換して液晶表示パネル10に光を照射する。40

## 【0017】

ソースドライバ12はタイミングコントローラ11の制御の下にデジタルビデオデータ(RGB)をラッチする。そしてソースドライバ12は正極性/負極性ガンマ補償基準電圧を利用してデジタルビデオデータ(RGB)を正極性/負極性アナログデータ電圧に変換してデータライン14に供給する。

## 【0018】

ゲートドライバ13はシフトレジスタ、シフトレジスタの出力信号を液晶セルのTFT駆動に適合するスイング幅に変換するためのレベルシフタ、及び出力バッファなどを含む。このゲートドライバ13は約1水平期間のパルス幅を有するゲートパルス(またはスキヤンパルス)を順次出力しゲートライン15に供給する。50

## 【0019】

タイミングコントローラ11はホストシステム1からデジタルビデオデータ(RGB)とタイミング信号(Vsync、Hsync、DE、CLK)を受信し、デジタルビデオデータ(RGB)をソースドライバ12に供給し、タイミング信号(Vsync、Hsync、DE、CLK)に基づいてソースドライバ12とゲートドライバ13の動作タイミングを制御するためのタイミング制御信号を生成する。このタイミングコントローラ11は入力映像を分析しその分析結果によって表示映像の動的範囲が拡がるように光源ドライバ22をローカルディミング方法で制御することもできる。

## 【0020】

ホストシステム1はテレビ(television)システム、ナビゲーションシステム、セットトップボックス、DVDプレーヤー、ブルーレイプレーヤー、パソコン(PC)、ホームシアターシステム、電話システム(Phone system)中のいずれにも具現されることがある。ホストシステム1はスケーラ(scaler)を利用し入力映像のデジタルビデオデータ(RGB)を液晶表示パネル20の解像度に対応するフォーマットに変換し、そのデータ(RGB)とともにタイミング信号(Vsync、Hsync、DE、CLK)をタイミングコントローラ11に伝送する。

10

## 【0021】

ホストシステム1は使用者データに応答して光源ドライバ22に供給される入力ディミング信号(MDC)を調整することで、光源ドライバ22を待機モードで動作させることができる。光源ドライバ22の待機モードへの動作制御のための入力ディミング信号(MDC)は、ノーマルモードでの入力ディミング信号(MDC)に比べてずっと低いディミング値に選択される。使用者は使用者インターフェースを通じてホストシステム110に使用者データを適用して待機モードを選択することができる。使用者インターフェースはキーパッド、キーボード、マウス、オンスクリーンディスプレイ(On Screen Display、OSD)、リモートコントローラ(Remote controller)、グラフィカルユーザインターフェース(Graphical User Interface GUI)、タッチUI(User Interface)、音声認識UI、3D UIなどに具現されることがある。

20

## 【0022】

光源ドライバ22はホストシステム110から適用される入力ディミング信号(MDC)によって光源チャンネルの明るさ制御のための出力ディミング値(DIM)を調整し液晶表示パネル10に照射される光の輝度を調整する。

30

## 【0023】

光源ドライバ22は入力ディミング信号(MDC)のディミング値があらかじめ決まった基準ディミング値より大きければノーマルモードで動作する。ノーマルモードで光源ドライバ22はPWM方式で出力ディミング信号のディミング値(DIM)を入力ディミング信号(MDC)のディミング値に一致させる。

## 【0024】

一方、光源ドライバ22は入力ディミング信号(MDC)のディミング値があらかじめ決まった基準ディミング値と同一であるかそれより小さければ待機モードで動作する。待機モードで光源ドライバ22はPWM方式及びPWMカウント方式で出力ディミング信号のディミング値(DIM)を入力ディミング信号(MDC)のディミング値に一致させローディミングを具現する。ローディミングのために、光源ドライバ22はPWM方式とPWMカウント方式を時系列的に組み合わせてディミング値を段階的に下げることで所望する出力ディミング値(DIM)を導出する。言い換えれば、光源ドライバ22は出力ディミング信号のディミング値(DIM)を、第1期間でPWM制御で第1ディミング値まで下げた後、前記第1期間に続く第2期間でPWMカウント制御で前記第1ディミング値より低い第2ディミング値まで下げる。光源ドライバ22はPWM方式とPWMカウント方式を時系列的に組み合わせることで相対的に少ない演算ロジックと低い基準クロックで待機モードで所望する出力ディミング信号のディミング値(DIM)を具現することができるようになる。演算ロジックのサイズと基準クロックの速度はPWM制御の時にPWMデ

40

50

ューティ比を計算することにだけ関係する。

【0025】

光源ドライバ22はPWM方式とPWMカウント方式を時系列的に組み合わせることだけでローディミングを具現することができ、またPWM方式及びPWMカウント方式以外にアナログディミング方式をさらに含みローディミングを具現することもできる。アナログディミング方式は、時系列的に組み合わせたPWM制御期間（前記第1期間）とPWMカウント制御期間（前記第2期間）の間で、またはPWM制御期間の前で、またはPWMカウント制御期間の後から選択的に行われることができる。

【0026】

ローディミング具現のための光源ドライバ22の動作は、アナログディミング制御期間が配置される時点によって次のような三種類の実施の形態に分けられることができる。以下の実施の形態ではローディミング具現のための出力ディミング値（DIM）を0.02%で仮定し説明するが、本発明の技術的思想は出力ディミング値（DIM）の具体的な数値に限定されない。

【0027】

[光源ドライバ22動作の第1実施の形態]

【0028】

図2はローディミングを具現するための光源ドライバ22の動作の一例を示すフローチャートである。図3は図2の動作による出力ディミング値（DIM）制御コンセプトを示す。

【0029】

第1実施の形態に係る光源ドライバ22は連続して行われるPWM制御手順及びPWMカウント制御手順の間でアナログディミング制御をさらに実行する。光源ドライバ22はローディミング具現のために出力ディミング信号のディミング値（DIM）を、PWM制御期間で第1ディミング値まで下げた後、アナログディミング制御期間で第2ディミング値まで下げ、次いで、PWMカウント制御期間で第3ディミング値まで下げことで、0.02%の出力ディミング値（DIM）を具現する。演算ロジックのサイズと基準クロックの速度はPWM制御による第1ディミング値にだけ依存し、第2及び第3ディミング値には無関係である。したがって、光源ドライバ22はPWMカウント制御とともに選択的にアナログディミング制御をさらに含むことで、第1ディミング値（例えば、3%）の計算のための8ビットの演算ロジックと1MHz程度の基準クロックで0.02%の出力ディミング値（DIM）を充分に具現することができるようになる。

【0030】

図2及び図3を参照すると、光源ドライバ22は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値（0.02%）と同一であるかそれより小さければ待機モードに入りローディミングを具現する（S21）。光源ドライバ22は出力ディミング信号のディミング値（DIM）を入力ディミング信号のディミング値に一致させるのに必要なディミング制御期間をPWM制御期間、アナログディミング制御期間、及びPWMカウント制御期間の順に時間的に分割する。

【0031】

光源ドライバ22はPWM制御期間で出力ディミング信号のPWMデューティを100%～3%範囲内で可変することで出力ディミング信号のディミング値（DIM）を第1ディミング値（DR1）である3%まで下げる（S22）。出力ディミング周波数の最大値が20kHzに設定された場合、3%のPWMデューティを計算するのに必要な最小基準クロックは約666kHz（ $1 \div 20 [kHz] \times 0.03 = 1.5 \times 10 - 6 [sec]$ ）数学666[kHz]であるから、適切な基準クロックは1MHz程度なら十分である。また、演算ロジックが8ビットの場0.4%（ $1 / 256 = 0.004$ ）まで演算ができるので、3%のPWMデューティを計算するのに適切な演算ロジックは8ビット位であると十分である。

【0032】

10

20

30

40

50

その後、出力ディミング信号のディミング値 (D I M) を 3 % から 0 . 0 2 % まで下げるため、光源ドライバ 2 2 は演算ロジックのサイズ及び基準クロックの速度と関係ないアナログディミング制御期間と P W M カウント制御期間を利用する。光源ドライバ 2 2 はアナログディミング制御期間で光源駆動電流を 1 0 0 % ~ 2 0 % 範囲内で可変することで出力ディミング信号のディミング値 (D I M) を第 2 ディミング値 (D R 2) である 0 . 6 % ( 0 . 0 3 × 0 . 2 = 0 . 0 0 6 = 0 . 6 % ) まで下げる (S 2 3)。次いで、光源ドライバ 2 2 は P W M カウント制御期間で第 2 ディミング値 (0 . 6 %) の P W M パルスを所定個数 (例えば、30 個) 単位についてカウントした後、カウントされた P W M パルスの一部 (例えば、29 個) をオフ (図 3 に点線で表記) にすることで出力ディミング信号のディミング値 (D I M) を第 3 ディミング値 (D R 3) である 0 . 0 2 % ( 0 . 0 0 6 × 1 / 3 0 = 0 . 0 0 0 2 = 0 . 0 2 % ) まで下げる (S 2 4)。光源ドライバ 2 2 は第 3 ディミング値 (D R 3) を出力ディミング信号のディミング値 (D I M) として決定することでローディミングを具現する。(S 2 6)

10

## 【0033】

一方、光源ドライバ 2 2 は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値より大きければノーマルモードに入り、入力ディミング信号のディミング値と同一である第 4 ディミング値 (D R 4) を出力ディミング信号のディミング値 (D I M) として決定することで正常ディミングを具現する (S 2 5、S 2 6)。

20

## 【0034】

[光源ドライバ 2 2 動作の第 2 実施の形態]

## 【0035】

図 4 はローディミングを具現するための光源ドライバ 2 2 動作の別の例を示すフローチャートである。図 5 は図 4 の動作による出力ディミング値 (D I M) 制御コンセプトを示す。

## 【0036】

第 2 実施の形態に係る光源ドライバ 2 2 は連続して行われる P W M 制御手順及び P W M カウント制御手順に先立って、すなわち P W M 制御手順に先立ってアナログディミング制御をさらに実行する。光源ドライバ 2 2 はローディミング具現のために出力ディミング信号のディミング値 (D I M) を、アナログ制御期間で第 1 ディミング値まで下げた後、P W M 制御期間で第 2 ディミング値まで下げ、次いで、P W M カウント制御期間で第 3 ディミング値まで下げることで、0 . 0 2 % の出力ディミング値 (D I M) を具現する。演算ロジックのサイズと基準クロックの速度は P W M 制御による第 2 ディミング値にだけ依存し、第 1 及び第 3 ディミング値には無関係である。したがって、光源ドライバ 2 2 は P W M カウント制御とともに選択的にアナログディミング制御をさらに含むことで、第 2 ディミング値 (例えば、0 . 6 %) 計算のための 8 ビットの演算ロジックと 4 M H z 程度の基準クロックで 0 . 0 2 % の出力ディミング値 (D I M) を充分に具現することができるようになる。

30

## 【0037】

図 4 及び図 5 を参照すると、光源ドライバ 2 2 は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値 (0 . 0 2 %) と同一であるかそれより小さければ待機モードに入りしローディミングを具現する (S 4 1)。光源ドライバ 2 2 は出力ディミング信号のディミング値 (D I M) を入力ディミング信号のディミング値に一致させるのに必要なディミング制御期間をアナログディミング制御期間、P W M 制御期間、及び P W M カウント制御期間の順に時間的に分割する。アナログディミング制御期間と P W M カウント制御期間は演算ロジックのサイズ及び基準クロックの速度と関係なく動作する。

40

## 【0038】

光源ドライバ 2 2 はアナログディミング制御期間で光源駆動電流を 1 0 0 % ~ 2 0 % 範囲内で可変することで出力ディミング信号のディミング値 (D I M) を第 1 ディミング値 (D R 1') である 2 0 % まで下げる。(S 4 2)

## 【0039】

50

次いで、光源ドライバ22は第1ディミング値(DR1')を有する出力ディミング信号のPWMデューティをPWM制御期間で100%~3%範囲内で可変することで出力ディミング信号のディミング値(DIM)を第2ディミング値(DR2')である0.6%まで下げる(S43)。出力ディミング周波数の最大値が20kHzに設定された場合、0.6%のPWMデューティを計算するのに必要な最小基準クロックは約3.33MHz( $1 \div 20 [kHz] \times 0.006 = 3 \times 10 - 7 [sec] = 3.33 [MHz]$ )であるから、適切な基準クロックは4MHz程度なら十分である。また、演算ロジックが8ビットの場合0.4%( $1 / 256 = 0.004$ )まで演算が可能なから、0.6%のPWMデューティを計算するのに適切な演算ロジックは8ビット位なら十分である。

## 【0040】

その後、光源ドライバ22はPWMカウント制御期間で第2ディミング値(0.6%)のPWMパルスを所定個数(例えば、30個)単位についてカウントした後、カウントされたPWMパルスの一部(例えば、29個)をオフ(図5に点線で表記)にすることで出力ディミング値(DIM)を第3ディミング値(DR3')である0.02%( $0.006 \times 1 / 30 = 0.0002 = 0.02\%$ )まで下げる(S44)。光源ドライバ22は第3ディミング値(DR3')を出力ディミング信号のディミング値(DIM)として決定することでローディミングを具現する(S46)。

## 【0041】

一方、光源ドライバ22は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値より大きければノーマルモードに入り、入力ディミング信号のディミング値と同一である第4ディミング値(DR4)を出力ディミング信号のディミング値(DIM)として決定することで正常ディミングを具現する(S45、S46)。

## 【0042】

[光源ドライバ22動作の第3実施の形態]

## 【0043】

図6はローディミングを具現するための光源ドライバ22動作のまた別の例を示すフローチャートである。図7は図6の動作による出力ディミング値(DIM)制御コンセプトを示す。

## 【0044】

第3実施の形態に係る光源ドライバ22は連続して行われるPWM制御手順及びPWMカウント制御手順に続けて、すなわちPWMカウント制御手順に続けてアナログディミング制御をさらに実行する。光源ドライバ22はローディミング具現のために出力ディミング信号のディミング値(DIM)を、PWM制御期間で第1ディミング値まで下げた後、PWMカウント制御期間で第2ディミング値まで下げ、次いで、アナログディミング制御期間で第3ディミング値まで下げることで、0.02%の出力ディミング値(DIM)を具現する。演算ロジックのサイズと基準クロックの速度はPWM制御による第1ディミング値にだけ依存し、第2及び第3ディミング値には無関係である。したがって、光源ドライバ22はPWMカウント制御とともに選択的にアナログディミング制御をさらに含むことで、第1ディミング値(例えば、3%)計算のための8ビットの演算ロジックと1MHz程度の基準クロックで0.02%の出力ディミング値(DIM)を充分に具現することができるようになる。

## 【0045】

図6及び図7を参照すると、光源ドライバ22は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値(0.02%)と同一であるかそれより小さければ待機モードに入りローディミングを具現する(S61)。光源ドライバ22は出力ディミング信号のディミング値(DIM)を入力ディミング信号のディミング値に一致させるのに必要なディミング制御期間をPWM制御期間、PWMカウント制御期間、及びアナログディミング制御期間の順に時間的に分割する。

## 【0046】

光源ドライバ22はPWM制御期間で出力ディミング信号のPWMデューティを100

10

20

30

40

50

%～3%範囲内で可変することで出力ディミング信号のディミング値(DIM)を第1ディミング値(DR1")である3%まで下げる(S62)。出力ディミング周波数の最大値が20kHzに設定された場合、3%のPWMデューティを計算するのに必要な最小基準クロックは約666kHz( $1 \div 20 [kHz] \times 0.03 = 1.5 \times 10 - 6 [sec] = 666 [kHz]$ )であるから、適切な基準クロックは1MHz程度なら十分である。また、演算ロジックが8ビットの場合 $0.4\% (1/256 = 0.004)$ まで演算が可能であるから、3%のPWMデューティを計算するのに適切な演算ロジックは8ビット位なら十分である。

#### 【0047】

その後、出力ディミング信号のディミング値(DIM)を3%から0.02%まで下げるため、光源ドライバ22は演算ロジックのサイズ及び基準クロックの速度と関係ないアナログディミング制御期間とPWMカウント制御期間を利用する。光源ドライバ22はPWMカウント制御期間で第1ディミング値(3%)のPWMパルスを所定個数(例えば、30個)単位についてカウントした後、カウントされたPWMパルスの一部(例えば、29個)をオフ(図7に点線で表記)にすることで出力ディミング信号のディミング値(DIM)を第2ディミング値(DR2")である $0.1\% (0.03 \times 1/30 = 0.001 = 0.1\%)$ まで下げる(S63)。次いで、光源ドライバ22はアナログディミング制御期間で光源駆動電流を100%～20%範囲内で可変することで出力ディミング信号のディミング値(DIM)を第3ディミング値(DR3")である $0.02\% (0.001 \times 0.2 = 0.0002 = 0.02\%)$ まで下げる(S64)。光源ドライバ22は第3ディミング値(DR3")を出力ディミング信号のディミング値(DIM)で決めることでローディミングを具現する(S66)。

10

20

20

#### 【0048】

一方、光源ドライバ22は入力ディミング信号のディミング値があらかじめ決まった基準ディミング値より大きければノーマルモードに入り、入力ディミング信号のディミング値と同一である第4ディミング値(DR4")を出力ディミング信号のディミング値(DIM)として決定することで正常ディミングを具現する(S65、S66)。

30

#### 【0049】

以上説明した内容を通じて、当業者であれば本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であることが分かる。したがって、本発明の技術的範囲は明細書の詳細な説明に記載した内容に限定されるのではなく特許請求の範囲によって決められなければならない。

#### 【符号の説明】

#### 【0050】

- 1 ホストシステム

- 10 液晶表示パネル

- 11 タイミングコントローラ

- 12 ソースドライバ

- 13 ゲートドライバ

- 14 データライン

- 15 ゲートライン

- 20 バックライトユニット

- 22 光源ドライバ

40

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

**【手続補正書】**

【提出日】平成25年12月17日(2013.12.17)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

光源と、

入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするために PWM 制御と PWM カウント制御を時系列的に組み合わせて前記光源の明るさ調整のための出力ディミング信号のディミング値を段階的に下げる光源ドライバを備え、

前記出力ディミング信号のディミング値は、

第1期間で前記 PWM 制御によって第1ディミング値まで下がった後、前記第1期間に続く第2期間で前記 PWM カウント制御によって前記第1ディミング値より低い第2ディミング値まで下がり、

前記 PWM カウント制御は前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、前記カウントされた PWM パルスの一部をオフにすることを特徴とするバックライトユニットの光源駆動装置。

**【請求項2】**

前記光源ドライバは前記待機モードでのローディミングを可能とするために前記 PWM 制御及び PWM カウント制御とともにアナログディミング制御を時系列的にさらに組み合わせ前記出力ディミング信号のディミング値を段階的に下げることを特徴とする請求項1記載のバックライトユニットの光源駆動装置。

**【請求項3】**

前記出力ディミング信号のディミング値は、

前記第1期間と前記第2期間の間の第3期間において前記アナログディミング制御によって、前記第1ディミング値と前記第2ディミング値の間の第3ディミング値に制御されることを特徴とする請求項2記載のバックライトユニットの光源駆動装置。

**【請求項4】**

前記出力ディミング信号のディミング値は、

前記第1期間より前の第3期間において前記アナログディミング制御によって前記第1ディミング値より高い第3ディミング値に制御されることを特徴とする請求項2記載のバックライトユニットの光源駆動装置。

**【請求項5】**

前記出力ディミング信号のディミング値は、

前記第2期間に続く第3期間において前記アナログディミング制御によって前記第2ディミング値より低い第3ディミング値に制御されることを特徴とする請求項2記載のバックライトユニットの光源駆動装置。

**【請求項6】**

前記光源ドライバは、

前記出力ディミング信号のディミング値を前記第1ディミング値まで下げるために前記出力ディミング信号の PWM デューティを調整し、

前記出力ディミング信号のディミング値を前記第2ディミング値まで下げるために前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、

前記カウントされた PWM パルスの一部をオフにし、

前記出力ディミング信号のディミング値を前記第3ディミング値まで下げるために光源駆動電流を調整することを特徴とする請求項3乃至5の内いずれか一項記載のバックライ

トユニットの光源駆動装置。

【請求項 7】

入力ディミング信号によって待機モードで動作し、前記待機モードでのローディミングを可能とするために PWM 制御と PWM カウント制御を時系列的に組み合わせ出力ディミング信号のディミング値を段階的に下げる段階と、

前記出力ディミング信号によって光源を駆動させ前記光源の明るさを調整する段階を含み、

前記出力ディミング信号のディミング値は、

第 1 期間で前記 PWM 制御によって第 1 ディミング値まで下がった後、前記第 1 期間に引き継いだ第 2 期間で前記 PWM カウント制御によって前記第 1 ディミング値より低い第 2 ディミング値まで下がり、

前記 PWM カウント制御は前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、前記カウントされた PWM パルスの一部をオフにすることを特徴とするバックライトユニットの光源駆動方法。

【請求項 8】

前記出力ディミング信号のディミング値を段階的に下げる段階では、前記 PWM 制御及び PWM カウント制御とともにアナログディミング制御を時系列的にさらに組み合わせることを特徴とする請求項 7 記載のバックライトユニットの光源駆動方法。

【請求項 9】

前記出力ディミング信号のディミング値は、

前記第 1 期間と前記第 2 期間の間の第 3 期間において前記アナログディミング制御によって、前記第 1 ディミング値と前記第 2 ディミング値の間の第 3 ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

【請求項 10】

前記出力ディミング信号のディミング値は、

前記第 1 期間より前の第 3 期間において前記アナログディミング制御によって前記第 1 ディミング値より高い第 3 ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

【請求項 11】

前記出力ディミング信号のディミング値は、

前記第 2 期間に続く第 3 期間において前記アナログディミング制御によって前記第 2 ディミング値より低い第 3 ディミング値に制御されることを特徴とする請求項 8 記載のバックライトユニットの光源駆動方法。

【請求項 12】

前記出力ディミング信号のディミング値を段階的に下げる段階は、

前記出力ディミング信号のディミング値を前記第 1 ディミング値まで下げるために前記出力ディミング信号の PWM デューティを調整する段階と

前記出力ディミング信号のディミング値を前記第 2 ディミング値まで下げるために前記出力ディミング信号を構成する PWM パルスを所定個数単位についてカウントした後、前記カウントされた PWM パルスの一部をオフにする段階と、

前記出力ディミング信号のディミング値を前記第 3 ディミング値まで下げるために光源駆動電流を調整する段階を含むことを特徴とする請求項 9 乃至 11 の内いずれか一項記載のバックライトユニットの光源駆動方法。

---

フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/36

(72)発明者 キム， ジヨンデ

大韓民国 730-380, キョンブク, クミシ, オッケドン, ヒヨンジン エヴァーヴ

ィル アパートメント, 105-3105

(72)発明者 キム， サンギュ

大韓民国 730-912, キョンブク, クミシ, ソンジョンドン, プリジオ キャッス

ル アパートメント, 106-304

(72)発明者 ユン， ピヨンギ

大韓民国 730-320, キョンブク, クミシ, イニドン, 986, イニ プリジオ

アパートメント, 102-1306

(72)発明者 パク， ミンウ

大韓民国 730-090, キョンブク, クミシ, ソンジョンドン, プリジオ キャッス

ル アパートメント, 102-903

F ターム(参考) 2H193 ZA04 ZA05 ZF21 ZF34 ZG04 ZG14 ZG45 ZG48 ZG50 ZG58

ZG60 ZQ06 ZQ11 ZQ16

3K073 AA16 AA54 AA83 AA84 AB04 CG10 CG12 CG13 CG14 CJ17

5C006 AA15 EA01 FA41 FA48 FA51

5C080 AA10 DD22 DD27 JJ02 JJ05 JJ07