【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成19年3月15日(2007.3.15)

【公開番号】特開2006-11573(P2006-11573A)

【公開日】平成18年1月12日(2006.1.12)

【年通号数】公開・登録公報2006-002

【出願番号】特願2004-184397(P2004-184397)

【国際特許分類】

**G 06 F 17/50 (2006.01)**

**H 05 K 1/02 (2006.01)**

**H 05 K 3/00 (2006.01)**

【F I】

**G 06 F 17/50 6 5 8 C**

**H 05 K 1/02 R**

**H 05 K 3/00 D**

【手続補正書】

【提出日】平成19年1月31日(2007.1.31)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

配線基板設計CAD装置により回路形成された配線基板の実装面に電子部品などを配置する配線基板の形成方法において、前記配線基板上に配置される電子部品などの寸法データと、電子部品の下部に高さ制限付きで他の電子部品の実装を許容する実装可能領域データと、下部に隙間を生ずる電子部品の隙間の高さ寸法に応じた実装部品の高さ制限値データと、電子部品などの実装禁止領域データと、回路配線禁止/実装禁止領域データとを基に、少なくとも高さ制限値データ内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とが視認可能に区画表示されたことを特徴とする配線基板設計における条件表示方法。

【請求項2】

隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して表示することを特徴とする請求項1記載の配線基板設計における条件表示方法。

【請求項3】

回路形成され、実装面に電子部品などが配置された配線基板において、高さ制限値内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とを配線基板上にシルク印刷等により視認可能に区画表示したことの特徴とする配線基板。

【請求項4】

隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して配線基板上にシルク印刷等により表示されることの特徴とする請求項3記載の配線基板。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【発明の詳細な説明】

【発明の名称】配線基板設計における条件表示方法及び配線基板

【技術分野】

【0001】

本発明は、C A D 装置などを使用して配線基板を形成する設計方法に関して、特に配線基板上に配置されるP C カードコネクターなどの電子部品の下部に生ずる隙間を有効利用して隙間高さに応じた電子部品を適正配置することを容易にするための技術分野に関する。

【背景技術】

【0002】

従来から複数の電子部品類を配置する配線基板の設計においては、限られた配線基板スペースの中に効率よく電子部品類を配置する目的で配線基板設計C A D 装置が広く利用され普及している。こうした中で、前記配線基板上にP C カードコネクターなどの電子部品が配置される場合においては、その下部に位置する配線基板との間にいくらかの隙間が生じていることがある。しかし、これら下部に生ずる電子部品と配線基板との隙間に隙間高さより低い他の電子部品を配置しようとする場合には、設計者が実際の電子部品を手に持ち、当該隙間を生ずる電子部品裏の段差寸法を実測して隙間高さ寸法に換算し、当該隙間に実装可能な隙間高さより低い他の電子部品を選択しながら配置するといった煩雑な作業を必要としていた。

【0003】

このようなC A D 装置による配線基板設計方法については、例えば次のような従来技術が知られている。特許文献1には、一方表面を部品面とし、他方表面を半田面とするプリント基板10に部品面側からリード線を半田面側に突出させて折曲げ及び半田付けを行う挿入型部品と、半田面側に装着される表面実装型部品34とを配置するための設計を支援する装置として、次のように紹介されている。図5において、半田面側に配置される表面実装型部品34の周囲に、該表面実装型部品の外形35に対する予め定める関係に基づいて、表面実装工程禁止領域36および挿入工程禁止領域37をそれぞれ設定する禁止領域設定手段と、禁止領域設定手段によって設定される表面実装工程禁止領域36または挿入工程禁止領域37を、他の表面実装型部品34の外形35または挿入型部品のリード線位置が侵害するか否かをそれぞれ判断し、判断結果を画像として表示する表示手段とを含むプリント基板用部品配置設計支援装置であり、半田面側に装着する表面実装型部品34の周囲には、部品外形等に基づいて、他の表面実装型部品34の装着を禁止する表面実装工程禁止領域36を設定する。また、挿入工程禁止領域37は、挿入部品のリード線の処理を行う挿入機工具の動作が表面実装部品34と干渉しないように設定し、表面実装型部品34の高さに応じて禁止領域の広さを変えるようにされている。また、挿入型部品に対しては、リード線の処理を行う挿入機工具に対応して挿入工程禁止領域37を設定し、動作に関連して、表面実装工程禁止領域36を表面実装型部品34の高さに応じて設定すると共に、各禁止領域同士で侵害の有無をチェックし、違反箇所を色と強調線で表示している。これにより、プリント基板に異なる工程で部品を実装する場合でも、C A D 装置等による侵害有無のチェックを可能にする。しかし、前記特許文献1に紹介された内容は、プリント基板10上に配置された電子部品の下に生ずる隙間に、隙間高さより低い他の電子部品を配置するための設計支援手段を保有した装置とはいえない。

【0004】

また、特許文献2には、実装基板の板面に、電子部品の搭載許容高さを表示するマークを実装基板の板面に設け、前記高さ表示マークが、所定高さ以内の電子部品を搭載する領域として実装基板の板面を区画するラインで表されると共に、当該高さ表示マークが、電子部品の搭載許容高さを表示する数値で表された。また、高さ表示マークが、所定高さ以内の電子部品を搭載する領域として実装基板の板面を区画するラインで表わすに加え、電

子部品の搭載許容高さを表示する数値で各領域内に表す方法が紹介されているが、当該特許文献2の方法は実装段階において表示された高さ制限を確認しながら電子部品を実装する工程のためのものであり、設計段階において設計者を支援するための方法とはいえない。

### 【0005】

【特許文献1】特開2000-331060号公報

【特許文献2】実開昭64-48065号公報

### 【発明の開示】

#### 【発明が解決しようとする課題】

### 【0006】

前記従来技術によれば、前記配線基板上にPCカードコネクターなどの電子部品が配置される場合においては、その下部に位置する配線基板との間にいくらかの隙間が生じていることがあり、これら下部に隙間を生ずる電子部品との隙間に隙間高さより低い他の電子部品を配置しようとする場合には、設計者が実際の電子部品を手に持ち、当該隙間を生ずる電子部品裏の段差寸法を実測して隙間高さ寸法に換算し、当該隙間に実装可能な隙間高さより低い他の電子部品を選択しながら配置するといった煩雑な作業を必要としていた。また、配線基板設計CAD装置を利用してこれら実装される電子部品の高さを制限される領域に、制限された高さに応じた電子部品を選択して配置するためには、前記配線基板設計CAD装置のプログラムの一部を変更して行うことが一般的であり、前記プログラム変更はコストを引き上げる要因のひとつでもあった。更に、配線基板上には少なくとも、回路配線も実装も禁止する領域と、実装を禁止する領域と、高さ制限付きで実装が可能な領域と、があり、配線基板を設計する段階ではこれらの区画を視認可能に表示する必要があると共に、前記高さ制限付き実装可能領域には当該高さ制限値を表示する必要がある。本明細書では前記回路配線も実装も禁止する領域を回路配線禁止/実装禁止領域として記載する。

### 【0007】

本発明は、配線基板設計CAD装置などにより配線基板の回路設計を行うにあたり、既存の配線基板設計CAD装置の設計支援機能を活用することにより、特に配線基板上に配置されるPCカードコネクターなどの電子部品の下部に生ずる隙間を有効利用して、前記隙間高さに応じた電子部品を適正配置することを容易にすることが出来る実用性に優れた配線基板の設計支援方法を提供すると共に、当該配線基板の設計方法を利用して配線基板の高密度実装を実現した電子機器を提供することを目的とする。

### 【課題を解決するための手段】

### 【0008】

請求項1に係る配線基板設計における条件表示方法は、配線基板設計CAD装置により回路形成された配線基板の実装面に電子部品などを配置する配線基板の形成方法において、前記配線基板上に配置される電子部品などの寸法データと、電子部品の下部に高さ制限付きで他の電子部品の実装を許容する実装可能領域データと、下部に隙間を生ずる電子部品の隙間の高さ寸法に応じた実装部品の高さ制限値データと、電子部品などの実装禁止領域データと、回路配線禁止/実装禁止領域データとを基に、少なくとも高さ制限値データ内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とが視認可能に区画表示されたことを特徴とする。

### 【0009】

請求項1の構成によれば、この配線基板設計における条件表示方法は、前記配線基板上に配置される電子部品などの寸法データと、電子部品の下部に高さ制限付きで他の電子部品の実装を許容する実装可能領域データと、下部に隙間を生ずる電子部品の隙間の高さ寸法に応じた実装部品の高さ制限値データと、電子部品などの実装禁止領域データと、回路配線禁止/実装禁止領域データとを基に、少なくとも高さ制限値データ内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とが視認可能に区画表示されたことにより、設計者は表示された当該作成途

中の図面を見ながら当該隙間領域には高さ制限内の電子部品が実装可能な高さ制限付き実装可能領域と、実装禁止領域と、回路配線禁止/実装禁止領域とがあることを認識することが出来る。

#### 【0010】

本発明の請求項2記載の配線基板設計における条件表示方法は、隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して表示することを特徴とする。

#### 【0011】

請求項2の構成によれば、隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して表示することにより、前記配線基板設計CAD装置に表示される作成途中の図面上において、設計者は当該高さ制限付き実装可能領域に表示される高さ制限値を表わす数値を見ながら実際に配置が可能な高さ制限値以内の電子部品を選択して適正配置することが出来る。

#### 【0012】

本発明の請求項3記載の配線基板は、回路形成され、実装面に電子部品などが配置された配線基板において、高さ制限値内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とを配線基板上にシルク印刷等により視認可能に区画表示したことを特徴とする。

#### 【0013】

請求項3の構成によれば、高さ制限値内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とを配線基板上にシルク印刷等により視認可能に区画表示したことにより、前記配線基板に実装する工程においても当該配線基板の当該隙間領域には高さ制限内の電子部品が実装可能な高さ制限付き実装可能領域と、実装禁止領域と、回路配線禁止/実装禁止領域とがあることを確認することが出来る。

#### 【0014】

本発明の請求項4記載の配線基板は、隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して配線基板上にシルク印刷等により表示されたことを特徴とする。

#### 【0015】

請求項4の構成によれば、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して配線基板上にシルク印刷等により表示されたことにより、前記配線基板に実装する工程においても当該配線基板を見て当該高さ制限付き実装可能領域の高さ制限値を確認することが出来る。

#### 【発明の効果】

#### 【0016】

請求項1に係る配線基板設計における条件表示方法の発明によれば、前記配線基板上に配置される電子部品などの寸法データと、電子部品の下部に高さ制限付きで他の電子部品の実装を許容する実装可能領域データと、下部に隙間を生ずる電子部品の隙間の高さ寸法に応じた実装部品の高さ制限値データと、電子部品などの実装禁止領域データと、回路配線禁止/実装禁止領域データとを基に、少なくとも高さ制限値データ内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とが視認可能に区画表示されたことにより、設計者は表示された当該作成中の図面を見ながら、当該隙間領域には高さ制限内の電子部品が実装可能な高さ制限付き実装可能領域と、実装禁止領域と、回路配線禁止/実装禁止領域とがあることを認識した上で前記隙間領域に表示された制限と禁止条件に基づき当該制限高さ内の電子部品を選択して配置し、回路配線を行うことが出来ることから、効率よく適正な配線基板の設計を行うことができると共に、下部に隙間を生ずる電子部品と当該配線基板との隙間領域を有効に利用することにより配線基板の高密度実装が成される。

#### 【0017】

請求項 2 に係る配線基板設計における条件表示方法の発明によれば、隙間領域において、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して表示することにより、前記配線基板設計 C A D 装置に表示される作成途中の図面上において、設計者は当該高さ制限付き実装可能領域に表示される高さ制限値を表わす数値を見ながら実際に配置が可能な高さ制限値以内の電子部品を選択して適正配置することが出来る。これにより、従来例のように設計者が前記配線基板設計 C A D 装置に表示された製作途中の図面上に配置した前記下部に隙間を生ずる電子部品を前に、当該隙間を生ずる電子部品の段差寸法を実測して隙間高さ寸法に換算し、当該隙間に実装可能な隙間高さより低い他の電子部品を選択しながら配置するといった煩雑な作業は必要がなくなると共に、これら実装される電子部品の高さを制限される領域に、配線基板設計 C A D 装置を利用して制限された高さに応じた電子部品を選択して配置するためには、前記配線基板設計 C A D 装置のプログラムの一部を変更して行うことも必要はなくなり、前記プログラム変更によるコストアップも回避される。

#### 【 0 0 1 8 】

請求項 3 に係る配線基板の発明によれば、高さ制限値内で電子部品が実装可能な高さ制限付き実装可能領域と、電子部品などの実装禁止領域と、回路配線禁止/実装禁止領域とを配線基板上にシルク印刷等により視認可能に区画表示したことにより、前記配線基板に実装する工程においても当該配線基板の当該隙間領域には高さ制限内の電子部品が実装可能な高さ制限付き実装可能領域と、実装禁止領域と、回路配線禁止/実装禁止領域とがあることを確認することが出来ることにより、当該高さ制限付き実装可能領域には高さ制限値を満たす電子部品が先に実装され、続いて下部に隙間を生ずる電子部品を実装するなどと実装工程の段取りを明確にすることが出来る。

#### 【 0 0 1 9 】

請求項 4 に係る配線基板の発明によれば、前記高さ制限付き実装可能領域は所定の高さ制限値ごとに区画されると共に、高さ制限値を表わす数値を付して配線基板上にシルク印刷等により表示されたことにより、前記線基板に実装する工程においても当該配線基板を見て当該高さ制限付き実装可能領域の高さ制限値を確認することが出来ると共に、当該領域に実装するために用意された電子部品類の高さなどを確認することが出来る。

#### 【 発明を実施するための最良の形態 】

#### 【 0 0 2 0 】

以下、本発明を実施するための最良の形態としての実施例を図 1 ~ 図 4 により以下に説明する。もちろん、本発明は、その発明の趣旨に反さない範囲で、実施例において説明した以外のものに対しても容易に適用可能なことは説明するまでもない。

#### 【 0 0 2 1 】

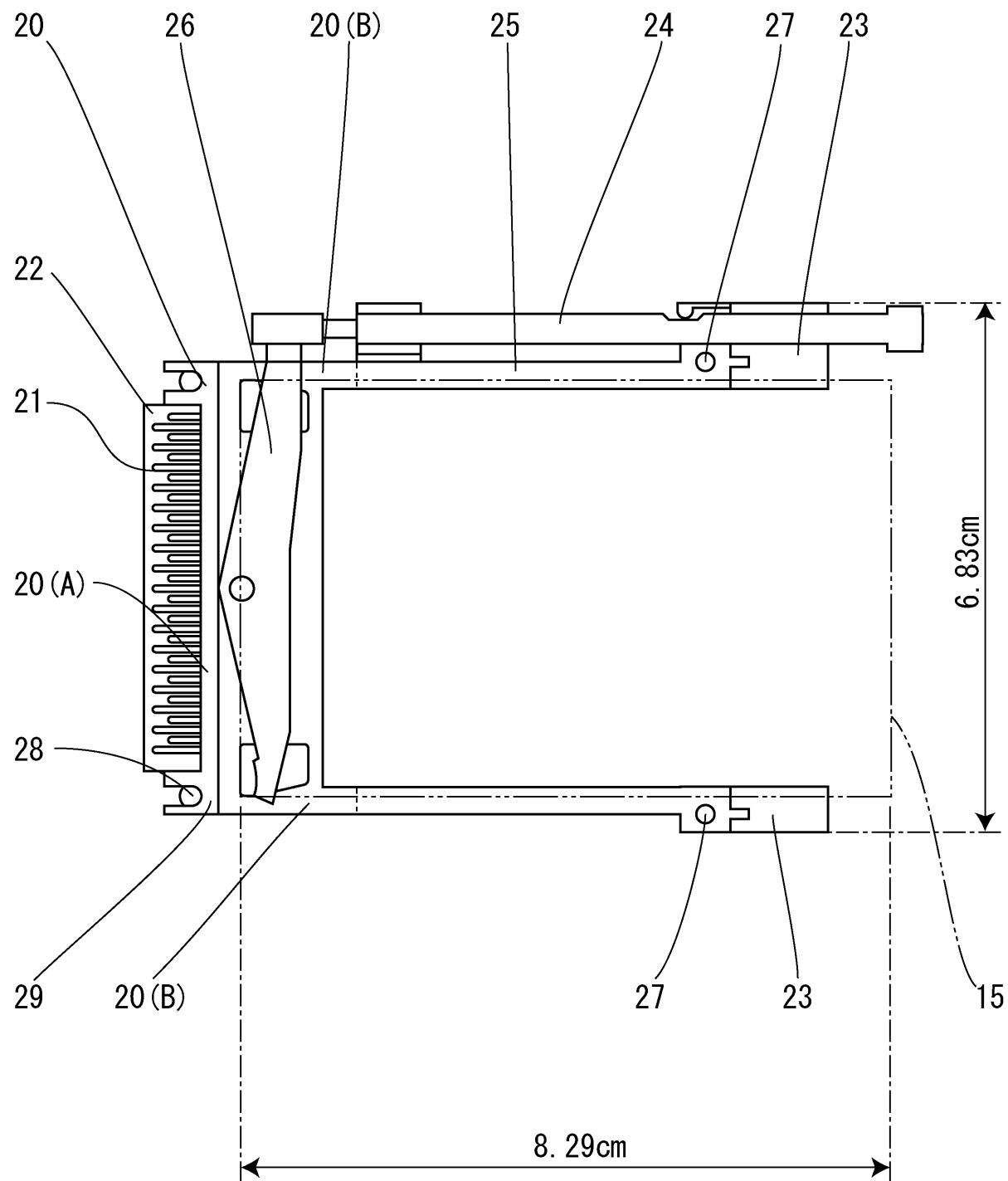

図 1 は本発明の一実施例を示す配線基板上に配置された電子部品の下部に生じた隙間領域を示す側面説明図であり、図 2 は本発明の一実施例を示す下部に隙間を生ずる電子部品を上から見た平面説明図である。また、図 3 は本発明の一実施例を示す配線基板設計 C A D 装置に表示された高さ制限付き実装可能領域と高さ制限値を表わす数値の表示例であり、図 4 は本発明の一実施例を示す高さ制限付き実装可能領域の区画表示により部品配置した配線基板 1 0 上のシルク印刷の説明図である。

#### 【 0 0 2 2 】

まず、下部に隙間を生ずる電子部品 2 0 の一例である、P C カードコネクター 2 0 について図 2 を参照しながら以下に説明する。

#### 【 0 0 2 3 】

図 2 に示す P C カードコネクター 2 0 は略コの字型をしており、略コの字の大きな凹み部は P C カード 1 5 が装填される領域である。また、そのコネクター基部 2 0 ( A ) の両縁には配線基板 1 0 に固定するための支持体部 2 0 ( B ) が左右一対に形成され、それぞれにナット 2 8 がハウジング部 2 9 により装着されている。また、前記コネクター基部 2 0 ( A ) には複数のコンタクト端子 2 1 が整列配置されており、その片端側には P C カード 1 5 のソケット( 図示略 )と当該カードコネクター 2 0 が接続されると共に、前記複数

のコンタクト端子 21 は配線基板 10 方向に L 字形に折れ曲がり前記コネクター基部 20 (A) に支持固定されたロケータ部 22 の貫通孔を介して配線基板 10 と接続される。また、当該カードコネクター 20 にはコネクター基部 20 (A) の両端から PC カード 15 を装填したときにその両側面を支持するためのガイドバー部 23 が左右一対を成すように突出して形成されており、金属製のフレーム 25 によって前記コネクター基部 20 (A) と前記ガイドバー部 23 は接続固定されている。さらに、前記一対のガイドバー部 23 の先端側にナット付きハトメ 27 が取り付けられており、前記配線基板 10 とビスで固定可能な構造となっている。更に、前記ガイドバー部 23 の片方の側面には、装填された PC カード 15 を取り出すためのプッシュバー 24 が備えられており、前記金属製のフレーム 25 と首振り自在に固定された回転アーム 26 の一端とが連結されることによりプッシュバー 24 を押すと回転アーム 26 が回転方向に動いて PC カード 15 を取り出せるように構成されている。

#### 【 0 0 2 4 】

こうした PC カードコネクター 20 を配線基板 10 に取り付けた場合、配線基板 10 と直接接する部分である前記カードコネクター 20 の支持体部 20 (B) とロケータ部 22 、及びガイドバー部 23 に配置されたナット付きハトメ 27 は配線基板 10 と接する面があり、当該接する面は他の電子部品を実装することが出来ない実装禁止領域 32 となる。特に、前記ナット付きハトメ 27 は金属であり配線基板 10 に直接接触してビス止めされるため回路配線が出来ない回路配線禁止領域となる。したがって、前記コネクター 20 の支持体部 20 (B) とロケータ部 22 とが接する配線基板 10 面は実装禁止領域 32 であり、前記ナット付きハトメ 27 と接する配線基板 10 面は回路配線禁止 / 実装禁止領域 33 となる。また、前記 2 種類の禁止領域を除き、PC カード 15 が実装されたときを想定した PC カードコネクター 20 の下部となる残りの領域は、概ね PC カード 15 の挿入口側の総幅 (6.83 cm) × PC カードの奥行き (8.29 cm) = 56.6 平方 cm で、この領域には配線基板 10 と当該 PC カードコネクター 20 との隙間が確保されており、前記隙間高さ寸法 40 以内の電子部品であれば実装が可能な高さ制限付き実装可能領域 31 となる。

#### 【 0 0 2 5 】

続いて、配線基板 10 上に配置された PC カードコネクター 20 における配線基板 10 と PC カードコネクター 20 との間に生ずる隙間領域 30 について図 1 に示す PC カードコネクターを配線基板に実装したときの側面図と、図 2 の PC カードコネクターの平面図を参照しながら以下に説明する。

#### 【 0 0 2 6 】

図 1、図 2 に示すように、前記 PC カードコネクター 20 に PC カード 15 を装填したとき、それらの下部となる領域において、前記カードコネクター 20 の支持体部 20 (B) とロケータ部 22 とが接する配線基板 10 面は実装禁止領域 32 であり、ガイドバー 23 に備えられたナット付きハトメ 27 と接する配線基板 10 面は回路配線禁止 / 実装禁止領域 33 となる。また、前記 2 種類の禁止領域を除き、PC カード 15 が装填されたときに PC カードコネクター 20 の下部となる残りの領域は図 1 に示すように配線基板 10 との間に隙間領域 30 が確保されており、前記隙間高さ以内の電子部品 50 であれば実装が可能な高さ制限付き実装可能領域 31 となる。このときの隙間高さ寸法 40 に対して、若干の余裕度を持たせた高さ制限値 41 を設定することで、この高さ制限値 41 と同等以下で高さ制限値を満たす電子部品 50 が配置可能となり、この隙間領域 30 に配置する当該電子部品 50 が前記 PC カードコネクター 20 や PC カードに接触することは避けることが出来る。これは次のような関係式で表わされ、隙間高さ寸法 40 > 高さ制限値 41 高さ制限値を満たす電子部品 50 の高さ、となる。更に図 1 を参照しながら詳細に説明を加えれば、前記制限付き実装可能領域 31 において、前記 PC カードコネクター 20 のガイドバー 23 には PC カード 15 が装填するためのガイドレールが前記 PC カード 15 の厚さに対応して溝状に設けてあり、ここに装填された PC カード 15 の底面と配線基板 10 との B 隙間高さ寸法 40 (B) は 6 mm とガイドレールの肉厚に相当する分だけ高い位置

となる。従って、前記 P C カードコネクター 2 0 のガイドバー 2 3 やプッシュバー 2 4 の下部となる A 隙間高さ寸法 4 0 ( A ) が 5 mm と前記 B 隙間高さ寸法 4 0 ( B ) より低く、 P C カードコネクター 2 0 の下部となる領域と、 P C カード 1 5 の下部となる領域とで隙間高さが異なる 2 つの領域に分けて活用することが出来る。図 1 には装填された P C カード 1 5 の底面と配線基板 1 0 においては、若干の余裕度を持たせて B 隙間高さ 4 0 ( B ) の 6 mm に対応した B 高さ制限値 4 1 ( B ) は 4 mm とし、前記 P C カードコネクター 2 0 のガイドバー 2 3 やプッシュバー 2 4 の下部となる A 隙間高さ寸法 4 0 ( A ) が 5 mm であるので A 高さ制限値 4 1 ( A ) は 3 mm と設定してある。

#### 【 0 0 2 7 】

次に、配線基板設計 CAD 装置に前記下部に隙間を生ずる電子部品である P C カードコネクター 2 0 のデータを入力し、表示された高さ制限付き実装可能領域 3 1 と、高さ制限値 4 1 を表わす数値の表示例について、図 3 を参照しながら以下に説明する。

#### 【 0 0 2 8 】

設計者が、前記配線基板 1 0 上に配置される P C カードコネクター 2 0 下部の隙間領域 3 0 に配置可能な高さ制限値を満たす電子部品 5 0 を配置しようとするには、まず当該カードコネクター 2 0 のカタログに掲載された形状寸法図と、当該カードコネクター 2 0 に P C カード 1 5 が装填された場合を想定した形状寸法図を参照しながら平面配置に関する当該形状寸法データを入力して、作成中の配線基板 1 0 を表示した図面上の所定の位置に前記カードコネクター 2 0 の輪郭線を配置して表示させる。このとき、 P C カードコネクター 2 0 の一部であるプッシュバー 2 4 の先端は電子機器の筐体外部に突き出す領域であり、前記配線基板 1 0 から前記輪郭線の一部が外部に食み出して描かれている。

#### 【 0 0 2 9 】

次に、前記カードコネクター 2 0 の下部となる領域のうち、前記カードコネクター 2 0 の支持体部 2 0 ( B ) とロケータ部 2 2 とが接する配線基板 1 0 面、及び配線基板 1 0 の外周縁部は電子部品類の実装を禁止する実装禁止領域 3 2 であり、ナット付きハトメ 2 7 と接する配線基板 1 0 面の回路配線禁止/実装禁止領域 3 3 と共に作成中の図面に区画を表わす線と網掛けなどにより表示させる。この時点では、前記 2 種類の禁止領域を除き、 P C カード 1 5 が装填されたときを想定した P C カードコネクター 2 0 の下部となる残りの領域は、配線基板 1 0 と当該 P C カードコネクター 2 0 との間に隙間領域 3 0 が確保されており、前記隙間高さ以内の高さ制限を満たす電子部品 5 0 であれば実装が可能な高さ制限付き実装可能領域 3 1 である。この領域は、 P C カード 1 5 の下部と、 P C カードコネクター 2 0 の下部とで若干の隙間高さが異なる。前記 P C カードコネクター 2 0 の下部の隙間高さは 5 mm であるが、全体の領域において前記 P C カード 1 5 の下部は 6 mm の隙間高さが確保されている。本実施例において、設計者はこの隙間高さの差により 2 種類の実装が可能な高さ制限付き実装可能領域 3 1 を設け、当該高さ制限付き実装可能領域 3 1 を示す区画線を通常と異なる線種で表示することにより視認可能に区画表示させた。

#### 【 0 0 3 0 】

続いて、前記 2 種類の高さ制限付き実装可能領域 3 1 には、図 1 に示す配線基板 1 0 に取り付けるときの取り付け基準面 5 1 に対する当該カードコネクター 2 0 裏面の段差寸法 5 mm を A 隙間高さ寸法 4 0 ( A ) とし、続いて P C カード 1 5 装填時の当該 P C カード 1 5 裏面と前記取り付け基準面 5 1 との段差寸法 6 mm を B 隙間高さ 4 0 ( B ) として当該 P C カードコネクター 2 0 のカタログに掲載された形状寸法図から読み出して、前記段差寸法、即ち前記 A 隙間高さ寸法 4 0 ( A ) 、及び B 隙間高さ寸法 4 0 ( B ) より若干低く設定した A 高さ制限値 4 1 ( A ) を 3 mm 、及び B 高さ寸法 4 1 ( B ) を 4 mm として前記配線基板設計 CAD 装置の CAD メニューに入力し、 A 高さ制限付き実装可能領域 3 1 ( A ) 、及び B 高さ制限付き実装可能領域 3 1 ( B ) の領域内に、それぞれ A 高さ制限値 4 1 ( A ) は 3 mm 、及び B 高さ制限値 4 1 ( B ) は 4 mm として表示させる。これにより、従来においては、下部にどのような隙間を生じているかを表示する手段がなく、設計者が配線基板設計 CAD 装置に表示された製作途中の図面上に配置した前記下部に隙間を生ずる部品を手に持ち、当該隙間を生ずる電子部品裏の段差寸法を実測して隙間高さ寸

法40に換算し、当該隙間に実装可能な隙間高さより低い他の電子部品を選択しながら配置するといった煩雑な作業を回避することが出来る。

#### 【0031】

以上の手順により、既存の配線基板設計CAD装置の設計支援機能を活用しながら複数の高さ制限付き実装可能領域31(A)、31(B)は異なる線種で区画表示され、各々の高さ制限値を表示することが出来たことにより、設計者は表示された当該作成途中の図面を見ながら当該隙間領域30は高さ制限値41(A)、41(B)に応じて異なる高さ制限内の電子部品50(A)、50(B)が実装可能な所定の高さ制限付き実装可能領域31(A)、31(B)であることを認識した上で前記隙間領域30に当該制限高さ以内の電子部品50(A)、50(B)を選択して配置し、回路配線を行うことが出来ることから、当該隙間高さ寸法40に応じた電子部品50を適正に選択して配置した配線基板10を効率よく設計することができると共に、電子部品20の下部に生ずる隙間を有効に活用して他の電子部品50を配置することが出来ることから、当該配線基板10上には、より一層の高密度実装を実現する能够性と共に、既存の配線基板設計CAD装置の設計支援機能を活用して電子部品20の下部に生ずる隙間に他の電子部品50を配置することが出来ることから、従来のように、配線基板設計CAD装置のプログラムの一部を変更する必要もなく、プログラム変更に要するコストと労力は不要となる。

#### 【0032】

続いて、前記表示された高さ制限付き実装可能領域の区画表示により部品配置した配線基板10上のシルク印刷の実施例について図4を参照しながら説明する。

#### 【0033】

本実施例における図4はシルク印刷の表示だけではPCカードコネクター20の下部にどんな電子部品が配置されているかが解り辛いため、敢えて当該高さ制限付き実装可能領域には電子部品が実装されたように記載してある。配線基板10の表面にはシルク印刷によりPCカードコネクター20の下部に生ずる隙間領域の高さ制限付き実装可能領域を表示する区画線と、各々の実装可能領域31に対応した高さ制限値41が印刷表示されていると共に、配線基板の外周縁部と前記カードコネクター20の支持体部20(B)とロケータ部22とが接する配線基板10面の2箇所の実装禁止領域32が網掛けなどで印刷表示されており、回路配線禁止/実装禁止領域33が塗りつぶしで印刷表示されている。更に、PCカードコネクター20裏面のA高さ制限付き実装可能領域31(A)には、A高さ制限値41(A)の3mmを満たすチップ抵抗器などが配置され、当該部品の種類を示す図形などがシルク印刷されている。また、PCカード15の裏面となるB高さ制限付き実装可能領域(B)には、B高さ制限値41(B)の4mmを満たすICなど複数の電子部品50が効率よく配置されていると共に当該部品の種類を示す図形などがシルク印刷されている。

#### 【0034】

以上のように本実施例によれば、本発明の配線基板設計における条件表示方法は、電子部品20の下部に生ずる隙間領域30における配線基板10との取り付け基準面51に対する段差寸法を当該電子部品20のカタログに掲載された形状寸法図から読み出して、前記隙間領域30と、前記段差寸法を前記隙間高さ寸法40に対応した高さ制限に換算した当該高さ制限値41とを前記配線基板設計CAD装置のCADメニューに入力することにより、既存の配線基板設計CAD装置の設計支援機能を活用して、前記隙間領域30の前記隙間高さ寸法40を許容する高さ制限値41内の電子部品50が実装可能な高さ制限付き実装可能領域31を視認可能に区画表示する能够性と共に、当該高さ制限値41を前記区画表示された高さ制限付き実装可能領域31に数値で表示することにより、設計者は配線基板設計CAD装置に表示された当該作成途中の図面を見ながら、当該隙間領域30は高さ制限内の電子部品50が実装可能な高さ制限付き実装可能領域31であることを認識した上で前記隙間領域30に当該制限高さ内の電子部品50を選択して配置し、回路配線を行う能够性と共に、下部に隙間を生ずる電子部品20と当該配線基板10との隙間領域30を有

効に利用することにより配線基板 10 の高密度実装が成される。また、従来例のように、前記電子部品 20 の下部にどのような隙間が生じているかが解らないため、設計者が前記配線基板設計 CAD 装置に表示された製作途中の図面上に配置した前記下部に隙間を生ずる電子部品 20 を前に、当該隙間を生ずる電子部品 20 の段差寸法を実測して隙間高さ寸法 40 に換算し、当該隙間に実装可能な隙間高さより低い他の電子部品 50 を選択しながら配置するといった煩雑な作業は解消されることから、本発明は実用性に優れた配線基板 10 の設計支援方法といえると共に、既存の配線基板設計 CAD 装置の設計支援機能を活用することにより配線基板設計 CAD 装置のプログラムの一部を変更することも必要がなく、プログラム変更に要するコストと労力は不要となる。また、前記禁止領域や高さ制限付き実装可能領域、高さ制限値を配線基板にシルク印刷表示することにより、電子部品の実装工程においても工程の段取りが容易になると共に電子部品の確認が可能となり、不要な品質トラブルも未然に回避することが出来る。

#### 【0035】

以上、本実施例を詳述したが、本発明は、前記実施例に限定されるものではなく、本発明の要旨の範囲内で種々の变形実施が可能である。例えば、下部に隙間を生ずる電子部品 20 は P C コネクターのようなものに限らず、電子機器内部に配置される D V D 装置や H D D 装置等と配線基板 10 上に配置される電子装置のように配線基板 10 上において、その下部に隙間を生ずる装置類でもよく、また、高さ制限付き実装可能領域を区画表示する手段としては異なる線種の他、当該領域に網掛けをするなどにより視認を容易にするなど、設計者が配線基板 10 の設計時における使い易さを配慮して変更するなど前記実施例に限定されるものではなく、適宜選定すればよい。

#### 【図面の簡単な説明】

#### 【0036】

【図 1】本発明の一実施例を示す配線基板上に配置された電子部品の下部に生じた隙間領域を示す側面説明図である。

【図 2】本発明の一実施例を示す下部に隙間を生ずる電子部品を上から見た平面説明図である。

【図 3】本発明の一実施例を示す配線基板設計 CAD 装置に表示された高さ制限付き実装可能領域と高さ制限値を表わす数値の表示例である。

【図 4】本発明の一実施例を示す高さ制限付き実装可能領域の区画表示により部品配置した配線基板 10 上のシルク印刷の説明図である。

【図 5】従来の基本的な禁止領域の設定状態を示す説明図である。

#### 【符号の説明】

#### 【0037】

- 10 配線基板

- 20 下部に隙間を生ずる電子部品（P C カードコネクター）

- 30 隙間領域

- 31 高さ制限付き実装可能領域

- 40 隙間高さ寸法

- 41 高さ制限値

- 50 高さ制限値を満たす電子部品

#### 【手続補正 3】

【補正対象書類名】図面

【補正対象項目名】図 2

【補正方法】変更

【補正の内容】

【図2】