(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-47829

(P2004-47829A)

(43) 公開日 平成16年2月12日(2004.2.12)

(51) Int.CI.<sup>7</sup>

**H01L 21/82**

**G06F 17/50**

**H01L 21/822**

**H01L 23/12**

**H01L 27/04**

F 1

H01L 21/82

G06F 17/50 658A

G06F 17/50 658K

G06F 17/50 658Z

G06F 17/50 666Z

テーマコード(参考)

5B046

5FO38

5FO64

審査請求 未請求 請求項の数 13 O L (全 19 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2002-204776 (P2002-204776)

平成14年7月12日 (2002.7.12)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100068342

弁理士 三好 保男

(74) 代理人 100100712

弁理士 岩▲崎▼ 幸邦

(74) 代理人 100100929

弁理士 川又 澄雄

(74) 代理人 100108707

弁理士 中村 友之

(74) 代理人 100095500

弁理士 伊藤 正和

最終頁に続く

(54) 【発明の名称】半導体装置の接続端子設計装置、半導体装置の接続端子設計方法、及び半導体装置の接続端子設計プログラム

## (57) 【要約】

【課題】接続端子の割り当てを効率的に且つ設計ルールに正確に行うことができる半導体装置の接続端子設計装置等を提供する。

【解決手段】半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置する電源セル配置部と、複数の入出力スロットの他の一部に入出力信号セルを配置する入出力信号セル配置部と、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成する第1の接続ネット生成部と、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成する第2の接続ネット生成部と、電源セル、入出力信号セル、及び第1及び第2の接続ネットが所定の設計ルールに違反しているか否かを検証する検証部とを有する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体チップ内に配設された複数の入出力スロットの一部に、電源セルを配置する電源セル配置部と、

前記複数の入出力スロットの他の一部に、入出力信号セルを配置する入出力信号セル配置部と、

前記複数の入出力スロットと前記半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成する第1の接続ネット生成部と、

前記複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成する第2の接続ネット生成部と、

前記電源セル、前記入出力信号セル、及び前記第1及び第2の接続ネットが、所定の設計ルールに違反しているか否かを検証する検証部と

を有することを特徴とする半導体装置の接続端子設計装置。

**【請求項 2】**

前記第1の接続ネット生成部は、前記電源セル又は前記入出力信号セルが配置された前記複数の入出力スロットと前記複数のバンプとの間を接続する前記第1の接続ネットを生成し、

前記第2の接続ネット生成部は、前記第1の接続ネットによって前記複数の入出力スロットに接続された前記複数のバンプと前記複数の外部電極との間を接続する前記第2の接続ネットを生成することを特徴とする請求項1記載の半導体装置の接続端子設計装置。

**【請求項 3】**

前記複数のバンプは前記半導体チップの主表面全体に配設され、前記複数の外部電極は前記パッケージ基体の主表面全体に配設されていることを特徴とする請求項1記載の半導体装置の接続端子設計装置。

**【請求項 4】**

前記所定の設計ルールには、

前記電源セルの数及び配置位置に関する電源セル配置ルールと、

前記入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールと、

等長配線の要求、ペア配線の要求、接続ネット同士が交差する数の制限、及び最大配線長に関する接続ピン配置ルールと

が含まれることを特徴とする請求項1記載の半導体装置の接続端子設計装置。

**【請求項 5】**

前記電源セル配置部は、前記電源セルの数及び配置位置に関する電源セル配置ルールに従って、前記電源セルを配置し、

前記入出力信号セル配置部は、前記入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールに従って、前記入出力信号セルを配置し、

前記第1及び第2の接続ネット生成部は、等長配線の要求、ペア配線の要求、接続ネット同士が交差する数の制限、及び最大配線長に関する接続ピン配置ルールに従って、前記第1及び第2の接続ネットをそれぞれ生成する

ことを特徴とする請求項1記載の半導体装置の接続端子設計装置。

**【請求項 6】**

半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置し、

前記複数の入出力スロットの他の一部に入出力信号セルを配置し、

前記複数の入出力スロットと前記半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成し、

前記複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成し、

前記電源セル、前記入出力信号セル、及び前記第1及び第2の接続ネットが、所定の設計ルールに違反しているか否かを検証する

ことを特徴とする半導体装置の接続端子設計方法。

10

20

30

40

50

**【請求項 7】**

前記第1の接続ネットは、前記電源セル及び前記入出力信号セルを配置した後に生成され

、

前記第2の接続ネットは、前記第1の接続ネットを生成した後に生成されることを特徴とする請求項6記載の半導体装置の接続端子設計方法。

**【請求項 8】**

前記所定の設計ルールには、

前記電源セルの数及び配置位置に関する電源セル配置ルールと、

前記入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールと、

等長配線の要求、ペア配線の要求、接続ネット同士が交差する数の制限、及び最大配線長 10

に関する接続ピン配置ルールと

が含まれることを特徴とする請求項6記載の半導体装置の接続端子設計方法。

**【請求項 9】**

前記電源セルは、当該電源セルの数及び配置位置に関する電源セル配置ルールに従って配置され、

前記入出力信号セルは、当該入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールに従って配置され、

前記第1及び第2の接続ネットは、等長配線の要求、ペア配線の要求、接続ネット同士が交差する数の制限、及び最大配線長に関する接続ピン配置ルールに従ってそれぞれ生成される 20

ことを特徴とする請求項6記載の半導体装置の接続端子設計方法。

**【請求項 10】**

コンピュータに、

半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置し、

前記複数の入出力スロットの他の一部に入出力信号セルを配置し、

前記複数の入出力スロットと前記半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成し、

前記複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成し、

前記電源セル、前記入出力信号セル、及び前記第1及び第2の接続ネットが、所定の設計 30

ルールに違反しているか否かを検証する

ことを実行させることを特徴とする半導体装置の接続端子設計プログラム。

**【請求項 11】**

前記第1の接続ネットは、前記電源セル及び前記入出力信号セルを配置した後に生成され

、

前記第2の接続ネットは、前記第1の接続ネットを生成した後に生成されることを特徴とする請求項10記載の半導体装置の接続端子設計プログラム。

**【請求項 12】**

前記所定の設計ルールには、

前記電源セルの数及び配置位置に関する電源セル配置ルールと、

前記入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールと、

等長配線の要求、ペア配線の要求、接続ネット同士が交差する数の制限、及び最大配線長 40

に関する接続ピン配置ルールと

が含まれることを特徴とする請求項10記載の半導体装置の接続端子設計プログラム。

**【請求項 13】**

前記電源セルは、当該電源セルの数及び配置位置に関する電源セル配置ルールに従って配置され、

前記入出力信号セルは、当該入出力信号セルの大きさ及び配置禁止領域に関する入出力信号セル配置ルールに従って配置され、

前記第1及び第2の接続ネットは、等長配線の要求、ペア配線の要求、接続ネット同士が 50

交差する数の制限、及び最大配線長に関する接続ピン配置ルールに従ってそれぞれ生成される

ことを特徴とする請求項10記載の半導体装置の接続端子設計プログラム。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体装置の接続端子設計装置、半導体装置の接続端子設計方法、及び半導体装置の接続端子設計プログラムに関わり、特に、半導体設計フローにおいて、チップ自動配置配線工程及びパッケージ基板詳細設計工程の前に行われるピニアサイン工程に関する。また特に、本発明は、複数のバンプ或いは外部電極が格子状に配置されたフリップチップパッケージ或いはBGA等の高密度実装半導体パッケージの設計に係る。

10

【0002】

【従来の技術】

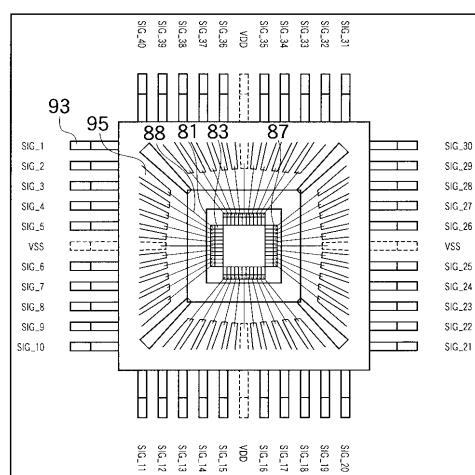

図11に示すように、従来のクワッドフラットパッケージ(Quad Flat Pack package:QFP)において、パッケージ最外周に配置されたパッケージピン93と、パッケージ内部において半導体チップ81に接続されるインナーリードピン95は、共にパッケージ外周に沿って線状に配設されている。したがって、両者の対応関係は明確である。また、半導体チップ81内のボンディングパッド87は、半導体チップ81の外周に沿って線状に配設されているため、インナーリードピン95とボンディングパッド87との対応関係は明確であり、両者の相対的な配置順序も同じである。更に、ボンディングパッド87と半導体チップ81内の入出力スロット83との対応関係も明確であり、両者の相対的な配置順序も同じである。

20

【0003】

したがって、図11に示すSIG1~40、VDD、VSSなどの信号をパッケージピン93にそれぞれ割り当てるとき、インナーリードピン95及びボンディングパッド83に割り当てられる信号も自動的に定まる。即ち、パッケージピン93からボンディングパッド83までの接続ネットはおのずと決まる。また更に、入出力バッファが置かれる入出力スロット83の位置、及びボンディングパッド87と入出力スロット83間の接続ネットもおのずと決まる。また、隣接する入出力スロット83に割り当たられる差動バッファセル等の特定のセルは、パッケージピン93のレベルにおいて隣接して配置することで、入出力スロット83のレベルにおいても自動的に隣接して配置される。なお、上記のQFPに係る接続端子の割り当て(ピニアサイン)は、ピン接続を単層で行うボールグリッドアレイ(Ball Grid array:BGA)等についても同様である。

30

【0004】

【発明が解決しようとする課題】

しかしながら、ピン接続を複数層で行うBGA(以後、単に「BGA」と呼ぶ)又はフリップチップパッケージなどの、近年の半導体装置の高密度実装・多ピン化に対応できるパッケージは、以下に示すにような従来のQFP等との構造上の相違点から様々な技術的問題点を有する。

40

【0005】

BGAでは、複数の外部電極(ボール型電極)はパッケージ基体の主表面に格子状に配設されている。BGAの外部電極は、QFPのパッケージピン93に対応する。また、フリップチップパッケージでは、複数のバンプ(突起状電極)が半導体チップの主表面に格子状に配設され、半導体チップはバンプを介してパッケージ基体にパッケージングされている。即ち、外部電極とバンプ間及びバンプと入出力スロット間の対応関係は明確であるとは言えず、相対的な配置順序も同じとは言えない。

【0006】

従って、信号を外部電極に割り当ても、バンプ及び入出力スロットに自動的に信号が割り当たることがなく、外部電極だけでなく、バンプ及び入出力スロットのピニアサイン作業をそれぞれ行わなければならない。

50

**【 0 0 0 7 】**

また、一般的に、チップ上のバンプからパッケージ基体の外部端子までの接続ネットは、設計の初期段階では放射状に設計する。BGAにおいて接続ネットを放射状に設計した場合、差動バッファの信号を隣接する外部電極に割り当てても、バンプのレベルで隣接して割り当てることができないことがある。更に、入出力スロットのレベルでは、より高い確率で差動バッファセルの隣接が不可能となる。同様に、セル仕様から要求される等長配線・ペア配線等の設計要求を満たすことが困難となる。これらの問題を解消すべく外部端子、バンプ及び入出力スロットへの信号の割り当てを変更すると、接続ネットの配線交差数が増大して、詳細な配線設計が困難になるなどの別の問題が生じてしまう。

**【 0 0 0 8 】**

更に、これらの設計ルールに基いて接続端子（外部電極、バンプ及び入出力スロット）の配置を検証する具体的手段は存在しない。よって、設計ルールによる検証は設計者の手作業で出来る範囲に絞られ、最終的な製造可否の判断は、チップ自動配置配線工程・パッケージ詳細設計工程に委ねられていた。そのため、ピンアサイン以降の工程においてピンアサイン起因のエラーが発見された場合、チップ自動配置配線工程及びパッケージ詳細設計工程の両方をやり直す可能性が大きかった。

**【 0 0 0 9 】**

近年のピン数の増大、設計制約の複雑化に伴い、上記の技術的問題点は作業時間増大の問題と相まって深刻化している。

**【 0 0 1 0 】**

本発明はこのような従来技術の問題点を解決するために成されたものであり、その目的は、接続端子の割り当てを、効率的に且つ設計ルールに正確に行うことができる半導体装置の接続端子設計装置、半導体装置の接続端子設計方法、及び半導体装置の接続端子設計プログラムを提供することである。

**【 0 0 1 1 】****【課題を解決するための手段】**

上記目的を達成するため、本発明の第1の特徴は、半導体チップ内に配設された複数の入出力スロットの一部に、電源セルを配置する電源セル配置部と、複数の入出力スロットの他の一部に入出力信号セルを配置する入出力信号セル配置部と、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成する第1の接続ネット生成部と、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成する第2の接続ネット生成部と、電源セル、入出力信号セル、及び第1及び第2の接続ネットが所定の設計ルールに違反しているか否かを検証する検証部とを有する半導体装置の接続端子設計装置であることである。

**【 0 0 1 2 】**

本発明の第1の特徴によれば、電源セル配置部、入出力信号セル配置部、及び第1及び第2の接続ネット生成部は、入出力スロット、バンプ、外部電極などの複数種類の接続端子に対して、それぞれ電源信号或いは入出力信号を割り当てる。そして、検証部は、各接続端子について所定の設計ルールに従った検証を行う。従って、外部電極とバンプ間及びバンプと入出力スロット間の対応関係は明確であるとは言えず、相対的な配置順序も同じとは言えない場合であっても、所定の設計ルールに違反することなく、接続端子に信号を効率的に割り当ることができる。

**【 0 0 1 3 】**

本発明の第2の特徴は、半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置し、複数の入出力スロットの他の一部に入出力信号セルを配置し、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成し、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成し、電源セル、入出力信号セル、及び第1及び第2の接続ネットが所定の設計ルールに違反しているか否かを検証する半導体装置の接続端子設計方法であることである。

10

20

30

40

50

**【 0 0 1 4 】**

本発明の第3の特徴は、コンピュータに、半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置し、複数の入出力スロットの他の一部に入出力信号セルを配置し、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成し、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成し、電源セル、入出力信号セル、及び第1及び第2の接続ネットが所定の設計ルールに違反しているか否かを検証することを実行させる半導体装置の接続端子設計プログラムであることである。

**【 0 0 1 5 】**

本発明の第2及び第3の特徴によれば、入出力スロット、バンプ、外部電極などの複数種類の接続端子に対してそれぞれ電源信号或いは入出力信号を割り当てる。そして、各接続端子について所定の設計ルールに従った検証を行う。従って、外部電極とバンプ間及びバンプと入出力スロット間の対応関係は明確であるとは言えず、相対的な配置順序も同じとは言えない場合であっても、所定の設計ルールに違反することなく、接続端子に信号を効率的に割り当ることができる。

**【 0 0 1 6 】****【 発明の実施の形態 】**

以下図面を参照して、本発明の実施の形態を説明する。図面の記載において同一あるいは類似の部分には同一あるいは類似な符号を付している。ただし、図面は模式的なものであり、層の厚みと幅との関係、各層の厚みの比率などは現実のものとは異なることに留意すべきである。また、図面の相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

**【 0 0 1 7 】****( 半導体装置について )**

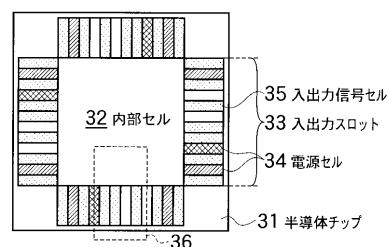

実施の形態に係る半導体装置の接続端子設計について説明する前に、設計対象となる半導体装置についてフリップチップBGAを例に取り説明する。

**【 0 0 1 8 】**

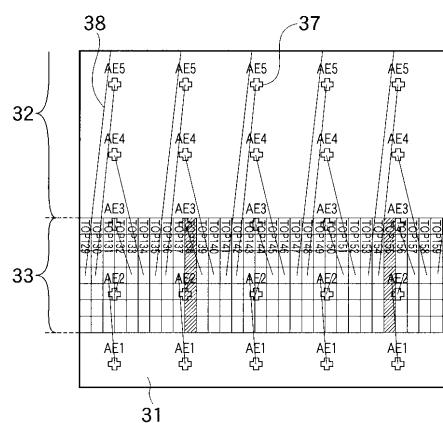

図2に示すように、半導体チップ31は、方形状の外周に沿って線状に配設された複数の入出力スロット33と、複数の入出力スロット33の内側に配置された内部セル32とを有する。入出力スロット33には、電源セル34或いは入出力信号セル35が配置されている。内部セル32は、半導体チップ31が実現する演算機能又は記憶機能などの特定の機能手段を構成している。電源セル34は、主に入出力信号セル35の動作に必要な電圧を供給するためのセルであり、通常、出力用電源セルと、入力用電源セル、若しくは入出力兼用の電源セルで構成されている。実際には、内部セル32用の電源は、入出力スロットを使っていないケースがほとんどで、内部セル32用の電源セルは使わずに、入出力スロットにつながらないバンプから直接電源を供給している。また、出力用電源セルと入力用電源セルは分けて使わないケース(入出力兼用セル)もある。なお、図2では、半導体チップ31の主表面上に配設されているバンプの記載を省略している。バンプと入出力スロット33との相互関係は図3(a)及び(b)を参照して説明する。

**【 0 0 1 9 】**

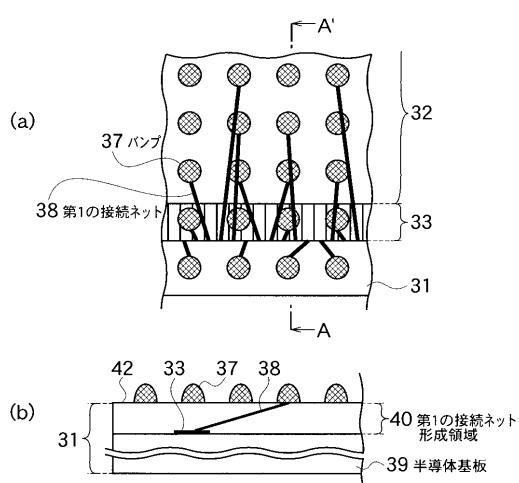

図3(a)に示すように、半導体チップ31の上には複数のバンプ37が格子状に配設されている。バンプ37は、内部セル32が配置されている領域、入出力スロット33が配置されている領域、及び入出力スロット33から半導体チップ31の外周端までの領域に配設されている。即ち、半導体チップ31の主表面全体に渡って配設されている。複数の入出力スロット33と複数のバンプ37との間は、第1の接続ネット38によって接続されている。入出力スロット33とバンプ37は、1対1に対応して接続されている。第1の接続ネット38は、入出力スロット33とバンプ37とをほぼ直線状に結ぶ線であり、入出力スロット33とバンプ37とを実際のデバイス上で接続する配線と区別されるべきである。入出力スロット33とバンプ37とを接続する実際の配線は、後述するチップ配置配線工程時に設計される。

10

20

30

40

50

## 【0020】

図3(b)は、図3(a)に示した入出力スロット33、バンプ37、及び第1の接続ネット38のチップ厚さ方向の構成を示す図である。半導体基板39の上方に入出力スロット33が配置され、入出力スロット33の上方に第1の接続ネット形成領域40を介してバンプ37が配置されている。また、バンプ37は、半導体チップ31の主表面42上に配置されている。第1の接続ネット38或いは実際のデバイス上の配線は、第1の接続ネット形成領域40内に形成される。

## 【0021】

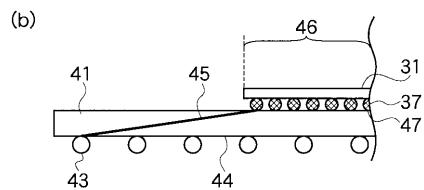

図4(a)に示すように、フリップチップBGAのパッケージ基体41は、格子状に配設された複数の外部電極43と、パッケージ基体41の中央部に配置された、半導体チップが接続されるチップ領域46とを有する。チップ領域46には、図3(a)のバンプ37に対応する位置に複数のバンプ接続部47が配設されている。複数のバンプ接続部47と複数の外部電極43との間は、第2の接続ネット45によって接続されている。第2の接続ネット45は、バンプ接続部47と外部電極43とをほぼ直線状に結ぶ線であり、バンプ接続部47と外部電極43とを実際のデバイス上で接続する配線と区別されるべきである。バンプ接続部47と外部電極43とを接続する実際の配線は、後述するパッケージ詳細設計工程時に設計される。なお、図4(a)においては、バンプ接続部47と外部電極43間を接続する第2の接続ネット45を図示する為、チップ領域46上に配設されるべき外部電極43の記載を省略している。しかし、実際の外部電極43は、チップ領域46を含むパッケージ基体41の主表面全体に渡って配設されている。

10

20

30

## 【0022】

図4(b)は、図4(a)に示したバンプ接続部47、外部電極43、及び第2の接続ネット45のパッケージ厚さ方向の構成を示す図である。パッケージ基体41の主表面44上に外部電極43が配置され、パッケージ基体41の主表面44に対抗する面上にバンプ接続部47が配置されている。また、半導体チップ31は、主表面44に対抗する面のチップ領域46内に、バンプ37を介してパッケージ基体41に接続されている。バンプ37は、パッケージ基体41のバンプ接続部47に接続されている。第2の接続ネット45或いは実際のデバイス上の配線は、パッケージ基体41内に形成され、バンプ37と外部電極43の間を接続している。

## 【0023】

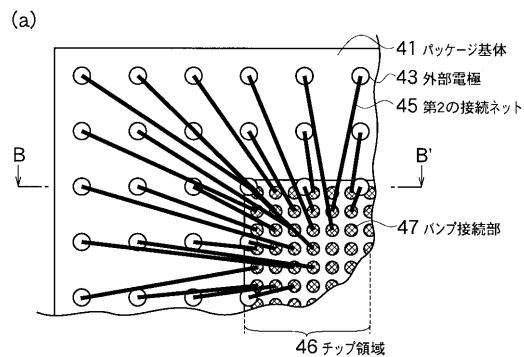

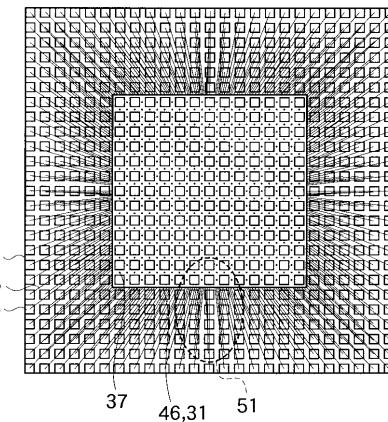

図5に示すように、正方形状のパッケージ基体41の主表面全体に渡って、複数の外部電極43が格子状に配設されている。パッケージ基体41の中央部には、正方形状のチップ領域46が形成され、半導体チップ31は、パッケージ基体41のチップ領域46に複数のバンプ37を介して接続されている。バンプ37は、半導体チップ31の主表面全体に渡って格子状に配設されている。バンプ37と外部電極43は、第2の接続ネット45によって接続されている。

40

## 【0024】

図6に示すように、半導体チップ31上のバンプ37は、第2の接続ネット45によって外部電極43に接続されている。

## 【0025】

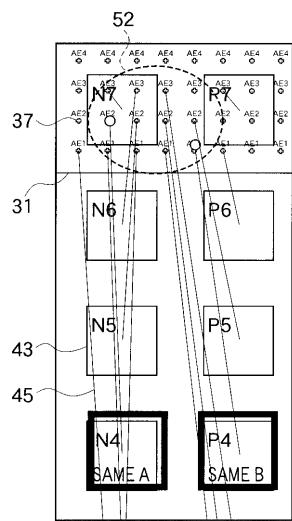

図7に示すように、複数の入出力スロット33が半導体チップ31の外周に沿って線状に配設され、複数の入出力スロット33の内側に内部セル32が配置されている。半導体チップ31の主表面全体に複数のバンプ37が格子状に配設されている。半導体チップ31内の入出力スロット33は、第1の接続ネット38によって半導体チップ31上のバンプ37に接続されている。入出力スロット33とバンプ37は、1対1に対応して接続されている。

## 【0026】

ここで「入出力スロット」は、上位概念「接続端子」に含まれる下位概念であり、どの入出力スロット33にどの電源セル34或いはどの入出力信号セル35を割り当てるかは、半導体装置の接続端子設計の対象に含まれる。同様に、「バンプ」及び「外部電極」は、

50

上位概念「接続端子」に含まれる下位概念であり、どのバンプ 37 及び外部電極 43 にどの電源信号或いはどの入出力信号を割り当てるかは、半導体装置の接続端子設計の対象に含まれる。

### 【0027】

<半導体装置の接続端子設計について>

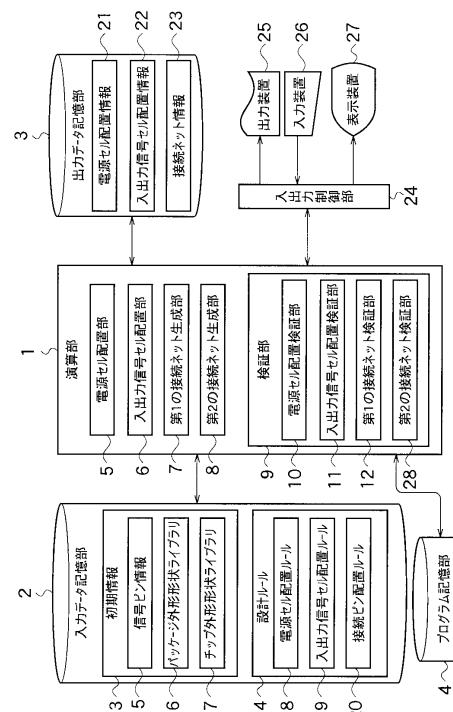

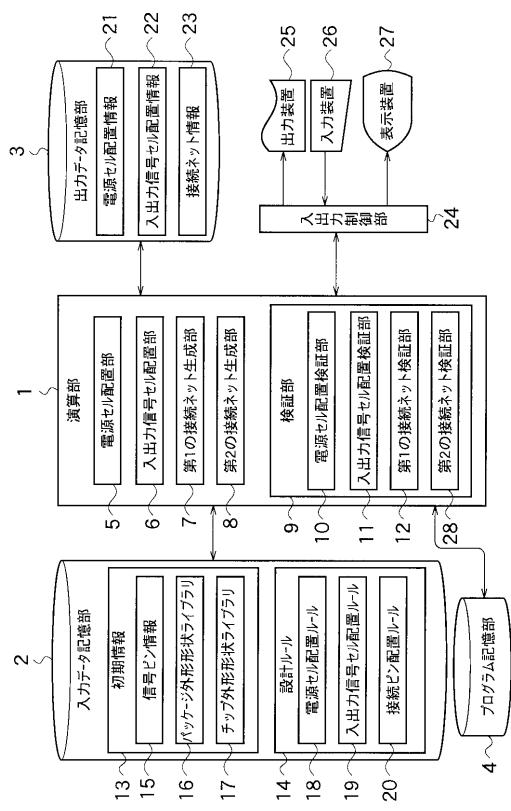

図1に示すように、第1の実施の形態に係る半導体装置の接続端子設計装置は、接続端子を設計する為の機能手段を備えた演算部1、演算部1に接続された入力データ記憶部2、出力データ記憶部3、及びプログラム記憶部4を少なくとも有する。

### 【0028】

演算部1は、電源セル配置部5、入出力信号セル配置部6、第1の接続ネット生成部7、第2の接続ネット生成部8、及び検証部9を有する。検証部9は、電源セル配置検証部10、入出力信号セル配置検証部11、第1の接続ネット検証部12、及び第2の接続ネット検証部28を有する。入力データ記憶部2には、初期情報13、及び設計ルール14に関する情報が記憶されている。出力データ記憶部3には、電源セル配置情報21、入出力信号セル配置情報22、及び接続ネット情報23が記憶されている。初期情報13には、信号ピン情報15、パッケージ外形形状ライブラリ16、チップ外形形状ライブラリ17が含まれる。設計ルール14には、電源セル配置ルール18、入出力信号セル配置ルール19、接続ピン配置ルール20が含まれる。

### 【0029】

演算部1は、通常のコンピュータシステムの中央処理装置(CPU)の一部として構成すればよい。電源セル配置部5、入出力信号セル配置部6、第1の接続ネット生成部7、第2の接続ネット生成部8、及び検証部9は、それぞれ専用のハードウェアで構成しても良く、通常のコンピュータシステムのCPUを用いて、ソフトウェアで実質的に等価な機能を有する機能手段として構成しても構わない。

### 【0030】

入力データ記憶部2、出力データ記憶部3、及びプログラム記憶部4は、それぞれ、半導体ROM、半導体RAM等の半導体メモリ装置、磁気ディスク装置、磁気ドラム装置、磁気テープ装置などの外部記憶装置で構成してもよく、CPUの内部の主記憶装置で構成しても構わない。

### 【0031】

また、演算部1には、入出力制御部24を介して、操作者からのデータや命令などの入力を受け付ける入力装置26と、接続端子の設計結果を出力する出力装置25及び表示装置27が接続されている。入力装置26は、キーボード、マウス、ライトペンまたはフレキシブルディスク装置などで構成されている。出力装置10はプリンタ装置などにより構成され、表示装置27はCRT、液晶などのディスプレイ装置などで構成されている。

### 【0032】

演算部1で実行される各処理の入力データは、入力データ記憶部2に記憶され、プログラム命令はプログラム記憶部4に記憶されている。そしてこれらの入力データやプログラム命令は必要に応じてCPUに読み込まれ、CPUの内部の演算部1によって、演算処理が実行されるとともに、一連の演算処理の各段階で発生した数値情報などのデータは、RAMや磁気ディスクなどの出力データ記憶部3に格納される。

### 【0033】

電源セル配置部5は、半導体チップ内に配設された複数の入出力スロットの一部に、電源セルを配置する。電源セル配置部5は、電源セル配置ルール18に従って電源セルを配置する。電源セル配置部5は、CPUに入力された信号ピン情報15及びチップ外形形状ライブラリ17に基いて、必要な電源セルの数を計算し、最適な位置に所望する電源セルを挿入する。必要な電源セルの数は、出力信号セルの同時スイッチングノイズや、入出力信号セル及び内部セルの消費電流量・使用条件等から計算される。電源セルが挿入される最適な位置は、出力バッファセルの近くに出力用電源セル、入力バッファセルの近くに入力用電源セルが置かれるようにし、同時スイッチングするグループには多数の電源セルを配

10

20

30

40

50

置する。

【0034】

入出力信号セル配置部6は、複数の入出力スロットの他の一部に、入出力信号セルを配置する。入出力信号セル配置部6は、入出力信号セル配置ルール19に従って入出力信号セルを配置する。入出力信号セルの配置は、電源セル配置部5によって挿入された電源セルの配置に合わせて行われる。

【0035】

第1の接続ネット生成部7は、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成する。第1の接続ネット生成部7は、接続ピン配置ルール20に従って第1の接続ネットを生成する。

10

【0036】

第2の接続ネット生成部8は、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成する。第2の接続ネット生成部8は、接続ピン配置ルール20に従って第2の接続ネットを生成する。

【0037】

検証部9は、電源セル、入出力信号セル、及び第1及び第2の接続ネットが、所定の設計ルールに違反しているか否かを検証する。ここでは「所定の設計ルール」として設計ルール14を使用する。具体的には、電源セル配置検証部10は、電源セルの数及び配置位置が電源セル配置ルール18に違反しているか否かを検証する。入出力信号セル配置検証部11は、入出力信号セルの配置位置が入出力信号セル配置ルール19に違反しているか否かを検証する。第1の接続ネット検証部12は、第1の接続ネットが接続ピン配置ルール20に違反しているか否かを検証する。第2の接続ネット検証部28は、第2の接続ネットが接続ピン配置ルール20に違反しているか否かを検証する。

20

【0038】

検証部9によって設計ルール14に違反していないと判定された電源セル、入出力信号セル、及び第1及び第2の接続ネットは、電源セル配置情報21、入出力信号セル配置情報22、及び接続ネット情報23として、出力データ記憶部3へそれぞれ出力され記憶される。一方、検証部9によって設計ルール14に違反していると判定された場合、検証部9は、例えば表示装置27の表示画面に、ルール違反があった違反項目、違反個所、違反内容などを表示して、操作者に対して設計変更の注意を促す。操作者は、表示装置27の表示画面を見ながら手作業で電源セル或いは入出力信号セルの配置変更や、第1及び第2の接続ネットの入れ替えを行う。そして、検証部9は、編集(変更、入れ替え)後の電源セル、入出力信号セル、及び第1及び第2の接続ネットに対して、再度ルールチェックを行う。

30

【0039】

電源セル配置ルール18は、電源セルの数及び配置位置に関するルールである。入出力信号セル配置ルール19は、入出力信号セルの大きさ及び配置禁止領域に関するルールである。接続ピン配置ルール20には、セル仕様から要求される等長配線の要求、ペア配線の要求、接続ネットが交差する数の制限、最大配線長、及び配線の引き出しが出来るバンプの口ウ(Row)数に関するルールが含まれる。ここでは「接続ピン」は、上位概念「接続端子」に含まれる下位概念であり、「バンプ」及び「外部電極」を含む上位概念である。

40

【0040】

信号ピン情報15には、信号名、I/Oバッファ名、パッケージ配線での等長配線ペアなどの要求事項等の情報が含まれる。パッケージ外形形状ライブラリ16は、外部電極の位置座標等の情報を有する。チップ外形形状ライブラリ17は、入出力スロット及びバンプの位置座標等の情報を有する。

【0041】

以上説明したように、図1に示す演算部(5~8)は、入出力スロット、バンプ、外部電極などの複数種類の接続端子に対して、それぞれ電源信号或いは入出力信号を割り当てる

50

。そして、検証部9は、各接続端子について設計ルール14に従った検証を行う。従って、外部電極とバンプ間及びバンプと入出力スロット間の対応関係は明確であるとは言えず、相対的な配置順序も同じとは言えない場合であっても、設計ルール14に違反することなく、接続端子に信号を効率的に割り当ることができる。

【0042】

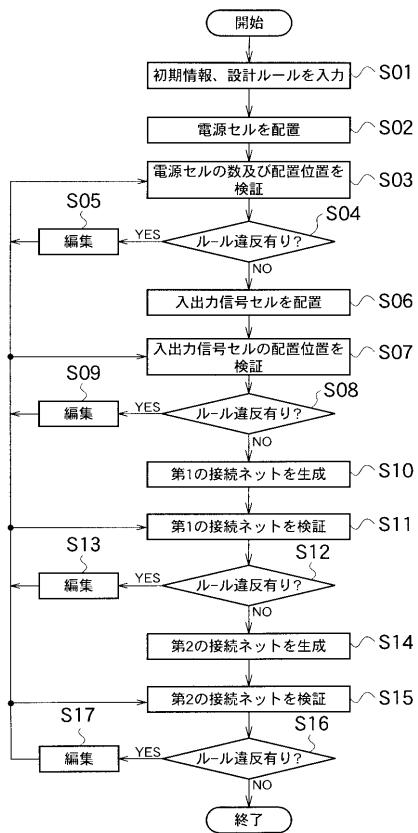

図8に示すように、本発明の実施の形態に係る半導体装置の接続端子設計方法は、S01～S17段階から構成されている。

【0043】

(イ)まず、S01段階において、信号ピン情報、パッケージ外形形状ライブラリ、チップ外形形状ライブラリなどの初期情報、及び電源セル配置ルール、入出力信号セル配置ルール、接続ピン配置ルールなどの設計ルールに関する情報を、図1の入力装置26を介して入力データ記憶部2へ入力する。10

【0044】

(ロ)次に、S02段階において、半導体チップ内に配設された複数の入出力スロットの一部に電源セルを配置する。この時、電源セルは、入力データ記憶部2に記憶されている電源セル配置ルールに従って配置される。具体的には、出力セルの同時スイッチングノイズや、入出力信号セル及び内部セルの消費電流量・使用条件等を考慮して、必要な電源セルの数を計算する。電源セルを挿入する位置は、出力用バッファセルの近くに出力用電源セルが、入力用バッファセルの近くに入力用電源セルがそれぞれ置かれるようにし、同時スイッチングするグループには多くの電源セルを配置する。次に、S03段階において、電源セルが、所定の設計ルールに違反しているか否かを検証する。S03段階での「所定の設計ルール」として、電源セル配置ルールを使用する。20

【0045】

(ハ)検証した結果、電源セルの数或いは配置位置にルール違反があると判定された場合(S04段階において、Yes)、図1の表示装置27に電源セルにルール違反がある旨及び違反個所を表示し、操作者に対して注意を促す。S05段階において、操作者は、ルール違反を回避するように、入力装置26を用いて電源セルの数或いは配置位置を編集することができる。そして、S03段階に戻り、再度、電源セルの数或いは配置位置のルールチェックを行う。S03～S05のループは、電源セルの数或いは配置位置にルール違反がないと判定された場合(S04段階において、No)、終了してS06段階へ進む。30

【0046】

(ニ)次に、S06段階において、複数の入出力スロットの他の一部に入出力信号セルを配置する。即ち、電源セルが配置されていない入出力スロットに入出力信号セルを配置する。この時、入出力信号セルは、入出力信号セル配置ルールに従って配置される。次に、S07段階において、入出力信号セルが、所定の設計ルールに違反しているか否かを検証する。S07段階での「所定の設計ルール」として、入出力信号セル配置ルールを使用する。

【0047】

(ホ)検証した結果、入出力信号セルの大きさ及び配置位置にルール違反があると判定された場合(S08段階において、Yes)、図1の表示装置27に入出力信号セルにルール違反がある旨及び違反個所を表示し、操作者に対して注意を促す。S09段階において、操作者は、ルール違反を回避するように、入力装置26を用いて入出力信号セルの数或いは配置位置を編集することができる。そして、S07段階に戻り、再度、入出力信号セルの大きさ及び配置禁止領域(位置)のルールチェックを行う。S07～S09のループは、入出力信号セルの大きさ及び配置禁止領域(位置)にルール違反がないと判定された場合(S08段階において、No)、終了してS10段階へ進む。40

【0048】

(ヘ)次に、S10段階において、複数の入出力スロットと半導体チップ上に配設された複数のバンプとの間を接続する第1の接続ネットを生成する。この時、第1の接続ネットは、接続ピン配置ルールに従って生成される。具体的には、「接続ピン配置ルール」には50

、図3(b)の第1の接続ネット形成領域40の配線可能層数及び配線間隔などから定まる第1の接続ネットの交差の制約、配線の引き出しが出来るバンプの口ウ(Row)数などの制約、セル仕様から要求される等長配線等の制約などが含まれている。次に、S11段階において、第1の接続ネットが、所定の設計ルールに違反しているか否かを検証する。S11段階での「所定の設計ルール」を接続ピン配置ルールを使用する。

#### 【0049】

(ト) 検証した結果、第1の接続ネットにルール違反があると判定された場合(S12段階において、Yes)、図1の表示装置27に第1の接続ネットにルール違反がある旨及び違反個所を表示し、操作者に対して注意を促す。S13段階において、操作者は、ルール違反を回避するように、入力装置26を用いてバンプの割り当てを編集することができる。そして、S11段階に戻り、再度、第1の接続ネットのルールチェックを行う。S11～S13のループは、第1の接続ネットにルール違反がないと判定された場合(S12段階において、No)、終了してS14段階へ進む。

10

#### 【0050】

(チ) 次に、S14段階において、複数のバンプとパッケージ基体上に配設された複数の外部電極との間を接続する第2の接続ネットを生成する。この時、第2の接続ネットは、接続ピン配置ルールに従って生成される。具体的には、「接続ピン配置ルール」には、図4(b)のパッケージ基体41の配線可能層数及び配線間隔などから定まる第2の接続ネットの交差の制約、配線の引き出しが出来る外部電極の口ウ(Row)数などの制約、セル仕様から要求される等長配線等の制約などが含まれている。次に、S15段階において、第2の接続ネットが、所定の設計ルールに違反しているか否かを検証する。S15段階での「所定の設計ルール」を接続ピン配置ルールを使用する。

20

#### 【0051】

(リ) 検証した結果、第2の接続ネットにルール違反があると判定された場合(S16段階において、Yes)、図1の表示装置27に第2の接続ネットにルール違反がある旨及び違反個所を表示し、操作者に対して注意を促す。S17段階において、操作者は、ルール違反を回避するように、入力装置26を用いて外部電極の割り当てを編集することができる。そして、S15段階に戻り、再度、第2の接続ネットのルールチェックを行う。S15～S17のループは、第2の接続ネットにルール違反がないと判定された場合(S16段階において、No)、終了する。

30

#### 【0052】

(ヌ) 最後に、電源セル配置情報、入出力信号セル配置情報、接続ネット情報を図1の出力データ記憶部3へ出力及び記憶する。

#### 【0053】

以上の段階を経て、接続端子の割り当てが終了した後、チップ自動配置配線工程、パッケージ詳細設計工程を実施する。「チップ自動配置配線工程」では、第1の接続ネットに従って実際の半導体チップの入出力スロットとバンプ間の配線を設計する。「パッケージ詳細設計工程」では、第2の接続ネットに従って実際のパッケージ基体のバンプと外部電極間の配線を設計する。

40

#### 【0054】

以上説明したように、S02、S06、S10、及びS14段階において、入出力スロット、バンプ、外部電極などの複数種類の接続端子に対して、それぞれ電源信号或いは入出力信号が割り当てられる。そして、S03、S07、S11、及びS15段階において、各接続端子について設計ルールに従った検証が行われる。従って、外部電極とバンプ間及びバンプと入出力スロット間の対応関係は明確であるとは言えず、相対的な配置順序も同じとは言えない場合であっても、設計ルールに違反することなく、接続端子に信号を効率的に割り当ることができる。

#### 【0055】

また、隣接する接続端子に割り当てるべき差動バッファ等の特定の信号を、設計ルールに違反することなく、入出力スロット、バンプ、及び外部電極にそれぞれ隣接して割り当て

50

ることができる。

【0056】

更に、チップ自動配置配線工程及びパッケージ詳細設計工程において、ピンアサイン起因のエラーが発見されることが防止され、チップ自動配置配線及びパッケージ詳細設計をやり直すことがなくなる。

【0057】

なお、図8の操作者による編集段階(S05、S09、S13、及びS13)の後、戻るべき段階は、一通りとは限らない。例えば、入出力信号セルの配置位置にルール違反が発見され(S08)、編集を行った後(S09)、S07段階に戻るだけに限られない。入出力信号セルの配置位置を編集した結果、電源セルの数或いは配置位置を検証する必要が生じる場合もあり得る。この場合、S07段階ではなくS03段階に戻り、電源セルのルールチェック(S03)を実施することが望ましい。同様に、第1及び第2の接続ネットについて編集(S13、S17)した結果、電源セル又は入出力信号セルについて検証する必要が生じる場合もあり得る。この場合、S11段階又はS15段階ではなくS03段階或いはS07段階に戻り、電源セル又は入出力信号セルのルールチェック(S03、S07)を実施することが望ましい。

【0058】

以上説明したように、本発明の実施の形態によれば、複数の外部電極或いは複数のバンプがパッケージ基体半導体或いはチップの主表面に格子状に配設されている半導体装置において、入出力スロット、バンプ、外部電極などの接続端子の割り当てを、効率的に且つ設計ルールに正確に行うことができる。即ち、BGA又はフリップチップパッケージなどの、近年の高密度実装・多ピン化に対応できるパッケージを有する半導体装置において、入出力信号セルの自動配置や、接続ネットの自動生成を、短時間で、しかも設計要求に正確に処理することができる。特に、入出力信号セルの配置における設計ルール検証や概略配線(接続ネット)の段階で設計ルール検証を行うため、チップ自動配置配線及びパッケージ詳細設計のやり直しを減少できる。

【0059】

上述した半導体装置の接続端子設計方法は、時系列的につながった一連の処理又は操作、即ち「手順」として表現することができる。従って、この方法を、コンピュータシステムを用いて実行するために、コンピュータシステム内のプロセッサーなどが果たす複数の機能を特定するプログラムとして構成することができる。また、このプログラムは、コンピュータ読み取り可能な記録媒体に保存することができる。この記録媒体をコンピュータシステムによって読み込ませ、このプログラムを実行してコンピュータを制御しながら上述した方法を実現することができる。この記録媒体は、図1に示したプログラム記憶部4として用いる、あるいはプログラム記憶部4に読み込ませ、このプログラムにより演算部1における種々の作業を所定の処理手順に従って実行することができる。ここで、このプログラムを保存する記録媒体としては、メモリ装置、磁気ディスク装置、光ディスク装置、その他のプログラムを記録することができるような装置が含まれる。

【0060】

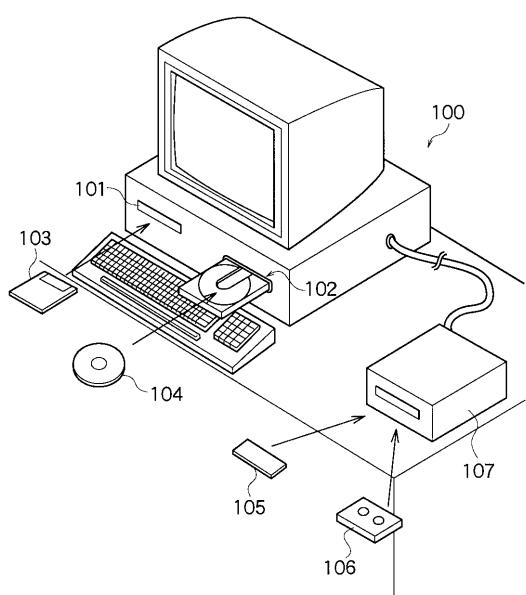

図10に示すように、半導体装置の接続端子設計装置100の本体全面には、フレキシブルディスクドライブ101、及びCD-ROMドライブ102が設けられている。磁気ディスクとしてのフレキシブルディスク103または光ディスクとしてのCD-ROM104を各ドライブ入り口から挿入し、所定の読み出し操作を行うことにより、これらの記録媒体に格納されたプログラムをシステム内にインストールすることができる。また、所定のドライブ装置107を接続することにより、例えばゲームパックなどに使用されている半導体メモリとしてのROM105や、磁気テープとしてのカセットテープ106を用いることもできる。

【0061】

(変形例)

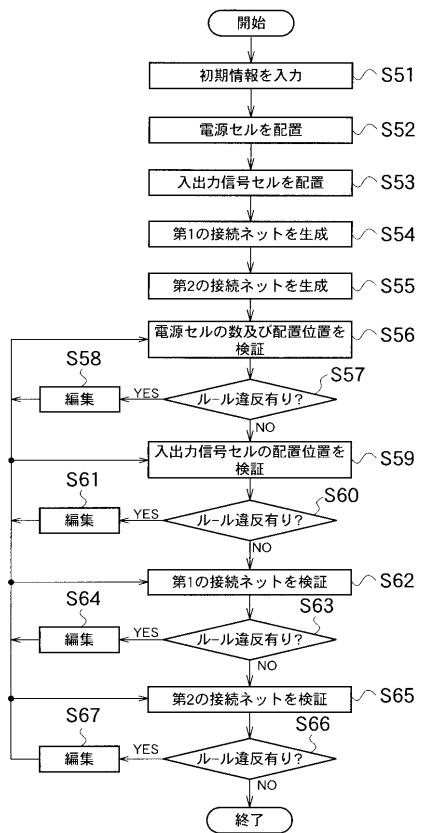

図9を参照して、変形例に係る半導体装置の接続端子設計方法について説明する。

10

20

30

40

50

**【 0 0 6 2 】**

(イ) まず、図8のS01段階と同様に、S51段階において初期情報及び設計ルールを入力する。

**【 0 0 6 3 】**

(ロ) 次に、S52段階～S55段階において、電源セルの配置、入出力信号セルの配置、及び第1及び第2の接続ネットの生成を実施する。即ち、変形例においては、電源セルを配置した(S52)後、電源セルの数及び位置を検証せずに入出力信号セルを配置する(S53)。そして、入出力信号セルの位置を検証せずに第1の接続ネットを生成し(S54)、続けて第2の接続ネットを生成する(S55)。

**【 0 0 6 4 】**

(ハ) その後、S56段階において電源セルの数及び配置位置を検証する。検証の結果、電源セルの数或いは配置位置にルール違反が有る場合(S57においてYes)、違反個所を編集した(S58)後、再び電源セルのルールチェックを行う。

**【 0 0 6 5 】**

(ニ) そして、S59段階において入出力信号セルの配置位置を検証する。検証の結果、入出力信号セルの位置にルール違反が有る場合(S60においてYes)、違反個所を編集した(S61)後、再び電源セルのルールチェックを行う。

**【 0 0 6 6 】**

(ホ) そして、S62段階において第1の接続ネットを検証する。検証の結果、第1の接続ネットにルール違反が有る場合(S63においてYes)、違反個所を編集した(S64)後、再び第1の接続ネットのルールチェックを行う。

**【 0 0 6 7 】**

(ヘ) そして、S65段階において第2の接続ネットを検証する。検証の結果、第2の接続ネットにルール違反が有る場合(S66においてYes)、違反個所を編集した(S67)後、再び第2の接続ネットのルールチェックを行う。

**【 0 0 6 8 】**

なお、図8のフローチャートと同様に、操作者による編集段階(S58、S61、S64、及びS67)の後、戻るべき段階は、一通りとは限らない。例えば、入出力信号セルの配置位置にルール違反が発見され(S60)、編集を行った後(S61)、S59段階に戻るだけに限られない。入出力信号セルの位置を編集した結果、電源セルの数或いは配置位置を検証する必要が生じる場合もあり得る。この場合、S59段階ではなくS56段階に戻り、電源セルのルールチェック(S56)を実施することが望ましい。同様に、第1及び第2の接続ネットについて編集(S64、S67)した結果、電源セル又は入出力信号セルについて検証する必要が生じる場合もあり得る。この場合、S62段階又はS65段階ではなくS56段階或いはS59段階に戻り、電源セル又は入出力信号セルのルールチェック(S56、S59)を実施することが望ましい。

**【 0 0 6 9 】**

このように、直前の検証段階ではなくそれ以前の検証段階へ戻る場合、変形例においては、以下に示す図8のフローチャートには無い特有の効果を有する。図8において、例えば、入出力信号セルのルール違反に対して操作者が編集を行い(S09)、電源セルの数或いは位置を再度検証した(S03)場合、S06段階において、再度入出力信号セルの配置を行うことになる。一方、図9においては、入出力信号セルのルール違反に対して操作者が編集を行い(S61)、電源セルの数或いは位置を再度検証しても(S56)、S56～S61のループの中に入出力信号セルの配置段階(S53)が含まれていないため、入出力信号セルの配置段階(S53)を実施することが無い。即ち、入出力信号セルのルール違反に対して操作者が行った編集(S61)の結果を十分に利用して、各検証段階(S56、S59、S62、S65)を実施することができる。よって、一度、配置／生成した電源セル、入出力信号セル、第1及び第2の接続ネットを有効に利用することができ、より効率的な設計を行うことが可能となる。

**【 0 0 7 0 】**

10

20

30

40

50

( その他の実施の形態 )

上記のように、本発明は、1つの実施の形態及びその変形例によって記載したが、この開示の一部をなす論述及び図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例及び運用技術が明らかとなろう。

【 0 0 7 1 】

図8に示したフローチャートには、図2～図7に示したフリップチップチップBGA等の半導体装置に適した接続端子設計方法を示す。即ち、フリップチップチップBGAにおいては、第1の接続ネットは、電源セル及び入出力信号セルを配置した後に生成され、第2の接続ネットは、第1の接続ネットを生成した後に生成されることが望ましい。基本的には、「電源セル及び入出力信号セルの配置」、「第1の接続ネットの生成」及び「第2の接続ネットの生成」の設計自由度は、「電源セル及び入出力信号セルの配置」<「第1の接続ネットの生成」<「第2の接続ネットの生成」の関係にある。従って、設計自由度の低いものから順番に設計していくことで設計効率が向上する。逆に、設計自由度の高いものから順番に設計していくことで設計制約を満たさない可能性が増加する。一般的に、「第1の接続ネット」は一層で形成されている為、その設計自由度は小さく、セルからバンプまでの対応関係はある程度決まっている(少ない選択の可能性)。しかし、「第2の接続ネット」は複数層で形成されている為、「第1の接続ネット」よりも設計自由度が大きい(大きな選択の可能性)。よって、設計自由度の低いものから作業していく方が効率的である。例えば等長配線が「第1の接続ネットの生成」のルールチェックでエラーが発生しても「第2の接続ネットの生成」においてそのエラーを吸収可能である。

10

20

30

40

【 0 0 7 2 】

しかし、本発明の実施の形態に係る接続端子の設計方法は、図8に示したフローチャートに限られない。フリップチップチップBGA以外の半導体装置、例えば、QFPなどにおいては、まず、第2の接続ネットの生成及び検証(S14～S17)を行い、次に第1の接続ネットの生成及び検証(S10～S13)を行い、次に入出力信号セル及び電源信号セルの配置及び検証(S02～S09)を行うことが望ましい。

【 0 0 7 3 】

図5等では複数のバンプ37が半導体チップ31の主表面全体に配設され、複数の外部電極43がパッケージ基体41の主表面全体に配設されている場合について示した。しかし、接続端子設計の対象となる半導体装置は、これに限定されるものではなく、半導体チップ31或いはパッケージ基体41の一部分にのみ配置されていても構わない。例えば、図5のパッケージ基体41の主表面の内、チップ領域46を除いた領域にのみに、複数の外部電極43が格子状に配設されていても構わない。同様に、図2の半導体チップ31の主表面の内、内部セル32が形成されていない領域にのみに、図3(a)の複数のバンプ37が格子状に配設されていても構わない。

【 0 0 7 4 】

このように、本発明はここでは記載していない様々な実施の形態等を包含するということを理解すべきである。したがって、本発明はこの開示から妥当な特許請求の範囲に係る発明特定事項によってのみ限定されるものである。

【 0 0 7 5 】

【 発明の効果 】

以上説明したように、本発明によれば、接続端子の割り当てを、効率的に且つ設計ルールに正確に行うことができる半導体装置の接続端子設計装置、半導体装置の接続端子設計方法、及び半導体装置の接続端子設計プログラムを提供することができる。

【 図面の簡単な説明 】

【 図1 】本発明の実施の形態に係る半導体装置の接続端子設計装置の構成を示すブロック図である。

【 図2 】フリップチップBGAにパッケージングされる半導体チップの全体構成を示す平面図である。

【 図3 】図3(a)は、図2の点線で囲んだ領域36の詳細な構成を示す拡大図である。

50

図3( b )は、図3( a )のA-A'切断面に沿った断面図である。

【図4】図4( a )は、図2の半導体チップをパッケージングするフリップチップBGAのパッケージ基体の一部分を示す平面図である。図4( b )は、B-B'切断面に沿った断面図である。

【図5】フリップチップBGAのより具体的な構成を示す平面図である。

【図6】図5の破線で囲まれた橙円の領域51を拡大した平面図である。

【図7】図5の破線で囲まれた橙円の領域52を拡大した平面図である。

【図8】本発明の実施の形態に係る半導体装置の接続端子設計方法を示すフローチャートである。

【図9】図8に示した半導体装置の接続端子設計方法の変形例を示すフローチャートである。 10

【図10】接続端子設計プログラムを読み取り、そこに記述された手順に従って、半導体装置の接続端子設計システムが果たす複数の機能を制御することにより、半導体装置の接続端子設計方法を実現するコンピュータシステムからなる半導体装置の接続端子設計装置の一例を示す外観図である。

【図11】従来のQFPの構成を示す平面図である。

#### 【符号の説明】

|    |                |    |

|----|----------------|----|

| 1  | 演算部            |    |

| 2  | 入力データ記憶部       |    |

| 3  | 出力データ記憶部       | 20 |

| 4  | プログラム記憶部       |    |

| 5  | 電源セル配置部        |    |

| 6  | 入出力信号セル配置部     |    |

| 7  | 第1の接続ネット生成部    |    |

| 8  | 第2の接続ネット生成部    |    |

| 9  | 検証部            |    |

| 10 | 電源セル配置検証部      |    |

| 11 | 入出力信号セル配置検証部   |    |

| 12 | 第1の接続ネット検証部    |    |

| 13 | 初期情報           | 30 |

| 14 | 設計ルール          |    |

| 15 | 信号ピン情報         |    |

| 16 | パッケージ外形形状ライブラリ |    |

| 17 | チップ外形形状ライブラリ   |    |

| 18 | 電源セル配置ルール      |    |

| 19 | 入出力信号セル配置ルール   |    |

| 20 | 接続ピン配置ルール      |    |

| 21 | 電源セル配置情報       |    |

| 22 | 入出力信号セル配置情報    |    |

| 23 | 接続ネット情報        | 40 |

| 24 | 入出力制御部         |    |

| 25 | 出力装置           |    |

| 26 | 入力装置           |    |

| 27 | 表示装置           |    |

| 28 | 第2の接続ネット検証部    |    |

| 31 | 半導体チップ         |    |

| 32 | 内部セル           |    |

| 33 | 入出力スロット        |    |

| 34 | 電源セル           |    |

| 35 | 入出力信号セル        | 50 |

- 3 7 バンプ

3 8 第1の接続ネット

3 9 半導体基板

4 0 第1の接続ネット形成領域

4 1 パッケージ基体

4 3 外部電極

4 5 第2の接続ネット

4 6 チップ領域

4 7 バンプ接続部

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |       |         |

|---------|-------|---------|

| H 0 1 L | 23/12 | 5 0 1 Z |

| H 0 1 L | 21/82 | C       |

| H 0 1 L | 27/04 | E       |

(74)代理人 100101247

弁理士 高橋 俊一

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 今田 知彦

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 柴田 豊和

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 渡辺 清次

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

F ターム(参考) 5B046 AA08 BA04 JA01

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5F038 | BE07 | CA10 | CA17 | CD02 | CD05 | EZ09 | EZ20 |      |      |      |

| 5F064 | DD32 | DD34 | DD42 | EE02 | EE03 | EE08 | EE14 | EE15 | EE16 | EE17 |

| EE19  | EE20 | EE26 | HH06 | HH10 | HH14 |      |      |      |      |      |