(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7438186号**

**(P7438186)**

(45)発行日 令和6年2月26日(2024.2.26)

(24)登録日 令和6年2月15日(2024.2.15)

## (51)国際特許分類

|         |                |     |         |              |

|---------|----------------|-----|---------|--------------|

| G 0 9 G | 3/36 (2006.01) | F I | G 0 9 G | 3/36         |

| G 0 9 G | 3/20 (2006.01) |     | G 0 9 G | 3/20 6 2 1 A |

| G 0 9 G | 3/34 (2006.01) |     | G 0 9 G | 3/20 6 2 2 D |

| G 0 2 F | 1/13 (2006.01) |     | G 0 9 G | 3/20 6 2 2 K |

| G 0 2 F | 1/133(2006.01) |     | G 0 9 G | 3/20 6 2 2 R |

請求項の数 6 (全44頁) 最終頁に続く

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2021-505339(P2021-505339) |

| (86)(22)出願日       | 令和1年8月2日(2019.8.2)          |

| (65)公表番号          | 特表2021-536031(P2021-536031) |

|                   | A)                          |

| (43)公表日           | 令和3年12月23日(2021.12.23)      |

| (86)国際出願番号        | PCT/US2019/044931           |

| (87)国際公開番号        | WO2020/046538               |

| (87)国際公開日         | 令和2年3月5日(2020.3.5)          |

| 審査請求日             | 令和4年7月25日(2022.7.25)        |

| (31)優先権主張番号       | 16/118,377                  |

| (32)優先日           | 平成30年8月30日(2018.8.30)       |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                           |

|----------|---------------------------------------------------------------------------|

| (73)特許権者 | 502161508<br>シナブティクス インコーポレイテッド<br>アメリカ合衆国, 95131 カリフォルニア州, サンノゼ, マッケイ ドラ |

| (74)代理人  | イブ 1109<br>100205350<br>弁理士 狩野 芳正                                         |

| (74)代理人  | 100117617<br>弁理士 中尾 圭策                                                    |

| (72)発明者  | モリン、スティーブン・エル<br>アメリカ合衆国, 95131 カリフォルニア州、サンノゼ、マッケイ ドライブ                   |

| 審査官      | 1251<br>西島 篤宏                                                             |

最終頁に続く

(54)【発明の名称】 ディスプレイの再スキャン

## (57)【特許請求の範囲】

## 【請求項 1】

行及び列に配列される複数のピクセル要素を含むピクセルアレーに表示されるべき画像に対応する表示データのフレームであって、前記画像が第1時刻において前記ピクセルアレーに表示されるべきものであるところの表示データのフレームを受信することと、前記ピクセルアレーに含まれる各ピクセル要素について、前記各ピクセル要素をそのターゲットピクセル値において安定させるターゲット電圧を受信した前記フレームに基づいて決定することと、

前記第1時刻より前のピクセル調節期間の間に、前記ピクセルアレーの第1の一部の行をスキャンして、決定された前記ターゲット電圧を、前記第1の一部の行の各ピクセル要素に印加することと、

前記ピクセル調節期間の間に、前記ピクセルアレーの第2の一部の行をスキャンして、前記第2の一部の行のピクセル要素についてのオーバードライブ電圧が前記第2の一部の行のピクセル要素のターゲット電圧と異なっているところのオーバードライブ電圧を、前記第2の一部の行のピクセル要素に印加することと、

前記ピクセル調節期間の間に、前記ピクセルアレーの前記第2の一部の行を再スキャンして、前記第2の一部の行に含まれる各ピクセル要素に決定された前記ターゲット電圧を印加することと、

1以上の光源によって、前記第1時刻に開始する表示期間において前記ピクセルアレーを照らすことと、

を含む、

方法。

**【請求項 2】**

前記 1 以上の光源が、前記ピクセル調節期間の間に非活性化される、

請求項 1 に記載の方法。

**【請求項 3】**

前記ピクセルアレーの前記第 1 の一部の行のスキャンが、前記ピクセルアレーの前記第 2 の一部の行のスキャンよりも前に行われる、

請求項 1 に記載の方法。

**【請求項 4】**

行及び列に配列された複数のピクセル要素を含むピクセルアレーと、

データドライバであり、

前記ピクセルアレーに表示されるべき画像に対応する表示データのフレームであって、前記画像が第 1 時刻において前記ピクセルアレーに表示されるべきものであるところの表示データのフレームを受信し、

前記ピクセルアレーに含まれる各ピクセル要素について、前記各ピクセル要素をそのターゲットピクセル値において安定させるターゲット電圧を受信した前記フレームに基づいて決定し、

前記第 1 時刻より前のピクセル調節期間の間に、前記ピクセルアレーの第 1 の一部の行をスキャンして、決定された前記ターゲット電圧を、前記第 1 の一部の行の各ピクセル要素に印加し、

前記ピクセル調節期間の間に、前記ピクセルアレーの第 2 の一部の行をスキャンして、前記第 2 の一部の行のピクセル要素についてのオーバードライブ電圧が前記第 2 の一部の行のピクセル要素のターゲット電圧と異なっているところのオーバードライブ電圧を、前記第 2 の一部の行のピクセル要素に印加し、

前記ピクセル調節期間の間に、前記ピクセルアレーの前記第 2 の一部の行を再スキャンして、前記第 2 の一部の行に含まれる各ピクセル要素に決定された前記ターゲット電圧を印加する、

ように構成されたデータドライバと、

前記第 1 時刻に開始する表示期間において前記ピクセルアレーを照らすように構成された 1 以上の光源と、

を備える、

表示デバイス。

**【請求項 5】**

前記 1 以上の光源が、前記ピクセル調節期間の間に非活性化される、

請求項 4 に記載の表示デバイス。

**【請求項 6】**

前記ピクセルアレーの前記第 1 の一部の行のスキャンが、前記ピクセルアレーの前記第 2 の一部の行のスキャンよりも前に行われる、

請求項 4 に記載の表示デバイス。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本実施形態は、一般には表示デバイスに関し、詳細には、表示デバイスを再スキャンするための技術に関する。

**【背景技術】**

**【0002】**

ヘッドマウントディスプレイ (Head-mounted display) (HMD) デバイスは、ユーザの頭に着用、又は、さもなくば取り付けるように構成されている。HMD デバイスは、ユーザの目の一方又は両方の前方に配置される 1 以上のディスプレイ

10

20

30

40

50

を備える場合がある。HMDは、ユーザの周辺環境（例えば、カメラでキャプチャされた）からの情報及び／又は画像を重ねられた、画像ソースからの画像（例えば、静止画像、連続した画像、及び／又は、動画）を表示し、例えば、ユーザを仮想世界に没頭させ得る。HMDデバイスは、医療、軍事、ゲーミング、航空、工学、及び、様々な他のプロフェッショナル及び／又はエンターテイメント産業において応用される。

#### 【0003】

多くのHMDデバイスは、そのディスプレイにおいて液晶ディスプレイ（l i q u i d - c r y s t a l d i s p l a y ）（LCD）の技術を用いる。LCD表示パネルは、行及び列に配列されたピクセル要素（例えば、液晶セル）のアレーから形成されている場合がある。ピクセル要素の各行は、それぞれのゲートラインに接続され、ピクセル要素の各列はそれぞれのデータ（あるいはソース）ラインに接続される。ピクセル要素は、相対的に高い電圧をゲートラインに印加してピクセル要素の対応する行を「選択」あるいは活性化し、対応するデータラインに他の電圧を印加して選択されたピクセル要素を更新することによって、アクセス（たとえば、新たなピクセルデータで更新）される場合がある。データラインの電圧レベルは、ターゲットピクセル値の所望の色及び／又は強度に依存する場合がある。そのため、LCD表示パネルは、ピクセルアレーの各行が更新されるまで、ピクセル要素の行を（例えば1度に1行ずつ）連続して「スキャン」することにより更新される場合がある。

#### 【0004】

データラインに印加される電圧は、特定のピクセル要素の物理状態を変更（例えば回転）することにより、ピクセル要素の色及び／又は明るさを変更する。そのため、各ピクセル要素は新たな状態あるいは位置に安定するための時間を必要とする場合がある。特定のピクセル要素の安定化時間は、色及び／又は明るさの変化の度合いに依存する場合がある。例えば、最大明るさ設定（例えば、「白色」のピクセル）から最小明るさ設定（例えば、「黒色」のピクセル）への遷移は、中間の明るさ設定から他の中間の明るさ設定への（例えば、「灰色」のうち一つの色合いから「灰色」の他の色合いへの）遷移よりも長い安定化時間を必要とし得る。ピクセルの遷移における遅延は、ピクセル要素の安定化時間が連続するフレーム更新の間の時間よりも遅い場合、ゴースト及び／又は他の視覚的なアーティファクトをディスプレイに生じさせ得る。

#### 【0005】

LCDオーバードライブは、LCDディスプレイの更新時にピクセル遷移を加速するための技術である。詳細には、ピクセル要素は、所望の色及び／又は明るさのレベルに対応するターゲット電圧より高い電圧を印加される。より高い電圧は液晶をより速く回転させるため、液晶をより短い時間でターゲットの明るさに到達させる。固定のLCDディスプレイ（例えば、テレビ、モニタ、携帯電話、等）においては、一つのオブジェクトは、複数のフレームの持続時間にわたって、しばしば同じピクセル要素によって照らされる。そのため、そのエラーが1フレームだけ持続する場合には、ユーザは対応するピクセルの色及び／又は明るさにおけるエラーを検知できない場合があるため、固定のLCDディスプレイのピクセル要素に適用されるオーバードライブの量は概算でよい。しかしながら、HMDデバイス、特に仮想現実（v i r t u a l r e a l i t y ）（VR）のアプリケーションにおいては、ディスプレイ上で視認されるオブジェクトは、ユーザの頭及び／又は目が動くにつれて、異なるピクセルに照らされる場合がある。そのため、HMDディスプレイのピクセル要素それぞれに適用されるオーバードライブの量は、仮想環境に没頭するユーザの感覚を維持するために、はるかに正確であるべきである。

#### 【発明の概要】

#### 【0006】

本概要は、以下の詳細な説明でさらに説明される、概念の選択を単純化された形態で紹介するために提供される。本概要は、請求された主題の範囲の鍵となる特徴や必須の特徴を特定することを意図せず、請求された主題の範囲を限定することを意図していない。

#### 【0007】

10

20

30

40

50

表示デバイスのピクセル要素を更新するための方法及び装置。表示デバイスは、複数のピクセル要素を含むピクセルアレーを備える。データドライバは、第1時刻においてピクセルアレーに表示されるべき画像に対応する表示データのフレームを受信するように構成されている。データドライバは、第1時刻より前のピクセル調節期間の間に、ピクセルアレーの各行をスキャンして、受信したフレームに基づいて、複数の第1電圧を、それぞれに、複数のピクセル要素に印加する。データドライバは、更に、ピクセル調節期間の間に、ピクセルアレーの一部の行を再スキャンして、受信したフレームに基づいて、一部の行に含まれるそれぞれのピクセル要素に第2電圧を印加する。1以上の光源は、第1時刻においてピクセルアレーを照らすように構成されている。いくつかの実施形態では、1以上の光源は、ピクセル調節期間の間に非活性化される場合がある。

10

#### 【0008】

いくつかの実施形態では、表示デバイスは、受信したフレームに基づいて、複数のピクセル要素について、それぞれに、複数のピクセル値を決定するように構成されたオーバードライブ回路部を備える場合がある。ピクセルアレーに含まれる各ピクセル要素について、オーバードライブ回路部は、ピクセル要素をそのターゲットピクセル値において安定させるターゲット電圧を決定する場合がある。オーバードライブ回路部は、更に、ピクセル要素についてのオーバードライブ電圧がそのピクセル要素についてのターゲット電圧とは異なるところのオーバードライブ電圧を受信するようにピクセル要素のうち少なくともいくつかを選択する場合がある。いくつかの態様では、オーバードライブ回路部は、オーバードライブ電圧を受信するように選択されたピクセル要素に少なくとも部分的に基づいて、再スキャンされるべき一部の行を選択する場合がある。

20

#### 【0009】

いくつかの実施形態では、データドライバは、ピクセルアレーの一部の行に含まれるそれぞれのピクセル要素にオーバードライブ電圧を印加し、ピクセルアレーのうち残る各行に含まれるそれぞれのピクセル要素にターゲット電圧を印加することで、ピクセルアレーの各行をスキャンする場合がある。データドライバは、更に、ピクセルアレーの一部の行に含まれるそれぞれのピクセル要素に、ターゲット電圧を印加することで、ピクセルアレーの各行を再スキャンする場合がある。

#### 【0010】

いくつかの実施形態では、画像が、全視野 (full field-of-view) (FFOV) 画像と、FFOV画像の内に位置する中心視画像と、を含む場合がある。表示デバイスは、FFOV画像の各ピクセルを表示するための、ピクセルアレーの複数のピクセル要素を選択するように構成されたディスプレイドライバを更に備える場合がある。ディスプレイドライバは、更に、ピクセルアレーのそれぞれのピクセル要素を中心視画像の各ピクセルを表示するように選択する場合がある。いくつかの態様では、ディスプレイドライバは、中心視画像を表示するように選択されたピクセル要素に少なくとも部分的に基づいて、一部の行を選択する場合がある。いくつかの実施形態では、第1電圧のそれぞれは、FFOV画像をピクセルアレーのそれぞれのピクセル要素に描写するために用いられる場合があり、第2電圧のうち少なくともいくつかは、中心視画像をピクセルアレーのそれぞれのピクセル要素に描写するために用いられる場合がある。

30

#### 【0011】

いくつかの実施形態では、データドライバは、ピクセル要素の各グループがピクセルアレーの複数の行を含むところの、ピクセル要素のグループを連続して活性化し、活性化された各グループについて複数の行に含まれるそれぞれのピクセル要素に、同時に、第1電圧を印加することで、ピクセルアレーの各行をスキャンする場合がある。データドライバは、更に、一部の行に含まれるピクセル要素の各行を連続して活性化し、活性化された各行に含まれるそれぞれのピクセル要素に第2電圧を印加することで、ピクセルアレーの各行を再スキャンする場合がある。いくつかの態様では、スキャンすることが、再スキャンすることよりも高速に実行される場合がある。

40

#### 【図面の簡単な説明】

50

**【0012】**

示された実施形態は、例として図示されており、添付の図面の図によって限定されることを意図されたものでは無い。

**【0013】**

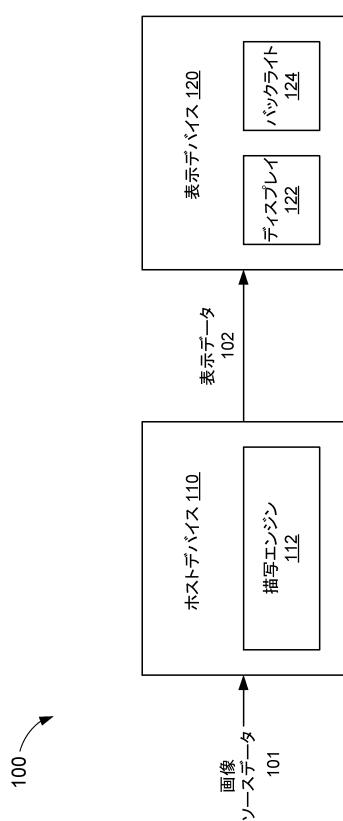

【図1】図1は、本実施形態がその中で実装され得る表示システムの例を示す。

**【0014】**

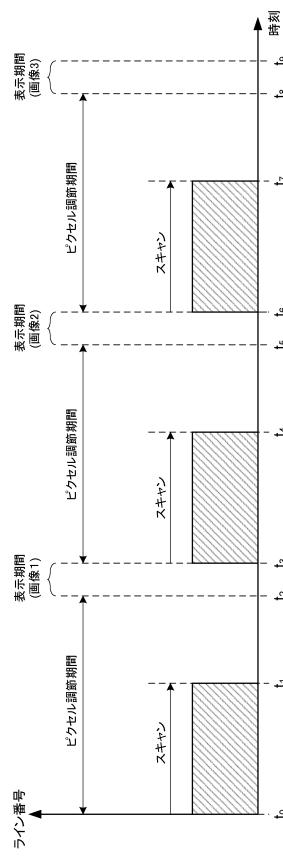

【図2】図2は、表示デバイスのピクセル要素を周期的に更新するための例示的な動作を表すタイミング図を示す。

**【0015】**

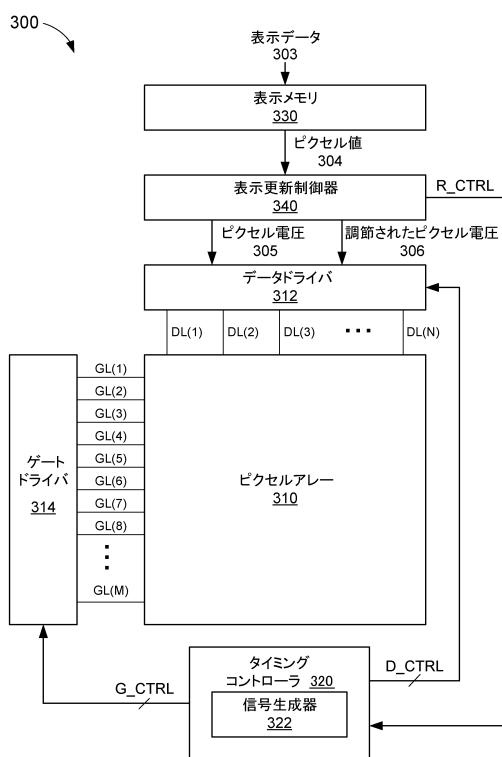

【図3】図3は、いくつかの実施形態に係る、表示デバイスのブロック図を示す。

10

**【0016】**

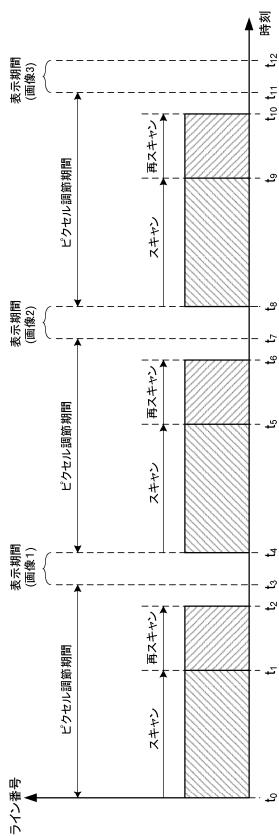

【図4】図4は、いくつかの実施形態に係る、例示的なスキャン 再スキャンピクセル更新動作を表すタイミング図を示す。

**【0017】**

【図5】図5は、いくつかの実施形態に係る、オーバードライブ回路部を有する表示デバイスのブロック図を示す。

**【0018】**

【図6】図6は、表示デバイスのピクセル更新の例示的なタイミングを表すタイミング図を示す。

**【0019】**

【図7A】図7Aは、いくつかの実施形態に係る、プログレッシブオーバードライブの実装例を表すタイミング図を示す。

20

【図7B】図7Bは、いくつかの実施形態に係る、プログレッシブオーバードライブの実装例を表すタイミング図を示す。

**【0020】**

【図8】図8は、いくつかの実施形態に係る、例示的なオーバードライブ補正動作を表すタイミング図を示す。

**【0021】**

【図9】図9は、いくつかの実施形態に係る、中心視描写回路部を有する表示デバイスのブロック図を示す。

30

**【0022】**

【図10】図10は、いくつかの実施形態に係る、表示デバイスに表示され得る例示的な画像を示す。

**【0023】**

【図11】図11は、いくつかの実施形態に係る、例示的なフレームバッファ画像を示す。

**【0024】**

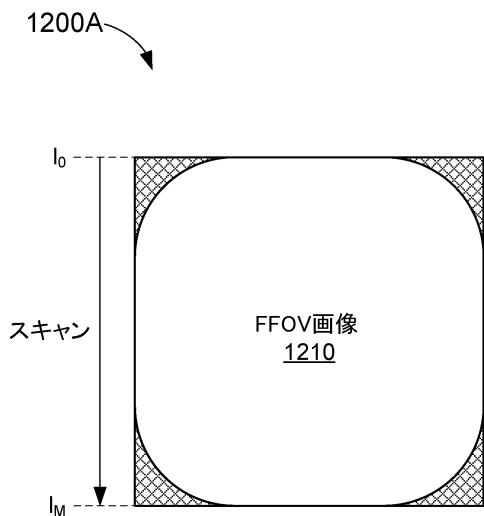

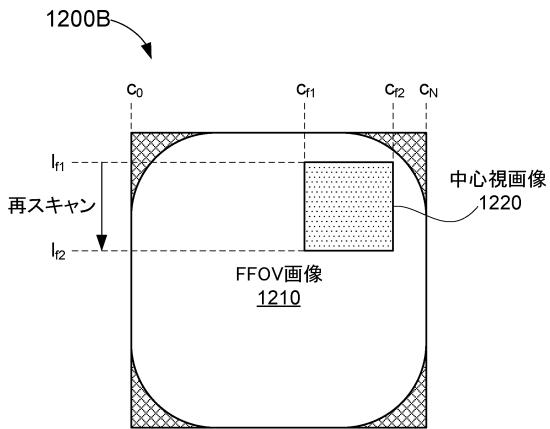

【図12A】図12Aは、いくつかの実施形態に係る、表示デバイスに画像を描写するための例示的な動作を示す。

【図12B】図12Bは、いくつかの実施形態に係る、表示デバイスに画像を描写するための例示的な動作を示す。

40

**【0025】**

【図13】図13は、いくつかの実施形態に係る、例示的な中心視描写処理を表すタイミング図を示す。

**【0026】**

【図14】図14は、いくつかの実施形態に係る、階層的なゲートドライバ回路のブロック図である。

**【0027】**

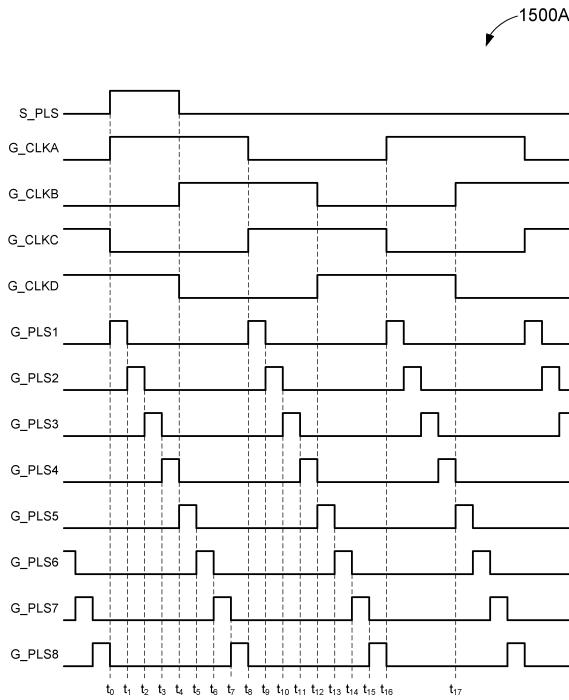

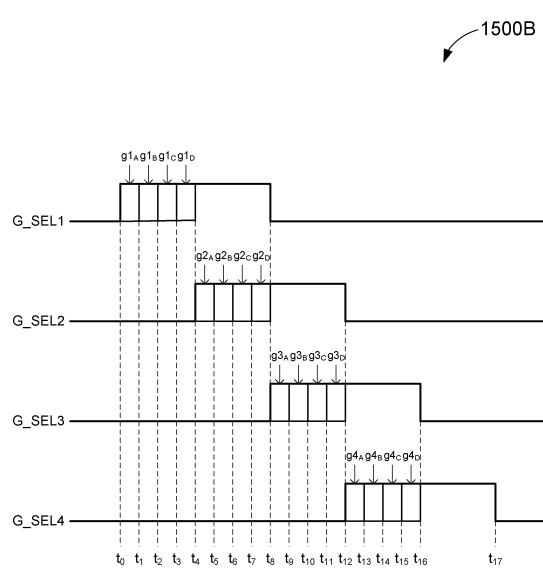

【図15A】図15Aは、いくつかの実施形態に係る、階層的なゲートドライバ回路の動作を制御するために用いられる例示的なタイミング信号を表すタイミング図である。

【図15B】図15Bは、いくつかの実施形態に係る、階層的なゲートドライバ回路の動

50

作を制御するために用いられる例示的なタイミング信号を表すタイミング図である。

【0028】

【図16】図16は、いくつかの実施形態に係る、階層的なゲートドライバ回路を用いたスキャン 再スキャンピクセル更新動作の例示的なタイミングを表すタイミング図を示す。

【0029】

【図17】図17は、いくつかの実施形態に係る、表示デバイスの一部を表すブロック図である。

【0030】

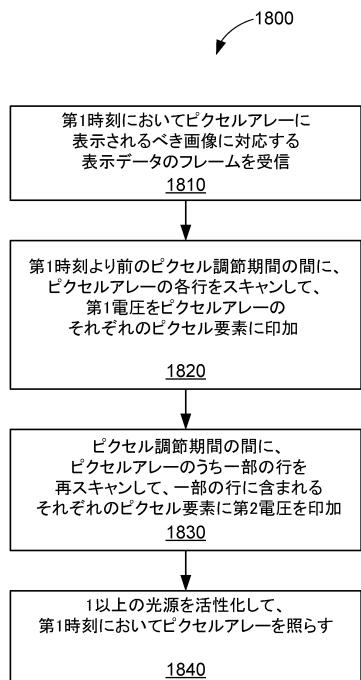

【図18】図18は、いくつかの実施形態に係る、例示的なスキャン 再スキャンピクセル更新動作を表す例示的なフローチャートである。

10

【0031】

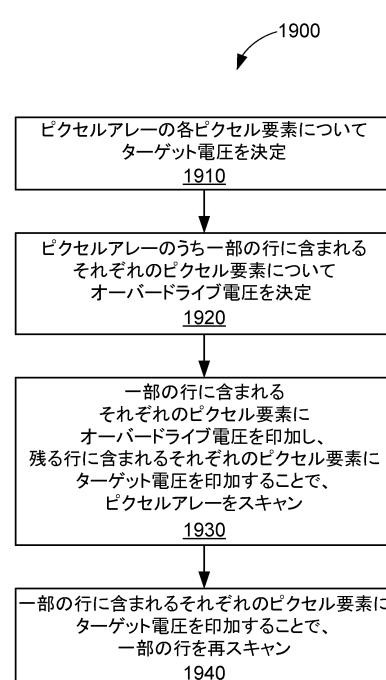

【図19】図19は、いくつかの実施形態に係る、例示的なオーバードライブ補正動作を表す例示的なフローチャートである。

【0032】

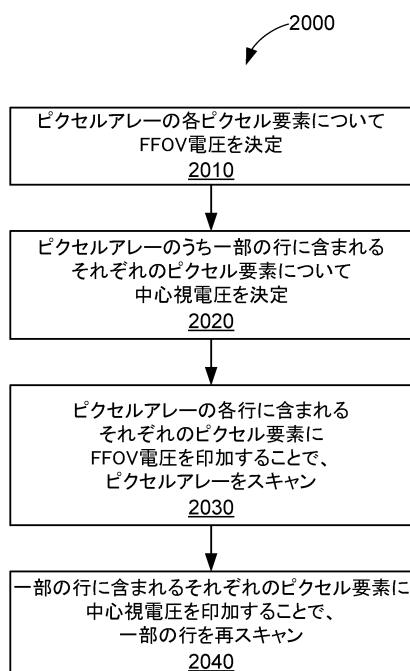

【図20】図20は、いくつかの実施形態に係る、例示的な中心視描写動作を表す例示的なフローチャートである。

【発明を実施するための形態】

【0033】

以下の説明では、本開示の十分な理解を提供するために、具体的なコンポーネント、回路、及び、処理の例のような、多くの具体的な詳細が示される。ここで使われる「接続された」という言葉は、直接に接続されている、又は、仲介する1以上のコンポーネント又は回路を介して接続されていることを意味する。「電子システム」や「電子デバイス」という用語は、情報を電子的に処理可能な任意のシステムを示すために、互換可能に用いられる場合がある。更に、以下の説明において、及び、説明を目的として、本開示の態様の十分な理解を提供するために、特定の命名法が用いられる。しかし、例示的な実施形態を実施するためには、これらの具体的な詳細が必要でない場合があることが当業者には明らかであろう。他の例では、本開示が不明確になることを避けるために、周知の回路及びデバイスがブロック図の形式で示される。以下の詳細な説明のいくつかの部分は、過程、論理ブロック、処理、及び、コンピュータのメモリ内のデータービットへの操作を他の記号で表現したもの、という形で提示されている。

20

【0034】

これらの説明及び表現は、データ処理技術の当業者によって、彼らの仕事の実質をもつとも効果的に他の当業者に伝えるために用いられる手段である。本開示においては、過程、論理ブロック、又は、処理等は、所望の結果を導くステップ又は命令の自己無撞着なシーケンスとなるように考案されている。当該ステップは、物理量の物理的な操作を必要とするステップである。通常、必須ではないものの、これらの量はコンピュータシステムにおいて、記憶、送信、合成、比較、及び他の操作が可能な電子的又は磁気的な信号の形態を取る。しかしながら、これら及び同様の文言の全てが、適切な物理量と関連付けられるべきであり、かつ、これらの量に適用される便利なラベルに過ぎないということが留意されるべきである。

30

【0035】

後述の議論から明らかなように、特にそうでないと述べられていない場合には、本出願を通して、「アクセスする」、「受信する」、「送信する」、「用いる」、「選択する」、「決定する」、「正規化する」、「乗算する」、「平均する」、「モニタする」、「比較する」、「適用する」、「更新する」、「計測する」、「導出する」、等のような表現を用いて行われる議論は、コンピュータシステム（又は同様の電子計算デバイス）によるアクション及び処理を参照していると認められる。これらのアクション及び処理は、コンピュータシステムのレジスタ及びメモリ内の物理（電気）量として示されるデータを、コンピュータシステムのメモリまたはレジスタ、又は他のそのような情報ストレージ、伝送器、又は表示デバイス内の物理量として同様に示される他のデータに操作及び変換する。

40

50

### 【0036】

図において、単一のブロックが一又は複数の機能を実行するように説明される場合がある。しかし、実際の実施においては、そのブロックによって実行される一又は複数の機能は、単一のコンポーネントによって、あるいは複数のコンポーネントにまたがって実行される場合があり、及び／又は、ハードウェアを用いて、ソフトウェアを用いて、又は、ハードウェア及びソフトウェアの組合せを用いて実行される場合がある。このハードウェアとソフトウェアの互換可能性を明確に示すために、様々な例示的なコンポーネント、ブロック、モジュール、回路、及び、ステップが、それらの機能性の観点から、以下で一般に説明される。そのような機能性がハードウェア又はソフトウェアのいずれとして実装されるかは、特有の用途と、システム全体に課せられる設計上の制約と、に依存する。当業者は、説明された機能性を各特有の用途に応じた多様な方法で実装し得るが、そのような実装の決定が、本発明の範囲からの逸脱を起こすと解釈されてはならない。さらに、例示的な入力デバイスは、示されたものとは異なるコンポーネントとして、プロセッサ、及び、メモリ等といった周知のコンポーネントを含む場合がある。

10

### 【0037】

ここで説明される技術は、特定の態様で実装されると特に記述されない場合は、ハードウェア、ソフトウェア、ファームウェア、又はそれらの組み合わせとして実装し得る。モジュール又はコンポーネントとして説明された任意の構成は、集積ロジックデバイスと一緒に実装されることがあり、又は、別々だが相互に情報交換可能な論理デバイス、として別々に実装されることがある。ソフトウェアとして実装された場合、この技術は、少なくとも部分的に、実行されたときに上述された方法のうち1以上を実施する命令を保存する非一時的なプロセッサ読み取り可能な記憶媒体によって実現され得る。この非一時的なプロセッサ読み取り可能なデータ記憶媒体は、コンピュータプログラム製品の一部を形成する場合がある。コンピュータプログラム製品は、包装材を含み得る。

20

### 【0038】

非一時的なプロセッサ読み取り可能な記憶媒体は、同期ダイナミックランダムアクセスメモリ(synchronous dynamic random access memory) (SDRAM)のようなランダムアクセスメモリ(random access memory) (RAM)、リードオンリーメモリ(read only memory) (ROM)、不揮発性ランダムアクセスメモリ(non-volatile random access memory) (NVRAM)、電子的消去可能プログラマブルリードオンリーメモリ(electrically erasable programmable read-only memory) (EEPROM)、フラッシュメモリ、他の既知の記憶媒体等、を備える場合がある。本技術は追加的に、あるいは代替的に、少なくとも一部が、コードを命令又はデータ構造の形で伝達または通信し、かつ、コンピュータ又は他のプロセッサによってアクセス、読み取り、及び／又は、実行可能な、プロセッサ読み取り可能な通信媒体によって実現され得る。

30

### 【0039】

本明細書で開示される実施形態に関して説明される様々な例示的な論理ブロック、モジュール、回路、及び、命令は、1以上のプロセッサによって実行され得る。本明細書で用いられる「プロセッサ」という言葉は、任意の汎用プロセッサ、従来のプロセッサ、コントローラ、マイクロコントローラ、及び／又は、メモリに記憶された1以上のソフトウェアプログラムのスクリプト又は命令を実行可能な状態機械、を示す場合がある。本明細書で用いられる「電圧源」という言葉は、直流(direct-current) (DC)の電圧源、交流(alternating-current) (AC)の電圧源、又は、(接地のような)電位を生成する他の手段を示す場合がある。

40

### 【0040】

図1は、本実施形態が実装され得る例示的な表示システム100を示す。表示システム100は、ホストデバイス110と、表示デバイス120と、を備える。表示デバイス120は、画像、又は、一連の画像(例えば、動画)をユーザに表示するように構成された

50

任意のデバイスであり得る。いくつかの実施形態では、表示デバイス 120 は、ヘッドマウントディスプレイ (HMD) デバイスである場合がある。いくつかの態様では、ホストデバイス 110 は、表示デバイス 120 の物理的な一部として実装され得る。あるいは、ホストデバイス 110 は、バスやネットワークのような様々な有線及び / 又は無線の相互接続及び通信技術を用いて、表示デバイス 120 の構成要素に対して接続される（及び構成要素と通信する）場合がある。例示的な技術は、集積回路間 (Inter - Integrated Circuit) (I<sup>2</sup>C), シリアル・ペリフェラル・インターフェース (Serial Peripheral Interface) (SPI), PS/2, ユニバーサルシリアルバス (Universal Serial bus) (USB), ブルートゥース (登録商標)、赤外線データ通信 (Infrared Data Association) (IrDA)、及び、IEEE 802.11 基準で定義された様々な無線周波数 (radio frequency) (RF) 通信プロトコルを含み得る。

#### 【0041】

ホストデバイス 110 は、画像ソースデータ 101 を画像ソース（シンプルにするために図示せず）から受信し、表示デバイス 120 において表示するために（例えば、表示データ 102 として）画像ソースデータ 101 を描写する。いくつかの実施形態では、ホストデバイス 110 は、画像ソースデータ 101 を表示デバイス 120 の 1 以上の能力に従って処理するように構成された描写エンジン 112 を備える場合がある。例えば、いくつかの態様では、表示デバイス 120 はユーザの目の位置に基づいて動的に更新された画像をユーザに表示する場合がある。より詳細には、表示デバイス 120 は、ユーザの頭及び / 又は目の動きを追跡する場合があり、画像のうちユーザが凝視する点と一致する部分（例えば、中心視領域）を、画像の他の領域（例えば、フルフレーム画像）よりも高い解像度で表示する場合がある。そのため、いくつかの実施形態では、描写エンジン 112 は、フルフレーム画像の中心視領域に重ねられるべき高解像度の中心視画像を生成する場合がある。いくつかの他の実施形態では、描写エンジン 112 は、フルフレーム画像を表示デバイス 120 において（例えば、中心視画像よりも低解像度で）表示するためにスケーリングする場合がある。

#### 【0042】

表示デバイス 120 は、表示データ 102 をホストデバイス 110 から受信し、受信した表示データ 102 に基づいて、対応する画像をユーザに表示する。いくつかの実施形態では、表示デバイス 120 はディスプレイ 122 と、バックライト 124 と、を備える場合がある。ディスプレイ 122 は、表示パネルの一方の表面から他方へと通過する光の量を（例えば、各ピクセル要素に印加される電圧又は電場に応じて）変化可能にするよう構成されたピクセル要素（例えば、液晶セル）のアレーから形成された液晶ディスプレイ (LCD) パネルである場合がある。例えば、表示デバイス 120 は、各ピクセル要素に適切な電圧を印加して、（フルフレーム画像に重ねられた中心視画像を含む場合がある）画像をディスプレイ 122 上で描写する場合がある。上述したように、LCD は発光しないため、画像がユーザに視認可能になるように、ピクセル要素を照らす別個の光源に依存する。

#### 【0043】

バックライト 124 は、背後からピクセル要素を照らすために、ディスプレイ 122 に近接して配置される場合がある。バックライト 124 は、冷陰極蛍光灯 (cold cathode fluorescent lamp) (CCFL)、外部電極型蛍光灯 (external electrode fluorescent lamp) (EEFL)、熱陰極蛍光灯 (hot-cathode fluorescent lamp) (HCFL)、フラット型蛍光灯 (flat fluorescent lamp) (FFL)、発光ダイオード (light-emitting diode) (LED)、又は、これらの任意の組合せ（しかしこれに限定されない）を含む 1 以上の光源を備える場合がある。いくつかの態様では、バックライト 124 は、ディスプレイ 122 の異なる領域に異なるレベルの照明を供給可能な（LED のような）個別の光源のアレーを備える場合がある。い

10

20

30

40

50

くつかの実施形態では、表示デバイス 120 は、例えば、画像の品質向上、及び／又は、消費電力の節約のために、バックライト 124 の強度又は明るさを動的に変更可能なインバータ（シンプルにするために図示せず）を備える場合がある。

#### 【0044】

固定 LCD ディスプレイでは、バックライト 124 はピクセルアレーに照明を継続して（例えば、バックライトが継続的にオンであるか、少なくとも所望の明るさレベルになるようにパルス幅が変調される）提供する場合がある。そのため、ピクセル値の任意の変化は、更新された電圧がピクセル要素に印加されるとすぐに認識可能となる場合がある。しかしながら、仮想現実（VR）のアプリケーションでは、ディスプレイで視認されるオブジェクトは、ユーザの頭及び／又は目が動くにつれて、異なるピクセルによって照らされる場合がある。ピクセル値の急激な変動は、LCD ディスプレイに描写された画像において、仮想現実体験を損ない得るモーションブラー及び／又は他のアーティファクトを生じ得る。表示デバイスは、表示を（継続的に行うよりは）周期的に更新することによりモーションブラーを低減あるいは防ぐことがある。例えば、表示デバイスは、そのような間隔でピクセル値が急激に変化することが（例えば、人の視覚認識におけるサッカード抑制現象と同様に）抑制されるように、バックライトを周期的な間隔で点滅する場合がある。

#### 【0045】

図 2 は、表示デバイスのピクセル要素を周期的に更新するための例示的な動作を表すタイミング図 200 を示す。図 2 で示すように、表示の更新はそれぞれ、ピクセル調節期間（例えば、時刻  $t_0$  から  $t_2$ 、 $t_3$  から  $t_5$ 、及び、 $t_6$  から  $t_8$ ）と、これに続く一連の画像（例えば、画像 1、画像 2、及び、画像 3）を表示するための表示期間（例えば、時刻  $t_2$  から  $t_3$ 、 $t_5$  から  $t_6$ 、及び、 $t_8$  から  $t_9$ ）と、を含む。各ピクセル調節期間の間に、表示デバイスはピクセル要素のアレーを“スキャン”して（例えば、一度に一行）、ディスプレイの各ピクセル要素についてピクセル値を更新する場合がある。より詳細には、各ピクセル要素は、ピクセル要素を新たなピクセル値に遷移（又は、現在のピクセル値を保持）させる所望の電圧を印加される場合がある。各表示期間の間、表示デバイスのバックライト（又は、1 以上の光源）が、ピクセルアレーを照らし、表示デバイスに画像を表示するために、短時間活性化又はオンにされる。なお、バックライトは、ピクセル調節期間の間に、（例えば、ピクセル更新をユーザに気づかれないように）非活性化又はオフにされる場合がある。

#### 【0046】

従来の LCD ディスプレイでは、ピクセルアレーは各ピクセル調節期間の間に一度だけスキャンされる。例えば、ピクセルアレーが表示のために照らされる前に、ピクセルアレーの各ピクセル要素に電圧が一度だけ印加され得る。しかし、本開示の態様では、初期スキャンが完了した後に、ピクセル値の更なる調節を行うことが望ましいことがあり得ることが認識されている。例えば、追加的な調節が、特定のピクセル要素についてのピクセル値を更に精緻化、又は、補正するために用いられる場合がある。そのため、いくつかの実施形態では、表示デバイスは、ピクセルアレーのうち 1 以上の行を（例えば、初期スキャンが実行された後に）再スキャンして、再スキャンされた行に含まれるピクセル要素に電圧の第 2 セットを印加する場合がある。より詳細には、表示デバイスは、单一のピクセル調節期間の間に（例えば、異なる時刻において）同じピクセル要素に 2 以上の電圧を印加する場合がある。

#### 【0047】

図 3 は、1 以上の実施形態に係る、表示デバイス 300 のブロック図を示す。表示デバイス 300 は、図 1 の表示デバイス 120 の例示的な実施形態である場合がある。表示デバイス 300 は、ピクセルアレー 310、タイミングコントローラ 320、表示メモリ 330、及び、表示更新制御器 340 を備える場合がある。いくつかの実施形態では、表示デバイス 300 は LCD 表示パネルに対応する場合がある。ピクセルアレー 310 は複数のピクセル要素（シンプルにするために図示せず）を備えている場合がある。ピクセル要素の各行はそれぞれのゲートライン（GL）に接続され、ピクセル要素の各列はそれれ

10

20

30

40

50

のデータライン ( D L ) に接続されている。これに応じて、アレー 3 1 0 に含まれる各ピクセル要素はゲートライン及びソースラインの交差点に配置されている。

#### 【 0 0 4 8 】

データドライバ 3 1 2 は、データライン D L ( 1 ) ~ D L ( N ) を介してピクセルアレー 3 1 0 に接続されている。いくつかの態様では、データドライバ 3 1 2 は、データライン D L ( 1 ) ~ D L ( N ) を介して、個別のピクセル要素に（例えば、対応する電圧の形で）ピクセルデータを印加して、ピクセルアレー 3 1 0 に表示されるフレーム又は画像を更新するように構成されている場合がある。例えば、データライン D L ( 1 ) ~ D L ( N ) に印加される電圧は、アレー 3 1 0 （例えば、ピクセル要素が液晶であるとき）のピクセル要素の物理状態を変える（例えば、回転）場合がある。そのため、各ピクセル要素に印加される電圧は、色、及び / 又は、ピクセル要素によって発される光の強度に影響を与える場合がある。なお、ピクセルアレー 3 1 0 のピクセル要素の各行は、それぞれ同じデータライン D L ( 1 ) ~ D L ( N ) に接続される。そのため、表示デバイス 3 0 0 は、ピクセル要素の行を逐次的に（例えば、一度に一行）スキャンすることで、ピクセルアレー 3 1 0 を更新する場合がある。10

#### 【 0 0 4 9 】

ゲートドライバ 3 1 4 は、ゲートライン G L ( 1 ) ~ G L ( M ) を介してピクセルアレー 3 1 0 に接続される。いくつかの態様では、ゲートドライバ 3 1 4 は、任意の所与の時刻において、データドライバ 3 1 2 によって印加されるピクセルデータをピクセル要素の何れの行が受信するかを選択するように構成される場合がある。例えば、アレー 3 1 0 に含まれる各ピクセル要素は、アクセストランジスタ（シンプルにするために図示せず）を介して、データライン D L ( 1 ) ~ D L ( N ) のうち 1 つ、及び、ゲートライン G L ( 1 ) ~ G L ( M ) のうち一つと接続される場合がある。アクセストランジスタは、ゲートライン G L ( 1 ) ~ G L ( M ) のうち一つと接続されたゲート端子と、データライン D L ( 1 ) ~ D L ( N ) のうち一つと接続されたドレイン（又はソース）端子と、アレー 3 1 0 に含まれる対応するピクセル要素と接続されたソース（又はドレイン）端子、を有する N MOS（又は PMOS）トランジスタである場合がある。ゲートライン G L ( 1 ) ~ G L ( M ) のうち一つが十分に高い電圧を印加されたときに、選択されたゲートラインと接続されたアクセストランジスタがオンになり、データライン D L ( 1 ) ~ D L ( N ) から、選択されたゲートラインと接続された対応するピクセル要素へと電流が流れることができるようになる。これに応じて、ゲートドライバ 3 1 4 は、ゲートライン G L ( 1 ) ~ G L ( M ) のそれを、ピクセルアレー 3 1 0 の各行が更新されるまで、逐次に選択する、あるいは活性化するように構成される場合がある。20

#### 【 0 0 5 0 】

タイミングコントローラ 3 2 0 は、データドライバ 3 1 2 とゲートドライバ 3 1 4 のタイミングを制御するように構成される。例えば、タイミングコントローラ 3 2 0 は、タイミング制御信号の第 1 セット ( D\_CTR\_L ) を生成して、データドライバ 3 1 2 によるデータライン D L ( 1 ) ~ D L ( N ) の活性化を制御する場合がある。タイミングコントローラ 3 2 0 は、タイミング制御信号の第 2 セット ( G\_CTR\_L ) を更に生成して、ゲートドライバ 3 1 4 によるゲートライン G L ( 1 ) ~ G L ( M ) の活性化を制御する場合がある。タイミングコントローラ 3 2 0 は、信号生成器 3 2 2 によって生成される基準クロック信号に基づいて、D\_CTR\_L 及び G\_CTR\_L 信号を生成する場合がある。例えば、信号生成器 3 2 2 は水晶発振器である場合がある。タイミングコントローラ 3 2 0 は、それぞれの位相オフセットを基準クロック信号に適用することに基づいて、D\_CTR\_L 及び G\_CTR\_L 信号を駆動する場合がある。より詳細には、D\_CTR\_L 信号及び G\_CTR\_L 信号のタイミングは、データドライバ 3 1 2 がそのピクセル要素の行について意図されたピクセルデータでデータライン D L ( 1 ) ~ D L ( N ) を駆動する時刻において、ゲートドライバ 3 1 4 が（例えば、ピクセルデータを印加されるべきピクセル要素の行に接続された）正しいゲートラインを活性化するように、同期される場合がある。30

#### 【 0 0 5 1 】

10

20

30

40

50

表示メモリ 330 は、ピクセルアレー 310 に表示されるべき画像に対応する表示データ 303 を記憶又はバッファするように構成される場合がある。表示データ 303 は、アレー 310 の 1 以上のピクセル要素についての（例えば、色及び / 又は強度に対応する）ピクセル値 304 を含む場合がある。例えば、各ピクセル要素は、赤色 (R)、緑色 (G)、及び、青色 (B) のサブピクセルを含む（しかしこれに限定されない）複数のサブピクセルを備える場合がある。いくつかの態様では、表示データ 303 は、表示されるべき画像のサブピクセルについての R、G、及び、B の値を示す場合がある。R、G、及び、B の値は、各ピクセルの色及び強度（例えば、階調）に影響を及ぼす場合がある。例えば、ピクセル値 304 はそれぞれに、256 の可能な階調レベルのうち 1 つを示す 8 ビットの値である場合がある。各ピクセル値 304 はターゲット電圧のレベルに対応し得る。ターゲット電圧は、特定のピクセル要素に印加されたときに、そのピクセル要素の色及び / 又は明るさを所望のピクセル値に安定させる電圧であってもよい。

#### 【0052】

表示更新制御器 340 は、ピクセル値 304 に少なくとも部分的に基づいて、アレー 310 に含まれる 1 以上のピクセル要素に印加されるべきピクセル電圧を決定する場合がある。より詳細には、アレー 310 の各ピクセル要素について、表示更新制御器 340 は、現在のピクセル値（例えば、直前のフレーム更新からのピクセル値）をターゲットピクセル値（例えば、次のフレーム更新についてのピクセル値）と比較して、フレーム更新期間内にピクセル値の所望の変化を達成するためにピクセル要素に印加されるべき電圧の量を決定する場合がある。いくつかの実施形態では、表示更新制御器 340 は、単一のフレーム更新期間の間での、ピクセルアレーの複数回のスキャンを（例えば、スキャン及び再スキャン）を容易にし得る。例えば、ピクセルアレーの初期スキャンの間、表示更新制御器 340 は、（例えば、データドライバ 312 によって）ピクセルアレー 310 の各ピクセル要素に印加されるべきそれぞれのピクセル電圧 305 を決定する場合がある。後続するピクセルアレーの再スキャンの間、表示更新制御器 340 は、ピクセルアレー 310 の 1 以上の行に含まれるそれぞれのピクセル要素に印加されるべき調節されたピクセル電圧 306 を決定する場合がある。

#### 【0053】

いくつかの実施形態では、ピクセルアレー 310 の各行は、再スキャンする処理の間に更新される場合がある。例えば、表示更新制御器 340 は、ピクセルアレー 310 の各ピクセル要素について、ピクセル電圧 305 及び調節されたピクセル電圧 306 を決定する場合がある。いくつかの他の実施形態では、再スキャン動作の間に、より少ない一部の行のみが再スキャンされる場合がある。例えば、表示更新制御器 340 は、一部の行に含まれるそれぞれのピクセル要素についてのみ、調節されたピクセル電圧 306 を決定する場合がある。いくつかの態様では、表示更新制御器 340 は、再スキャンされるべき一部の行を示す再スキャン制御信号 (R\_CTR\_L) をタイミングコントローラ 320 に供給する場合がある。そして、再スキャン動作の間、タイミングコントローラ 320 は再スキャン制御信号によって調節されたピクセル電圧 306 を印加されるべきと示された一部の行のみを連続的に活性化する場合がある。

#### 【0054】

図 4 は、例示的なスキャン - 再スキャンピクセル更新動作を表すタイミング図 400 を示す。図 4 に示された例示的な動作は、図 3 の表示デバイス 300 のような表示デバイスによって実行される場合がある。そのため、いくつかの実施形態では、表示デバイスは、単一のフレーム更新期間（例えば、ピクセルアレーを更新して新たなフレーム又は画像を表示するとき）の間にピクセルアレーのスキャンを複数回実行するように構成されている場合がある。

#### 【0055】

図 4 に示すように、各フレーム更新期間は、ピクセル調節期間（例えば、時刻  $t_0$  から  $t_3$ 、 $t_4$  から  $t_7$ 、及び、 $t_8$  から  $t_{11}$ ）と、これに続いて、対応する画像（例えば、画像 1、画像 2、及び、画像 3）を表示するための表示期間（例えば、時刻  $t_3$  から  $t_4$

、 $t_7$ から $t_8$ 、及び、 $t_{11}$ から $t_{12}$ ）と、を含む。表示デバイスは、各ピクセル調節期間の間に、ピクセル要素のアレーを（例えば、時刻 $t_0$ から $t_1$ 、 $t_4$ から $t_5$ 、及び、 $t_8$ から $t_9$ までに）スキャンして、ディスプレイのピクセル要素それぞれについてピクセル値を更新する場合がある。表示デバイスは、そして、同一のピクセル調節期間の間に（例えば、時刻 $t_1$ から $t_2$ 、 $t_5$ から $t_6$ 、及び、 $t_9$ から $t_{10}$ までに）ピクセル要素の1以上の行を再スキャンして、ピクセルアレーのピクセル要素の一部について電圧及び／又はピクセル値を更に調節する場合がある。そのため、本開示の態様は、表示期間の持続時間を（特に、スキャンの終了と表示期間の開始の間）を利用して、1以上のピクセル要素についてのピクセル値を精緻化、又は、補正する場合がある。

#### 【0056】

いくつかの実施形態では、再スキャン動作は、オーバードライブ補正のために利用される場合がある。例えば、いくつかの態様では、ピクセル要素は、ピクセル要素をターゲットピクセル値に安定させ得るターゲット電圧を超える（例えば、ターゲット電圧より高い、又は、低い）オーバードライブ電圧を印加される場合がある。以下でより詳細に説明するように、オーバードライブ電圧は、ピクセル要素をターゲットピクセル値により高速に遷移させる。しかしながら、オーバードライブ電圧は、ピクセル要素を、ターゲットピクセル値を越えた（例えば、ターゲットピクセル値より高い又は低い）ピクセル値に安定させる場合もある。このことは、表示されるべき次の画像又はフレームについてのピクセル電圧の計算を更に複雑にし得る。そのため、いくつかの実施形態では、表示デバイスは、ピクセル要素をターゲットピクセル値に安定させるために、オーバードライブ電圧が印加されるピクセル要素を（例えば、初期スキャンから）再スキャンする場合がある。例えば、表示デバイスは再スキャンされた行に含まれるそれぞれのピクセル要素にターゲット電圧を印加する場合がある。

#### 【0057】

いくつかの他の実施形態では、再スキャン動作は中心視描画のために用いられる場合がある。例えば、いくつかの態様では、表示される画像は、中心視画像と合成された全視野（FFOV）画像を含む場合がある。より詳細には、中心視画像は、FFOV画像の中心視領域内で表示される場合がある。FFOV画像及び中心視画像のピクセル値をマージすることは時間とリソースを消費する場合があり、それによりピクセルアレーの更新が可能な速度をさらに制限する場合がある。そこで、いくつかの実施形態では、表示デバイスはFFOV画像及び中心視画像をピクセルアレー上で、別々に、異なる速度で描写する場合がある。例えば、表示デバイスは、FFOV画像を中心視画像よりも高速に描写する場合がある。いくつかの態様では、表示デバイスは、ピクセルアレーの各ピクセル要素を更新して、初期スキャンの間にFFOV画像を描写する場合がある。表示デバイスは、FFOV画像の中心視領域に対応するピクセルアレーの行を連続的に再スキャンして、中心視画像をそこに描写する場合がある。

#### 【0058】

オーバードライブ補正

#### 【0059】

上記で説明したように、各ピクセル要素の色及び／又は明るさは、そのピクセル要素に印加される電圧を変化することで調節される場合がある。具体的には、特定のピクセル値に対応するターゲット電圧は、ピクセル要素に印加されたときに、該ピクセル要素を希望のピクセル値に安定させる電圧を表す場合がある。しかしながら、単一のフレーム遷移又は更新において達成可能な色及び／又は明るさの変化の度合いは、ピクセル要素の安定化時間によって制限される場合がある。例えば、最大明るさの値（例えば、「白色」のピクセル）から最小明るさの値（例えば、「黒色」のピクセル）への遷移は、中間の明るさ設定から他の中間の明るさ設定への（例えば、「灰色」のうち一つの色合いから「灰色」の他の色合いへの）遷移よりも長い安定化時間を必要とし得る。

#### 【0060】

もしピクセル値の変化が閾値量を超える場合、ターゲット電圧は、所与のフレーム更新

10

20

30

40

50

期間内にピクセル要素を所望のピクセル値で駆動するためには不十分である場合がある。ピクセル要素が連續するフレーム更新の間に所望の色、及び／又は、明るさに到達できない場合には、（ゴーストのような）アーティファクトが表示された画像に現れる場合がある。LCDオーバードライブはLCDディスプレイを更新するときのピクセルの遷移の速度を速くするための技術である。具体的には、ピクセル要素は、所望の色及び／又は明るさに関連するターゲット電圧よりも高い電圧を駆動され得る。より高い電圧は、ピクセル要素の中の液晶をより速く回転させ、そのため、ターゲットの明るさにより短時間で遷移させる。

#### 【0061】

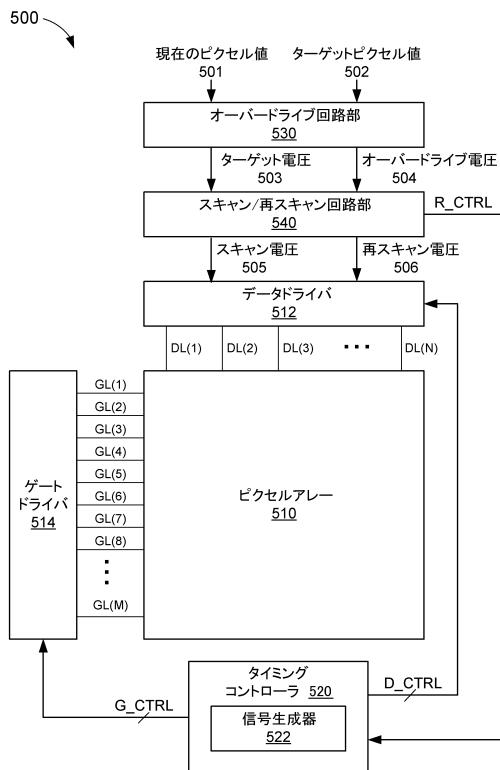

図5は、いくつかの実施形態に係る、オーバードライブ回路部を有する表示デバイス500のブロック図を示す。表示デバイス500は、図1の表示デバイス120、又は、図3の表示デバイス300の例示的な実施形態である場合がある。表示デバイス500は、ピクセルアレー510、タイミングコントローラ520、及び、オーバードライブ回路部530、スキャン／再スキャン回路部540を備える場合がある。いくつかの実施形態では、表示デバイス500はLCD表示パネルに対応する場合がある。ピクセルアレー510は複数のピクセル要素（シンプルにするために図示せず）を備えている場合がある。ピクセル要素の各行はそれぞれのゲートライン（GL）に接続され、ピクセル要素の各列はそれぞれのデータライン（DL）に接続されている。

10

#### 【0062】

データドライバ512は、データラインDL(1)～DL(N)を介してピクセルアレー510に接続されている。いくつかの態様では、データドライバ512は、データラインDL(1)～DL(N)を介して、個別のピクセル要素に（例えば、対応する電圧の形で）ピクセルデータを印加して、ピクセルアレー510に表示されるフレーム又は画像を更新するように構成されている場合がある。なお、ピクセルアレー510のピクセル要素の各行は、それぞれ同じデータラインDL(1)～DL(N)に接続される。そのため、表示デバイス500は、ピクセル要素の行を逐次的に（例えば、一度に一行）スキャンすることで、ピクセルアレー510を更新する場合がある。

20

#### 【0063】

ゲートドライバ514は、ゲートラインGL(1)～GL(M)を介してピクセルアレー510に接続される。いくつかの態様では、ゲートドライバ514は、任意の所与の時刻において、データドライバ512によって駆動されるピクセルデータをピクセル要素の何れの行が受信するかを選択するように構成される場合がある。例えば、ゲートドライバ514は、ゲートラインGL(1)～GL(M)のそれぞれを、ピクセルアレー510の各行が更新されるまで、逐次に選択する、あるいは活性化するように構成される場合がある。

30

#### 【0064】

タイミングコントローラ520は、データドライバ512とゲートドライバ514のタイミングを制御するように構成される。例えば、タイミングコントローラ520は、タイミング制御信号の第1セット(D\_CTR\_L)を生成して、データドライバ512によるデータラインDL(1)～DL(N)の活性化を制御する場合がある。タイミングコントローラ520は、タイミング制御信号の第2セット(G\_CTR\_L)を更に生成して、ゲートドライバ514によるゲートラインGL(1)～GL(M)の活性化を制御する場合がある。タイミングコントローラ520は、信号生成器522によって生成される基準クロック信号に基づいて、D\_CTR\_L及びG\_CTR\_L信号を生成する場合がある。

40

#### 【0065】

オーバードライブ回路部530は、アレー510の各ピクセル要素についての現在のピクセル値501及びターゲットピクセル値502に少なくとも部分的に基づいて、ピクセルアレー510の各ピクセル要素に印加されるべきピクセル電圧を決定する場合がある。例えば、現在のピクセル値501及びターゲットピクセル値502は、（図3の表示メモリ330のような）フレームバッファメモリから取得される場合がある。より詳細には、

50

アレー 510 の各ピクセル要素について、オーバードライブ回路部 530 は現在のピクセル値 501（例えば、直前のフレーム更新からのピクセル値）をターゲットピクセル値 502（例えば、次のフレーム更新についてのピクセル値）と比較して、フレーム更新期間内にピクセル値の所望の変化を達成するためにピクセル要素に印加されるべき電圧の量を決定する場合がある。

#### 【0066】

いくつかの実施形態では、オーバードライブ回路部 530 はアレー 510 に含まれるピクセル要素のそれについて、ターゲット電圧 503 を決定する場合がある。上記で説明したように、特定のピクセル要素についてのターゲット電圧 503 は、該ピクセル要素をそのターゲットピクセル値 502 に安定させる。しかしながら、ピクセル値の変化が閾値量を超えている場合には、ターゲット電圧 503 は、ピクセル要素を所与のフレーム更新期間内に所望のピクセル値に駆動するためには十分でない場合がある。言い換えると、ピクセル要素は、自らのターゲットピクセル値 502 に安定するための時間を十分に有していない場合がある。そのため、いくつかの実施形態では、オーバードライブ回路部 530 は、アレー 510 に含まれる 1 以上のピクセル要素に印加されるべきオーバードライブ電圧 504 を決定する場合がある。上記で説明したように、オーバードライブ電圧 504 は、ピクセル要素についてのターゲット電圧 503 を超える（例えば、より高い、又は、より低い）場合があり、このため、オーバードライブ電圧 504 はターゲットピクセル値に向けて該ピクセル要素をより速く遷移させる場合がある。

#### 【0067】

本開示の態様は、オーバードライブ電圧はピクセル要素をより短い期間でターゲットピクセル値に到達させ得るが、オーバードライブ電圧はピクセル要素をターゲットピクセル値からオーバーシュートさせることを認識している。言い換えると、ピクセル要素は、最終的にターゲットピクセル値とは異なるピクセル値で安定する場合がある。このことは、連続するフレーム間でのピクセル電圧の計算を更に複雑にし得る。例えば、上記で説明したように、特定のピクセル要素に適用されるべきオーバードライブの量は、現在のピクセル値 501 からターゲットピクセル値 502 までの変化量に依存する。しかし、オーバードライブ電圧がピクセル要素に印加された後には、そのピクセル要素の現在のピクセル値 501 は、そのピクセル要素の前のフレームからのピクセル値に依存する。

#### 【0068】

例えば図 2 を参照して、第 3 のピクセル調節期間（例えば、時刻  $t_6$  から  $t_8$ ）の間に、特定のピクセル要素に印加されるべきピクセル電圧は、そのピクセル要素の現在の（例えば、時刻  $t_6$  から  $t_7$  までの）ピクセル値に加えて次の表示期間の開始（例えば、時刻  $t_8$ ）までに到達すべきターゲットピクセル値にも依存し得る。第 2 ピクセル調節期間（例えば、時刻  $t_3$  から  $t_5$ ）の間にオーバードライブ電圧がピクセル要素に印加される場合、ピクセル要素についての現在のピクセル値は、前のフレームについての該ピクセル要素のターゲットピクセル値とは異なる場合がある。より詳細には、ピクセル要素の現在の（例えば、第 3 のピクセル調節期間の間の）ピクセル値は、そのピクセル要素の第 1 のピクセル調節期間からの（例えば、時刻  $t_0$  から  $t_2$  までの）ピクセル値に加えて、そのピクセル要素の第 2 のピクセル調節期間からのピクセル値にも依存し得る。しかしながら、メモリの制限のために、受信した表示データの 2 以上のフレームを記憶することは、表示デバイスにとって実用的（または、実現可能）ではない場合がある。

#### 【0069】

そのため、いくつかの実施形態では、表示デバイス 500 は、ピクセルアレー 510 に含まれる各ピクセル要素をそのターゲット電圧 503 に安定させることで、ピクセル電圧の計算の複雑さを低減する場合がある。例えば、ピクセルアレー 510 の初期スキャンの間に、表示デバイス 500 は、ピクセルアレー 510 に含まれる 1 以上のピクセル要素にオーバードライブ電圧 504 を印加する場合がある。そして、表示デバイス 500 は、初期スキャンから、それぞれのターゲット電圧 503 をオーバードライブされた任意のピクセル要素（例えば、オーバードライブ電圧が印加されたピクセル要素）に印加することで

10

20

30

40

50

、ピクセルアレー 510 の少なくとも一部を再スキャンする場合がある。各ピクセル調整期間の終了時において、各ピクセル要素がそのターゲットピクセル値に調節されるため、次のフレームについての現在のピクセル値 501 は、直前のフレームについてのそのピクセル要素のターゲットピクセル値 502 と等しくなる場合がある。これに応じて、画像バッファメモリ（例えば、図 3 の表示メモリ 330）は、表示データの現在のフレーム（例えば、そこからターゲットピクセル値 502 が取得される）、及び、表示データの直前のフレーム（例えば、そこから現在のピクセル値 501 が取得される）のみを記憶する場合がある。

#### 【0070】

いくつかの実施形態では、スキャン / 再スキャン回路部 540 は、ターゲット電圧 503 及びオーバードライブ電圧 504 に基づいて、スキャン電圧 505 と、再スキャン電圧 506 と、を生成する場合がある。例えば、各スキャン電圧 505 は、アレー 510 の初期スキャンの間に、ピクセルアレー 510 に含まれる各ピクセル要素に印加される場合がある。そのため、スキャン電圧 505 は、任意のピクセル要素についての、次の表示期間の開始時までにそのピクセル要素のターゲットピクセル値に安定させることができないオーバードライブ電圧 504 を含む場合がある。更に、再スキャン電圧 506 は、（例えば、初期スキャンから）オーバードライブされた各ピクセル要素をそのターゲット電圧 503 に駆動するために用いられる場合がある。これに応じて、再スキャン電圧 506 は、1 以上のピクセル要素についてのターゲット電圧 503 のみを含む場合がある。

#### 【0071】

本開示の態様は、多くの実例では、次の表示期間の前にピクセルの全ての行をスキャン及び再スキャンすることが実用的（又は実現可能）でない場合があることを認識している。そのため、表示デバイス 500 は、いくつかの実施形態では、初期スキャンの間、ピクセルアレー 510 に含まれる少なくともいくつかのピクセル要素にそれらのターゲット電圧 503 を印加し、一方で、ピクセル要素のより少ない一部のみにそれらのオーバードライブ電圧 504 を印加する場合がある。言い換えると、スキャン電圧 505 は、アレー 510 に含まれるピクセル要素のうち少なくともいくつかのためのターゲット電圧 503 と、アレー 510 に含まれる他のピクセル要素のためのオーバードライブ電圧 504 と、を含む場合がある。これに応じて、表示デバイス 500 は、オーバードライブされたピクセル要素を含むピクセルアレー 510 の行のうち一部のみを再スキャンする場合がある。いくつかの実施形態では、スキャン / 再スキャン回路部 540 は、再スキャンされるべき該一部の行を示す再スキャン制御信号（R\_CTR\_L）をタイミングコントローラ 520 に供給する場合がある。そのため、再スキャン動作の間、タイミングコントローラ 520 は再スキャン制御信号によって再スキャン電圧 506 を印加されるべきと示された該一部の行のみを逐次的に活性化する場合がある。

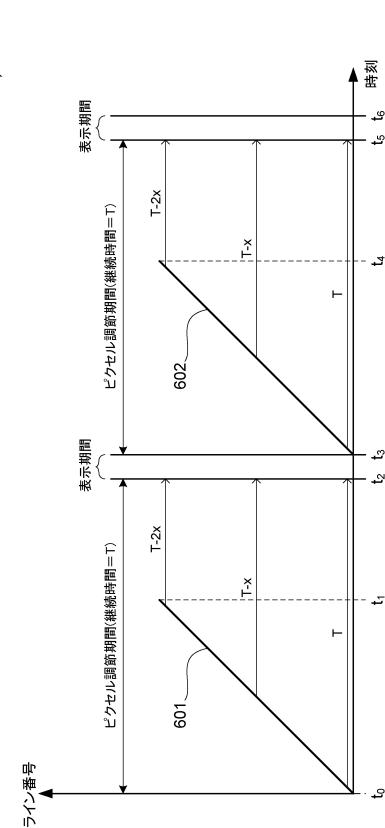

#### 【0072】

図 6 は、表示デバイス内のピクセル更新の例示的なタイミングを表すタイミング図 600 を示す。表示デバイスは、それぞれに、図 1、3、及び、5 の表示デバイス 120、300、又は 500 の例示的な実施形態である場合がある。例えば図 5 を参照して、画像は、連続するフレーム更新期間の間に、ピクセルアレー 510 によって周期的に表示される場合がある。各フレーム更新期間（例えば、時刻 t<sub>0</sub> から t<sub>3</sub>、及び、時刻 t<sub>3</sub> から t<sub>6</sub>）は、ピクセル調節期間（例えば、時刻 t<sub>0</sub> から t<sub>2</sub>、及び、時刻 t<sub>3</sub> から t<sub>5</sub>）と、これに続く表示期間（例えば、時刻 t<sub>2</sub> から t<sub>3</sub>、及び、時刻 t<sub>5</sub> から t<sub>6</sub>）を含む場合がある。各ピクセル調節期間の間に、ピクセルアレー 510 はピクセル更新（例えば、時刻 t<sub>0</sub> から t<sub>1</sub>、及び、時刻 t<sub>3</sub> から t<sub>4</sub>）で駆動される。更新されたピクセル要素は、その後、続く表示期間の間に、ユーザに対して“表示される”（例えば、可視化される）。例えば、ピクセルアレー 510 上の画像は、ピクセルアレー 510 を照らすように構成された（図 1 のバックライト 124 のような）光源を活性化することにより、ユーザに対して表示され得る。

#### 【0073】

10

20

30

40

50

各ピクセル調節期間の間に、ピクセルアレー 510 の個々の行は、（例えば、カスケード方式で）逐次的に更新される場合がある。曲線 601 及び 602 は、その行に関連付けられた行番号に基づく、ピクセルアレー 510 の各行についての例示的なピクセル更新時間を示す。そのため、図 6 に示すように、より高い（例えば、カスケードの更に下）ライン番号に関連づけられた行は、より低い（例えば、カスケードの開始に向けて）ライン番号に関連づけられた行よりも遅れて更新される。しかし、ピクセル要素が表示期間の間にのみ照らされるため、表示期間の前又は後に現れたピクセル値の如何なる変化も、ユーザによって視認され得ない。その結果、より高いライン番号に関連するピクセル要素（例えば、該カスケードのうちより遅く更新されるピクセル要素）は、より低いライン番号に関連するピクセル要素（例えば、該カスケードのうちより早く更新されるピクセル要素）よりも、自身の所望のピクセル値に遷移するための時間が短い。例えば、アレー 510 の最上段のピクセル要素は、それらのターゲットピクセル値へ到達するために、ピクセル調節期間の継続時間（T）を有し得る。これに対して、アレー 510 の中段のピクセル要素は、それらのターゲットピクセル値に到達するために有意に短い期間（T - x）を有する場合があり、アレー 210 の最下段のピクセル要素は、それらのターゲットピクセル値に到達するために更に短い期間（T - 2x）を有する場合がある。

#### 【0074】

本開示の態様は、ピクセルアレー 510 のうち個々の行について遷移時間が異なるために、ピクセル要素の異なる行に異なる量のオーバードライブが適用され得ることを認識している。例えば、相対的に低いライン番号に関連するピクセル要素は、次の表示期間までにそれらのターゲットピクセル値に到達するために、少しのオーバードライブしか要しないか、オーバードライブを要しない場合がある。しかし、より高いライン番号に関連するピクセル要素は、次の表示期間までにそれらのターゲットピクセル値に到達するために、しだいにより高いオーバードライブ電圧を要する場合がある。そのため、いくつかの実施形態では、オーバードライブ回路部 530 は、アレー 510 におけるそれらの位置（例えば、ライン番号）に少なくとも部分的に基づいて、ピクセル要素の行に適用されるオーバードライブの量を漸次増加させる場合がある。より詳細には、より高いライン番号に関連付けられた（例えば、表示更新期間のうちより遅く更新される）ピクセル要素は、一般に、より低いライン番号に関連付けられた（例えば、表示更新期間のうちより早く更新される）ピクセル要素よりも大きい量のオーバードライブ電圧を供給される。

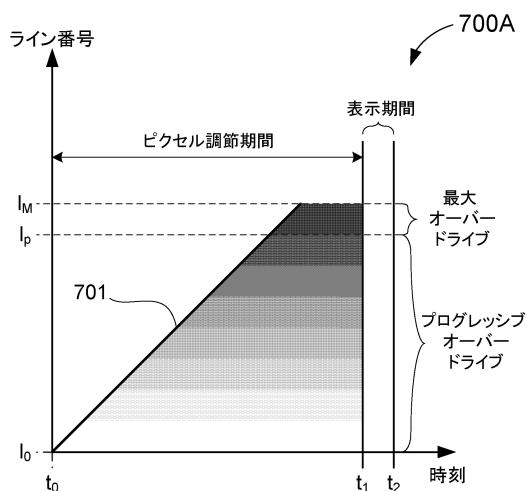

#### 【0075】

図 7A は、いくつかの実施形態に係る、プログレッシブオーバードライブの実装例を示すタイミング図 700A を示す。いくつかの実施形態では、図 7A に示されたプログレッシブオーバードライブの方法は、図 5 のオーバードライブ回路部 530 によって実行される場合がある。タイミング図 700A は、ピクセル調節期間（例えば、時刻  $t_0$  から  $t_1$ ）と、これに続く表示期間（例えば、時刻  $t_1$  から  $t_2$ ）と、を含み得る例示的なフレーム更新期間（例えば、時刻  $t_0$  から  $t_2$ ）を示す。曲線 701 は、ピクセルアレー 510 の各行に関連付けられたライン番号に基づく、その行の例示的なピクセル更新時間を表す。

#### 【0076】

図 7A の例では、オーバードライブ回路部 530 は、ピクセルアレー 510 のライン 1<sub>0</sub> から 1<sub>p</sub> の間のピクセル要素の連続する行について、プログレッシブオーバードライブ電圧を生成する場合がある。より詳細には、オーバードライブ電圧の量は、ライン 1<sub>0</sub> から 1<sub>p</sub> の間のピクセル要素の連続する行それについて、漸次増加する場合がある。例えば、ライン 1<sub>p</sub> に接続されたピクセル要素は、表示期間の開始までにピクセル値において同量の変化（例えば、グレースケールのレベルにおいて同量の変化）を達成するために、ライン 1<sub>0</sub> に接続されたピクセル要素よりも高い電圧を印加される場合がある。いくつかの態様では、ピクセル要素に印加可能なオーバードライブの量は、データドライバ 512 の電圧レンジによって制限され得る。図 7A の例では、ライン 1<sub>p</sub> に接続されたピクセル要素が更新される時刻までに、オーバードライブ電圧が飽和する場合がある。そのため、オーバードライブ回路部 530 は、ピクセルアレー 510 のライン 1<sub>p</sub> とライン 1<sub>M</sub> の

10

20

30

40

50

間のピクセル要素の行に対して最大のオーバードライブを適用する場合がある。言い換えると、ライン $l_p$ とライン $l_M$ の間の任意のピクセル要素がピクセル調節期間の間に更新されるときには、オーバードライブ回路部530は、そのようなピクセル要素のピクセル値を変更するために最大のオーバードライブを適用する場合がある。

#### 【0077】

本開示の態様は、プログレッシブオーバードライブの必要性はLCDディスプレイの特性（例えば、ピクセルの数、温度、応答時間、等）に強く依存し得ることを認識している。例えば、より少ないピクセル要素を有する（又は、少なくともピクセルのラインがより少ない）LCDディスプレイは、ピクセルアレー全体の更新のために必要となる時間が短い場合がある。そのため、より小さいピクセルアレーにおいては、ピクセル要素の一つの行から他の行へのオーバードライブの変化がよりゆるやかである場合がある。本開示の態様は、いくつかの実施形態では、次の表示期間までにオーバードライブを用いることなく（例えば、ターゲット電圧のみをピクセル要素に印加することで）、1以上のピクセル要素の行がそのターゲットピクセル値で安定することを更に認識している。

10

#### 【0078】

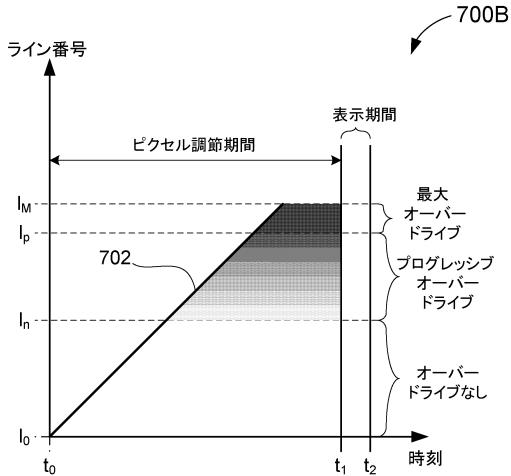

図7Bは、いくつかの実施形態に係る、プログレッシブオーバードライブの他の実装例を示すタイミング図700Bを示す。いくつかの実施形態では、図7Bに示されたプログレッシブオーバードライブの方法は、図5のオーバードライブ回路部530によって実行される場合がある。タイミング図700Bは、ピクセル調節期間（例えば、時刻 $t_0$ から $t_1$ ）と、これに続く表示期間（例えば、時刻 $t_1$ から $t_2$ ）と、を含み得る例示的なフレーム更新期間（例えば、時刻 $t_0$ から $t_2$ ）を示す。曲線702は、ピクセルアレー510の各行に関連付けられたライン番号（例えば、ゲートライン）に基づく、その行の例示的なピクセル更新時間を表す。

20

#### 【0079】

図7Bの例では、オーバードライブ回路部530は、ピクセルアレー510のライン $l_0$ から $l_n$ の間のピクセル要素の行に、如何なるオーバードライブも印加しない場合がある。その代わりに、ピクセル調節期間の間、ライン $l_0$ から $l_n$ の間の各ピクセル要素はそのターゲット電圧を印加される場合がある。オーバードライブ回路部530は、ピクセルアレー510のライン $l_n$ から $l_p$ の間のピクセル要素の連続する行について、漸増するオーバードライブ電圧を生成する場合がある。上記で説明したように、オーバードライブ電圧の量は、ライン $l_n$ から $l_p$ の間のピクセル要素の連続する行それぞれについて、漸次増加する場合がある。図7Bの例では、ライン $l_p$ に接続されたピクセル要素が更新される時刻までに、オーバードライブ電圧が飽和する場合がある。そのため、オーバードライブ回路部530は、ピクセルアレー510のライン $l_p$ とライン $l_M$ の間のピクセル要素の行に対して最大のオーバードライブを適用する場合がある。言い換えると、ライン $l_p$ とライン $l_M$ の間の任意のピクセル要素がピクセル調節期間の間に更新されるときには、オーバードライブ回路部530は、そのようなピクセル要素のピクセル値を変更するために最大のオーバードライブを適用する場合がある。

30

#### 【0080】

オーバードライブを（図7A及び7Bに示したような）漸進的な態様で適用することで、オーバードライブ回路部530は、アレー510のピクセル要素のそれぞれが、次の表示期間よりも前に、そのターゲットピクセル値（あるいは、少なくとも、ターゲットピクセル値に十分に近いピクセル値）に更新されることを保証する場合がある。その上、（例えば、図7Bで示したように）オーバードライブをピクセルアレーの一部のみに選択的に適用することで、本明細書の実施形態は、ピクセルアレー510のためにオーバードライブ電圧を生成するために要するリソース（例えば、メモリ、時間、電力、及び他の処理リソース）の量を低減し得る。

40

#### 【0081】

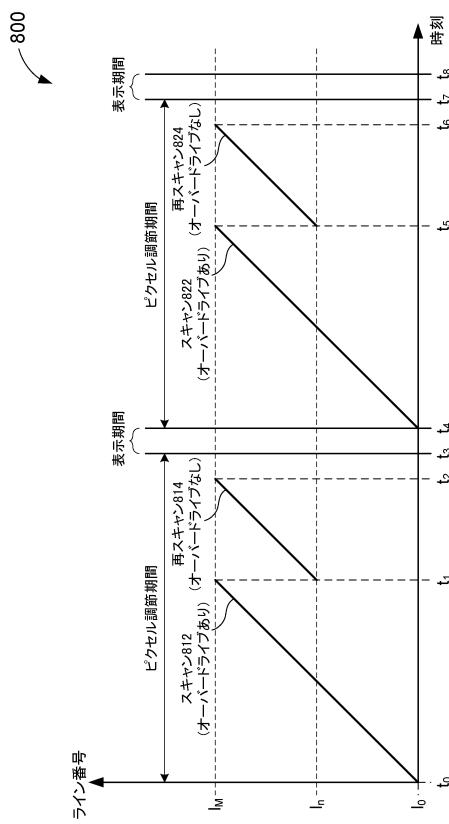

図8は、いくつかの実施形態に係る、例示的なオーバードライブ補正動作を表すタイミング図800を示す。いくつかの実施形態では、図8で示されたオーバードライブ補正動

50

作は、それぞれに、図1、3、及び、5の表示デバイス120、300、又は500の何れかによって実行される場合がある。例えば図5を参照して、画像は、連続するフレーム更新期間の間に、ピクセルアレー510によって周期的に表示される場合がある。各フレーム更新期間（例えば、時刻 $t_0$ から $t_4$ 、及び、時刻 $t_4$ から $t_8$ ）は、ピクセル調節期間（例えば、時刻 $t_0$ から $t_3$ 、及び、時刻 $t_4$ から $t_7$ ）と、これに続く表示期間（例えば、時刻 $t_3$ から $t_4$ 、及び、時刻 $t_7$ から $t_8$ ）を含む場合がある。

#### 【0082】

各ピクセル調節期間の間に、ピクセルアレー510の個々の行は、（例えば、カスクード方式で）逐次的に更新される場合がある。曲線812、814、822、及び、824は、各行に関連付けられた行番号に基づく、ピクセルアレー510の対応する各行についての例示的なピクセル更新時間を示す。より詳細には、第1のピクセル調節期間（例えば、時刻 $t_0$ から $t_3$ ）において、曲線812はピクセルアレー510の初期スキャン（例えば、時刻 $t_0$ から $t_1$ ）に対応し、曲線814はピクセルアレー510の再スキャン（例えば、時刻 $t_1$ から $t_2$ ）に対応する。同様に、第2のピクセル調節期間（例えば、時刻 $t_4$ から $t_7$ ）において、曲線822はピクセルアレー510の初期スキャン（例えば、時刻 $t_4$ から $t_5$ ）に対応し、曲線824はピクセルアレー510の再スキャン（例えば、時刻 $t_5$ から $t_6$ ）に対応する。いくつかの実施形態では、表示デバイス500は、初期スキャンと再スキャンの間に生じ得る任意の不所望なエッジを隠すために、ディザリングの技術を用いる場合がある。

10

#### 【0083】

図8の例では、オーバードライブ回路部530は、ピクセルアレー510のライン $1_0$ から $1_n$ の間のピクセル要素の行に、如何なるオーバードライブも印加しない場合がある。そのため、ライン $1_0$ から $1_n$ の間の各行は、初期スキャン812及び822の間、そのターゲット電圧を印加される場合がある。オーバードライブ回路部530は、ピクセルアレー510のライン $1_n$ から $1_M$ の間のピクセル要素の各行について、オーバードライブ電圧を生成する場合がある。いくつかの実施形態では、オーバードライブ電圧の量は、ライン $1_n$ から $1_M$ の間のピクセル要素の連続する行それぞれについて、漸次増加する場合がある。そのため、ライン $1_n$ から $1_M$ の間の各ピクセル要素は、初期スキャン812及び822の間、それぞれのオーバードライブ電圧に駆動される場合がある。オーバードライブ電圧がピクセルアレー510の行の一部（ライン $1_0$ から $1_n$ ）のみに印加されたため、再スキャン814及び824のそれぞれは、ピクセルアレー510の行の対応する一部に限定される。より詳細には、ライン $1_n$ から $1_M$ の間の各ピクセル要素は、再スキャン814及び824の間、そのターゲット電圧に駆動される。

20

#### 【0084】

なお、再スキャン814の後、ピクセルアレー510の各ピクセル要素（ライン $1_0$ から $1_M$ ）は、そのターゲットピクセル値で安定する場合がある。そのため、オーバードライブ回路部530は、第1のピクセル調節期間から、第2のピクセル調節期間の間に印加されるべきオーバードライブ電圧を計算するために、（例えば現在のピクセル値として）ターゲットピクセル値を用いる場合がある。これに応じて、本実施形態は、（例えば、初期スキャン812及び822の間に少なくもいくつかのピクセル要素にオーバードライブ電圧を印加することにより）ピクセルの遷移時間がより早くなるという利益を提供するとともに、後続のフレーム更新において印加されるべきピクセル電圧を求めるためのストレージの要求量及び計算の複雑さを低減する（例えば、再スキャン814及び824の間にオーバードライブされたピクセル要素にターゲット電圧を印加することによる）。

30

#### 【0085】

中心視の描写

#### 【0086】

上述したように、ヘッドマウントディスプレイ（HMD）デバイスは、ユーザの頭に着用、又は、さもなくば取り付けるように構成されている。HMDデバイスは、ユーザの目の方又は両方の前方に配置される1以上のディスプレイを備える。HMDデバイスは、

40

50

ユーザの周辺環境（例えば、カメラでキャプチャされた）からの情報及び／又は画像を重ねられた、画像ソースからの画像（例えば、静止画像、連続した画像、及び／又は、動画）を表示し、例えば、ユーザを仮想世界に没頭させ得る。

#### 【0087】

いくつかの態様では、（HMDデバイスのような）表示デバイスは、ユーザの目の位置に基づいて動的に更新された画像をユーザに表示する場合がある。より詳細には、表示デバイスは、ユーザの目の動きを追跡する場合があり、画像のうちユーザが凝視する点と一致する部分（例えば、中心視領域）を、画像の他の領域（例えば、全視野画像）よりも高い解像度で表示する場合がある。そのため、いくつかの実施形態では、表示デバイスは高解像度の中心視画像を、全視野（FOV）画像のうち中心視領域に重ねられた画像として表示または描写する場合がある。10

#### 【0088】

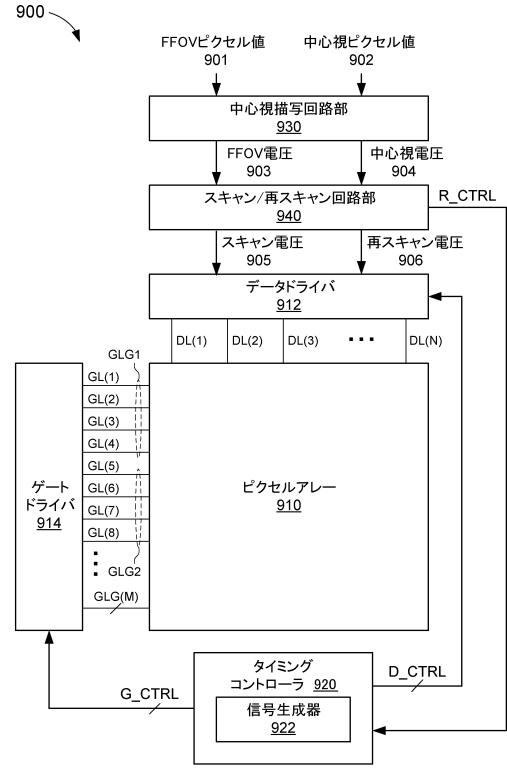

図9は、いくつかの実施形態に係る、中心視描写回路部を有する表示デバイス900のブロック図を示す。表示デバイス900は、図1の表示デバイス120、又は、図3の表示デバイス300の例示的な実施形態である場合がある。表示デバイス900は、ピクセルアレー910、タイミングコントローラ920、及び、中心視描写回路部930、スキヤン／再スキヤン回路部940を備える場合がある。いくつかの実施形態では、表示デバイス900はLCD表示パネルに対応する場合がある。ピクセルアレー910は複数のピクセル要素（シンプルにするために図示せず）を備えている場合がある。ピクセル要素の各行はそれぞれのゲートライン（GL）に接続され、ピクセル要素の各列はそれぞれのデータライン（DL）に接続されている。20

#### 【0089】

データドライバ912は、データラインDL(1)～DL(N)を介してピクセルアレー510に接続されている。いくつかの態様では、データドライバ912は、データラインDL(1)～DL(N)を介して、個別のピクセル要素に（例えば、対応する電圧の形で）ピクセルデータを印加して、ピクセルアレー910に表示されるフレーム又は画像を更新するように構成されている場合がある。なお、ピクセルアレー910のピクセル要素の各行は、それぞれ同じデータラインDL(1)～DL(N)に接続される。そのため、表示デバイス900は、ピクセル要素の行を逐次的に（例えば、一度に一行）スキヤンすることで、ピクセルアレー910を更新する場合がある。30

#### 【0090】

ゲートドライバ914は、ゲートラインGL(1)～GL(M)を介してピクセルアレー910に接続される。いくつかの態様では、ゲートドライバ914は、任意の所与の時刻において、データドライバ912によって駆動されるピクセルデータをピクセル要素の何れの行が受信するかを選択するように構成される場合がある。例えば、ゲートドライバ914は、ゲートラインGL(1)～GL(M)のそれぞれを、ピクセルアレー910の各行が更新されるまで、逐次に選択する、あるいは活性化するように構成される場合がある。

#### 【0091】

タイミングコントローラ920は、データドライバ912とゲートドライバ914のタイミングを制御するように構成される。例えば、タイミングコントローラ920は、タイミング制御信号の第1セット(D\_CTRL)を生成して、データドライバ912によるデータラインDL(1)～DL(N)の活性化を制御する場合がある。タイミングコントローラ920は、タイミング制御信号の第2セット(G\_CTRL)を更に生成して、ゲートドライバ914によるゲートラインGL(1)～GL(M)の活性化を制御する場合がある。タイミングコントローラ920は、信号生成器922によって生成される基準クロック信号に基づいて、D\_CTRL及びG\_CTRL信号を生成する場合がある。40

#### 【0092】

中心視描写回路部930は、受信した表示データのフレームからのFOVピクセル値901及び中心視ピクセル値902に少なくとも部分的に基づいて、ピクセルアレー910

10

20

30

40

50

0 の各ピクセル要素に印加されるべきピクセル電圧を決定する場合がある。例えば、FFOV ピクセル値 901 及び中心視ピクセル値 902 は、(図 3 の表示メモリ 330 のような) フレームバッファメモリから取得される場合がある。いくつかの態様では、FFOV ピクセル値 901 は FFOV 画像に対応する場合があり、中心視ピクセル値 902 は、FFOV 画像と合成されて表示されるべき中心視画像に対応する場合がある。例えば、FFOV 画像は相対的に低解像度で描写され、中心視画像は相対的に高解像度で描写されて FFOV 画像内に位置する場合がある。

#### 【0093】

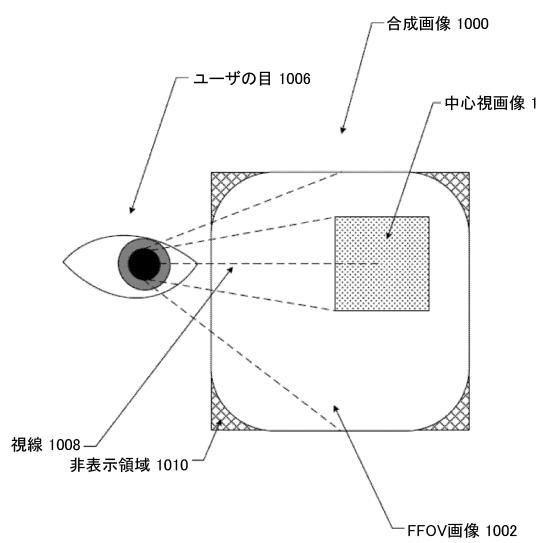

例えば、図 10 は、ピクセルアレー 910 上に表示され得る合成画像 1000 を示す。

合成画像 1000 は、FFOV 画像 1002 に統合された中心視画像 1004 を含むように示されている。FFOV 画像 1002 は、ユーザの視線 1008 の周辺に広がる。そのため、FFOV 画像 1002 は、ピクセルアレー 910 のピクセル要素のうち(全てで無い場合は) 大半にわたって表示されるべきフルフレーム画像に対応し得る。例えば、仮想現実環境においては、FFOV 画像 1002 が、任意の所与の瞬間にユーザの目によって視認される、観測可能な仮想又は現実の世界の範囲を示し得る。一方、中心視画像 1004 は、ユーザの視線 1008 の中心視領域にのみ広がる。中心視領域は合成画像 1000 のうち、ユーザの目 1006 のうち中心窓の部分(例えば、任意の所与の瞬間にユーザが最大の視力をを持つと判断される領域)によって視認可能な部分に対応し得る。

10

#### 【0094】

図 10 に示すように、中心視画像 1004 は、合成画像 1000 のうち、FFOV 画像 1002 と比べて相対的に小さい領域を内包する場合がある。より詳細には、合成画像 1000 を生成する時、中心視画像 1004 は FFOV 画像 1002 の(例えば、ユーザの視線 1008 のうち中心視領域に一致する)一部に重ねられる場合がある。中心視画像 1004 がユーザの視力が最大となる領域に広がるため、中心視画像 1004 は FFOV 1002 よりも高い解像度で描写される場合がある。例えば、中心視画像 1004 の各ピクセルはピクセルアレー 910 のそれぞれのピクセル要素上に描写され得る。これに対して、FFOV 画像 1002 の各ピクセルはピクセルアレー 910 の複数のピクセル要素にわたって描写され得る。このため、中心視画像 1004 は、合成画像 1000 において FFOV 画像 1002 よりも鮮明に表示され得る。

20

#### 【0095】

図 9 に戻って、中心視描写回路部 930 は、FFOV ピクセル値 901 及び中心視ピクセル値 902 にそれぞれ基づいて、ピクセルアレー 910 に印加されるべき FFOV 電圧 903 及び中心視電圧 904 を決定する場合がある。より詳細には、FFOV 電圧 903 及び中心視電圧 904 は、FFOV ピクセル値 901 及び中心視ピクセル値 902 に関連付けられたターゲット電圧に対応し得る。例えば、FFOV ピクセル値 901 は、ピクセルアレー 910 のピクセル要素のうち(すべてで無い場合は) ほとんどにわたって表示されるべきフルフレーム画像(例えば、FFOV 画像 1002)に対応し得る。FFOV 画像はユーザの視線の周辺に広がり得るため、FFOV ピクセル値 901 は相対的に低い解像度を有する場合がある。これに対して、中心視ピクセル値 902 はユーザの視線の中心視画像のみに広がる中心視画像(例えば、中心視画像 1004)に対応し得る。中心視領域はユーザが最大の視力を有すると判断される領域に対応するため、中心視ピクセル値 902 は相対的に高い解像度を有する場合がある。

30

40

#### 【0096】

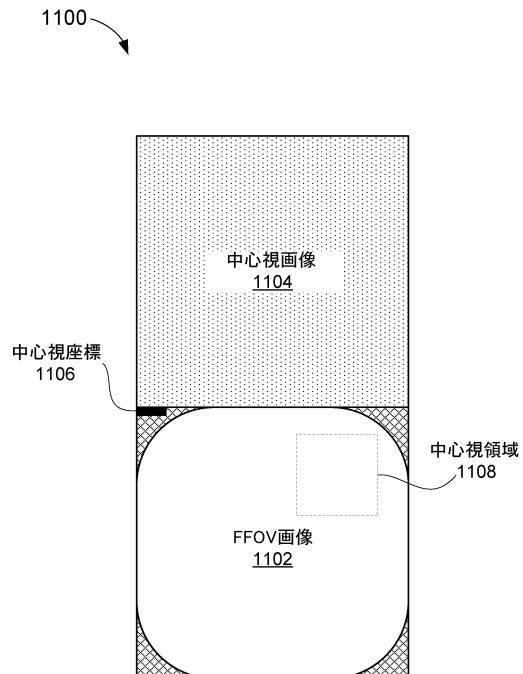

本開示の態様は、合成画像 1000 の各ピクセルについてのそれぞれのピクセル値を受信及び記憶するために必要な帯域幅及びメモリの量が非常に多く成り得ることをも認識している。そのため、いくつかの実施形態では、表示デバイス 900 は FFOV 画像 1002 と中心視画像 1004 とを同じフレームバッファ画像内で別々に受信する場合がある。例えば、図 11 は表示デバイス 900 によって受信され得る例示的なフレームバッファ画像 1100 を示す。フレームバッファ画像 1100 は、FFOV 画像 1102 と、中心視画像 1104 とを含む。例えば、FFOV 画像 1102 及び中心視画像 1104 は、それ

50

それ、図10のFFOV画像1102及び中心視画像1104と対応し得る。

#### 【0097】

図11の例では、FFOV画像1102はフレームバッファ画像1100の第1部分において符号化される場合があり、中心視画像1104はフレームバッファ画像1100の第2部分において符号化される場合がある。これに応じて、FFOV画像1102及び中心視画像1104は、表示デバイス900によって連続して受信され得る。いくつかの実施形態では、FFOV画像1102は、(例えば、図10で示したように)それが表示されるべき解像度にアップスケールされていない。むしろ、FFOV画像1102及び中心視画像1104は共に、それらの“ネイティブ”な解像度で送信される。このことにより、フレームバッファ画像1100を伝達及び記憶するために必要な帯域幅を実質的に低減し得る。

10

#### 【0098】

いくつかの実施形態では、FFOV画像1102の中心視領域1108を指定する中心視座標1106が、フレームバッファ画像1100内で符号化されている場合がある。例えば、表示デバイス900は、中心視座標1106に基づいて、ピクセルアレー910に合成画像を描写するときにFFOV画像1102に対して中心視画像1104を重ねる場所を決定する場合がある。中心視座標1106は、FFOV画像1102の中心視領域1108に対応する少なくとも1つのピクセルの位置を指定する場合がある。例えば、いくつかの態様では、中心視座標1106は、中心視領域の特定の角、又は中心のピクセルを指定し得る。他のいくつかの態様では、中心視座標1106は中心視領域の境界を定義するピクセルのセットを指定する場合がある。

20

#### 【0099】

いくつかの実施形態では、中心視座標1106は、フレームバッファ画像1100のうち、FFOV画像1102の非表示領域1010と一致する部位に符号化され得る。図11の例では、中心視座標1106は、フレームバッファ画像1100の左上の隅において符号化される。いくつかの実施形態では、中心視座標1106はピクセルデータとして符号化される場合がある。例えば、中心視座標1106はフレームバッファ画像1100の最初の32ピクセルを用いて符号化される場合がある。いくつかの実装では、中心視座標1106は、ピクセル毎2ビットのスペース符号化技術を用いて符号化される場合がある。例えば、「00」のビットは黒のピクセルとして符号化される場合があり、「01」のビットは赤のピクセルとして符号化される場合があり、「10」のビットは緑のピクセルとして符号化される場合があり、そして、「11」のビットは白のピクセルとして符号化される場合がある。

30

#### 【0100】

いくつかの実施形態では、FFOV画像1102の各ピクセルは、それぞれのFFOVピクセル値901に対応する場合があり、また、中心視画像1104の各ピクセルは、それぞれの中心視ピクセル値902に対応する場合がある。FFOV画像1102はアップスケールされた解像度で表示されるべきであるため、中心視描写回路部930は、各FFOVピクセル値901を、(例えば、ピクセルアレー910のそれぞれのピクセル要素に印加されるべき)複数のFFOV電圧903と関連付ける場合がある。一方で、中心視画像はそのネイティブな解像度(又は、少なくともネイティブに近い解像度)で表示される得るため、中心視描写回路部930は各中心視電圧904を、(例えば、ピクセルアレー910の一部に含まれる、それぞれのピクセル要素に印加されるべき)それぞれの中心視電圧904と関連づけする場合がある。

40

#### 【0101】

本開示の態様は、FFOV画像1102の解像度が相対的に低いため、FFOV電圧903をピクセルアレー910に印加するときに、(例えば、複数のピクセル要素が同じFFOV電圧903を印加され得るため)行毎にスキャンすることが非効率であり得ることを更に認識している。そのため、いくつかの実施形態では、表示デバイス900は、異なる時刻において異なる速度で、ピクセルアレー910上にFFOV画像1102及び中心

50

視画像 1104 を描写し得る。例えば図 12A を参照して、表示デバイス 900 は、初期スキャン処理 1200A の間に、FFOV 画像 1210 をピクセルアレー 910 上に描写する場合がある。より詳細には、表示デバイス 900 は、ピクセルアレー 910 の各行を（例えば、ライン  $l_0$  から  $l_M$  まで）スキャンすることで、FFOV 画像 1210 を描写する場合がある。例えば図 12B を参照して、表示デバイス 900 は、続く再スキャン動作 1200B の間に、FFOV 画像 1210 に重ねられる画像として、中心視画像 1220 をピクセルアレー 910 上に描写する場合がある。より詳細には、表示デバイス 900 は、ピクセルアレー 910 のうち FFOV 画像 1210 の中心視領域に対応する一部の行のみを（例えば、ライン  $l_{f_1}$  から  $l_{f_2}$  まで）再スキャンすることで、中心視画像 220 を描写する場合がある。

10

#### 【0102】

いくつかの実施形態では、表示デバイス 900 は、フレームバッファ画像において各画像を受信する順で、FFOV 画像 1210 及び中心視画像 1220 をピクセルアレー 910 上に描写する場合がある。図 11 に関して上記で説明したように、表示デバイス 900 は、FFOV 画像 1210 及び中心視画像 1220 を順次にフレームバッファ画像において受信する場合がある。そのため、表示デバイス 900 は、FFOV 画像 1210 を受信した時に初期スキャン動作 1200A を実行する場合があり、中心視画像 1220 を受信した時に再スキャン動作 1200B を実行する場合がある。なお、FFOV 画像 1210 は、再スキャン動作 1200B が実行される時刻までに、既にピクセルアレー 910 上に描写されているであろう。そのため、FFOV ピクセル値の少なくともいくつかは、初期スキャン処理 1200A が終了するとすぐに廃棄される場合がある。このことは、表示デバイス 900 のメモリの要件を更に低減し得る。

20

#### 【0103】

いくつかの実施形態では、スキャン / 再スキャン回路部 940 は、スキャン電圧 905 及び再スキャン電圧 906 を、FFOV 電圧 903 及び中心視電圧 904 に基づいて生成する場合がある。例えば、スキャン電圧 905 は、ピクセルアレー 910 の初期スキャンの間に、ピクセルアレー 910 の各ピクセルに印加される場合がある。そのため、スキャン電圧 905 はそれぞれの FFOV 電圧 903 に対応する場合がある。更に、再スキャン電圧 906 は、それぞれの中心視電圧 904 を、ピクセルアレー 910 上に表示される FFOV 画像の中心視領域内の各ピクセル要素に印加するために用いられる場合がある。これに応じて、再スキャン電圧 905 は、再スキャンされるピクセル要素の少なくともいくつかについての中心視電圧 904 を含む場合がある。再スキャン動作の間、スキャン / 再スキャン回路部 940 は、ピクセルアレー 910 のうち再スキャンされる行に含まれる FFOV 画像の中心視領域の外側にある任意の（図 12B の列  $c_0$  から  $c_{f_1}$  まで、及び、 $c_{f_2}$  から  $c_N$  までに含まれるピクセル要素のような）ピクセル要素に、FFOV 電圧 903 を再印加する場合がある。そのため、いくつかの実施形態では、再スキャン電圧 906 は、再スキャンされるピクセル要素のうち少なくともいくつかについての FFOV 電圧 903 をまた含む場合がある。

30

#### 【0104】

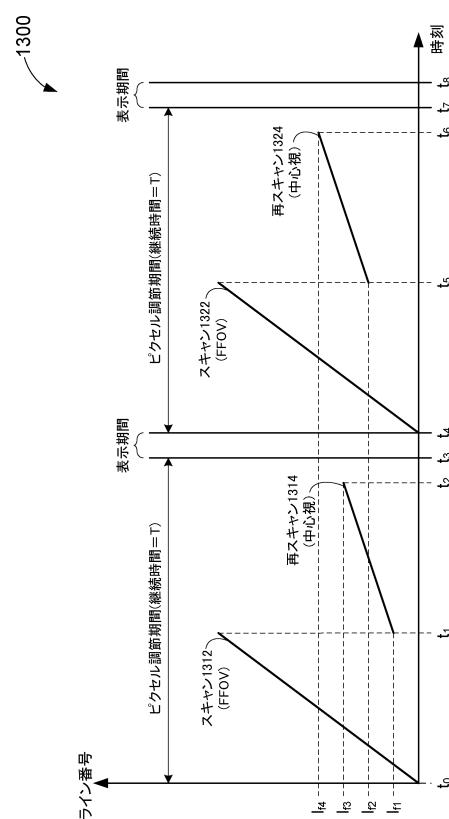

図 13 は、いくつかの実施形態に係る、例示的な中心視描写動作を表すタイミング図 1300 を示す。いくつかの実施形態では、図 8 で示された中心視描写動作は、それぞれに、図 1、3、及び、9 の表示デバイス 120、300、又は 900 によって実行される場合がある。例えば図 9 を参照して、画像は、連続するフレーム更新期間の間に、ピクセルアレー 910 によって周期的に表示される場合がある。各フレーム更新期間（例えば、時刻  $t_0$  から  $t_4$ 、及び、時刻  $t_4$  から  $t_8$ ）は、ピクセル調節期間（例えば、時刻  $t_0$  から  $t_3$ 、及び、時刻  $t_4$  から  $t_7$ ）と、これに続く表示期間（例えば、時刻  $t_3$  から  $t_4$ 、及び、時刻  $t_7$  から  $t_8$ ）を含む場合がある。

40

#### 【0105】

各ピクセル調節期間の間に、ピクセルアレー 910 の個々の行は、（例えば、カスクード方式で）逐次的に更新される場合がある。曲線 1312、1314、1322、及び、

50

1324は、各行に関連付けられた行番号に基づく、ピクセルアレー910の対応する各行についての例示的なピクセル更新時間を示す。より詳細には、第1のピクセル調節期間（例えば、時刻 $t_0$ から $t_3$ ）の間ににおいて、曲線1312はピクセルアレー910の初期スキャン（例えば、時刻 $t_0$ から $t_1$ ）に対応し、曲線1314はピクセルアレー910の再スキャン（例えば、時刻 $t_1$ から $t_2$ ）に対応する。同様に、第2のピクセル調節期間（例えば、時刻 $t_4$ から $t_7$ ）の間ににおいて、曲線1322はピクセルアレーの初期スキャン（例えば、時刻 $t_4$ から $t_5$ ）に対応し、曲線1324はピクセルアレー910の再スキャン（例えば、時刻 $t_5$ から $t_6$ ）に対応する。いくつかの実施形態では、表示デバイス900は、初期スキャンと再スキャンの間に生じ得る任意の不所望なエッジを隠すために、ディザリングの技術を用いる場合がある。

10

#### 【0106】

第1FFOV画像が、第1ピクセル調節期間の間に、ピクセルアレー910上に描写され得る。例えば、スキャン／再スキャン回路部940は、初期スキャン1312の間に、ピクセルアレー910の各行に含まれるそれぞれのピクセル要素に（例えばスキャン電圧905として）FFOV電圧903を印加する場合がある。中心視画像は、その後、第1FFOV画像の中心視領域内に描写され得る。図13の例では、第1FFOV画像の中心視領域は、ピクセルアレー910のライン $l_{f1}$ と $l_{f3}$ の間に位置し得る。そのため、再スキャン1314の間に、スキャン／再スキャン回路部940は、ライン $l_{f1}$ と $l_{f3}$ の間のFFOV画像の中心視領域内に位置する（例えば、図12Bの列 $c_{f1}$ と $c_{f2}$ の間の）それぞれのピクセル要素に（例えば再スキャン電圧906として）中心視電圧904を印加する場合がある。スキャン／再スキャン回路部940は、更に、ライン $l_{f1}$ と $l_{f3}$ の間のFFOV画像の中心視領域の外側に位置する（例えば、図12Bの列 $c_0$ から $c_{f1}$ まで、及び、列 $c_{f2}$ から $c_N$ までの）それぞれのピクセル要素に（例えば再スキャン電圧906として）FFOV電圧903を再印加する場合がある。

20

#### 【0107】

第2FFOV画像が、第2ピクセル調節期間の間に、ピクセルアレー910上に描写され得る。例えば、スキャン／再スキャン回路部940は、初期スキャン1322の間に、ピクセルアレー910の各行に含まれるそれぞれのピクセル要素に（例えばスキャン電圧905として）FFOV電圧903を印加する場合がある。中心視画像は、その後、第2FFOV画像の中心視領域内に描写され得る。図13の例では、第2FFOV画像の中心視領域は、ピクセルアレー910のライン $l_{f2}$ と $l_{f4}$ の間に位置し得る。そのため、再スキャン1324の間に、スキャン／再スキャン回路部940は、ライン $l_{f2}$ と $l_{f4}$ の間のFFOV画像の中心視領域内に位置するそれぞれのピクセル要素に（例えば再スキャン電圧906として）中心視電圧904を印加する場合がある。スキャン／再スキャン回路部940は、更に、ライン $l_{f2}$ と $l_{f4}$ の間のFFOV画像の中心視領域の外側に位置するそれぞれのピクセル要素に（例えば再スキャン電圧906として）FFOV電圧903を再印加する場合がある。

30

#### 【0108】

図13に示すように、初期スキャン1312及び1322は、再スキャン1314及び1324よりも十分に高速度で実行される。そのような“速い”スキャンを容易にするために、ゲートドライバ914は、ピクセルアレー910の複数のラインを同時に活性化するように構成されている場合がある。例えば、いくつかの実施形態では、（例えば、G\_C\_T\_R\_L信号のセットに含まれている）ゲートクロック信号の各遷移は、ゲートドライバ914に、活性化されるゲートラインGL(1) - GL(M)を複数選択させる場合がある。いくつかの態様では、複数の隣接するゲートラインが、特定のゲートライングループに割当てられる場合がある。例えば、ゲートラインGL(1) - GL(4)は、第1ゲートライングループ(GLG1)に割当てられる場合があり、ゲートラインGL(5) - GL(8)は、第2ゲートライングループ(GLG2)に割当てられる場合がある。いくつかの態様では、ゲートドライバ914は、ゲートライングループGLG1が選択されているときに、ゲートラインGL(1) - GL(4)を逐次的に駆動する。いくつかの他の態様

40

50

では、ゲートドライバ914は、ゲートライングループG L G 1が選択されているときに、ゲートラインG L ( 1 ) - G L ( 4 )のうち2以上を同時に駆動する。

#### 【 0 1 0 9 】

いくつかの実施形態では、ゲートドライバ914は、ゲートラインG L ( 1 ) - G L ( M )を階層的な手法で駆動するように構成されている場合がある。例えば、ゲートクロック信号の各遷移に応答して特定のゲートラインを直接駆動するのではなく、代わりに、ゲートドライバ914は、ゲートクロック信号の各遷移に応答して、活性化されるゲートラインのグループを選択する場合がある。その後、ゲートドライバ914は選択されたグループに含まれる個々のゲートラインを選択的に活性化する場合がある。ゲートラインG L ( 1 ) - G L ( M )が駆動される階層的な手法により、ゲートドライバ914にとって( 10 例えば、相対的に低解像度なFFOV画像を描写しているときに)ピクセルアレー910を速くスキャンし、( 例えば、相対的に高解像度な中心視画像を描写しているときに)ピクセルアレー910をよりゆっくりとスキャンすることが容易になる。更にまた、ゲートラインG L ( 1 ) - G L ( M )が駆動される階層的な手法により、( 例えば、同数のゲートラインを駆動するために必要なシフトレジスタステージの数がより少ないため )ゲートドライバ914が既存のゲートドライバ回路部よりも小さいフットプリントを有することを可能にする。

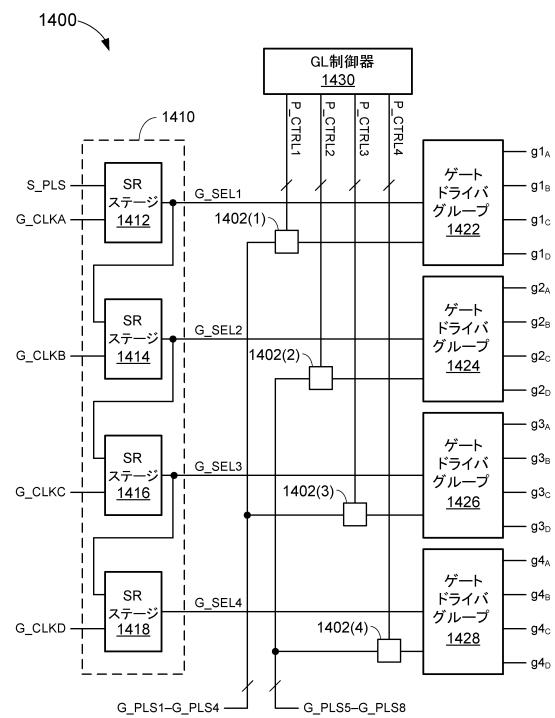

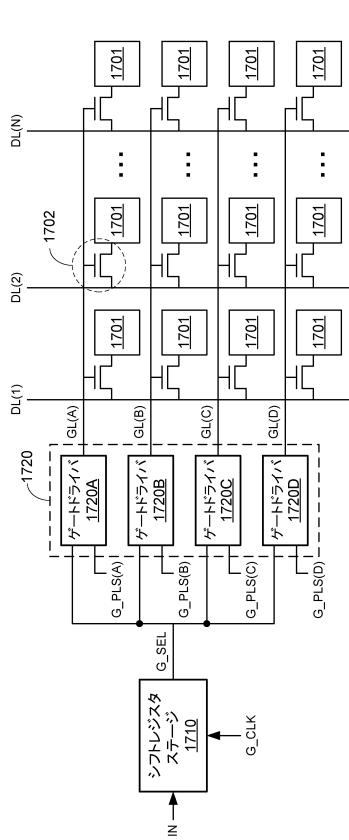

#### 【 0 1 1 0 】

図14は、いくつかの実施形態に係る、階層的なゲートドライバ回路1400のブロック図である。例えば、階層的なゲートドライバ回路1400は図9で示したゲートドライバ914の実施形態である場合がある。階層的なゲートドライバ回路1400は、シフトレジスタ1410と、複数のゲートドライバグループ1422 - 1428とを備える。シンプルにするために、図14の例では4つのゲートドライバグループ1422 - 1428のみが表されている。しかし、実際の実装では、階層的なゲートドライバ回路1400は図14で示されたものよりも少ない、あるいはより多いゲートドライバグループを有しても良い。

#### 【 0 1 1 1 】

シフトレジスタ1410は、複数のステージ1412 - 1418を備える場合がある。例えば、シフトレジスタ(SR)ステージ1412 - 1418は、シリアルイン/パラレルアウト(serial-in/parallel-out)(SIPPO)の構成で配列されたフリップフロップのカスケードとして実装される場合がある。いくつかの実施形態では、シフトレジスタ1410内のSRステージの数は、階層的なゲートドライバ回路1400内のゲートドライバグループの数と対応している場合がある。そのため、図14の例では4つのSRステージ1412 - 1418のみが表されているが、実際の実装では、シフトレジスタ1410は図14で示されたものよりも少ない、あるいはより多いステージを有しても良い。シフトレジスタ1410は、スタートパルス(S\_PLS)及び複数のゲートクロック信号(G\_CLK\_A - G\_CLK\_D)を受け取るように接続されている。上記で説明したように、スタートパルスS\_PLSは、複数のゲートライン(g1A - g4D)と接続された(図9のピクセルアレー910のような)ピクセルアレーのスキャンのトリガーとして用いられる場合がある。ゲートクロック信号G\_CLK\_A - G\_CLK\_Dは、異なる時刻でのゲートラインg1A - g4Dの活性化を制御するために用いられる場合がある。そのため、ゲートクロック信号G\_CLK\_A - G\_CLK\_Dのそれぞれは、互いに対し異なる位相オフセットを有する場合がある。

#### 【 0 1 1 2 】

カスケード内の第1SRステージ1412は、S\_PLSを入力として受信するように構成され、さらに、S\_PLSと第1ゲートクロック信号(G\_CLK\_A)に基づいて第1グループ選択ライン(G\_SEL1)を駆動するように構成されている。第2SRステージ1414の入力は、第1SRステージ1412の出力と接続されている。そのため、第2SRステージ1414は、G\_SEL1と第2ゲートクロック信号(G\_CLK\_B)に基づいて第2グループ選択ライン(G\_SEL2)を駆動するように構成されている。

10

20

30

40

50

第3 S Rステージ1416の入力は、第2 S Rステージ1414の出力と接続されている。そのため、第3 S Rステージ1416は、G\_SEL2と第3ゲートクロック信号(G\_CLK\_C)に基づいて第3グループ選択ライン(G\_SEL3)を駆動するように構成されている。第4 S Rステージ1419の入力は、第3 S Rステージ1416の出力と接続されている。そのため、第4 S Rステージ1418は、G\_SEL3と第4ゲートクロック信号(G\_CLK\_D)に基づいて第4グループ選択ライン(G\_SEL4)を駆動するように構成されている。いくつかの実施形態では、第4 S Rステージ1418の出力は、カスケード内の第5 S Rステージ(シンプルにするために図示せず)の入力と接続されている場合がある。

#### 【0113】

ゲートドライバグループ1422-1428は、グループ選択ラインG\_SEL1-G\_SEL4をそれぞれに介して、S Rステージ1412-1418の出力と接続されている。ゲートドライバグループ1422-1428のそれぞれは、対応するグループセレクトラインが駆動されているときに、ゲートラインのグループ(g1-g4)を選択的に駆動するように構成されている。より詳細には、グループ選択ラインG\_SEL1-G\_SEL4は、それぞれのゲートドライバグループ1422-1428が対応するゲートラインのグループを駆動することを可能にする。例えば、第1グループ選択ラインG\_SEL1の活性化は、第1ゲートドライバグループ1422がゲートラインの第1グループg1\_A-g1\_Dを駆動することを可能にする。第2グループ選択ラインG\_SEL2の活性化は、第2ゲートドライバグループ1424がゲートラインの第2グループg2\_A-g2\_Dを駆動することを可能にする。第3グループ選択ラインG\_SEL3の活性化は、第3ゲートドライバグループ1426がゲートラインの第3グループg3\_A-g3\_Dを駆動することを可能にする。第4グループ選択ラインG\_SEL4の活性化は、第4ゲートドライバグループ1428がゲートラインの第4グループg4\_A-g4\_Dを駆動することを可能にする。

10

#### 【0114】

いくつかの実施形態では、ゲートドライバグループ1422-1428は、一連のゲートパルスG\_PLS1-G\_PLS8に少なくとも部分的に基づいて、ゲートラインg1\_A-g4\_Dを駆動する場合がある。より詳細には、ゲートパルスG\_PLS1-G\_PLS8は、ゲートドライバグループ1422-1428がゲートラインg1\_A-g4\_Dを駆動するタイミングを制御する場合がある。例えば、ゲートパルスG\_PLS1-G\_PLS4は、第1ゲートドライバグループ1422及び第3ゲートドライバグループ1426に提供される場合がある一方で、ゲートパルスG\_PLS5-G\_PLS8は、第2ゲートドライバグループ1424及び第4ゲートドライバグループ1428に提供される場合がある。そのため、第1ゲートドライバグループ1422は、ゲートパルスG\_PLS1-G\_PLS4に基づいて、ゲートラインの第1グループg1\_A-g1\_Dを駆動する場合がある。第2ゲートドライバグループ1424は、ゲートパルスG\_PLS5-G\_PLS8に基づいて、ゲートラインの第2グループg2\_A-g2\_Dを駆動する場合がある。第3ゲートドライバグループ1426は、ゲートパルスG\_PLS1-G\_PLS4に基づいて、ゲートラインの第3グループg3\_A-g3\_Dを駆動する場合がある。第4ゲートドライバグループ1428は、ゲートパルスG\_PLS5-G\_PLS8に基づいて、ゲートラインの第4グループg4\_A-g4\_Dを駆動する場合がある。

20

30

#### 【0115】

図15A及び15Bは、それぞれ、階層的なゲートドライバ回路の動作を制御するために用いられる例示的なタイミング信号を示すタイミング図1500A及び1500Bである。例えば図14を参照して、図15A及び15Bで示されているタイミング信号は、階層的なゲートドライバ回路1400の動作を制御する場合がある。

40

#### 【0116】

時刻t<sub>0</sub>において、スタートパルスS\_PLSはアサートされ、第1ゲートクロック信号G\_CLK\_Aは論理ハイ状態へと遷移する。G\_CLK\_Aの立ち上がりエッジ遷移は、

50

第1 S Rステージ1412に、S\_P L Sの現在の状態をシフトイン（例えば、記憶）させる。S\_P L Sが現在は論理ハイ状態にアサートされているため、時刻t<sub>0</sub>において、第1 S Rステージ1412はまた、第1グループ選択ラインG\_SEL1を論理ハイ状態に駆動する。G\_SEL1の活性化は、第1ゲートドライバグループ1422に、ゲートパルスG\_PLS1 - G\_PLS4に応答してゲートラインの第1グループg<sub>1A</sub> - g<sub>1D</sub>を駆動できるようにする。

#### 【0117】

第1ゲートドライバグループ1422は、時刻t<sub>0</sub>において、G\_SEL1及びG\_PLS1が同時にアサートされる期間（例えば、時刻t<sub>0</sub>からt<sub>1</sub>まで）の間、ゲートラインg<sub>1A</sub>を駆動する場合がある。第1ゲートドライバグループ1422は、時刻t<sub>1</sub>において、G\_SEL1及びG\_PLS2が同時にアサートされる期間（例えば、時刻t<sub>1</sub>からt<sub>2</sub>まで）の間、ゲートラインg<sub>1B</sub>を駆動する場合がある。第1ゲートドライバグループ1422は、時刻t<sub>2</sub>において、G\_SEL1及びG\_PLS3が同時にアサートされる期間（例えば、時刻t<sub>2</sub>からt<sub>3</sub>まで）の間、ゲートラインg<sub>1C</sub>を駆動する場合がある。第1ゲートドライバグループ1422は、時刻t<sub>3</sub>において、G\_SEL1及びG\_PLS4が同時にアサートされる期間（例えば、時刻t<sub>3</sub>からt<sub>4</sub>まで）の間、ゲートラインg<sub>1D</sub>を駆動する場合がある。

10

#### 【0118】

時刻t<sub>4</sub>において、スタートパルスS\_PLSはディアサートされ、第2ゲートクロック信号G\_CLK\_Bは論理ハイ状態へと遷移する。G\_CLK\_Bの立ち上がりエッジ遷移は、第2 S Rステージ1414に、G\_SEL1の現在の状態をシフトインさせる。G\_SEL1が現在は論理ハイ状態にアサートされているため、時刻t<sub>4</sub>において、第2 S Rステージ1414はまた、第2グループ選択ラインG\_SEL2を論理ハイ状態に駆動する。G\_SEL2の活性化は、第2ゲートドライバグループ1424に、ゲートパルスG\_PLS5 - G\_PLS8に応答してゲートラインの第2グループg<sub>2A</sub> - g<sub>2D</sub>を駆動できるようにする。

20

#### 【0119】

第2ゲートドライバグループ1424は、時刻t<sub>4</sub>において、G\_SEL2及びG\_PLS5が同時にアサートされる期間（例えば、時刻t<sub>4</sub>からt<sub>5</sub>まで）の間、ゲートラインg<sub>2A</sub>を駆動する場合がある。第2ゲートドライバグループ1424は、時刻t<sub>5</sub>において、G\_SEL2及びG\_PLS6が同時にアサートされる期間（例えば、時刻t<sub>5</sub>からt<sub>6</sub>まで）の間、ゲートラインg<sub>2B</sub>を駆動する場合がある。第2ゲートドライバグループ1424は、時刻t<sub>6</sub>において、G\_SEL2及びG\_PLS7が同時にアサートされる期間（例えば、時刻t<sub>6</sub>からt<sub>7</sub>まで）の間、ゲートラインg<sub>2C</sub>を駆動する場合がある。第2ゲートドライバグループ1424は、時刻t<sub>7</sub>において、G\_SEL2及びG\_PLS8が同時にアサートされる期間（例えば、時刻t<sub>7</sub>からt<sub>8</sub>まで）の間、ゲートラインg<sub>2D</sub>を駆動する場合がある。

30

#### 【0120】

時刻t<sub>8</sub>において、第1ゲートクロック信号G\_CLK\_Aは論理ロー状態へと遷移し、一方で、第3ゲートクロック信号G\_CLK\_Cは論理ハイ状態へと遷移する。G\_CLK\_Aの立ち下がりエッジ遷移は、第1 S Rステージ1412に、S\_PLSの現在の状態をシフトインさせる。S\_PLSが現在は論理ロー状態にディアサートされているため、時刻t<sub>8</sub>において、第1 S Rステージ1412はまた、G\_SEL1を論理ロー状態にする。G\_SEL1の非活性化は、第1ゲートドライバグループ1422を無効にし、そのため、ゲートラインの第1グループg<sub>1A</sub> - g<sub>1D</sub>のいずれかが活性化されることを防ぐ。

40

#### 【0121】

G\_CLK\_Cの立ち上がりエッジ遷移は、第3 S Rステージ1416に、G\_SEL2の現在の状態をシフトインさせる。G\_SEL2が現在は論理ハイ状態にアサートされているため、時刻t<sub>8</sub>において、第3 S Rステージ1416はまた、第3グループ選択ラインG\_SEL3を論理ハイ状態に駆動する。G\_SEL3の活性化は、第3ゲートドライ

50

バグループ 1426 に、ゲートパルス G\_PLS1 - G\_PLS4 に応答してゲートラインの第3グループ g3A - g3D を駆動できるようにする。

#### 【0122】

第3ゲートドライバグループ 1426 は、時刻 t<sub>8</sub>において、G\_SEL3 及び G\_PLS1 が同時にアサートされる期間（例えば、時刻 t<sub>8</sub>から t<sub>9</sub>まで）の間、ゲートライン g3A を駆動する場合がある。第3ゲートドライバグループ 1426 は、時刻 t<sub>9</sub>において、G\_SEL3 及び G\_PLS2 が同時にアサートされる期間（例えば、時刻 t<sub>9</sub>から t<sub>10</sub>まで）の間、ゲートライン g3B を駆動する場合がある。第3ゲートドライバグループ 1426 は、時刻 t<sub>10</sub>において、G\_SEL3 及び G\_PLS3 が同時にアサートされる期間（例えば、時刻 t<sub>10</sub>から t<sub>11</sub>まで）の間、ゲートライン g3C を駆動する場合がある。第3ゲートドライバグループ 1426 は、時刻 t<sub>11</sub>において、G\_SEL3 及び G\_PLS4 が同時にアサートされる期間（例えば、時刻 t<sub>11</sub>から t<sub>12</sub>まで）の間、ゲートライン g3D を駆動する場合がある。10

#### 【0123】

時刻 t<sub>12</sub>において、第2ゲートクロック信号 G\_CLK\_B は論理ロー状態へと遷移し、一方で、第4ゲートクロック信号 G\_CLK\_D は論理ハイ状態へと遷移する。G\_CLK\_B の立ち下がりエッジ遷移は、第2SRステージ 1414 に、G\_SEL1 の現在の状態をシフトインさせる。G\_SEL1 が現在は論理ロー状態にディアサートされているため、時刻 t<sub>12</sub>において、第2SRステージ 1414 はまた、G\_SEL2 を論理ロー状態にする。G\_SEL2 の非活性化は、第2ゲートドライバグループ 1424 を無効にし、そのため、ゲートラインの第2グループ g2A - g2D のいずれかが活性化されることを防ぐ。20

#### 【0124】

G\_CLK\_D の立ち上がりエッジ遷移は、第4SRステージ 1418 に、G\_SEL3 の現在の状態をシフトインさせる。G\_SEL3 が現在は論理ハイ状態にアサートされているため、時刻 t<sub>12</sub>において、第4SRステージ 1418 はまた、第4グループ選択ライン G\_SEL4 を論理ハイ状態に駆動する。G\_SEL4 の活性化は、第4ゲートドライバグループ 1428 に、ゲートパルス G\_PLS5 - G\_PLS8 に応答してゲートラインの第4グループ g4A - g4D を駆動できるようにする。30

#### 【0125】

第4ゲートドライバグループ 1428 は、時刻 t<sub>12</sub>において、G\_SEL4 及び G\_PLS5 が同時にアサートされる期間（例えば、時刻 t<sub>12</sub>から t<sub>13</sub>まで）の間、ゲートライン g4A を駆動する場合がある。第4ゲートドライバグループ 1428 は、時刻 t<sub>13</sub>において、G\_SEL4 及び G\_PLS6 が同時にアサートされる期間（例えば、時刻 t<sub>13</sub>から t<sub>14</sub>まで）の間、ゲートライン g4B を駆動する場合がある。第4ゲートドライバグループ 1428 は、時刻 t<sub>14</sub>において、G\_SEL4 及び G\_PLS7 が同時にアサートされる期間（例えば、時刻 t<sub>14</sub>から t<sub>15</sub>まで）の間、ゲートライン g4C を駆動する場合がある。第4ゲートドライバグループ 1428 は、時刻 t<sub>15</sub>において、G\_SEL4 及び G\_PLS8 が同時にアサートされる期間（例えば、時刻 t<sub>15</sub>から t<sub>16</sub>まで）の間、ゲートライン g4D を駆動する場合がある。40

#### 【0126】

時刻 t<sub>16</sub>において、第3ゲートクロック信号 G\_CLK\_C は論理ロー状態へと遷移し、一方で、第1ゲートクロック信号 G\_CLK\_A は論理ハイ状態へと遷移する。G\_CLK\_C の立ち下がりエッジ遷移は、第3SRステージ 1416 に、G\_SEL2 の現在の状態をシフトインさせる。G\_SEL2 が現在は論理ロー状態にディアサートされているため、時刻 t<sub>16</sub>において、第3SRステージ 1416 はまた、G\_SEL3 を論理ロー状態にする。G\_CLK\_A の立ち上がりエッジ遷移は、第1SRステージ 1412 に、S\_PLS の現在の状態をシフトインさせる。しかしながら、S\_PLS が、時刻 t<sub>16</sub>においていまだ論理ロー状態であるため、第1SRステージ 1412 は G\_SEL1 を論理ロー状態に保持し続ける場合がある。50

### 【0127】

時刻  $t_{17}$ において、第4ゲートクロック信号  $G_{CLKD}$  は論理ロー状態へと遷移し、一方で、第2ゲートクロック信号  $G_{CLKB}$  は論理ハイ状態へと遷移する。 $G_{CLKD}$  の立ち下がりエッジ遷移は、第4SRステージ1418に、 $G_{SEL3}$  の現在の状態をシフトインさせる。 $G_{SEL3}$  が現在は論理ロー状態にディアサートされているため、時刻  $t_{17}$ において、第4SRステージ1418はまた、 $G_{SEL4}$  を論理ロー状態にする。 $G_{CLKB}$  の立ち上がりエッジ遷移は、第2SRステージ1414に、 $G_{SEL1}$  の現在の状態をシフトインさせる。しかしながら、 $G_{SEL1}$  が、時刻  $t_{17}$ においていまだ論理ロー状態であるため、第2SRステージ1414は $G_{SEL2}$  を論理ロー状態に保持し続ける場合がある。

10

### 【0128】

図15Aの例では、ゲートクロック信号  $G_{CLKA} - G_{CLKD}$  は、互いに少なくとも部分的にオーバーラップしている。例えば、 $G_{CLKA}$  は、 $G_{CLKB}$  がアサートされている期間の少なくとも一部でアサートされたままであり、 $G_{CLKB}$  は、 $G_{CLKC}$  がアサートされている期間の少なくとも一部でアサートされたままであり、 $G_{CLKC}$  は、 $G_{CLKD}$  がアサートされている期間の少なくとも一部でアサートされたままであり、 $G_{CLKD}$  は、 $G_{CLKA}$  がアサートされている期間の少なくとも一部でアサートされたままである。しかしながら、ゲートパルス  $G_{PLS1} - G_{PLS8}$  は、ゲートパルス  $G_{PLS1} - G_{PLS8}$  がオーバーラップしないような短い期間の間アサートされる。このことにより、階層的なゲートドライバ回路1400は、特定のゲートクロック信号の単一のクロック周期の間に、複数のゲートラインを連続して駆動できる。いくつかの実施形態では、ゲートドライバグループ1422 - 1428はそれぞれ、次のゲートラインを論理ハイ状態に駆動する前に、各ゲートラインを完全に論理ロー状態にすることができる。

20

### 【0129】

その上、SRステージ1412 - 1418の出力が、負荷（例えば、ピクセル要素の行）を直接駆動するのではなく、ゲートドライバグループ1422 - 1428を有効にするために使用されるため、階層的なゲートドライバ回路1400は、ピクセルアレーの行を既存のゲートドライバ回路よりも大きい速度及び柔軟性でスキャンし得る。例えば、第2SRステージ1414は、ゲートラインの第1グループ  $g_{1A} - g_{1D}$  の何れとも関連付けられていないため、第2SRステージ1414は、 $g_{1A} - g_{1D}$  の何れかが十分に高い電圧（例えば、 $V_{GH}$ ）で駆動することを待つ必要なしに、第2グループ選択ライン  $G_{SEL2}$  を駆動し得る。このことにより、階層的なゲートドライバ回路1400は、スキャン動作をより荒い粒度、及び／又は、より高い精度で実行し得る。

30

### 【0130】

いくつかの実施形態では、階層的なゲートドライバ回路1400は、ゲートパルス  $G_{PLS1} - G_{PLS8}$  のゲートドライバグループ1422 - 1428への流れを制御するためのゲートライン（ $GL$ ）制御器1430を備える場合がある。いくつかの態様では、 $GL$  制御器1430は、ゲートドライバグループ1422 - 1428を対象とする1以上のゲートパルス  $G_{PLS1} - G_{PLS8}$  を抑制、及び／又は、リダイレクトし得る。例えば、 $GL$  制御器1430は、同じゲートパルスに応答して、同時に、2以上のゲートドライバ要素にそれぞれのゲートラインを駆動させる場合がある。いくつかの態様では、 $GL$  制御器1430は複数のパルスフィルタ1402(1) 1402(4)と接続されている場合がある。複数のパルスフィルタ1402(1) 1402(4)のそれぞれは、ゲートドライバグループ1422 - 1428の1つにそれぞれに供給されたゲートパルスを選択的に抑制し得る。 $GL$  制御器1430は、複数のパルス制御信号  $P_{CTRL1} - P_{CTRL4}$  により、パルスフィルタ1402(1) 1402(4)を制御する場合がある。

40

### 【0131】

いくつかの実施形態では、パルスフィルタ1402(1) 1402(4)はそれぞれ

50

、 AND ロジックゲートのセットを備える場合がある。例えば、第 1 パルスフィルタ 1402 (1) は、パルス制御信号 P\_CTRL1 の第 1 セットがアサートされているときのみに、ゲートパルス G\_PLS1 - G\_PLS4 を第 1 ゲートドライバグループ 1422 に供給する場合がある。第 2 パルスフィルタ 1402 (2) は、パルス制御信号 P\_CTRL2 の第 2 セットがアサートされているときのみに、ゲートパルス G\_PLS5 - G\_PLS8 を第 1 ゲートドライバグループ 1422 に供給する場合がある。第 3 パルスフィルタ 1402 (3) は、パルス制御信号 P\_CTRL3 の第 3 セットがアサートされているときのみに、ゲートパルス G\_PLS1 - G\_PLS4 を第 3 ゲートドライバグループ 1426 に供給する場合がある。第 4 パルスフィルタ 1402 (4) は、パルス制御信号 P\_CTRL4 の第 4 セットがアサートされているときのみに、ゲートパルス G\_PLS5 - G\_PLS8 を第 4 ゲートドライバグループ 1428 に供給する場合がある。

10

#### 【 0132 】

パルス制御信号 P\_CTRL1 の第 1 セットのうち 1 以上がディアサートされているときには、第 1 パルスフィルタ 1402 (1) は、ゲートパルス G\_PLS1 - G\_PLS4 のうち対応する 1 以上を抑制する場合がある。パルス制御信号 P\_CTRL2 の第 2 セットのうち 1 以上がディアサートされているときには、第 2 パルスフィルタ 1402 (2) は、ゲートパルス G\_PLS5 - G\_PLS8 のうち対応する 1 以上を抑制する場合がある。パルス制御信号 P\_CTRL3 の第 3 セットのうち 1 以上がディアサートされているときには、第 3 パルスフィルタ 1402 (3) は、ゲートパルス G\_PLS1 - G\_PLS4 のうち対応する 1 以上を抑制する場合がある。パルス制御信号 P\_CTRL4 の第 4 セットのうち 1 以上がディアサートされているときには、第 4 パルスフィルタ 1402 (4) は、ゲートパルス G\_PLS5 - G\_PLS8 のうち対応する 1 以上を抑制する場合がある。

20

#### 【 0133 】

いくつかの他の実施形態では、GL 制御器 1430 は、各ゲートドライバグループ 1422 - 1428 の内のゲートドライバ要素の間で、ゲートパルス G\_PLS1 - G\_PLS8 のうち 1 以上を再分配する場合がある。例えば、第 1 パルスフィルタ 1402 (1) は、GL 制御器 1430 から受信した P\_CTRL1 信号の第 1 セットに応答してゲートパルス G\_PLS2 - G\_PLS4 が第 1 ゲートドライバグループ 1422 に配信されないようにする場合がある。P\_CTRL1 信号の第 2 セットに応答して、パルスフィルタ 1402 (1) は、第 1 ゲートパルス G\_PLS1 を第 1 ゲートドライバグループ 1422 内の各ゲートドライバ要素に再分配する場合がある。その結果、第 1 ゲートドライバグループ 1422 に接続された各ゲートライン g<sub>1A</sub> - g<sub>1D</sub> は、同じゲートパルス（例えば、G\_PLS1）に応答して同時に駆動される場合がある。

30

#### 【 0134 】

他の利点の中でも、階層的なゲートドライバ回路 1400 は、表示ピクセルのアレーを既存のゲートドライバ回路よりも大きい速度及び / 又は柔軟性でスキャンし得る。いくつかの実施形態では、GL 制御器 1430 は、ゲートパルス G\_PLS1 - G\_PLS8 のうち 1 以上を抑制して、（例えば、ピクセルアレー上で FFOV 画像を描写するために）対応するピクセルアレーの高速なスキャンを実行する場合がある。いくつかの他の実施形態では、GL 制御器 1430 は、ゲートパルス G\_PLS1 - G\_PLS8 のうち特定のゲートドライバに対応する 1 以上ののみが、（例えば、ピクセルアレー上で中心視画像を描写するために）ピクセルアレーの行のうち対応する一部のみについてより低速な再スキャンの実行を可能にし得る。

40

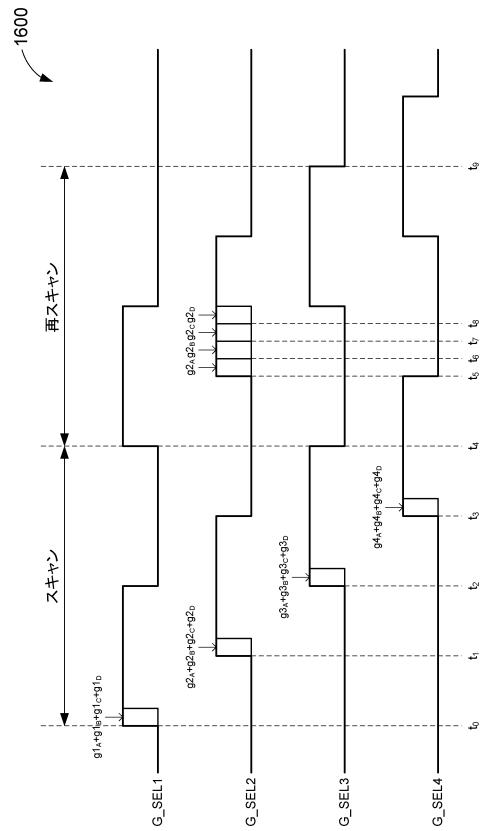

#### 【 0135 】

図 16 は、いくつかの実施形態に係る、階層的なゲートドライバ回路を用いたスキャン - 再スキャンピクセル更新動作の例示的なタイミングを示すタイミング図 1600 である。図 14 の例を参照して、図 16 の処理例は、ピクセルアレー上で中心視画像を FFOV 画像内に描写するために、階層的なゲートドライバ回路 1400 によって実行される場合がある。より詳細には、図 16 の例では、初期スキャンの間に（例えば、時刻 t<sub>0</sub> から t<sub>4</sub>

)、FFOV画像がピクセルアレー上に描写される場合があり、続く再スキャンの間に(例えば、時刻 $t_4$ から $t_9$ )、中心視画像がピクセルアレー上に描写される場合があり、

【0136】

時刻 $t_0$ において、第1グループ選択ラインG\_SEL1が論理ハイ状態に駆動される。G\_SEL1の活性化は、第1ゲートドライバグループ1422を、ゲートラインg1A-g1Dの第1グループをゲートパルスG\_PLS1-G\_PLS4に応答して駆動可能にし得る。図16の例では、GL制御器1430はゲートパルスG\_PLS2-G\_PLS4を抑制し、ゲートパルスG\_PLS1のみが第1ゲートドライバグループ1422に供給されることを可能にする。これに応じて、第1ゲートドライバグループ1422は、ゲートパルスG\_PLS5に応答して、ゲートラインg1A-g1Dを同時に駆動する場合がある。その結果、データライン(例えば、DL(1)-DL(N))の電圧(例えば、スキャン電圧905)が、時刻 $t_0$ において、ゲートラインg1A-g1Dのそれぞれに接続されたそれぞれのピクセル要素に同時に印加され得る。

10

#### 【0137】

時刻 $t_1$ において、第2グループ選択ラインG\_SEL2が論理ハイ状態に駆動される。G\_SEL2の活性化は、第2ゲートドライバグループ1424を、ゲートラインg2A-g2Dの第2グループをゲートパルスG\_PLS6-G\_PLS8に応答して駆動可能にし得る。図16の例では、GL制御器1430はゲートパルスG\_PLS2-G\_PLS4を抑制し、ゲートパルスG\_PLS5のみが第2ゲートドライバグループ1424に供給されることを可能にする。これに応じて、第2ゲートドライバグループ1424は、ゲートパルスG\_PLS5に応答して、ゲートラインg2A-g2Dを同時に駆動する場合がある。その結果、データラインの電圧(例えば、スキャン電圧905)が、時刻 $t_1$ において、ゲートラインg2A-g2Dのそれぞれに接続されたそれぞれのピクセル要素に同時に印加され得る。

20

#### 【0138】

時刻 $t_2$ において、第3グループ選択ラインG\_SEL3が論理ハイ状態に駆動される。G\_SEL3の活性化は、第3ゲートドライバグループ1426を、ゲートラインg3A-g3Dの第3グループをゲートパルスG\_PLS1-G\_PLS4に応答して駆動可能にし得る。図16の例では、GL制御器1430はゲートパルスG\_PLS2-G\_PLS4を抑制し、ゲートパルスG\_PLS1のみが第3ゲートドライバグループ1426に供給されることを可能にする。これに応じて、第3ゲートドライバグループ1426は、ゲートパルスG\_PLS1に応答して、ゲートラインg3A-g3Dを同時に駆動する場合がある。その結果、データラインの電圧(例えば、スキャン電圧905)が、時刻 $t_2$ において、ゲートラインg3A-g3Dのそれぞれに接続されたそれぞれのピクセル要素に同時に印加され得る。

30

#### 【0139】

時刻 $t_3$ において、第4グループ選択ラインG\_SEL4が論理ハイ状態に駆動される。G\_SEL4の活性化は、第4ゲートドライバグループ1428を、ゲートラインg4A-g4Dの第4グループをゲートパルスG\_PLS5-G\_PLS8に応答して駆動可能にし得る。図16の例では、GL制御器1430はゲートパルスG\_PLS6-G\_PLS8を抑制し、ゲートパルスG\_PLS5のみが第4ゲートドライバグループ1428に供給されることを可能にする。これに応じて、第4ゲートドライバグループ1428は、ゲートパルスG\_PLS5に応答して、ゲートラインg4A-g4Dを同時に駆動する場合がある。その結果、データラインの電圧(例えば、スキャン電圧905)が、時刻 $t_3$ において、ゲートラインg4A-g4Dのそれぞれに接続されたそれぞれのピクセル要素に同時に印加され得る。

40

#### 【0140】

ピクセルアレーの再スキャンは、(例えば、他のスタートパルスS\_PLSに応答して)時刻 $t_4$ においてトリガーされる。図16の例では、FFOV画像の中心視領域は、ゲートラインg4A-g4Dと一致する場合がある。表示デバイスは、中心視画像を描写し

50

ているときに（例えば、時刻  $t_4$  から  $t_9$ ）、中心視領域のみを再スキャンし得るため、G L 制御器 1430 は、ゲートパルス G\_PLS1 - G\_PLS4 が第1ゲートドライバグループ 1422 及び第3ゲートドライバグループ 1426 に供給されないようにすることがある。G L 制御器 1430 は更に、ゲートパルス G\_PLS5 - G\_PLS8 が第4ゲートドライバグループ 1428 に供給されないようにすることがある。しかしながら、G L 制御器 1430 はゲートパルス G\_PLS1 - G\_PLS4 のそれぞれを、（例えば、ゲートライン  $g_{2A}$  -  $g_{2D}$  の活性化を制御するところの）第2ゲートドライバグループ 1424 に供給可能にする場合がある。

#### 【0141】

そのため、時刻  $t_5$ において、第2ゲート選択ライン G\_SEL2 の活性化は、ゲートパルス G\_PLS5 と組み合わせて、第2ゲートドライバグループ 1424 にゲートライン  $g_{2A}$  を活性化させる。時刻  $t_6$ において、第2ゲート選択ライン G\_SEL2 の活性化は、ゲートパルス G\_PLS6 と組み合わせて、第2ゲートドライバグループ 1424 にゲートライン  $g_{2B}$  を活性化させる。時刻  $t_7$ において、第2ゲート選択ライン G\_SEL2 の活性化は、ゲートパルス G\_PLS7 と組み合わせて、第2ゲートドライバグループ 1424 にゲートライン  $g_{2C}$  を活性化させる。時刻  $t_8$ において、第2ゲート選択ライン G\_SEL2 の活性化は、ゲートパルス G\_PLS8 と組み合わせて、第2ゲートドライバグループ 1424 にゲートライン  $g_{2D}$  を活性化させる。

#### 【0142】

なお、ピクセル要素の複数の行がゲートパルス G\_PLS1 及び G\_PLS5 のそれに応答してデータで駆動されるため、個々のピクセル要素の初期スキャンの行を通り過ぎてスキャンを進めるために必要な時間の量は、効果的に低減される。このことは、初期スキャン（例えば、時刻  $t_0$  から  $t_4$ ）が、相対的に高速度で実行されることを可能にする。さらに、グループ選択ライン G\_SEL1、G\_SEL3、及び、G\_SEL4 が負荷を駆動しないため、再スキャン（時刻  $t_4$  から  $t_9$ ）は初期スキャンのすぐ後に完了され得る。例えば、第1グループ選択ライン G\_SEL1 が負荷を駆動しないため、第2SRステージ 1414 は、第1グループ選択ライン G\_SEL1 が活性化されたほとんど直後に、第2グループ選択ライン G\_SEL2 を活性化する場合がある。その結果、ゲートライン  $g_{2A}$  -  $g_{2D}$  と接続されたピクセル要素は、ゲートライン  $g_{4A}$  -  $g_{4D}$  と接続されたピクセル要素が（例えば、時刻  $t_3$ において）スキャンされたほとんど直後に、（例えば、時刻  $t_5$ において）再スキャンされ得る。

#### 【0143】

図 17 は、いくつかの実施形態に係る、表示デバイス 1700 の一部を表すブロック図である。表示デバイス 1700 は、図 9 の表示デバイス 900 の例示的な実施形態である場合がある。表示デバイス 1700 は、シフトレジスタステージ 1710 と、ゲートドライバグループ 1720 と、複数のピクセル要素 1701 と、を備える。例えば、ピクセル要素 1701 は図 9 のピクセルアレー 910 の少なくとも一部を備える。シフトレジスタステージ 1710 とゲートドライバグループ 1720 は、図 14 の、ゲートドライバ 914、及び / 又は、階層的なゲートドライバ回路 1400 の少なくとも一部を備える場合がある。図 17 の例では、シンプルするために、一つのシフトレジスタステージ 1710 と一つのゲートドライバグループ 1720 のみが表されている。しかし、実際の実装では、表示デバイス 1700 は図 17 で示されたものよりも少ない、あるいはより多いシフトレジスタステージ、及び / 又は、ゲートドライバグループを有しても良い。

#### 【0144】

ピクセル要素 1701 は、表示ピクセル（例えば、液晶キャパシタ）、フォトダイオード（例えば、画像感知のための）、センサ電極（例えば、容量性感知のための）、又は、それらの組合せを備える場合がある。図 17 の例では、ピクセル要素 1701 は行及び列に配列されている。ピクセル要素 1701 の各行は、それぞれのゲートライン（G\_L）と接続されている。ピクセル要素 1701 の各列は、それぞれのデータライン（D\_L）と接続されている。より詳細には、各ピクセル要素 1701 は、ゲートライン G\_L(A) - G

10

20

30

40

50

L (D) のうち一つ、及び、データライン DL (1) - DL (N) のうち一つと、アクセストランジスタ 1702 を介して接続されている。図 17 の例では、アクセストランジスタ 1702 は、対応するゲートラインと接続されたゲート端子と、対応するデータラインと接続されたドレイン端子と、を有する NMOS トランジスタである。ピクセル要素 1701 は、アクセストランジスタ 1702 を介してソース端子と接続されている。

#### 【0145】

いくつかの実施形態では、シフトレジスタステージ 1710 及びゲートドライバグループ 1720 は、ゲートライン GL (A) - GL (D) の駆動を階層的な手法で制御する場合がある。例えば、シフトレジスタステージ 1710 は、入力信号 (IN) 及び対応するゲートクロック信号 (G\_CLK) に少なくとも部分的に基づいて、グループ選択ライン (G\_SEL) を駆動する場合がある。図 14 に関連して上記で説明したように、入力信号 IN は、(例えば、シフトレジスタステージ 1710 がカスケードの第 1 ステージに対応する場合に) スタートパルス、又は、カスケードにおける前のシフトレジスタステージの出力と対応する場合がある。シフトレジスタステージ 1710 は、入力信号 IN が論理ハイ状態に駆動されており、ゲートクロック信号 G\_CLK もまた論理ハイ状態に遷移するときに、グループ選択ライン G\_SEL を駆動する場合がある。グループ選択ライン G\_SEL の活性化は、ゲートドライバグループ 1720 が個々のゲートライン GL (A) - GL (D) を駆動可能にする。

#### 【0146】

いくつかの実施形態では、ゲートドライバグループ 1720 は複数のゲートドライバ要素 1720A - 1720D を備える場合がある。ゲートドライバ要素 1720A - 1720D のそれぞれは、グループ選択ライン G\_SEL が活性化されたときに、ゲートライン GL (A) - GL (D) のそれぞれ一つを駆動するように構成されている場合がある。いくつかの態様では、ゲートドライバ要素 1720A - 1720D は、ゲートライン GL (A) - GL (D) を複数のゲートパルス (G\_PLS (A) - G\_PLS (D)) に基づいて駆動する場合がある。例えば、第 1 ゲートドライバグループ 1720A は、G\_SEL と G\_PLS (A) が同時に論理ハイ状態にアサートされている間に、第 1 ゲートライン GL (A) に相対的に高いゲート電圧 (例えば、V<sub>GH</sub>) を印加する場合がある。第 1 ゲートライン GL (A) の活性化は、ピクセル要素 1701 の第 1 の行についてアクセストランジスタ 1702 をオンにし、そのため、ピクセル要素 1701 の (例えば、GL (A) と接続された) 第 1 の行に、データライン DL (1) - DL (N) を介してピクセルデータが印加されることを可能にする。

#### 【0147】

第 2 ゲートドライバグループ 1720B は、G\_SEL と G\_PLS (B) が同時に論理ハイ状態にアサートされている間に、第 2 ゲートライン GL (B) に相対的に高いゲート電圧 (例えば、V<sub>GH</sub>) を印加する場合がある。第 2 ゲートライン GL (B) の活性化は、ピクセル要素 1701 の第 2 の行についてアクセストランジスタ 1702 をオンにし、そのため、ピクセル要素 1701 の (例えば、GL (B) と接続された) 第 2 の行に、データライン DL (1) - DL (N) を介してピクセルデータが印加されることを可能にする。(例えば、図 15A のタイミング図と関連して説明されたように) いくつかの態様では、第 1 ゲートパルス G\_PLS (A) は、第 2 ゲートパルス G\_PLS (B) が論理ハイ状態にアサートされる前に、論理ロー状態にディアサートされる場合がある。そのため、第 1 ゲートドライバグループ 1720A は、第 2 ゲートライン GL (B) が活性化される前に、(例えば、ゲート電圧を V<sub>GL</sub> にすることで) 第 1 ゲートライン GL (A) を非活性化する場合がある。

#### 【0148】

第 3 ゲートドライバグループ 1720C は、G\_SEL と G\_PLS (C) が同時に論理ハイ状態にアサートされている間に、第 3 ゲートライン GL (C) に相対的に高いゲート電圧 (例えば、V<sub>GH</sub>) を印加する場合がある。第 3 ゲートライン GL (C) の活性化は、ピクセル要素 1701 の第 3 の行についてアクセストランジスタ 1702 をオン

10

20

30

40

50

にし、そのため、ピクセル要素 1701 の（例えば、GL(C) と接続された）第3の行に、データライン DL(1) - DL(N) を介してピクセルデータが印加されることを可能にする。いくつかの態様では、第2ゲートパルス G\_PLS(B) は、第3ゲートパルス G\_PLS(C) が論理ハイ状態にアサートされる前に、論理ロー状態にディアサートされる場合がある。そのため、第2ゲートドライバグループ 1720B は、第3ゲートライン GL(C) が活性化される前に、（例えば、ゲート電圧を V\_GL にすることで）第2ゲートライン GL(B) を非活性化する場合がある。

#### 【0149】

第4ゲートドライバグループ 1720D は、G\_SEL と G\_PLS(D) が同時に論理ハイ状態にアサートされている間に、第4ゲートライン GL(D) に相対的に高いゲート電圧（例えば、V\_GH）を印加する場合がある。第4ゲートライン GL(D) の活性化は、ピクセル要素 1701 の第4の行についてアクセストランジスタ 1702 をオンにし、そのため、ピクセル要素 1701 の（例えば、GL(D) と接続された）第4の行に、データライン DL(1) - DL(N) を介してピクセルデータが印加されることを可能にする。いくつかの態様では、第3ゲートパルス G\_PLS(C) は、第4ゲートパルス G\_PLS(D) が論理ハイ状態にアサートされる前に、論理ロー状態にディアサートされる場合がある。そのため、第3ゲートドライバグループ 1720C は、第4ゲートライン GL(D) が活性化される前に、（例えば、ゲート電圧を V\_GL にすることで）第3ゲートライン GL(C) を非活性化する場合がある。

#### 【0150】

なお、ピクセル要素 1701 の各行を（例えば、G\_CLK がアサートされる期間の半分以内で）素早く連続して駆動するために、ゲートドライバ要素 1720A - 1720D は、ゲートライン GL(A) - GL(D) に印加されるべきゲートパルス G\_PLS(A) - G\_PLS(D) を全電圧範囲で変化可能とすべきである。しかしながら、グループ選択ライン G\_SEL の電圧は、対応するゲートライン GL(A) - GL(D) を駆動する際に、ゲートドライバ要素 1720A - 1720D のそれぞれに電力供給する場合がある。そのため、グループ選択ライン G\_SEL の電圧は、ゲートライン GL(A) - GL(D) を駆動するために用いられ得る“ターンオン”電圧の量を制限する場合がある。いくつかの実施形態では、ゲートドライバ要素 1720A - 1720D のそれぞれは、グループ選択ライン G\_SEL の電圧を、ゲートライン GL(A) - GL(D) に印加されるべきゲートパルス G\_PLS(A) - G\_PLS(D) の全電圧範囲で変化可能にするように“昇圧”するように構成されている場合がある。いくつかの態様では、1以上のゲートドライバ要素 1720A - 1720D は、相補型 MOS (CMOS) インバータを備える場合がある。他の態様では、1以上のゲートドライバ要素 1720A - 1720D は、昇圧 NMOS ドライバ又は、昇圧 PMOS ドライバを備える場合がある。

#### 【0151】

図 18 は、いくつかの実施形態に係る、例示的なスキャン - 再スキャン更新動作 1800 を表す例示的なフローチャートである。例示的な動作 1800 は、例えば、図 1、3、5、及び、9 の表示デバイス 120、300、500、900 を含む、本開示の任意の表示デバイスによって実行され得る。例えば図 3 を参照して、例示的な動作 1800 は、单一のフレーム更新期間の間に、ピクセルアレーを複数回スキャンするために、表示デバイス 300 によって実行される場合がある。

#### 【0152】

表示デバイスは、第1時刻において、ピクセルアレーに表示されるべき画像に対応する表示データのフレームを受信する場合がある（1810）。例えば、表示データは、アレー 310 の 1 以上のピクセル要素についてのピクセル値（例えば、色、及び / 又は、強度に対応する）を含む場合がある。各ピクセル値は、ターゲット電圧レベルに対応する場合がある。ターゲット電圧は、特定のピクセル要素に印加されたときに、ピクセル要素の色及び / 又は強度を所望のピクセル値に安定させる電圧である場合がある。

#### 【0153】

10

20

30

40

50

表示デバイスは、第1時刻より前のピクセル調節期間の間に、ピクセルアレーの各行をスキヤンして、第1電圧をピクセルアレーのそれぞれのピクセル要素に印加する(1820)。例えば、表示更新制御器340は、ピクセル値に少なくとも部分的に基づいて、アレーの1以上のピクセル要素に印加されるべきピクセル電圧を決定する場合がある。いくつかの実施形態では、第1電圧は、ピクセルアレーの1以上の行に含まれるそれぞれのピクセル要素に印加されるべきオーバードライブ電圧を含む場合がある(図5-8に関して上記で説明したように)。他のいくつかの実施形態では、第1電圧は、ピクセルアレーの各行に含まれるそれぞれのピクセル要素に印加されるべきFFOV電圧を含む場合がある(図9-13に関して上記で説明したように)。

**【0154】**

表示デバイスは、更に、ピクセル調節期間の間に、ピクセルアレーのうち一部の行を再スキヤンして、一部の行に含まれるそれぞれのピクセル要素に第2電圧を印加する(1830)。例えば、後続のピクセルアレーの再スキヤンの間、表示更新制御器340は、ピクセルアレーの1以上の行に含まれるそれぞれのピクセル要素に印加されるべき調節されたピクセル電圧を決定する場合がある。いくつかの実施形態では、第2電圧は、ピクセルアレーのオーバードライブされたそれぞれのピクセル要素に印加されるべきターゲット電圧を含む場合がある(図5-8に関して上記で説明したように)。他のいくつかの実施形態では、第2電圧は、ピクセルアレーの1以上の行に含まれるそれぞれのピクセル要素に印加されるべき中心視電圧を含む場合がある(図9-13に関して上記で説明したように)。

**【0155】**

表示デバイスは、その後、1以上の光源を活性化して、第1時刻においてピクセルアレーを照らす場合がある(1840)。例えば、ピクセルアレーの各ピクセル要素は、第1電圧を印加されると、それぞれのピクセル値へ遷移を開始する場合がある。第2電圧は、ピクセルアレーのそれぞれのピクセル要素の状態、及び/又は、転移の速度を改変する場合がある。しかしながら、ピクセル要素は表示期間の間にのみ照らされるため、表示期間の前又は後に現れたピクセル値の如何なる変化も、ユーザによって視認され得ない。

**【0156】**

図19は、いくつかの実施形態に係る、例示的なオーバードライブ補正動作1900を表す例示的なフローチャートである。例えば図5を参照して、例示的な動作1900は、ピクセルアレー510の1以上のオーバードライブされたピクセル要素についてのピクセル値を補正するために、表示デバイス500によって実行される場合がある。

**【0157】**

表示デバイスは、ピクセルアレーの各ピクセル要素についてターゲット電圧を決定する場合がある(1910)。例えば、オーバードライブ回路部530は、ピクセルアレーのピクセル要素のそれぞれに印加されるべきピクセル電圧を、アレーの各ピクセル要素それについての現在のピクセル値及びターゲットピクセル値に少なくとも部分的に基づいて決定する場合がある。より詳細には、アレーの各ピクセル要素について、オーバードライブ回路部530は現在のピクセル値(例えば、直前のフレーム更新からのピクセル値)をターゲットピクセル値(例えば、次のフレーム更新についてのピクセル値)と比較して、フレーム更新期間内にピクセル値の所望の変化を達成するためにピクセル要素に印加されるべき電圧の量を決定する場合がある。特定のピクセル要素についてのターゲット電圧は、ピクセル要素をそのターゲットピクセル値に安定させる。

**【0158】**

表示デバイスは、更に、ピクセルアレーのうち一部の行に含まれるそれぞれのピクセル要素についてオーバードライブ電圧を決定する場合がある(1920)。上記で説明したように、オーバードライブ回路部530は、アレーの各ピクセル要素についての現在のピクセル電圧及びターゲットピクセル電圧に少なくとも部分的に基づいて、ピクセルアレーの各ピクセル要素に印加されるべきピクセル電圧を決定する場合がある。しかしながら、もしピクセル値の変化が閾値量を超える場合、ターゲット電圧は、所与のフレーム更新期

10

20

30

40

50

間内にピクセル要素を所望のピクセル値に駆動するためには不十分である場合がある。そのため、オーバードライブ回路部 530 は、アレーの各ピクセル要素に印加されるべきオーバードライブ電圧を決定する場合がある。上記で説明したように、オーバードライブ電圧は、ピクセル要素についてのターゲット電圧を超える（例えば、ターゲット電圧より高い、又は、低い）場合があり、そのため、ピクセル要素をターゲットピクセル値により高速に遷移（例えば、回転）させる。

#### 【 0159 】

表示デバイスは、一部の行に含まれるそれぞれのピクセル要素にオーバードライブ電圧を印加し、残る行に含まれるそれぞれのピクセル要素にターゲット電圧を印加することと、ピクセルアレーをスキャンする場合がある（1930）。例えば、スキャン／再スキャン回路部 540 は、ピクセルアレーの各行に含まれるそれぞれのピクセル要素についてのターゲット電圧及び／又はオーバードライブ電圧に基づいて、スキャン電圧を生成する場合がある。より詳細には、それぞれのスキャン電圧は、アレーの初期スキャンの間に、ピクセルアレーの各ピクセル要素に印加される場合がある。そのため、スキャン電圧は、次の表示期間の開始時までにそれらのピクセル要素のターゲットピクセル値に安定させることができない、任意のピクセル要素についてのオーバードライブ電圧を含む場合がある。いくつかの実施形態では、表示デバイスは、初期スキャンの間に、ピクセルアレーのピクセル要素のうち少なくともいくつかをそれらのターゲット電圧に駆動し、一方で、ピクセル要素のより少ない一部のみをそれらのオーバードライブ電圧に駆動する場合がある。

10

#### 【 0160 】

表示デバイスは、更に、一部の行に含まれるそれぞれのピクセル要素にターゲット電圧を印加することで、一部の行を再スキャンする場合がある（1940）。例えば、スキャン／再スキャン回路部 540 は、任意のオーバードライブされたピクセル要素について、ターゲット電圧に基づいて再スキャン電圧を生成する場合がある。再スキャン電圧は、各オーバードライブされたピクセル要素を（例えば、初期スキャンから）そのターゲット電圧に駆動するために用いられる場合がある。これに応じて、再スキャン電圧 506 は、1 以上のピクセル要素についてのターゲット電圧のみを含む場合がある。いくつかの実施形態では、表示デバイスは、再スキャンの間に、ピクセル要素のより少ない一部のみをそれらのターゲット電圧に駆動する場合がある。他のいくつかの実施形態では、表示デバイスは、初期スキャンと再スキャンの間に生じ得る任意の不所望なエッジを隠すために、ディザリングの技術を用いる場合がある。

20

30

#### 【 0161 】

図 20 は、いくつかの実施形態に係る、例示的な中心視描写動作 2000 を表す例示的なフローチャートである。図 9 を参照して、例示的な動作 2000 は、FFOV 画像を中心視画像と合成してピクセルアレー 910 上で描写するために、表示デバイス 900 によって実行される場合がある。

#### 【 0162 】

表示デバイスは、ピクセルアレーの各ピクセル要素について FFOV 電圧を決定する場合がある（2010）。例えば、中心視描写回路部 930 は、受信した表示データのフレームからの FFOV ピクセル値及び中心視ピクセル値に少なくとも部分的に基づいて、ピクセルアレーの各ピクセル要素に印加されるべきピクセル電圧を決定する場合がある。FFOV ピクセル値は、ピクセルアレーのピクセル要素のうち（全てで無い場合は）大半にわたって表示されるべきフルフレーム画像に対応し得る。FFOV 画像は、ユーザの視線の周辺に広がり得るため、FFOV ピクセル値は相対的に低い解像度を有する。そのため、いくつかの実施形態では、中心視描写回路部 930 は、各 FFOV ピクセル値を、（例えば、ピクセルアレーのそれぞれのピクセル要素に印加されるべき）複数の FFOV 電圧と関連付ける場合がある。

40

#### 【 0163 】

表示デバイスは、更に、ピクセルアレーのうち一部の行に含まれるそれぞれのピクセル要素について中心視電圧を決定する場合がある（2020）。上記で説明したように、中

50

心視描写回路部 930 は、受信した表示データのフレームからの FFOV ピクセル値及び中心視ピクセル値に少なくとも部分的に基づいて、ピクセルアレーの各ピクセル要素に印加されるべきピクセル電圧を決定する場合がある。中心視ピクセル値は、ユーザの視線の中心視領域のみに広がる中心視画像に対応し得る。中心視領域はユーザが最大の視力を有すると判断される領域に対応するため、中心視ピクセル値は相対的に高い解像度を有する場合がある。そのため、いくつかの実施形態では、中心視描写回路部 930 は、各中心視ピクセル値を、（例えば、ピクセルアレーの一部に含まれるそれぞれのピクセル要素に印加されるべき）それぞれの中心視電圧と関連付ける場合がある。

#### 【0164】

表示デバイスは、ピクセルアレーの各行に含まれるそれぞれのピクセル要素に FFOV 電圧を印加することで、ピクセルアレーをスキャンする場合がある（2030）。例えば、表示デバイスは、初期スキャン動作の間に、FFOV 画像をピクセルアレー上に描写する場合がある（例えば、図 12A に関して上記で説明したように）。より詳細には、表示デバイスは、（例えば、ライン  $l_0$  から  $l_M$  まで）ピクセルアレーの各行をスキャンすることで、FFOV 画像を描写する場合がある。いくつかの実施形態では、スキャン／再スキャン回路部 940 は、FFOV 電圧に基づいてスキャン電圧を生成する場合がある。例えば、スキャン電圧は、アレーの初期スキャンの間に、ピクセルアレーの各ピクセル要素に印加される場合がある。そのため、各スキャン電圧 905 は、それぞれの FFOV 電圧に対応し得る。

#### 【0165】

表示デバイスは、更に、一部の行に含まれるそれぞれのピクセル要素に中心視電圧を印加することで、該一部の行を再スキャンする場合がある（2040）。例えば、表示デバイスは、後続の再スキャン動作の間に、中心視画像を FFOV 画像に重ねあわせる画像としてピクセルアレー上に描写する場合がある（例えば、図 12B に関して上記で説明したように）。より詳細には、表示デバイスは、ピクセルアレーのうち FFOV 画像の中心視領域に対応する一部の行のみを（例えば、ライン  $l_{f_1}$  から  $l_{f_2}$  まで）再スキャンすることで、中心視画像を描写する場合がある。いくつかの実施形態では、スキャン／再スキャン回路部 940 は中心視電圧に基づいて、再スキャン電圧を生成する場合がある。例えば、再スキャン電圧 906 は、ピクセルアレー上に表示される FFOV 画像の中心視領域内の各ピクセル要素に、それぞれの中心視電圧を印加するために用いられる場合がある。これに応じて、再スキャン電圧は、再スキャンされるピクセル要素のうち少なくともいくつかについての中心視電圧を含む場合がある。

#### 【0166】

スキャン／再スキャン回路部 940 は、再スキャン動作の間に、ピクセルアレーのうち再スキャンされる行に含まれる FFOV 画像の中心視領域の外側にある任意の（図 12B の列  $c_0$  から  $c_{f_1}$  まで、及び、 $c_{f_2}$  から  $c_N$  までに含まれるピクセル要素のような）ピクセル要素に、FFOV 電圧を再印加する場合がある。そのため、いくつかの実施形態では、再スキャン電圧は、再スキャンされるピクセル要素のうち少なくともいくつかについての FFOV 電圧をまた含む場合がある。その上更に、いくつかの実施形態では、表示デバイスは、初期スキャンと再スキャンの間に生じ得る任意の不所望なエッジを隠すために、ディザリングの技術を用いる場合がある。

#### 【0167】

当業者は、様々な異なる任意のテクノロジー及び技術を用いて、情報及び信号が表し得ることを理解するであろう。例えば、上述の説明を通して参照され得るデータ、命令、コマンド、情報、信号、ビット、記号、及び、チップは、電圧、電流、電磁波、磁界又は粒子、光場又は粒子、あるいは、これらの組合せによって表し得る。

#### 【0168】

さらに、当業者は、本開示の態様に関連して説明された様々な例示的な論理ブロック、モジュール、回路、及び、アルゴリズムのステップが、電気的なハードウェア、コンピュータソフトウェア、及び両者の組合せとして実装し得ることを理解しよう。このハードウ

10

20

30

40

50

エアとソフトウェアの交換可能性を明確に図示するために、説明のための様々なコンポーネント、ブロック、モジュール、回路、及び、ステップが、一般に、その機能の観点で上述のように説明されてきた。このような機能がハードウェア又はソフトウェアの何れで実装されるかは、独特の用途とシステム全体に要求されるデザイン上の制約に依存する。当業者は説明された機能を独特の用途毎に様々な方法で実装し得るが、そのような実装上の決定が、本開示の範囲からの逸脱を生じさせると解釈されてはならない。

【0169】

本開示の態様に関連して説明された方法、手順、又はアルゴリズムは、ハードウェアにより、プロセッサによって実行されるソフトウェアモジュールにより、あるいは、両者の組合せにより、直接的に具体化され得る。ソフトウェアモジュールは、RAMメモリ、フラッシュメモリ、ROMメモリ、EPROMメモリ、EEPROMメモリ、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で既知の他の形式の記憶媒体に常駐することができる。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、プロセッサに接続される。あるいは、記憶媒体はプロセッサに統合されてもよい。

10

【0170】

前述の明細書では、その具体的な例を参照して実施形態が説明されてきた。しかしながら、添付の特許請求の範囲に提示されているように、本開示のより広い範囲を逸脱することなく、それらに対して様々な変形や変更が成し得ることは明らかであろう。したがって、明細書及び図面は、限定的な意味ではなく説明としての意味で解釈される。

20

30

40

50

【図面】

【図 1】

FIG. 1

【図 2】

FIG. 2

10

20

30

40

【図 3】

FIG. 3

【図 4】

FIG. 4

50

【図 5】

FIG. 5

【図 6】

FIG. 6

10

20

30

40

【図 7A】

FIG. 7A

【図 7B】

FIG. 7B

50

【図 8】

FIG. 8

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

10

20

30

40

50

【図 12 A】

【図 12 B】

10

FIG. 12B

FIG. 12A

20

【図 13】

FIG. 13

【図 14】

30

40

FIG. 14

50

【図 15 A】

【図 15 B】

10

FIG. 15B

20

FIG. 15A

20

【図 16】

FIG. 16

30

【図 17】

40

FIG. 17

50

【図 18】

【図 19】

10

20

FIG. 18

FIG. 19

【図 20】

30

40

FIG. 20

50

---

**フロントページの続き****(51)国際特許分類**

| F I     |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 3 U |

| G 0 9 G | 3/20  | 6 2 1 E |

| G 0 9 G | 3/34  | J       |

| G 0 2 F | 1/13  | 5 0 5   |

| G 0 2 F | 1/133 | 5 5 0   |

**(56)参考文献**

特開2006-243185 (JP, A)

国際公開第2010/095387 (WO, A1)

特開平02-246482 (JP, A)

特表2009-516210 (JP, A)

韓国公開特許第10-2018-0036429 (KR, A)

**(58)調査した分野** (Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3

G 0 2 F 1 / 1 3 3