(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3710342号

(P3710342)

(45) 発行日 平成17年10月26日(2005.10.26)

(24) 登録日 平成17年8月19日(2005.8.19)

(51) Int.C1.<sup>7</sup>

F 1

H03M 7/30

H03M 7/30

A

H04N 7/30

H04N 7/133

Z

請求項の数 17 (全 17 頁)

(21) 出願番号

特願平11-253495

(22) 出願日

平成11年9月7日(1999.9.7)

(65) 公開番号

特開2001-77697(P2001-77697A)

(43) 公開日

平成13年3月23日(2001.3.23)

審査請求日

平成15年10月20日(2003.10.20)

特許法第30条第1項適用 1999年3月8日 社団

法人電子情報通信学会発行の「1999年電子情報通信

学会総合大会講演論文集 情報・システム2」に発表

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100093908

弁理士 松本 研一

(74) 代理人 100101306

弁理士 丸山 幸雄

(72) 発明者 梶原 浩

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 郭 睦凌

栃木県宇都宮市戸祭1-8-9 東京電力

(株)戸祭寮

最終頁に続く

(54) 【発明の名称】デジタル信号処理装置および方法および記憶媒体

## (57) 【特許請求の範囲】

## 【請求項1】

入力信号系列を低周波帯域の信号と高周波帯域の信号の2つに分解するデジタル信号処理装置であって、

入力信号系列を奇数番信号系列と偶数番信号系列に分離する信号系列分離手段と、

前記奇数番信号系列と偶数番信号系列の夫々に対してリフティング処理を施すことにより

、第1の低周波帯域係数信号列と第1の高周波帯域係数信号列とを生成する第1のフィルタ手段と、

前記2つの信号系列の夫々に対して、前記リフティング処理と異なるフィルタ処理を施すことにより、第2の低周波帯域係数信号列と第2の高周波帯域係数信号列とを生成する第2のフィルタ手段と、

前記第1の低周波帯域係数信号列と前記第2の低周波帯域係数信号列のいずれか一方と、

前記第1の高周波帯域係数信号列と前記第2の高周波帯域係数信号列のいずれか一方とを

適応的に選択して、夫々、低周波帯域係数信号列出力と高周波帯域係数信号列出力として

出力する適応的選択手段とを具備することを特徴とするデジタル信号処理装置。

## 【請求項2】

前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理と第2のリフティング処理とを直列に行うことを特徴とする請求項1に記載のデジタル信号処理装置。

## 【請求項3】

前記第2のフィルタ手段は、前記奇数番信号系列と偶数番信号系列のいずれか一方を取り出して前記第2の低周波帯域係数信号列とし、前記奇数番信号系列と偶数番信号系列の差分を前記第2の高周波帯域係数信号列として前記適応的選択手段に出力することを特徴とする請求項2に記載のデジタル信号処理装置。

【請求項4】

前記適応的選択手段は、この適応的選択手段による以前の選択結果としての前記低周波帯域係数信号列出力に基づいて、二値領域か多値領域かを判定することを特徴とする請求項1乃至3のいずれかに記載のデジタル信号処理装置。

【請求項5】

前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理を行う第1リフティング回路と、この第1リフティング回路の後段に設けられ第2のリフティング処理を行う第2リフティング回路とを有し、

前記適応的選択手段は、第1と第2の適応的選択回路を有し、

前記第1の適応的選択回路は、前記第1のリフティング回路の出力に対して適応的選択動作を行い、

前記第2のリフティング回路は、前記第1の適応的選択回路によって選択された結果に対して前記第2のリフティング処理を行い、

前記第2の適応的選択回路は、前記第2のリフティング回路によりリフティング処理された結果に対して適応的選択動作を行うことを特徴とする請求項1記載のデジタル信号処理装置。

10

20

【請求項6】

入力信号系列から所定の周波数帯域の信号を得るデジタル信号処理装置であって、入力信号系列を奇数番信号系列と偶数番信号系列に分離する信号系列分離手段と、前記奇数番信号系列或いは偶数番信号系列にリフティング処理を用いたフィルタ処理を施すことにより、所定の周波数帯域の係数信号列を生成する第1のフィルタ手段と、前記リフティング処理される信号系列に対して、前記第1のフィルタ手段が用いるリフティング処理とは異なるフィルタ処理を施すことにより、前記所定の周波数帯域の係数信号列を生成する第2のフィルタ手段と

前記第1、第2フィルタ手段で得られる複数の係数信号列のいずれか一方を適応的に選択して出力する適応的選択手段とを具備することを特徴とするデジタル信号処理装置。

30

【請求項7】

前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理と第2のリフティング処理とを直列に行うことにより、第1の低周波帯域係数信号列と第1の高周波帯域係数信号列とを出力することを特徴とする請求項6に記載のデジタル信号処理装置。

【請求項8】

前記第2のフィルタ手段は、前記奇数番信号系列と偶数番信号系列のいずれか一方を取り出して第2の低周波帯域係数信号列とし、前記奇数番信号系列と偶数番信号系列の差分を第2の高周波帯域係数信号列として前記適応的選択手段に出力することを特徴とする請求項6に記載のデジタル信号処理装置。

40

【請求項9】

前記適応的選択手段は、この適応的選択手段による以前の選択結果としての前記低周波帯域係数信号列出力に基づいて、二値領域か多値領域かを判定することを特徴とする請求項6乃至8のいずれかに記載のデジタル信号処理装置。

【請求項10】

前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理を行う第1リフティング回路と、この第1リフティング回路の後段に設けられ第2のリフティング処理を行う第2リフティング回路とを有し、

前記適応的選択手段は、第1と第2の適応的選択回路を有し、

前記第1の適応的選択回路は、前記第1のリフティング回路の出力に対して適応的選択動

50

作を行い、

前記第2のリフティング回路は、前記第1の適応的選択回路によって選択された結果に対して前記第2のリフティング処理を行い、

前記第2の適応的選択回路は、前記第2のリフティング回路によりリフティング処理された結果に対して適応的選択動作を行うことを特徴とする請求項6記載のデジタル信号処理装置。

【請求項11】

前記所定の周波数帯域は高周波帯域であることを特徴とする請求項6に記載のデジタル信号処理装置。

【請求項12】

10

入力信号系列から所定の周波数帯域の信号を得るデジタル信号処理方法であって、

入力信号系列を奇数番信号系列と偶数番信号系列に分離する信号系列分離工程と、

前記奇数番信号系列或いは偶数番信号系列にリフティング処理を用いたフィルタ処理を施すことにより、所定の周波数帯域の係数信号列を生成する第1のフィルタ工程と、

前記リフティング処理される信号系列に対して、前記第1のフィルタ工程で用いるリフティング処理とは異なるフィルタ処理を施すことにより、前記所定の周波数帯域の係数信号列を生成する第2のフィルタ工程と、

前記第1、第2フィルタ工程で得られる複数の係数信号列のいずれか一方を適応的に選択して出力する適応的選択工程とを具備することを特徴とするデジタル信号処理方法。

【請求項13】

20

前記第1のフィルタ工程は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理と第2のリフティング処理とを直列に行うことにより、第1の低周波帯域係数信号列と第1の高周波帯域係数信号列とを出力することを特徴とする請求項12に記載のデジタル信号処理方法。

【請求項14】

前記第2のフィルタ工程は、前記奇数番信号系列と偶数番信号系列のいずれか一方を取り出して第2の低周波帯域係数信号列とし、前記奇数番信号系列と偶数番信号系列の差分を第2の高周波帯域係数信号列として前記適応的選択工程に出力することを特徴とする請求項12に記載のデジタル信号処理方法。

【請求項15】

30

前記適応的選択工程は、この適応的選択工程による以前の選択結果としての前記低周波帯域係数信号列出力に基づいて、二値領域か多値領域かを判定することを特徴とする請求項12乃至14のいずれかに記載のデジタル信号処理方法。

【請求項16】

前記所定の周波数帯域は高周波帯域であることを特徴とする請求項12に記載のデジタル信号処理方法。

【請求項17】

請求項12乃至16のいずれかに記載のデジタル信号処理方法を実施するコンピュータプログラムを記憶するプログラム記憶媒体。

【発明の詳細な説明】

40

【0001】

【発明の属する技術分野】

本発明は、デジタル信号処理装置および方法およびこの方法を記憶した記憶媒体に関するものである。

【0002】

【従来の技術】

画像は非常に多くの情報を含んでおり、その蓄積・伝送に於いては膨大なデータ量が問題となる。そこで蓄積・伝送に際しては、画像の持つ冗長性を除く、或いはさらに視覚的に認識し難い程度で画素値に操作を加えること等によってデータ量を削減する高能率符号化が用いられる。

50

## 【0003】

近年、エントロピーの低減効果が高いことや、画像の段階的伝送に適しているといった理由から、離散ウェーブレット変換を用いた画像符号化方式の検討が盛んである。ウェーブレット変換は有効なデータ解析ツールとみなされ、低ビットレートで高画質を目指すスケーラブル画像符号化に広く使われている。

## 【0004】

ウェーブレット変換を簡易・高速に実装する方法としてW. Sweldensにより、リフティング手法(Lifting Scheme)が提案されている。リフティング手法は離散ウェーブレット変換を簡単なフィルタリフティングステップに分解して実装するものであり、この手法により演算コストとメモリコストとを削減できることが知られている。

## 【0005】

従来の離散ウェーブレット変換の一例としてデジタル信号系列  $x(n)$  に対する  $5 \times 3$  フィルタによる離散ウェーブレット変換の式を以下に示す。

## 【0006】

## [EQ1]

$$r(n) = -\frac{x(2n-2)}{8} + \frac{x(2n-1)}{4} + \frac{3 \cdot x(2n)}{4} + \frac{x(2n+1)}{4} - \frac{x(2n+2)}{8}$$

## 【0007】

## [EQ2]

$$d(n) = -\frac{x(2n)}{2} + x(2n+1) - \frac{x(2n+2)}{2}$$

## 【0008】

周知のように、 $r(n)$  は平滑化の程度を表す係数であり、従って、低周波帯域出力の係数を表し、 $d(n)$  は詳細度(detail)の程度を表す係数であり、従って、高周波帯域出力の係数を表す。

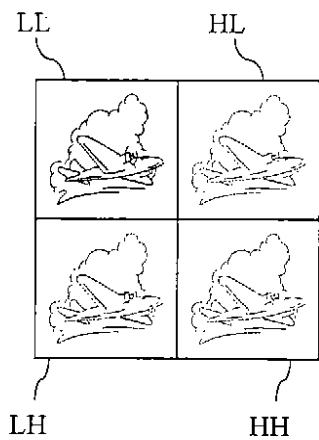

尚、上の [EQ1], [EQ2] は 1 次元の離散ウェーブレット変換処理を示したものである。2 次元離散ウェーブレット変換は、1 次元の変換を水平・垂直方向に順次行うものである。図 1 乃至図 3 は、2 次元離散ウェーブレット変換により変換対象画像を L L, L H, H L, H H の 4 つの周波数帯域(サブバンド)に分解する様子を模式的に示したものである。その詳細は公知であるので本明細書では説明を省略する。

## 【0009】

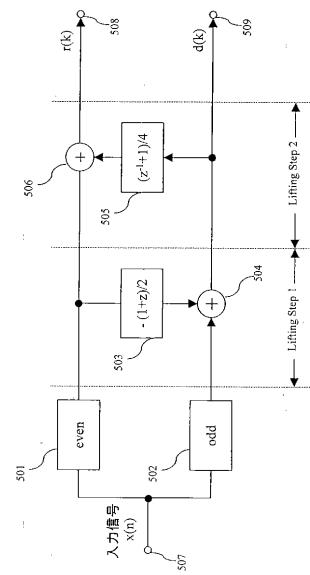

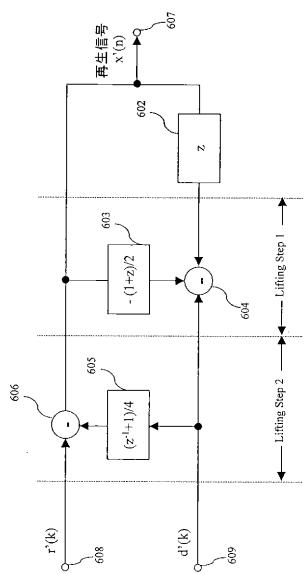

この  $5 \times 3$  フィルタをリフティング方式を用いて構成した場合のブロック図は図 4 のようになる。

## 【0010】

同図に於いて、501 は偶数番のサンプルを取り出すサンプリング回路、502 は奇数番のサンプルを取り出すサンプリング回路、503, 505 はフィルタ回路、504, 506 は加算器、507 は信号入力端子、508, 509 は信号出力端子である。デジタル信号系列  $x(n)$  は、サンプリング回路 501, 502 により、夫々、偶数アドレスのサンプル  $x_e (= x(2n))$  と奇数アドレスのサンプル  $x_o (= x(2n+1))$  に分けられ、夫々に対して、2 つのフィルタ処理(図中、Lifting Step 1 と Lifting Step 2)が施される。このようなリフティングを用いた場合、[EQ1] と [EQ2] の  $5 \times 3$  フィルタは次式のように変形される。

## 【0011】

## [EQ3]

$$r(n) = x(2n) + \frac{d(n-1) + d(n)}{4}$$

10

20

30

40

50

## 【0012】

[EQ4]

$$d(n) = x(2n+1) - \frac{x(2n)+x(2n+2)}{2}$$

## 【0013】

上の[EQ3],[EQ4]を前述の[EQ1],[EQ2]と比較すると、演算回数の削減、必要なデータアクセスの削減がなされていることが分かる。なお、この逆変換も、変換処理と対称な処理で実現できる。

図5は合成側のブロック図を示したものであり、分解処理と同様に簡易な処理であることが分かる。尚、合成処理手順の詳細は公知であるので説明を省略する。なお、通常、前述の $5 \times 3$  フィルタを実現する場合、除算による丸めの誤差を考慮して次式のように整数化することにより完全再構成を可能とすることが一般的である。

10

## 【0014】

[EQ5]

$$r(n) = x(2n) + \text{floor}\left\{\frac{d(n-1) + d(n) + 2}{4}\right\}$$

## 【0015】

[EQ6]

20

$$d(n) = x(2n+1) - \text{floor}\left\{\frac{x(2n) + x(2n+2) + 1}{2}\right\}$$

## 【0016】

但し、上式において、 $\text{floor}\{X\}$ はXを超えない最大の整数を表すものとする。

## 【0017】

## 【発明が解決しようとする課題】

しかしながら、従来の離散ウェーブレット変換により、自然画像を主たる符号化対象とする符号化システムを構成した場合、2値画像及び混在画像に対しては高い圧縮性能を実現できないという問題がある。これは離散ウェーブレット変換に使用するフィルタが、変換対象画像の特性に適合していない場合に発生する。

30

## 【0018】

即ち、自然画像に対して良好なエントロピー低減効果を持つフィルタを選択した場合には、選択されたフィルタによる変換対象となる画像が、2値画像、CG画像など、その特性が自然画像と異なるものとなった場合には、良好なエントロピー低減効果を得ることができない。

## 【0019】

このようなフィルタ不適合の問題を解決する手法として、変換処理の前に、画像毎に、あるいは画像から分割された領域毎に、その特性を調べて、特性に適切なフィルタを選択するといった方法が種々提案されているが、特性判定のためのプリスキャンを必要とするために、メモリコストの増加、処理の複雑化という問題がある。

40

## 【0020】

更に、画像毎にフィルタを選択する場合には、選択されたフィルタは、そのフィルタを特定する局所的な特性に対応できないという問題がある。逆に、画像を分割して各領域毎にフィルタを選択する場合には、そのフィルタは、画像の局所的性質への対応が可能となるものの、画像の細分化による変換効率の低下、フィルタ選択情報伝送による圧縮性能の低下などの問題を来す。

## 【0021】

したがって、従来の離散ウェーブレット変換用の信号処理装置は、ユーザ要求を満たすに十分ではなかった。

50

**【0022】**

本発明は、前述の問題点に鑑みてなされたものであり、リフティング方式により全ての離散ウェーブレット変換を簡単なフィルタリフティングステップに分解できることに着目し、それぞれのリフティングステップにおいて、その時点での低周波帯域信号から最適なフィルタを選択して適用するデジタル信号処理装置および方式および記憶媒体を提供することを目的とする。

**【0023】**

本発明の第2の目的は、プリスキャンを行わず、画像の局所的な性質に応じて適切なフィルタを適用する、効率の良いサブバンド分解を行うデジタル信号処理装置および方式および記憶媒体を提供することを目的とする。

10

**【0024】****【課題を解決するための手段】**

上述の課題を解決するために本発明の、入力信号系列を低周波帯域の信号と高周波帯域の信号の2つに分解するデジタル信号処理装置は、

入力信号系列を奇数番信号系列と偶数番信号系列に分離する信号系列分離手段と、前記奇数番信号系列と偶数番信号系列の夫々に対してリフティング処理を施すことにより、第1の低周波帯域係数信号列と第1の高周波帯域係数信号列とを生成する第1のフィルタ手段と、

前記2つの信号系列の夫々に対して、前記リフティング処理と異なるフィルタ処理を施すことにより、第2の低周波帯域係数信号列と第2の高周波帯域係数信号列とを生成する第2のフィルタ手段と、

20

前記第1の低周波帯域係数信号列と前記第2の低周波帯域係数信号列のいずれか一方と、前記第1の高周波帯域係数信号列と前記第2の高周波帯域係数信号列のいずれか一方とを適応的に選択して、夫々、低周波帯域係数信号列出力と高周波帯域係数信号列出力として出力する適応的選択手段とを具備することを特徴とする。

**【0029】**

所謂ウェーブレットフィルタ出力の適応的切換が実現される。

**【0030】**

本発明の好適な一態様である請求項2に拠れば、前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理と第2のリフティング処理とを直列に行う。

30

**【0031】**

本発明の好適な一態様である請求項3に拠れば、前記第2のフィルタ手段は、前記奇数番信号系列と偶数番信号系列のいずれか一方を取り出して前記第2の低周波帯域係数信号列とし、前記奇数番信号系列と偶数番信号系列の差分を前記第2の高周波帯域係数信号列として前記適応的選択手段に出力する。

**【0032】**

本発明の好適な一態様である請求項4に拠れば、前記適応的選択手段は、この適応的選択手段による以前の選択結果としての前記低周波帯域係数信号列出力に基づいて、二値領域か多値領域かを判定する。特に、処理時以前に生成される低周波係数値に基づいてフィルタ選択を行うので、プリスキャンや領域判定情報の伝送を必要としないという利点が生まれる。

40

**【0033】**

本発明の好適な一態様である請求項5に拠れば、前記第1のフィルタ手段は、前記奇数番信号系列と偶数番信号系列の夫々に対して、第1のリフティング処理を行う第1リフティング回路と、この第1リフティング回路の後段に設けられ第2のリフティング処理を行う第2リフティング回路とを有し、

前記適応的選択手段は、第1と第2の適応的選択回路を有し、

前記第1の適応的選択回路は、前記第1のリフティング回路の出力に対して適応的選択動作を行い、

50

前記第2のリフティング回路は、前記第1の適応的選択回路によって選択された結果に対して前記第2のリフティング処理を行い、

前記第2の適応的選択回路は、前記第2のリフティング回路によりリフティング処理された結果に対して適応的選択動作を行うことを特徴とする。

【0038】

上記課題は、以下の構成のデジタル信号処理装置によっても達成される。即ち、請求項6に記載の、入力信号系列から所定の周波数帯域の信号を得るデジタル信号処理装置は、入力信号系列を奇数番信号系列と偶数番信号系列に分離する信号系列分離手段と、

前記奇数番信号系列或いは偶数番信号系列にリフティング処理を用いたフィルタ処理を施すことにより、所定の周波数帯域の係数信号列を生成する第1のフィルタ手段と、

前記リフティング処理される信号系列に対して、前記第1のフィルタ手段が用いるリフティング処理とは異なるフィルタ処理を施すことにより、前記所定の周波数帯域の係数信号列を生成する第2のフィルタ手段と

前記第1、第2フィルタ手段で得られる複数の係数信号列のいずれか一方を適応的に選択して出力する適応的選択手段とを具備することを特徴とする。

【0043】

尚、請求項11のように、前記所定の周波数帯域は例えば高周波帯域である。

【0044】

上記の課題は、上述の信号処理装置に組み込まれた信号処理方法、更には、その方法を実現するコンピュータプログラムを記憶する記憶媒体によっても達成される。

【0045】

【発明の実施形態】

第1実施形態

以下、本発明を代表する一実施形態について図面を用いて説明する。

【0046】

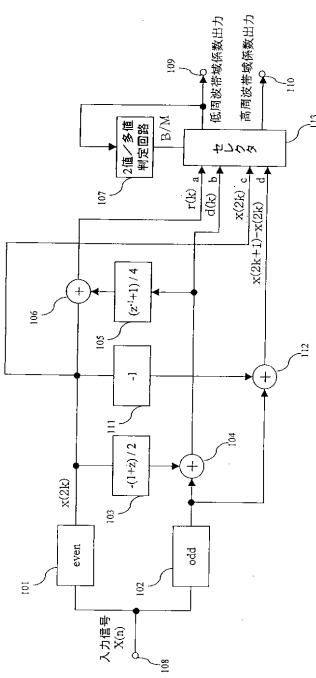

図6は本発明の第1の実施形態を実行するデジタル信号処理装置のブロック図を示したものである。

【0047】

同図に於いて101は偶数番サンプルを取出すサンプリング回路、102は奇数番サンプルを取出すサンプリング回路、103, 105, 111はフィルタ回路、104, 106, 112は加算器、107は2値/多値判定回路、108は信号入力端子、109, 110は信号出力端子、113はセレクタである。

【0048】

図6に示した本実施形態を実行するデジタル信号処理装置は、信号入力端子108から入力される信号 $x(n)$ ( $n$ は0から $2m-1$ までとする)を、適応的に離散ウェーブレット変換し、低周波帯域と高周波帯域における2つの係数(以下、「低周波帯域出力係数」、「高周波帯域出力係数」と呼ぶ)を生成して、夫々を、端子109と110から出力するものである。通常有限の信号系列を離散ウェーブレット変換する場合には信号系列の両端で信号の折り返しが必要になる。ここでは説明を簡略化するため、信号系列両端で必要となる特殊処理は装置外部で行われており、そのように入力信号系列が構成されているものと仮定する。

【0049】

本装置の変換対象画像は、自然画像、2値/多値混在画像、さらに2値画像とする。即ち、自然画像、2値/多値混在画像、さらに2値画像が、順不同に端子108から入力される。尚、2値領域は輝度レベル0か255で構成されるものとする。

【0050】

以下、図6のブロック図を用いて、本実施形態における各部の動作を詳細に説明する。

【0051】

まず、信号入力端子108から入力される信号 $x(n)$ は、偶数番サンプリング回路101と奇数番サンプリング回路102により2つの系列に分けられる。偶数番サンプリング回路

10

20

40

50

101は入力信号 $x(n)$ の偶数番目のサンプル、即ち、 $x(2k)$  ( $k=0 \sim m-1$ )を取り出す。また、奇数番サンプリング回路102は入力信号 $x(n)$ の奇数番目のサンプル、即ち、 $x(2k+1)$  ( $k=0 \sim m-1$ )を取り出す。

【0052】

フィルタ回路103は、

【0053】

[EQ7]

$$-\frac{1+Z}{2}$$

10

【0054】

のフィルタ演算を行う、即ち、偶数番のサンプル系列からの $x(2k)$ と $x(2k+2)$ とを用いて、

[EQ8]

$$-\text{floor}\left\{\frac{x(2k)+x(2k+2)+1}{2}\right\}$$

【0055】

の演算を行い、その演算結果を加算器104に出力する。加算器104は奇数番サンプリング回路102の出力 $x(2k+1)$ とフィルタ回路103の出力([EQ8]の出力)の和を求め出力する。従って、この加算器104の出力は[EQ6]に示す $d(k)$ に等価である。

20

一方、フィルタ回路105は、

【0056】

[EQ9]

$$\frac{Z^{-1}+1}{4}$$

【0057】

の演算を、即ち、加算器104の出力系列から $d(k-1)$ と $d(k)$ を用いて、

[EQ10]

$$\text{floor}\left\{\frac{d(k-1)+d(k)+2}{4}\right\}$$

30

【0058】

を求めて加算器106に出力する。加算器106は、フィルタ回路105の出力と、偶数番サンプリング回路101の出力 $x(2k)$ との和を求め、出力する。この加算器106の出力は[EQ5]に示す $r(k)$ に相当する。図4と比較しても明らかのように、上述のフィルタ103, 105と加算器104, 106による処理は $5 \times 3$ フィルタの演算そのものである。これにより、 $5 \times 3$ フィルタによる低周波帯域の係数 $r(k)$ がセレクタ113の端子aに、高周波帯域の係数 $d(k)$ が同じく端子bに入力される。

一方、フィルタ回路111は、偶数番サンプル系列から $-x(2k)$ を求めて、これを加算器112に出力する。加算器112は、奇数番サンプリング回路102の出力 $x(2k+1)$ とフィルタ回路111の出力 $-x(2k)$ の和を求め、セレクタ113に出力する。これにより、偶数番サンプルと奇数番サンプルの差分がセレクタ113の入力端子dに入力される。一方、サンプリング回路101の出力 $x(2k)$ はセレクタの入力端子cにも供給されている。かくして、セレクタ113が各端子において入力する信号は、

40

【0059】

端子a: フィルタ処理結果の低周波帯域の係数、即ち、 $r(k)$

端子b: フィルタ処理結果の高周波帯域の係数、即ち、 $d(k)$

端子c: 偶数番サンプル、即ち、 $x(2k)$

端子d: 偶数番サンプルと奇数番サンプルの差分、即ち、 $x(2k+1) - x(2k)$

50

となる。

【0063】

セレクタ113は、所謂ホールドタイプのセレクタである。即ち、出力は前回の入力信号を選択した結果を維持することができる。このようなホールドタイプのセレクタは例えばクロック同期のセレクタにより簡単に実現できる。

【0064】

図6の信号処理装置において、セレクタ113の出力端子配列を、109端子に低周波帯域係数出力が、110端子に高周波帯域係数出力が現れるように配置されている。2値/多値判定回路107は、この109端子の低周波帯域係数出力を入力して、信号系列 $x(n)$ の像域判定を行う。判定回路107の出力である像域判定信号B/Mの値が、“1”であれば2値領域であると判断したことを、また、“0”であれば多値領域であると判断したことを示している。像域判定信号B/Mはセレクタ113の動作を制御する。

10

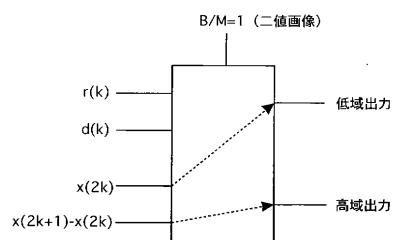

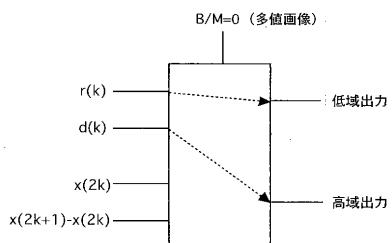

【0065】

図7、図8に、セレクタ113の一般的な動作を示す。即ち、図7に拠れば、判定回路107が二値判定( $B/M=1$ )を出力すれば、入力端子cの信号が出力端子109に現れ、入力端子dの信号が出力端子110に現れる。また、図8に拠れば、判定回路107が多値判定( $B/M=0$ )を出力すれば、入力端子aの信号が出力端子109に現れ、入力端子bの信号が出力端子110に現れる。

【0066】

判定回路107の動作を更に説明する。

20

【0067】

上述のように、セレクタ113の出力は2値/多値判定回路107の出力する像域判定信号B/Mに応じて切り替わる。しかしながら、像域判定信号B/Mが0または1いずれの場合であっても、入力系列が2値領域、即ち、0か255の値しか出現しない場合には、低周波帯域の係数として出力端子109に現れる信号は、次の集合Vの13個の要素のいずれかである。

【0068】

[EQ11]

$$V = \{-64, -32, 0, 32, 64, 96, 128, 159, 191, 223, 255, 287, 319\}$$

【0069】

30

そこで、判定回路107を、低周波帯域の係数値（即ち、端子109の信号）が集合Vに属する値であることが所定の回数だけ連續して起こった場合には、判定信号B/Mを、

【0070】

$B/M = 1$

【0071】

とし、上記事象が認識できていない場合には

$B/M = 0$

【0072】

を出力するように設定する。即ち、判定回路107が2値領域を認識すると、セレクタ113は、入力端子c, dの接続を、それぞれ低周波・高周波帯域の係数として選択し、また、多値領域であると判断した場合には、入力端子a, bの接続を、それぞれ低周波・高周波帯域の係数として選択して出力する。

40

以上の動作により、画像中の2値領域/多値領域に応じてフィルタを選択して作られた低周波帯域係数出力、高周波帯域係数出力が信号出力端子109、信号出力端子110からそれぞれ出力される。

【0073】

第2実施形態

第1実施形態は、 $5 \times 3$ フィルタにより生成した低周波帯域の係数の値に基づいて2値領域・多値領域を判定する方法を採用した。また、ここでの2値領域判定条件は低周波帯域の係数値が所定回数連續してVに属するということを、2値領域判定の条件として採用し

50

ていた。しかしながら、この判定条件のため、変換処理が多値領域から 2 値領域に移っても直ぐには 2 値領域と判定されず、判定の遅れが生じる。

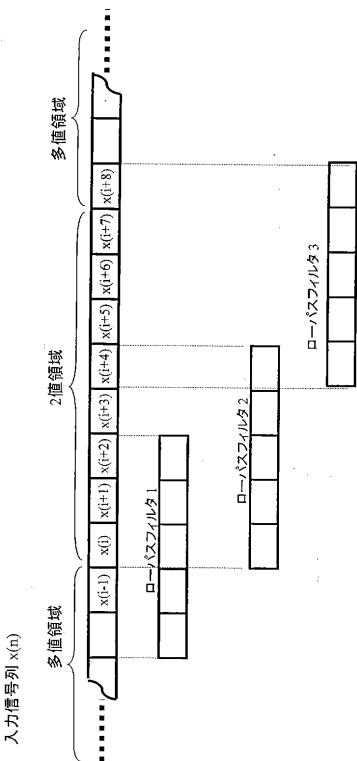

【0074】

判定遅れの例として、図 9 のように変換対象となる系列  $x(n)$  が、ある時点  $n = i$  で多値領域から 2 値領域へ、また、時点  $n = i + 8$  で、2 値領域から多値領域へと推移する場合を考える。

【0075】

5 × 3 フィルタの場合、ローパスフィルタは 5 タップであるため、2 値領域に入った段階では、 $x(i)$ を中心としてフィルタ処理を考えると、図 9 中で、ローパスフィルタ 1 が系列  $x(n)$  を処理することとなり、したがって、端子 109 の低周波帯域出力係数は集合  $V$  に属するとは限らない。フィルタすべてが 2 値領域に属するようになる時点（図中、ローパスフィルタ 2 が系列  $x(n)$  を処理する時点）では、低周波帯域出力係数が  $V$  に属するようになる。この状態が一定回数連続して発生した場合に、第 1 実施形態の判定回路 107 は、2 値領域と判定しているので、実際は 2 値領域であっても多値領域と判定したままとなり、判定の遅れが生じるのである。

【0076】

また、図 9 中において、ローパスフィルタ 3 のように多値領域の信号系列データがかかってしまえば、端子 109 の低周波帯域出力係数は  $V$  に属さなくなる。

したがって、2 値領域が十分に長く連続する場合でなければ、即ち、上記所定回数以上二値領域が連続して発生しなければ、2 値領域判定が有効にならない。

【0077】

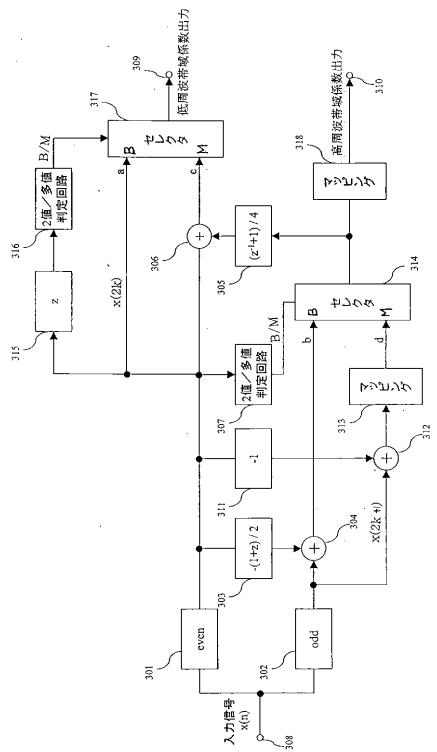

この第 2 実施形態においては、2 値 / 多値判定を各リフティングステップ毎に設け、判定遅れの改善を図ったものである。

【0078】

図 10 は、本発明の第 2 の実施形態を実行するディジタル信号処理装置のブロック図を示したものである。

【0079】

同図に於いて、301 は偶数番サンプリング回路、302 は奇数番サンプリング回路、303, 305, 311 はフィルタ回路、304, 306, 312 は加算器、307, 316 は 2 値 / 多値判定回路、308 は信号入力端子、309, 310 は信号出力端子、313, 318 はマッピング回路、314, 317 はセレクタ、315 は遅延回路である。尚、サンプリング回路 301, 302、フィルタ回路 303, 305, 311 の夫々の単独の動作は、前述の第 1 実施形態のサンプリング回路 101, 102、フィルタ回路 103, 105, 111 と同じである。

【0080】

図 10 に示した第 2 実施形態に係るディジタル信号処理装置は信号入力端子 308 から入力される信号  $x(n)$  ( $n=0 \sim 2m-1$ ) を、適応的に離散ウェーブレット変換し、低周波帯域と高周波帯域の 2 つの係数を生成して、端子 309, 310 から出力するものである。通常、有限の信号系列を離散ウェーブレット変換する場合には信号系列の両端で信号の折り返しが必要になる。第 2 実施形態では、説明を簡略化するため、第 1 実施形態と同じように、信号系列両端で必要な特殊処理は装置外部で行われて、入力信号系列が構成されているものと仮定する。

【0081】

本装置の変換対象画像は、第一の実施形態と同じく、自然画像、2 値 / 多値混在画像、2 値画像とし、2 値領域は輝度レベル 0 か 255 で構成されるものとする。

【0082】

以下、図 3 のブロック図を用いて、第 2 実施形態における各部の動作を詳細に説明する。

【0083】

まず、信号入力端子 308 から入力される信号  $x(n)$  は、偶数番サンプリング回路 301 と奇数番サンプリング回路 302 により 2 つの系列に分けられる。偶数番サンプリング回路

3 0 1 は入力信号  $x(n)$  の偶数番目のサンプル  $x(2k)$  ( $k = 0 \sim m-1$ ) を取り出す。また、奇数番サンプリング回路 3 0 2 は入力信号  $x(n)$  の奇数番目のサンプル  $x(2k+1)$  ( $k = 0 \sim m-1$ ) を取り出す。

【 0 0 8 4 】

フィルタ回路 3 0 3 は、偶数番のサンプル系列から  $x(2k)$  と  $x(2k+2)$  を用いて、

【 0 0 8 5 】

[EQ12]

$$-\text{floor}\left\{\frac{x(2k) + x(2k+2) + 1}{2}\right\}$$

10

【 0 0 8 6 】

の演算を行い、演算結果を加算器 3 0 4 に出力する。加算器 3 0 4 は奇数番サンプリング回路 3 0 2 の出力  $x(2k+1)$  とフィルタ回路 3 0 3 の出力の和を求め出力する。この加算器 3 0 4 の出力は前述の [EQ6] に示す  $d(k)$  に相当する。

一方、フィルタ回路 3 1 1 は偶数番のサンプル系列から  $-x(2k)$  を求めて加算器 3 1 2 に出力する。加算器 3 1 2 はフィルタ回路 3 1 1 の出力値と奇数番サンプリング回路 3 0 2 の出力  $x(2k+1)$  の和（即ち、 $x(2k+1) - x(2k)$ ）を求めて、マッピング回路 3 1 3 に出力する。

【 0 0 8 7 】

加算器 3 1 2 の出力値  $x(2k+1) - x(2k)$  が、集合  $V'$

20

【 0 0 8 8 】

[EQ13]

$$V' = \{-255, 0, 255\}$$

【 0 0 8 9 】

に属するのは、 $x(2k)$ ,  $x(2k+1)$  が共に 0 または 255 である場合のみである。ここで、出力値  $x(2k+1) - x(2k)$  の正負の符号を取り除いても、合成処理側で判断できるため、マッピング回路 3 1 3 で、“ -255 ”を“ 255 ”に置き換えることにより、完全再構成（即ち、ロスレス）の性質を残したまま冗長性を除くことができる。

2 値 / 多値判定回路 3 0 7 は、サンプリング回路 3 1 0 出力の偶数番サンプル  $x(2k)$  を調べ、2 値領域か多値領域かを判断し、判定結果に応じてセレクタ 3 1 4 の動作を制御する。入力系列が 2 値領域の場合、 $x(2k)$  は 0 か 255 の値しか出現しない。そこで、 $x(2k)$  が 0 か 255 である場合には、判定回路 3 0 7 は 2 値領域であると判断して、入力端子  $d$  に入力される信号を選択するように、制御信号 B/M をセレクタ 3 1 4 に出力する。また、上記条件が満たされない場合には、多値領域であると判断して、判定回路 3 0 7 は、入力端子  $b$  から入力される信号を選択して出力するように制御信号 B/M をセレクタ 1 1 3 に送る。

30

【 0 0 9 0 】

セレクタ 3 1 4 は、2 値 / 多値判定回路 3 0 7 からの制御信号 B/M に応じて、入力端子  $b$  から入力される信号か、入力端子  $d$  から入力される信号のいずれか一方を選択して、マッピング回路 3 1 8 並びにフィルタ回路 3 0 5 に出力する。

40

【 0 0 9 1 】

マッピング回路 3 1 8 は、第 2 実施形態を実行するデジタル信号処理装置を、2 次元のウエーブレット変換に用いる場合に必要となるものであって、水平または垂直方向のいずれか一方の方向に既に 1 次元変換を適用して得られた係数（即ち、セレクタ 3 1 4 の出力係数）に、他の方向に再適用する場合のみに機能するもので、セレクタ 3 1 4 の出力係数において、“ 128 ”と“ 255 ”の入れ替えを行う。この操作により M S B プレーンに 2 値情報が集められるため、伝送の早期段階での 2 値領域の再生画質向上を図ることができる。

【 0 0 9 2 】

フィルタ回路 3 0 5 は、第 1 実施形態と同じように、セレクタ 3 1 4 の出力系列から  $d(k)$

50

- 1 )とd(k)を用いて、

【 0 0 9 3 】

[EQ14]

$$\text{floor}\left\{\frac{d(k-1) + d(k) + 2}{4}\right\}$$

【 0 0 9 4 】

を求めて加算器 3 0 6 に出力する。加算器 3 0 6 は、フィルタ回路 3 0 5 の出力と偶数番サンプリング回路 3 0 1 の出力x(2k)の和を求め、セレクタ 3 1 7 の入力端子 c に出力する。

10

一方、遅延回路 3 1 5 は偶数番サンプリング回路 3 0 1 の出力x(2k)を遅延させ、x(2k-2)を2値 / 多値判定回路 3 1 6 に出力する。2値 / 多値判定回路 3 1 6 は遅延回路 3 1 5 の出力するx(2k-2)の値を調べ、x(2k-2)の値が“0”か“255”である場合には、2値領域であると判断して、入力端子 a で入力される信号を選択して出力するよう制御信号B/Mをセレクタ 3 1 7 に送る。また、この条件が満たされない場合には多値領域であると判断して、入力端子 c から入力される信号を選択して出力するよう制御信号B/Mをセレクタ 3 1 7 に送る。セレクタ 3 1 7 は2値 / 多値判定回路 3 1 6 からの制御信号に応じて、入力端子 a から入力される信号か、入力端子 c から入力される信号のいずれか一方を選択して出力する。

【 0 0 9 5 】

20

以上の動作により、画像中の2値領域 / 多値領域に応じてフィルタを選択して作られた低周波帯域係数出力と高周波成分帯域係数出力とが、夫々、信号出力端子 3 0 9 、信号出力端子 3 1 0 から出力される。

【 0 0 9 6 】

上記第1実施形態及び第2実施形態では、その信号処理回路の出力を2つとし、一方を低周波帯域係数出力と、他方を高周波帯域係数出力とした。この結果、第1実施形態と第2実施形態の信号処理回路を、従来の図4の信号処理回路を用いている回路基板において、その従来の信号処理回路の代わりに置き換えることができる。

【 0 0 9 7 】

30

なお、第1実施形態と第2実施形態による分解処理に対応する合成処理は上述の処理を逆順に行うものであり、図5に示した従来の合成処理からも容易にわかるので説明を省略する。

【 0 0 9 8 】

その他の実施形態

本発明は上述した実施形態に限定されるものではない。

【 0 0 9 9 】

上述の第1、第2実施形態では、低周波帯域出力係数と高周波帯域出力係数の両方を選択する構成を説明したが、本発明はこれに限られず、高周波帯域出力係数のみ、或いは低周波帯域出力係数のみを選択出力するように変更することも可能である。

【 0 1 0 0 】

40

例えば第1、第2の実施形態に於いては、 $5 \times 3$  フィルタをベースとした適応的離散ウェーブレット変換を示したが、 $2 \times 10$  ,  $2 \times 6$  ,  $9 \times 7$  フィルタといった、その他のフィルタをベースとして適応的な離散ウェーブレット変換を構成しても全く構わない。

【 0 1 0 1 】

また、変換対象の画像は1画素8ビットの画像であるとして説明したが、8ビット以上の画像にも適用しても構わないことは言うまでもない。同様にカラー画像への適応、静止画像以外でも音声信号、動画像への適用も本発明の範疇に含まれる。

【 0 1 0 2 】

また、上述の実施形態においては2値 / 多値領域判定をベースとしてフィルタ処理の切り替えを行ったが、本発明はこれに限定されるものでなく、その他、例えば、低周波帯域の

50

係数の分散によってフィルタを切り替えたり、係数値の連続性に着目してフィルタの切り替えを行っても構わない。

#### 【0103】

なお、本発明は複数の機器（例えばホストコンピュータ、インターフェース機器、リーダ、プリンタ等）から構成されるシステムの一部として適用しても、1つの機器（例えば複写機、ファクシミリ装置、デジタルカメラ等）からなる装置の1部に適用してもよい。

#### 【0104】

また、本発明は上記実施形態を実現するための装置及び方法のみに限定されるものではなく、上記システム又は装置内のコンピュータ（C P UあるいはM P U）に、上記実施形態を実現するためのソフトウェアのプログラムコードを供給し、このプログラムコードに従って上記システムあるいは装置のコンピュータが上記各種デバイスを動作させることにより上記実施形態を実現する場合も本発明の範疇に含まれる。

10

#### 【0105】

またこの場合、前記ソフトウェアのプログラムコード自体が上記実施形態の機能を実現することになり、そのプログラムコード自体、及びそのプログラムコードをコンピュータに供給するための手段、具体的には上記プログラムコードを格納した記憶媒体は本発明の範疇に含まれる。

#### 【0106】

この様なプログラムコードを格納する記憶媒体としては、例えばフロッピーディスク、ハードディスク、光ディスク、光磁気ディスク、C D - R O M、磁気テープ、不揮発性のメモリカード、R O M等を用いることができる。

20

#### 【0107】

また、上記コンピュータが、供給されたプログラムコードのみに従って各種デバイスを制御することにより、上記実施形態の機能が実現される場合だけではなく、上記プログラムコードがコンピュータ上で稼動しているO S（オペレーティングシステム）、あるいは他のアプリケーションソフト等と共同して上記実施形態が実現される場合にもかかるプログラムコードは本発明の範疇に含まれる。

#### 【0108】

更に、この供給されたプログラムコードが、コンピュータの機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに格納された後、そのプログラムコードの指示に基づいてその機能拡張ボードや機能拡張ユニットに備わるC P U等が実際の処理の一部または全部を行い、その処理によって上記実施形態が実現される場合も本発明の範疇に含まれる。

30

#### 【0109】

#### 【発明の効果】

以上説明した様に本発明によれば、離散ウェーブレット変換を簡単なフィルタリフティングステップに分解して実装し、それぞれのリフティングステップにおいて、各時点での低周波帯域信号から最適なフィルタを選択して適用することにより、ブリスキャンを行わず、画像の局所的な性質に応じた効率の良いサブバンド分解を行うデジタル信号処理装置および方式および記憶媒体を実現することができる。

40

#### 【図面の簡単な説明】

【図1】 一般的な2次元離散ウェーブレット変換の対象となる画像の一例を示す図である。

【図2】 図1の画像を低周波帯域と高周波帯域との分解した様子を模式的に示す図である。

【図3】 図2の分解された画像を更に分解する様子を模式的に示す図である。

リフティングを用いた $5 \times 3$ フィルタによる分解処理のブロック図である。

【図4】 従来技術に係る、リフティングを用いた $5 \times 3$ フィルタによる合成処理のブロック図である。

【図5】 図の処理回路により変換された信号系列を復元する処理のブロック図である。

50

【図 6】 本発明に係わる第 1 の実施形態の信号処理装置のブロック図である。

【図 7】 第 1 の実施形態の信号処理装置に用いられているセレクタの動作を示す図である。

【図 8】 第 1 の実施形態の信号処理装置に用いられているセレクタの動作を示す図である。

【図 9】 第 1 実施形態の領域判定の遅れを示す図である。

【図 10】 本発明に係わる第 2 の実施形態の信号処理装置のブロック図である。

【符号の説明】

108, 507, 308 信号入力端子

101, 501, 301 偶数番サンプリング回路

10

102, 502, 302 奇数番サンプリング回路

103, 105, 111, 503, 505, 303, 305, 311 フィルタ回路

104, 106, 112, 504, 506, 304, 306, 312 加算器

107, 307, 316 2 値 / 多値判定回路

113, 314, 317 セレクタ

315 遅延回路

313, 318 マッピング回路、

109, 110, 508, 509, 309, 310 信号出力端子

【図 1】

変換対象画像

【図 2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

---

フロントページの続き

(72)発明者 加藤 茂夫

栃木県宇都宮市西川田南1-31-12

(72)発明者 宮道 壽一

埼玉県久喜市中央1-15-4

審査官 北村 智彦

(56)参考文献 特開平11-103460 (JP, A)

国際公開第98/024053 (WO, A1)

国際公開第98/054675 (WO, A1)

特表2003-505967 (JP, A)

特開2000-312361 (JP, A)

特開2000-341693 (JP, A)

特開2000-197052 (JP, A)

特開2000-040943 (JP, A)

特開2000-244743 (JP, A)

Minbo Shim, Andrew Laine, Overcomplete Lifted Wavelet Representation for Multiscale Feature Analysis, Image Processing, 1998. ICIP 98. Proceedings., 1998年10月, Vol.2, p. 242-246

Roger L. Claypoole, Jr., Richard G. Baraniuk, Robert D. Nowak, LIFTING CONSTRUCTION OF NON-LINEAR WAVELET TRANSFORMS, Time-Frequency and Time-Scale Analysis, 1998. Proceedings., 1998年10月, p.49-52

貴家仁志、小林弘幸, 整数ウェーブレットの設計とそのリフティング構成, 電子情報通信学会技術研究報告, 1998年12月10日, Vol.98, No.450, DSP98-123, p.45-51

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03M3/00-11/00

H04N 7/30