(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-167184

(P2005-167184A)

(43) 公開日 平成17年6月23日(2005.6.23)

(51) Int.Cl.<sup>7</sup>

**H01L 21/822**

**H01L 21/82**

**H01L 27/04**

**H03K 3/037**

**H03K 3/356**

F 1

H01L 27/04

H03K 3/037

H01L 27/04

H01L 21/82

D

B

A

A

D

5 F 03 8

5 F 06 4

5 J 03 4

5 J 04 3

5 J 05 6

審査請求 未請求 請求項の数 23 O L (全 43 頁) 最終頁に続く

(21) 出願番号 特願2004-185475 (P2004-185475)

(22) 出願日 平成16年6月23日 (2004. 6. 23)

(31) 優先権主張番号 特願2003-384237 (P2003-384237)

(32) 優先日 平成15年11月13日 (2003.11.13)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 菅野 雄介

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 水野 弘之

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 入江 直彦

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置

## (57) 【要約】

【課題】電源遮断時にそれ以前の情報を保持する低消費電力モードにおいてその復帰を高速にする。その一つに従来のデータ保持型フリップフロップを用いることが考えられるが、そのためにセルを大きくする等の面積オーバーヘッドが生じるのは望ましくない。

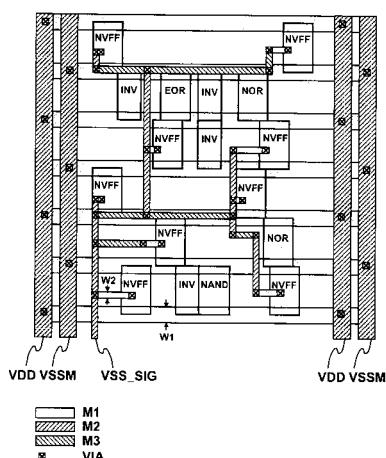

図 1

【解決手段】電源遮断時のデータ保持のための電源線は一般的の電源幹線よりも細い配線にて形成する。望ましくは、データ保持回路の電源を信号線扱いとして、自動配置配線時に配線することである。のために、セルにはあらかじめ上記データ保持回路用電源のための端子を通常の信号線と同様に設けて設計しておく。

【効果】セルに余分な電源線のレイアウトが不要となり省面積化が図られるとともに、既存の自動配置配線ツールにより設計が可能となる。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

複数のフリップフロップと、上記複数のフリップフロップの出力ノードに接続される複数の論理回路と、第1乃至第3電源線とを有する半導体集積回路装置であって、

上記フリップフロップは、その出力ノードが上記フリップフロップの出力ノードに接続された第1ラッチ回路と、その入力ノードが上記第1ラッチ回路の出力ノードまたは入力ノードに接続された第2ラッチ回路とを有し、

上記第1ラッチ回路及び上記論理回路の動作電圧は、上記第1及び上記第2電源線により供給され、

上記第2ラッチ回路の動作電圧は、上記第1及び上記第3電源線により供給され、

10

上記第1及び第2電源線は第1の配線幅を有し、

上記第3電源線は第2の配線幅を有し、

上記第2のラッチ回路の入力ノードと上記第1のラッチ回路の出力ノードまたは入力ノードと接続する配線は第3の配線幅を有し、

上記第1の配線幅と上記第2の配線幅の差は、上記第2の配線幅と上記第3の配線幅の差よりも大きい半導体集積回路装置。

**【請求項 2】**

請求項1において、

上記半導体集積回路装置は第1モードと第2モードとを有し、

上記第1モードにおいて上記論理回路及び上記フリップフロップの動作電圧が供給され、

20

上記第2モードにおいて上記論理回路及び上記フリップフロップの上記第1ラッチ回路の動作電圧の供給が停止され、上記フリップフロップの上記第2ラッチ回路の動作電圧の供給が継続される半導体集積回路装置。

**【請求項 3】**

請求項2において、

上記第1電源線と上記第3電源線との間にソース・ドレイン経路を有する第1MISFETを有し、

上記第1MISFETは上記第1モードにおいてはオン状態に制御され、上記第1MISFETは上記第2モードにおいてはオフ状態に制御される半導体集積回路装置。

30

**【請求項 4】**

請求項3において、

上記第1ラッチ回路及び上記論理回路は第2MISFETを含み、

上記第2ラッチ回路は第3MISFETを含み、

上記第3MISFETのしきい値電圧の絶対値は上記第2MISFETのしきい値電圧の絶対値よりも大きい半導体集積回路装置。

**【請求項 5】**

請求項4において、

上記第1MISFETのしきい値電圧の絶対値は上記第3MISFETのしきい値電圧よりも大きい半導体集積回路装置。

40

**【請求項 6】**

請求項2において、

上記第2ラッチ回路と上記第2電源線とを接続する第4MISFETを有し、

上記第1モードにおいて上記第4MISFETがオンとなり、上記第2モードにおいて上記第4MISFETがオフとなる半導体集積回路装置。

**【請求項 7】**

請求項6において、

上記第2ラッチ回路と上記第3電源線とを接続する第5MISFETを有し、

上記第1モードにおいて上記第5MISFETがオフとなり、上記第2モードにおいて上記第5MISFETがオンとなる半導体集積回路装置。

50

**【請求項 8】**

請求項 1 において、

上記第 2 モードにおいて上記第 2 ラッチに供給される動作電圧は、上記第 1 モードにおいて上記第 2 ラッチに供給される動作電圧よりも低くされる半導体集積回路装置。

**【請求項 9】**

請求項 1 において、

上記第 2 ラッチは容量素子を有する半導体集積回路装置。

**【請求項 10】**

第 1 方向に延在する第 1 導電型の第 1 ウェルと、

上記第 1 ウェルに隣接して設けられ、上記第 1 方向に延在する第 2 導電型の第 2 ウェル 10

と、

上記第 1 ウェルの上層に設けられ、上記第 1 方向に延在し、第 1 電位を供給するための第 1 電源線と、

上記第 2 ウェルの上層に設けられ、上記第 1 方向に延在し、上記第 1 電源線と同層に設けられた第 2 電位を供給するための第 2 電源線と、

上記第 1 ウェルに形成される第 2 導電型の第 1 M I S F E T と上記第 2 ウェルに形成される第 1 導電型の第 2 M I S F E T とで構成される第 1 C M O S 回路と、

上記第 1 ウェルに形成される第 2 導電型の第 3 M I S F E T と上記第 2 ウェルに形成される第 1 導電型の第 4 M I S F E T とで構成される第 2 C M O S 回路とを有し、

上記第 1 C M O S 回路の上記第 1 M I S F E T のソース電位は上記第 1 電源線により供給され、上記第 1 C M O S 回路の上記第 2 M I S F E T のソース電位は上記第 2 電源線より供給され、

上記第 2 C M O S 回路の上記第 3 M I S F E T のソース電位は上記第 1 電源線により供給され、上記第 4 M I S F E T のソース電位は第 3 電源線により供給され、

上記第 3 電源線は、上記第 1 電源線及び上記第 2 電源線と同層または下層にあって、その線幅と上記第 1 電源線もしくは上記第 2 電源線の線幅との差が、上記第 1 電源線と上記第 2 電源線との線幅の差よりも大きい部分を有する半導体集積回路装置。

**【請求項 11】**

請求項 10 において、

上記第 1 電源線に接続され、上記第 1 方向と交差する第 2 方向に延在する複数の第 1 電源強化線を有し、

上記複数の第 1 電源強化線のうち、隣接する第 1 電源強化線の間に上記第 1 M I S F E T 乃至第 4 M I S F E T が配置され、

上記第 3 電源線は、上記第 2 方向に延在する部分を有する半導体集積回路装置。

**【請求項 12】**

請求項 10 において、

上記第 2 電源線に接続され、上記第 1 方向と交差する第 2 方向に延在する複数の第 2 電源強化線を有し、

上記複数の第 2 電源強化線のうち、隣接する第 2 電源強化線の間に上記第 1 M I S F E T 乃至第 4 M I S F E T が配置され、

上記第 3 電源線は、上記第 2 方向に延在する部分を有する半導体集積回路装置。

**【請求項 13】**

請求項 10 において、

上記第 3 電源線は上記第 1 電源線及び上記第 2 電源線と平行に設けられる半導体集積回路装置。

**【請求項 14】**

請求項 10 において、

上記半導体集積回路装置は、複数のフリップフロップと、上記複数のフリップフロップの出力ノードに接続される複数の論理回路とを有し、

上記フリップフロップは、その出力ノードが上記フリップフロップの出力ノードに接続

20

30

40

50

された第1ラッチ回路と、その入力ノードが上記第1ラッチ回路の出力ノードまたは入力ノードに接続された第2ラッチ回路とを有し、

上記第1ラッチ回路及び上記論理回路は上記第1CMOS回路により構成され、

上記第2ラッチ回路は上記第2CMOS回路により構成される半導体集積回路装置。

#### 【請求項15】

請求項10において、

上記第3MISFETのしきい値電圧の絶対値は上記第1MISFETのしきい値電圧の絶対値よりも大きく、

上記第4MISFETのしきい値電圧の絶対値は上記第2MISFETのしきい値電圧の絶対値よりも大きい半導体集積回路装置。 10

#### 【請求項16】

複数のフリップフロップ及び上記複数のフリップフロップと接続される複数の論理回路を含み第1動作モードと第2動作モードとを有する論理回路ブロックと、上記論理回路ブロックに供給するクロック信号を生成するクロック生成回路とを有する半導体集積回路装置であって、

上記フリップフロップは、

その出力ノードが上記フリップフロップの出力ノードに接続される第1ラッチ回路と、

その入力ノードが上記第1ラッチ回路の入力ノードまたは出力ノードに接続された第2ラッチ回路と、 20

上記フリップフロップの入力ノードと上記第1ラッチ回路の入力ノードとの間に設けられた伝送ゲートとを有し、

上記第1動作モードでは、上記第1ラッチ回路及び上記論理回路に第1動作電圧が供給され、上記第2ラッチ回路に第2動作電圧が供給され、上記クロック生成回路は上記伝送ゲートに上記クロック信号を供給し、

上記第2動作モードでは、上記第1ラッチ回路及び上記論理回路への上記第1動作電圧の供給が停止され、上記第2ラッチ回路に上記第2動作電圧が供給され、上記クロック生成回路は上記伝送ゲートへの上記クロック信号の供給を停止し、

上記第2動作モードから上記第1動作モードへの移行時には、上記フリップフロップの第1ラッチ回路の上記第1動作電圧が所定のレベルに達した後、上記伝送ゲートへの上記クロック信号の供給が開始される前、所定期間上記伝送ゲートをオフとし、 30

上記所定期間において、上記第2ラッチ回路のデータを上記第1ラッチ回路に書き戻す半導体集積回路装置。

#### 【請求項17】

請求項16において、

上記第1ラッチ回路のノードと上記第2ラッチ回路の入力ノードとの間に上記第2動作電源が供給されるクロックトインバータを有し、

上記第2動作モードにおいて、上記クロックトインバータは遮断される半導体集積回路装置。 40

#### 【請求項18】

請求項16において、

上記第1モードにおける上記第2ラッチ回路への電流供給量が、上記第2モードにおける上記第2ラッチ回路への電流供給量よりも大きくなるように制御する半導体集積回路装置。

#### 【請求項19】

請求項16において、

上記第2モードにおける上記第2動作電圧は、上記第1モードにおける上記第2動作電圧よりも低くされる半導体集積回路装置。

#### 【請求項20】

請求項16において、 50

上記第2ラッチは容量素子を有する半導体集積回路装置。

【請求項21】

請求項16において、

上記第1ラッチ回路及び上記論理回路は第1MISFETを含み、

上記第2ラッチ回路は第2MISFETを含み、

上記第2MISFETのしきい値電圧の絶対値は上記第1MISFETのしきい値電圧よりも大きい半導体集積回路装置。

【請求項22】

請求項16において、

上記第1動作電圧は、第1及び第2電源線により供給され、

10

上記第2動作電圧は、上記第1電源線及び第3電源線により供給され、

上記第1電源線は第1の配線幅を有し、

上記第2電源線は第2の配線幅を有し、

上記第3電源線は第3の配線幅を有し、

上記第1の配線幅と上記第3の配線幅の差は、上記第1の配線幅と上記第2の配線幅の差よりも大きい半導体集積回路装置。

【請求項23】

請求項22において、

上記第1ラッチ回路の入力ノードまたは出力ノードと上記第2ラッチ回路の入力ノードとを接続する配線は第4の配線幅を有し、

20

上記第1の配線幅もしくは上記第2の配線幅と上記第3の配線幅との差は、上記第4の配線幅と上記第3の配線幅との差よりも大きい半導体集積回路装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体集積回路装置に関するものであり、特にシステムLSI又はマイクロプロセッサに適用して有用なものである。

【背景技術】

【0002】

携帯電話に代表される携帯情報端末向けのシステムLSIでは、限られたバッテリ容量で長時間動作させる要求が従来に増して高まっている。特に、携帯電話では長時間の待ち受け（電源はオンしているが高負荷な処理は実行されていない状態）時間における低消費電力化が長時間動作の要求を満たすために非常に重要である。その一つの方法として、待機状態にはシステムLSI内の全クロックを停止する方法（ソフトウェア・スタンバイと呼ばれる）がある。ソフトウェア・スタンバイは待機状態に入るヒステムLSI内部のクロックが停止するため、システムLSI内の回路動作による消費電流がほぼ0となる。その結果、待機状態のスタンバイ電流はトランジスタのリーク電流による消費電流のみにできる。

【0003】

しかし、最先端の微細プロセスを用いた絶縁ゲート型電界効果型トランジスタ（本出願ではMISFETを絶縁ゲート型電界効果型トランジスタの呼称として用いる）を用いる場合、電源電圧の低電圧化に応じたトランジスタのしきい値電圧の低下に起因するサブスレッショルド・リーク電流や、MISFETのゲート絶縁膜厚の薄膜化に起因するゲートトンネルリーク電流に代表される、各種のリーク電流が非常に大きい。これらのスタンバイ電流により電力を消費してしまう結果、長い待ち受け時間を達成することができない。

【0004】

このような状況を鑑みて、待ち受け時にシステムLSIの電源を遮断する方法（Uスタンバイと呼ばれる）が非特許文献1に提案されている。Uスタンバイでは待ち受け状態に入ると復帰処理に必要な最低限の回路を除いて電源が遮断される。その結果、回路動作による消費電流のみでなく、漏れ電流による消費電流もほぼ0となり、スタンバイ電流をほ

40

50

ぼ〇にできる。

#### 【0005】

これに対して、待機状態からの復帰時間に着目して両者を比べると以下のようになる。まず、ソフトウェア・スタンバイでは、システムLSIの内部状態（レジスタの値など）を待機状態でも保持できるため、待機状態から割り込み処理で復帰することが可能である。そのため、復帰に要する時間はクロック再開に必要な時間程度であり、高速に復帰できる。これに対して、Uスタンバイでは電源の遮断によりシステムLSIの内部状態が破壊されるため、割り込み処理のみでは待機状態からの復帰ができず、復帰のためにはリセット処理が必要である。リセット処理はシステムLSIの初期設定や動作に必要なソフトウェアの立ち上げを含み、長い時間が必要である。ソフトウェアの立ち上げは実行すべき命令数が多いため、特に処理時間が長い。Uスタンバイから復帰する場合は、割り込み要求に対してそのまま割り込み処理を行うわけではなく、一旦リセット処理してソフトウェアが立ち上がった後に割り込み要求に応じた処理をすることになる。

#### 【0006】

非特許文献2または非特許文献3に示されるように、待機状態において電源遮断された回路ブロック内的一部のデータ保持回路には電源を供給し、待機状態においても情報を保持することが提案されている。具体的には、回路ブロック内のフリップフロップに待機状態でも電源が供給されるラッチ回路を設け、そのラッチ回路により電源遮断時においても内部情報を保持することにより、高速に元の状態に復帰することを可能としている。

【非特許文献1】T. Yamada et al., "A 133MHz 170mW 10µA Standby Application Processor for 3G Cellular Phones", ISSCC 2002, February, pp.370-371

【非特許文献2】S. Mutoh, et al., "A 1V Multi-Threshold Voltage CMOS DSP with a Efficient Power Management Technique for Mobile Phone Application", ISSCC 1996, February, pp. 168-169

【非特許文献3】V. Zyuban, et al., "Low Power Integrates Scan-Retention Mechanism", ISLPED 2002, August, pp.98-102

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

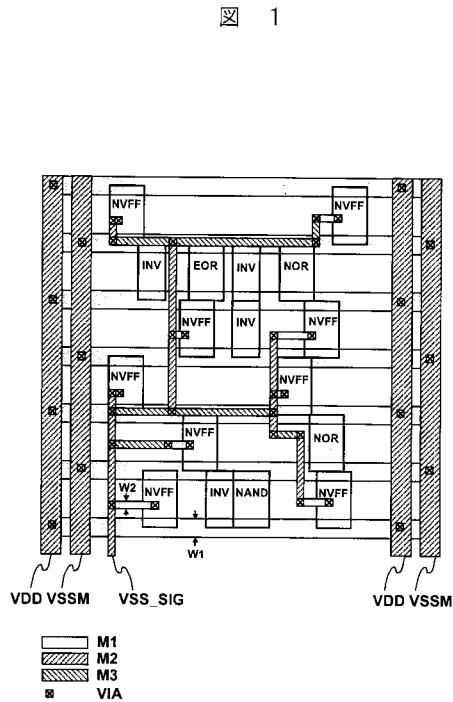

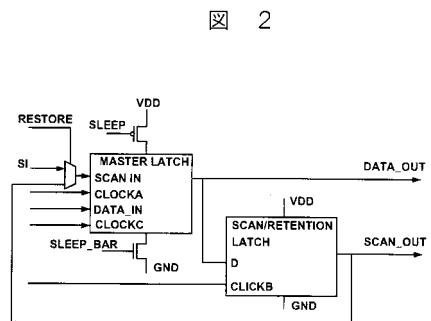

本願発明者らは、背景技術に示すようなデータ保持回路について検討したところ、以下のような課題があることに気が付いた。図2に非特許文献3に開示されるデータ保持型フリップフロップの構成図を示す。これは待機時にメインのラッチ部（MASTER LATC H）の電源を遮断し、常時通電されるサブのラッチ部（SCAN/RETENTION LATC H）で待機時の情報を保持する構成である。メインのラッチ部及びそれらに接続される組合せ回路の電源は電源スイッチを介して図示しない仮想電源線に接続されており、電源線（VDD, GND）のほかにメインのラッチ部及びそれらに接続される組合せ回路が直接接続される仮想電源線が必要になることを示している。そのため、図3に示す回路構成をレイアウトするには、電源線は少なくともVDD、VSS、仮想電源線の3本必要であり（電源スイッチをVDD側またはVSS側の一方とした場合）、ひとつのセルに少なくとも3本の電源線がレイアウトされなくてはならなくなることを見出した。

#### 【0008】

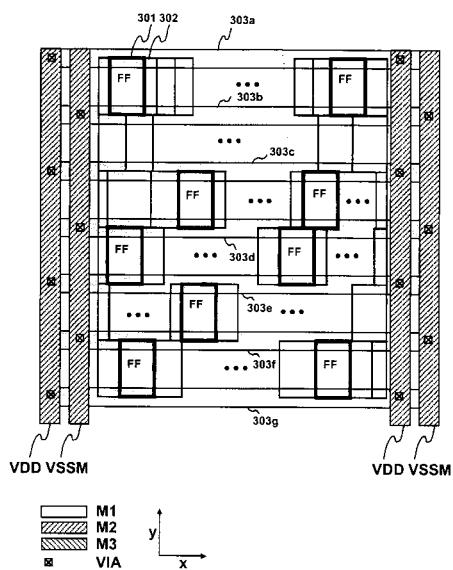

これは、一般的なシステムLSIが、CADを用いた自動配置配線によりスタンダードセル（以下、セルという）を配列してレイアウトしていることに起因する。図3はセルを配列して構成した集積回路のレイアウトを示す図である。ただし、セルと電源幹線のみを示し、信号配線等は省略している。矩形301、302がセルである。各セルには、インバータ、NAND等の基本論理を実現する回路が実装される。これらのセルを敷き詰め、互いに配線することにより所望の論理回路を実現する。セルが実現する基本論理に応じてその回路規模は異なるが、セルの高さ（y方向）は揃え、回路規模に応じてセルの幅（x方向）を異ならせるのが一般的である。これは電源幹線のレイアウトをメッシュ状に行うことによる起因している。すなわち、メタル第1層にx方向に伸びる電源線303a～gをほ

ば等間隔で配置して回路動作に必要な電源を供給するため、電源幹線のレイアウトとセルのレイアウトとを整合させたものである。

#### 【0009】

このようなレイアウト設計環境の下では、電源線と仮想電源線の双方の配線が必要になるセルが一部のセル（フリップフロップ）に過ぎなくても、他の電源遮断時にデータを保持する必要のないセル（例えば、インバータ、NAND回路等）にもあまねく電源線と仮想電源線とを配線することが必要になる。そのため、仮想電源線と同じ電源線をさらにメタル第1層にレイアウトするならば、セルの高さが大きくなり、全体のレイアウトに与える影響が無視できなくなってしまうであろう。逆に、信号線の配線チャネルを流用することでセルの高さを固定したまま電源線をさらにレイアウトするとすれば、信号配線の自由度が極端に削減されてしまう懸念もある。

10

#### 【0010】

このように分散配置されるフリップフロップセルに電源遮断時にもデータを保持させ、かつ現在のレイアウト設計環境の下で回路面積のオーバーヘッドを抑制するレイアウトについては検討されていなかった。

#### 【課題を解決するための手段】

#### 【0011】

本発明では、電源遮断時にデータを保持するデータ保持回路には通常動作時に要求される大きな電流供給能力は必要としないことに着目し、一般的電源幹線よりも細い電源線により動作電圧を供給することとした。望ましくは、データ保持回路の電源線を信号線扱いとして、自動配置配線時に配線することである。これによりCADによるレイアウト設計環境に適合させることができる。この場合、セルにはあらかじめデータ保持回路用電源の端子を通常の信号線端子と同様に設けておく。これにより、セルに電源線のための余分なレイアウトが不要となり省面積化が図られることに加えて、既存の自動配置配線ツールにより設計が可能となる。

20

#### 【発明の効果】

#### 【0012】

電源遮断からの復帰時間が大幅に短縮できるとともに、そのための回路面積へのオーバーヘッドを少なくして実現することができる。

30

#### 【発明を実施するための最良の形態】

#### 【0013】

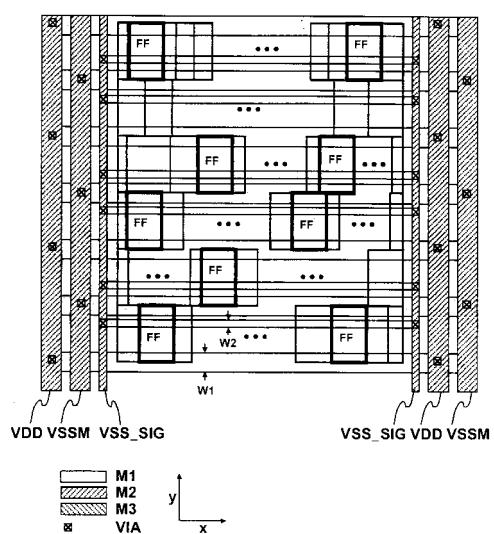

図1は本発明を適用したチップの配線レイアウトイメージを示す実施例である。この図には通常の電源幹線、すなわち電源線VDD（たとえば1.2V）および仮想電源線VSSM（0V）と、不揮発フリップフロップNFFF（以下、不揮発FFとする）の情報保持回路用電源VSS\_SIG（0V）を配線した例を示している。この例では、待機時には接地側（低電位側）の電源線を遮断制御することを想定しているため、低電位側の電源線が仮想電源線VSSMとなっている。自動配置配線ツールでは、仮想電源線VSSMがセルの実質的な接地線として扱われる。この図に示されるように、配線VSS\_SIGは、自動配置配線ツールにより回路ブロックに分散して配置されている不揮発FF\_NVFFの端子に、任意の経路で、また、任意の配線層を用いて接続されている。

40

#### 【0014】

このように配線VSS\_SIGを配線することで、インバタ回路やNAND回路などの各機能回路（セル）のレイアウト寸法を変えることなく、既存のフリップフロップセルを不揮発FFセルに置き換えて自動配置配線することでレイアウトできるので容易に設計することができるようになる。

#### 【0015】

ここで、所定の配線層における配線幅（図ではメタル第1層M1）を比較する。電源幹線の配線幅をW1、情報保持回路用電源VSS\_SIGの配線幅をW2、図示しない信号配線（セルの入出力端子に接続される配線をいう）の配線幅をW3とすると、W1 > W2 = W3の関係が成立する。配線幅のプロセスばらつきを考慮すれば、(W1 - W2) > (

50

W<sub>3</sub> - W<sub>2</sub>) の関係が成立する。

【0016】

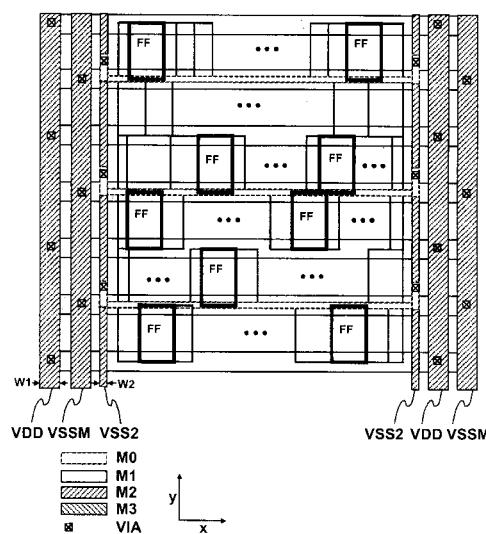

図4及び図5は別の配線レイアウトの例である。この例では配線接続の自由度は図1の実施例には及ばないが、配線チャネルに余裕がある場合には単純にレイアウトできる利点がある。特徴は、情報保持回路用電源VSS\_SIGが電源幹線よりも電流供給能力が小さくてよいことに着目し、情報保持回路用電源VSS\_SIGの配線幅を電源幹線よりも細くすることで、新たな配線による面積オーバーヘッドを抑制させるレイアウトである。図4では、電源幹線に比較して線幅の細い情報保持回路用電源VSS\_SIGを電源幹線と同層に平行させて配置する。これにより、セルの高さを高くする必要がある場合がある。一方、図5では、電源幹線に比較して線幅の細い情報保持回路用電源VSS\_SIGを電源幹線M1の下層(例えば、メタル第0層M0)に配置する。これにより配線チャネルを消費せずに済み、セル高さを高くしなくてもよい。したがって、図5のレイアウトは図4のレイアウトよりもコンパクトになりうるが、一般的にM0はメタルの材質が異なる場合が多く、その配線抵抗が高くなるおそれはある。図5のタイプの配線形態は、回路の基板電極を電源線と独立させて制御する、いわゆる基板バイアス制御においては公知の配線方法である。この場合も、電源幹線の配線幅をW1、情報保持回路用電源VSS\_SIGの配線幅をW2、図示しない信号配線の配線幅をW3とすると、(W1-W2) > (W3-W2)の関係が成立する。

【0017】

このように、不揮発FFN V F Fの情報保持回路用電源を従来の電源幹線とは異なる方法で配線できる理由を詳細に説明する。一般に電源幹線は、機能ブロックを構成するMISFETの速度を維持するため低抵抗化する必要がある。そのため、電源幹線は図3に示すようにメッシュ状に配線される。ところが、不揮発FFN V F Fの電源遮断時に供給すべき電源は待機時のリーク電流分が供給できるだけでよいため、配線の高抵抗化はそれほど問題にはならない。たとえば、待機時に一つの不揮発FFN V F Fのデータを保持するために必要なMISFETの大きさをゲート幅で1ミクロンとし、構成するMISFETの常温(25)で単位幅(1μm)あたり1nA流すためのゲート電圧を0.15Vと仮定すると、不揮発FFN V F F一個当たりの待機時のリーク電流は30pA程度である。チップ内のフリップフロップの割合を4000個/mm<sup>2</sup>と仮定して7mm×7mmのチップを考えると全不揮発FFN V F Fの総数は196,000個となり、全リーク電流は6μA程度となる。製造ばらつき(しきい値ばらつき100mVとする)と高温度(45)とを仮定してこれより1.5桁多いと仮定しても180μA程度となる。必要なのはこの程度の電流であるため、不揮発FFN V F Fの電源遮断時データ保持用の電源線は一般的の電源幹線構造を用いなくてもよいのである。

【0018】

ただし、さらに80のような高温時には、DC電流が増加するため微細配線ではエレクトロ・マイグレーションが危惧される。この場合でも個々のセルに必要な電流は依然として少ないため、多量の電流が流れるスタンバイ回路STBYC側の分岐元配線の配線幅を太くしたり、当該箇所のスルーホールの数を増やしたりすることで対策できる。図4、図5のレイアウトでは縦方向に延在する電源強化線を太くすることで対策できる。

【0019】

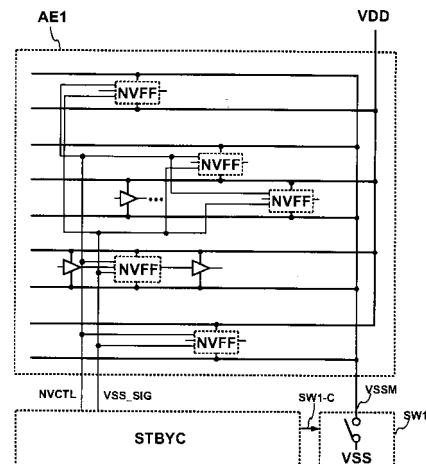

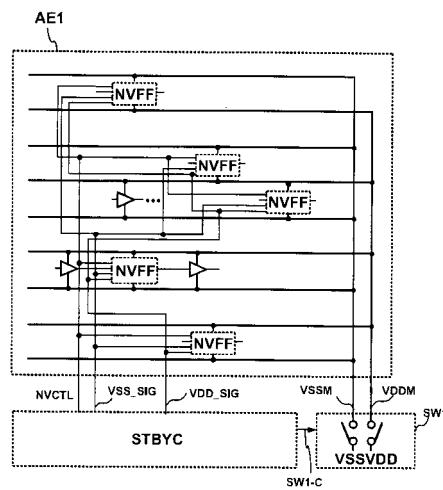

次に、各回路要素間の結線について説明する。図6は、図1のレイアウトに対応する待機時に電源を接地側より遮断する例であり、その制御系も含めた回路ブロック図である。待機時に電源遮断制御される機能ブロックAE1と、機能ブロックAE1の供給電源を制御するスイッチ回路SW1と、機能ブロックAE1の不揮発FFN V F Fおよびスイッチ回路SW1を制御するスタンバイ回路STBYCとを示している。図32に関連して後述するように、機能ブロックAE1の中にはたとえば中央処理装置CPU(以下、CPUと呼ぶ)や、デジタルシグナルプロセッサ(以下、DSPとよぶ)、MPEGアクセラレータ等の周辺回路モジュールが集積される。スタンバイ回路STBYCには常時電源が供給されており、チップ外部から電源が遮断されない限り電源が供給され続ける。機能ブロ

10

20

30

40

50

ック A E 1 は論理回路が集積され、そのフリップフロップに本発明の不揮発 F F N V F F を用いているのが特徴である。機能ブロック A E 1 が電源遮断制御される場合、スタンバイ回路 S T B Y C は、スイッチ回路 S W 1 を制御信号 S W 1 - C により遮断制御し、不揮発 F F N V F F を N V F F 制御信号線群 N V C T L により制御する。また、不揮発 F F N V F F の電源遮断時の情報保持用電源 V S S \_ S I G もスタンバイ回路 S T B Y C から供給され、機能ブロック A E 1 内の不揮発 F F N V F F へ任意の経路で接続される。この接続はディジタル・チェーンのようであってもよいし、ツリー型で結線されてもよい。自動配置配線ツールの配線ストラテジで自由に配線してよい。図 6 では情報保持用電源線 V S S \_ S I G はスタンバイ回路 S T B Y C の 1 つの端子から全ての不揮発 F F N V F F に結線するように描かれているが、スタンバイ回路 S T B Y C の 2 以上の端子から不揮発 F F N V F F に結線するようにすることも可能である。このように構成した場合には、スタンバイ回路 S T B Y C の端子 1 つあたりに接続される不揮発 F F N V F F の個数を減らすことができ、情報保持用電源線 V S S \_ S I G に要求される電流供給能力を低くできる利点がある。ただし、自動配置配線ツールで結線する場合にあらかじめ不揮発 F F N V F F を端子ごとに分けておく必要があるため、レイアウト工程が複雑になる。

10

## 【0020】

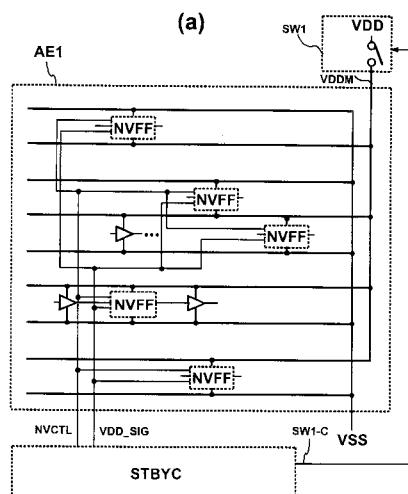

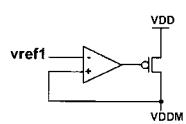

図 7 ( a ) は各回路要素間の結線の別の例である。ここでは機能ブロック A E 1 への電源遮断はスイッチ回路 S W 1 にて高電位側 ( V D D ) が遮断される場合であり、その制御はスタンバイ回路 S T B Y C からの制御信号 S W 1 - C で実施される。N V F F 制御信号線群 N V S T L と情報保持用電源線 V D D \_ S I G については上記図 6 と同様である。図 7 ( a ) の構成は機能ブロック A E 1 が外部電源を降圧して内部電源を供給している場合に有効である。スイッチ回路 S W 1 は降圧回路 ( レギュレータ ) で代用することも可能である。図 7 ( b ) にその構成例を示す。この回路は伊藤清男著「超 L S I メモリ」培風館 ( 1994 年初版発行 ) の第 271 頁に開示されているものである。

20

## 【0021】

また、図 8 は各回路要素間の結線のさらに別の例である。機能ブロック A E 1 への電源遮断はスイッチ回路 S W 1 にて高電位側 ( V D D ) と低電位側 ( V S S ) の双方を遮断することにより行われる。その制御はスタンバイ回路 S T B Y C からの制御信号 S W 1 - C により行われる。この例では、情報保持用電源線として高電位側情報保持用電源線 V D D \_ S I G と低電位側情報保持用電源線 V S S \_ S I G の 2 種類が必要となる点に特徴を有する。

30

## 【0022】

以上に示したように、本発明は高電位側 / 低電位側のいずれの電源を遮断する場合にも適用できる。以後は低電位側電源を遮断する場合を例にして説明する。すなわち、以後特に断らない限り、チップ内の各セルへ供給されるグローバルな接地電源は真のグランド V S S から電源スイッチ用の N 型 M I S F E T を介した仮想電源 V S S M であり、不揮発部分に供給される接地電源は電源 V S S \_ S I G である。特に制限されないが、この電源遮断用 N 型 M I S F E T は I / O 回路等で用いられるゲート絶縁膜厚の薄く、しきい値電圧の大きな M I S F E T で構成することが望ましい。電源遮断用 N 型 M I S F E T のしきい値電圧を大きくすることにより回路に流れるサブストレッショルド電流を効果的に低減でき、ゲート絶縁膜厚を薄くすることで回路に流れるいわゆるゲートトンネルリーク電流を効果的に低減できる。この場合、制御信号 S W 1 - C は I / O 用の高い電圧 ( 例えは 3.3 V ) に応じた振幅をもつ。

40

## 【0023】

本発明の一つの特徴は、C P U や周辺回路モジュールの内部情報をこれらのモジュールに存在する不揮発 F F N V F F で保持する機構を有していることであり、望ましくは不揮発 F F N V F F への情報保持用電源を信号線として配線する設計手法をとる。ここで不揮発 F F N V F F に用いる信号電源線と一般的な電源幹線の外見上の違いは、この信号電源線がセルの自動配置配線 ( プレイス・アンド・ラウティング ) の段階でいわばアドホックに結線されるため、配線の形態が整然とした幾何学的なパターンを有しておらず、図

50

1に示したようにランダムな結線となることである。自動配置配線ツールによって自由に配線できることで設計の自由度が高まり、効率的なレイアウトができる効果がある。

#### 【0024】

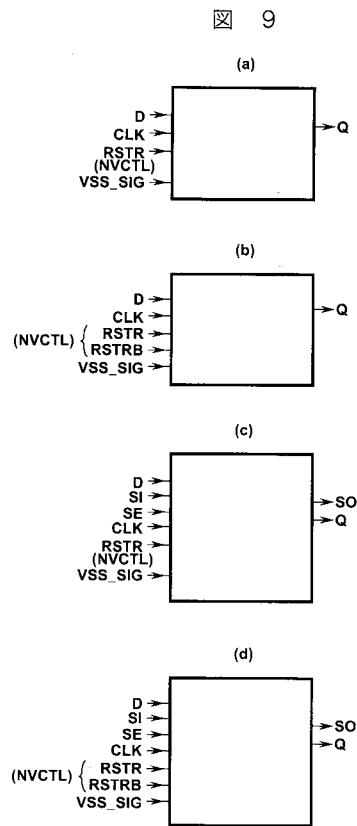

図9は自動配置配線ツールで用いる不揮発FFセル(NVFFセル)のシンボルを示す図である。図9(a)は不揮発FF NVFFの情報保持制御信号群NVCCTLとして一本の信号線RSTRのみ用いる場合の例である。このNVFFセルは、D(データ入力ピン)、CLK(クロックピン)、RSTR(不揮発FF制御ピン)、VSSSIG(信号電源入力ピン)の各入力と、Q(データ出力ピン)の各出力ピンを備えている。

#### 【0025】

一方、図9(b)は不揮発FF NVFFの情報保持制御信号群NVCCTLとして2本の信号線RSTR、RSTRbを用いる場合の例である。このNVFFセルは、D(データ入力ピン)、CLK(クロックピン)、RSTR、RSTRb(不揮発FF制御ピン)、VSSSIG(信号電源入力ピン)の各入力と、Q(データ出力ピン)の各出力ピンを備えている。

#### 【0026】

図9(c)はスキャン機能つきの不揮発FFの例であり、その情報保持制御信号群NVCCTLとして一本の信号線RSTRのみ用いる場合を示した。このNVFFセルは、D(データ入力ピン)、SI(スキャンデータ入力ピン)、SE(スキャンイネーブルピン)、CLK(クロックピン)、RSTR(不揮発FF制御ピン)、VSSSIG(信号電源入力ピン)の各入力と、Q(データ出力ピン)、SO(スキャンデータ出力ピン)の各出力ピンを備えていることが特徴である。

#### 【0027】

一方、図9(d)もスキャン機能つき不揮発FFの例であり、その情報保持制御信号群NVCCTLとして2本の信号線RSTR、RSTRbを用いる場合を示した。このNVFFセルは、D(データ入力ピン)、SI(スキャンデータ入力ピン)、SE(スキャンイネーブルピン)、CLK(クロックピン)、RSTR、RSTRb(不揮発FF制御ピン)、VSSSIG(信号電源入力ピン)の各入力と、Q(データ出力ピン)、SO(スキャンデータ出力ピン)の各出力ピンを備えていることが特徴である。

#### 【0028】

ここに示したセルシンボルは、一例であり、出力信号線群が反転した信号を出力する構成でもよい。

#### 【0029】

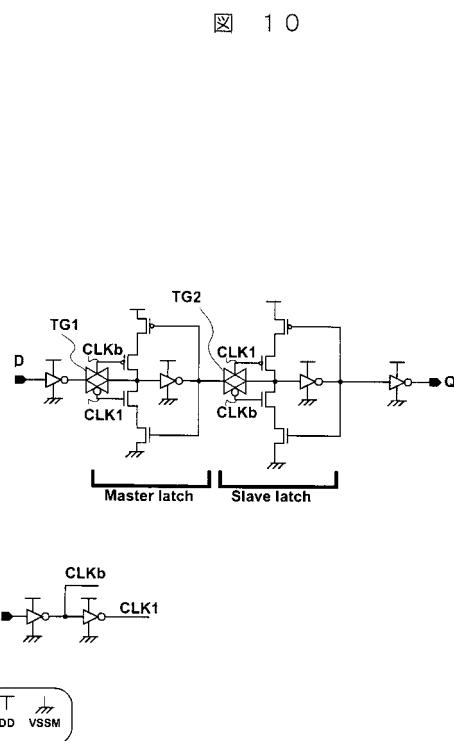

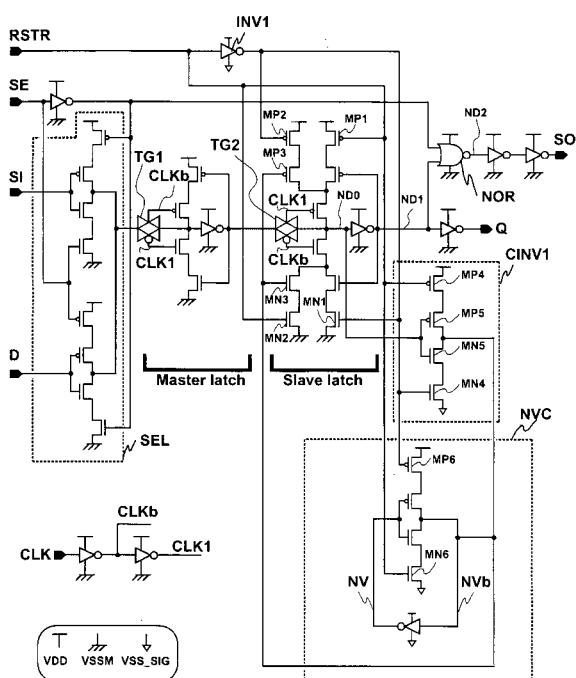

次に具体的な不揮発FFの構成について説明する。図10は電源遮断時にデータ保持機能を有さないマスタースレーブ型ラッチ回路(フリップフロップ回路)である。このようなマスタースレーブ型ラッチ回路の前後に組合せ回路が接続され、同期回路が構成される。

#### 【0030】

図10の回路では、クロックの立ち上がりエッジ(CLK:L H)でマスターラッチ(Master Latch)のトランスマッシュゲートTG1が閉じてデータをラッチするとともに、スレーブラッチ(Slave Latch)のトランスマッシュゲートTG2が開いてマスターラッチが取り込んだ情報を出力Qへ出力する。一方、クロックの立ち下がりエッジ(CLK:H L)ではマスターラッチのトランスマッシュゲートTG1が開き、スレーブラッチのトランスマッシュゲートTG2が閉じてスレーブラッチ内の情報を保持する。

#### 【0031】

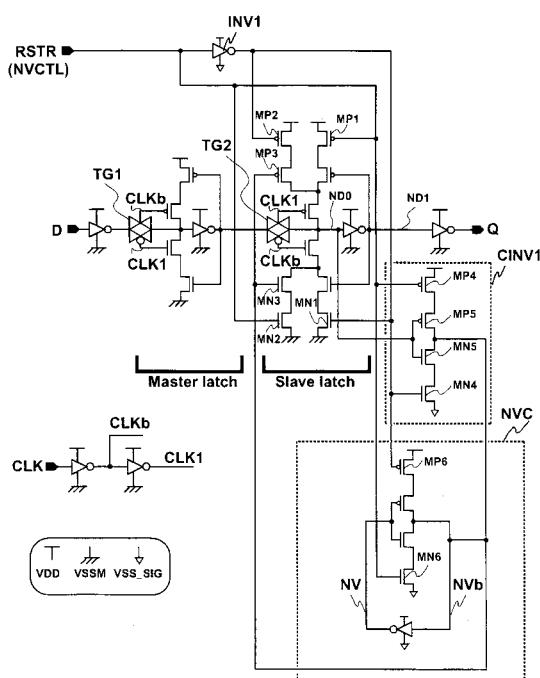

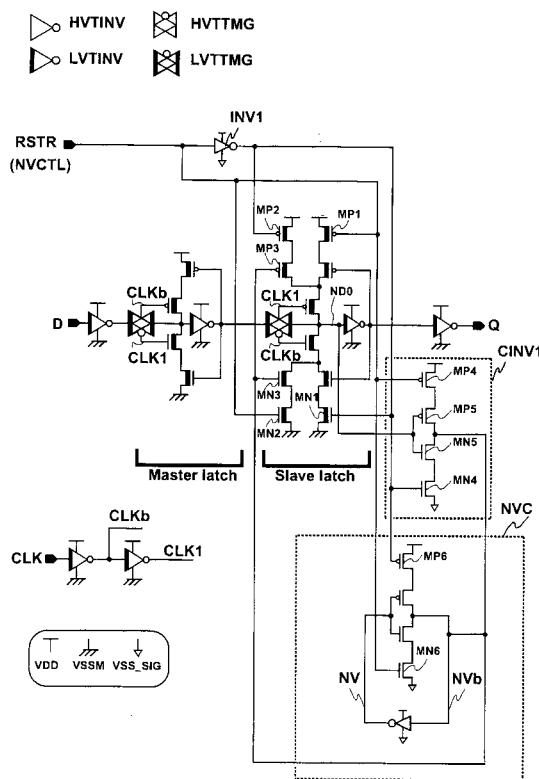

図11は本発明の不揮発型マスタースレーブラッチ回路の1構成例である。図10のマスタースレーブラッチからの変更点として、制御信号RSTRと、不揮発回路NVCと、スレーブラッチの制御MOS(MP1, MN1)、NVCとスレーブラッチの接続インターフェース部のクロックトインバータCINV1(MP4, MP5, MN4, MN5で構成される)と、NVCの情報をスレーブラッチへ書き戻す書き込み選択回路(MP2, M

10

20

30

40

50

P3, MN2, MN3)と、そしてNVC等の電源遮断時の必要な回路の電源であるVSS\_SIGが追加されている。

#### 【0032】

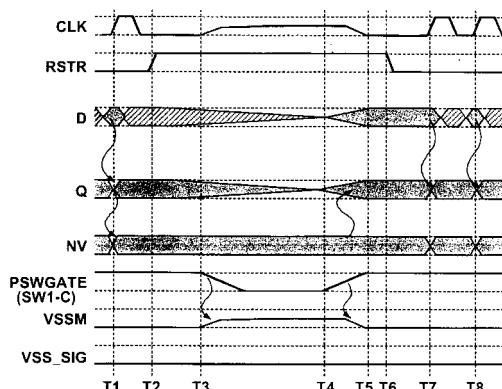

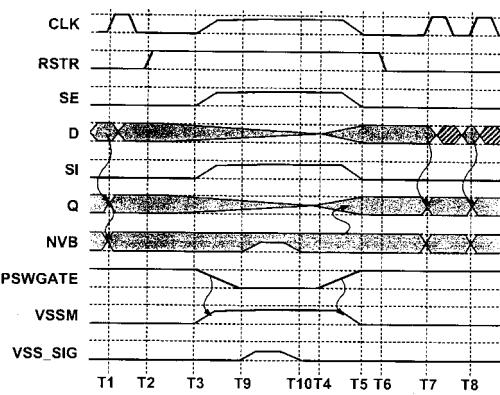

図12は図11の不揮発型マスタースレーブラッチ回路の動作と制御方法を示す動作波形図である。

#### 【0033】

時刻T1は通常動作時のクロック立ち上がりの状態を示している。制御信号RSTR=LOレベルの場合は、図11中トランジスタMP2, MN2がオフであり、トランジスタMP1, MN1がオンであるため、図10の回路と論理的に同様なスレーブラッチの機能が形成され、クロックCLKの立ち上がりに応じて、入力データDは出力Qへ出力される。そのとき、ノードND0と不揮発回路NVC内のノードNVb間に挿入されたクロックトインバータCINV1がオープンであるため、ノードND0のレベルは不揮発回路NVCへ伝達され、ノードNVに情報が書き込まれる。ただし、この段階では、図11のMP6, MN6がオフであるため、不揮発回路NVCのループは開いている。

#### 【0034】

次に電源遮断が実施され、不揮発FF\_NVFFの不揮発回路NVCで情報を保持する動作を説明する。時刻T2のとき、まず制御信号RSTRをHIレベルにする。このとき、図11に示す不揮発回路NVCのループがトランジスタMP6, MN6がオンすることで閉じるとともに、トランジスタMP4, MN4がオフすることでクロックトインバータCINV1が遮断されることによりスレーブラッチから不揮発回路NVCへの経路が遮断される。それとともに、トランジスタMP1, MN1がオフし、トランジスタMP2, MN2がオンすることにより、ノードND1のレベルに代えて不揮発回路NVCからのノードNVbのレベルがスレーブラッチでフィードバックされるようになる。この場合マスターラッチはトランスマッシュゲートTG2が閉じているため、一般に入力Dの値は確定値が変化してもかまわない。

#### 【0035】

その後、時刻T3で電源遮断制御が実行される。ここではN型MISFETにより接地側の電源が遮断される場合を想定している。PSWGATE信号は制御信号SW1-Cに相当し、PSWGATE信号をLOとする制御を実施する。電源遮断用N型MISFETとしてI/O回路等に用いられるゲート絶縁膜の厚いMISFETを用いる場合には、PSWGATE信号の制御振幅はI/Oの電源電圧(たとえば、3.3V)の振幅で制御されることになる。この制御により仮想電源線VSSMは真のグランドから遮断され、仮想電源線VSSMの電位は内部回路のリーク電流により高電位(VDD)側に上昇する。図12の例ではちょうどVDDと0Vの中間レベルを示しているが、実際には集積する回路規模、温度、MISFETのしきい値など諸条件によっては限りなくVDDに近いレベルに上昇する。そのため、通常の回路は情報が保持できなくなってしまう。

#### 【0036】

ここで時刻T3とT2の時間間隔はチップ内の不揮発FFのデータが退避されたことを見計って制御する必要がある。そのため、RSTR信号線を駆動するドライバを駆動力の小さいドライバで、そのドライバ出力レベルがあるしきい値以上になるまでを時間計測し、その後その時間の数倍の時間を待った後に電源遮断制御を開始するなどの方法が考えられる。

#### 【0037】

電源遮断制御が実施されると仮想電源線VSSMの電位は上昇し、不揮発回路NVC以外の保持データは消滅する。このときも、不揮発回路NVCおよび制御信号RSTRが入力されるインバータCINV1の電源は情報保持用信号線VSS\_SIGで供給されているため、不揮発回路NVCの内部ノードNVは所望の値を保持し続けられる。

#### 【0038】

一方、電源投入時は、時刻T4でPSWGATE信号がHIレベルに向けて駆動される。すると仮想電源線VSSMの電位は徐々に0Vへに向けて駆動され、マスタースレーブラ

ツチ回路は情報保持可能な状態になる。不揮発回路NVCからのデータはまずスレーブラッヂにトランジスタMP3, MN3を介して書き戻される。制御信号RSTRはVDDであり、その反転信号もINV1により0Vが保証されているため、制御信号NVCのデータは電源印加時のマスタースレーブラッヂ回路の動きにより擾乱を受けることなくデータを保持し続ける。待機時においてはクロック信号CLKの駆動回路も電源が遮断されているため、クロックCLKのLOレベルは正確なグランドレベル(0V)が保証されない。しかし、電源が印加された後速やかにLOレベルを出力するように、クロック信号を制御する。

#### 【0039】

電源スイッチが完全にオンした後、仮想接地線VSSMの電位が0Vになったことを見計って、時刻T6で制御信号RSTRをLOとする。これにより、図11のトランジスタMP2, MN2がオフとなり、不揮発回路NVCからのフィードバックループが開くとともに、トランジスタMP1、MN1がオンしてノードND1からのフィードバックループが形成される。また、トランジスタMP4、MN4がオンしてスレーブラッヂから不揮発回路NVCへの信号経路が形成され、トランジスタMP6、MN6がオフすることにより不揮発回路NVC内のラッチのループが開く。これで図11の不揮発性マスタースレーブラッヂ回路は通常動作時における機能を実現するようになる。すなわち、時刻T7、T8に示すようにクロックの立ち上がりエッジでデータを取り込むというマスタースレーブラッヂ回路の通常動作が実現される。

#### 【0040】

この構成により従来のマスタースレーブラッヂ回路の特性をほぼ劣化させること無く、電源遮断時のデータ保持機構が設けられ、このマスタースレーブラッヂ回路をシステムLSIに適用することで電源遮断時のデータ保持が低コストで実現可能となる効果がある。

#### 【0041】

図11の構成では、制御信号RSTRは不揮発FFNFFF内部でインバータINV1により反転信号を生成する構成としている。その理由は、RSTR信号とその反転信号の到着時刻に多大な差があると、クロックトインバータのオフ動作ならびに不揮発回路NVCのラッチ形成がうまくいかず、データが破壊されてしまう。本構成のようにRSTR信号の反転信号を不揮発FFNFFF内で生成すれば、両者の時間差は最小限に抑えられるためクロックトインバータの貫通問題を回避し、結果として低消費電力になる効果がある。また、制御信号RSTRと反転信号の両方を受ける構成に比べてピン数が少ないため、自動配線の配線数が減るため配線がより容易になるという効果もある。

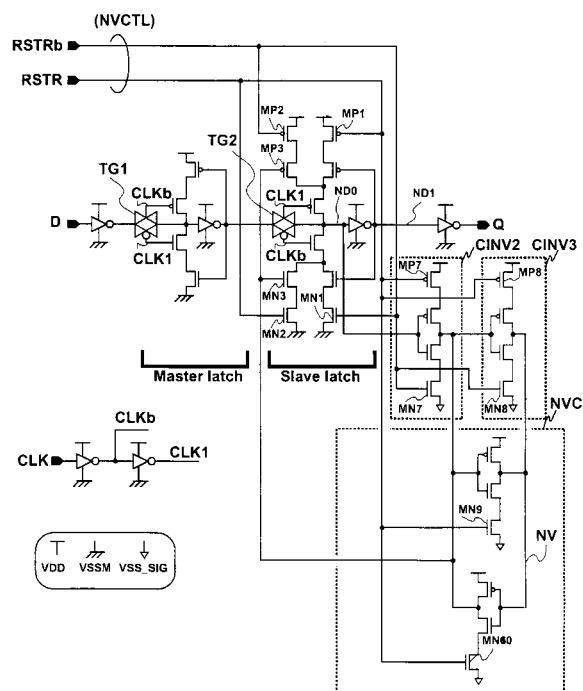

#### 【0042】

図13は不揮発制御信号NVC TLを相補信号であるRSTR信号とRSTRb信号の2本を用いて制御する例である。図11との違いは2つのクロックトインバータCINV2, CINV3を有し、不揮発回路NVCがトランジスタMN9, MN10のスイッチがついたインバータにより構成されていることである。なおこの図ではクロックトインバータCINV2とCINV3の電源を遮断するMISFETをトランジスタMN7, MN8, MP7, MP8により独立に設けているが、これは2つのクロックトインバータで共有してもよい。同様に、不揮発回路NVCの電源スイッチであるMN9, MN10も両者で共用してもよい。こうすることで更なる省面積化が図れる効果がある。

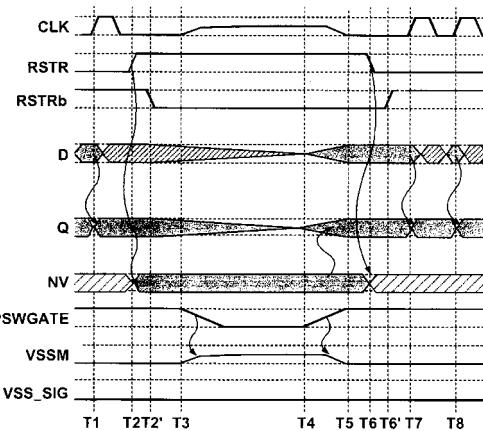

#### 【0043】

図14は図13に示した不揮発型マスタースレーブラッヂ回路の動作と制御方法を示す動作波形図である。時刻T1は、制御信号RSTR = LOであるため通常動作時のクロック立ち上がりの状態を示している。なぜならこの場合も図12で述べたように、制御信号RSTR = LO(したがって制御信号RSTRb = HI)の場合は図13で示したトランジスタMP2, MN2がオフであり、トランジスタMP1, MN1がオンであるため、図10のマスタースレーブラッヂ回路と論理的に同様の機能が形成されるからである。クロック信号CLKの立ち上がりに応じて、入力データDは出力Qへ出力される。このとき本構成例では、ノードND0と不揮発回路NVC内のノードNV間に挿入されたクロックト

10

20

30

40

50

インバータ C I N V 2 および C I N V 3 がオープンであるため、そのまま不揮発回路 N V C へ情報が伝達され、ノード N V に情報が達する。ただし、この段階では、図 13 のトランジスタ M P 9 , M N 1 0 がオフであるため、不揮発回路 N V C のループは閉じていない。

#### 【 0 0 4 4 】

次に電源遮断が実施され、不揮発 F F N V F F 内の不揮発回路 N V C で情報を保持する動作を説明する。時刻 T 2 のとき、まず R S T R 信号を H I レベルにする。このとき、図 13 に示す不揮発回路 N V C のループがトランジスタ M P 9 , M N 1 0 がオンすることで閉じ、トランジスタ M N 7 , M N 8 がオフすることでスレーブラッチから不揮発回路 N V C 間にあるクロックトインバータ C I N V 2 、 C I N V 3 の接地レベルへの経路が遮断される。このときトランジスタ M N 2 がオンし、トランジスタ M P 1 がオフするので、通常動作時のスレーブラッチの高電位側電源への経路が遮断され、かつ、不揮発回路 N V C からのフィードバックが入力できるようにフィードバック用ドライバ M N 3 の接地側の電流経路が形成される。その後時刻 T 2 ' で R S T R b 信号を L O レベルとすることで、クロックトインバータ C I N V 2 , C I N V 3 の高電位側電源のスイッチ M I S F E T M P 7 , M P 8 が遮断されてスレーブラッチと不揮発回路 N V C が分離される。それと同時にトランジスタ M P 2 がオンし、トランジスタ M N 1 がオフすることで、通常動作時のスレーブラッチのフィードバックループが開くとともに不揮発回路 N V C からのフィードバックループが完全に閉じることになる。これで、通常動作時のスレーブラッチの各ノードがいかなる値をとっても不揮発回路 N V C へ影響を与えることはない。この間、マスター ラッチのトランスミッショングート T G 2 が閉じているため、入力 D は確定値が遷移してしまってもよい。また、 T 2 と T 2 ' の時間間隔は、チップ全体の R S T R 信号が H I レベルになるまでの時間が必要であり、それを実現するために、 R S T R 信号のドライバトランジスタを小駆動力のトランジスタにして、そのドライバの出力があるしきい値以上になるまでの時間を計測し、その時間の数倍の時間後に R S T R b 信号を L O とすればよい。これは自動配置配線ツールを用いることを前提とすると、一般には R S T R 信号と R S T R b 信号とでは配線経路が異なり、同じ遅延で到達する保証がないからである。もし、同一セルへの R S T R 信号と R S T R b 信号が同様の遅延で到達する、すなわち、ほぼ等しい経路で配線できるのであれば、たとえば、 R S T R 信号線の所定の位置からスタンバイ回路 S T B Y C に R S T R 信号を戻す経路を設け、スタンバイ回路 S T B Y C に戻された R S T R 信号のレベルにより時刻 T 2 と T 2 ' の間隔を制御してもよい。

#### 【 0 0 4 5 】

その後、時刻 T 3 で電源遮断制御が実行される。ここでは図 12 と同様に、 N 型 M I S F E T により接地側の電源を遮断する場合を想定している。そのため、 N 型 M I S F E T の制御信号 P S W G A T E ( S W 1 - C ) を L O とする制御を実施する。

#### 【 0 0 4 6 】

電源遮断制御が実施されると仮想電源線 V S S M の電位は上昇し、不揮発回路 N V C 以外の保持データは消滅する。不揮発回路 N V C の電源は情報保持用信号線 V S S \_ S I G で供給されているため、不揮発回路 N V C の内部ノード N V は所望の値を保持し続ける。

#### 【 0 0 4 7 】

一方、電源投入時は、時刻 T 4 で P S W G A T E 信号が H I レベルに向けて駆動される。すると仮想電源線 V S S M のレベルが徐々に 0 V へに向けて駆動され、マスター スレーブラッチ回路は情報保持な状態にされる。不揮発回路 N V C からのデータはスレーブラッチに M P 3 , M N 3 を介して書き戻される。このとき R S T R 信号は V D D であり、 R S T R b 信号も 0 V が保証されているため、不揮発回路 N V C のデータは電源印加時のマスター スレーブラッチ回路の動きにより擾乱を受けることなくデータを保持し続ける。なお、この場合も図 12 での説明同様、クロック信号 C L K の駆動回路も電源が遮断されているため、クロックの L O レベルは正確なグランドレベル ( 0 V ) が保証されない。しかし電源が印加された後速やかに L O レベルを出力するように、クロック信号 C L K を制御することが望ましい。

## 【0048】

その後、電源スイッチが完全にオンし仮想電源線VSSMの電位が0Vになったことを見計って、時刻T6でRSTR信号をLOとする。これにより、図13のトランジスタMN2がオフとなり、不揮発回路NVCからのフィードバックループの接地側の電流経路が遮断されるとともに、トランジスタMP1がオンして、通常動作時におけるスレーブラッチのフィードバックループの高電位側電流経路が形成される。それとともにトランジスタMP7, MP8がオンしスレーブラッチから不揮発回路NVCへの信号経路において高電位側電流経路が形成され、トランジスタMN9, MN10がオフすることにより不揮発回路NVC内のラッチのループが開く。

## 【0049】

その後、時刻T6'でRSTRb信号をHIレベルとすることで、クロックトインバータCINV2, CINV3の低電位側のスイッチMN7, MN8がオンしてスレーブラッチと不揮発回路NVCとが接続されるとともに、トランジスタMP2がオフし、トランジスタMN1がオンすることで、スレーブラッチのフィードバックループが完全に閉じるとともに不揮発回路NVCからのフィードバックループが開くことになる。その後、これで本発明の不揮発性マスタースレーブラッチ回路は通常動作時の機能を実現するようになる。

## 【0050】

また、時刻T6とT6'の時間間隔は、チップ全体に伝達されるRSTR信号がLOレベルになるまでの時間が必要であり、そのために時刻T2とT2'の時間間隔を制御する方法と同様に、RSTR信号をLOに駆動するドライバの駆動能力を小さくし、ドライバ出力があるしきい値以下となるまでの時間を計測し、その時間の数倍の時間を待ってRSTRb信号をHIレベルにするなどの方法が考えられる。

## 【0051】

図15はスキャン機能を追加した不揮発性マスタースレーブ回路の構成例である。図11の構成との相違は、スキャン入力信号(SI)とスキャンイネーブル信号(SE)とスキャン出力信号(SO)が端子として加わったことと、セレクタ回路SELとスキャン出力端子SOに通じるNOR回路とインバータである。セレクタ回路SELは図11にあつた入力Dにつながるインバータをクロックトインバータとしたものでありゲート幅を適切に設計すれば速度劣化はほぼ考慮しなくてよい。セレクタ回路SELはSE信号により、データ入力信号Dかスキャン入力信号SIのいずれかを選択しラッチ部に入力する。SE信号がHIレベルの場合スキャン入力信号SIが選択され、SE信号がLOレベルの場合データ入力信号Dが選択される。

## 【0052】

クロック信号CLKの立ち上がりエッジ(CLK:LH)でマスターラッチ(Master Latch)のトランスミッショングートTG1が閉じデータをラッチし、スレーブラッチ(Slave Latch)のトランスミッショングートTG2が開いてマスターラッチが取り込んだ情報を出力Qへ出力する。一方、クロック信号CLKの立ち下がりエッジ(CLK:HL)ではマスターラッチのトランスミッショングートTG1が開きスレーブラッチのトランスミッショングートTG2が閉じてスレーブラッチ内の情報を保持する。この一連のクロック動作に際して、スキャン出力信号SOは、SE信号がHIの場合はスキャン入力信号SIの値によりクロック信号に同期して変化し、SE信号がLOの場合はデータ入力信号Dの値がいかなる値をとっても常にLOを出力する。また、基本的な動作は図12と同様であって、SE信号がLOであれば全く同様の動作が実現する。

## 【0053】

さらに、不揮発回路NVCへのデータ取り込み経路をノードND0からノードND2に変えると、DQバス上の負荷を低減できて高速化の効果がある。この場合、図16に示すように、SE信号はRSTR信号をHIレベルにする前の時刻T2''にHIレベルにする必要がある。スレーブラッチの情報をNOR出力に反映させるためである。その後、S

E 信号を L O にするのは R S T R 信号が L O レベルなる前が望ましい。図 16 の例では S E 信号を R S T R 信号が L O レベルになる(時刻 T 6 )前の時刻 T 6' にて L O レベルとする制御例を示した。この場合、次段のマスタースレーブラッチ回路には通常のバス(データバス)を通ってデータが反映されることになる。もし、スキャンバスを通してデータのセットを実施するほうが効果的である場合、S E 信号を L O とする制御は R S T R 信号が L O レベルになった後に実施すればよい。

#### 【 0 0 5 4 】

なお、図示しないが図 13 のような R S T R 信号および R S T R b 信号による相補信号で制御する場合にもスキャン機能は追加できる。その場合、入力 D の部分と出力 Q の部分に上述したようなスキャン用回路を付加すればよい。

10

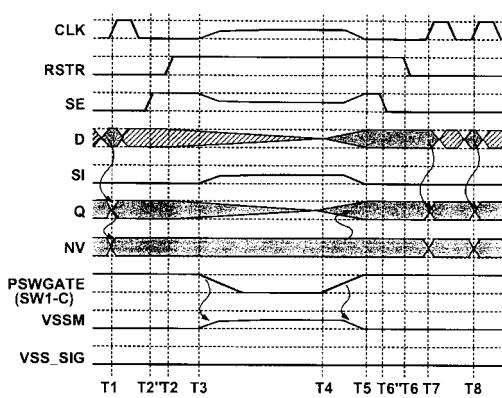

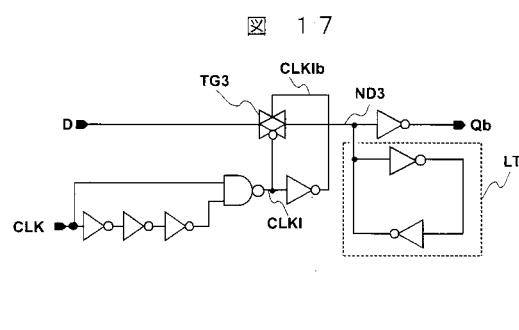

#### 【 0 0 5 5 】

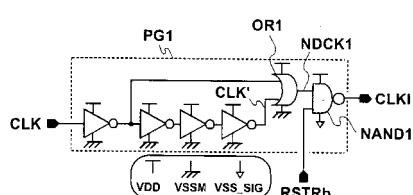

図 10 から図 16 はマスタースレーブ型ラッチ回路の構成例を示したが、他の形態のラッチ回路にも適用できる。図 17 はパルスラッチ回路の例である。パルスラッチ回路は、クロック信号 C L K とクロック信号 C L K がインバータ 3 段の遅延回路による遅延クロック信号とを N A N D 回路に入力することで、クロック信号の立ち上がり時にパルスを発生させ、そのパルス C L K I とインバータで反転させた反転パルス C L K I b を用いてトランスマッシュゲート T G 3 を開き、入力 D を後段の出力 Q b へ伝達する回路である。パルスラッチ回路はパルスの終了と共にトランスマッシュゲート T G 3 が閉じるため、取り込んだデータをノード N D 3 に設けられたインバータ 2 段のラッチで保持するものである。

20

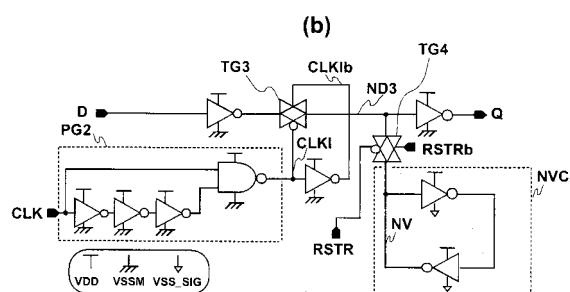

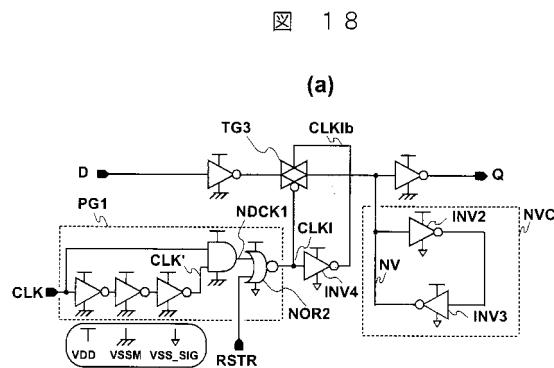

#### 【 0 0 5 6 】

不揮発情報保持機能をこのパルスラッチ回路に適用した構成例を図 18 ( a ) , ( b ) に示す。図 18 ( a ) はその第一の構成例である。図 18 からの変更点は、まず、データ保持用のラッチ L T を情報保持回路用電源 V S S \_ S I G から電源を供給することにより電源遮断時にも情報が保持されるようになると、パルス発生回路を制御信号 R S T R により制御するために図示したような A N D N O R 型回路とし、少なくとも N O R 側の低電位側電源を情報保持回路用電源 V S S \_ S I G とすること、パルス C L K I をドライブするインバータの低電位側電源を情報保持回路用電源 V S S \_ S I G とすることである。図 18 ( a ) の例では、入力 D にインバータを設けることで、出力 Q を正論理としている。これにより論理ゲート一段分の遅延が生じるが正論理を後段に伝えられ、さらに、入力 D のゆれに対してより安定な動作が可能になる。例えば、入力 D がノイズにより高電位側電源 V D D より高い電位になった場合に、本来オフ状態のはずのトランスマッシュゲート T G 3 にしきい値電圧を超えるゲート電圧が実質的に印加されることで、トランスマッシュゲート T G 3 を通過してしまうという誤動作のおそれを減少する効果がある。もちろん、当該インバータを設けずに図 17 のような入力 D を反転出力する構成も可能である。トランスマッシュゲート T G 3 を駆動するドライバ N O R 2 , I N V 4 の低電位側電源を情報保持回路用電源 V S S \_ S I G とすることで、電源遮断時にも電源を印加できるため正確な制御が可能となる効果がある。この構成では制御信号としては R S T R 信号のみで構成できるため、自動配置配線が楽になるという効果がある。

30

#### 【 0 0 5 7 】

図 19 は図 18 ( a ) に示した不揮発型パルスラッチ回路の動作と制御方法を示す動作波形図である。時刻 T 1においては、制御信号 R S T R = L O であるため、通常動作時のクロック立ち上がりの状態を示している。なぜなら制御信号 R S T R = L O の場合は図 18 ( a ) で示した N O R ゲート N O R 2 はパルス N D C K 1 をそのまま反転出力させるからである。クロック信号 C L K の立ち上がりに応じて、パルス発生回路 P G 1 にて生成されたパルスクロック C L K I および C L K I b はそれぞれ H I レベルと L O レベルになる。そのパルスの幅は 3 段のインバターチェーンの遅延分である。パルスクロック C L K I が L O 、 C L K I b が H I となるとトランスマッシュゲート T G 3 がオンし、入力データ D は出力 Q へ出力される。同時に図 18 ( a ) の構成では、不揮発回路 N V C 内のノード N V に情報が伝達される。

40

50

## 【0058】

次に電源遮断が実施され、不揮発回路NVCで情報を保持する動作を説明する。時刻T2のとき、まずRSTR信号をHIレベルにする。これによりNORゲートNOR2はパルスNDCK1のレベルによらずLOレベルを出力する。

## 【0059】

その後、時刻T3で電源遮断制御を実行する。図11の例と同様にPSWGate信号をLOとする制御により、仮想電源線VSSMの電位が内部回路のリーク電流により高電位側へ上昇する場合を想定している。時刻T3とT2の間隔はチップ内の不揮発FFFNFFFのデータが退避するのに十分な時間とする。このタイミング制御は図11に関して開示したタイミング制御と同様の方法で実施できる。

10

## 【0060】

電源遮断制御が実施されると仮想電源線VSSMの電位は上昇し、不揮発回路NVC以外の保持データは消滅する。不揮発回路NVCの電源は情報保持用電源線VSSSIGで供給されているため、不揮発回路NVCの内部ノードNVは所望の値を保持し続けられる。

## 【0061】

一方、電源投入時は、時刻T4でPSWGate信号がHIレベルに向けて駆動される。すると仮想電源線VSSMのレベルは徐々に0Vへに向けて駆動され、不揮発回路NVCから出力Qに情報が伝達される。クロック信号CLKの駆動回路も電源が遮断されているため、クロック信号CLKのLOレベルは正確なグランドレベル(0V)が保証されない。しかし電源が印加された後速やかにLOレベルを出力するように、クロック信号CLKを制御することが望ましい。

20

## 【0062】

その後、電源スイッチが完全にオンし、仮想電源線VSSMのレベルが0Vになったことを見計って、時刻T6でRSTR信号をLOとする。これにより、NORゲートNOR2はNDCK1をそのまま反転出力する。時刻T5とT6の間隔は、電源スイッチが完全にオンするだけの十分な間隔が必要であるため、電源スイッチコントローラからのアクノリッジ信号等を用いて制御することができる。その後は、時刻T7、T8に示すようにクロックの立ち上がりエッジでデータを取り込むというパルスラッチ回路の通常動作が実現される。

30

## 【0063】

この構成によりパルスラッチ回路の特性をほぼ劣化させること無く、電源遮断時のデータ保持機構が設けられ、このパルスラッチ回路をシステムLSIに適用することで電源遮断時のデータ保持が低コストで実現可能となる効果がある。

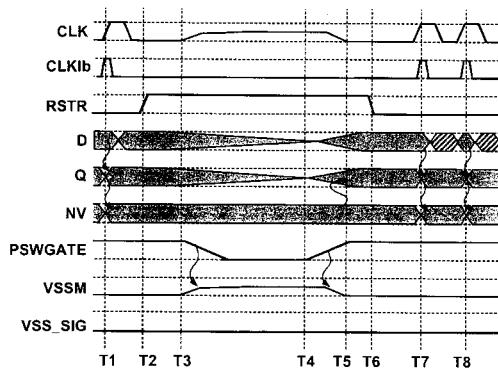

## 【0064】

図18(b)はパルスラッチ回路の別の例である。図17からの変更点は、データ保持用のラッチLTを情報保持回路用電源VSSSIGに接続し不揮発化することと、ノードND3と不揮発回路NVCのノードNVとの接続経路にトランスマッシュゲートTG4を設けたことである。この場合、不揮発制御信号がRSTR信号およびRSTRb信号の2本必要になる。この構成では、情報保持回路用電源VSSSIGを必要とする回路を最小限とすることができるため、動作に大きな電流を必要とするパルス発生回路PG2への電流供給能力を高める効果がある。

40

## 【0065】

図20は図18(a), (b)に示した不揮発型パルスラッチ回路にスキャン機能をつけるための回路例である。図18(a), (b)のノードNVにつながる不揮発回路NVCを図20に示す不揮発回路NVCと置き換えることにより実現できる。通常動作時は、スキャン用クロックCLKSをLOレベル、反転スキャン用クロックCLKSbをHIレベルとして、パルスラッチ回路の機能を実現する。一方、スキャン機能でデータを送るために、スキャン用クロックCLKSがHIレベル、反転スキャン用クロックCLKSbがLOレベルとして、スキャン入力信号SIがノードNVBへ伝達され、そ

50

の後スキャン用クロック C L K S が L O レベル、反転スキャン用クロック C L K S b が H I レベルとなることでノード N V B に保持されたデータがスキャン出力 S O へ伝達される。スキャン機能を用いる場合は、パルスラッチ回路の入力 D の影響を避けるため、本体のパルスラッチ回路のクロック信号 C L K は L O とすることにより、入力 D の取り込みを不可能としておく必要がある。

#### 【 0 0 6 6 】

また、ここでは図示しないが、図 15 に示したように、スキャン入力 S I と通常のデータ入力 D とを S E 信号で選択可能とするセレクタ回路を図 18 ( a ) または ( b ) の入力部に置き換え、さらに図 18 ( a ) または ( b ) の出力部 Q にも図 15 に示したような Q 出力とスキャン出力 S O を引き出す回路を付加してスキャン機能を実現してもよい。

10

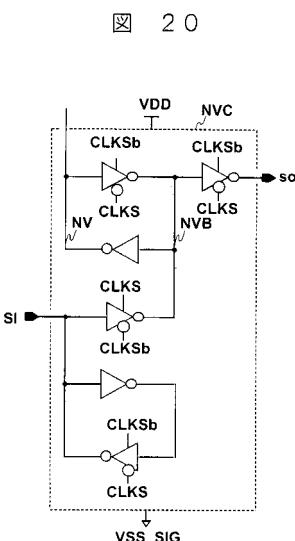

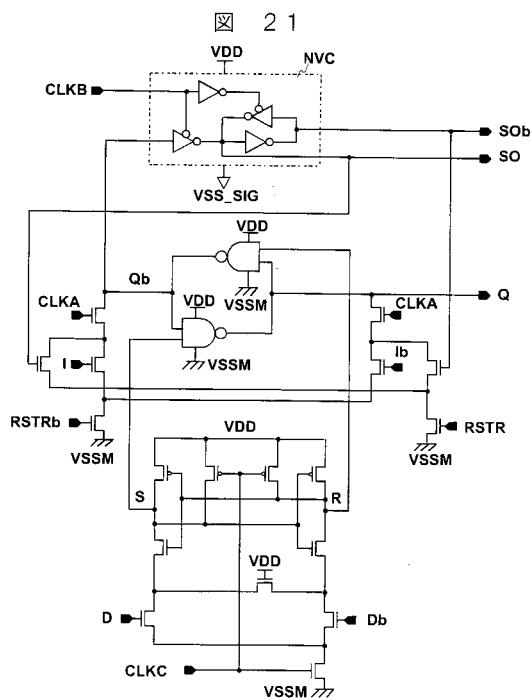

#### 【 0 0 6 7 】

図 21 はセンスアンプ型フリップフロップの回路例である。不揮発回路 N V C の低電位側電源が情報保持回路用電源 V S S \_ S I G であり、その他回路の低電位側電源が仮想電源線 V S S M となっている。

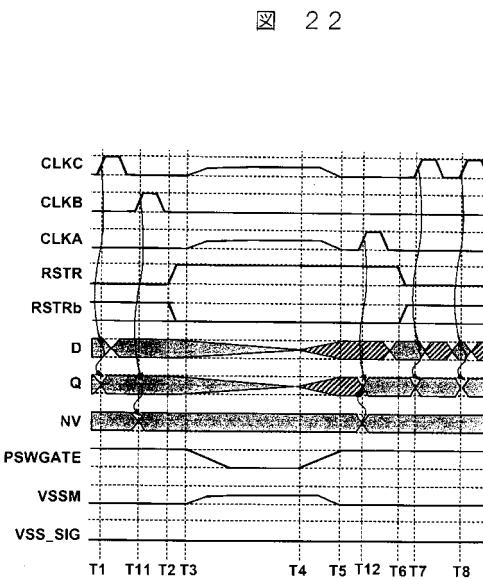

#### 【 0 0 6 8 】

図 22 は図 21 に示した不揮発型センスアンプ型フリップフロップ回路の動作と制御方法を示す動作波形図である。時刻 T 1 においては、制御信号 R S T R = L O 、制御信号 R S T R b = H I 、制御信号 C L K B = L O 、制御信号 C L K A = L O であるため通常動作時のクロック立ち上がりの状態を示している。クロック信号 C L K C の立ち上がりに応じて、入力 D を取り込み、その値に応じた出力 Q を出力する。

20

#### 【 0 0 6 9 】

次に電源遮断を実施する場合を説明する。まず、クロック信号 C L K C を L O レベルとしてセンスアンプ型フリップフロップ回路の入力 D の情報を反映させない状態とする。時刻 T 1 で制御信号 C L K B を H I レベルとして不揮発回路 N V C へノード Q b の情報を取り込み、その後制御信号 C L K B を L O レベルとする。これにより不揮発回路 N V C をフリップフロップ本体から電気的に切りはなす。このときも制御信号 C L K A は L O レベルに制御される。その後、時刻 T 2 で不揮発回路 N V C からのフィードバック経路を設けるため、制御信号 R S T R を H I レベルにし、制御信号 R S T R b を H I レベルにする。この状態は、ノード Q およびノード Q b のグランドへの電気的な経路を不揮発回路 N V C からのフィードバック経路で制御することを意味する。図 22 では制御信号 R S T R および制御信号 R S T R b をほぼ同時に制御する例を示したが、特にこの制御の順序は問題ない。不揮発回路 N V C にて必要なデータが保持済みであるからである。また、図 11 および図 13 で示したように、外部から 2 本の信号線として制御してもよいし、R S T R b 信号はフリップフロップ内でインバータ回路を用いて生成してもよい。

30

#### 【 0 0 7 0 】

その後、時刻 T 3 で電源遮断制御が実行される。ここでは図 11 の例と同様に P S W G A T E 信号を L O とする制御により、仮想電源線 V S S M の電位は内部回路のリーケ電流により高電位側へ上昇するものとする。時刻 T 3 と T 2 の間隔はチップ内の不揮発 F F のデータが退避されるのに十分な時間とする。このタイミング制御は図 11 の制御と同様の方法で可能である。

40

#### 【 0 0 7 1 】

電源遮断制御が実施されると仮想電源線 V S S M の電位は上昇し、不揮発回路 N V C 以外の保持データは消滅する。このとき、不揮発回路 N V C および制御信号 C L K B の電源は情報保持回路用電源 V S S \_ S I G で供給されているため、不揮発回路 N V C の内部ノード S O および S O b は所望の値を保持し続けられる。

#### 【 0 0 7 2 】

一方、電源投入時は、時刻 T 4 で P S W G A T E 信号が H I レベルに向けて駆動される。これにより仮想電源線 V S S M の電位は徐々に 0 V へに向けて駆動され、不揮発回路 N V C から出力 Q に情報が伝達される。なお、クロック信号の駆動回路も電源が遮断されているため、クロック信号 C L K C の L O レベルは正確なグランドレベル ( 0 V ) が保証され

50

ない。しかし電源が印加された後速やかに L O レベルを出力するように、クロック信号 C L K C を制御することが望ましい。

#### 【 0 0 7 3 】

その後、電源スイッチが完全にオンし、仮想電源線 V S S M の電位が 0 V になったことを見計って、時刻 T 1 2 で制御信号 C L K A を H I レベルにする。これにより不揮発回路 N V C のデータがノード Q および Q b へ書き戻されるため、出力が決定する。その後制御信号 C L K A を L O レベルにした後、時刻 T 6 で R S T R 信号を L O 、 R S T R b 信号を H I とする。ここで、R S T R 信号が L O であり、R S T R b 信号が H I である状態は、ノード Q および Q b への書き込みにおいてスキャン入力側が選択されるということであるから、R S T R 信号および R S T R b 信号の制御はスキャン時だけ R S T R 信号を L O 、 R S T R b 信号を H I とし、その他は R S T R 信号を H I 、 R S T R b 信号を L O としておくことも可能である。時刻 T 5 と T 6 の間隔は、電源スイッチが完全にオンするだけの十分な間隔が必要である。そのため、電源スイッチコントローラからのアクノリッジ信号等を用いて制御すればよい。

10

#### 【 0 0 7 4 】

その後は、時刻 T 7 、 T 8 に示すようにクロックの立ち上がりエッジでデータを取り込むという従来のセンスアンプ型フリップフロップの通常動作が実現される。

#### 【 0 0 7 5 】

この構成によりセンスアンプ型フリップフロップの特性をほぼ劣化させること無く、電源遮断時のデータ保持機構が設けられ、このセンスアンプ型フリップフロップをシステム L S I に適用することで電源遮断時のデータ保持が低コストで実現可能となる効果がある。

20

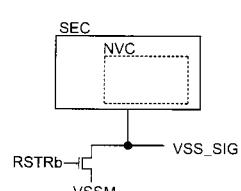

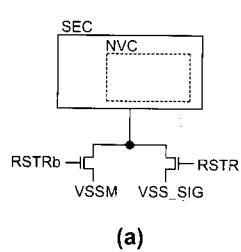

#### 【 0 0 7 6 】

図 2 3 ( a ) 、 ( b ) に情報保持要素回路 S E C への情報保持回路用電源 V S S \_ S I G の接続の変形例を示している。ここで、情報保持要素回路 S E C とは図 1 1 、図 1 3 、図 1 5 、図 1 8 、図 2 0 、図 2 1 の各図で情報保持回路用電源線 V S S \_ S I G により電源が供給される回路要素の総称であり、不揮発回路 N V C や、クロックトインバータ C I N V 1 ( 図 1 1 ) 等が含まれる。図 2 3 ( a ) は、情報保持要素回路 S E C への電源供給を R S T R 信号および R S T R b 信号により、仮想電源線 V S S M と情報保持用電源線 V S S \_ S I G とを切り替える例である。これにより、情報保持要素回路 S E へ大電流を供給したい場合には仮想電源線 V S S M から電源供給を可能にすることで所望の大電流が得られる効果がある。例えば、図 1 8 ( a ) に示したパルスラッチ回路の場合、パルス発生部 P G 1 は多量の電流を必要とするが、かかる構成を用いることでパルス発生部 P G 1 の動作時には必要十分な動作電流を供給でき、ひいては速度劣化を引き起こさないという効果がある。もちろん、情報を保持する場合 ( 待機時 ) は微小電流のみでよいため、情報保持回路用電源線 V S S \_ S I G へ接続し低消費電流を実現する。

30

#### 【 0 0 7 7 】

図 2 3 ( b ) は R S T R b 信号で仮想電源線 V S S M と情報保持回路用電源線 V S S \_ S I G の接続をオン・オフ制御する変形例である。大電流が必要な場合は、仮想電源線 V S S M と接続して所望の大電流を得て、待機時には情報保持回路用電源線 V S S \_ S I G により微小電流の供給を受けて低消費電力化を実現することができる効果がある。

40

#### 【 0 0 7 8 】

これら 2 つの変形例では、R S T R 信号および R S T R b 信号により制御している例を示したが、これらの信号とは別の独立信号線で制御してもよい。その場合、図 9 のセルイメージで独立信号線が 1 本追加される。独立制御線で制御する場合には、ピン数増加はあるものの、R S T R 信号とは独立に電流制御ができるため、動作時には情報保持回路用電源 V S S \_ S I G 側の電源遮断を行い、ほとんど高インピーダンス状態に保つことも可能である。これによりさらなる低消費電力が達成できる効果がある。

#### 【 0 0 7 9 】

図 2 4 は図 2 3 に示した情報保持回路用電源 V S S \_ S I G の制御を実施するにあたり

50

、パルスラッチ回路を用いて1本の制御信号N V C T Lで制御する場合の実施例であり、図18(a)に示したパルス発生回路PG1の変形例である。この例では、R S T R b信号を用いて、不揮発化制御が制御信号R S T R b = L Oのときに実現されることを前提としている。図23(b)に示した回路を用いた場合、このようにすると制御信号線が1本ですむ。この場合の動作は図19においてR S T R信号をその反転信号であるR S T R b信号に変えたものに相当する。その場合でも、その他の信号の動作および相互関係は同様に制御されればよい。また、図23(a)においてR S T R b信号とR S T R信号の結線を逆にしても所望の不揮発制御が実現できることは明らかである。

#### 【0080】

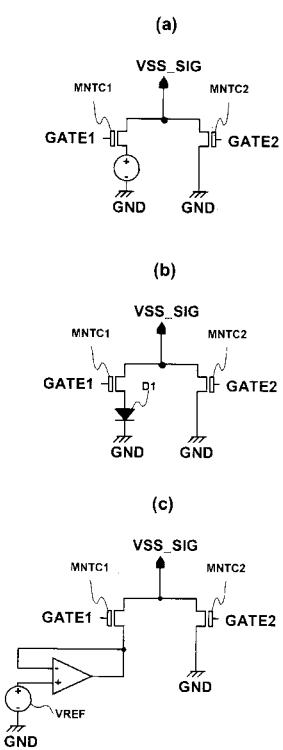

図25は、情報保持回路用電源V S S \_ S I Gの生成例を示している。この例では、待機時にさらに低消費電力化させるために、情報保持回路用電源V S S \_ S I Gの値を動的に制御可能にしている。図25(a)は情報保持回路用電源線V S S \_ S I Gへの経路が、N型M I S F E T M N T C 1及び電圧源を介してグランドG N Dへ接続される経路と、N型M I S F E T M N T C 2のみを介してグランドG N Dへ接続する経路とを、それぞれG A T E 1信号とG A T E 2信号を用いて選択できる構成をとっている。この図のように、制御用トランジスタとしてはI / O用のゲート絶縁膜厚の厚いM I S F E Tを用いることが望ましい。また、図25(b)は図25(a)の電圧源をダイオード接続により実現した例であり、図25(c)はリファレンス電圧発生回路V R E Fを用いた定電圧発生回路により定常電圧を供給する回路例である。

#### 【0081】

図26は図25に示したV S S \_ S I G生成方法を図11に示したマスタースレーブラッチに適用した場合の動作波形を示した図である。情報保持回路用電源V S S \_ S I Gの値が時刻T 9から時刻T 10にかけて中間レベルに制御されていることが特徴である。時刻T 9は完全に電源遮断された後に制御されることが望ましく、時刻T 10は電源投入動作に入る前に0 Vレベルに戻されることが望ましい。これは、電源が遮断・印加される際に内部回路が動き、そのノイズの影響が情報保持回路用電源V S S \_ S I Gに入り、不揮発回路N V Cの保持データが破壊されることを防ぐためである。時刻T 9は時刻T 3で電源が遮断された後、電源スイッチコントローラなどから生成される、電源が完全に遮断されたことを示す信号(アクノリッジ信号など)を元に制御すればよく、時刻T 10を知るためにには、図25(a)～(c)のドライバM N T C 2の駆動力を小さくし、情報保持回路用電源線V S S \_ S I Gの根元の電位があるしきい値以下になる時間を計測し、その時間の数倍の時間を持って電源スイッチをオンする制御を実施するといった方法が可能である。

#### 【0082】

さらに、本発明は2種類以上のトランジスタを用いることで、さらに高速化および低消費電力化が実現される。図27は図11に示したマスタースレーブラッチ回路の変形例である。この構成例の特徴は、通常動作時に動作するマスタースレーブラッチ部分に低しきい値電圧のM I S F E T及びそれを用いた論理ゲートL V T I N VやトランスマッシュゲートL V T T M Gを用いていることである。これにより、通常動作を高速にできる。一方、待機時に必要な回路には高しきい値電圧のM I S F E T及びそれを用いた論理ゲートH V T I N VやトランスマッシュゲートH V T T M Gを用いることでリーク電流を小さく抑えることが可能となる。さらに、待機時に必要な回路(I N V 1, C I N V 1, N V C)を構成するM I S F E Tのゲート絶縁膜厚を厚くすれば、ゲートリーク電流も削減できる効果がある。

#### 【0083】

このとき、ゲート絶縁膜厚の選定に当たっては、S R A Mを基準にすることが望ましい。S R A Mのメモリセルもゲートリーク電流が今後問題となることが予想される。たとえばコア側のE O T(等価絶縁膜厚)が1.5 n m程度となった場合に、S R A Mのゲート絶縁膜厚をE O Tで2.0 n m～2.2 n m程度に厚くすることで、S R A Mに流れるゲートリーク電流を劇的に小さくできる。ゲートリーク電流はE O Tが0.2 n m厚くなる

10

20

30

40

50

毎に1桁低減するからである。そこで、このようなS R A Mが実現されるような、多ゲート絶縁膜プロセス(マルチT O Xプロセス)にて製造されるシステムL S Iにおいては、不揮発F Fの情報保持部分(I N V 1、C I N V 1、N V C)をこのS R A Mメモリセルに用いられる膜厚のM I S F E Tをもちいて構成すれば、システムL S Iに新たな工程を付加することなくより低リークな不揮発F Fが実現できて好都合である。

#### 【0084】

なお、このような変形は、図18のパルスラッチ回路や図21のセンスアンプ型フリップフロップ回路にも適用できる。これらについても情報保持回路要素S E C以外の回路に低しきい値のM I S F E Tを用いたり、情報保持回路要素S E Cのトランジスタのゲート絶縁膜厚をS R A Mと同様にしたりすればよい。

10

#### 【0085】

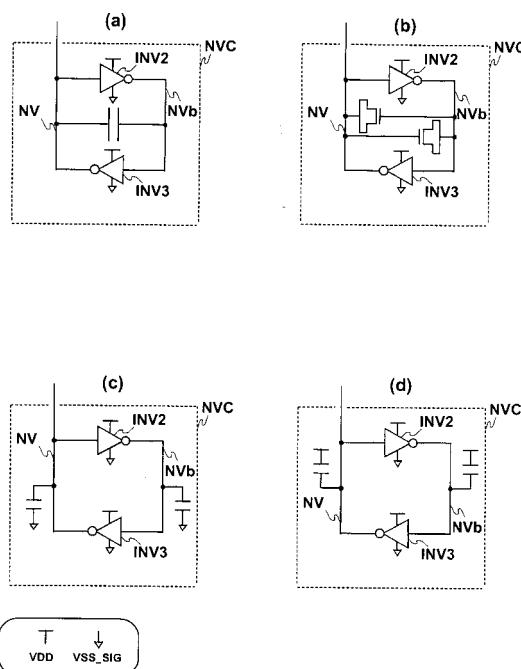

図28は不揮発回路N V Cに容量素子を追加した例である。容量素子を追加する理由は、不揮発回路N V Cにおける中性子線や宇宙線によるソフトエラー耐性などの各種ノイズマージンを向上させるためである。特に、図25および図26に示した情報保持回路用電源V S S \_ S I Gの制御を実施し、待機時の電源電圧を低減する場合にはソフトエラーの影響が顕著になるからである。これらは、図11、図13、図15、図18、図20、図21の不揮発回路N V CのN V、N V bノード間に接続される。ここでは、インバータ2段のラッチのみ示しているが、図11等のように、これらのラッチがクロックトインバータによって構成されていても、スイッチ用M I S F E Tを備えていても同様に適用できる。図28(a)はノードN VとノードN V b間に容量素子を設けた例であり、図28(b)はその実現形態を示したものである。図28(b)のように双方向にM I S F E Tを容量素子として接続することで、N V、V N bの値に応じて常にいずれかのM I S F E Tが容量素子として作用するため、安定動作が可能である。

20

#### 【0086】

図28(c)は情報保持回路用電源線V S S \_ S I Gへの容量カップリングの例である。仮想電源線V S S Mは電源投入・遮断時のノイズや、動作時のノイズが多いためカップリングする相手としてはふさわしくなく、情報保持回路用電源線V S S \_ S I Gへの容量カップリングが望ましい。この容量素子はN型M I S F E Tを用い、N型M I S F E TのゲートをノードN VおよびノードN V bへ接続し、ソースおよびドレインを情報保持回路用電源線V S S \_ S I Gに接続すれば実現できる。P型M I S F E Tを用いる場合は、ゲートと、ドレインおよびソースの接続が逆になる。また、図28(d)は高電位側電源V D Dへのカップリングを示している。これもN型M I S F E Tを用い、N型M I S F E Tのゲートを高電位側電源V D Dへ接続し、ソースおよびドレインをノードN VおよびノードN V b側へ接続すれば実現できる。P型M I S F E Tを用いる場合は、ゲートと、ドレインおよびソースの接続を逆にすればよい。これらを適用することで、ソフトエラー耐性が高まる効果がある。

30

#### 【0087】

なお、高電位側電源線V D Dを遮断する場合は、セルに配線される仮想電源線V D D Mへのカップリングを避けるように容量素子を設ければよい。

40

#### 【0088】

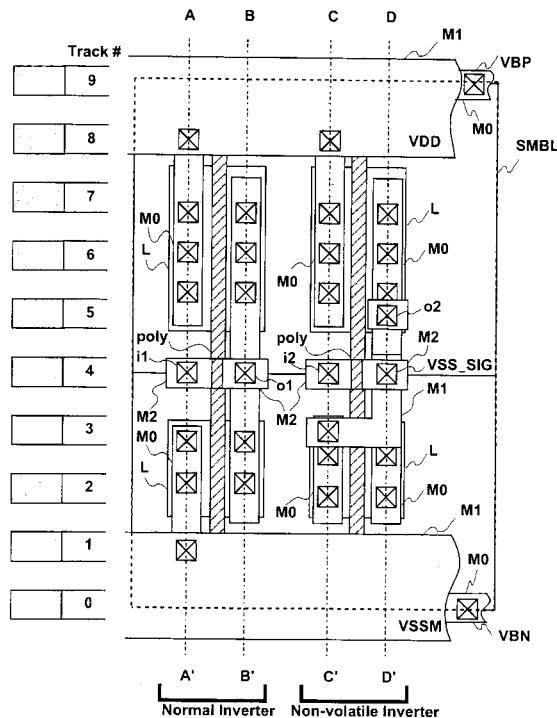

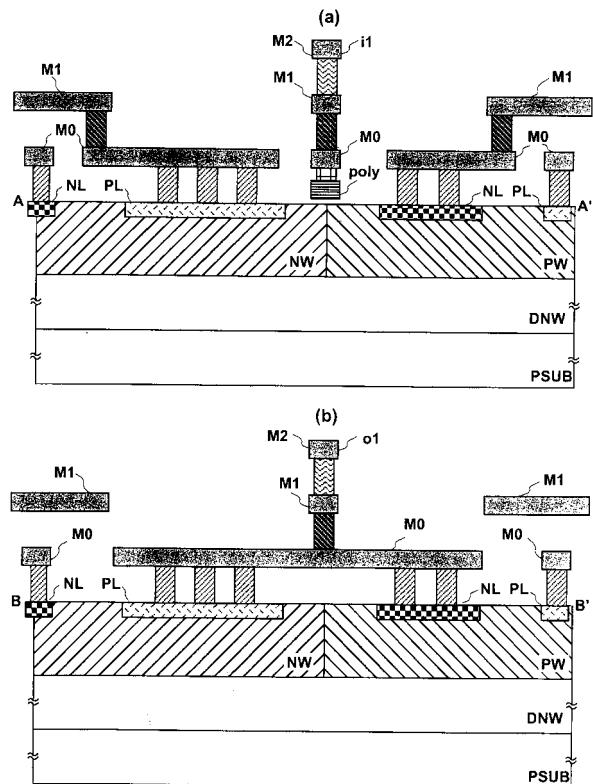

図29に本発明を実現するための標準セルのレイアウト例を示す。最小配線幅のメタル9本分のセル高さを持っている、いわゆる、9グリッドセルを示している。この例では、0番トラックと1番トラックをまたがるV S S M配線と8番トラックと9番トラックをまたがるV D D配線がある例を示した。電源線にこのような太い幅のメタルを用いる場合、露光解像の条件からスペースも広げる必要があり、多くの場合、2番トラックと7番トラックは配線禁止となる。そのため、この例ではセル内配線には3番トラック、4番トラック、5番トラックが割り当てられ、セル間配線チャネルとして6番トラックが割り当てられている。

#### 【0089】

セル内のトランジスタの配線構造について説明するため、この図には2個のインバータ

50

を示してある。一つは通常インバータ (Normal Inverter) であり、これは仮想電源線 VSSM により給電されるインバータである。このインバータの入力端子は i<sub>1</sub> であり、出力端子は o<sub>1</sub> である。もう一つは不揮発インバータ (Non-Volatile Inverter) であり、情報保持回路用電源線 VSS\_SIG を用いて給電されるインバータである。このインバータの入力端子は i<sub>2</sub> であり、出力端子は o<sub>2</sub> である。通常インバータは 2 つの電源 (VDD および VSSM) がセル内に配線された電源用メタル (M1) から M0 配線層を介して拡散層 (L) へ接続される。これは、同図の A - A' 間にあたり、その断面図を図 30 (a) に示す。この図から明らかなように、2 つの電源は電源配線と接続している。なお、この図では端子は第 2 メタル (M2) から取り出す例を示しており、また、基板電源は通常インバータと不揮発インバータで同一としている。通常インバータと不揮発インバータで基板電源を別に構成することもできるが、その場合、基板電源の分離のためのウエル分離が必要となり面積効率が低下してしまう。

10

20

30

40

#### 【0090】

ここで断面構造について簡単に説明しておく。この例は P 型基板 PSUB 上に N 型のウエル DNW を深く作り、その上に N 型 MISFET を形成する P 型ウエル PW、P 型 MISFET を形成する N 型ウエル NW を形成する、いわゆる、3 重ウエル構造を示した。このような基板構造を採用する場合には、基板電位を制御してリーク電流を削減する基板バイアス制御が可能となる。基板バイアス制御を用いると、待機時に基板電圧を N 型 MISFET の場合は N 型 MISFET のソース電圧より低く、P 型 MISFET の場合は P 型 MISTFET の電源電圧より高くすることで実効的にしきい値電圧（絶対値）を大きくしてリーク電流を削減する。本発明においても待機時にかかる基板バイアス制御を実施すると、さらに低消費電力化が実現できる。もちろんここでは図示しないが、N ウエル DNW を設けない、いわゆる 2 重ウエル構造にも適用可能である。

#### 【0091】

出力 O<sub>1</sub> は P 型 MISFET と N 型 MISFET の拡散層を共に繋いだ後、ビアホール VIA を介してメタル配線 M<sub>1</sub>、M<sub>2</sub> へ接続される。これは図 29 の B - B' に相当し、その断面図を図 30 (b) に示した。

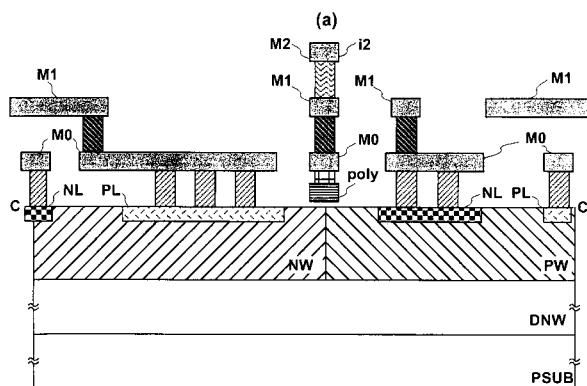

#### 【0092】

一方、不揮発インバータは VDD 側の電源は上記 VDD 電源配線から M<sub>0</sub> を経由して接続されているが、接地側はセル高さのほぼ中央に位置する VSS\_SIG ピンから配線されていることが特徴である。これは同図で C - C' にあたり、その断面図を図 31 (a) に示す。この図からも明らかであるが、N 型 MISFET のソースは仮想電源線 VSSM とは接続していない。出力 O<sub>2</sub> は P 型 MISFET と N 型 MISFET の拡散層をともにつないだ後、ビアホール VIA を介してメタル配線 M<sub>1</sub>、M<sub>2</sub> へ接続される。これは図 29 の D - D' に相当し、その断面図を図 31 (b) に示した。

#### 【0093】

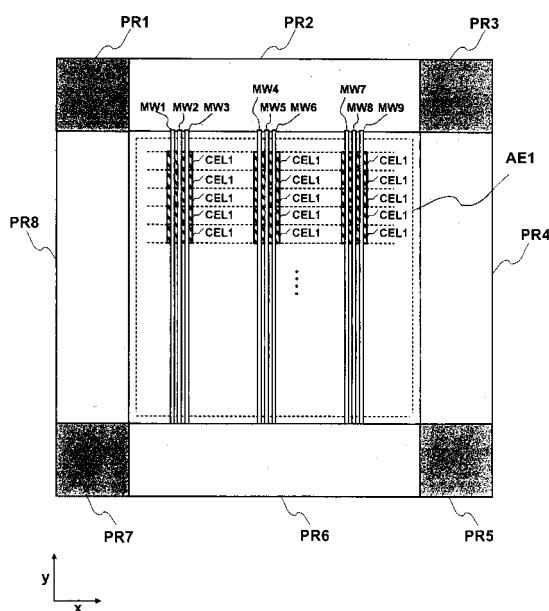

図 32 は第 1 領域 AE1 のレイアウト図である。第 1 領域 AE1 を取り巻くように周回電源幹線がレイアウトされる。ここには電源線 VDD と電源線 VSS、仮想電源線 VSSM および各種制御信号などが配線される。図 32 の電源リング領域 PR1 ~ PR8 の下にはスタンバイ制御回路 STBYC 等を配置すると面積の有効活用が可能となる。メタル第 1 層の電源幹線は x 方向に延在するように配置され、領域 PR4 および領域 PR8 はセル行の両端に位置することになるから、電源遮断用の MISFET を設けると都合がよい。電源遮断用の MISFET は大きな電流供給能力を必要とされるので、複数の MISFET としてレイアウトするのが望ましい。また、電源リング領域の 4 隅にあたる領域 PR1, PR3, PR5, PR7 の下には、電源スイッチコントローラや、図 25 (a) ~ (c) に示した VSS\_SIG 生成回路、不揮発回路 NVIC の制御信号群を生成する NVCL 制御回路などをレイアウトするのが望ましい。

#### 【0094】

また、図 32 には縦方向に電源補強するメタル第 2 層の電源線 MW1 乃至 MW9 をレイアウトした例を示している。この図には y 方向に延在する電源幹線群（「縦幹線群」とい

50

う)として3本の電源線(電源線VDDとVSS、及び仮想電源線VSSM)が描いてあるが、とくに3本に限定されることはない。さらに実際のレイアウトとしては、多層に渡って様々な電源をレイアウトすることも可能であるし、ひとつの配線層(たとえばM2層)のみでこれらの電源をレイアウトすることも可能である。

#### 【0095】

自動配置配線において、縦幹線をレイアウトするため縦幹線のみがレイアウトされたセルCEL1を用いて等間隔に配置する構成とすればレイアウトが容易となる。このセルCEL1にはMISFETは作成されず、電源配線のみレイアウトされるのが一般的である。

#### 【0096】

ここで、本発明の数多くの不揮発FFの制御信号NVCCTLをスタンバイ制御回路STBYCの單一ドライバのみで駆動すると、駆動力が十分に得られない場合がある。その場合には、中継バッファをセルCEL1内に設けると都合がよい。このセルCEL1には常時電源供給される電源線VSSが配線可能されるため、待機時にも動作できるドライバを設けることが可能だからである。このドライバのレイアウトは、図29のレイアウトで不揮発インバータのNMOSソース側結線のごとく結線すればよい。

#### 【0097】

図33に本発明を適用したLSIチップの構成例を示す。LSIチップとしては、情報処理装置、特にマイクロプロセッサに適用した場合のブロック図を示している。LSIチップ(システムLSI)は望ましくは単一の半導体基板上に形成される。

#### 【0098】

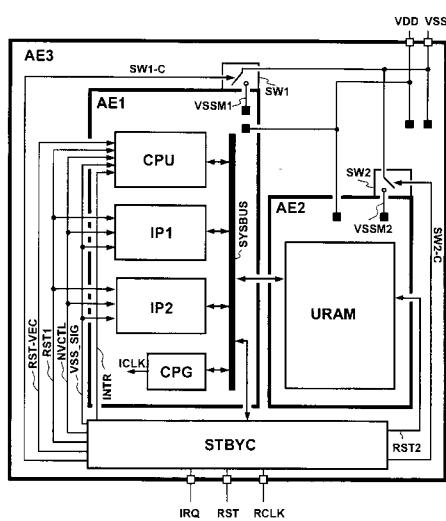

システムLSIは独立に電源を制御できる領域として、第1領域AE1、第2領域AE2、第3領域AE3がある。第1領域AE1は、プロセッサCPU、周辺回路モジュールIP1、IP2、システムバスSYSBUS、クロック発生回路CPGを含み、電源スイッチSW1により電源の供給が制御される。この第1領域AE1内のフリップフロップまたはラッチはすべて不揮発FFで構成されることが望ましいが、状態保持に必要最低限のフリップフロップまたはラッチのみを不揮発FFで構成させることも可能である。次に、第2領域AE2は、内部メモリURAMを含み、電源スイッチSW2により電流の供給が制御される。最後に、第3領域AE3にはスタンバイ制御回路STBYCが含まれ、システムLSIに電源供給がなされる限り、常に電源が供給される。ここで、電源スイッチSW1及びSW2は、接地電位VSSと各領域の間に配置され、電流の供給を制御しているが、当然に動作電位VDDと各領域の間に配置されてもよい。特に、降圧回路を設ける場合には降圧回路に電源スイッチの機能をもたせることも可能である。また、接地電位VSSと各領域の間及び動作電位VDDと各領域の間の両方に配置しても構わない。

#### 【0099】

CPUは、システムLSIの全体を制御する。周辺回路モジュールIP1はCPUが命令をフェッチする際に必要とならない周辺回路モジュールであって、例えばMPEGアクセラレータである。周辺回路モジュールIP2はCPUが命令をフェッチする際に必要となる周辺回路モジュールであって、例えばバスステートコントローラである。システムバスSYSBUSは、CPUを含む各回路モジュールが接続され、図示しないデータバス及びアドレスバスを含む。クロック発生回路CPGは、外部から供給されるクロック信号RCLKを受けて内部クロック信号ICLKを発生する。内部クロック信号ICLKは各回路モジュールに供給され、システムLSIは、内部クロック信号ICLKに従って動作する。内部メモリURAMは大きな容量をもち、現在処理しているデータ等、必要な情報を保持する。図33の構成例では、第1領域AE1に含まれる各回路モジュールをまとめて配置し、第2領域AE2に含まれる各回路モジュールをまとめて配置している。このように配置することにより、複数の回路モジュールに対して電源スイッチSW1、SW2を共通に設けることができるため面積を小さくすることができる。また、図33で第1領域AE1に配置した周辺回路モジュールをそれぞれ独立に電源遮断可能な領域として構成することも可能である。この場合、モジュールごとに不使用であれば電源遮断制御が実施でき

るため、CPUが動作中であっても非動作の周辺回路モジュールの電源遮断が実施で、動作時のリーク電流をも削減できる効果がある。

#### 【0100】

本発明の不揮発FFを利用したスタンバイモード（「第1スタンバイモードSTBY1」という）においては、電源スイッチSW1はオフ状態とされ、電源スイッチSW2はオン状態で維持される。これにより、プロセッサCPU、周辺モジュールIP1、IP2、クロック発生回路CPGに対する電源供給は遮断されるため消費電流を低減できる。このときでも第1領域AE1内の全ての不揮発FFに電源が供給されるため、その情報を保持し続けることができる。

#### 【0101】

遷移動作について説明する。第1領域AE1内の内部情報は、不揮発FFにて保持して保持される。また、必要に応じてキャッシュのデータなどを内部メモリURAMへ退避させる。不揮発FFは、第3領域AE3のスタンバイ制御回路STBYCによって電源および制御信号の供給を受ける。その後、電源スイッチ制御信号SW1-Cにより電源スイッチSW1をオフ状態とし、第1領域AE1に含まれる各回路モジュールへの電流の供給を停止する。電源スイッチSW2はオン状態で維持されるので、第1領域AE1内の不揮発FFと第2領域AE2内の回路モジュールには電流が供給され、システムLSIの内部情報は保持される。これにより外部からの割込み要求により不揮発FFの情報や内部メモリURAMに保持された情報を第1領域AE1内の所定の回路に復帰させることで、第1スタンバイモードからの復帰時の割り込み処理を行うことが可能となる。割り込み要求があった場合は、スタンバイ制御回路STBYCは、図11および図12等で説明したように、電源スイッチSW1をオン状態とし、第1領域AE1へ電流を供給後、不揮発FFの不揮発回路NVCに保持されたデータを不揮発FFの出力に反映することで、第1領域AE1のランダム論理を電源遮断前の状態に復帰させる。内部メモリURAMへ退避させたデータがある場合には、退避したシステムLSIの内部情報を第1領域AE1へ復帰させる。

#### 【0102】

この動作は、OS等のソフトウェアの立ち上げを伴うリセット処理に比べて短時間で行われるので、内部情報が失われるUスタンバイモードに比べて高速に復帰することが可能になる。なお、内部メモリURAMへ内部情報を退避させる例を説明したが、外部メモリに退避することも可能である。

#### 【0103】

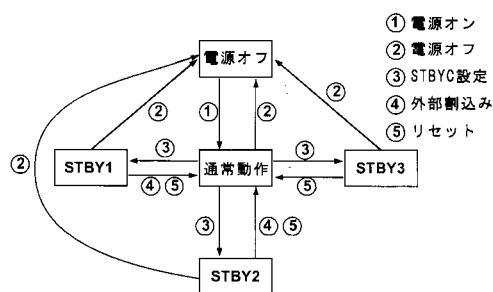

また、システムLSIでは他のスタンバイモード、例えば従来のソフトウェア・スタンバイ（「第2スタンバイモードSTBY2」という）やUスタンバイ（「第3スタンバイモードSTBY3」という）を併用することも可能である。これにより、システムLSIの使用状態により柔軟に低電流モードを設定することができる。図34に各モードの表を示す。

#### 【0104】

第1スタンバイモードSTBY1は第1領域AE1の電源を遮断し、第2領域AE2では、電源は供給されるがクロックは停止されている状態である。第1領域AE1の内部情報は不揮発FFで保持できるため内部情報は不揮発であり、外部からの割り込み処理で復帰が可能である。そのため、復帰時間は電源スイッチの動作時間と並行してなされるクロック再開までの時間を考慮すればよく、数100μ秒程度の時間で復帰できる。第1スタンバイモードへの遷移はスタンバイ制御回路STBYCのモード設定レジスタSTBCRを設定することで実現される。第1スタンバイモードにおいては、第1領域AE1の大部分の回路の電源が電源スイッチにより遮断されるため、消費電流は100μA程度に抑えられる。

#### 【0105】

第2スタンバイモードSTBY2は、第1領域AE1、第2領域AE2、第3領域AE3全ての電源が印加されているが、第1領域AE1および第2領域AE2へのクロック信

10

20

30

40

50

号の分配が停止されている。このため第1領域A E 1と第2領域A E 2の回路モジュールは動作しないため、トランジスタのリーク電流程度の消費電力で待機できる。この場合も内部情報を保持し続けられるので内部情報は不揮発となる。また、復帰時間は上述したように割り込み処理で復帰できるため、クロック再開の時間程度で済み数100μ秒程度で復帰できる。このモードへの遷移もスタンバイ制御回路S T B Y Cのモード設定レジスタS T B C Rを設定することで実現される。

#### 【0106】

第3スタンバイモードS T B Y 3は第3領域A E 3以外全ての領域の電源を遮断するモードであり、消費電流は10μA程度であるものの、内部情報が揮発してしまうためリセット動作でしか復帰できず、復帰にかかる時間は数100μ秒程度を必要とする。このモードへの遷移もスタンバイ制御回路S T B Y Cのモード設定レジスタS T B C Rを設定することで実現される。10

#### 【0107】

図34の表から読みとれるように、第1スタンバイモードS T B Y 1と第2スタンバイモードS T B Y 2は消費電流の違いだけであるから、第1スタンバイモードと第2スタンバイモードとをまとめてひとつの低電流モードとすることも可能であろう。また、通常動作時は第1領域A E 1、第2領域A E 2、第3領域A E 3の全てに電源及びクロック信号が供給され、電源オフ時には、全ての回路に対して電源の供給が遮断される。

#### 【0108】

スタンバイモードは、ここに示したモードの種々の組み合わせが可能である。その場合、その組み合わせに必要な程度にシステムL S Iの構成も変形される。例えば、第3スタンバイモードを有さないシステムL S Iであれば、図33の第2領域A E 2をなくし、第2領域A E 2の回路モジュールを第3領域A E 3に設けることになる。また、システムL S I内部の電源スイッチに代えて、システムL S Iの外部の電源制御回路により電源を遮断する構成も可能である。さらに、第1領域A E 1の全ての不揮発F Fが一つのスタンバイ制御回路S T B Y Cから制御されるのではなく、各モジュール毎にスタンバイ制御回路を設けることも可能である。20

#### 【0109】

図35は各モード間の遷移を示した図である。電源オフモードから通常動作モードへは電源をオンすることで遷移する。逆に通常動作モードから電源オフモードへは電源をオフすることで遷移する。30

#### 【0110】

通常動作モードから第3スタンバイモードS T B Y 3への遷移はレジスタS T B C Rの設定で遷移する。逆に第3スタンバイモードS T B Y 3から通常動作モードへの復帰はリセットで遷移する。第3スタンバイモードS T B Y 3から電源オフモードへは電源をオフすることで遷移する。

#### 【0111】

通常動作モードから第1スタンバイモードS T B Y 1への遷移はレジスタS T B C Rの設定で遷移する。逆に第1スタンバイモードS T B Y 1から通常動作モードへの復帰は外部割込みもしくはリセットで遷移する。第1スタンバイモードS T B Y 1から電源オフモードへは電源をオフすることで遷移する。40

#### 【0112】

通常動作モードから第2スタンバイ状態S T B Y 2への遷移はレジスタS T B C Rの設定で遷移する。逆に第2スタンバイモードS T B Y 2から通常動作モードへの復帰は外部割込みもしくはリセットで遷移する。第2スタンバイモードS T B Y 2から電源オフモードへは電源をオフすることで遷移する。

#### 【0113】

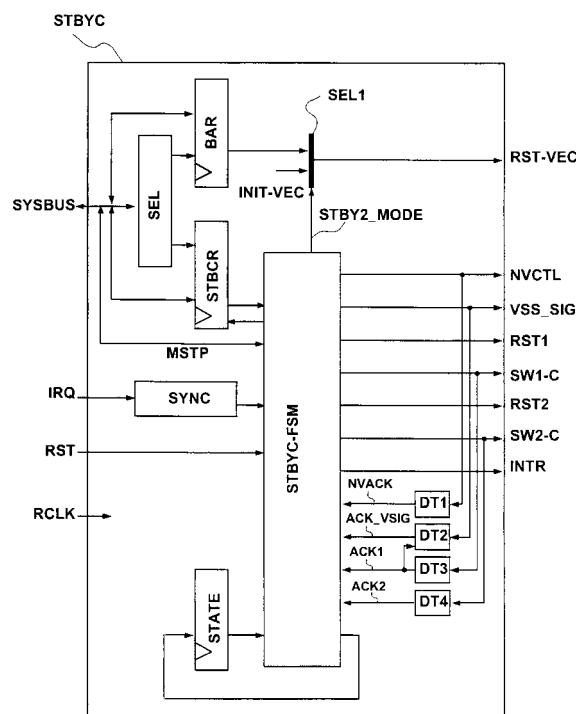

図36に、各種スタンバイモードへの遷移・復帰を制御するスタンバイ制御回路S T B Y Cの構成を示している。最初に、本発明の不揮発F Fを必要最低限のフリップフロップとレジスタに対して適用した場合について説明する。スタンバイ制御回路S T B Y Cには50

、内部レジスタの読み書きを行うためシステムバス S Y S B U S が接続されており、また割り込み要求信号 I R Q 、リセット信号 R S T 、クロック信号 R C L K が入力される。スタンバイ制御回路 S T B Y C の出力は、不揮発制御信号 N V C T L 、情報保持回路用電源 V S S \_ S I G 、第 2 スタンバイモードからの復帰後に C P U へ割り込みを通知する割り込み信号 I N T R 、リセット後の C P U 実行開始アドレス R S T - V E C 、第 1 領域 A E 1 のリセット信号 R S T 1 と電源スイッチ S W 1 の制御信号 S W 1 - C 、第 2 領域 A E 2 のリセット信号 R S T 2 と電源スイッチ S W 2 の制御信号 S W 2 - C である。なお、図 3 3において割り込み信号 I N T R は C P U に直接接続されているが、割り込みコントローラ等を介して C P U と接続してもよい。

## 【 0 1 1 4 】

スタンバイ制御回路 S T B Y C は、システムバス S Y S B U S から読み書きできるレジスタとしてスタンバイモード制御レジスタ S T B C R とブートアドレスレジスタ B A R を持つ。システムバス S Y S B U S からの読み書き操作はデコーダにより制御する。スタンバイモード制御レジスタ S T B C R は現在のスタンバイモードに対応する値を保持する。また、システムバス S Y S B U S からのスタンバイモード制御レジスタ S T B C R への書き込みは、対応する各低電流モードへの遷移要求となる。ここではスタンバイ制御回路 S T B Y C は、第 1 スタンバイモード、第 2 スタンバイモード、第 3 スタンバイモードへの遷移又はこれらのモードからの復帰を制御するように構成されている。なお、第 1 スタンバイモードへの遷移または復帰は、 C P U がクロック発生回路 C P G に直接クロック停止を指示することでも可能である。

## 【 0 1 1 5 】

ブートアドレスレジスタ B A R は、第 2 スタンバイモードから復帰しリセットを解除した際、 C P U が最初に実行する命令のアドレスを保持する。なお、この例では、第 2 スタンバイモードへの遷移要求をスタンバイモード制御レジスタ S T B C R への書き込みにより与えるが、スリープ命令やスタンバイ命令などの専用命令の利用やスタンバイモード制御レジスタ S T B C R と専用命令との組み合わせにより遷移を要求することも可能である。その場合、 C P U は、図示しないスリープ要求応答線を介して遷移要求をスタンバイ制御回路 S T B Y C に伝えることで実現できる。

## 【 0 1 1 6 】

スタンバイ制御回路 S T B Y C に含まれる同期化回路 S Y N C はチップ外部からの割り込み要求 I R Q を外部クロック信号 R C L K に同期化する。電流モード制御順序回路 S T B Y C - F S M はスタンバイモードの遷移・復帰の必要性を判別し、必要ならば遷移・復帰のシーケンスを出力する。入力はスタンバイモードレジスタ S T B C R の値、割り込み要求 I R Q 、遷移・復帰時のシーケンスの中でどのステップを実行しているかを示す状態保持レジスタ S T A T E 、出力はスタンバイ制御回路 S T B Y C の出力と、現在第 2 スタンバイモードかどうかを示す第 2 スタンバイモード信号 S T B Y 2 - M O D E である。

## 【 0 1 1 7 】

外部からの割り込み要求信号 I R Q を受けて第 2 スタンバイモードから復帰する際には、内部メモリ U R A M や外部メモリに退避した情報を C P U 等の第 1 領域 A E 1 にある各回路モジュールに戻した後に、割り込み要求信号 I R Q に対応した割り込み処理を行う必要がある。この割り込み処理は所定の命令を実行することにより行われる。したがって、第 2 スタンバイモードから復帰する際には、復帰後に最初に実行すべき命令が格納されているメモリのアドレスを保持しておく必要がある。そこで、第 2 スタンバイモードから復帰する際に最初に実行する命令を格納しているメモリのアドレスを保持するためのブートアドレスレジスタ B A R を設け、第 2 スタンバイモードに遷移する際にブートアドレスレジスタ B A R に実行開始アドレスを設定する構成としている。なお、第 2 スタンバイモードから復帰する際の実行開始アドレスを常に同じにすることも可能である。この場合には、ハードワイヤードで構成して第 2 スタンバイモードへの遷移時の実行アドレスの設定を省略することも可能である。図 3 6 の構成によれば、ブートアドレスレジスタ B A R を設けることで、ソフトウェア作成者が復帰後の実行開始アドレスを自由に設定することを可

10

20

30

40

50

能とし、第2スタンバイモード復帰時に必要なプログラムをメモリ空間の任意の位置に配置することを可能としている。

#### 【0118】

これに対し、第3スタンバイモードからの復帰は常にリセット処理であるため、ブートアドレスINIT-VECが最初に実行される。図36の構成では、セレクタSEL1を設け、電流モード制御順序回路STBYC-FSMから第2スタンバイモード信号STBY2-MODEを出力し、CPU実行開始アドレスRST-VECをブートアドレスレジスタBARに格納されたアドレスと通常リセット時のブートアドレスINIT-VECのいずれかを選択する構成としている。これにより、第3スタンバイモードから復帰するためにリセット処理をする際には、ブートアドレスINIT-VECを出力し、第2スタンバイモードからの復帰時だけ、ブートアドレスレジスタBARに保持されるアドレスから命令を実行する機能が実現される。なお、第1スタンバイからの復帰は、内部クロック信号を供給開始した後、通常動作モード時の割り込み処理と同様に割込み要求IRQの種類に対応したアドレスから命令が読み出される。10

#### 【0119】

また、図36の構成では、第2スタンバイモード又は第3スタンバイモードから復帰する際の実行開始アドレスをスタンバイ制御回路STBYCで決定し、CPUに入力する構成を取っている。これに対して、CPUに復帰後の実行開始アドレスを保持するレジスタを設け、このレジスタを不揮発FFを使用してハードウェアで退避回復する構成を取ることも可能である。20

#### 【0120】

以上、不揮発FFを部分的に採用した場合のスタンバイ制御回路STBYCの構成について述べたが、第1領域AE1に含まれる全てのFF及びレジスタを不揮発FFで置き換えてよい。このようなシステムでは割り込みによる復帰に際し、CPU（回路モジュール）内の情報が全て保持されているため、CPU実行開始アドレスRST-VECで値を書き込む必要は無くなる。したがって、このようなシステムでは、ブートアドレスレジスタBAR、セレクタSEL1を除いて構成できる。

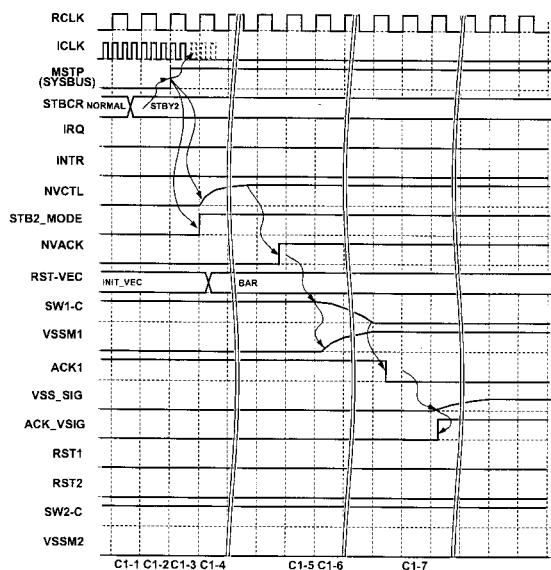

#### 【0121】

図37と図38を用いて、第2スタンバイモードSTBY2への遷移と通常動作モードNORMALへの復帰のシーケンスを説明する。まず、図37は通常動作モードから第2スタンバイモードSTBY2に遷移するシーケンスである。サイクルC1-1においてシステムバスSYSBUSからスタンバイモード制御レジスタSTBCRに第2スタンバイモードを意味する値STBY2が書き込まれる。スタンバイ制御回路STBYCはサイクルC1-2においてその値を読み、サイクルC1-3においてシステムSYSBUSを通じてモジュールストップ信号MSTOPを「1」にして、第1領域AE1へのクロック供給を止める。次に、サイクルC1-4において第2スタンバイモード信号STBY2-MODEと不揮発FF制御信号NVCTLとを「1」として、第1領域AE1にあるモジュール内のフリップフロップの情報を不揮発FFの情報保持部へ退避させる。その後、不揮発FFの制御信号NVCTLが全ての不揮発FFを制御し終わったことを、アクノレッジ信号NVACKを「1」とすることで電流モード制御順序回路STBYC-FSMへ通知する。サイクルC1-5でアクノレッジ信号NVACKが「1」であることを検出して、サイクルC1-6で電流モード制御順序回路STBYC-FSMは電源スイッチSW1の制御信号SW1-Cを「0」とする制御を実施する。その結果、第1領域AE1の電源が遮断され、第1領域AE1の接地レベルVSSM1は徐々に上昇する。電源スイッチSW-1が完全に遮断されたことは、制御信号SW1-Cが完全に0となったことにより検出し、これをACK1信号で電流モード制御順序回路STBYC-FSMへ通知する。サイクルC1-7において、電流モード制御順序回路STBYC-FSMはACK1信号が「0」となったことを検出し、その後、電流モード制御順序回路STBYC-FSMは不揮発FFの情報保持回路用電源VSS-SIGを不揮発回路の低リーク化のための電圧制御を実施する。このとき、電流モード制御順序回路VSS-SIGが電圧制御状態にあること304050

をACK\_VSIG信号で電流モード制御順序回路STBYC-FSMへ伝達することにより、電流モード制御順序回路STBYC-FSMは不揮発FFの状態を把握することができる。これで電源オン状態から不揮発FFで情報を保持しつつ電源遮断するための遷移が完了する。

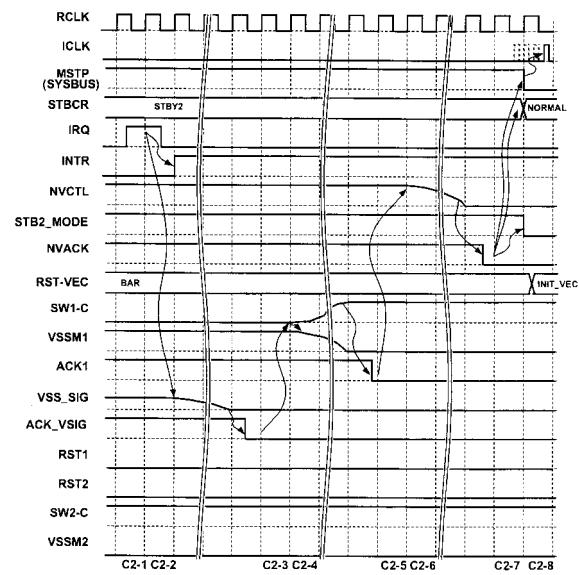

#### 【0122】

次に、図38は第2スタンバイモードから割り込みにより復帰するシーケンスである。サイクルC2-1で割込みが発生し割り込み要求信号IRQが「1」になる。スタンバイ制御回路STBYCはサイクルC2-2においてこれを受理し、第2スタンバイモード復帰後の割り込み要求INTRをアサートするとともに、情報保持回路用電源VSSSIGの電圧レベルをグランドへ戻す動作を実施する。サイクルC2-3で電流モード制御順序回路STBYC-FSMはACK\_VSIG信号が「0」であることを検出し、情報保持回路用電源VSSSIGが0Vになったことを受理する。ACK\_VSIG信号が「0」になったことを受けて、電流モード制御順序回路STBYC-FSMはサイクルC2-4で電源SW1の制御信号SW1-Cを1にして第1領域AE1の電源を投入する。これにより第1領域AE1の接地レベルVSSM1は0Vへ駆動される。その後、電源スイッチが完全にオンになったことを検出しACK1信号が「1」になると、電流モード制御順序回路STBYC-FSMはサイクルC2-5でACK1信号が「1」になったことを受理する。不揮発FFの不揮発回路に退避したデータを元のラッチ部へ戻す動作はNVCTLを0とすることで実施されるが、これはサイクルC2-6で開始される。全ての不揮発FFのデータ復帰が終了したことは不揮発FF制御信号NVCTLが完全に0となったことで判別し、それはアクノレッジ信号NACKを「0」とすることで電流モード制御順序回路STBYC-FSMへ伝達される。サイクルC2-7でアクノレッジ信号NACKが「0」になったことを電流モード制御順序回路STBYC-FSMが検出し、ミュールストップMSTPを「0」として内部クロックICKLを再開させ、サイクルC2-8からCPUの動作が開始する。このとき、CPU実行開始アドレスRST-VECの値はブートアドレスレジスタBARに格納されたアドレスなので、CPUの動作開始アドレスはブートアドレスINIT-VECではなくブートアドレスレジスタBARに格納されたアドレスになる。その後、サイクルC2-8で第2スタンバイモード信号STABY2-MODEを0、スタンバイモード制御レジスタSTBCRの値を通常動作モードを示す「NORMAL」に更新し、復帰が完了する。

#### 【0123】

図33の構成では、第2スタンバイモードに遷移しても電源遮断されない第2領域AE2に内部メモリURAMがあり、内部メモリURAMに格納されたデータは第2スタンバイモード中でも保持される。そのため、不揮発FFを必要最低限の数だけ搭載する場合、内部メモリURAMを用いて不揮発FFによる退避・回復を行わない周辺回路モジュールのレジスタも退避回復することができる。まず、レジスタ値の退避は、第2スタンバイモードへの遷移を指示するスタンバイモード制御レジスタSTBCRへの書き込み以前に、退避／回復したいレジスタの値を内部メモリURAMへ転送するようなプログラムを実行することで可能となる。この場合、通常動作モードへ復帰する時にレジスタ値を回復するため、ブートアドレスレジスタBARに設定したアドレスに内部メモリURAMの値を回復するレジスタへ転送するプログラムが必要になる。なお、第2スタンバイモード中に値を保持する必要のないレジスタに対してはこれらの退避、回復処理は不要である。そのため、より高速に第2スタンバイモードから復帰したい場合には、退避回復するレジスタの数を絞ることができる。

#### 【0124】

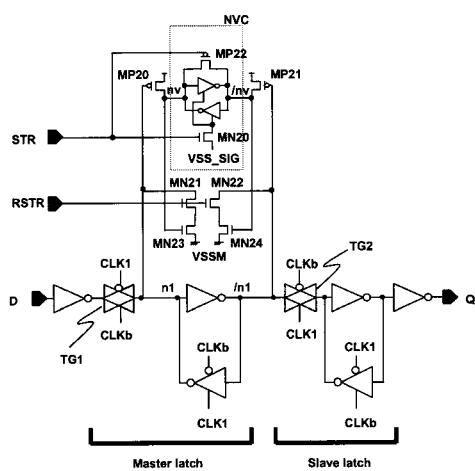

図39は不揮発FFのさらに別の構成を示している。マスタースレーブ型ラッチ回路のマスター・ラッチに不揮発回路NV Cを設ける構成をとっている。また、この構成では電源遮断時における不揮発回路NV Cへのデータ書き込みは差動アンプを用いて行われる。図10のマスタースレーブラッチとの変更点として、インバータ2段のループ、プリチャージ制御トランジスタMN20、イコライザトランジスタMP22)を含む不揮発回路NV

10

20

30

40

50

Cと、書き込み用トランジスタ(MP20、MP21)と、書き戻し用トランジスタ(MN23、MN24)と、書き戻し制御トランジスタ(MN21、MN22)と、情報保持回路用電源VSS\_SIG、不揮発回路NVCへの書き込み制御信号STRと不揮発回路NVCからマスタースレーブ型ラッチ回路へのデータ書き戻し信号RSTRが追加されている。

#### 【0125】

図40を用いて図39の不揮発FFの動作を説明する。制御信号STR及び制御信号RSTRが共にLOで、仮想電源線VSSMがグランドレベル(0V)となっている場合は通常動作が可能である。このとき、マスタースレーブ型ラッチ回路は、クロックCLKの立ち上がりエッジで入力データDがマスターラッチに取り込まれ、後段の出力Qへ伝達される。なお、制御信号STRがLOの場合はプリチャージ制御トランジスタMN20がオフし、イコライザトランジスタMP22がオンしており、さらに、マスターラッチの相補ノードn1、/n1の値に応じてトランジスタMP20、MP21のいずれかがオンするため、ノードnv、/nvは電源VDDにプリチャージされている。クロックCLKがLOになると、スレーブラッチでデータを保持して後段への出力Qを保持する。この図では時刻T1において入力Dが変化し、時刻T2の立ち上がりエッジで入力データが出力される例を示している。実線で示したのは入力がLOからHIへ変化する場合であり、破線は入力がHIからLOへ変化する場合である。

#### 【0126】

その後、電源遮断に備えたシーケンスを実施する。まず、時刻T3でクロックを停止させるが、ここではマスターラッチをラッチ状態とするため、クロックCLKはHIで停止させる。すなわち、スレーブラッチに不揮発回路NVCを設ける場合とは逆相である。その後、時刻T4で不揮発回路NVCにラッチデータを退避させる。これは制御信号STRをHIレベルとすることで実施できる。制御信号STRがHIレベルになると時刻T4でプリチャージが終了し、図39のトランジスタMP20、MP21のいずれかがオンし、もう一方がオフの状態を受けてインバータ2段のラッチにデータが退避される。例えば、入力DがHIの場合については、トランジスタMP20がオンし、トランジスタMP21がオフするため、ノードnvがHI、ノード/nvがLOになる。その後、時刻T5で電源遮断制御が実施される。ここではグランド側の電源を切断することにしている。さらにリーキ電流を削減するためには、時刻T6で情報保持回路用電源VSS\_SIGの電圧レベルを制御(例えば電源VDDが1.2Vのときに電圧レベルを0Vより大きく0.6V程度以下の電圧値に引き上げる)する。これによりスタンバイ時のリーキ電流をより削減できる効果がある。なお、図中破線で示した波形は入力データDがLOの場合を示したものである。

#### 【0127】

次に、電源を復帰させるシーケンスを説明する。時刻T7で情報保持回路用電源VSS\_SIGのレベルを0Vに戻す制御を実施し、情報保持回路用電源VSS\_SIGが0Vになったことを受けて不揮発回路NVCのデータを元のマスターラッチへ戻す制御を実施する。まず、不揮発回路NVCのデータをマスターラッチに書き込む準備を行う。すなわち、時刻T8で制御信号RSTRをHIとすることで、図39の書き込み制御用トランジスタ(MN21、MN22)がオンすることで実現する。不揮発回路NVCの保持データに応じて書き込みトランジスタ(MN23、MN24)のいずれかがオン状態になっているので、マスターラッチの相補ノードn1、/n1のいずれかをLOに駆動してデータの復帰を実現する。

#### 【0128】

マスターラッチへのデータ書き戻しは、仮想電源線VSSMをLOレベルにすることで実現させる。時刻T9で仮想電源線VSSMを0Vに向けて制御を開始し、ラッチデータが不揮発回路NVCのデータに応じて書き戻される。その後、仮想電源線VSSMが0Vとなったことを受けて、時刻T10で制御信号RSTRをLOとし、時刻T11で制御信号STRをLOとして不揮発回路NVCをプリチャージさせる。その後、クロックCLK

10

20

30

40

50

を動作させれば通常通りの動作が実現される。

【0129】

マスター・ラッチ側で電源遮断時の情報を保持するメリットについて説明する。一般にマスター・ラッチを構成するトランジスタのサイズはスレーブ・ラッチを構成するトランジスタよりも小さい。これは、スレーブ・ラッチは後段の負荷を駆動する必要があるため、その負荷に応じたトランジスタサイズが必要となるからである。電源遮断時のデータを保持するための回路部（情報保持部）は、リーク電流を削減するために小さなトランジスタサイズで構成されることが望ましいが、本体のラッチのトランジスタサイズが大きくなると情報保持部のサイズも大きくなれるを得なくなる場合がある。したがって、LSIシステムとしてクロックCLKがHIでスタンバイモードに遷移可能な場合は、比較的トランジスタサイズの小さいマスター・ラッチ側に情報保持部を設けることで、情報保持部のトランジスタサイズを小さく出来て、リーク電流の削減の効果が高くなる。10

【0130】

なお、不揮発回路NVCをスレーブ・ラッチに設けた場合（図11等）においても、不揮発回路NVCへの書き込みに差動アンプを用いることが可能である。その場合、電源遮断時のクロックCLK=LOとすればよい。

【0131】

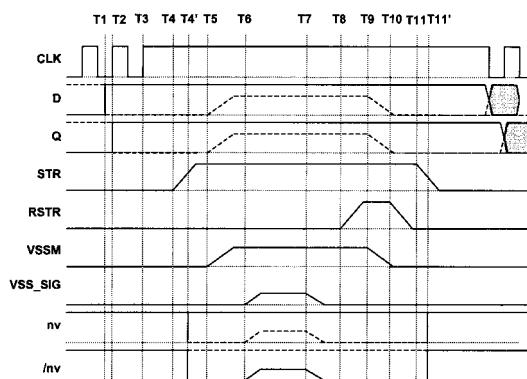

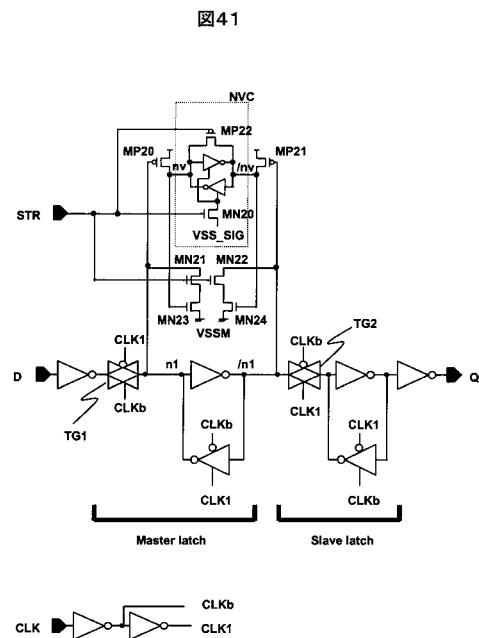

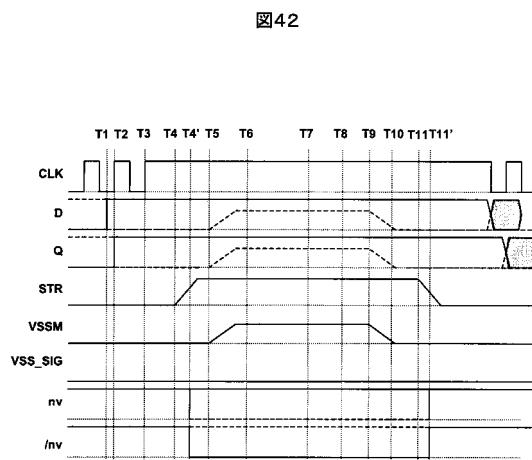

図41は不揮発FFのさらに別の構成を示し、制御信号が一本となっている点で図39の例と異なっている。したがって、不揮発回路NVCとマスター・ラッチの間の情報退避と復帰とが同時に実施されることになる。基本的な制御方法は図40と同様であり、図42を用いて説明する。制御信号STRがHIになると、図41の不揮発回路NVCに保持情報が書き込まれ、その書き込まれたデータに応じてマスター・ラッチへの0V側の経路が選択的に作られることにより、不揮発回路NVCとマスター・ラッチとが同一のデータを保持できる状態にある。この状態で電源が遮断されると、マスター・ラッチのデータは消失してしまうが、選択的にVSSMレベルへの経路が確保されるため、次に仮想電源線VSSMが0Vとなつた場合に電源遮断以前のデータが復帰されることになる。また、図41の回路では、情報保持回路用電源VSS\_SIGの電圧レベルを変化させるとVSSMレベルとVSS\_SIGレベルの関係によっては書き込み用トランジスタ（MN23、MN24）のゲート電位が上昇し、ソースに当たるVSSMとの電位差の関係から、いずれかが完全にオフとならない状態になる可能性がある。しかし、その場合でもVSSMレベルがVDLレベル方向への充電が加速されるだけであり、保持回路自体のリーク削減および十分に時間がたつた後のリーク削減には効果がある。そのため、頻繁にオン・オフする使用が想定されないLSI用途においては、図42のタイミングチャートに加えて、図40に示したような時刻T6、T7において行った情報保持回路用電源VSS\_SIGの制御を実施すれば、さらに低消費電力の効果を得ることができる。2030

【0132】

図41の構成の特徴は制御信号が1本少ないことである。一般にラッチが挿入されるところは配線が混雑する傾向にあるため、信号線数の少ないラッチを設けることでレイアウト容易化が達成され、動作速度と面積効率の点で有利になる効果がある。また、制御信号STRがHIになっている間のデータの退避復帰が電源遮断の制御、すなわちVSSMレベルの制御に連動しているため、制御が容易になるという効果もある。40

【産業上の利用可能性】

【0133】

半導体集積回路装置に関するものであり、特に低消費電力が要求されるシステムLSI又はマイクロプロセッサに適用されるものである。

【図面の簡単な説明】

【0134】

【図1】本発明の電源配線のレイアウト例を示す図である。

【図2】情報保持型フリップフロップの従来例である。

【図3】標準セルを敷き詰めて形成する半導体集積回路の例である。50

【図4】本発明の電源配線の別のレイアウト例を示す図である。

【図5】本発明の電源配線のさらに別のレイアウト例を示す図である。

【図6】接地側を電源遮断する場合に本発明を適用した際の配線を示した図である。

【図7】図7(a)は、高圧側を電源遮断する場合に本発明を適用した際の配線を示した図であり、図7(b)は電源スイッチSW1を降圧回路にて実現した回路例である。

【図8】接地側および高圧側を共に電源遮断する場合に本発明を適用した際の配線を示した図である。

【図9】(a)～(d)は、本発明の不揮発性フリップフロップのセルシンボルを示す図である。

【図10】マスタースレーブ型ラッチの従来例を示した図である。

10

【図11】本発明の不揮発フリップフロップ(マスタースレーブ型ラッチ)である。

【図12】図11に示された回路の動作波形図である。

【図13】本発明の不揮発フリップフロップ(マスタースレーブ型ラッチ)の別の例である。

【図14】図13に示された回路の動作波形図である。

【図15】本発明の不揮発フリップフロップ(スキャン機能つきマスタースレーブ型ラッチ)である。

【図16】図15に示された回路の動作波形図である。

【図17】パルスラッチの従来例を示した図である。

【図18】図18(a)は、本発明の不揮発フリップフロップ(パルスラッチ)であり、図18(b)は本発明の不揮発フリップフロップ(パルスラッチ)である。

20

【図19】図18(a)に示された回路の動作波形図である。

【図20】図18(a)または図18(b)の回路にスキャン機能をつける場合の変形例である。

【図21】本発明の不揮発フリップフロップ(センスアンプ型フリップフロップ)である。

【図22】図21に示された回路の動作波形図である。

【図23】(a),(b)は、不揮発フリップフロップの情報保持要素回路の電源接続制御を示す例である。

【図24】図18(a),(b)に示したパルスラッチのパルス発生部の変形例である。

30

【図25】(a)～(c)は、情報保持回路用電源VSS\_SIGの生成方法を示す構成例である。

【図26】図25の情報保持回路用電源VSS\_SIGの制御方法を、図11の不揮発フリップフロップに適用した場合の動作波形図である。

【図27】図11の不揮発フリップフロップを複数種類のMISFETを用いて構成した回路例である。

【図28】(a)～(d)は、不揮発フリップフロップの不揮発回路のソフトエラー耐性を高めるための変形例である。

【図29】本発明の不揮発フリップフロップの要素レイアウトの例である。

【図30】図30(a),(b)は、図29に示されたインバータ(Normal Inverter)の断面図である。

40

【図31】図31(a),(b)は、図29に示された不揮発部を構成するインバータ(Non-Volatile Inverter)の断面図である。

【図32】第1領域AE1のレイアウト図である。

【図33】本発明を用いた集積回路のチップ構成を示す図である。

【図34】低電流モードの比較表である。

【図35】各種状態間の状態遷移図である。

【図36】スタンバイ制御回路STBYCの構成例である。

【図37】通常動作モードから第2スタンバイモードに遷移する遷移シーケンスである。

【図38】第2スタンバイモードから通常動作モードへの復帰する復帰シーケンスである

50

【図39】本発明の不揮発フリップフロップ(マスタースレーブ型ラッチ)である。

【図40】図39に示された回路の動作波形図である。

【図41】本発明の不揮発フリップフロップ(マスタースレーブ型ラッチ)である。

【図42】図41に示された回路の動作波形図である。

【符号の説明】

【0135】

N V F F . . . 不揮発フリップフロップ、I N V . . . インバータ回路、N O R . . .

N O R 回路、N A N D . . . N A N D 回路、E O R . . . 排他論理和回路、M 1 . . . メタル第1層、M 2 . . . メタル第2層、M 3 . . . メタル第3層、V I A . . . 層間配線

(スルーホール)、V D D . . . 高圧側電源、V S S . . . 接地電源、V S S M . . . 仮想接地電源、V D D M . . . 仮想高圧側電源、V S S \_ S I G . . . 信号配線接地電源、

S W 1 , S W 2 . . . 電源スイッチ、S W 1 - C , S W 2 - C . . . 電源スイッチ制御信号、N V C T L . . . 不揮発フリップフロップ制御信号線群、D . . . フリップフロップ

入力、Q . . . フリップフロップ出力、C L K . . . クロック入力、R S T R , R S T R

b . . . 不揮発制御信号、S I . . . スキャン用入力信号、S O . . . スキャン用出力信号、

S E . . . スキャンイネーブル信号、N V C . . . 不揮発回路部、C I N V 1 , C I

N V 2 , C I N V 3 . . . クロックトインバータ、P S W G A T E . . . 電源スイッチ用

M I S F E T ゲート制御信号、N V , N V b . . . 不揮発回路の内部ノード、G A T E 1

, G A T E 2 . . . V S S \_ S I G 発生回路ドライバ制御信号、H V T I N V . . . しきい値の大きなインバータ、L V T I N V . . . しきい値の小さいインバータ、H V T T M

G . . . しきい値の大きいトランスマッシュョンゲート、L V T T M G . . . しきい値の小

さいトランスマッシュョンゲート、p o l y . . . ポリシリコン層、V B P . . . P型M I

S F E T 基板電源、V B N . . . N型M I S F E T 基板電源、S M B L . . . セル枠シン

ボル、P L . . . P型M I S F E T 拡散層、N L . . . N型M I S F E T 拡散層、N W .

. . . P型M I S F E T 用ウエル層、P W . . . N型M I S F E T 用ウエル層、D N W .

. . . 3重ウエル用の絶縁用ウエル、P S U B . . . P型シリコン基板、R C L K . . . 外部

クロック信号、I C L K . . . 内部クロック信号、C P U . . . 中央処理装置、I P 1 ,

I P 2 . . . 周辺回路モジュール、U R A M . . . 内部メモリ、S T B Y C . . . スタン

バイ制御回路、S Y S B U S . . . システムバス、R S T , R S T 1 , R S T 2 . . . リ

セット信号、I R Q . . . 割込み要求信号、I N T R . . . 割込み信号、P R A , P R B

, P R C , P R D , P R E , P R F , P R G , P R H . . . 電源リング、S T B C R . .

. . . スタンバイモード制御レジスタ、S T B Y 1 . . . 第1スタンバイモード、S T B Y 2

. . . 第2スタンバイモード、S T B Y 3 . . . 第3スタンバイモード。

【図1】

【図2】

【図3】

図 3

【図4】

図 4

【図5】

図 5

【図6】

図 6

【図7】

図 7

(b)

【図8】

図 8

【図9】

【図10】

【図11】

【図12】

【図13】

図 13

【図14】

図 14

【図15】

図 15

【図16】

図 16

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

図23

【図24】

図24

【図25】

図 25

【図26】

図 26

【図27】

図 27

【図28】

図 28

【 図 2 9 】

【図30】

図 29

図 30

【図31】

【図32】

図 31

図 32

【図33】

【図34】

図 33

図 34

| 状態    | 電源の状態           |                 |     | 遷移手法    | 復帰手法   | 復帰時間   | 消費電流   | 内部情報 |

|-------|-----------------|-----------------|-----|---------|--------|--------|--------|------|

|       | AE1             | AE2             | AE3 |         |        |        |        |      |

| 通常動作  | ON              | ON              | ON  |         |        |        | 数100mA | 不揮発  |

| STBY1 | OFF             | ON<br>(CLK OFF) | ON  | STBCR設定 | 外部割り込み | 数100us | ~100uA | 不揮発  |

| STBY2 | ON<br>(CLK OFF) | ON<br>(CLK OFF) | ON  | STBCR設定 | 外部割り込み | 数100us | 数10mA  | 不揮発  |

| STBY3 | OFF             | OFF             | ON  | STBCR設定 | リセット   | 数100ms | ~10uA  | 揮発   |

| 電源オフ  | OFF             | OFF             | OFF |         |        |        |        | 揮発   |

【図35】

【図36】

図 35

図 36

【図37】

図37

【図38】

図38

【図39】

図39

【図40】

図40

【図41】

【図42】

## フロントページの続き

| (51)Int.Cl. <sup>7</sup> | F I         | テーマコード(参考) |

|--------------------------|-------------|------------|

| H 03K 3/3562             | H 01L 21/82 | L          |

| H 03K 19/00              | H 03K 3/356 | C          |

| H 03K 19/0175            | H 03K 3/356 | D          |

|                          | H 03K 3/356 | B          |

|                          | H 03K 19/00 | 101R       |

F ターム(参考) 5F038 BH03 BH19 CA02 CA17 CD02 CD03 CD05 CD06 CD12 CD16

DF01 DF04 DF08 DF11 DF17 EZ09 EZ20

5F064 BB02 BB09 BB19 BB26 BB37 CC09 DD02 DD25 EE10 EE16

EE22 EE42 EE52 EE54 FF07 FF36 HH06

5J034 AB03 CB01 DB08

5J043 AA03 HH01 JJ10 KK01 KK06

5J056 AA00 BB17 BB53 BB57 CC00 CC14 DD13 DD29 EE06 FF01

FF07 FF08 GG14 KK00 KK01 KK02