(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6280985号

(P6280985)

(45) 発行日 平成30年2月14日(2018.2.14)

(24) 登録日 平成30年1月26日(2018.1.26)

(51) Int.Cl.

HO1P 5/18 (2006.01)

HO3H 7/48 (2006.01)

F 1

HO1P 5/18

HO3H 7/48D

A

請求項の数 19 (全 20 頁)

(21) 出願番号 特願2016-507692 (P2016-507692)

(86) (22) 出願日 平成26年4月11日 (2014.4.11)

(65) 公表番号 特表2016-518080 (P2016-518080A)

(43) 公表日 平成28年6月20日 (2016.6.20)

(86) 國際出願番号 PCT/US2014/033863

(87) 國際公開番号 WO2014/169247

(87) 國際公開日 平成26年10月16日 (2014.10.16)

審査請求日 平成29年4月4日 (2017.4.4)

(31) 優先権主張番号 61/811,455

(32) 優先日 平成25年4月12日 (2013.4.12)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 503031330

スカイワークス ソリューションズ、イン

コーポレイテッド

S K Y W O R K S S O L U T I O N S,

I N C.

アメリカ合衆国、O 1 8 0 1 マサチュー

セッツ州、ウォーバーン、シリバン・ロード

、20

(74) 代理人 100083806

弁理士 三好 秀和

(74) 代理人 100095500

弁理士 伊藤 正和

(74) 代理人 100111235

弁理士 原 裕子

最終頁に続く

(54) 【発明の名称】セルラー用途向けの小型無線方向性結合器

## (57) 【特許請求の範囲】

## 【請求項 1】

方向性結合器であって、入力ポートと、出力ポートと、結合ポートと、バラストポートと、

直列接続された複数のインダクタを含むインダクタの一次連鎖であって、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、

直列接続された複数のインダクタを含むインダクタの二次連鎖であって、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、を備え、前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、前記インダクタの一次連鎖は、2つのインダクタを含み、

10

20

前記インダクタの二次連鎖は、2つのインダクタを含み、

前記インダクタの物理配置は、第1の一次連鎖インダクタ、第1の二次連鎖インダクタ、第2の一次連鎖インダクタ、及び第2の二次連鎖インダクタの交互パターンからなる、方向性結合器。

**【請求項2】**

方向性結合器であって、

入力ポートと、

出力ポートと、

結合ポートと、

バラストポートと、

10

直列接続された複数のインダクタを含むインダクタの一次連鎖であって、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、

直列接続された複数のインダクタを含むインダクタの二次連鎖であって、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、

前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、

20

を備え、

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、

前記インダクタの一次連鎖は、2つのインダクタを含み、

前記インダクタの二次連鎖は、2つのインダクタを含み、

前記インダクタの物理配置は、2つの二次連鎖インダクタの外側に配置される2つの一次連鎖インダクタからなり、

前記インダクタの物理配置は、第1の一次連鎖インダクタ、第1の二次連鎖インダクタ、第2の二次連鎖インダクタ、及び第2の一次連鎖インダクタのパターンに続く、方向性結合器。

**【請求項3】**

30

方向性結合器であって、

入力ポートと、

出力ポートと、

結合ポートと、

バラストポートと、

直列接続された複数のインダクタを含むインダクタの一次連鎖であって、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、

直列接続された複数のインダクタを含むインダクタの二次連鎖であって、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、

前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、

を備え、

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、

前記インダクタの一次連鎖は、2つのインダクタを含み、

前記インダクタの二次連鎖は、2つのインダクタを含み、

前記インダクタの物理配置は、2つの二次連鎖インダクタに隣接して配置される2つの一

50

次連鎖インダクタからなり、

前記インダクタの物理配置は、第1の一次連鎖インダクタ、第2の一次連鎖インダクタ、第1の二次連鎖インダクタ、及び第2の二次連鎖インダクタのパターンに続く、方向性結合器。

**【請求項4】**

前記入力ポート及び前記第1の二次連鎖インダクタの前記結合ポートから離れる側と接続される第3の補償キャパシタを更に備える、請求項1から3のいずれか一項の方向性結合器。

**【請求項5】**

前記入力ポート及び前記出力ポートと接続される第4の補償キャパシタを更に備える、請求項4の方向性結合器。10

**【請求項6】**

方向性結合器であつて、

入力ポートと、

出力ポートと、

結合ポートと、

バラストポートと、

直列接続された複数のインダクタを含むインダクタの一次連鎖であつて、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、20

直列接続された複数のインダクタを含むインダクタの二次連鎖であつて、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、

前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、

誘電体層と

を備え、

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、

前記インダクタは、らせん状導電トレースであり、

前記インダクタの一次連鎖及び前記インダクタの二次連鎖は、異なる金属層上に位置付けられる、方向性結合器。

**【請求項7】**

方向性結合器であつて、

入力ポートと、

出力ポートと、

結合ポートと、

バラストポートと、

直列接続された複数のインダクタを含むインダクタの一次連鎖であつて、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、40

直列接続された複数のインダクタを含むインダクタの二次連鎖であつて、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、

前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、

誘電体層と

50

を備え、

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、

前記インダクタは、らせん状導電トレースであり、

前記方向性結合器は、

前記入力ポートを第1の一次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第1の一次アンダーパスと、

前記第1の一次連鎖らせん状導電トレースを第2の一次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第2の一次アンダーパスと、

前記結合ポートを第1の二次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第1の二次アンダーパスと、

前記第1の二次連鎖らせん状導電トレースを第2の二次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第2の二次アンダーパスと、

を更に備える、方向性結合器。

**【請求項8】**

前記一次連鎖を前記二次連鎖と接続する少なくとも1つの容量性スタブを更に備える、請求項7の方向性結合器。

**【請求項9】**

前記一次連鎖は、第1の予め定義された幅を有し、

前記二次連鎖は、第2の予め定義された幅を有し、

前記一次アンダーパスは、第3の予め定義された幅を有し、

前記二次アンダーパスは、第4の予め定義された幅を有し、

前記一次連鎖は、第5の予め定義された幅によって前記二次連鎖から隔てられる、請求項7の方向性結合器。

**【請求項10】**

前記第1の予め定義された幅は、前記第2の予め定義された幅よりも長い、請求項9の方向性結合器。

**【請求項11】**

前記第3の予め定義された幅は、前記第1の予め定義された幅よりも長く、

前記第4の予め定義された幅は、前記第2の予め定義された幅及び前記第5の予め定義された幅と実質的に等しい、請求項10の方向性結合器。

**【請求項12】**

前記第1の予め定義された幅は $5 \mu m$ であり、

前記第2の予め定義された幅は $2.5 \mu m$ であり、

前記第3の予め定義された幅は $20 \mu m$ であり、

前記第4の予め定義された幅は $2.5 \mu m$ であり、

前記第5の予め定義された幅は $2.5 \mu m$ である、請求項11の方向性結合器。

**【請求項13】**

$105 \mu m \times 85 \mu m$ のフットプリント面積を有する、請求項12の方向性結合器。

**【請求項14】**

$130 \mu m \times 110 \mu m$ のフットプリント面積を有する、請求項12の方向性結合器。

**【請求項15】**

前記誘電体層は、半導体基板上にある、請求項6の方向性結合器。

**【請求項16】**

前記誘電体層は、低温同時焼成セラミックス( L T C C )基板上にある、請求項6の方向性結合器。

**【請求項17】**

前記誘電体層は、薄膜回路基板上にある、請求項6の方向性結合器。

**【請求項18】**

方向性結合器であって、

入力ポートと、

10

20

30

40

50

出力ポートと、

結合ポートと、

バラストポートと、

直列接続された複数のインダクタを含むインダクタの一次連鎖であって、前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される、インダクタの一次連鎖と、

直列接続された複数のインダクタを含むインダクタの二次連鎖であって、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される、インダクタの二次連鎖と、

10

前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、

前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、

誘電体層と

を備え、

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合され、

前記インダクタは、らせん状導電トレースであり、

前記誘電体層は、積層基板上にある、方向性結合器。

**【請求項19】**

前記インダクタの一次連鎖は、前記インダクタの二次連鎖と離間し、平行であり、かつ部分的に同一の広がりを有する関係で配置される、請求項7の方向性結合器。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

(関連出願の相互参照)

本願は、2013年4月12日付けで出願されたMINIATURE RADIO FREQUENCY DIRECTIONAL COUPLER FOR CELLULAR APPLICATIONSと題する米国仮特許出願第61/811,455号の関連出願であり、この仮特許出願の優先権の利益を主張し、その全体が本明細書に参照により援用される。

30

**【0002】**

本開示は、無線(RF)回路部品に関するものであり、より具体的には、小型化されたRF方向性結合器に関するものである。

**【背景技術】**

**【0003】**

方向性結合器は、予め定義された量により、ある信号経路から別の信号経路への送信電力の一部を結合するために使用されるパッシブデバイスである。従来、これは、互いに閉物理近接に2つの信号経路を配置することにより実現され、一方に伝わるエネルギーは他方に伝えられる。この特性は、電力監視及び制御、試験及び測定などを含む複数の異なる用途にとって有益である。

40

**【0004】**

方向性結合器は、入力ポート(P1)、出力ポート(P2)、結合ポート(P3)及びアイソレート又はバラストポート(isolated or ballasting port)(P4)を含む4ポートデバイスである。P1へ供給されるRF信号の入力電力は、P3へ伝えられる入力電力の一部を定義する結合係数に応じてP3へ結合される。P1での電力の残りの部分は、P2へ伝達され、理想的な場合には、P4へは伝達されない。前進波及び後進波が隔てられる度合いは、結合器の指向性であり、また、理想的な場合には、無限大である。指向性は、S31(結合係数)とS32(リバースアイソレーション(reverse isolation))との差としても定義されてもよい。しかし、実際の実装では、信号の一部のレベルは、P3及びP4の双方へ伝えられるが、P4へ

50

のバラスト抵抗の追加は、電力の一部を消散してしまう。

【0005】

このようなR F方向性結合器で使用される伝送線の型は、同軸線、ストリップライン及びマイクロストリップラインを含む。幾何学的大きさは、与えられた結合係数についての送信された信号の波長に比例する。集中定数部品を使用する方向性結合器は、従来から知られているが、このようなデバイスも大きさが大きくなる。これらのデバイスは、セラミック基板及び薄膜プリント基板で実装され、 $2 \times 1 . 6 \text{ mm}$ かつ $1 . 6 \times 0 . 8 \text{ mm}$ 超のフットプリントを有し、これは、半導体ダイの実装よりも大きい。伝送線の相対的に大きな物理結合面積にもかかわらず、このような方向性結合器は、10 dB程度の指向性のみを有する。得られる電力制御精度は、約 $+/-0 . 45 \text{ dB}$ である。このような性能は、アンテナにおいて高い電圧定在波比 (voltage standing wave ratios (VSWR)) が可能なモバイルコミュニケーションを含む多くの用途向けに不適切である。 10

【0006】

集中定数回路に代えて、方向性結合器は、集積パッシブデバイス (integrated passive devices (IPD)) 技術に基づいてもよく、ウェーハレベルチップスケールパッケージ (wafer level chip scale packaging (WL-CSP)) で実装されてもよい。フットプリントの制限により、半導体ダイ上の方向性結合器の実装は、一般的には、マイクロ波及びミリ波動作周波数に限定される。これらのタイプの方向性結合器は、2つの結合インダクタを使用する。オン-ダイ実装用に適したこのような結合器は、小さい幾何学大きさにより、低レベルの指向性を示す。出力ポート (P2) でのミスマッチにより、反射された信号は、結合ポート (P3) に漏洩し、元の結合信号と混ざり、それにより、出力ポート P2への伝搬電力の測定に高レベルの不確実性をもたらす。高い結合係数が可能であり、内巻きマイクロストリップライン結合インダクタのターン数を増加するが、指向性は低いままである。 20

【0007】

基本的な結合インダクターアーキテクチャの改善は、米国特許第7,446,626号に開示される。結合インダクタに加えて、小さな形状にもかかわらず、高レベルの指向性 (60 dB程度) を提供すると理解される補償キャパシタ及び補償抵抗が存在する。低いインダクタンス値を使用することにより、低い挿入損失が得られる。しかし、このような初期の方向性結合器にはいくつかの欠点がある。使用される定数集中キャパシタは、制限された電圧レベルを持続することしかできない。典型的な金属-絶縁体-金属 (metal-insulator-metal (MIM)) キャパシタでは、降伏電圧は、使用される特定の半導体技術に応じて、5 Vから30 Vの範囲である。容量密度を増加させるための従来技術は、金属板間の誘電体の厚さを数百オングストロームに薄くすることを含んでいますが、フットプリントが減少し、降伏電圧もそうなる。広い周波数範囲に亘って高い指向性を実現するための上述された補償抵抗の使用は、より高価な半導体プロセスが使用される必要がある点でも問題となる。いくつかの例では、補償抵抗を除くことができるが、これは、指向性の低下をもたらす。 30

【0008】

方向性結合器の更なる改善は、2011年12月21日に提出されたON-DIE RADIOPRUEQUENCY DIRECTIONAL COUPLERと題する米国特許出願第13/333,706号及び2012年6月28日に公開された米国特許出願公開第2012/0161898号に開示され、その全体が参照により本明細書に援用される。この開示は、2つの結合インダクタ及び2又は3つの補償キャパシタを使用する。補償キャパシタの使用は、これらの結合器の高電圧動作を可能にする。これは、妥当な性能で相対的に小さいサイズを可能にした。しかし、セルラー (WCDMA等) 向け設計で、約20 dBの結合係数を有することが望まれており、これは、この設計が続く場合、適正な大きさの方向性結合器及び高い関連挿入損失をもたらす。 40

【0009】

したがって、当技術分野では、挿入損失を低減するために、従来技術と比較して高いレベルの指向性及び小型化されたサイズのセルラー用途で使用されることができる改善されたR F指向性結合器の需要が存在する。

【発明の概要】

【0010】

本開示の一実施形態によれば、小型化された方向性結合器が考慮される。任意の方向性結合器と同様に、入力ポートと、出力ポートと、結合ポートと、バラストポートと、が存在する。前記結合器は、インダクタの一次連鎖と共に、インダクタの二次連鎖を更に有する。各インダクタの連鎖は、直列接続された複数のインダクタを含む。前記インダクタの一次連鎖のうちの先頭のインダクタは、前記入力ポートと接続され、前記インダクタの一次連鎖のうちの最後のインダクタは、前記出力ポートと接続される一方で、前記インダクタの二次連鎖のうちの先頭のインダクタは、前記結合ポートと接続され、前記インダクタの二次連鎖のうちの最後のインダクタは、前記バラストポートと接続される。前記方向性結合器は、前記入力ポート及び前記結合ポートと接続される第1の補償キャパシタと、前記入力ポート及び前記バラストポートと接続される第2の補償キャパシタと、を更に含む。前記インダクタの一次連鎖は、前記インダクタの二次連鎖と容量結合される。

10

【0011】

特定の実施形態では、前記インダクタの一次連鎖は、2つのインダクタ（すなわち、第2のインダクタは、連鎖の最後のインダクタである）を含んでもよく、前記インダクタの二次連鎖は、2つのインダクタ（すなわち、第2のインダクタは、連鎖の最後のインダクタである）を含んでもよい。各連鎖が2つのインダクタを含むとき、インダクタの配置は、各種の構成を取りうる。例えば、インダクタの物理配置は、交互パターンであってもよく、第1の一次連鎖インダクタ、第1の二次連鎖インダクタ、第2の一次連鎖インダクタ、及び第2の二次連鎖インダクタの順序で続く。それに代えて、前記インダクタの物理配置は、2つの一次連鎖インダクタが2つの二次連鎖インダクタの外側に配置されてもよく、前記配置は、第1の一次連鎖インダクタ、第1の二次連鎖インダクタ、第2の二次連鎖インダクタ、及び第2の一次連鎖インダクタのパターンに続く。インダクタの更に別の構成は、2つの一次連鎖インダクタが2つの二次連鎖インダクタに隣接して配置されてもよく、前記配置は、第1の一次連鎖インダクタ、第2の一次連鎖インダクタ、第1の二次連鎖インダクタ、及び第2の二次連鎖インダクタのパターンに続く。

20

【0012】

前記方向性結合器は、追加の補償キャパシタを更に含んでもよい。例えば、前記方向性結合器は、前記入力ポート及び前記第1の二次連鎖インダクタと接続される第3の補償キャパシタ及び／又は前記入力ポート及び前記出力ポートと接続される第4の補償キャパシタを更に含んでもよい。

30

【0013】

前記方向性結合器の別の実施形態は、誘電体層を更に含むと考えられ、前記インダクタは、らせん状導電トレースである。この実施形態では、前記インダクタの一次連鎖及び前記インダクタの二次連鎖は、異なる金属層上に位置付けられてもよい。この実施形態は、前記入力ポートを前記第1の一次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第1の一次アンダーパスを更に含んでもよい。前記第1の一次連鎖らせん状導電トレースを第2の一次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第2の一次アンダーパスも存在してもよい。更に、前記結合ポートを第1の二次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第1の二次アンダーパスが存在してもよい。また、前記第1の二次連鎖らせん状導電トレースを第2の二次連鎖らせん状導電トレースと接続する前記誘電体層上に形成される第2の二次アンダーパスが存在してもよい。

40

【0014】

前記方向性結合器は、前記一次連鎖を前記二次連鎖と接続する少なくとも1つの容量性スタブを更に含んでもよい。前記一次連鎖は、第1の予め定義された幅を有し、前記二次

50

連鎖は、その独自の第2の予め定義された幅を有してもよい。更に、前記一次アンダーパスは、第3の予め定義された幅を有し、前記二次アンダーパスは、第4の予め定義された幅を有し、前記一次連鎖は、第5の予め定義された幅によって前記二次連鎖から隔てられてもよい。これに関して、前記第1の予め定義された幅は、前記第2の予め定義された幅よりも長くてもよい。また、前記第3の予め定義された幅は、前記第1の予め定義された幅よりも長く、前記第4の予め定義された幅は、前記第2の予め定義された幅及び前記第5の予め定義された幅と実質的に等しくてもよい。特定の実施形態では、前記第1の予め定義された幅は、約5μmであり、前記第2の予め定義された幅は、約2.5μmであり、前記第3の予め定義された幅は、約20μmであり、前記第4の予め定義された幅は、約2.5μmであり、前記第5の予め定義された幅は、約2.5μmであってもよい。更に、前記方向性結合器は、使用目的に応じて様々な構成で配置されてもよい。例えば、前記方向性結合器は、セルラー高帯域用途で使用されるときに、約105μm×85μmのフットプリント面積を有してもよく、又はセルラー低帯域用途で使用されるときに、約130μm×110μmのフットプリント面積を有してもよい。これらの大きさは、異なる半導体ファウンドリにより提供されるレイアウトルールによるラインにあるため、特に良好に適合される。

#### 【0015】

前記誘電体層は、半導体基板、低温同時焼成セラミックス<sub>1</sub>o<sub>w</sub> t e m p e r a t u r e c o - f i r e d c e r a m i c (L T C C) 基板及び薄膜プリント基板と共に、異なる種類の積層基板を含む技術で知られる各種形態を取りうるが、これらに限定されない。インダクタの一次連鎖をインダクタの二次連鎖と容量結合するために、2つの連鎖は、平行な関係で、離間して配置されてもよい。前記方向性結合器のフットプリントを最小限にするために、2つの連鎖は、複数の逐次内巻きターンを有するらせん状構成に配置されてもよい。本発明は、添付の図面と共に読まれるときに、以下の詳細な説明を参照することにより最も良く理解されるであろう。

#### 【図面の簡単な説明】

#### 【0016】

本明細書に開示される各種実施形態のこれらの及び他の構成及び利点は、以下の詳細な説明及び図面についてより良く理解されるであろう。

#### 【0017】

30

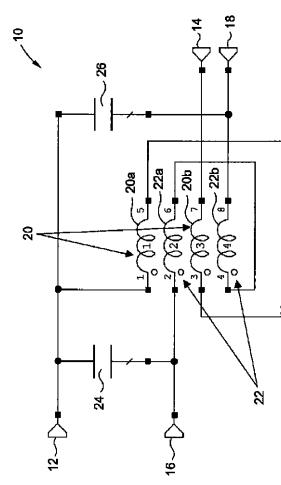

【図1】図1は、本開示に係る方向性結合器を示す回路図である。

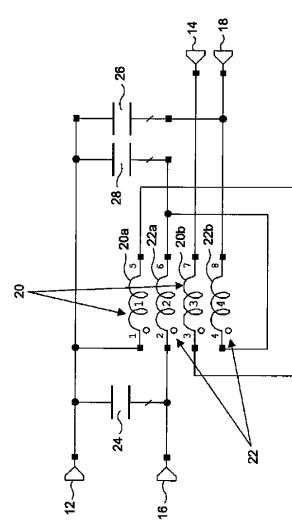

【図2】図2は、方向性結合器の第2の実施形態を示す回路図である。

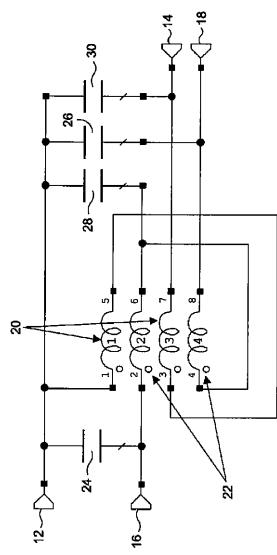

【図3】図3は、方向性結合器の第3の実施形態を示す回路図である。

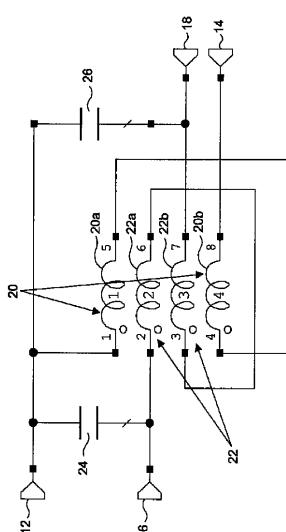

【図4】図4は、方向性結合器の第4の実施形態を示す回路図である。

【図5】図5は、方向性結合器の第5の実施形態を示す回路図である。

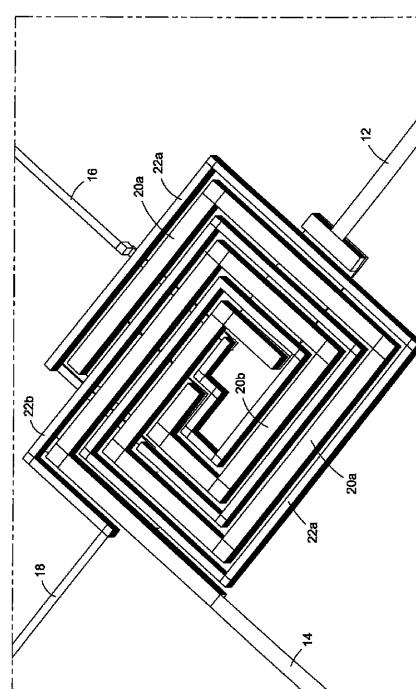

【図6】図6は、セルラー高帯域用途向けの図1に示される方向性結合器の第1の実施形態の平面図である。

【図7】図7は、図6に示される方向性結合器の第1の実施形態の詳細な平面図である。

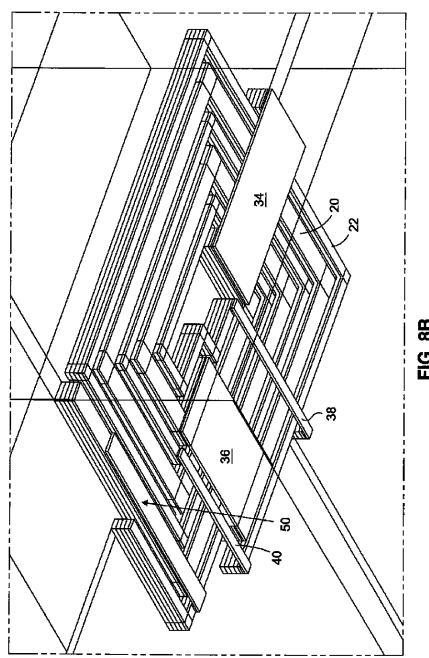

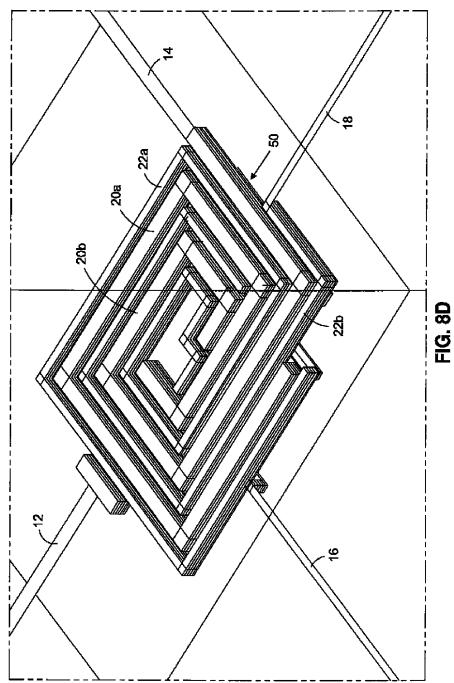

【図8】図8A-8Dは、図6に示される方向性結合器の第1の実施形態の斜視図である。

40

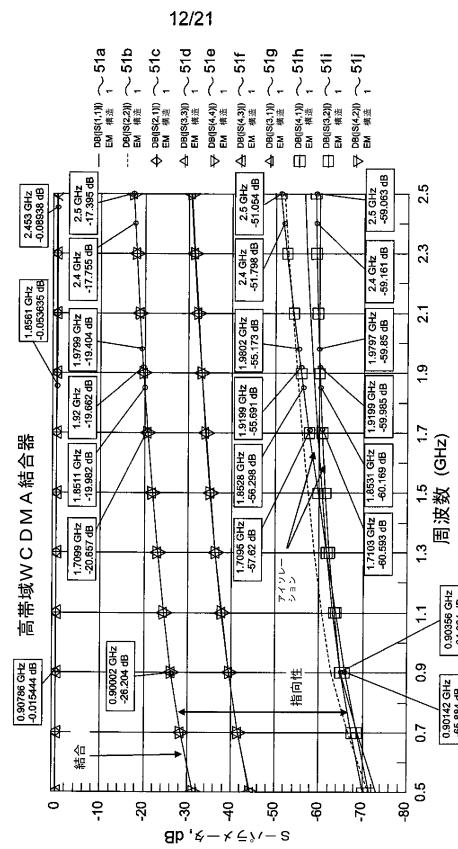

【図9】図9は、図6に示される方向性結合器の散乱パラメータ(S-パラメータ)を示すグラフである。

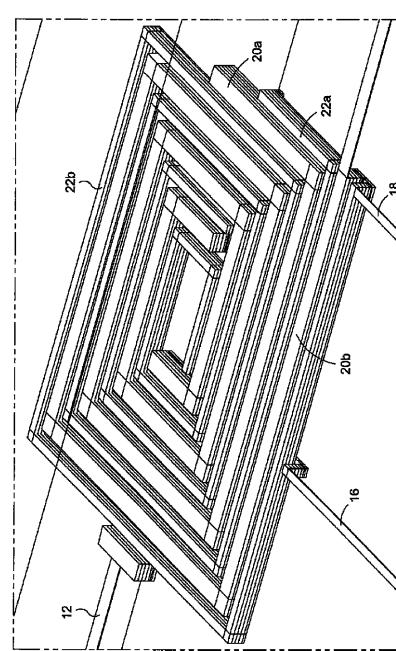

【図10】図10は、セルラー低帯域用途向けの図1に示される方向性結合器の第1の実施形態の平面図である。

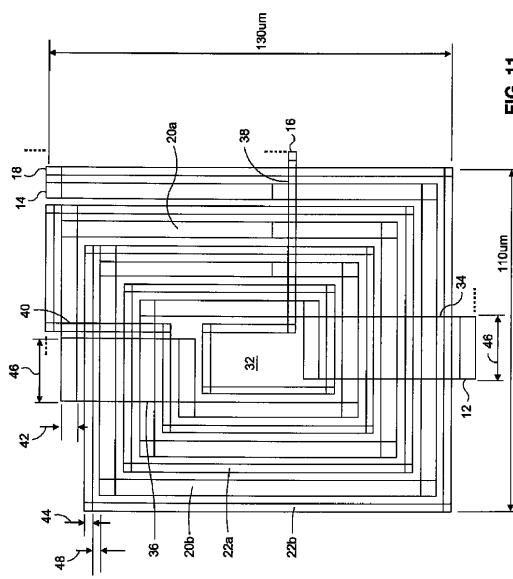

【図11】図11は、図10に示される方向性結合器の第1の実施形態の詳細な平面図である。

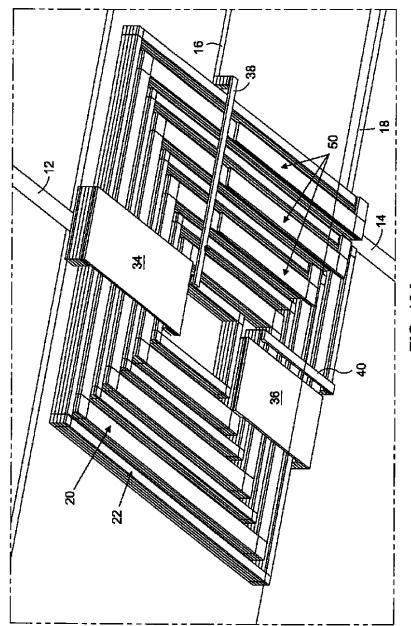

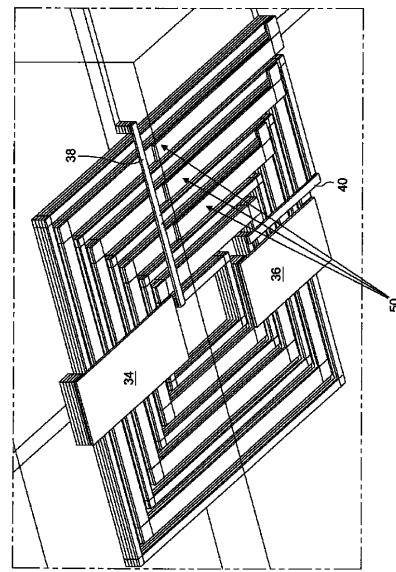

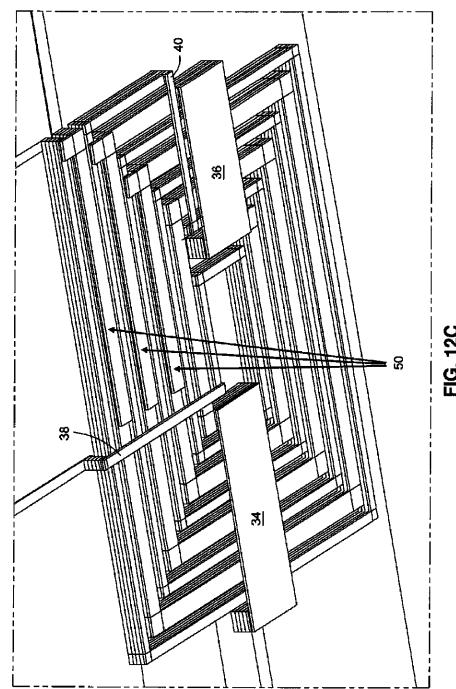

【図12】図12A-12Dは、図10に示される方向性結合器の第1の実施形態の斜視図である。

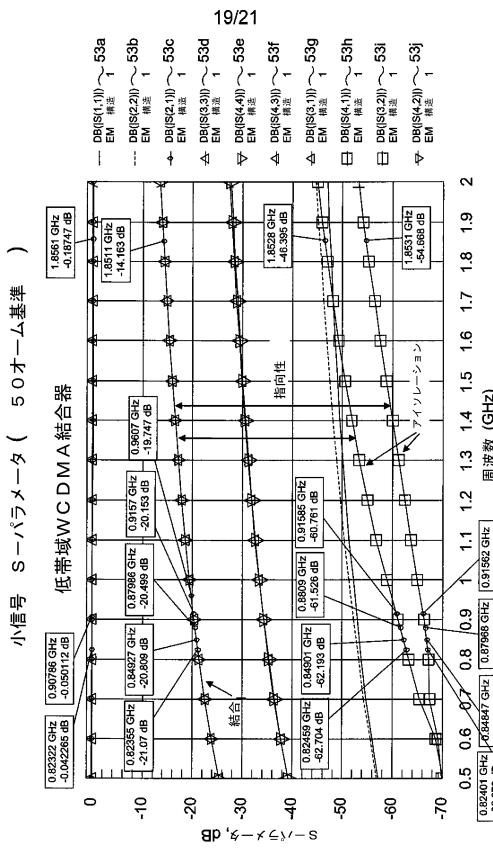

【図13】図13は、図10に示される方向性結合器の散乱パラメータを示すグラフである。

50

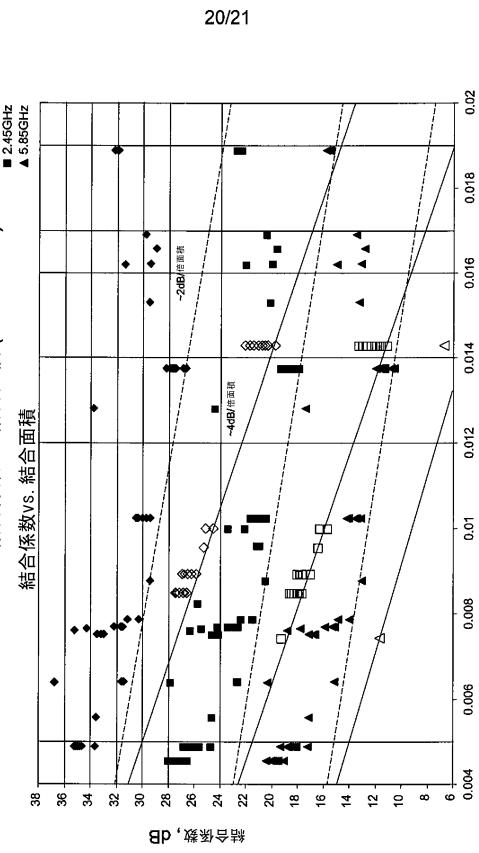

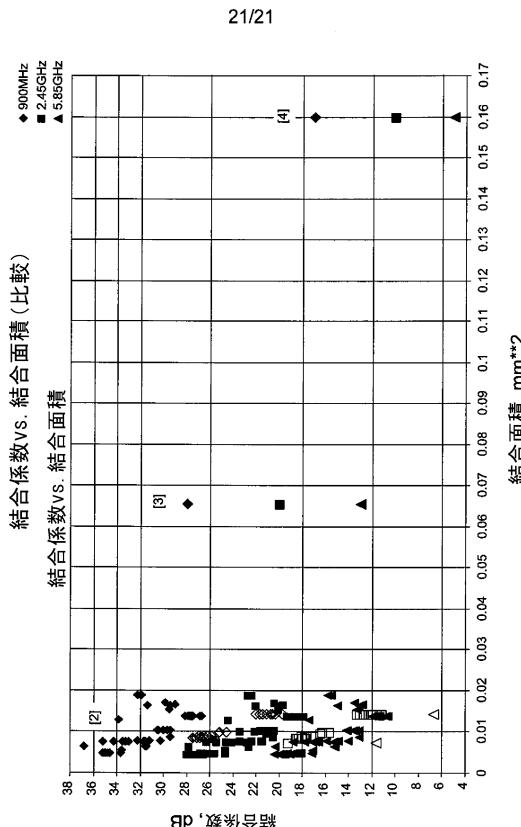

【図14】図14は、従来の結合器と比較した本開示の方向性結合器の全体フットプリント面積に関する結合係数をプロットしたグラフである。

【図15】図15は、様々な従来の結合器と比較した本開示の方向性結合器の全体フットプリント面積に関する結合係数をプロットしたグラフである。

【発明を実施するための形態】

【0018】

添付の図面と共に述べられる詳細な説明は、無線（RF）方向性結合器の現在の好ましい実施形態の説明として意図されるものであり、本発明が発揮又は使用されてもよい形態のみを示すことを意図するものではない。詳細な説明は、図示される実施形態と共に本発明の機能を述べる。しかし、同一又は同様の機能は、本発明の範囲内に包含されることが意図される異なる実施形態により実現されてもよいことが理解されるべきである。更に、第1及び第2の等のような関係語の使用は、実際のこののような関係又はこののような存在間の順序を必ずしも要求又は意味せずに、一方から他方を区別するためにのみ使用される。

【0019】

高い指向性、高い電力レベル、低い挿入損失及び他の電気部品に接続されたときの変動に対する低い感度を含む、RF方向性結合器に適用可能であるいくつかの性能目標が存在する。本開示の各種実施形態は、以下により詳細に説明するようなこれらの目標に合致し、かつ低減されたサイズ及び簡素化、低コスト実装等のような追加の実務的に有利な特性を更に有する方向性結合器を考慮する。

【0020】

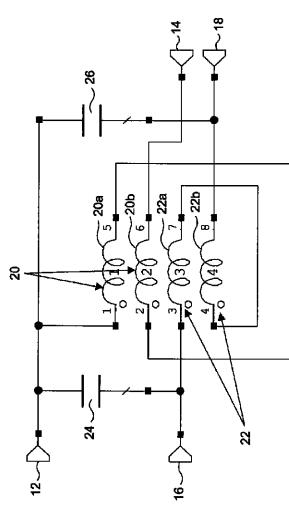

図1の回路図を参照すると、このような方向性結合器10の一実施形態は、入力ポート12と、出力ポート14と、結合ポート16と、バラストポート18と、を有する。上述したように、一般的な場合の方向性結合器については、入力ポート12に印加される信号の一部は、出力ポート14へ通過し、同じ信号の別の部分は、結合ポート16に伝えられる。理想的な場合には、信号は、バラストポート18へ伝えられないが、典型的な実装では、少なくとも最小限の信号レベルが存在する。方向性結合器10である4ポートデバイスの散乱パラメータ（S-パラメータ）を説明及び図説する目的のために、入力ポート12は、ポートP1として示され、出力ポート14は、ポートP2として示され、結合ポート16は、ポートP3として示され、バラストポート18は、ポートP4として示されてもよい。ポートのそれぞれは、部品の標準的なマッチングのために50オームの特性インピーダンスを有すると理解される。しかし、場合に応じて、インピーダンスは、標準的な50オームから変化しうる。

【0021】

方向性結合器の各種ポートの前述したネーミングコンベンションにかかわらず、信号を、ポートP4（バラストポート18）へ伝えられるポートP3（結合ポート16）に印加し、その一部分は、ポートP1（入力ポートP12）へ伝えられ、ポートP2（出力ポート14）で最小となることができる。すなわち、ポートP1及びP2は、ポートP3及びP4と機能的に逆である。しかし、指向性は、信号がポートP1に印加されたときと、信号がポートP3に印加されたときとで、異なっていてもよい。全体的に対称でないが、両方の場合とも、多くの用途向けに十分な指向性が期待される。これらのラインに沿って、ポートP2は、入力ポートとして使用されうる一方で、ポートP1は、出力ポートとして使用されうる。このような使用に応じて、ポートP4は、結合ポートであり、ポートP3は、バラストポートであるという結果になる。ポートP4が入力ポートとして使用される別の構成で、出力ポートは、ポートP3であり、ポートP2は、結合ポートであり、ポートP1は、バラストポートである。ポートP1とポートP2との損失、及びポートP3とポートP4との損失は、以下により詳細に説明される方向性結合器10の導電トレースの幅及び厚さが異なる場合に、異なっていてもよい。

【0022】

方向性結合器10は、インダクタの二次連鎖22に結合されるインダクタの一次連鎖20を更に含む。インダクタの各連鎖20, 22は、直列接続された複数のインダクタ20

10

20

30

40

50

a, 20b, 22a, 22b からなる。第1の一次連鎖インダクタ20aは、入力ポート12及び第2の一次連鎖インダクタ20bと接続される一方で、第2の一次連鎖インダクタ20bは、出力ポート14と更に接続される。第1の二次連鎖インダクタ22aは、結合ポート16及び第2の二次連鎖インダクタ22bと接続される一方で、第2の二次連鎖インダクタ22bは、バラストポート18と接続される。

【0023】

本開示の各種実施形態によれば、方向性結合器10は、入力ポート12及び結合ポート16と接続される第1の補償キャパシタ24と、入力ポート12及びバラストポート18と接続される第2の補償キャパシタ26と、を含む。図2に示されるように、方向性結合器10は、入力ポート12及び第1の二次連鎖インダクタ22aと接続される第3の補償キャパシタ28を更に含んでもよい。図3に示されるように、方向性結合器は、入力ポート12及び出力ポート14と接続される第4の補償キャパシタ30を更に含んでもよい。第3及び第4の補償キャパシタの追加は、異なる周波数における指向性の微調整を可能にする。

【0024】

一次連鎖インダクタ20a, 20bは、互いに直列接続され、二次連鎖インダクタ22a, 22bも同様に互いに直列接続されるが、4つのインダクタ20a, 20b, 22a, 22bは、任意の特定のインダクタ間の結合を最大化するために、各種の構成で配置されてもよい。例えば、図1-3に示されるように、インダクタの物理配置は、一次連鎖20と二次連鎖22との交互パターンからなってもよい。つまり、これらの図面に示されるインダクタは、以下：第1の一次連鎖インダクタ20a、第1の二次連鎖インダクタの22a、第2の一次連鎖インダクタ20b及び第2の二次連鎖インダクタ22bのパターンの構成で配置される。このようにインダクタを配置することにより、2つの一次連鎖インダクタ20a, 20bと、第1の二次連鎖インダクタ22aとの間に大きな結合が形成される。第2の二次連鎖インダクタ22bも第1の一次連鎖インダクタ20aと接続され、第2の一次連鎖インダクタ20bとの増大した結合を有する。本開示のこの実施形態は、従来の方向性結合器とは対照的に、同一のフットプリント面積に対して一次連鎖インダクタ20と二次連鎖インダクタ22との実質的に高レベルな結合を提供する。言い換えれば、本開示を使用する同一の結合係数について、従来の方向性結合器と比べて、結合されたインダクタの短い長さが、他では実現し得ない、低減された損失をもたらす。

【0025】

図4は、インダクタの別のあり得る配置を示す。特に、この実施形態では、2つの一次連鎖インダクタ20a, 20bは、2つの二次連鎖インダクタ22a, 22bの外側に配置される。すなわち、パターンは、以下、第1の一次連鎖インダクタ20a、第1の二次連鎖インダクタ22a、第2の二次連鎖インダクタ22b、第2の一次連鎖インダクタ20bのようになる。このようにインダクタを配置することにより、2つの二次連鎖インダクタ22a, 22bの間に大きな結合が形成され、それらは共に2つの一次連鎖インダクタ20a, 20bとの増大した結合を有する。この配置は、上述したように、第3のキャパシタ28及び/又は第4のキャパシタ30を同様に含みうる。

【0026】

図5は、インダクタの更に別のあり得る配置を示す。特に、この実施形態では、2つの一次連鎖インダクタ20a, 20bは、2つの二次連鎖インダクタ22a, 22bに続いて配置される。つまり、パターンは、以下、第1の一次連鎖20a、第2の一次連鎖インダクタ20b、第1の二次連鎖インダクタ22a、第2の二次連鎖インダクタ22bのようになる。このようにインダクタを配置することにより、2つの二次連鎖インダクタ22a, 22bの間に大きな結合が形成され、2つの一次連鎖インダクタ20a, 20bの間に大きな結合が形成される。また、二次インダクタ22a, 22bの双方は、一次連鎖インダクタ20a, 20bの双方と増大した結合を有する。また、この配置は、第3のキャパシタ28及び/又は第4のキャパシタ30を同様に含みうる。

【0027】

10

20

30

40

50

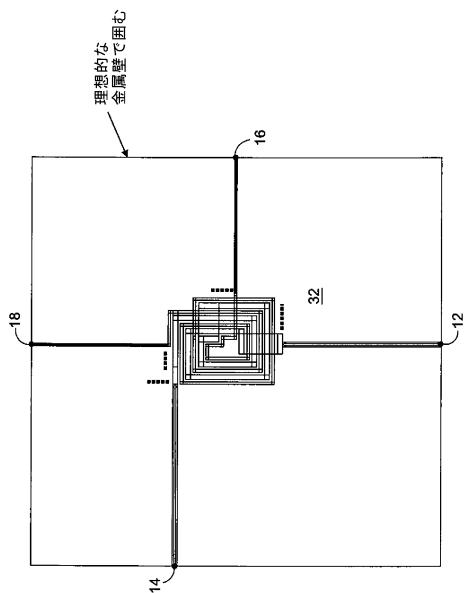

図6-9は、特定の形状、サイズ及び全体のフットプリントを有する導電トレースのような上述された各種部品を実装する方向性結合器を示す。特に、この配置は、概要レベル図のようなセルラー高帯域用途向けに最適化され、方向性結合器は、入力ポート12と、出力ポート14と、結合ポート16と、バラストポート18と、を含む。これらのポートのそれぞれは、別の部品からの接続点であってもよい各接続トレースの終端であると理解される。よって、用語「ポート」は、電気部品接続への方向性結合器10のインターフェースとしての役割を果たす任意の導電性素子を示す。図6は、構造の電磁気シミュレーションで典型的に用いられる理想的な金属壁での囲いを示す。更に、シミュレーション基準面は、破線によって示される。

## 【0028】

10

方向性結合器10の導電素子は、誘電体層32に配置され、これは、半導体基板の一部分であってもよい。低温同時焼成セラミックスlow temperature co-fired ceramic (LTCC) 及び薄膜プリント基板のような別の基板材料も可能である。方向性結合器10は、導電経路が配置される適切な誘電体基板に製造されても良いことを当業者は理解するであろう。これらのラインに沿って、導電経路は、金属のような電気伝導性材料で形成されてもよい。

## 【0029】

20

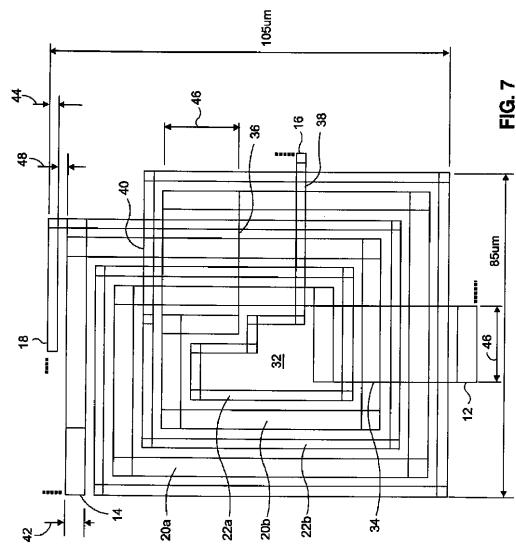

図7で最も良くみられるように、方向性結合器10は、相対的に広いトレースにより定義される、第1の一次連鎖らせん状導電トレース20aと、第2の一次連鎖らせん状導電トレース20bと、を含む。これについては、主RF信号経路に特化した一次連鎖トレース20向けである。特定の垂直なターンの用語で図示されているが、本願明細書に記載のらせん状導電トレースは、その代わりに、複数の斜角ターン又は円形ターン又は別のらせん状構成によって定義されてもよい。

## 【0030】

入力ポート12を第1の一次連鎖らせん状トレース20aと接続するために、方向性結合器10は、誘電体層32に形成される第1の一次アンダーパス34を含む。誘電体層32に形成され、第1の一次連鎖らせん状導電トレース20aを第2の一次連鎖らせん状導電トレース20bと接続する第2の一次アンダーパス36も存在する。第2の一次連鎖らせん状導電トレース20bは、その後、出力ポート14で終端する。

## 【0031】

30

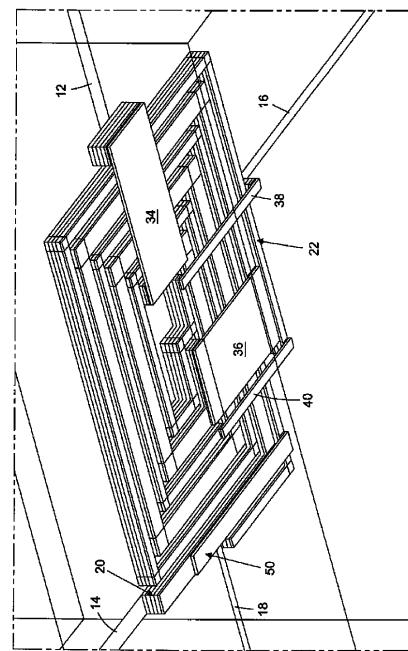

方向性結合器10は、相対的に狭いトレースによって定義される、第1の二次連鎖らせん状導電トレース22aと、第2の二次連鎖らせん状導電トレース22bと、を更に含む。結合ポート16を第1の二次連鎖らせん状導電トレース22aと接続するために、方向性結合器10は、誘電体層32に形成される第1の二次アンダーパス38を含む。誘電体層32に形成され、第1の二次連鎖らせん状導電トレース22aを第2の二次連鎖らせん状導電トレース22bと接続する第2の二次アンダーパス40も存在する。第2の二次連鎖らせん状導電トレース22bは、その後、バラストポート18で終端する。二次連鎖らせん状導電トレース22は、一次連鎖らせん状導電トレース20と連結し、離間された同一平面上にある関係で誘電体層32に配置され、かつ容量結合される。本実施形態では、一次連鎖トレース20及び二次連鎖トレース22は、単一水平面に配置される一方で、アンダーパス34, 36, 38, 40は、異なる第2の水平面に配置される。しかし、当該面は、特定の厚さを有する誘電体層32によって隔てられる。

40

## 【0032】

これらの全体長さを通じて、一次連鎖らせん状導電トレース20は、第1の幅42を定義する。本開示の一実施形態によれば、第1の幅42は5μmである。また、これらの全体長さを通じて、二次連鎖らせん状導電トレース22は、第2の幅44を定義する。第1の幅42に対して、第2の幅44は狭く、例えば、2.5μmである。二次連鎖らせん状導電トレース22は、結合RF信号経路に特化されており、よって、信号レベルが低く、そのため、狭い導電体が使用されることが理解される。また、一次アンダーパス34, 36は、第3の幅46を定義する。この第3の幅46は、挿入損失を低減し、かつ一次連鎖

50

20と二次連鎖22との別の容量結合を導入するために、第1の幅よりも広いと考えられる。一つの例示的な実施形態では、第3の幅は20μmである。これは二次アンダーパス38, 40に必ずしも必要ではないが、それらは第4の幅を定義し、第2の幅44と等しい又はほぼ等しいと考えられる。二次連鎖らせん状導電トレース22及び一次連鎖導電トレース20上の任意の与えられた点の間の距離は、一定の第5の幅48であり、そのため、二次連鎖らせん状導電トレース22の形状及び構成は、一次連鎖らせん状導電トレース20のものと同様である。一つの例示的な実施形態では、第5の幅は2.5μmである。一次連鎖らせん状導電トレース20及び二次連鎖らせん状導電トレース22と共に、図6-9に示される例示的な実施形態の全体大きさは、105μm×85μmである。一般的には、閉じた金属トレースが互いに配置され、より高いレベルの磁気及び電気結合がそれらの間になされる。トレースの配置は、使用される特定の技術によって限定される。

#### 【0033】

上記と同様に、図10-13は、セルラー用途向けの低帯域用途向けに最適化された実施形態を示す。この構成では、一次連鎖らせん状導電トレース20及び二次連鎖らせん状導電トレース22は、130μm×110μmの全体大きさを含む。なお、図8及び12は、シミュレーション目的のためにいくつかの金属で“スタック”された金属トレースを示していることに留意すべきである。金属トレースの総厚は、使用される特定の製造プロセスによって定義される。

#### 【0034】

本開示の別の態様によれば、方向性結合器10は、一次連鎖らせん状導電トレース20と二次連鎖らせん状導電トレース22との容量結合を増加させるために、誘電体層32に配置される一以上の導電回路素子を更に含んでもよい。これに関して、導電回路素子は、一次連鎖20を二次連鎖22と容量結合する容量性スタブ50であってもよい。導電容量性スタブ50は、一次連鎖トレース20又は二次連鎖トレース22のいずれかと電気的に接続されてもよい。容量性スタブの長さ及び幅の調整と共に、特定の連鎖との電気的な接続の物理点は、適切な周波数での指向性の最大レベルを可能にする。

#### 【0035】

図9のグラフを参照すると、方向性結合器10の4つのポートが与えられ、スタンバイ状態入力に応じたその電気的な態様は、一連の散乱パラメータ(scattering parameters (S-parameters))によって説明されうる。方向性結合器10の動作特性に適切な場合、一次連鎖20及び二次連鎖22は、予め設定された結合係数、つまり、一次連鎖20での信号が二次連鎖22に伝わる又は結合される度合いによって特徴付けられてもよい。結合係数は、S31に対応する、又は入力ポート12(P1)と結合ポート16(P3)との間のゲイン係数に対応する。これは、第7のプロット51gに示される。また、結合インダクタ連鎖20, 22もまた、入力ポート12と結合ポート16との間の予め定義されたアイソレーション係数によって特徴付けられる。第1のアイソレーション係数は、第9のプロット51iとして示されるS32に対応し、かつ出力ポート14(P2)と結合ポート16(P3)との間のゲイン係数である。結合インダクタ連鎖20, 22は、入力ポート12とバラストポート18との間の予め設定された第2のアイソレーション係数によって更に特徴付けられる。予め定義された第2のアイソレーション係数は、第8のプロット51hとして示されるS41に対応し、入力ポート12(P1)とバラストポート18(P4)との間のゲイン係数である。図9に示されるグラフのプロットの残りの部分は、入力ポート反射係数S11を記載する第1のプロット51aと、出力ポート反射係数S22を記載する第2のプロット51bと、入力ポート-出力ポートゲイン係数S21を記載する第3のプロット51cと、結合ポート16反射係数S33を記載する第4のプロット51dと、バラストポート18の反射係数S44を記載する第5のプロット51eと、結合ポート-バラストポートゲイン係数S43を記載する第6のプロット51fと、出力ポート-バラストポートゲイン(結合)係数S42を記載する第10のプロット51jと、を含む。

#### 【0036】

10

20

30

40

50

特定の動作周波数における結合係数と、そのような動作周波数における対応する第1及び第2のアイソレーション係数との差は、それぞれ、第1の指向性及び第2の指向性を定義する。上記で示したように、第1の指向性は、第2の指向性とは異なっており、つまり、方向性結合器10は非対称である。図9のグラフは、図6-8Dに示されるような方向性結合器のシミュレートされた例を示している。ここから分かるように、結合は、高帯域で約20dBであり、指向性は、高帯域で40dBを超える。同様に、図13は、図10-12Dに示されるような方向性結合器のシミュレートされた例を示す。ここからも分かるように、プロット53a-53jによって示されるように、結合は約20dBであり、指向性は低帯域で45dBを超え、ここで、記号は図9に対して上述されたものと同一のプロットラインを示す。

10

### 【0037】

方向性結合器の様々な最適化は、結合及び指向性を最大にしつつ、直列損失を最小にするために、使用されるスタブの数及び全体のフットプリント面積に対して可能であると明確に考えられる。実際、方向性結合器10の全体フットプリント面積は、結合係数、指向性及び直列損失に影響を与える。図14のグラフは、900MHz、2.45GHz及び5.85GHz、異なる全体フットプリント面積の結合係数を含む、各種動作周波数でプロットしている（黒塗りプロット点を有する破線により示されるような従来技術、及び白抜きプロット点を有する実線により示される本開示の両方）。一般的には、フットプリントが増大すると、結合係数は同一周波数について減少する。更に、同一周波数の同一フットプリントについて、結合係数は、上述したように、結合器の形状、及び使用されるスタブの数に応じて、変化してもよい（典型的には、1dBから2dBの範囲）。ここから分かるように、結合係数の最も高いレベルは、従来技術の結合面積の2倍あたりに2dBの割合で変化するが、本明細書に開示される構造については4dBの割合で変化する。したがって、本開示のフットプリント面積は、既存のものと比較して、同一の結合係数に対して非常に小さくなる。例えば、20dBの結合係数を有する低帯域セルラー用途向けの結合器は、以下の本開示で、約0.015mm\*\*2（約120×120μmのフットプリント）で実現され、一方で、従来技術は、0.025mm\*\*2（約165×165μmのフットプリント）を必要とする。非常に小さいフットプリントを実現することにより、製造コストを低減すると共に、挿入損失を低減することができる。同様に、図15の拡張された結合面積範囲を有するグラフは、本願の結合器（白抜きのプロット点により示される）のフットプリントが、従来から知られる既存の結合器（黒塗りのプロット点により示される）と比較してどの程度小さいかを示している。

20

### 【0038】

本願の小型化された方向性結合器10の各種実施形態は、結合係数を実質的に増加させるために、2つの一次インダクタ及び2つの二次インダクタの最小限の結合に基づく。方向性結合器は、2、3又は4つの補償キャパシタを使用し、これは、方向性結合器10に組み込まれる導電トレースの分配結合として実装される。一次及び二次インダクタは、半導体基板の異なる金属層に実装されてもよい。また、考慮される特定の構成は、各種部品の高い降伏電圧による高電力レベルを可能にする。上記で示したように、高レベルの指向性は、また、特定の動作周波数において補償キャパシタの調整に基づいて実現される。挿入損失は、特に、結合インダクタの小さな値及び補償キャパシタからの損失の低減のために、方向性結合器の考慮された構成でも最小化される。異なる周波数帯域と共に用途も、ガイドとして本開示を用いて容易に設計されうる。

30

### 【0039】

本明細書に示される詳細は、例示によるものであり、かつ本発明の実施形態の例示的な説明の目的のためのものであり、最も有益であると考えられ、かつ本発明の原理的及び概念的な態様の説明を明示的に理解されることを提供するために示される。これに関して、本発明の根本的な理解のために必要であるものよりもより詳細な本発明の詳細を示そうとするものではなく、図面を伴う詳細な説明は、本発明のいくつかの形態がどのように実際に具現化されるかを当業者に明らかにする。

40

50

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

6/21

FIG. 6

【図 7】

FIG. 7

【図 8 A】

FIG. 8A

【図 8 B】

FIG. 8B

【図 8 C】

FIG. 8C

【図 8 D】

FIG. 8D

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12 A】

FIG. 12A

【図 12 B】

FIG. 12B

【図 12 C】

FIG. 12C

【図 12 D】

FIG. 12D

【図 1 3】

FIG. 13

【図 1 4】

FIG. 14

【図 1 5】

FIG. 15

---

フロントページの続き

(72)発明者 ゴルバチョフ オレクサンドル

アメリカ合衆国 カリフォルニア州 92618 アーヴァイン スイート 200 アーヴァイン センター ドライヴ 7595 アールエフアクシス インコーポレイテッド内

審査官 岸田 伸太郎

(56)参考文献 特開昭57-068917(JP, A)

米国特許出願公開第2012/0161898(US, A1)

特開平08-307116(JP, A)

国際公開第2012/081307(WO, A1)

米国特許第03576505(US, A)

(58)調査した分野(Int.Cl., DB名)

H01P 1/00-11/00

H03H 7/48