(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7512422号

(P7512422)

(45)発行日 令和6年7月8日(2024.7.8)

(24)登録日 令和6年6月28日(2024.6.28)

(51)国際特許分類

|        |                  |        |        |

|--------|------------------|--------|--------|

| H 04 N | 19/11 (2014.01)  | H 04 N | 19/11  |

| H 04 N | 19/119 (2014.01) | H 04 N | 19/119 |

| H 04 N | 19/157 (2014.01) | H 04 N | 19/157 |

| H 04 N | 19/176 (2014.01) | H 04 N | 19/176 |

| H 04 N | 19/46 (2014.01)  | H 04 N | 19/46  |

F I

請求項の数 14 (全44頁)

(21)出願番号 特願2022-564462(P2022-564462)

(86)(22)出願日 令和4年1月18日(2022.1.18)

(65)公表番号 特表2023-524406(P2023-524406

A)

(43)公表日 令和5年6月12日(2023.6.12)

(86)国際出願番号 PCT/US2022/012741

(87)国際公開番号 WO2022/211877

(87)国際公開日 令和4年10月6日(2022.10.6)

審査請求日 令和4年10月21日(2022.10.21)

(31)優先権主張番号 17/564,583

(32)優先日 令和3年12月29日(2021.12.29)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 63/168,984

(32)優先日 令和3年3月31日(2021.3.31)

最終頁に続く

(73)特許権者 520353802

テンセント・アメリカ・エルエルシー

アメリカ合衆国 94306 カリフォルニア州 パロアルト パーク・ブルヴァード 2747

(74)代理人 100110364

弁理士 実広 信哉

100150197

(74)代理人 弁理士 松尾 直樹

リヤン・ジャオ

アメリカ合衆国・カリフォルニア・94085・サニーベール・サンタ・セシリア・テラス・723

(72)発明者 シン・ジャオ

アメリカ合衆国・カリフォルニア・95 最終頁に続く

(54)【発明の名称】 複数基準線イントラ予測と変換分割との間の調和した設計

## (57)【特許請求の範囲】

## 【請求項1】

命令を格納するメモリと、前記メモリと通信するプロセッサとを備える装置が実行する、ビデオデコーディングにおける複数基準線イントラ予測のための方法であって、前記方法は、

プロックのコーディングされたビデオビットストリームを受信するステップと、

複数のサブプロックを取得するために前記プロックを分割するステップと、

基準線を示す第1のパラメータに基づいて、前記複数のサブプロック内のサブプロックに対して複数基準線イントラ予測を実行するステップであって、前記第1のパラメータは前記基準線が非隣接基準線であることを示し、

複数の変換プロックを取得するために前記サブプロックを分割するステップと、

前記複数の変換プロックに対して前記複数基準線イントラ予測を実行するステップであつて、

前記複数の変換プロック内の第1の変換プロックが前記サブプロックの境界に位置していることに応じて、前記第1の変換プロックの前記複数基準線イントラ予測のために前記第1のパラメータによって示される基準線が使用され、

前記複数の変換プロック内の第2の変換プロックが前記サブプロックの前記境界に位置していないことに応じて、前記第2の変換プロックの前記複数基準線イントラ予測のためにデフォルト値によって示される基準線が使用される、

ステップと

を含む、ステップと

を含む、方法。

**【請求項 2】**

前記コーディングされたビデオビットストリームが、前記第1のパラメータを含み、前記複数の変換ブロックを取得するために前記サブブロックを分割する前記ステップは、前記複数の変換ブロックを取得するために、変換パラメータを使用せずに、前記サブブロックを分割するステップ

を含む、請求項1に記載の方法。

**【請求項 3】**

前記複数の変換ブロック内の変換ブロックについて、

前記サブブロックのサイズが最大変換ブロックのサイズ以下であることに応じて、前記変換ブロックのサイズが前記サブブロックの前記サイズと等しく、

前記サブブロックの前記サイズが前記最大変換ブロックの前記サイズ以上であることに応じて、前記変換ブロックの前記サイズが前記最大変換ブロックの前記サイズと等しい、

請求項1または2に記載の方法。

**【請求項 4】**

前記複数の変換ブロックの変換深度が、前記基準線が隣接基準線であると示されるかそれとも非隣接基準線であると示されるかに基づいて決定される、

請求項1に記載の方法。

**【請求項 5】**

非隣接基準線であると示された前記基準線に応じた前記複数の変換ブロックの変換深度が、隣接基準線であると示された前記基準線に応じた前記複数の変換ブロックの変換深度よりも小さいN深度であり、Nが非負の整数である、

請求項1から4のいずれか一項に記載の方法。

**【請求項 6】**

前記第1のパラメータが基準線インデックスであり、

前記基準線インデックスに基づいて導出されたコンテキストが、前記複数の変換ブロックの少なくとも1つのパラメータをパースするために使用される、

請求項1に記載の方法。

**【請求項 7】**

前記コーディングされたビデオビットストリームが、前記第1のパラメータおよび第2のパラメータを含み、前記第2のパラメータが前記複数の変換ブロックを示す、

請求項1に記載の方法。

**【請求項 8】**

前記複数の変換ブロック内の変換ブロックが、前記複数のサブブロック内の前記サブブロックよりも小さい、

請求項1から7のいずれか一項に記載の方法。

**【請求項 9】**

エントロピーデコーディング中に、前記第2のパラメータの構文が前記第1のパラメータのコンテキストとして使用される、

請求項7に記載の方法。

**【請求項 10】**

前記コーディングされたビデオビットストリームが、前記複数の変換ブロックを示す第2のパラメータを含み、

前記基準線が、前記第2のパラメータに基づいて決定される、

請求項1に記載の方法。

**【請求項 11】**

前記複数の変換ブロックの変換深度が閾値よりも大きいことに応じて、前記基準線がデフォルト選択として決定される、

請求項1に記載の方法。

10

20

30

40

50

**【請求項 1 2】**

前記コーディングされたビデオビットストリームが、前記基準線を示す前記第1のパラメータを含み、

前記複数の変換ブロック内の変換ブロックごとの前記基準線が、前記サブブロック内の各変換ブロックの相対位置に基づいて決定される、

請求項1に記載の方法。

**【請求項 1 3】**

請求項1～12のいずれか一項に記載の方法を行うように構成された

、装置。

**【請求項 1 4】**

コンピュータに、請求項1～12のいずれか一項に記載の方法を実行させるためのコンピュータプログラム。

10

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

関連出願

本出願は、2021年3月31日の出願された米国仮特許出願第63/168,984号および2021年12月29日に出願された米国非仮特許出願第17/564,583号に基づき、これらに対する優先権の利益を主張するものであり、両出願の全体が参照により本明細書に組み込まれる。

20

**【0 0 0 2】**

本開示は、ビデオコーディングおよび／またはビデオデコーディングに関し、特に、複数基準線イントラ予測および変換分割の改善された設計およびシグナリングに関する。

**【背景技術】****【0 0 0 3】**

本明細書で提供される背景技術の説明は、本開示の文脈を一般的に提示することを目的としている。本発明者らの研究は、その研究がこの背景技術の項に記載されている限りにおいて、またそれ以外の本出願の出願時に先行技術として認められない可能性のある説明の態様と共に、本開示に対する先行技術としては明示的にも暗示的にも認められない。

**【0 0 0 4】**

30

ビデオコーディングおよびビデオデコーディングは、動き補償を伴うインターピクチャ予測を使用して実行することができる。非圧縮デジタルビデオは、一連のピクチャを含むことができ、各ピクチャは、例えば $1920 \times 1080$ の輝度サンプルおよび関連するフルサンプリングまたはサブサンプリングされた色差サンプルの空間次元を有する。一連のピクチャは、例えば毎秒60ピクチャまたは毎秒60フレームの固定または可変のピクチャレート（あるいはフレームレートとも呼ばれる）を有し得る。非圧縮ビデオは、ストリーミングまたはデータ処理のための特定のビットレート要件を有する。例えば、 $1920 \times 1080$ の画素解像度、60フレーム／秒のフレームレート、および色チャネルあたり画素あたり8ビットで4:2:0のクロマサブサンプリングを有するビデオは、1.5Gbit/sに近い帯域幅を必要とする。1時間分のそのようなビデオは、600GByteを超える記憶空間を必要とする。

**【0 0 0 5】**

40

ビデオコーディングおよびビデオデコーディングの1つの目的は、圧縮による非圧縮入力ビデオ信号の冗長性の低減であり得る。圧縮は、前述の帯域幅および／または記憶空間要件を、場合によっては2桁以上低減させるのに役立ち得る。可逆圧縮と非可逆圧縮の両方、およびそれらの組み合わせを使用することができる。可逆圧縮とは、原信号の正確なコピーをデコーディングプロセスによって圧縮された原信号から再構成することができる技術を指す。非可逆圧縮とは、元のビデオ情報がコーディング時に完全に保持されず、デコーディング時に完全に回復できないコーディング／デコーディングプロセスを指す。非可逆圧縮を使用する場合、再構成された信号は原信号と同一ではない可能性があるが、原信号と再構成された信号との間の歪みは、多少の情報損失はあっても、再構成された信号

50

を意図された用途に役立てるのに十分なほど小さくなる。ビデオの場合、非可逆圧縮が多くの用途で広く採用されている。耐容できる歪みの量は用途に左右される。例えば、特定の消費者ビデオストリーミング用途のユーザは、映画やテレビ放送用途のユーザよりも高い歪みを容認し得る。特定のコーディングアルゴリズムによって達成可能な圧縮比を、様々な歪み耐性を反映するように選択または調整することができる。すなわち、一般に、歪み耐性が高いほど、高い損失および高い圧縮比をもたらすコーディングアルゴリズムが可能になる。

#### 【 0 0 0 6 】

ビデオエンコーダおよびビデオデコーダは、例えば、動き補償、フーリエ変換、量子化、およびエントロピーコーディングを含む、いくつかの広範なカタゴリおよびステップからの技術を利用することができる。

10

#### 【 0 0 0 7 】

ビデオコーデック技術は、イントラコーディングとして知られる技術を含むことができる。イントラコーディングでは、サンプル値は、以前に再構成された参照ピクチャからのサンプルまたは他のデータを参照せずに表される。一部のビデオコーデックでは、ピクチャがサンプルのブロックに、空間的に細分される。サンプルのすべてのブロックがイントラモードでコーディングされる場合、そのピクチャをイントラピクチャと呼ぶことができる。イントラピクチャおよび独立したデコーダリフレッシュピクチャなどのそれらの派生ピクチャは、デコーダ状態をリセットするために使用することができ、したがって、コーディングされたビデオビットストリームおよびビデオセッション内の最初のピクチャとして、または静止画像として使用することができる。次いで、イントラ予測後のブロックのサンプルに周波数領域への変換を施すことができ、そのように生成された変換係数をエントロピーコーディングの前に量子化することができる。イントラ予測は、変換前領域におけるサンプル値を最小化する技術を表す。場合によっては、変換後のDC値が小さいほど、およびAC係数が小さいほど、エントロピーコーディング後のブロックを表すために所与の量子化ステップサイズで必要とされるビット数が少なくなる。

20

#### 【 0 0 0 8 】

例えば、MPEG - 2生成コーディング技術から知られているような従来のイントラコーディングは、イントラ予測を使用しない。しかしながら、いくつかのより新しいビデオ圧縮技術は、例えば、空間的隣接のエンコーディングおよび／またはデコーディング時に取得される、イントラコーディングまたはイントラデコーディングされているデータのブロックにデコーディング順序で先行する、周囲のサンプルデータおよび／またはメタデータに基づいて、ブロックのコーディング／デコーディングを試みる技術を含む。そのような技術を、これ以降、「イントラ予測」技術と呼ぶ。少なくともいくつかの場合において、イントラ予測は、再構成中の現在のピクチャのみからの参照データを使用し、他の参照ピクチャからの参照データは使用しないことに留意されたい。

30

#### 【 0 0 0 9 】

イントラ予測には、多くの異なる形態があり得る。そのような技術のうちの2つ以上が所与のビデオコーディング技術において利用可能である場合、使用される技術を、イントラ予測モードと呼ぶことができる。1つまたは複数のイントラ予測モードが特定のコーデックで提供され得る。特定の場合には、モードは、サブモードを有することができ、かつ／または様々なパラメータと関連付けられていてもよく、モード／サブモード情報およびビデオのブロックのイントラコーディングパラメータは、個別にコーディングするか、またはまとめてモードのコードワードに含めることができる。所与のモード、サブモード、および／またはパラメータの組み合わせにどのコードワードを使用するかは、イントラ予測を介したコーディング効率向上に影響を与える可能性があり、そのため、コードワードをビットストリームに変換するために使用されるエントロピーコーディング技術も影響を与える可能性がある。

40

#### 【 0 0 1 0 】

イントラ予測の特定のモードは、H.264で導入され、H.265で改良され、共同探索モ

50

デル (JEM)、多用途ビデオコーディング (VVC)、およびベンチマークセット (BMS) などのより新しいコーディング技術でさらに改良された。一般に、イントラ予測では、利用可能になった隣接サンプル値を使用して予測子ブロックを形成することができる。例えば、特定の方向および / または線に沿った特定の隣接サンプルセットの利用可能な値が、予測子ブロックにコピーされ得る。使用される方向への参照は、ビットストリーム内でコーディングすることができるか、またはそれ自体が予測され得る。

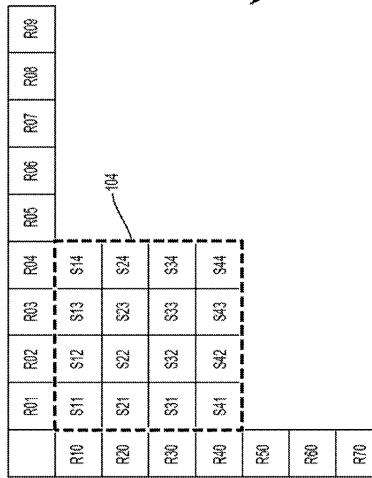

#### 【0011】

図1Aを参照すると、右下に示されているのは、(H.265で指定される35のイントラモードのうちの33の角度モードに対応する) H.265の33の可能な予測子方向で指定される9つの予測子方向のサブセットである。矢印が集中する点 (101) は、予測されているサンプルを表す。矢印は、隣接サンプルがそこから101のサンプルを予測するために使用される方向を表す。例えば、矢印 (102) は、サンプル (101) が、1つまたは複数の隣接サンプルから右上へ、水平方向から45度の角度で予測されることを示している。同様に、矢印 (103) は、サンプル (101) が、1つまたは複数の隣接サンプルからサンプル (101) の左下へ、水平方向から22.5度の角度で予測されることを示している。

10

#### 【0012】

さらに図1Aを参照すると、左上に、(破線太線で示された)  $4 \times 4$  サンプルの正方形ブロック (104) が示されている。正方形ブロック (104) は16サンプルを含み、各々が「S」、そのY次元の位置 (例えば、行番号)、およびそのX次元の位置 (例えば、列番号) でラベル付けされている。例えば、サンプルS21は、Y次元で (上から) 2番目のサンプルであり、X次元で (左から) 1番目のサンプルである。同様に、サンプルS44は、Y次元とX次元の両方でブロック (104) 内の4番目のサンプルである。ブロックのサイズは  $4 \times 4$  サンプルであるため、S44は右下にある。同様の番号付け方式に従う参照サンプルの例がさらに示されている。参照サンプルは、R、ブロック (104) に対するそのY位置 (例えば、行番号) およびX位置 (列番号) でラベル付けされている。H.264とH.265の両方で、再構成中のブロックに隣接する予測サンプルが使用される。

20

#### 【0013】

ブロック104のイントラピクチャ予測は、シグナリングされた予測方向に従って隣接サンプルから参照サンプル値をコピーすることから開始し得る。例えば、コーディングされたビデオビットストリームは、このブロック104について、矢印 (102) の予測方向を示すシグナリングを含む、すなわち、サンプルは1つまたは複数の予測サンプルから右上へ、水平方向から45度の角度で予測されると仮定する。そのような場合、サンプルS41、S32、S23、S14が、同じ参照サンプルR05から予測される。次いで、サンプルS44が、参照サンプルR08から予測される。

30

#### 【0014】

特定の場合には、特に、方向が45度で均等に割り切れない場合に、参照サンプルを計算するために、例えば補間によって複数の参照サンプル値が組み合わされてもよい。

#### 【0015】

可能な方向の数は、ビデオコーディング技術が発展し続けるにつれて増加してきた。H.264 (2003年) では、例えば、9つの異なる方向がイントラ予測に利用可能である。これは、H.265 (2013年) では33まで増加し、JEM / VVC / BMSは、本開示の時点で、最大65の方向をサポートすることができる。最も適切なイントラ予測方向を特定するのに役立つ実験研究が行われており、エントロピーコーディングの特定の手法を使用して、方向についての特定のビットペナルティを受け入れて、それらの最も適切な方向が少数のビットでエンコーディングされ得る。さらに、方向自体を、デコーディングされた隣接するブロックのイントラ予測で使用された隣接する方向から予測できる場合もある。

40

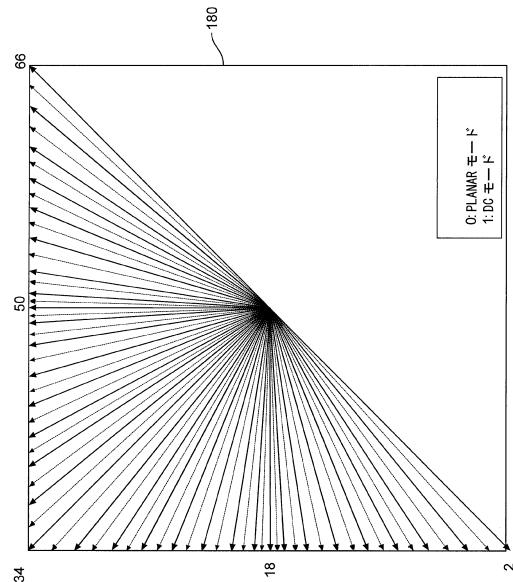

#### 【0016】

図1Bに、時間の経過と共に発展した様々なエンコーディング技術における増加する予測方向の数を例示するために、JEMによる65のイントラ予測方向を示す概略図 (180) を示す。

50

## 【0017】

コーディングされたビデオビットストリームにおけるイントラ予測方向を表すビットの予測方向へのマッピングは、ビデオコーディング技術によって異なる可能性があり、例えば、予測方向対イントラ予測モードの単純な直接マッピングから、コードワード、最も可能性の高いモードを含む複雑な適応方式、および同様の技術にまで及び得る。ただし、すべての場合において、他の特定の方向よりもビデオコンテンツで発生する可能性が統計的に低いイントロ予測の特定の方向が存在し得る。ビデオ圧縮の目的は冗長性の低減であるため、うまく設計されたビデオコーディング技術においては、それらのより可能性の低い方向はより可能性の高い方向よりも多くのビット数で表される。

## 【0018】

インターピクチャ予測、またはインター予測は、動き補償に基づくものあり得る。動き補償では、以前に再構成されたピクチャまたはその一部（参照ピクチャ）からのサンプルデータが、動きベクトル（これ以降はMV）によって示される方向に空間的にシフトされた後、新たに再構成されたピクチャまたはピクチャ部分（例えば、ブロック）の予測に使用され得る。場合によっては、参照ピクチャは、現在再構成中のピクチャと同じであり得る。MVは、2つの次元XおよびY、または3つの次元を有していてもよく、第3の次元は、（時間次元と類似した）使用される参照ピクチャの指示である。

## 【0019】

いくつかのビデオ圧縮技術では、サンプルデータの特定のエリアに適用可能な現在のMVを、他のMVから、例えば再構成中のエリアに空間的に隣接し、コーディング順序で現在のMVに先行する、サンプルデータの他のエリアに関連する他のMVから予測することができる。そうすることにより、相関するMVの冗長性の除去に依拠することによってMVをコーディングするのに必要とされる全体のデータ量を大幅に削減することができ、それによって圧縮効率が高まる。MV予測が効果的に機能することができるのは、例えば、（自然なビデオとして知られている）カメラから導出された入力ビデオ信号をコーディングするときに、単一のMVが適用可能なエリアよりも大きいエリアは、ビデオシーケンスにおいて同様の方向に移動する統計的尤度があり、したがって、場合によっては、隣接するエリアのMVから導出された同様の動きベクトルを使用して予測することができるからである。その結果として、所与のエリアの実際のMVが周囲のMVから予測されたMVと同様または同一になる。そのようなMVはさらに、エントロピーコーディング後に、MVが（1つまたは複数の）隣接するMVから予測されるのではなく直接コーディングされた場合に使用されることになるビット数よりも少ないビット数で表され得る。場合によっては、MV予測を、原信号（すなわち、サンプルストリーム）から導出された信号（すなわち、MV）の可逆圧縮の一例とすることができます。場合によっては、例えば、いくつかの周囲のMVから予測子を計算するときの丸め誤差のために、MV予測自体が非可逆であり得る。

## 【0020】

H.265 / HEVC (ITU-T Rec. H.265, "High Efficiency Video Coding", December 2016)には、様々なMV予測機構が記載されている。H.265が指定する多くのMV予測機構のうち、以下で説明するのは、これ以降「空間マージ」と呼ぶ技術である。

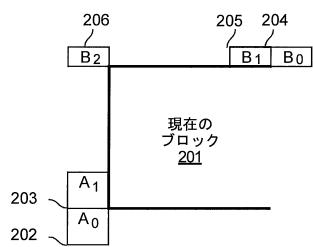

## 【0021】

具体的には、図2を参照すると、現在のブロック（201）は、動き探索プロセス中にエンコーダによって、空間的にシフトされた同じサイズの前のブロックから予測可能であると検出されたサンプルを含む。そのMVを直接コーディングする代わりに、MVを、A0、A1、およびB0、B1、B2（それぞれ202から206）で表された5つの周囲のサンプルのいずれか1つと関連付けられたMVを使用して、1つまたは複数の参照ピクチャと関連付けられたメタデータから、例えば、（コーディング順序で）最後の参照ピクチャから導出することができる。H.265では、MV予測は、隣接するブロックが使用しているのと同じ参照ピクチャからの予測子を使用することができる。

## 【発明の概要】

## 【課題を解決するための手段】

10

20

30

40

50

**【 0 0 2 2 】**

本開示は、ビデオエンコーディングおよび／またはビデオデコーディングのための方法、装置、およびコンピュータ可読記憶媒体の様々な実施形態を説明する。

**【 0 0 2 3 】**

一態様によれば、本開示の一実施形態は、ビデオデコーディングにおける複数基準線イントラ予測のための方法を提供する。方法は、装置が、ブロックのためのコーディングされたビデオビットストリームを受信するステップを含む。装置は、命令を格納するメモリと、メモリと通信するプロセッサとを含む。方法は、装置が、複数のサブブロックを取得するためにブロックを分割するステップと、装置が、基準線に基づいて、複数のサブブロック内のサブブロックに対して複数基準線イントラ予測を実行するステップと、装置が、複数の変換ブロックを取得するためにサブブロックを分割するステップとをさらに含む。

10

**【 0 0 2 4 】**

別の態様によれば、本開示の一実施形態は、ビデオエンコーディングおよび／またはビデオデコーディングのための装置を提供する。装置は、命令を格納するメモリと、メモリと通信するプロセッサとを含む。プロセッサが命令を実行すると、プロセッサは、装置に、ビデオデコーディングおよび／またはビデオエンコーディングのための上記の方法を実行させるように構成される。

**【 0 0 2 5 】**

別の態様では、本開示の一実施形態は、ビデオデコーディングおよび／またはビデオエンコーディングのためにコンピュータによって実行されると、ビデオデコーディングおよび／またはビデオエンコーディングのための上記の方法をコンピュータに実行させる命令を格納する非一時的コンピュータ可読媒体を提供する。

20

**【 0 0 2 6 】**

上記その他の態様およびそれらの実装形態を、図面、明細書、および特許請求の範囲においてさらに詳細に説明する。

**【 0 0 2 7 】**

開示の主題のさらなる特徴、性質、および様々な利点は、以下の詳細な説明および添付の図面からより明らかになるであろう。

**【図面の簡単な説明】****【 0 0 2 8 】**

30

【図 1 A】イントラ予測方向性モードの例示的なサブセットの概略図である。

【図 1 B】例示的なイントラ予測方向を示す図である。

【図 2】一例における現在のブロックおよび動きベクトル予測のためのその周囲の空間マージ候補を示す概略図である。

【図 3】一例示的実施形態による通信システム(300)の簡略化されたブロック図を示す概略図である。

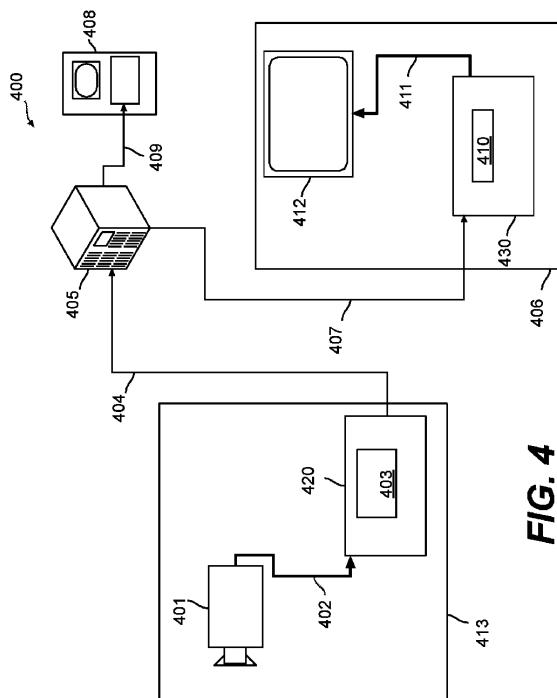

【図 4】一例示的実施形態による通信システム(400)の簡略化されたブロック図を示す概略図である。

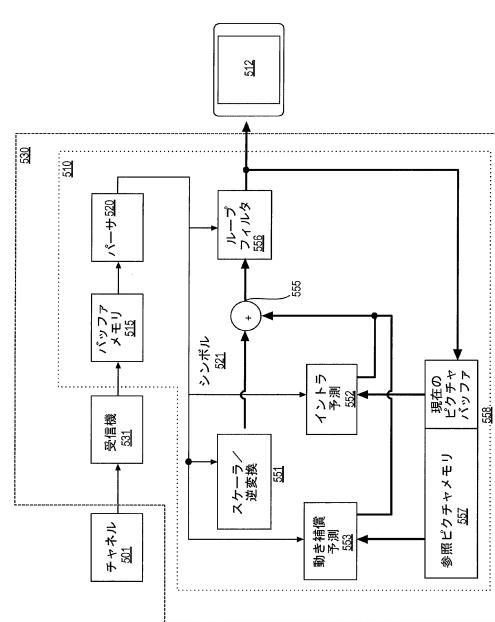

【図 5】一例示的実施形態によるビデオデコーダの簡略化されたブロック図を示す概略図である。

40

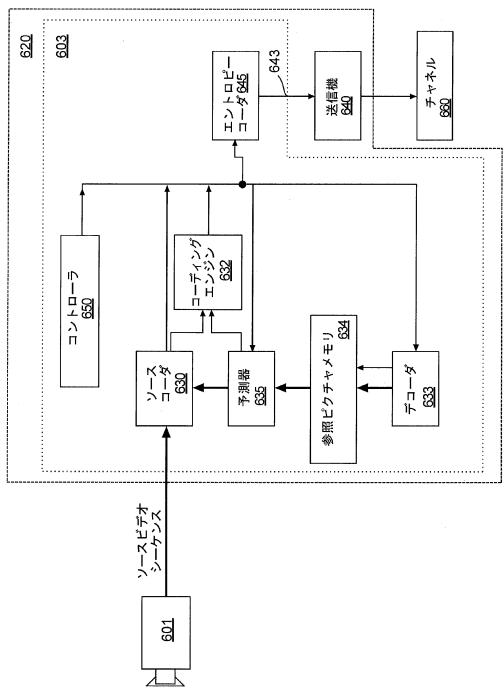

【図 6】一例示的実施形態によるビデオエンコーダの簡略化されたブロック図を示す概略図である。

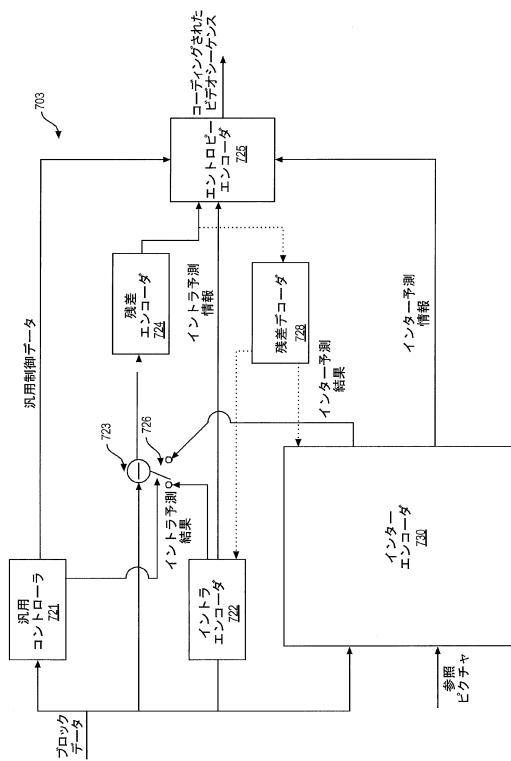

【図 7】別の例示的実施形態によるビデオエンコーダを示すブロック図である。

【図 8】別の例示的実施形態によるビデオデコーダを示すブロック図である。

【図 9】本開示の例示的実施形態によるコーディングブロック分割の方式を示す図である。

【図 1 0】本開示の例示的実施形態によるコーディングブロック分割の別的方式を示す図である。

【図 1 1】本開示の例示的実施形態によるコーディングブロック分割の別的方式を示す図である。

【図 1 2】本開示の例示的実施形態によるコーディングブロック分割の別的方式を示す図

50

である。

【図13】本開示の例示的実施形態による、コーディングブロックを複数の変換ブロックに分割する方式および変換ブロックのコーディング順序を示す図である。

【図14】本開示の例示的実施形態による、コーディングブロックを複数の変換ブロックに分割する別的方式および変換ブロックのコーディング順序を示す図である。

【図15】本開示の例示的実施形態による、コーディングブロックを複数の変換ブロックに分割する別的方式を示す図である。

【図16】本開示の例示的実施形態による、様々な基準線に基づくイントラ予測方式を示す図である。

【図17】本開示の一例示的実施形態による方法を示すフローチャートである。

10

【図18】本開示の一例示的実施形態によるコンピュータシステムを示す概略図である。

【発明を実施するための形態】

【0029】

次に、本発明の一部を形成し、実施形態の具体例を例示として示す添付の図面を参照して本発明を以下で詳細に説明する。しかしながら、本発明は、様々な異なる形態で具体化されてもよく、したがって、対象として含まれるまたは特許請求される主題は、以下に記載される実施形態のいずれにも限定されないと解釈されることが意図されていることに留意されたい。また本発明は、方法、装置、構成要素、またはシステムとして具体化され得ることにも留意されたい。したがって、本発明の実施形態は、例えば、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組み合わせの形態をとり得る。

20

【0030】

本明細書および特許請求の範囲を通して、用語は、明示的に記載される意味を超えて文脈において示唆または暗示される微妙な意味を有し得る。本明細書で使用される「一実施形態では」または「いくつかの実施形態では」という語句は、必ずしも同じ実施形態を指すものではなく、本明細書で使用される「別の実施形態では」または「他の実施形態では」という語句は、必ずしも異なる実施形態を指すものではない。同様に、本明細書で使用される「一実装形態では」または「いくつかの実装形態では」という語句は、必ずしも同じ実装形態を指すものではなく、本明細書で使用される「別の実装形態では」または「他の実装形態では」という語句は、必ずしも異なる実装形態を指すものではない。例えば、特許請求される主題は、例示的な実施形態／実装形態の全部または一部の組み合わせを含むことが意図されている。

30

【0031】

一般に、用語は、文脈における用法から少なくとも部分的に理解され得る。例えば、本明細書で使用される「および」、「または」、または「および／または」などの用語は、そのような用語が使用される文脈に少なくとも部分的に依存し得る様々な意味を含み得る。典型的には、A、BまたはCなどのリストを関連付けるために使用される場合の「または」は、ここでは包括的な意味で使用されるA、BおよびC、ならびにここでは排他的な意味で使用されるA、BまたはCを意味することを意図されている。さらに、本明細書で使用される「1つまたは複数」または「少なくとも1つ」という用語は、文脈に少なくとも部分的に依存して、単数の意味で任意の特徴、構造、もしくは特性を記述するために使用され得るか、または複数の意味で特徴、構造、もしくは特性の組み合わせを記述するために使用され得る。同様に、「a」、「an」、または「the」などの用語もやはり、文脈に少なくとも部分的に依存して、単数形の用法を伝えるか、または複数形の用法を伝えると理解され得る。さらに、「に基づいて」または「によって決定される」という用語は、必ずしも排他的な要因のセットを伝えることを意図されていないと理解され、代わりに、やはり文脈に少なくとも部分的に依存して、必ずしも明示的に説明されていない追加の要因の存在を許容する場合もある。

40

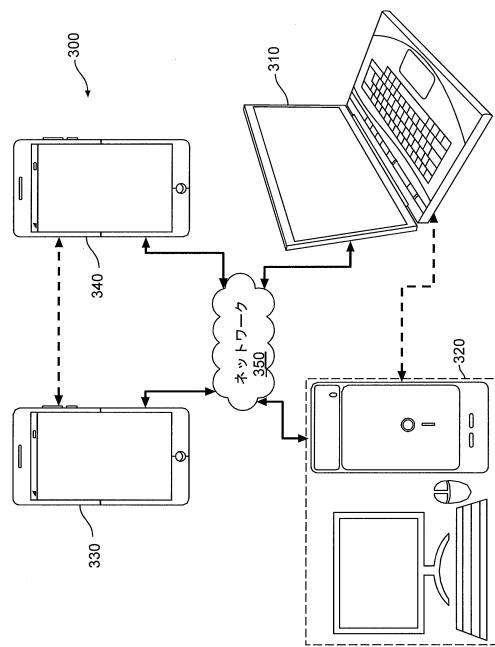

【0032】

図3に、本開示の一実施形態による通信システム(300)の簡略化されたブロック図を示す。通信システム(300)は、例えばネットワーク(350)を介して互いに通信するこ

50

とができる複数の端末装置を含む。例えば、通信システム(300)は、ネットワーク(350)を介して相互接続された第1の対の端末装置(310)および(320)を含む。図3の例では、第1の対の端末装置(310)および(320)は、データの一方向伝送を実行し得る。例えば、端末装置(310)は、ネットワーク(350)を介して他方の端末装置(320)に送信するための(例えば、端末装置(310)によって取り込まれたビデオピクチャのストリームの)ビデオデータをコーディングし得る。エンコーディングされたビデオデータは、1つまたは複数のコーディングされたビデオビットストリームの形で送信することができる。端末装置(320)は、ネットワーク(350)からコーディングされたビデオデータを受信し、コーディングされたビデオデータをデコーディングしてビデオピクチャを復元し、復元されたビデオデータに従ってビデオピクチャを表示し得る。一方向データ伝送は、メディアサービング用途などで実施され得る。

10

#### 【0033】

別の例では、通信システム(300)は、例えばビデオ会議用途の間に実施され得るコーディングされたビデオデータの双方向伝送を実行する第2の対の端末装置(330)および(340)を含む。データの双方向伝送のために、一例では、端末装置(330)および(340)の各端末装置は、ネットワーク(350)を介して端末装置(330)および(340)の他方の端末装置に送信するための(例えば、その端末装置によって取り込まれたビデオピクチャのストリームの)ビデオデータをコーディングし得る。端末装置(330)および(340)の各端末装置はまた、端末装置(330)および(340)の他方の端末装置によって送信されたコーディングされたビデオデータを受信し、コーディングされたビデオデータをデコーディングしてビデオピクチャを復元し、復元されたビデオデータに従ってビデオピクチャを表示し得る。

20

#### 【0034】

図3の例では、端末装置(310)、(320)、(330)、および(340)は、サーバ、パーソナルコンピュータ、およびスマートフォンとして実施され得るが、本開示の基礎となる原理の適用性はそのように限定されない。本開示の実施形態は、デスクトップコンピュータ、ラップトップコンピュータ、タブレットコンピュータ、メディアプレーヤ、ウェアラブルコンピュータ、専用のビデオ会議機器などにおいて実装され得る。ネットワーク(350)は、例えば、有線(有線接続)および/または無線通信ネットワークを含む、端末装置(310)、(320)、(330)および(340)間でコーディングされたビデオデータを伝達する任意の数またはタイプのネットワークを表す。通信ネットワーク(350)は、回線交換チャネル、パケット交換チャネル、および/または他のタイプのチャネルでデータを交換し得る。代表的なネットワークには、電気通信ネットワーク、ローカルエリアネットワーク、ワイドエリアネットワーク、および/またはインターネットが含まれる。本考査の目的にとって、ネットワーク(350)のアーキテクチャおよびトポロジーは、本明細書で明示的に説明されない限り、本開示の動作にとって重要ではない場合がある。

30

#### 【0035】

図4に、開示の主題の用途の一例として、ビデオストリーミング環境におけるビデオエンコーダおよびビデオデコーダの配置を示す。開示の主題は、例えば、ビデオ会議、デジタルテレビ放送、ゲーム、仮想現実、CD、DVD、メモリスティックなどを含むデジタルメディア上の圧縮ビデオの格納などを含む、他のビデオ対応用途に等しく適用され得る。

40

#### 【0036】

ビデオストリーミングシステムは、圧縮されていないビデオピクチャまたは画像のストリーム(402)を作成するためのビデオソース(401)、例えばデジタルカメラを含むことができるビデオ取り込みサブシステム(413)を含み得る。一例では、ビデオピクチャのストリーム(402)は、ビデオソース401のデジタルカメラによって記録されたサンプルを含む。ビデオピクチャのストリーム(402)は、エンコーディングされたビデオデータ(404)(またはコーディングされたビデオビットストリーム)と比較した場合の高データ量を強調するために太線で示されており、ビデオソース(401)に結合されたビデオエンコーダ(403)を含む電子装置(420)によって処理することができる。ビデオエン

50

コーダ (403) は、以下により詳細に説明されるように開示の主題の態様を可能にし、または実装するために、ハードウェア、ソフトウェア、またはそれらの組み合わせを含むことができる。エンコーディングされたビデオデータ (404) (またはエンコーディングされたビデオビットストリーム (404)) は、非圧縮ビデオピクチャのストリーム (402) と比較した場合の低データ量を強調するために細線で示されており、将来の使用のためにストリーミングサーバ (405) に、または下流のビデオ装置 (図示せず) に直接格納することができる。図4のクライアントサブシステム (406) および (408) などの1つまたは複数のストリーミングクライアントサブシステムは、ストリーミングサーバ (405) にアクセスして、エンコーディングされたビデオデータ (404) のコピー (407) および (409) を取得することができる。クライアントサブシステム (406) は、例えば電子装置 (430) 内のビデオデコーダ (410) を含むことができる。ビデオデコーダ (410) は、エンコーディングされたビデオデータの入力コピー (407) をデコーディングし、圧縮されていない、ディスプレイ (412) (例えば、表示画面) または他のレンダリング装置 (図示せず) 上にレンダリングすることができるビデオピクチャの出力ストリーム (411) を作成する。ビデオデコーダ 410 は、本開示に記載される様々な機能の一部または全部を実行するように構成され得る。一部のストリーミングシステムでは、エンコーディングされたビデオデータ (404)、(407)、および (409) (例えば、ビデオビットストリーム) を、特定のビデオコーディング / 圧縮規格に従ってエンコーディングすることができる。それらの規格の例として、ITU - T勧告 H.265 が挙げられる。一例では、開発中のビデオコーディング規格は、多用途ビデオコーディング (VVC) として非公式に知られている。開示の主題は、VVC、および他のビデオコーディング規格の文脈で使用され得る。

#### 【0037】

電子装置 (420) および (430) は、他の構成要素 (図示せず) を含むことができることに留意されたい。例えば、電子装置 (420) はビデオデコーダ (図示せず) を含むことができ、電子装置 (430) はビデオエンコーダ (図示せず) も含むことができる。

#### 【0038】

図5に、以下の本開示の任意の実施形態によるビデオデコーダ (510) のブロック図を示す。ビデオデコーダ (510) は、電子装置 (530) に含めることができる。電子装置 (530) は、受信機 (531) (例えば、受信回路) を含むことができる。ビデオデコーダ (510) は、図4の例のビデオデコーダ (410) の代わりに使用することができる。

#### 【0039】

受信機 (531) は、ビデオデコーダ (510) によってデコーディングされるべき1つまたは複数のコーディングされたビデオシーケンスを受信し得る。同じまたは別の実施形態では、一度に1つのコーディングされたビデオシーケンスがデコーディングされ得、各コーディングされたビデオシーケンスのデコーディングは、他のコーディングされたビデオシーケンスから独立している。各ビデオシーケンスは、複数のビデオフレームまたはビデオ画像と関連付けられ得る。コーディングされたビデオシーケンスはチャネル (501) から受信され、チャネル (501) は、エンコーディングされたビデオデータを格納する記憶装置へのハードウェア / ソフトウェアリンク、またはエンコーディングされたビデオデータを送信するストリーミングソースであり得る。受信機 (531) は、エンコーディングされたビデオデータを、それぞれの処理回路 (図示せず) に転送され得る、コーディングされたオーディオデータおよび / または補助データストリームなどの他のデータと共に受信し得る。受信機 (531) は、コーディングされたビデオシーケンスを他のデータから分離し得る。ネットワークジッタに対抗するために、バッファメモリ (515) が、受信機 (531) とエントロピーデコーダ / パーサ (520) (これ以降は「パーサ (520)」)との間に配置されてもよい。特定の用途では、バッファメモリ (515) は、ビデオデコーダ (510) の一部として実装され得る。他の用途では、バッファメモリ (515) は、ビデオデコーダ (510) から分離されて外部にあり得る (図示せず)。さらに他の用途では、例えばネットワークジッタに対抗するためにビデオデコーダ (510) の外部にバッファメモリ (515) が配置され得る。

図示せず) があってもよく、例えば再生タイミングを処理するためにビデオデコーダ(510)の内部に別のバッファメモリ(515)があり得る。受信機(531)が十分な帯域幅および可制御性の記憶/転送装置から、またはアイソシンクロナス(isosynchronous)ネットワークからデータを受信しているときには、バッファメモリ(515)は不要であり得るか、または小さくすることができる。インターネットなどのベストエフォートパケットネットワークで使用するために、十分なサイズのバッファメモリ(515)が必要とされる場合があり、そのサイズは比較

的大きくなり得る。そのようなバッファメモリは、適応サイズで実装されてもよく、ビデオデコーダ(510)の外部のオペレーティングシステムまたは同様の要素(図示せず)に少なくとも部分的に実装され得る。

10

#### 【0040】

ビデオデコーダ(510)は、コーディングされたビデオシーケンスからシンボル(521)を再構成するためのパーサ(520)を含み得る。それらのシンボルのカテゴリは、ビデオデコーダ(510)の動作を管理するために使用される情報と、潜在的に、図5に示すように、電子装置(530)の不可欠な部分である場合もそうでない場合もあるが、電子装置(530)に結合することができるディスプレイ(512)(例えば、表示画面)などのレンダリング装置を制御するための情報とを含む。(1つまたは複数の)レンダリング装置のための制御情報は、補足拡張情報(SEIメッセージ)またはビデオユーザビリティ情報(VUI)パラメータセットフラグメント(図示せず)の形であり得る。パーサ(520)は、パーサ(520)によって受け取られるコーディングされたビデオシーケンスをパース/エントロピードコーディングし得る。エントロピードコーディングされたビデオシーケンスのコーディングは、ビデオコーディング技術または規格に従ったものとすることができます、可変長コーディング、ハフマンコーディング、文脈依存性ありまたはなしの算術コーディングなどを含む様々な原理に従ったものとすることができます。パーサ(520)は、コーディングされたビデオシーケンスから、サブグループに対応する少なくとも1つのパラメータに基づいて、ビデオデコーダ内の画素のサブグループのうちの少なくとも1つのサブグループパラメータのセットを抽出し得る。サブグループには、Groups of Pictures(GOP)、ピクチャ、タイル、スライス、マクロブロック、コーディングユニット(CU)、ブロック、変換ユニット(TU)、予測ユニット(PU)などを含めることができます。パーサ(520)はまた、コーディングされたビデオシーケンスから、変換係数(例えば、フーリエ変換係数)、量子化パラメータ値、動きベクトルなどの情報も抽出し得る。

20

#### 【0041】

パーサ(520)は、シンボル(521)を作成するために、バッファメモリ(515)から受け取られたビデオシーケンスに対してエントロピードコーディング/パース操作を実行し得る。

30

#### 【0042】

シンボル(521)の再構成は、コーディングされたビデオピクチャまたはその部分のタイプ(インターピクチャおよびイントラピクチャ、インターブロックおよびイントラブロックなど)、ならびに他の要因に応じて、複数の異なる処理ユニットまたは機能ユニットを含むことができる。含まれるユニットおよびユニットがどのように含まれるかは、パーサ(520)によってコーディングされたビデオシーケンスからパースされたサブグループ制御情報によって制御され得る。パーサ(520)と以下の複数の処理ユニットまたは機能ユニットとの間のそのようなサブグループ制御情報の流れは、簡潔にするために図示されていない。

40

#### 【0043】

すでに述べた機能ブロックを超えて、ビデオデコーダ(510)を、以下で説明するように、いくつかの機能ユニットに概念的に細分することができる。商業的制約の下で動作する実際の実装形態では、これらの機能ユニットの多くは互いに密接に相互作用し、少なくとも部分的に、互いに統合することができる。しかしながら、開示の主題の様々な機能を明確に説明するために、以下の開示においては機能ユニットへの概念的細分を採用する。

50

## 【 0 0 4 4 】

第1のユニットはスケーラ / 逆変換ユニット (551) である。スケーラ / 逆変換ユニット (551) は、量子化変換係数、ならびにどのタイプの逆変換を使用するかを示す情報、ブロックサイズ、量子化係数 / パラメータ、量子化スケーリング行列などを含む制御情報を、パーサ (520) から (1つまたは複数の) シンボル (521) として受け取り得る。スケーラ / 逆変換ユニット (551) は、アグリゲータ (555) に入力することができるサンプル値を備えるブロックを出力することができる。

## 【 0 0 4 5 】

場合によっては、スケーラ / 逆変換 (551) の出力サンプルは、イントラコーディングされたブロック、すなわち、以前に再構成されたピクチャからの予測情報を使用しないが、現在のピクチャの以前に再構成された部分からの予測情報を使用することができるブロックに関係し得る。そのような予測情報は、イントラピクチャ予測ユニット (552) によって提供することができる。場合によっては、イントラピクチャ予測ユニット (552) は、すでに再構成され、現在のピクチャバッファ (558) に格納されている周囲のブロックの情報を使用して、再構成中のブロックと同じサイズおよび形状のブロックを生成してもよい。現在のピクチャバッファ (558) は、例えば、部分的に再構成された現在のピクチャおよび / または完全に再構成された現在のピクチャをバッファする。アグリゲータ (555) は、いくつかの実装形態では、サンプルごとに、イントラ予測ユニット (552) が生成した予測情報を、スケーラ / 逆変換ユニット (551) によって提供される出力サンプル情報に追加し得る。

10

## 【 0 0 4 6 】

他の場合には、スケーラ / 逆変換ユニット (551) の出力サンプルは、インターフェービングされ、潜在的に動き補償されたブロックに関係し得る。そのような場合、動き補償予測ユニット (553) は、参照ピクチャメモリ (557) にアクセスして、インターピクチャ予測に使用されるサンプルをフェッチすることができる。ブロックに関連するシンボル (521) に従ってフェッチされたサンプルを動き補償した後、これらのサンプルを、出力サンプル情報を生成するために、アグリゲータ (555) によってスケーラ / 逆変換ユニット (551) の出力に追加することができる (ユニット 551 の出力は、残差サンプルまたは残差信号と呼ばれ得る)。動き補償予測ユニット (553) がそこから予測サンプルをフェッチする参照ピクチャメモリ (557) 内のアドレスは、例えば、X 成分、Y 成分 (シフト) 、および参照ピクチャ成分 (時間) を有し得るシンボル (521) の形で動き補償予測ユニット (553) が利用可能な、動きベクトルによって制御することができる。動き補償はまた、サブサンプルの正確な動きベクトルが使用されているときに参照ピクチャメモリ (557) からフェッチされたサンプル値の補間も含んでいてもよく、動きベクトル予測機構などと関連付けられてもよい。

20

## 【 0 0 4 7 】

アグリゲータ (555) の出力サンプルは、ループフィルタユニット (556) において様々なループフィルタリング技術を受けることができる。ビデオ圧縮技術は、コーディングされたビデオシーケンス (コーディングされたビデオビットストリームとも言う) に含まれるパラメータによって制御され、パーサ (520) からのシンボル (521) としてループフィルタユニット (556) が利用可能なインループフィルタ技術を含むことができるが、コーディングされたピクチャまたはコーディングされたビデオシーケンスの (デコーディング順序で) 前の部分のデコーディング中に取得されたメタ情報を応答することもでき、以前に再構成され、ループフィルタリングされたサンプル値に応答することもできる。以下でさらに詳細に説明するように、いくつかのタイプのループフィルタが、様々な順序でループフィルタユニット 556 の一部として含まれ得る。

30

## 【 0 0 4 8 】

ループフィルタユニット (556) の出力は、レンダリング装置 (512) に出力することができると共に、将来のインターピクチャ予測で使用するために参照ピクチャメモリ (557) に格納することもできるサンプルストリームであり得る。

40

50

## 【0049】

特定のコーディングされたピクチャは、完全に再構成されると、将来のインターピクチャ予測のための参照ピクチャとして使用することができる。例えば、現在のピクチャに対応するコーディングされたピクチャが完全に再構成され、コーディングされたピクチャが（例えば、パーサ（520）によって）参照ピクチャとして識別されると、現在のピクチャバッファ（558）は、参照ピクチャメモリ（557）の一部になることができ、次のコーディングされたピクチャの再構成を開始する前に、新しい現在のピクチャバッファを再割り振りすることができる。

## 【0050】

ビデオデコーダ（510）は、例えばITU-T Rec. H.265などの規格で採用された所定のビデオ圧縮技術に従ってデコーディング動作を実行し得る。コーディングされたビデオシーケンスは、コーディングされたビデオシーケンスがビデオ圧縮技術または規格の構文と、ビデオ圧縮技術または規格に文書化されたプロファイルの両方に忠実であるという意味において、使用されているビデオ圧縮技術または規格によって指定された構文に準拠し得る。具体的には、プロファイルは、そのプロファイルの下でのみ使用に供されるツールとして、ビデオ圧縮技術または規格で利用可能なすべてのツールの中から特定のツールを選択することができる。規格に準拠するために、コーディングされたビデオシーケンスの複雑さが、ビデオ圧縮技術または規格のレベルによって定義される範囲内にあり得る。場合によっては、レベルは、最大ピクチャサイズ、最大フレームレート、最大再構成サンプルレート（例えば、毎秒のメガサンプル数で測定される）、最大参照ピクチャサイズなどを制限する。レベルによって設定される制限は、場合によっては、仮想参照デコーダ（HRD）仕様およびコーディングされたビデオシーケンスでシグナリングされたHRDバッファ管理のためのメタデータによってさらに制限され得る。

10

## 【0051】

いくつかの例示的実施形態では、受信機（531）は、エンコーディングされたビデオと共に追加の（冗長な）データを受信し得る。追加のデータは、（1つまたは複数の）コーディングされたビデオシーケンスの一部として含まれ得る。追加のデータは、ビデオデコーダ（510）によって、そのデータを適切にデコーディングするため、および／または元のビデオデータをより正確に再構成するために使用され得る。追加のデータは、例えば、時間、空間、または信号対雑音比（SNR）増強層、冗長スライス、冗長ピクチャ、前方誤り訂正コードなどの形であり得る。

20

## 【0052】

図6に、本開示の一例示的実施形態によるビデオエンコーダ（603）のブロック図を示す。ビデオエンコーダ（603）は、電子装置（620）に含まれ得る。電子装置（620）は、送信機（640）（例えば、送信回路）をさらに含み得る。ビデオエンコーダ（603）は、図4の例のビデオエンコーダ（403）の代わりに使用することができる。

30

## 【0053】

ビデオエンコーダ（603）は、ビデオエンコーダ（603）によってコーディングされるべき（1つまたは複数の）ビデオ画像を取り込み得るビデオソース（601）（図6の例では電子装置（620）の一部ではない）からビデオサンプルを受信し得る。別の例では、ビデオソース（601）は電子装置（620）の一部分として実装され得る。

40

## 【0054】

ビデオソース（601）は、ビデオエンコーダ（603）によってコーディングされるべきソースビデオシーケンスを、任意の適切なビット深度（例えば、8ビット、10ビット、12ビット、. . .）、任意の色空間（例えば、BT.601 Y CrCb、RGB、XYZ. . .）、および任意の適切なサンプリング構造（例えば、Y CrCb 4:2:0、Y CrCb 4:4:4）のものとすることができますデジタルビデオサンプルストリームの形で提供し得る。メディアサービングシステムでは、ビデオソース（601）は、以前に準備されたビデオを格納することができる記憶装置であり得る。ビデオ会議システムでは、ビデオソース（601）は、ローカル画像情報をビデオシーケンスとして取り込むカメラであり得る。ビデオデータは

50

、順を追って見たときに動きを与える複数の個別のピクチャまたは画像として提供され得る。ピクチャ自体は、画素の空間配列として編成されてもよく、各画素は、使用されているサンプリング構造、色空間などに応じて、1つまたは複数のサンプルを含むことができる。当業者であれば、画素とサンプルとの関係を容易に理解することができる。以下の説明はサンプルに焦点を当てている。

#### 【 0 0 5 5 】

いくつかの例示的実施形態によれば、ビデオエンコーダ(603)は、リアルタイムで、または用途によって必要とされる他の任意の時間制約の下で、ソースビデオシーケンスのピクチャをコーディングされたビデオシーケンス(643)にコーディングおよび圧縮し得る。適切なコーディング速度を強制することが、コントローラ(650)の1つの機能を構成する。いくつかの実施形態では、コントローラ(650)は、他の機能ユニットに機能的に結合され、以下で説明されるように他の機能ユニットを制御し得る。簡潔にするために、結合は図示されていない。コントローラ(650)によって設定されるパラメータには、レート制御関連のパラメータ(ピクチャスキップ、量子化器、レート歪み最適化手法のラムダ値など)、ピクチャサイズ、Group of Pictures(GOP)レイアウト、最大動きベクトル探索範囲などが含まれ得る。コントローラ(650)は、特定のシステム設計のために最適化されたビデオエンコーダ(603)に関係する他の適切な機能を有するように構成することができる。

#### 【 0 0 5 6 】

いくつかの例示的実施形態では、ビデオエンコーダ(603)は、コーディングループで動作するように構成され得る。過度に簡略化された説明として、一例では、コーディングループは、ソースコーダ(630)(例えば、コーディングされるべき入力ピクチャと、(1つまたは複数の)参照ピクチャとに基づいて、シンボルストリームなどのシンボルを作成する役割を担う)と、ビデオエンコーダ(603)に組み込まれた(ローカル)デコーダ(633)とを含むことができる。デコーダ(633)は、組み込まれたデコーダ633がエントロピーコーディングなしでソースコーダ630によってコーディングされたビデオストリームを処理するとしても、シンボルを再構成して、(リモート)デコーダが作成することになるのと同様の方法でサンプルデータを作成する(開示の主題で考慮されるビデオ圧縮技術では、シンボルとコーディングされたビデオビットストリームとの間の任意の圧縮が可逆であり得るため)。再構成サンプルストリーム(サンプルデータ)は、参照ピクチャメモリ(634)に入力される。シンボルストリームのデコーディングにより、デコーダの位置(ローカルまたはリモート)に関係なくビットイグザクトな結果が得られるため、参照ピクチャメモリ(634)内の内容もまたローカルエンコーダとリモートエンコーダとの間でビットイグザクトになる。言い換えると、エンコーダの予測部分は、デコーディング中に予測を使用するときにデコーダが「見る」ことになるのとまったく同じサンプル値を参照ピクチャサンプルとして「見る」。参照ピクチャの同期性(および、例えばチャネル誤差が原因で同期性を維持することができない場合には、結果として生じるドリフト)のこの基本原理はコーディング品質を向上させるために使用される。

#### 【 0 0 5 7 】

「ローカル」デコーダ(633)の動作は、図5に関連して上記で詳細に説明した、ビデオデコーダ(510)などの「リモート」デコーダの動作と同じであり得る。図5も簡単に参照すると、しかしながら、シンボルが利用可能であり、エントロピーコーダ(645)およびパーサ(520)によるコーディングされたビデオシーケンスへのシンボルのエンコーディング/デコーディングが可逆であり得るため、バッファメモリ(515)およびパーサ(520)を含むビデオデコーダ(510)のエントロピーデコーディング部分は、エンコーダ内のローカルデコーダ(633)においては完全に実装されない場合がある。

#### 【 0 0 5 8 】

この時点で言えることは、デコーダ内にのみ存在し得るパース/エントロピーデコーディングを除く任意のデコーダ技術もまた必然的に、対応するエンコーダにおいて、実質的に同一の機能形態で存在する必要があり得るということである。このため、開示の主題は

デコーダ動作に焦点を当てる場合があり、この動作はエンコーダのデコーディング部分と同様である。よって、エンコーダ技術の説明は、包括的に説明されるデコーダ技術の逆であるので、省略することができる。特定の領域または態様においてのみ、エンコーダのより詳細な説明を以下に示す。

#### 【 0 0 5 9 】

動作中、いくつかの例示的実装形態では、ソースコーダ(630)は、「参照ピクチャ」として指定されたビデオシーケンスからの1つまたは複数の以前にコーディングされたピクチャを参照して入力ピクチャを予測的にコーディングする、動き補償予測コーディングを実行する場合がある。このようにして、コーディングエンジン(632)は、入力ピクチャの画素ブロックと、入力ピクチャへの(1つまたは複数の)予測参照として選択され得る(1つまたは複数の)参照ピクチャの画素ブロックとの間の色チャネルの差分(または残差)をコーディングする。

#### 【 0 0 6 0 】

ローカルビデオデコーダ(633)は、ソースコーダ(630)によって作成されたシンボルに基づいて、参照ピクチャとして指定され得るピクチャのコーディングされたビデオデータをコーディングし得る。コーディングエンジン(632)の動作は、有利には、非可逆プロセスであり得る。コーディングされたビデオデータがビデオデコーダ(図6には示されていない)でコーディングされ得る場合、再構成されたビデオシーケンスは、通常、多少の誤差を伴うソースビデオシーケンスの複製であり得る。ローカルビデオデコーダ(633)は、参照ピクチャに対してビデオデコーダによって実行され得るコーディングプロセスを複製し、再構成された参照ピクチャを参照ピクチャキャッシュ(634)に格納させ得る。このようにして、ビデオエンコーダ(603)は、遠端(リモート)ビデオデコーダによって取得される再構成された参照ピクチャと共に内容を有する再構成された参照ピクチャのコピーをローカルに格納し得る(伝送誤差なし)。

#### 【 0 0 6 1 】

予測器(635)は、コーディングエンジン(632)のための予測探索を実行し得る。すなわち、コーディングされるべき新しいピクチャについて、予測器(635)は、(候補参照画素ブロックとしての)サンプルデータまたは新しいピクチャの適切な予測参照として役立ち得る参照ピクチャ動きベクトル、ブロック形状などの特定のメタデータを求めて、参照ピクチャメモリ(634)を探索し得る。予測器(635)は、適切な予測参照を見つけるために、サンプルブロックごと画素ブロックごと動作し得る。場合によっては、予測器(635)によって取得された探索結果によって決定されるように、入力ピクチャは、参照ピクチャメモリ(634)に格納された複数の参照ピクチャから引き出された予測参照を有し得る。

#### 【 0 0 6 2 】

コントローラ(650)は、例えば、ビデオデータをエンコーディングするために使用されるパラメータおよびサブグループパラメータの設定を含む、ソースコーダ(630)のコーディング動作を管理し得る。

#### 【 0 0 6 3 】

前述のすべての機能ユニットの出力は、エントロピーコーダ(645)でエントロピーコーディングされ得る。エントロピーコーダ(645)は、ハフマンコーディング、可変長コーディング、算術コーディングなどといった技術に従ったシンボルの可逆圧縮により、様々な機能ユニットによって生成されたシンボルをコーディングされたビデオシーケンスに変換する。

#### 【 0 0 6 4 】

送信機(640)は、エントロピーコーダ(645)によって作成された(1つまたは複数の)コーディングされたビデオシーケンスを、エンコーディングされたビデオデータを格納することになる記憶装置へのハードウェア/ソフトウェアリンクであり得る、通信チャネル(660)を介した送信に備えてバッファし得る。送信機(640)は、ビデオコーダ(603)からのコーディングされたビデオデータを、送信されるべき他のデータ、例えば、

10

20

30

40

50

コーディングされたオーディオデータおよび / または補助データストリーム (ソースは図示せず) とマージし得る。

【 0 0 6 5 】

コントローラ (650) は、ビデオエンコーダ (603) の動作を管理し得る。コーディング中に、コントローラ (650) は、コーディングされた各ピクチャに特定のコーディングされたピクチャタイプを割り当ててもよく、ピクチャタイプは、それぞれのピクチャに適用され得るコーディング技術に影響を及ぼし得る。例えば、ピクチャは多くの場合、以下のピクチャタイプのうちの1つとして割り当てられ得る。

【 0 0 6 6 】

イントラピクチャ (Iピクチャ) は、シーケンス内の任意の他のピクチャを予測ソースとして使用せずに、コーディングおよびデコーディングされ得るピクチャであり得る。一部のビデオコーデックは、例えば、独立したデコーダリフレッシュ (「IDR」) ピクチャを含む異なるタイプのイントラピクチャを可能にする。当業者であれば、Iピクチャのそれらの変形ならびにそれらそれぞれの用途および特徴を認識している。

10

【 0 0 6 7 】

予測ピクチャ (Pピクチャ) は、最大で1つの動きベクトルおよび参照インデックスを使用して各ブロックのサンプル値を予測するイントラ予測またはインター予測を使用してコーディングおよびデコーディングされ得るピクチャであり得る。

【 0 0 6 8 】

双方向予測ピクチャ (Bピクチャ) は、最大で2つの動きベクトルおよび参照インデックスを使用して各ブロックのサンプル値を予測するイントラ予測またはインター予測を使用してコーディングおよびデコーディングされ得るピクチャであり得る。同様に、複数予測ピクチャは、単一のブロックの再構成のために3つ以上の参照ピクチャおよび関連するメタデータを使用することができる。

20

【 0 0 6 9 】

ソースピクチャは、一般に、複数のサンプルコーディングブロック (例えば、各々  $4 \times 4$  、  $8 \times 8$  、  $4 \times 8$  、または  $16 \times 16$  サンプルのブロック) に空間的に細分され、ブロックごとにコーディングされ得る。ブロックは、ブロックそれぞれのピクチャに適用されたコーディング割り当てによって決定されるように他の (すでにコーディングされた) ブロックを参照して予測的にコーディングされ得る。例えば、Iピクチャのブロックは、非予測的にコーディングされ得るか、または、同じピクチャのすでにコーディングされたブロックを参照して、予測的にコーディングされ得る (空間予測またはイントラ予測)。Pピクチャの画素ブロックは、1つの以前にコーディングされた参照ピクチャを参照して、空間予測によって、または時間予測によって予測的にコーディングされ得る。Bピクチャのブロックは、1つまたは2つの以前にコーディングされた参照ピクチャを参照して、空間予測によって、または時間予測を介して予測的にコーディングされ得る。ソースピクチャまたは中間処理されたピクチャは、他の目的で他のタイプのブロックに細分されてもよい。コーディングブロックおよびその他のタイプのブロックの分割は、以下でさらに詳細に説明するように、同じ方法に従う場合もそうでない場合もある。

30

【 0 0 7 0 】

ビデオエンコーダ (603) は、ITU - T Rec. H. 265などの所定のビデオコーディング技術または規格に従ってコーディング動作を実行し得る。その動作において、ビデオエンコーダ (603) は、入力ビデオシーケンスにおける時間的冗長性および空間的冗長性を利用する予測コーディング動作を含む、様々な圧縮動作を実行し得る。したがって、コーディングされたビデオデータは、使用されているビデオコーディング技術または規格によって指定された構文に準拠し得る。

40

【 0 0 7 1 】

いくつかの例示的実施形態では、送信機 (640) は、エンコーディングされたビデオと共に追加のデータを送信し得る。ソースコーダ (630) は、そのようなデータをコーディングされたビデオシーケンスの一部として含めてよい。追加のデータは、時間 / 空間 / S

50

NR増強層、冗長なピクチャやスライスなどの他の形の冗長データ、SEIメッセージ、VUI パラメータセットフラグメントなどを含み得る。

#### 【0072】

ビデオは、複数のソースピクチャ（ビデオピクチャ）として時系列で取り込まれ得る。イントラピクチャ予測（しばしばイントラ予測と略される）は、所与のピクチャにおける空間相関を利用し、インターピクチャ予測は、ピクチャ間の時間またはその他の相関を利用する。例えば、現在のピクチャと呼ばれる、エンコーディング／デコーディング中の特定のピクチャがブロックに分割され得る。現在のピクチャ内のブロックは、ビデオ内の以前にコーディングされたまだバッファされている参照ピクチャ内の参照ブロックに類似している場合、動きベクトルと呼ばれるベクトルによってコーディングされ得る。動きベクトルは、参照ピクチャ内の参照ブロックを指し示し、複数の参照ピクチャが使用されている場合には、参照ピクチャを識別する第3の次元を有することができる。

#### 【0073】

いくつかの例示的実施形態では、インターピクチャ予測に双予測技術を使用することができる。そのような双予測技術によれば、両方ともデコーディング順序でビデオにおいて現在のピクチャ続行する（ただし、表示順序では、それぞれ過去または未来にあり得る）第1の参照ピクチャおよび第2の参照ピクチャなどの2つの参照ピクチャが使用される。現在のピクチャ内のブロックは、第1の参照ピクチャ内の第1の参照ブロックを指し示す第1の動きベクトルと、第2の参照ピクチャ内の第2の参照ブロックを指し示す第2の動きベクトルとによってコーディングすることができる。ブロックは、第1の参照ブロックと第2の参照ブロックの組み合わせによって協調して予測することができる。

#### 【0074】

さらに、マージモード技術が、インターピクチャ予測においてコーディング効率を改善するために使用されてもよい。

#### 【0075】

本開示のいくつかの例示的実施形態によれば、インターピクチャ予測およびイントラピクチャ予測などの予測は、ブロック単位で実行される。例えば、ビデオピクチャのシーケンス内のピクチャは、圧縮のためにコーディングツリーユニット（CTU）に分割され、ピクチャ内のCTUは、 $64 \times 64$ 画素、 $32 \times 32$ 画素、または $16 \times 16$ 画素などの同じサイズを有し得る。一般に、CTUは、3つの並列のコーディングツリーブロック（CTB）、すなわち、1つのルマCTBおよび2つのクロマCTBを含み得る。各CTUは、1つまたは複数のコーディングユニット（CU）に再帰的に四分木分割することができる。例えば、 $64 \times 64$ 画素のCTUを、 $64 \times 64$ 画素の1つのCU、または $32 \times 32$ 画素の4つのCUに分割することができる。 $32 \times 32$ ブロックのうちの1つまたは複数の各々は、 $16 \times 16$ 画素の4つのCUにさらに分割され得る。いくつかの例示的実施形態では、各CUは、インター予測タイプやイントラ予測タイプなどの様々な予測タイプの中からそのCUのエンコーディングを決定するためにエンコーディング中に分析され得る。CUは、時間的予測可能性および／または空間的予測可能性に応じて、1つまたは複数の予測ユニット（PU）に分割され得る。一般に、各PUは、1つのルマ予測ブロック（PB）と、2つのクロマPBとを含む。一実施形態では、コーディング（エンコーディング／デコーディング）における予測動作は、予測ブロック単位で実行される。CUのPU（または異なる色チャネルのPB）への分割は、様々な空間パターンで実行され得る。ルマPBまたはクロマPBは、例えば、 $8 \times 8$ 画素、 $16 \times 16$ 画素、 $8 \times 16$ 画素、 $16 \times 8$ 画素などといった、サンプルの値（例えば、ルマ値）の行列を含み得る。

#### 【0076】

図7に、本開示の別の例示的実施形態によるビデオエンコーダ（703）の図を示す。ビデオエンコーダ（703）は、ビデオピクチャのシーケンスにおける現在のビデオピクチャ内のサンプル値の処理ブロック（例えば、予測ブロック）を受け取り、処理ブロックを、コーディングされたビデオシーケンスの一部であるコーディングされたピクチャにエンコーディングするように構成される。例示的なビデオエンコーダ（703）は、図4の例のビデオエンコーダ（403）の代わりに使用され得る。

10

20

30

40

50

## 【0077】

例えば、ビデオエンコーダ(703)は、 $8 \times 8$ サンプルの予測ブロックなどの処理ブロックのサンプル値の行列を受け取る。次いでビデオエンコーダ(703)は、例えばレート歪み最適化(RDO)を使用して、処理ブロックがそれを使用して最良にコーディングされるのは、イントラモードか、インターモードか、それとも双予測モードかを決定する。処理ブロックがイントラモードでコーディングされると決定された場合、ビデオエンコーダ(703)は、イントラ予測技術を使用して処理ブロックをコーディングされたピクチャにエンコーディングし、処理ブロックがインターモードまたは双予測モードでコーディングされると決定された場合、ビデオエンコーダ(703)は、それぞれインター予測技術または双予測技術を使用して、処理ブロックをコーディングされたピクチャにエンコーディングし得る。いくつかの例示的実施形態では、インターピクチャ予測のサブモードとして、動きベクトルが予測子の外側のコーディングされた動きベクトル成分の恩恵を受けずに1つまたは複数の動きベクトル予測子から導出されるマージモードが使用され得る。いくつかの他の例示的実施形態では、対象ブロックに適用可能な動きベクトル成分が存在し得る。したがって、ビデオエンコーダ(703)は、処理ブロックの予測モードを決定するために、モード決定モジュールなどの、図7に明示的に示されていない構成要素を含み得る。

10

## 【0078】

図7の例では、ビデオエンコーダ(703)は、図7の例示的な構成に示されるように互いに結合されたインターベンコーダ(730)、イントラエンコーダ(722)、残差計算器(723)、スイッチ(726)、残差エンコーダ(724)、汎用コントローラ(721)、およびエントロピーエンコーダ(725)を含む。

20

## 【0079】

インターベンコーダ(730)は、現在のブロック(例えば、処理ブロック)のサンプルを受け取り、そのブロックを参照ピクチャ内の1つまたは複数の参照ブロック(例えば、表示順序で前のピクチャ内および後のピクチャ内のブロック)と比較し、インター予測情報(例えば、インターベンコーディング技術による冗長情報、動きベクトル、マージモード情報の記述)を生成し、任意の適切な技術を使用してインター予測情報に基づいてインター予測結果(例えば、予測されたブロック)を計算するように構成される。いくつかの例では、いくつかの例では、参照ピクチャは、(以下でさらに詳細に説明するように、図7の残差デコーダ728として示されている)図6の例示的なエンコーダ620に組み込まれたデコーディングユニット633を使用してエンコーディングされたビデオ情報に基づいてデコーディングされたデコーディングされた参照ピクチャである。

30

## 【0080】

イントラエンコーダ(722)は、現在のブロック(例えば、処理ブロック)のサンプルを受け取り、ブロックを同じピクチャ内のですにコーディングされたブロックと比較し、変換後の量子化係数を生成し、場合によってはイントラ予測情報(例えば、1つまたは複数のイントラエンコーディング技術によるイントラ予測方向情報)も生成するように構成される。イントラエンコーダ(722)は、イントラ予測情報と、同じピクチャ内の参照ブロックとに基づいて、イントラ予測結果(例えば、予測されたブロック)を計算し得る。

40

## 【0081】

汎用コントローラ(721)は、汎用制御データを決定し、汎用制御データに基づいてビデオエンコーダ(703)の他の構成要素を制御するように構成され得る。一例では、汎用コントローラ(721)は、ブロックの予測モードを決定し、予測モードに基づいてスイッチ(726)に制御信号を提供する。例えば、予測モードがイントラモードである場合、汎用コントローラ(721)は、スイッチ(726)を制御して、残差計算器(723)が使用するためのイントラモード結果を選択させ、エントロピーエンコーダ(725)を制御して、イントラ予測情報を選択させてそのイントラ予測情報をビットストリームに含めさせ、ブロックの叙述モードがインターモードである場合、汎用コントローラ(721)は、スイッチ(726)を制御して、残差計算器(723)が使用するためのインター予測結果を選択させ、エントロピーエンコーダ(725)を制御して、インター予測情報を選択させてそのイ

50

ンター予測情報をビットストリームに含めさせる。

【0082】

残差計算器(723)は、受け取ったブロックと、イントラエンコーダ(722)またはインターエンコーダ(730)から選択されたブロックについての予測結果との差分(残差データ)を計算するように構成され得る。残差エンコーダ(724)は、残差データをエンコーディングして変換係数を生成するように構成され得る。例えば、残差エンコーダ(724)は、残差データを空間領域から周波数領域に変換して変換係数を生成するように構成され得る。変換係数は次いで、量子化変換係数を得るために量子化処理を受ける。様々な例示的実施形態において、ビデオエンコーダ(703)は、残差デコーダ(728)も含む。残差デコーダ(728)は、逆変換を実行し、デコーディングされた残差データを生成するように構成される。デコーディングされた残差データは、イントラエンコーダ(722)およびインターエンコーダ(730)によって適切に使用することができる。例えば、インターエンコーダ(730)は、デコーディングされた残差データとインター予測情報に基づいてデコーディングされたブロックを生成することができ、イントラエンコーダ(722)は、デコーディングされた残差データとイントラ予測情報に基づいてデコーディングされたブロックを生成することができる。デコーディングされたブロックは、デコーディングされたピクチャを生成するために適切に処理され、デコーディングされたピクチャは、メモリ回路(図示せず)にバッファし、参照ピクチャとして使用することができる。

10

【0083】

エントロピーエンコーダ(725)は、ビットストリームをエンコーディングされたブロックを含むようにフォーマットし、エントロピーコーディングを実行するように構成される。エントロピーエンコーダ(725)は、ビットストリームに様々な情報を含めるように構成される。例えば、エントロピーエンコーダ(725)は、汎用制御データ、選択された予測情報(例えば、イントラ予測情報やインター予測情報)、残差情報、および他の適切な情報をビットストリームに含めるように構成され得る。インターモードまたは双予測モードのどちらかのマージサブモードでブロックをコーディングするときには、残差情報が存在しない場合がある。

20

【0084】

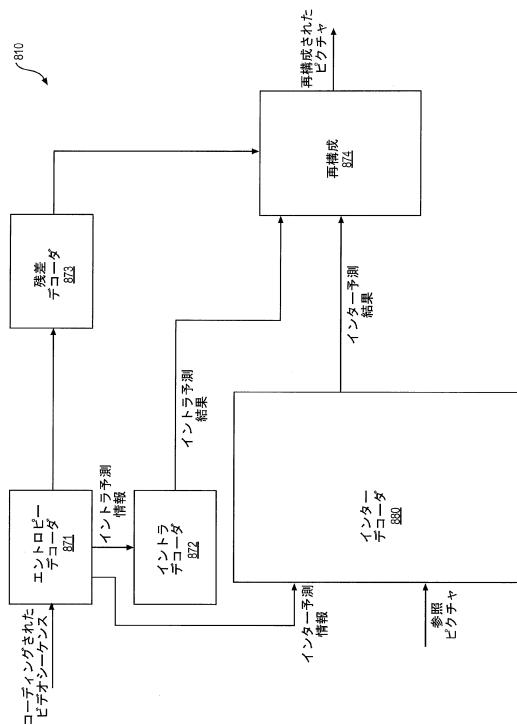

図8に、本開示の別の実施形態による例示的なビデオデコーダ(810)の図を示す。ビデオデコーダ(810)は、コーディングされたビデオシーケンスの一部であるコーディングされたピクチャを受け取り、コーディングされたピクチャをデコーディングして再構成されたピクチャを生成するように構成される。一例では、ビデオデコーダ(810)は、図4の例のビデオデコーダ(410)の代わりに使用され得る。

30

【0085】

図8の例では、ビデオデコーダ(810)は、図8の例示的な構成に示されるように互いに結合されたエントロピーデコーダ(871)、インターデコーダ(880)、残差デコーダ(873)、再構成モジュール(874)、およびイントラデコーダ(872)を含む。

【0086】

エントロピーデコーダ(871)は、コーディングされたピクチャから、コーディングされたピクチャを構成する構文要素を表す特定のシンボルを再構成するように構成することができる。そのようなシンボルは、例えば、ブロックがコーディングされているモード(例えば、イントラモード、インターモード、双予測モード、マージサブモードまたは別のサブモード)、イントラデコーダ(872)またはインターデコーダ(880)によって予測に使用される特定のサンプルまたはメタデータを識別することができる予測情報(例えば、イントラ予測情報やインター予測情報)、例えば量子化変換係数の形の残差情報などを含むことができる。一例では、予測モードがインターモードまたは双予測モードである場合、インター予測情報がインターデコーダ(880)に提供され、予測タイプがイントラ予測タイプである場合、イントラ予測情報がイントラデコーダ(872)に提供される。残差情報は逆量子化を受けることができ、残差デコーダ(873)に提供される。

40

【0087】

50

インターデコーダ(880)は、インター予測情報を受け取り、インター予測情報に基づいてインター予測結果を生成するように構成され得る。

【0088】

イントラデコーダ(872)は、イントラ予測情報を受け取り、イントラ予測情報に基づいて予測結果を生成するように構成され得る。

【0089】

残差デコーダ(873)は、逆量子化を実行して逆量子化変換係数を抽出し、逆量子化変換係数を処理して残差を周波数領域から空間領域に変換するように構成され得る。残差デコーダ(873)はまた、(量子化パラメータ(QP)を含めるために)特定の制御情報を利用とする場合もあり、その情報はエントロピーデコーダ(871)によって提供され得る(これは少量の制御情報のみであり得るためデータパスは図示しない)。

10

【0090】

再構成モジュール(874)は、空間領域において、残差デコーダ(873)による出力としての残差と、(場合によって、インター予測モジュールまたはイントラ予測モジュールによる出力としての)予測結果とを組み合わせて、再構成されたビデオの一部としての再構成されたピクチャの一部を形成する再構成されたブロックを形成するように構成され得る。視覚品質を改善するために、非ブロック化動作などの他の適切な動作が実行されてもよいことに留意されたい。

【0091】

ビデオエンコーダ(403)、(603)、および(703)、ならびにビデオデコーダ(410)、(510)、および(810)は、任意の適切な技術を使用して実装することができることに留意されたい。いくつかの例示的実施形態では、ビデオエンコーダ(403)、(603)、および(703)、ならびにビデオデコーダ(410)、(510)、および(810)を、1つまたは複数の集積回路を使用して実装することができる。別の実施形態では、ビデオエンコーダ(403)、(603)、および(603)、ならびにビデオデコーダ(410)、(510)、および(810)を、ソフトウェア命令を実行する1つまたは複数のプロセッサを使用して実装することができる。

20

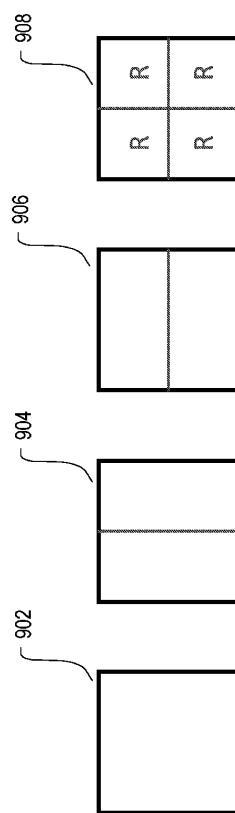

【0092】

コーディングブロック分割を見ると、いくつかの例示的実装形態では、所定のパターンが適用され得る。図9に示すように、第1の所定のレベル(例えば、 $64 \times 64$ ブロックレベル)から開始して第2の所定のレベル(例えば、 $4 \times 4$ レベル)に至る例示的な4ウェイ分割ツリーが用いられ得る。例えば、ベースブロックは、902、904、906および908で示される4つの分割オプションに従うことができ、Rで表されたパーティションは、図9に示される同じ分割ツリーが最下位レベル(例えば、 $4 \times 4$ レベル)まで下位スケールで繰り返され得るという点で、再帰分割が可能である。いくつかの実装形態では、図9の分割方式に追加の制限が適用され得る。図9の実装形態では、長方形分割(例えば、1:2/2:1の長方形分割)は、可能であるが繰り返して用いることはできず、一方、正方形分割は繰り返して用いることができる。必要に応じて、再帰による図9の後に続く分割により、コーディングブロックの最終セットが生成される。そのような方式が、色チャネルのうちの1つまたは複数に適用され得る。

30

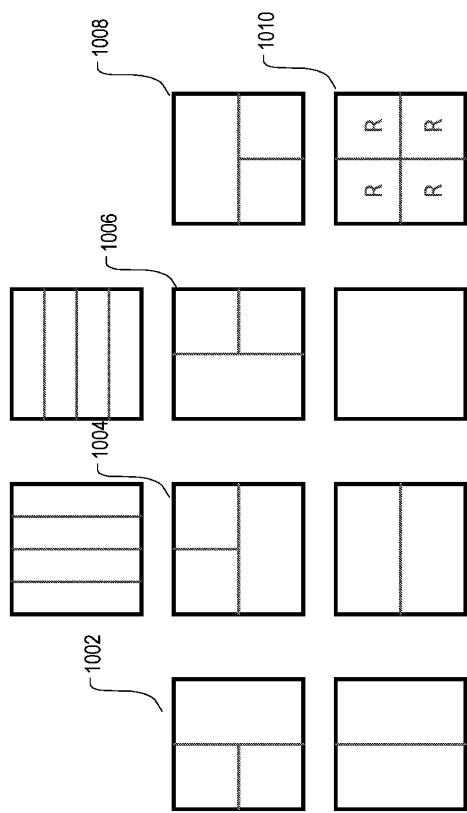

【0093】

図10に、再帰分割により分割ツリーを形成することを可能にする別の例示的な所定の分割パターンを示す。図10に示すように、例示的な10ウェイ分割構造またはパターンが事前定義され得る。ルートブロックは、所定のレベルから(例えば、 $128 \times 128$ レベルまたは $64 \times 64$ レベルから)開始し得る。図10の例示的な分割構造は、様々な2:1/1:2および4:1/1:4の長方形パーティションを含む。図10の2列目の1002、1004、1006、および1008で示される3つのサブパーティションを有する分割タイプは、「T型」分割と呼ばれ得る。「T型」分割1002、1004、1006、および1008は、左T型、上T型、右T型、および下T型と呼ばれてもよい。いくつかの実装形態では、図10の長方形パーティションのいずれもさらに細分されることができない。ルートノードまたはルートブロックか

40

50

らの分割深度を示すために、コーディングツリー深度がさらに定義され得る。例えば、 $128 \times 128$  ブロックのルートノードまたはルートブロックのコーディングツリー深度は0に設定されてもよく、ルートブロックが図10の後に続いてさらに1回分割された後、コーディングツリー深度は1増加する。いくつかの実装形態では、1010の全正方形パーティションのみが、図10のパターンの後に続く分割ツリーの次のレベルへの再帰分割を可能とし得る。言い換えると、再帰分割は、パターン1002、パターン1004、パターン1006、およびパターン1006の正方形パーティションでは不可能である。必要に応じて、再帰による図10の後に続く分割により、コーディングブロックの最終セットが生成される。そのような方式が、色チャネルのうちの1つまたは複数に適用され得る。

#### 【0094】

上記の分割手順または他の手順のいずれかに従ってベースブロックを区分または分割した後にやはり、パーティションまたはコーディングブロックの最終セットが取得され得る。これらのパーティションの各々は、様々な分割レベルのうちの1つにあり得る。各パーティションは、コーディングブロック (CB) と呼ばれ得る。上記の様々な例示的な分割実装形態では、結果として得られる各CBは、許容されるサイズおよび分割レベルのいずれかのものであり得る。それらは、そのためのいくつかの基本的なコーディング / デコーディング決定が行われ、コーディング / デコーディングパラメータが、最適化され、決定され、エンコーディングされたビデオビットストリームにおいてシグナリングされ得るユニットを形成し得るので、コーディングブロックと呼ばれる。最終分割における最高レベルは、コーディングブロック分割ツリーの深度を表す。コーディングブロックは、ルマコーディングブロックまたはクロマコーディングブロックであり得る。

#### 【0095】

いくつかの他の例示的実装形態では、ベースルマブロックおよびベースクロマブロックを再帰的にコーディングユニットに分割するために四分木構造が使用され得る。そのような分割構造はコーディングツリーユニット (CTU) と呼ばれる場合があり、CTUは、四分木構造を使用して分割をベースCTUの様々なローカル特性に適合させることによってコーディングユニット (CU) に分割される。そのような実装形態では、サイズがピクチャ境界に収まるまでブロックが四分木分割を続けるように、ピクチャ境界で暗黙的な四分木分割が実行され得る。CUという用語は、ルマコーディングブロック (CB) およびクロマコーディングブロック (CB) のユニットを集合的に指すために使用される。

#### 【0096】

いくつかの実装形態では、CBがさらに分割され得る。例えば、CBは、コーディングプロセスおよびデコーディングプロセス中のイントラフレーム予測またはインターフレーム予測を目的として、複数の予測ブロック (PB) にさらに分割され得る。言い換えると、CBは異なるサブパーティションにさらに分割されてもよく、そこで個々の予測決定 / 構成が行われ得る。並行して、CBは、ビデオデータの変換または逆変換が実行されるレベルを記述する目的で、複数の変換ブロック (TB) にさらに分割され得る。CBのPBおよびTBへの分割方式は、同じである場合もそうでない場合もある。例えば、各分割方式は、例えば、ビデオデータの様々な特性に基づいて独自の手順を使用して実行され得る。PBおよびTBの分割方式は、いくつかの例示的実装形態では独立してもよい。PBおよびTBの分割方式および境界は、いくつかの他の例示的実装形態では相關していてもよい。いくつかの実装形態では、例えば、TBは、PB分割後に分割されてもよく、特に、各PBは、コーディングブロックの分割の後に続いて決定された後、次いで1つまたは複数のTBにさらに分割されてもよい。例えば、いくつかの実装形態では、PBは、1つ、2つ、4つ、または他の数のTBに分割され得る。

#### 【0097】

いくつかの実装形態では、ベースブロックをコーディングブロックに分割し、さらに予測ブロックおよび / または変換ブロックに分割するために、ルマチャネルおよびクロマチャネルは異なって処理され得る。例えば、いくつかの実装形態では、ルマチャネルに対してはコーディングブロックの予測ブロックおよび / または変換ブロックへの分割が許容さ

10

20

30

40

50

れ得るが、クロマチャネルに対してはコーディングブロックの予測ブロックおよび／または変換ブロックへのそのような分割が許容されない場合がある。そのような実装形態では、よって、ルマブロックの変換および／または予測は、コーディングブロックレベルでのみ実行され得る。別の例では、ルマチャネルおよび（1つまたは複数の）クロマチャネルの最小変換ブロックサイズが異なっていてもよく、例えば、ルマチャネルのコーディングブロックは、クロマチャネルよりも小さい変換ブロックおよび／または予測ブロックに分割されることが許容され得る。さらに別の例では、コーディングブロックの変換ブロックおよび／または予測ブロックへの分割の最大深度がルマチャネルとクロマチャネルとの間で異なっていてもよく、例えば、ルマチャネルのコーディングブロックは、（1つまたは複数の）クロマチャネルよりも深い変換ブロックおよび／または予測ブロックに分割されることが許容され得る。具体例として、ルマコーディングブロックは、最大2レベルだけ下がる再帰分割によって表すことができる複数のサイズの変換ブロックに分割されてもよく、正方形、2:1/1:2、4:1/1:4などの変換ブロック形状、および4×4から64×64の変換ブロックサイズが許容され得る。しかしながら、クロマブロックについては、ルマブロックに指定された可能な最大の変換ブロックのみが許容され得る。

#### 【0098】

コーディングブロックをPBに分割するためのいくつかの例示的実装形態では、PB分割の深度、形状、および／または他の特性は、PBがイントラコーディングされるかそれともインターフォーマンスされるかに依存し得る。

#### 【0099】

コーディングブロック（または予測ブロック）の変換ブロックへの分割は、四分木分割および所定のパターン分割を含むがこれらに限定されない様々な例示的な方式で、再帰的または非再帰的に、コーディングブロックまたは予測ブロックの境界の変換ブロックをさらに考慮して実施され得る。一般に、結果として得られる変換ブロックは、異なる分割レベルにあってもよく、同じサイズでない場合もあり、形状が正方形でなくてもよい（例えば、それらのブロックは、いくつかの許容されるサイズおよびアスペクト比を有する長方形とすることができます）。

#### 【0100】

いくつかの実装形態では、コーディング分割ツリー方式または構造が使用され得る。ルマチャネルとクロマチャネルとに使用されるコーディング分割ツリー方式は、同じでなくてもよい場合がある。言い換えると、ルマチャネルとクロマチャネルとは、別個のコーディングツリー構造を有し得る。さらに、ルマチャネルとクロマチャネルとが同じコーディング分割ツリー構造を使用するか、それとも異なるコーディング分割ツリー構造か、および使用されるべき実際のコーディング分割ツリー構造は、コーディングされているスライスがPスライスか、Bスライスか、それともIスライスかに依存し得る。例えば、Iスライスの場合、クロマチャネルとルマチャネルとは、別個のコーディング分割ツリー構造またはコーディング分割ツリー構造モードを有し得るが、PスライスまたはBスライスの場合、ルマチャネルとクロマチャネルとは、同じコーディング分割ツリー方式を共有し得る。別個のコーディング分割ツリー構造またはモードが適用される場合、ルマチャネルは、あるコーディング分割ツリー構造によってCBに分割され、クロマチャネルは、別のコーディング分割ツリー構造によってクロマCBに分割され得る。

#### 【0101】

コーディングブロックおよび変換ブロックの分割の具体的な例示的実装形態を以下で説明する。そのような一例示的実装形態では、ベースコーディングブロックが、上述した再帰的四分木分割を使用してコーディングブロックに分割され得る。各レベルで、特定のパーティションのさらなる四分木分割を続行すべきかどうかが、ローカルビデオデータ特性によって決定され得る。結果として得られるCBは、様々なサイズの様々な四分木分割レベルにあり得る。ピクチャエリアをインターピクチャ（時間的）予測を使用してコーディングするか、それともイントラピクチャ（空間的）予測を使用してコーディングするかの判断は、CBレベル（または、3色チャネルの場合にはCUレベル）で行われ得る。各CBは、P

10

20

30

40

50

B分割タイプに従って、1つ、2つ、4つ、または他の数のPBにさらに分割され得る。1つのPB内で、同じ予測プロセスが適用されてもよく、関連情報はPBベースでデコーダに送られる。PB分割タイプに基づく予測プロセスを適用することによって残差ブロックを取得した後、CBを、CBのコーディングツリーと同様の別の四分木構造に従ってTBに分割することができる。この特定の実装形態では、CBまたはTBは、ただし、正方形に限定されなくてもよい。さらにこの特定の例では、PBは、インター予測では正方形または長方形の形状であってもよく、イントラ予測では正方形のみであります。コーディングブロックは、例えば4つの正方形形状のTBにさらに分割され得る。各TBは、(四分木分割を使用して)再帰的に、残差四分木 (Residual Quad - Tree (RQT)) と呼ばれるよりも小さいTBにさらに分割され得る。

10

### 【0102】

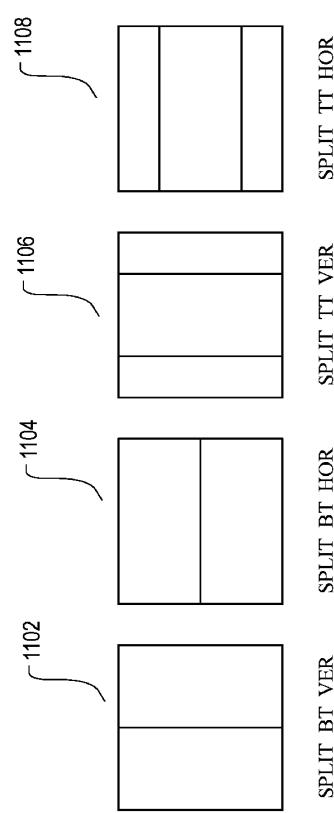

ベースコーディングブロックをCBおよび他のPBおよびまたはTBに分割するための別の具体例を以下で説明する。例えば、図10に示されるような複数の分割ユニットタイプを使用するのではなく、二分割および三分割のセグメント化構造を使用するネストされたマルチタイプツリーを有する四分木が使用されてもよい。CB、PB、およびTBの概念の分離(すなわち、CBのPBおよび/またはTBへの分割、ならびにPBのTBへの分割)は、CBがさらなる分割を必要とし得る、最大変換長には大きすぎるサイズを有するCBに必要な場合を除いて、断念されてもよい。この例示的な分割方式は、予測と変換の両方をさらなる分割なしでCBレベルで実行できるように、CB分割形状のより高い柔軟性をサポートするように設計され得る。コーディングツリー構造では、CBは正方形または長方形のどちらかの形状を有し得る。具体的には、コーディングツリーブロック (CTB) が、まず四分木構造によって分割され得る。次いで、四分木のリーフノードは、マルチタイプツリー構造によってさらに分割され得る。図11にマルチタイプツリー構造の一例を示す。具体的には、図11の例示的なマルチタイプツリー構造は、垂直二分割 (SPLIT\_BT\_VER) (1102)、水平二分割 (SPLIT\_BT\_HOR) (1104)、垂直三分割 (SPLIT\_TT\_VER) (1106)、および水平三分割 (SPLIT\_TT\_HOR) (1108) の4つの分割タイプを含む。CBはその場合、マルチタイプツリーのリーフに対応する。この例示的実装形態では、CBが最大変換長に対して大きすぎない限り、このセグメント化は、さらなる分割なしで予測と変換両方の処理に使用される。これは、ほとんどの場合、CB、PB、およびTBが、ネストされたマルチタイプツリーコーディングブロック構造を有する四分木において同じブロックサイズを有することを意味する。例外が発生するのは、サポートされる最大変換長がCBの色成分の幅または高さよりも小さい場合である。

20

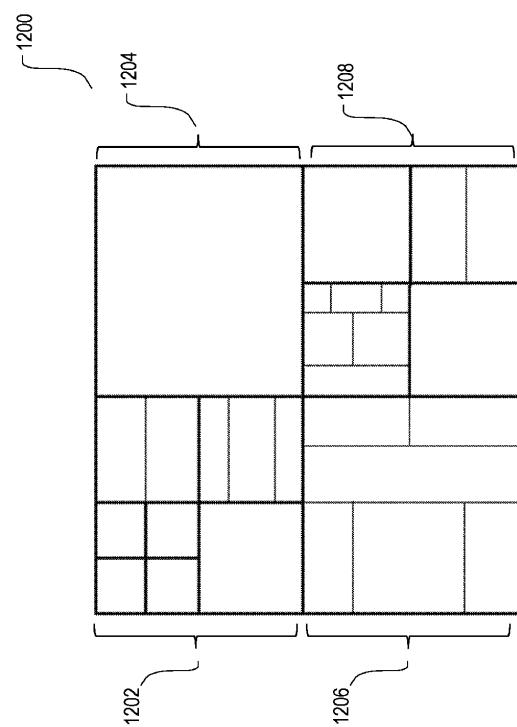

### 【0103】

図12に、1つのCTBのブロック分割のネストされたマルチタイプツリーコーディングブロック構造を有する四分木の一例を示す。より詳細には、図12は、CTB1200が4つの正方形パーティション1202、1204、1206、および1208に四分木分割されることを示している。分割のために図11のマルチタイプツリー構造をさらに使用する決定は、四分木分割されたパーティションの各々について行われる。図12の例では、パーティション1204はこれ以上分割されない。パーティション1202およびパーティション1208は、別の四分木分割を各々採用する。パーティション1202では、第2レベルの四分木分割された左上パーティション、右上パーティション、左下パーティション、および右下パーティションは、四分木、図11の1104、非分割、および図11の1108の第3レベルの分割をそれぞれ採用する。パーティション1208は別の四分木分割を採用し、第2レベルの四分木分割された左上パーティション、右上パーティション、左下パーティション、および右下パーティションは、図11の1106、非分割、非分割、および図11の1104の第3レベルの分割をそれぞれ採用する。1208の第3レベルの左上パーティションのサブパーティションのうちの2つは、1104および1108に従ってさらに分割される。パーティション1206は、2つのパーティションへの図11の1102による第2レベルの分割パターンを採用し、2つのパーティションは図11の1108および1102に従って第3レベルでさらに分割される。第4レベルの分割が、図11の1104に従ってそれらのうちの1つにさらに適用される。

30

40

50

## 【0104】

上記の具体例では、最大ルマ変換サイズは $64 \times 64$ であってもよく、サポートされる最大クロマ変換サイズを、ルマとは異なる、例えば $32 \times 32$ とすることもできる。ルマコーディングブロックまたはクロマコーディングブロックの幅または高さが最大変換幅または最大変換高さよりも大きい場合、ルマコーディングブロックまたはクロマコーディングブロックは、水平方向および/または垂直方向の変換サイズ制限を満たすように水平方向および/または垂直方向に自動的に分割され得る。

## 【0105】

上記のベースコーディングブロックをCBに分割するための具体例では、コーディングツリー方式は、ルマとクロマとが別個のブロックツリー構造を有する能力をサポートし得る。例えば、PスライスおよびBスライスの場合、1つのCTU内のルマCTBとクロマCTBは同じコーディングツリー構造を共有し得る。Iスライスの場合、例えば、ルマとクロマとは別個のコーディングブロックツリー構造を有し得る。別個のブロックツリーモードが適用される場合、ルマCTBは1つのコーディングツリー構造によってルマCBに分割されてもよく、クロマCTBは別のコーディングツリー構造によってクロマCBに分割される。これは、Iスライス内のCUはルマ成分のコーディングブロックまたは2つのクロマ成分のコーディングブロックからなり得、PスライスまたはBスライス内のCUは常に、ビデオがモノクロでない限り3つの色成分すべてのコーディングブロックからなることを意味する。

10

## 【0106】

コーディングブロックまたは予測ブロックを変換ブロックに分割するための例示的実装形態、および変換ブロックのコーディング順序を、以下でさらに詳細に説明する。いくつかの例示的実装形態では、変換分割は、例えば $4 \times 4$ から $64 \times 64$ までの範囲の変換ブロックサイズを有する、複数の形状、例えば $1:1$  (正方形)、 $1:2/2:1$ 、および $1:4/4:1$ の変換ブロックをサポートし得る。いくつかの実装形態では、コーディングブロックが $64 \times 64$ 以下の場合、変換ブロック分割は、クロマブロックについては、変換ブロックサイズがコーディングブロックサイズと同一であるように、ルマ成分にのみ適用され得る。そうではなく、コーディングブロックの幅または高さが $64$ よりも大きい場合には、ルマコーディングブロックとクロマコーディングブロックの両方が、それぞれ、 $\min(W, 64) \times \min(H, 64)$ および $\min(W, 32) \times \min(H, 32)$ の変換ブロックの倍数に暗黙的に分割され得る。

20

## 【0107】

いくつかの例示的実装形態では、イントラコーディングされたブロックとインターフォーマンスコーディングされたブロックの両方について、コーディングブロックが、所定の数のレベル (例えば、2レベル) までの分割深度を有する複数の変換ブロックにさらに分割され得る。変換ブロックの分割深度およびサイズは、関連し得る。現在の深度の変換サイズから次の深度の変換サイズへの例示的なマッピングを以下で表1に示す。

30

## 【0108】

40

50

【表1】

表1：変換分割サイズ設定

| 現在の深度の<br>変換サイズ | 次の深度の<br>変換サイズ |    |

|-----------------|----------------|----|

| TX_4X4          | TX_4X4         | 10 |

| TX_8X8          | TX_4X4         |    |

| TX_16X16        | TX_8X8         |    |

| TX_32X32        | TX_16X16       |    |

| TX_64X64        | TX_32X32       |    |

| TX_4X8          | TX_4X4         |    |

| TX_8X4          | TX_4X4         |    |

| TX_8X16         | TX_8X8         |    |

| TX_16X8         | TX_8X8         |    |

| TX_16X32        | TX_16X16       |    |

| TX_32X16        | TX_16X16       | 20 |

| TX_32X64        | TX_32X32       |    |

| TX_64X32        | TX_32X32       |    |

| TX_4X16         | TX_4X8         |    |

| TX_16X4         | TX_8X4         |    |

| TX_8X32         | TX_8X16        |    |

| TX_32X8         | TX_16X8        |    |

| TX_16X64        | TX_16X32       |    |

| TX_64X16        | TX_32X16       |    |

## 【0109】

表1の例示的なマッピングによれば、1:1正方形ブロックの場合、次のレベルの変換分割は、4つの1:1正方形サブ変換ブロックを作成し得る。変換分割は、例えば、4×4で停止し得る。したがって、4×4の現在の深度の変換サイズは、次の深度の4×4の同じサイズに対応する。表1の例では、1:2/2:1の非正方形ブロックの場合、次のレベルの変換分割は2つの1:1の正方形サブ変換ブロックを作成し、1:4/4:1の非正方形ブロックの場合、次のレベルの変換分割は2つの1:2/2:1サブ変換ブロックを作成する。

## 【0110】

いくつかの例示的実装形態では、インストラコーディングされたブロックのルマ成分に対して、さらなる制限が適用され得る。例えば、変換分割のレベルごとに、すべてのサブ変換ブロックは、等しいサイズを有するように制限され得る。例えば、32×16のコーディングブロックの場合、レベル1の変換分割は、2つの16×16のサブ変換ブロックを作成し、レベル2の変換分割は、8つの8×8のサブ変換ブロックを作成する。言い換えると、変

10

20

30

40

50

換ユニットを等しいサイズに保つために、第2レベルの分割がすべての第1レベルのサブロックに適用されなければならない。表1に従ったイントラコーディングされた正方形ブロックのための変換ブロック分割の一例を、矢印で示されたコーディング順序と共に図13に示す。具体的には、1302は正方形コーディングブロックを示している。表1による4つの等しいサイズの変換ブロックへの第1レベルの分割が、矢印で示されたコーディング順序と共に1304に示されている。表1によるすべての第1レベルの等しいサイズのブロックの16個の等しいサイズの変換ブロックへの第2レベルの分割が、矢印で示されたコーディング順序と共に1306に示されている。

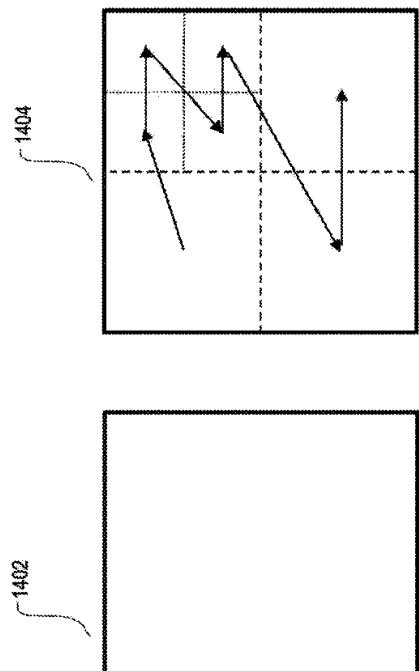

#### 【0111】

いくつかの例示的実装形態では、インターフェースでコーディングされたブロックのルマ成分に対して、イントラコーディングに対する上記の制限が適用されない場合がある。例えば、第1レベルの変換分割の後に、サブ変換ブロックのいずれか1つが、もう1つのレベルでさらに独立して分割され得る。よって、結果として得られる変換ブロックは、同じサイズのものである場合もそうでない場合もある。インターフェースでコーディングされたブロックのコーディング順序を有する変換ブロックへの例示的分割を図14に示す。図14の例では、インターフェースでコーディングされたブロック1402は、表1に従って2つのレベルで変換ブロックに分割される。第1レベルで、インターフェースでコーディングされたブロックは、等しいサイズの4つの変換ブロックに分割される。次いで、4つの変換ブロックのうちの（それらのすべてではなく）1つのみが4つのサブ変換ブロックにさらに分割され、1404で示されるように、2つの異なるサイズを有する合計7つの変換ブロックが得られる。これらの7つの変換ブロックの例示的なコーディング順序が、図14の1404に矢印で示されている。

10

#### 【0112】

いくつかの例示的実装形態では、（1つまたは複数の）クロマ成分に対して、変換ブロックについての何らかの追加の制限が適用され得る。例えば、（1つまたは複数の）クロマ成分について、変換ブロックサイズは、コーディングブロックサイズと同じ大きさとすることができるが、所定のサイズ、例えば $8 \times 8$ より小さくすることはできない。

20

#### 【0113】

いくつかの他の例示的実装形態では、幅（W）または高さ（H）が64よりも大きいコーディングブロックについて、ルマコーディングブロックとクロマコーディングブロックの両方が、それぞれ、 $\min(W, 64) \times \min(H, 64)$  および  $\min(W, 32) \times \min(H, 32)$  の変換ユニットの倍数に暗黙的に分割され得る。

30

#### 【0114】

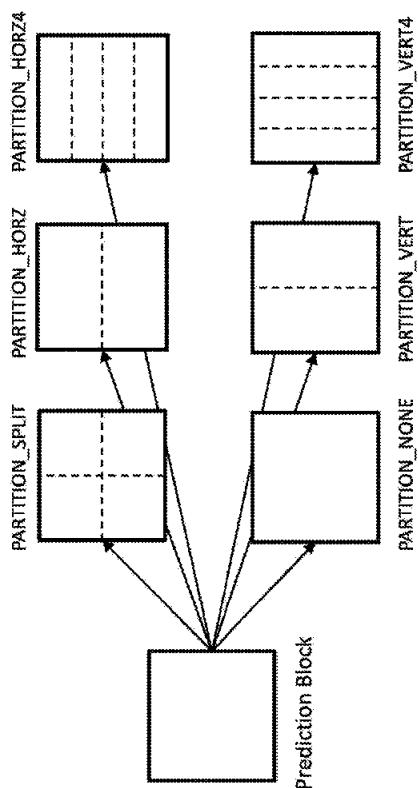

図15に、コーディングブロックまたは予測ブロックを変換ブロックに分割するための別の代替的な例示的方式をさらに示す。図15に示すように、再帰変換分割を使用する代わりに、コーディングブロックの変換タイプに従って所定の分割タイプのセットがコーディングブロックに適用され得る。図15に示す特定の例では、6つの例示的な分割タイプのうちの1つが、コーディングブロックを様々な数の変換ブロックに分割するために適用され得る。このような方式が、コーディングブロックまたは予測ブロックのどちらかに適用され得る。

40

#### 【0115】

より詳細には、図15の分割方式は、図15に示すように、任意の所与の変換タイプに対して最大6つの分割タイプを提供する。この方式では、すべてのコーディングブロックまたは予測ブロックに、例えばレート歪みコストに基づいて変換タイプが割り当てられ得る。一例では、コーディングブロックまたは予測ブロックに割り当てられる分割タイプは、コーディングブロックまたは予測ブロックの変換分割タイプに基づいて決定され得る。図15に例示される4つの分割タイプによって示されるように、特定の分割タイプが、変換ブロックの分割サイズおよびパターン（または分割タイプ）に対応し得る。様々な変換タイプと様々な分割タイプとの間の対応関係が、事前定義され得る。例示的な対応関係を、レート歪みコストに基づいてコーディングブロックまたは予測ブロックに割り当てられ得る変換タイプを示す大文字のラベルと共に以下に示す。

50

## 【0116】

- ・PARTITION\_NONE：ブロックサイズに等しい変換サイズを割り当てる。

## 【0117】

- ・PARTITION\_SPLIT：ブロックサイズの1/2の幅、ブロックサイズの1/2の高さの変換サイズを割り当てる。

## 【0118】

- ・PARTITION\_HORZ：ブロックサイズと同じ幅、ブロックサイズの1/2の高さの変換サイズを割り当てる。

## 【0119】

- ・PARTITION\_VERT：ブロックサイズの1/2の幅、ブロックサイズと同じ高さの変換サイズを割り当てる。

10

## 【0120】

- ・PARTITION\_HORZ 4：ブロックサイズと同じ幅、ブロックサイズの1/4の高さの変換サイズを割り当てる。

## 【0121】

- ・PARTITION\_VERT 4：ブロックサイズの1/4の幅、ブロックサイズと同じ高さの変換サイズを割り当てる。

## 【0122】

上記の例では、図15に示される分割タイプはすべて、分割された変換ブロックについての均一な変換サイズを含む。これは限定ではなく単なる例である。いくつかの他の実装形態では、混合変換ブロックサイズが、特定の分割タイプ（またはパターン）における分割された変換ブロックについて使用され得る。

20

## 【0123】

イントラ予測に戻って、いくつかの例示的実装形態では、コーディングブロックまたは予測ブロック内のサンプルの予測は、基準線のセットのうちの1本に基づくものであり得る。言い換えると、常に最近傍の隣接線（例えば、上記の図1に示されるような予測ブロックの直近の上隣接線や直近の左隣接線）を使用するのではなく、イントラ予測のための選択のオプションとして複数の基準線が提供され得る。そのようなイントラ予測実装形態は、複数基準線選択（Multiple Reference Line Selection (MRLS)）と呼ばれ得る。これらの実装形態では、複数の基準線のうちのどの基準線がイントラ予測子を生成するために使用されるかをエンコーダが決定し、シグナリングする。デコーダ側では、基準線インデックスをパースした後、イントラ予測モード（そのような方向性イントラ予測モード、非方向性イントラ予測モード、およびその他のイントラ予測モード）に従って指定された基準線を探して再構成された参照サンプルを識別することによって、現在のイントラ予測ブロックのイントラ予測を生成することができる。いくつかの実装形態では、基準線インデックスがコーディングブロックレベルでシグナリングされてもよく、複数の基準線のうちの1本のみが選択され、1つのコーディングブロックのイントラ予測に使用され得る。いくつかの例では、複数の基準線がイントラ予測のために一緒に選択され得る。例えば、複数の基準線は、予測を生成するために、重みありまたはなしで、組み合わされ、平均化され、補間され、または任意の他の方法とされ得る。いくつかの例示的実装形態では、MRLSは、ルマ成分にのみ適用され、（1つまたは複数の）クロマ成分には適用されない場合がある。

30

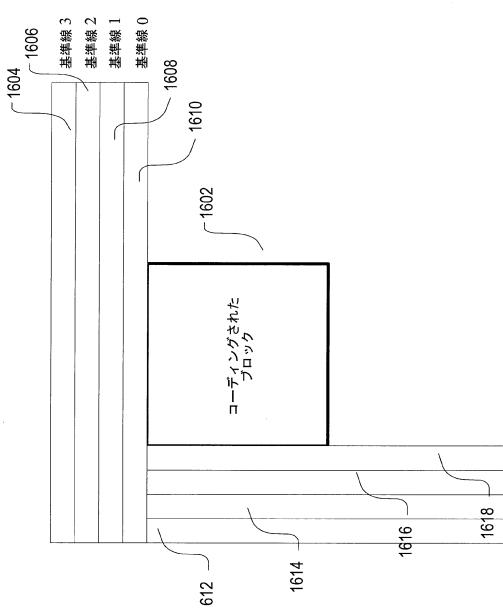

## 【0124】

図16に、4本の基準線MRLSの一例を示す。図16の例に示すように、イントラコーディングブロック1602は、4本の水平基準線1604、1606、1608、および1610、ならびに4本の垂直基準線1612、1614、1616、および1618のうちの1本に基づいて予測され得る。これらの基準線のうち、1610、1618は直接隣接する基準線である。基準線は、コーディングブロックからの距離に従ってインデックス付けされ得る。例えば、基準線1610および基準線1618はゼロ基準線と呼ばれ、その他の基準線は非ゼロ基準線と呼ばれ得る。具体的には、基準線1608および基準線1616は1番目の基準線と呼ばれ、基準線1606

40

50

および基準線1614は2番目の基準線と呼ばれ、基準線1604および基準線1612は3番目の基準線と呼ばれ得る。

【0125】

いくつかの実装形態では、変換ブロックのサイズは、対応するコーディングされたブロックのサイズ以下であり得る。変換ブロックのサイズが対応するコーディングされたブロックのサイズよりも小さい状況下では、コーディングされたブロック内に複数の変換ブロックが存在し得る。しかしながら、コーディングされたブロックの基準線インデックスがコーディングブロックレベルでシグナリングされる場合、コーディングされたブロック内のすべての変換ブロックが、イントラ予測に基準線インデックスを使用する必要があり得る。このアプローチは、個々の変換ブロックのためのローカルテクスチャに適応しない場合があるので、複数の変換ブロックの同じ基準線インデックスは、望ましくなく、非効率である場合がある。

10

【0126】

本開示は、上述の論点／問題のうちの少なくとも1つに対処する、ビデオコーディングおよび／またはビデオデコーディングにおける複数基準線イントラ予測をシグナリングおよび／または決定するための様々な実施形態を説明する。

【0127】

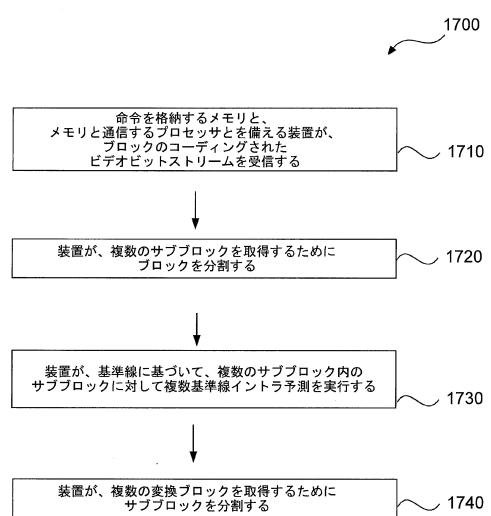

様々な実施形態において、図17を参照すると、ビデオデコーディングにおける複数基準線イントラ予測のための方法1700。方法1700は、以下のステップ、ステップ1710、命令を格納するメモリと、メモリと通信するプロセッサとを備える装置が、ブロックのコーディングされたビデオビットストリームを受信するステップ、ステップ1720、装置が、複数のサブブロックを取得するためにブロックを分割するステップ、ステップ1730、装置が、基準線に基づいて、複数のサブブロック内のサブブロックに対して複数基準線イントラ予測を実行するステップ、および／またはステップ1740、装置が、複数の変換ブロックを取得するためにサブブロックを分割するステップ、の一部または全部を含み得る。いくつかの実装形態では、基準線は、複数基準線イントラ叙述を実行するためのサブブロックについて選択され得る。いくつかの他の実装形態では、複数のサブブロックは、複数のコーディングされたブロックであってもよく、サブブロックは、複数のサブブロック内のコーディングされたブロックであってもよい。

20

【0128】

本開示の様々な実施形態において、ブロック（例えば、これらに限定されないが、コーディングブロック、予測ブロック、または変換ブロック）のサイズは、ブロックの幅または高さを指し得る。ブロックの幅または高さは、画素単位の整数であり得る。

30

【0129】

本開示の様々な実施形態において、ブロック（例えば、これらに限定されないが、コーディングブロック、予測ブロック、または変換ブロック）のサイズは、ブロックの面積サイズを指し得る。ブロックの面積サイズは、画素単位でブロックの幅にブロックの高さを乗じて計算された整数であり得る。

【0130】

本開示のいくつかの様々な実施形態において、ブロック（例えば、これらに限定されないが、コーディングブロック、予測ブロック、または変換ブロック）のサイズは、ブロックの幅もしくは高さの最大値、ブロックの幅もしくは高さの最小値、またはブロックのアスペクト比を指し得る。ブロックのアスペクト比は、ブロックの幅を高さで割ったものとして計算され得るか、またはブロックの高さを幅で割ったものとして計算され得る。

40

【0131】

本開示では、基準線インデックスは、複数の基準線のうちの基準線を示す。様々な実施形態において、基準線インデックスがブロックについて0であることは、ブロックの最近傍の基準線である、ブロックの隣接基準線を示し得る。例えば、図16のブロック（1602）を参照すると、上基準線（1610）は、ブロックの最近傍の上基準線である、ブロック（1602）の上隣接基準線であり、左基準線（1618）は、ブロックの最近傍の左基準線

50

でもある、ブロック(1602)の左隣接基準線である。基準線インデックスがブロックについて0よりも大きいことは、ブロックの非最近傍の基準線である、ブロックの非隣接基準線を示す。例えば、図16のブロック(1602)を参照すると、基準線インデックスが1であることは、上基準線(1608)および／もしくは左基準線(1616)を示し得、基準線インデックスが2であることは、上基準線(1606)および／もしくは左基準線(1614)を示し得、かつ／または基準線インデックスが3であることは、上基準線(1604)および／もしくは左基準線(1612)を示し得る。

#### 【0132】

ビデオコーディングおよび／またはビデオデコーディングのための様々な実施形態において、1本または複数の非隣接基準線がイントラ叙述に使用される場合と比較して、隣接基準線がイントラ叙述に使用される場合には、変換ブロックのサイズを決定および／または指示するための異なるシグナリング方法が適用され得る。

10

#### 【0133】

ステップ1710を参照すると、装置は、図5の電子装置(530)または図8のビデオデコーダ(810)であり得る。いくつかの実装形態では、装置は、図6のエンコーダ(620)内のデコーダ(633)であり得る。いくつかの実装形態では、装置は、図5の電子装置(530)の一部分、図8のビデオデコーダ(810)の一部分、または図6のエンコーダ(620)内のデコーダ(633)の一部分であり得る。コーディングされたビデオビットストリームは、図8のコーディングされたビデオシーケンス、または図6もしくは図7の中間のコーディングされたデータであり得る。いくつかの実装形態では、ブロックは、コーディングブロックまたはコーディングされたブロックを指し得る。

20

#### 【0134】

ステップ1720を参照すると、装置は、複数のコーディングされたブロックを取得するためにブロックを分割し得る。いくつかの実装形態では、装置は、コーディングブロック分割ツリーを取得するために、または集合的にコーディングツリーブロック(CTB)としてブロックを分割し得る。コーディングブロック分割ツリーは、複数のコーディングされたブロックを含み得る。

#### 【0135】

ステップ1730を参照すると、装置は、1本または複数の選択された基準線に基づいて、複数のコーディングされたブロック内のコーディングされたブロックに対して複数基準線イントラ予測を実行する。選択された基準線は、上隣接基準線および／または左隣接基準線を含む隣接基準線、1本もしくは複数の上非隣接基準線および／または1本もしくは複数の左非隣接基準線を含む、1本または複数の非隣接基準線、のうちの少なくとも1本であり得る。選択された基準線は、所定の規則および／または何らかの条件が満たされたときのデフォルト値によって示されてもよい。選択された基準線は、コーディングされたビデオビットストリームから抽出されたパラメータによって示されてもよい。

30

#### 【0136】

ステップ1740を参照すると、装置は、複数の変換ブロックを取得するためにコーディングされたブロックをさらに分割してもよく、これにより、複数の変換ブロック内の1つまたは複数の変換ブロックがコーディングされたブロックよりも小さくなり得る。いくつかの実装形態では、装置は、変換ブロック分割ツリーを取得するためにコーディングされたブロックを分割し得る。

40

#### 【0137】

様々な実施形態において、コーディングされたビデオビットストリームは、選択された基準線が非隣接基準線であることを示す第1のパラメータを含む。方法1700は、コーディングされたビデオビットストリームから第1のパラメータを抽出するステップをさらに含み得る。ステップ1740は、複数の変換ブロックを取得するために、変換パラメータを使用せずに、コーディングされたブロックを分割するステップを含み得る。いくつかの実装形態では、非隣接基準線が選択された基準線であると示される場合、複数の変換ブロックを取得するために、いかなる変換パラメータも使用せずにコーディングされたブロックが

50

分割され得る。

【 0 1 3 8 】

本開示の様々な実装形態において、ブロックの隣接基準線は、ブロックに最も近い基準線を指し得る。例えば、図16のブロック(1602)を参照すると、上基準線(1610)は、ブロックの最近傍の上基準線である、ブロック(1602)の上隣接基準線であり、左基準線(1618)は、ブロックの最近傍の左基準線である、ブロック(1602)の左隣接基準線である。非隣接基準線は、ブロックの最近傍ではない基準線、すなわち、ブロックの非最近傍の基準線を指し得る。例えば、図16のブロック(1602)を参照すると、上基準線(1608)、左基準線(1616)、上基準線(1606)、左基準線(1614)、上基準線(1604)、および／または左基準線(1612)は、ブロック(1602)の非隣接基準線である。

10

【 0 1 3 9 】

いくつかの実装形態では、変換ブロック分割ツリーは変換ブロックを含み、コーディングされたブロックのサイズが最大変換ブロックのサイズ以下であることに応じて、変換ブロックのサイズはコーディングされたブロックのサイズと等しく、かつ／またはコーディングされたブロックのサイズが最大変換ブロックのサイズ以上であることに応じて、変換ブロックのサイズは最大変換ブロックのサイズと等しい。

【 0 1 4 0 】

様々な実装形態において、非隣接基準線が現在のコーディングされたブロックのイントラ叙述に使用される場合、変換ブロックのサイズがコーディングされたビデオビットストリームによってシグナリングされる必要がない場合があり、そのため、ビデオデコーディングが、コーディングされたビデオビットストリームを変換ブロックのサイズを示す余分な任意のシグナリングまでパースする必要がない場合がある。

20

【 0 1 4 1 】

一例では、非隣接基準線が現在のブロックに使用され、コーディングされたブロックのサイズが最大変換ブロックサイズ以下である場合、変換ブロックのサイズは常にコーディングされたブロックのサイズと等しくてもよい。最大変換ブロックサイズは、変換ブロックの最大サイズであり得る。

【 0 1 4 2 】

別の例では、非隣接基準線が現在のブロックに使用され、コーディングされたブロックのサイズが最大変換ブロックサイズ以上である場合、変換ブロックサイズは常に最大変換ブロックサイズと等しい。

30

【 0 1 4 3 】

様々な実装形態において、複数の変換ブロックまたは変換ブロック分割ツリーの変換深度は、選択された基準線が隣接基準線であるかそれとも非隣接基準線であるかに基づいて決定される。

【 0 1 4 4 】

いくつかの実装形態では、非隣接基準線であると示された選択された基準線に応じた変換ブロック分割ツリーの変換深度は、隣接基準線であると示された選択された基準線に応じた変換ブロック分割ツリーの変換深度よりも小さいN深度であり、Nは非負の整数である。

40

【 0 1 4 5 】

様々な実装形態において、現在のブロックのイントラ予測を実行するために異なる基準線が適用される場合、許容される変換深度は、イントラ予測を行うために隣接基準線が使用されるかどうかまたは非隣接基準線が使用されるかどうかに応じて異なり得る。

【 0 1 4 6 】

一例では、イントラ予測を実行するために非隣接基準線が使用されていることに応じた許容される変換深度は、イントラ予測を実行するために隣接基準線が使用されていることに応じた許容される変換深度よりも小さいN深度であり得る。いくつかの実装形態では、Nは、0、1または2などの非負の整数である。

50

**【 0 1 4 7 】**

別の例では、 $N = 1$ の場合、イントラ予測を実行するために非隣接基準線が使用されていることに応じた許容される変換深度は0であり、イントラ予測を実行するために隣接基準線が使用されていることに応じた許容される変換深度は1であり得る。

**【 0 1 4 8 】**

別の例では、 $N = 2$ の場合、イントラ予測を実行するために非隣接基準線が使用されていることに応じた許容される変換深度は0であり、イントラ予測を実行するために隣接基準線が使用されていることに応じた許容される変換深度は2であり得る。

**【 0 1 4 9 】**

様々な実装形態において、基準線インデックスは、選択された基準線を示し、基準線インデックスに基づいて導出されたコンテキストが、複数の変換ブロックまたは変換ブロック分割ツリーの少なくとも1つのパラメータをパースするために使用される。いくつかの実装形態では、基準線インデックスは、装置によってコーディングされたビデオビットストリームから抽出されたパラメータによって示され得る。いくつかの他の実装形態では、コンテキストは、変換ブロックのサイズをシグナリングするために導出される様々な確率の累積密度関数（CDF）であり得る。

10

**【 0 1 5 0 】**

いくつかの実装形態では、現在のコーディングされたブロックのイントラ叙述を実行するために異なる基準線が使用される場合、変換ブロックサイズのシグナリングに異なるコンテキスト（またはCDF）が使用される。いくつかの他の実装形態では、現在のブロックのイントラ叙述を実行するために隣接または非隣接の参照先取特権が使用される場合、変換ブロックサイズのシグナリングに異なるコンテキスト（またはCDF）が使用される。

20

**【 0 1 5 1 】**

様々な実装形態において、コーディングされたビデオビットストリームは、第1のパラメータおよび第2のパラメータを含み、第1のパラメータは複数の変換ブロックまたは変換ブロック分割ツリーを示し、第2のパラメータは選択された基準線を示す。いくつかの実装形態では、変換ブロックのレベルにおける基準線インデックスが個々の変換ブロックに対して別々にシグナリングされ得るので、各変換ブロックが異なる基準線を使用する柔軟性を有し得る。

30

**【 0 1 5 2 】**

いくつかの実装形態では、コーディングブロック分割ツリー内のコーディングされたブロックが複数の変換ブロックにさらに分割され得るので、変換ブロック分割ツリー内の変換ブロックは、コーディングブロック分割ツリー内のコーディングブロックよりも小さい。コーディングされたビットストリームは、コーディングされたブロックのさらなる分割、変換分割、または変換ブロックのサイズをシグナリングするパラメータを含み得る。

**【 0 1 5 3 】**

いくつかの他の実装形態では、イントラ叙述のための基準線のシグナリングは、変換ブロックサイズまたは変換分割のシグナリングに依存し得る。

**【 0 1 5 4 】**

一例として、変換ブロックの分割深度が所与の閾値よりも大きい場合、基準線の選択はシグナリングに依存せず、デフォルト値として導出され得る。所与の閾値は非負の整数であってもよく、例えば、これらに限定されないが、所与の閾値は、0、1、2、3、4、. . . . . または8のうちの1つを含み得る。基準線インデックスのデフォルト値は、例えば、これに限定されないが、イントラ叙述に使用されるべき隣接基準線を示し得る。

40

**【 0 1 5 5 】**

エントロピーコーディングおよび／またはエントロピーデコーディングのための様々な実装形態では、第1のパラメータの構文が第2のパラメータのコンテキストとして使用される。第1のパラメータは、複数の変換ブロックまたは変換ブロック分割ツリーを示し、第2のパラメータは、選択された基準線を示す。

**【 0 1 5 6 】**

50

いくつかの実装形態では、変換ブロックサイズ / 変換分割と基準線インデックスとの間の相関のために、変換ブロックサイズまたは変換分割のシグナリングに関連する構文値を、基準線インデックスのエントロピーコーディングのためのコンテキストとして使用することができる。

#### 【 0 1 5 7 】

いくつかの実施形態では、コーディングされたビデオビットストリームは、選択された基準線を示す第1のパラメータを含み、コーディングブロック分割ツリー内のコーディングされたブロックは、変換ブロック分割ツリー内の複数の変換ブロックにさらに分かれ、かつ / または複数の変換ブロック内の変換ブロックごとの選択された基準線が、コーディングされたブロック内の各変換ブロックの相対位置に基づいて決定される。いくつかの実装形態では、複数の変換ブロック内の第1の変換ブロックがコーディングされたブロックの境界に位置していることに応じて、第1の変換ブロックのための第1の選択された基準線が第1のパラメータによって示され、複数の変換ブロック内の第2の変換ブロックがコーディングされたブロックの境界に位置していないことに応じて、第2の変換ブロックのための第2の選択された基準線がデフォルト値によって示される。

#### 【 0 1 5 8 】

いくつかの実装形態では、構文が、特定の非隣接基準線が適用されていることを示す値でシグナリングされるとき、異なる変換ブロックについて、イントラ予測に使用される基準線は、コーディングブロック内の変換ブロックの相対位置に依存する。いくつかの他の実装形態では、コーディングブロックの境界に位置する変換ブロックは、イントラ予測を行うための構文によって示される基準線を使用することができ、イントラ予測を行うための残りの変換ブロックにはデフォルトの基準線（例えば、隣接基準線）が使用される。コーディングブロックの境界は、上境界、左境界、または上境界および左境界などのうちの1つを含み得る。

#### 【 0 1 5 9 】

本開示の実施形態は、別々に使用されてもよく、任意の順序で組み合わされてもよい。さらに、方法（または実施形態）、エンコーダ、およびデコーダの各々が、処理回路（例えば、1つまたは複数のプロセッサや1つまたは複数の集積回路）によって実装されてもよい。一例では、1つまたは複数のプロセッサは、非一時的コンピュータ可読媒体に格納されたプログラムを実行する。本開示の実施形態はルマブロックまたはクロマブロックに適用されてもよく、クロマブロックでは、実施形態は、複数の色成分に別々に適用され得るか、または複数の色成分に一緒に適用され得る。

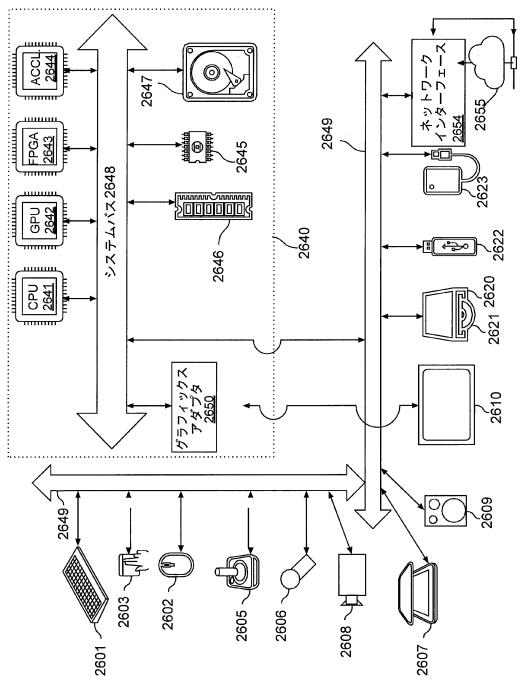

#### 【 0 1 6 0 】

前述した技術は、コンピュータ可読命令を使用する、1つまたは複数のコンピュータ可読媒体に物理的に格納されたコンピュータソフトウェアとして実装することができる。例えば、図18に、開示の主題の特定の実施形態を実装するのに適したコンピュータシステム（2600）を示す。

#### 【 0 1 6 1 】

コンピュータソフトウェアは、1つまたは複数のコンピュータ中央処理装置（CPU）、グラフィックスプロセッシングユニット（GPU）などによって直接、または解釈、マイクロコード実行などを介して、実行することができる命令を含むコードを作成するために、アセンブリ、コンパイル、リンクなどの機構を施される得る任意の適切な機械コードまたはコンピュータ言語を使用してコーディングすることができる。

#### 【 0 1 6 2 】

命令は、例えば、パーソナルコンピュータ、タブレットコンピュータ、サーバ、スマートフォン、ゲームデバイス、モノのインターネットデバイスなどを含む様々なタイプのコンピュータまたはその構成要素上で実行することができる。

#### 【 0 1 6 3 】

コンピュータシステム（2600）について図18に示す構成要素は、本質的に例示的なものであり、本開示の実施形態を実装するコンピュータソフトウェアの使用または機能の範

10

20

30

40

50

囲に関する限定を示唆することを意図するものではない。構成要素の構成は、コンピュータシステム(2600)の例示的な実施形態に示されている構成要素のいずれか1つまたは組み合わせに関する依存関係または要件を有すると解釈されるべきではない。

#### 【0164】

コンピュータシステム(2600)は、特定のヒューマンインターフェース入力装置を含み得るそのようなヒューマンインターフェース入力装置は、例えば、触覚入力(例えば、キーストローク、スワイプ、データグローブの動き)、オーディオ入力(例えば、声、拍手)、視覚入力(例えば、ジェスチャ)、嗅覚入力(図示せず)を介した、1人または複数の人間のユーザによる入力に応答し得る。ヒューマンインターフェース装置はまた、オーディオ(例えば、音声、音楽、周囲音)、画像(例えば、走査画像、写真画像は静止画像カメラから取得)、ビデオ(例えば、二次元映像、立体映像を含む三次元映像)などの、必ずしも人間による意識的な入力に直接関連しない特定のメディアを取り込むために使用することもできる。

10

#### 【0165】

入力ヒューマンインターフェース装置は、キーボード(2601)、マウス(2602)、トラックパッド(2603)、タッチスクリーン(2610)、データグローブ(図示せず)、ジョイスティック(2605)、マイクロフォン(2606)、スキャナ(2607)、カメラ(2608)のうちの1つまたは複数(図示された各々のうちの1つのみ)を含み得る。

#### 【0166】

コンピュータシステム(2600)はまた、特定のヒューマンインターフェース出力装置も含み得る。そのようなヒューマンインターフェース出力装置は、例えば、触覚出力、音、光、および匂い/味によって1人または複数の人間ユーザの感覚を刺激し得る。そのようなヒューマンインターフェース出力装置は、触覚出力装置(例えば、タッチスクリーン(2610)、データグローブ(図示せず)、またはジョイスティック(2605)による触覚フィードバック、ただし、入力装置として機能しない触覚フィードバック装置もあり得る)、オーディオ出力装置(例えば、スピーカ(2609)、ヘッドホン(図示せず))、視覚出力装置(例えば、各々タッチスクリーン入力機能ありまたはなしの、各々触覚フィードバック機能ありまたはなしの、CRTスクリーン、LCDスクリーン、プラズマスクリーン、OLEDスクリーンを含むスクリーン(2610)など、それらの一部は、二次元視覚出力、または立体画像出力、仮想現実眼鏡(図示せず)、ホログラフィックディスプレイおよびスモークタンク(図示せず)などの手段による四次元以上の出力が可能であり得る)、ならびにプリンタ(図示せず)を含み得る。

20

#### 【0167】

コンピュータシステム(2600)はまた、人間がアクセス可能な記憶装置およびそれらの関連媒体、例えば、CD/DVDなどの媒体(2621)を有するCD/DVD ROM/RW(2620)を含む光学媒体、サムドライブ(2622)、リムーバブルハードドライブまたはソリッドステートドライブ(2623)、テープやフロッピーディスクなどのレガシー磁気媒体(図示せず)、セキュリティドングルなどの専用ROM/ASIC/PLDベースのデバイス(図示せず)なども含むことができる。

30

#### 【0168】

当業者はまた、本開示の主題に関連して使用される「コンピュータ可読媒体」という用語が、伝送媒体、搬送波、または他の一時的信号を包含しないことも理解するはずである。

40

#### 【0169】

コンピュータシステム(2600)はまた、1つまたは複数の通信ネットワーク(2655)へのインターフェース(2654)も含むことができる。ネットワークは、例えば、無線、有線、光とすることができます。ネットワークはさらに、ローカル、広域、メトロポリタン、車両および産業、リアルタイム、遅延耐性などとすることができます。ネットワークの例には、イーサネット、無線LANなどのローカルエリアネットワーク、GSM、3G、4G、5G、LTEなどを含むセルラーネットワーク、ケーブルテレビ、衛星テレビ、および地上波放送テレビを含むテレビ有線または無線広域デジタルネットワーク、CANbusを含む車両およ

50

び産業用などが含まれる。特定のネットワークは、一般に、特定の汎用データポートまたは周辺バス (2649) (例えば、コンピュータシステム (2600) のUSBポートなど)に取り付けられた外部ネットワークインターフェースアダプタを必要とする。他のネットワークは、一般に、後述するようなシステムバスへの取り付けによってコンピュータシステム (2600) のコアに統合される (例えば、PCコンピュータシステムへのイーサネットインターフェースやスマートフォンコンピュータシステムへのセルラーネットワークインターフェース)。これらのネットワークのいずれかを使用して、コンピュータシステム (2600) は他のエンティティと通信することができる。そのような通信は、例えば、ローカルまたはワイドエリアデジタルネットワークを使用する他のコンピュータシステムに対して、一方向の受信のみ (例えば、テレビ放送)、一方向の送信のみ (例えば、特定のCANbusデバイスへのCANbus)、または双方向とすることができます。上述のようなネットワークおよびネットワークインターフェースの各々で特定のプロトコルおよびプロトコルスタックを使用することができる。

#### 【0170】

前述のヒューマンインターフェース装置、人間がアクセス可能な記憶装置、およびネットワークインターフェースは、コンピュータシステム (2600) のコア (2640) に取り付けることができる。

#### 【0171】

コア (2640) は、1つまたは複数の中央処理装置 (CPU) (2641)、グラフィックスプロセッsingユニット (GPU) (2642)、フィールドプログラマブルゲートエリア (FPGA) (2643) の形の専用プログラマブル処理装置、特定のタスク用のハードウェアアクセラレータ (2644)、グラフィックスアダプタ (2650)などを含むことができる。これらのデバイスは、読み出し専用メモリ (ROM) (2645)、ランダムアクセスメモリ (2646)、内部非ユーザアクセス可能ハードドライブ、SSDなどの内部大容量ストレージ (2647) と共に、システムバス (2648) を介して接続され得る。一部のコンピュータシステムでは、システムバス (2648) を、追加のCPU、GPUなどによる拡張を可能にするために、1つまたは複数の物理プラグの形でアクセス可能とすることができます。周辺装置は、コアのシステムバス (2648) に直接、または周辺バス (2649) を介して取り付けることができる。一例では、スクリーン (2610) をグラフィックスアダプタ (2650) に接続することができる。周辺バスのアーキテクチャには、PCI、USBなどが含まれる。

#### 【0172】

CPU (2641)、GPU (2642)、FPGA (2643)、およびアクセラレータ (2644) は、組み合わせて前述のコンピュータコードを構成することができる特定の命令を実行することができる。そのコンピュータコードを、ROM (2645) またはRAM (2646) に格納することができる。また移行データをRAM (2646) に格納することもでき、永続データは、例えば内部大容量ストレージ (2647) に格納することができる。メモリデバイスのいずれかへの高速記憶および検索を、1つまたは複数のCPU (2641)、GPU (2642)、大容量ストレージ (2647)、ROM (2645)、RAM (2646) などと密接に関連付けることができるキャッシュメモリの使用によって可能にすることができる。

#### 【0173】

コンピュータ可読媒体は、様々なコンピュータ実装動作を実行するためのコンピュータコードを有し得る。媒体およびコンピュータコードは、本開示の目的のために特別に設計および構築されたものとすることもでき、またはコンピュータソフトウェア技術の当業者に周知の利用可能な種類のものとすることもできる。

#### 【0174】

非限定的な例として、アーキテクチャを有するコンピュータシステム (2600)、特にコア (2640) は、(CPU、GPU、FPGA、アクセラレータなどを含む) (1つまたは複数の) プロセッサが、1つまたは複数の有形のコンピュータ可読媒体において具現化されたソフトウェアを実行した結果として機能を提供することができる。そのようなコンピュータ可読媒体は、上述のようなユーザアクセス可能な大容量ストレージ、ならびにコア内部

10

20

30

40

50

大容量ストレージ (2647) や ROM (2645) などの非一時的な性質のものであるコア (2640) の特定のストレージと関連付けられた媒体とすることができる。本開示の様々な実施形態を実装するソフトウェアを、そのようなデバイスに格納し、コア (2640) によって実行することができる。コンピュータ可読媒体は、特定の必要性に応じて、1つまたは複数のメモリデバイスまたはチップを含むことができる。ソフトウェアは、コア (2640) 、具体的にはその中の (CPU、GPU、FPGAなどを含む) プロセッサに、RAM (2646) に格納されたデータ構造を定義すること、およびソフトウェアによって定義されたプロセスに従ってそのようなデータ構造を変更することを含む、本明細書に記載される特定のプロセスまたは特定のプロセスの特定の部分を実行させることができる。加えて、または代替として、コンピュータシステムは、ソフトウェアの代わりに、またはソフトウェアと共に動作して、本明細書に記載される特定のプロセスまたは特定のプロセスの特定の部分を実行することができる、回路 (例えば、アクセラレータ (2644)) におけるハードウェアードの、または他の方法で具現化された論理の結果として機能を提供することもできる。ソフトウェアと言う場合、それは、適切な場合には、論理を含むことができ、逆もまた同様である。コンピュータ可読媒体と言う場合、それは、適切な場合には、実行のためのソフトウェアを格納する回路 (集積回路 (IC) など) 、実行のための論理を具現化する回路、またはその両方を含むことができる。本開示は、ハードウェアとソフトウェアの任意の適切な組み合わせを包含する。

#### 【0175】

例示的な実施形態を参照して特定の発明を説明したが、この説明は限定を意図したものではない。この説明を読めば当業者には本発明の例示的な実施形態および追加の実施形態の様々な改変形態が明らかになるであろう。本発明の趣旨および範囲から逸脱することなく、本明細書において図示および説明された例示的実施形態に対して上記その他の様々な改変を行うことができることを、当業者は容易に理解するであろう。したがって、添付の特許請求の範囲は、任意のそのような改変形態および代替の実施形態を包含することが企図されている。図内の特定の部分が誇張されている場合もあり、他の部分が最小化されている場合もある。したがって、本開示および図面は、限定的ではなく例示的であるとみなされるべきである。

#### 【符号の説明】

#### 【0176】

- 101 予測されているサンプル、点

- 102 矢印

- 103 矢印

- 104 正方形ブロック

- 180 概略図

- 201 現在のブロック

- 202 周囲のサンプル

- 203 周囲のサンプル

- 204 周囲のサンプル

- 205 周囲のサンプル

- 206 周囲のサンプル

- 300 通信システム

- 310 端末装置

- 320 端末装置

- 330 端末装置

- 340 端末装置

- 350 通信ネットワーク

- 400 通信システム

- 401 ビデオソース

- 402 ビデオピクチャのストリーム

10

20

30

40

50

|     |                               |    |

|-----|-------------------------------|----|

| 403 | ビデオエンコーダ                      |    |

| 404 | エンコーディングされたビデオデータ、ビデオビットストリーム |    |

| 405 | ストリーミングサーバ                    |    |

| 406 | クライアントサブシステム                  |    |

| 407 | エンコーディングされたビデオデータのコピー         |    |

| 408 | クライアントサブシステム                  |    |

| 409 | エンコーディングされたビデオデータのコピー         |    |

| 410 | ビデオデコーダ                       |    |

| 411 | ビデオピクチャの出力ストリーム               |    |

| 412 | ディスプレイ                        | 10 |

| 413 | ビデオ取り込みサブシステム                 |    |

| 420 | 電子装置                          |    |

| 430 | 電子装置                          |    |

| 501 | チャネル                          |    |

| 510 | ビデオデコーダ                       |    |

| 512 | レンダリング装置、ディスプレイ               |    |

| 515 | バッファメモリ                       |    |

| 520 | パーサ                           |    |

| 521 | シンボル                          |    |

| 530 | 電子装置                          | 20 |

| 531 | 受信機                           |    |

| 551 | スケーラ / 逆変換ユニット                |    |

| 552 | イントラピクチャ予測ユニット                |    |

| 553 | 動き補償予測ユニット                    |    |

| 555 | アグリゲータ                        |    |

| 556 | ループフィルタユニット                   |    |

| 557 | 参照ピクチャメモリ                     |    |

| 558 | 現在のピクチャバッファ                   |    |

| 601 | ビデオソース                        |    |

| 603 | ビデオエンコーダ、ビデオコーダ               | 30 |

| 620 | 電子装置                          |    |

| 630 | ソースコーダ                        |    |

| 632 | コーディングエンジン                    |    |

| 633 | ローカルデコーダ                      |    |

| 634 | 参照ピクチャメモリ、参照ピクチャキャッシュ         |    |

| 635 | 予測器                           |    |

| 640 | 送信機                           |    |

| 643 | コーディングされたビデオシーケンス             |    |

| 645 | エントロピーコーダ                     |    |

| 650 | コントローラ                        | 40 |

| 660 | 通信チャネル                        |    |

| 703 | ビデオエンコーダ                      |    |

| 721 | 汎用コントローラ                      |    |

| 722 | イントラエンコーダ                     |    |

| 723 | 残差計算器                         |    |

| 724 | 残差エンコーダ                       |    |

| 725 | エントロピーエンコーダ                   |    |

| 726 | スイッチ                          |    |

| 728 | 残差デコーダ                        |    |

| 730 | インターベンコーダ                     | 50 |

|      |                                                   |    |

|------|---------------------------------------------------|----|

| 810  | ビデオデコーダ                                           |    |

| 871  | エントロピーデコーダ                                        |    |

| 872  | イントラデコーダ                                          |    |

| 873  | 残差デコーダ                                            |    |

| 874  | 再構成モジュール                                          |    |

| 880  | インターデコーダ                                          |    |

| 902  | 分割オプション                                           |    |

| 904  | 分割オプション                                           |    |

| 906  | 分割オプション                                           |    |

| 908  | 分割オプション                                           | 10 |

| 1002 | 左T型分割                                             |    |

| 1004 | 上T型分割                                             |    |

| 1006 | 右T型分割                                             |    |

| 1008 | 下T型分割                                             |    |

| 1010 | 全正方形パーティション                                       |    |

| 1102 | 垂直二分割                                             |    |

| 1104 | 水平二分割                                             |    |

| 1106 | 垂直三分割                                             |    |

| 1108 | 水平三分割                                             |    |

| 1200 | CTB                                               | 20 |

| 1202 | 正方形パーティション                                        |    |

| 1204 | 正方形パーティション                                        |    |

| 1206 | 正方形パーティション                                        |    |

| 1208 | 正方形パーティション                                        |    |

| 1302 | 正方形コーディングブロック                                     |    |

| 1304 | 4つの等しいサイズの変換ブロックへの第1レベルの分割                        |    |

| 1306 | すべての第1レベルの等しいサイズのブロックの16個の等しいサイズの変換ブロックへの第2レベルの分割 |    |

| 1402 | インターフェースされたブロック                                   |    |

| 1404 | 2つの異なるサイズを有する7つの変換ブロック                            | 30 |

| 1602 | イントラコーディングブロック                                    |    |

| 1604 | 水平基準線、上基準線                                        |    |

| 1606 | 水平基準線、上基準線                                        |    |

| 1608 | 水平基準線、上基準線                                        |    |

| 1610 | 水平基準線、上基準線                                        |    |

| 1612 | 垂直基準線、左基準線                                        |    |

| 1614 | 垂直基準線、左基準線                                        |    |

| 1616 | 垂直基準線、左基準線                                        |    |

| 1618 | 垂直基準線、左基準線                                        |    |

| 1700 | 方法                                                | 40 |

| 2600 | コンピュータシステム                                        |    |

| 2601 | キーボード                                             |    |

| 2602 | マウス                                               |    |

| 2603 | トラックパッド                                           |    |

| 2605 | ジョイスティック                                          |    |

| 2606 | マイクロフォン                                           |    |

| 2607 | スキヤナ                                              |    |

| 2608 | カメラ                                               |    |

| 2609 | スピーカ                                              |    |

| 2610 | タッチスクリーン                                          | 50 |

- 2620 CD / DVD ROM / RW

2621 CD / DVDなどの媒体

2622 サムドライブ

2623 リムーバブルハードドライブまたはソリッドステートドライブ

2640 コア

2641 中央処理装置 (CPU)

2642 グラフィックスプロセッシングユニット (GPU)

2643 フィールドプログラマブルゲートエリア (FPGA)

2644 特定のタスク用のハードウェアアクセラレータ

2645 読み出し専用メモリ (ROM)

2646 ランダムアクセスメモリ

2647 コア内部大容量ストレージ

2648 システムバス

2649 汎用データポートまたは周辺バス

2650 グラフィックスアダプタ

2654 ネットワークインターフェース

2655 通信ネットワーク

- 10

【図面】

【図 1 A】

FIG. 1A

(prior art)

【図 1 B】

【図2】

【図3】

10

20

【図4】

FIG. 4

【図5】

30

40

50

【図 6】

【図 7】

10

20

30

【図 8】

【図 9】

FIG. 9

40

50

【図10】

FIG. 10

【 図 1 1 】

FIG. 11

【図12】

FIG. 12

### 【図 1 3】

FIG. 13

【図 1 4】

【図 1 5】

10

20

30

40

50

【図 1 6】

【図 1 7】

【図 1 8】

10

20

30

40

50

---

フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

1 2 9 · サン · ノゼ · フェアフォード · ウェイ · 1 1 7 2

(72)発明者 シャン・リュウ

アメリカ合衆国・カリフォルニア・9 5 1 2 5 · サン · ノゼ · ネバダ · アベニュー · 1 1 5 5

審査官 岩井 健二

(56)参考文献 米国特許出願公開第2 0 1 9 / 0 3 7 9 8 9 1 ( U S , A 1 )

米国特許出願公開第2 0 1 9 / 0 1 8 2 4 8 1 ( U S , A 1 )

国際公開第2 0 2 0 / 0 0 5 5 0 6 ( W O , A 1 )

(58)調査した分野 (Int.Cl. , D B 名)

H 0 4 N 1 9 / 0 0 - 1 9 / 9 8