### (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2001/0040282 A1 Corisis et al.

Nov. 15, 2001 (43) Pub. Date:

(54) STACKABLE BALL GRID ARRAY PACKAGE

Inventors: David J. Corisis, Meridian, ID (US); Jerry M. Brooks, Caldwell, ID (US);

Walter L. Moden, Meridian, ID (US)

Correspondence Address:

TRASK BRITT P.O. BOX 2550

SALT LAKE CITY, UT 84110 (US)

09/917,969 (21) Appl. No.:

(22) Filed: Jul. 30, 2001

### Related U.S. Application Data

Continuation of application No. 09/537,879, filed on Mar. 29, 2000.

### **Publication Classification**

(51) Int. Cl.<sup>7</sup> ...... H01L 23/02

#### (57) ABSTRACT

A stackable FBGA package is configured such that conductive elements are placed along the outside perimeter of an integrated circuit (IC) device mounted to the FBGA. The conductive elements also are of sufficient size so that they extend beyond the bottom or top surface of the IC device, including the wiring interconnect and encapsulate material, as the conductive elements make contact with the FBGA positioned below or above to form a stack. The IC device, such as a memory chip, is mounted upon a first surface of a printed circuit board substrate forming part of the FBGA. Lead wires are used to attach the IC device to the printed board substrate and encapsulant is used to contain the IC device and wires within and below the matrix and profile of the conductive elements.

Fig. 1

Fig. 2

Fig. 5

Fig. 6

Fig. 8

Fig. 9

Fig. 11

Fig. 12

#### STACKABLE BALL GRID ARRAY PACKAGE

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of application Ser. No. 09/537,879, filed Mar. 29, 2000, pending, which is a continuation of application Ser. No. 09/072,101, filed May 4, 1998, now U.S. Pat. No. 6,072,233, issued Jun. 6, 2000.

### BACKGROUND OF THE INVENTION

[0002] The present invention relates generally to packaging semiconductor devices and, more particularly, the present invention relates to fine ball grid array packages that can be stacked to form highly dense components.

[0003] Ball grid array (BGA) semiconductor packages are well known in the art. BGA packages typically comprise a substrate, such as a printed circuit board, with a semiconductor die mounted on the top side of the substrate. The semiconductor die has a multitude of bond pads electrically connected to a series of metal traces on the top side of the printed circuit board. The connection between the bond pads and the metal traces is provided by wire bonds electrically and mechanically connected between the two. This series of metal traces is connected to a second series of metal traces on the underside of the printed circuit board through a series of vias. The second series of metal traces each terminate with a connect contact pad where a conductive element is attached. The conductive elements can be solder balls or conductive filled epoxy. The conductive elements are arranged in an array pattern and the semiconductor die and wire bonds are encapsulated with a molding compound.

[0004] As chip and grid array densities increase, the desire in packaging semiconductor chips has been to reduce the overall height or profile of the semiconductor package. The use of BGAs has allowed for this reduction of profile as well as increased package density. Density reduction has been achieved by utilizing lead frames, such as lead-over chips, in order to increase the densities as well as to branch out into being able to stack units one on top another.

[0005] One example of a lead chip design in a BGA package is shown in U.S. Pat. No. 5,668,405, issued Sep. 16, 1997. This patent discloses a semiconductor device that has a lead frame attached to the semiconductor chip. Through holes are provided that allow for solder bumps to connect via the lead frame to the semiconductor device. This particular reference requires several steps of attaching the semiconductor device to the lead frame, then providing sealing resin, and then adding a base film and forming through holes in the base film. A cover resin is added before solder bumps are added in the through holes to connect to the lead frame. This particular structure lacks the ability to stack devices one on top another.

[0006] U.S. Pat. No. 5,677,566, issued Oct. 14, 1997, and commonly assigned to the assignee of the present invention, discloses a semiconductor chip package that includes discrete conductive leads with electrical contact bond pads on a semiconductor chip. The lead assembly is encapsulated with a typical encapsulating material and electrode bumps are formed through the encapsulating material to contact the conductive leads. The electrode bumps protrude from the encapsulating material for connection to an external circuit.

The semiconductor chip has the bond leads located in the center of the die, thus allowing the conductive leads to be more readily protected once encapsulated in the encapsulating material. Unfortunately, this particular assembly taught in the '566 patent reference also lacks the ability to stack one semiconductor device on top another.

Nov. 15, 2001

[0007] Attempts have been made to stack semiconductor devices in three dimensional integrated circuit packages. One such design is disclosed in U.S. Pat. No. 5,625,221, issued Apr. 29, 1997. This patent discloses a semiconductor package assembly that has recessed edge portions that extend along at least one edge portion of the assembly. An upper surface lead is exposed therefrom and a top recess portion is disposed on a top surface of the assembly. A bottom recess portion is disposed on the bottom surface of the assembly such that when the assembly is used in fabricating a three-dimensional integrated circuit module, the recessed edge portion accommodates leads belonging to an upper semiconductor assembly to provide electrical interconnection therebetween. Unfortunately, the assembly requires long lead wires from the semiconductor chip to the outer edges. These lead wires add harmful inductance and unnecessary signal delay and can form a weak link in the electrical interconnection between the semiconductor device and the outer edges. Further, the device profile is a sum of the height of the semiconductor die, the printed circuit board to which it is bonded, the conductive elements, such as the solder balls, and the encapsulant that must cover the die and any wire bonds used to connect the die to the printed circuit board. So, reducing the overall profile is difficult because of the geometries required in having the lead pads on the semiconductor chip along the outer periphery with extended lead wires reaching from the chip to the outer edges. Another stacked arrangement of semiconductor devices on a substrate interconnected by pins is illustrated in U.S. Pat. Nos. 5,266,912 and 5,400,003. However, the height of the stacked package is limited by the length of the pin connections between the individual multi-chip modules or printed circuit boards.

[0008] Accordingly, what is needed is a ball grid array package that allows stacking of packages on one another. This stackable package would have a lower profile than otherwise provided in the prior art and would reduce the number of steps in the assembly of the package.

### SUMMARY OF THE INVENTION

[0009] According to the present invention, a stackable fine ball grid array (FBGA) package is disclosed that allows the stacking of one array upon another. This stackable FBGA package is configured such that conductive elements are placed along the outside perimeter of a semiconductor device (integrated circuit (IC) device) mounted to the FBGA. The conductive elements also are of sufficient size so that they extend beyond the bottom or top surface of the IC device. Wire interconnect connects the IC device in a way that does not increase the overall profile of the package. Encapsulating material protects both the IC device and the wire interconnect as the conductive elements make contact with the FBGA positioned below or above to form a stack. The IC device, such as a memory chip, is mounted upon a first surface of a printed circuit board substrate forming part of the FBGA. Lead wires, or wire interconnect, are used to attach the IC device to the printed circuit board substrate and

an encapsulant is used to contain the IC device and wires within and below the matrix and profile of the conductive elements.

[0010] Additionally, certain pins on the FBGA in the stack require an isolated connection to the PC board. An example of such a requirement is when an activation signal for a particular IC device within the stack must be sent solely to that device and not to any of the other devices within the stack. This isolated connection connects to an adjacent ball on a different FBGA stack above or below that particular isolated connection since in common pin layouts of the devices are stacked together, and each device requires an isolated connection to the PC board. This provides for a stair step connection from the bottom of the FBGA stacked array to the top that allows each device, from the bottom one to the top one, to have an isolated connection from each other. This allows IC devices to be stacked one upon the other while maintaining a unique pin out for each pin required in the stack.

[0011] Further, the FBGA of the present invention keeps the wire lengths between the IC device and the conductors of the PC board to a minimum for the control of the impedance of the conductors.

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

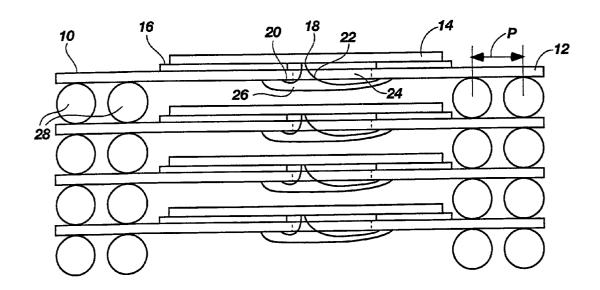

[0012] FIG. 1 depicts a schematic cross-sectional representation of a stacked array of FBGAs according to the present invention;

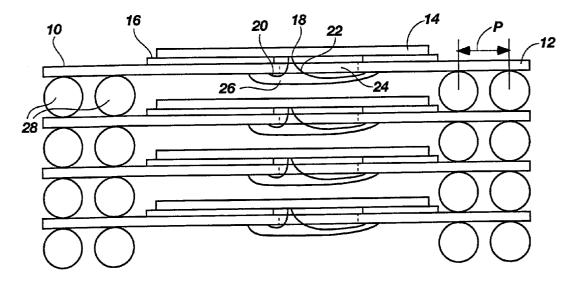

[0013] FIG. 2 depicts a top plan view of a representative circuit board as used in the array of FIG. 1;

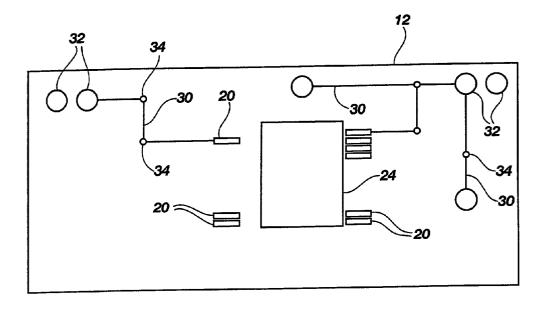

[0014] FIG. 3 depicts a perspective view of a printed circuit board having traces connected one to another with vias and contact through holes;

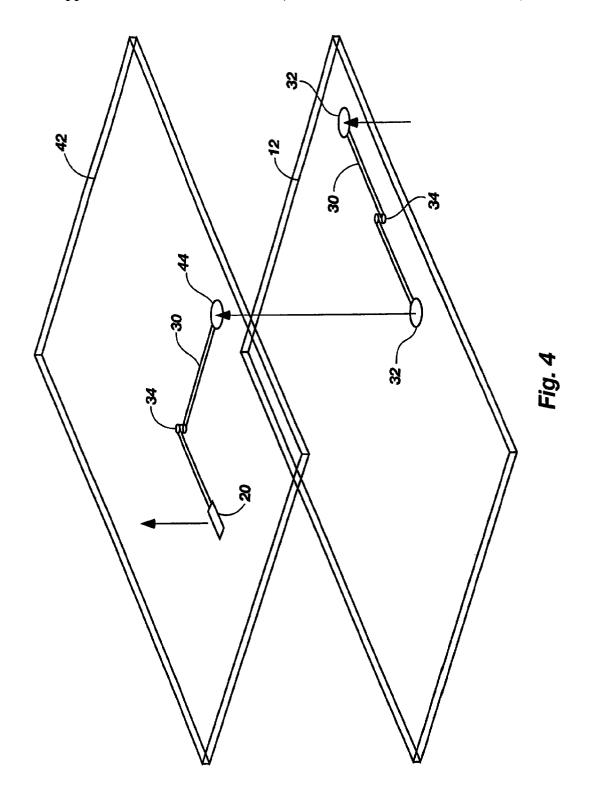

[0015] FIG. 4 depicts a perspective view of a pair of different printed circuit boards having an electrical connection extending from one location on one board to another location on the second board;

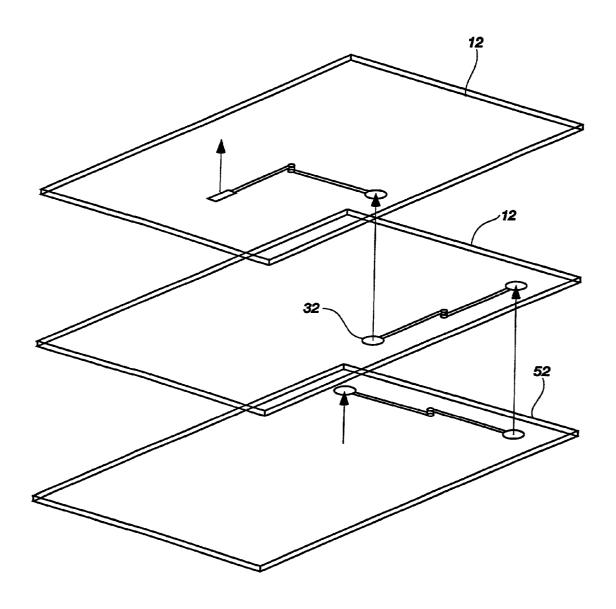

[0016] FIG. 5 depicts a perspective view of multiple PC boards interconnected in a manner according to the present invention:

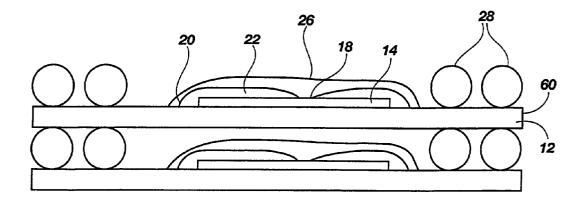

[0017] FIG. 6 is an alternative embodiment of a stackable array according to the present invention;

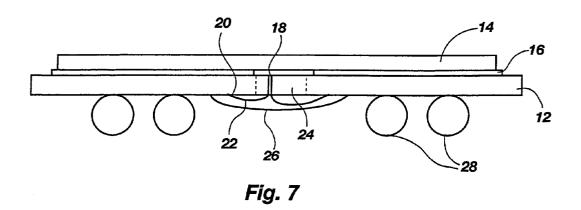

[0018] FIG. 7 depicts another embodiment where the ball grid array matrix extends below the semiconductor device;

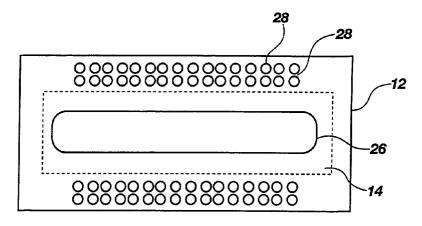

[0019] FIG. 8 depicts a bottom plan view of an FBGA device found in FIG. 1;

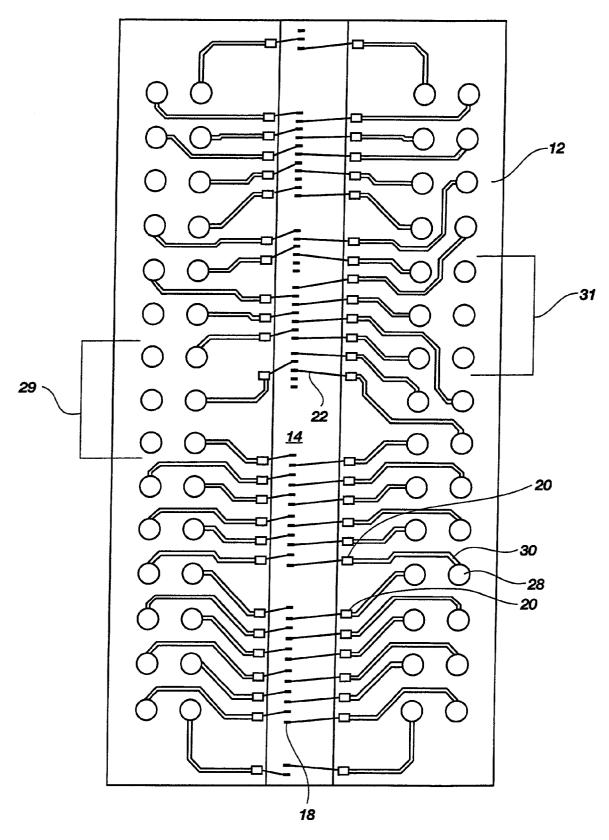

[0020] FIG. 9 is a schematic diagram of a view of a printed circuit board having a mounted IC with wire leads attaching the bond pads of the IC to the bond pads of the printed circuit board;

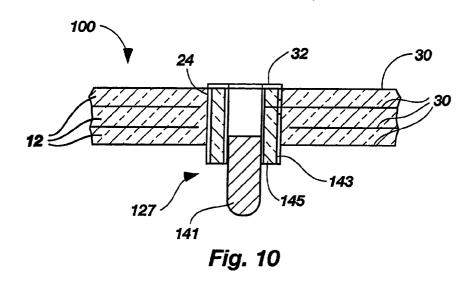

[0021] FIG. 10 is a cross-sectional view of a portion of a printed circuit board illustrating the pin and connection therebetween;

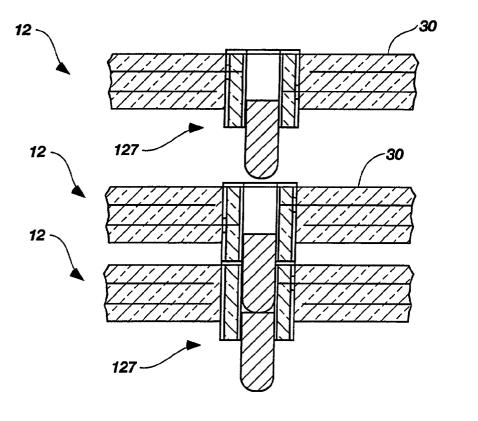

[0022] FIG. 11 is a cross-sectional view of portions of printed circuit boards illustrating the pins and connections therebetween; and

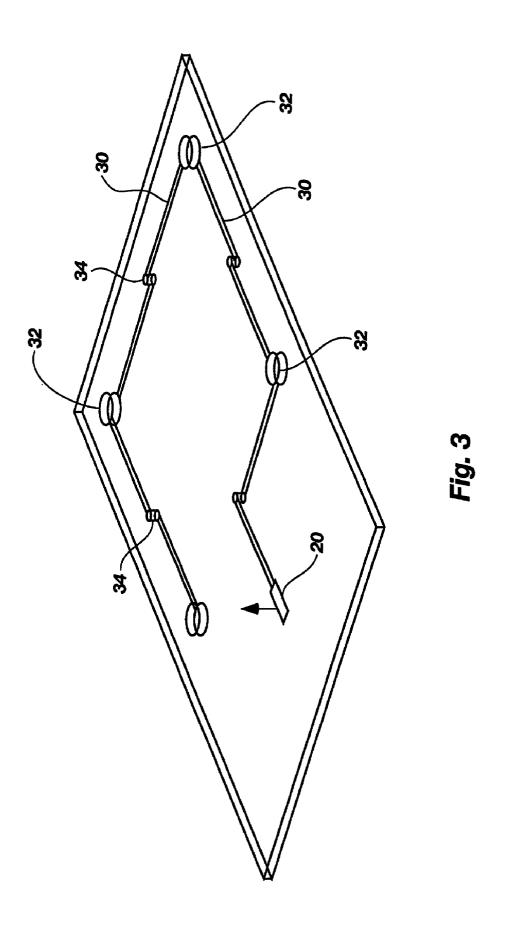

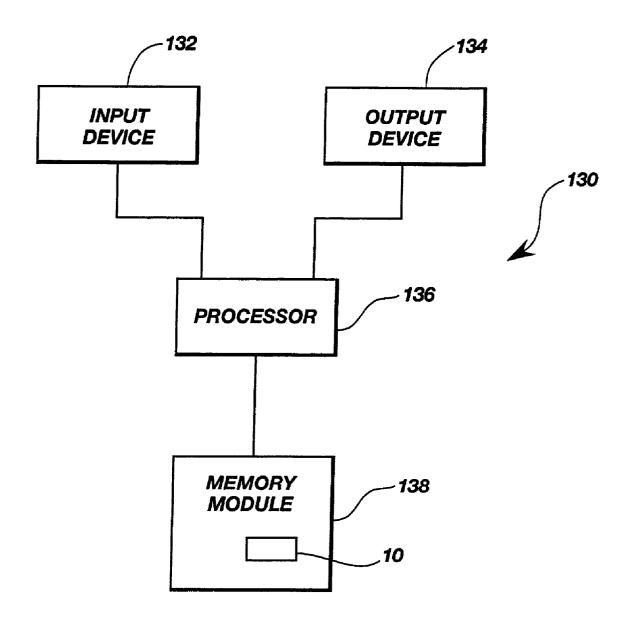

[0023] FIG. 12 is a block diagram of an electronic system incorporating the FBGA module of FIG. 1.

# DETAILED DESCRIPTION OF THE INVENTION

[0024] Referring to drawing FIG. 1, illustrated in a cross-sectional view is a plurality of fine ball grid array (FBGA) packages 10 in a stacked arrangement. Each FBGA package 10 is stacked one upon another via a matrix of conductive elements or solder balls 28 having a first height. Each FBGA package 10 includes a substrate 12 that has conductive traces formed both on the top surface and the bottom surface. Substrate 12 may be formed from an organic epoxy-glass resin base material, such as bismaleimide-triazin (BT) resin or FR-4 board, but is not limited thereto. Other carrier substrate materials well known to those skilled in the art may also be utilized instead, such as, for example, either a ceramic or silicon substrate.

[0025] FBGA package 10 further comprises an integrated circuit or semiconductor die 14 attached to a die attach pad 16 formed on the upper surface of substrate 12. Semiconductor die 14 is attached to die attach pad 16 using a dielectric adhesive that is non-conductive and has a thermal coefficient of expansion (TCE) that closely matches that of the semiconductor die 14. The adhesive can be any type of epoxy resin or other polymer adhesives typically used for such purposes. Alternately, the die attach pad 16 may be formed of double sided, adhesively coated tape, such as an adhesively coated Kapton™ tape or the like. The semiconductor die 14 is formed having a plurality of bond pads 18 that is formed on the active surface thereof which mates with die attach pad 16 of the substrate 12. Each bond pad of the plurality of bond pads 18 aligns with a corresponding aperture 24 in substrate 12. Each bond pad of the plurality of bond pads 18 is electrically connected to terminal pads 20 that are on the surface of substrate 12. Wire bonds 22 are used to form the connections between the plurality of bond pads 18 on the semiconductor die 14 and the terminal pads 20 of the substrate 12 wherein the wire bonds 22 pass through an aperture 24 formed in the substrate 12. A portion of semiconductor die 14 where the bond pads 18 are located, along with the cavity formed by aperture 24, is covered by an encapsulating material 26. Encapsulating material 26 covers or seals bond pads 18, terminal pads 20, and wire bonds 22 to protect them from dust, moisture, and any incidental contact. The encapsulating material 26 has a second height, the second height being less than the first height of the conductive elements 28.

[0026] Conductive elements 28 are attached or bonded to conductive traces 30 (see FIG. 2) of substrate 12. Conductive elements 28 may be selected from acceptable bonding substances such as solder balls, conductive or conductor-filled epoxy, and other substances known to those skilled in the art. The conductive elements 28, which, for example, are solder balls, may be attached, as is known in the art, by coating the solder balls or bond areas or both with flux, placing the solder balls 28 on the conductive traces 30 with conventional ball placing equipment and reflowing the balls in place using an infrared or hot air reflow process. The excess flux is then removed with an appropriate cleaning agent. In this way, the solder balls 28 are electrically and mechanically connected to the conductive leads to form the external electrodes. Other processes may also be used to

form external electrodes. For example, the electrodes may be "plated up" using conventional plating techniques rather than using solder balls as described above. The completed FBGA packages 10 can then be attached to a printed circuit board or the like using conventional surface mount processes and equipment. Likewise, each FBGA package 10 can be mounted one on top another, stacked, as is illustrated in drawing FIG. 1. Solder balls 28 may have a diameter of approximately 0.6 mm with a pitch P that is 0.80 mm. The profile for each FBGA package 10, as measured from the bottom of solder balls 28 to the top of the semiconductor die, may range from 1.0 mm to 1.22 mm.

[0027] Next, as illustrated in drawing FIG. 2, is a top plan view of the bottom surface of substrate 12. This bottom surface includes pass-through aperture 24 where the wire bonds (not shown) are attached to terminal pads 20. Each terminal pad 20 is connected to a metal conductive trace 30, which further connects to a conductive element pad 32. Conductive element pads 32 are placed on either side of substrate 12 and are located where the conductive elements 28 of drawing FIG. 1 are mounted. Additionally, as conductive element pads 32 are placed on the opposite side of substrate 12, they provide a pass-through connection for the stacking of FBGA packages 10 as shown in drawing FIG. 1. Conductive traces 30 are electrically connected to conductive traces on the opposite side (not shown) using vias 34. Conductive traces 30 may be comprised of electrically conductive material such as copper or copper plated with gold. While conductive traces 30 are illustrated in drawing FIG. 2 on the top and bottom of the substrate 12, other conductive traces 30 (not shown) may be located in the substrate 12 along with other vias 34 therein and conductive element pads 32 in addition to those illustrated. Depicted in drawing FIG. 3 is a perspective view of a three dimensional drawing of how conductive traces 30 may be laid out on both the top surface and bottom surface of substrate 12. Additionally, the conductive element pads 32 are also shown to provide connection on either side of substrate 12. Conductive traces 30 are on both sides connected using vias 34 as well as the conductive elements pads 32. The conductive traces 30 are also connected to terminal pads 20. The aperture 24 through substrate 12 may be any desired size in relation to the semiconductor die 14 as may be necessary. Also, the substrate 12 may have portions thereof removed after the mounting of the semiconductor die 14 thereon.

[0028] Depicted in drawing FIG. 4 is an expanded view of the three-dimensional arrangement of substrates 12 achieved using the pass-through holes or vias 34 in conjunction with conductive traces 30 of the substrates 12 to form a stacked arrangement. A first substrate 12 is provided to connect to a second substrate 42. The connection occurs at conductive element pad 32 on substrate 12 and a like conductive element pad 32 on second substrate 42. Next, conductive element pad 32 on second substrate 42 connects to a conductive trace 30 on the surface of second substrate 42, which then passes from one side of second substrate 42 using via 34 to connect to a bond pad on the opposite side of second substrate 42. Referring to drawing FIG. 5, depicted is the manner in which the stepping of conductive traces can continue to yet another level. Referring to drawing FIG. 5, depicted is a third conductive substrate 52 placed below substrate 12 having additional conductive element pads 32 on either side thereof that provide connection to the adjacent substrate 12, which then, in turn, provides connection to second substrate 42. The arrows represent the plane connection on semiconductor packages yet to be added.

[0029] Referring to drawing FIG. 6, depicted is an alternative embodiment of the invention where a semiconductor die 14 is mounted on the upper surface of substrate 12. Wire bonds 22 are then used to connect the bond pads 18 on the active surface of the semiconductor die 14 to the terminal pads 20 of substrate 12. Encapsulating material 26 is then provided to cover the semiconductor die 14, wire bonds 22, bond pads 18 and terminal pads 20. Next, conductive elements 28 are then mounted on the upper surface of substrate 12 around the perimeter of semiconductor die 14. As illustrated, this arrangement allows the stacking of multiple die packages 60. It is understood that the substrate 12 includes circuitry and vias (not shown) as described hereinbefore in drawing FIGS. 2 through 5.

[0030] A third embodiment of the present invention is depicted in drawing FIG. 7. Referring to drawing FIG. 7, shown in a cross-sectional diagram is the manner in which a semiconductor die 14 can extend near to the peripheral edges of substrate 12. In this case, conductive elements 28 are no longer outside the perimeter of semiconductor die 14. Again, wire bonds 22 interconnect bond pads 18 of the semiconductor die 14 to terminal pads 20 on substrate 12. Encapsulating material 26 is utilized to cover the aperture 24, the bond pads 18, terminal pads 20, and wire bonds 22. This particular arrangement of the substrate 12 and semiconductor die 14 may be used as either a bottom level or as a top level in a stacked array, typically, with the use of an interposer.

[0031] Referring to drawing FIG. 8, depicted is a bottom plan view of a semiconductor package 10 as illustrated in drawing FIG. 1. In this example, substrate 12 has a plurality of solder balls 28 mounted along the perimeter of semiconductor die 14, which is shown in outline form. The conductive elements 28 form a connective matrix for connecting to the top surface of another substrate 12 or to the top surface of a carrier substrate that provides external electrical connectivity for the module. Encapsulating material 26 covers the wire leads and bonding pads on either substrate 12 or semiconductor die 14.

[0032] Referring to drawing FIG. 9, illustrated is a schematic diagram of a sample pin and trace layout having isolated connection pads used to connect to the conductive elements 28. As shown, semiconductor die bond pads 18 are aligned in a row down the center of the semiconductor die 14. Wire bonds 22 interconnect bond pads 18 of the semiconductor die 14 to the terminal pads 20 of the substrate 12. From terminal pads 20, conductive traces 30 interconnect conductive elements 28. As can be seen, selected conductive elements 28 have no connection to any of the conductive traces 30 or terminal pads 20 on the substrate 12. These conductive element areas, grouped as 29 and 31, illustrate how certain connections are isolated from that particular semiconductor die 14 mounted on that particular substrate 12. These isolated conductive element areas 29 and 31 allow interconnection among other packages 10 (not shown) stacked one on top of the other within the stacked package arrangement of drawing FIG. 1. The use of selected isolated pins allows for each semiconductor die 14 within the stacked array of packages 10 to have a unique pin out for selected pins on each layer of packages 10. For example, in a

memory package of like semiconductor dies 14 stacked in an array, each semiconductor die 14 requires a select pin that is separate from all other select pins of the other semiconductor dies 14 within the array and that connects to a unique pin in the final pin out configuration. The stackable BGA packages are useful in many types of electronic systems including SDRAM, EDO RAM, video RAM, cache memory, and Read-Only Memory (ROM), as well as microprocessors, application specific integrated circuits (ASIC), digital signal processors, flash memories, electrically erasable programmable read only memory (EEPROM), among others

[0033] Referring to drawing FIG. 10, a connection terminal 100 is illustrated of substrate 12 having conductive traces 30 thereon and therein. The substrate 12 includes conductive traces 30 and an insulator material therebetween, thereby providing the ability of controlling the impedance of the conductive traces 30 having semiconductor die 14 connected thereto by wire bonds 22. The connection terminals 127 include a connection pin 141 which is connected to one of the conductive traces 30. Circuitry in intermediate layers of the substrate 12 extend through apertures 24 in order to permit all connections of the connection pins 141 to be effected through the top of the substrate 12. The terminals include a shield 143, which is separated from the connection pin 141 by an isolation spacer 145. The isolation spacer 145 may be of any material, preferably a dielectric, provided that the isolation spacer 145 permits impedance matched connection through the connection terminals 127. Impedance matching is commonly used for signal transfer applications in which the impedance between signal carrying conductors is a predetermined value per unit length. Changes in length will result in proportional (inverse) changes in impedance, but not changes in the impedance expressed per unit length. The consistent impedance per unit length, colloquially referred to as "impedance value", results in signal matching. This is of interest as operating frequencies exceed those at which unmatched circuits are effective. The use of impedance matched conductors in the present invention of the conductive traces 30, wire bonds 22, and connection terminals 127 therefore facilitates the fabrication of circuits which are inherently impedance matched as desired. Matched impedance is thereby able to reduce spurious signals between semiconductor dies 14, reduce circuit discontinuities, and allow connection circuitry to be designed while controlling the establishment of critical timing paths between components, such as semiconductor dies 14.

[0034] Referring to drawing FIG. 11, the connection terminals 127 permit the stacking of the substrate 12 with connections formed by connection pins 141.

[0035] Referring to drawing FIG. 12, depicted is an electronic system 130 that includes an input device 132 and an output device 134 coupled to a processor device 136, which, in turn, is coupled to a memory device 138 incorporating the exemplary stackable FBGA package 10 and various embodiments thereof as illustrated in drawing FIGS. 1 through 9. Likewise, even processor device 136 may be embodied in a stackable array package 10 comprising a microprocessor, a first level cache memory, and additional ICs, such as a video processor, an audio processor, or a memory management processor, but not limited thereto.

[0036] There has been shown and described a novel semiconductor chip package that is stackable and has a lower profile over that of the prior art. The particular embodiments shown in the drawings and described herein are for purposes of example and are not to be construed to limit the invention as set forth in the pending claims. Those skilled in the art may know numerous uses and modifications of the specific embodiments described without departing from the scope of the invention. The process steps described may, in some instances, be formed in a different order or equivalent structures and processes may be substituted for various structures and processes described.

What is claimed is:

- 1. A ball grid array package, comprising:

- a substrate having a first surface, a second surface, a plurality of conductive element pads on said second surface, and having an aperture extending therethrough;

- a semiconductor device having at least one bond pad thereon, said semiconductor device mounted on said first surface of said substrate;

- at least one wire bond connected to at least one of said plurality of conductive element pads on said second surface of said substrate and said at least one bond pad of said semiconductor device, said at least one wire bond extending through the aperture extending through said substrate;

- material covering said at least one wire bond, said at least one of said plurality of conductive element pad of said substrate, and said at least one bond pad of said semiconductor device, said material forming a first profile height; and

- at least one conductive element located on said second surface of said substrate connected to said at least one conductive element pad of said plurality of conductive element pads of said substrate, said at least one conductive element having a second profile height including one of a profile height at least equal to said first profile height and a profile height at least greater than said first profile height, said at least one conductive element located along a portion of the perimeter of a surface of said substrate.

- 2. The ball grid array package according to claim 1, wherein said material fills a portion of said aperture in said substrate.

- 3. The ball grid array package according to claim 1, wherein at least another one conductive element is located along a portion of the perimeter of said second surface of said substrate.

- **4**. The ball grid array package according to claim 1, wherein said substrate includes a plurality of terminal pads on said first surface thereof.

- 5. A stackable ball grid array package, comprising:

- a substrate having a first surface, a second surface, an aperture extending from the first surface through the substrate to the second surface, and a plurality of conductive element pads on said second surface;

- a semiconductor device having a plurality of bond pads on a first surface thereof, said semiconductor device mounted on said first surface of said substrate;

- at least one wire bond connected to at least one of said plurality of conductive element pads on said second surface of said substrate and at least one bond pad of said plurality of bond pads of said semiconductor device:

- encapsulant material placed on said at least one wire bond, said at least one of said plurality of conductive element pads of said substrate, and said at least one bond pad of said semiconductor device, said encapsulant material forming a first profile height; and

- a plurality of conductive elements located on said second surface of said substrate, at least one conductive element of said plurality of conductive elements coupled to said at least one conductive element pad of said plurality of conductive element pads of said substrate, said plurality of conductive elements having a second profile height being one greater than said first profile height, said at least one conductive element is located along a portion of a perimeter of a surface of said substrate.

- **6.** The stackable ball grid array package according to claim 5, wherein said at least one wire bond extends through said aperture in said substrate.

- 7. The stackable ball grid array package according to claim 5, wherein said encapsulant material fills a portion of said aperture in said substrate.

- **8**. The stackable ball grid array package according to claim 5, wherein said plurality of conductive elements is located along a perimeter of said second surface of said substrate.

- **9.** The stackable ball grid array package according to claim 5, wherein said substrate includes a plurality of terminal pads on said first surface thereof.

- 10. The stackable ball grid array package according to claim 5, wherein said plurality of conductive elements includes a plurality of solder balls, a first portion of said plurality of solder balls aligning in a parallel row having a substantially uniform first pitch space.

- 11. The stackable ball grid array package according to claim 10, wherein a second portion of said plurality of solder balls aligns in a second parallel row having a substantially uniform second pitch space.

- 12. The stackable ball grid array package according to claim 11, wherein said first pitch space of said first portion of said plurality of solder balls and said second pitch space of said second portion of said plurality of solder balls are substantially equal.

- 13. The stackable ball grid array package according to claim 9, wherein at least one predetermined terminal pad of said plurality of terminal pads of said substrate is connected to at least one predetermined bond pad of said plurality of bond pads through said substrate.

- 14. The stackable ball grid array package according to claim 5, wherein at least one of said plurality of conductive elements is isolated from connection to a conductive element pad.

- 15. The stackable ball grid array package according to claim 5, wherein a portion of said plurality of conductive elements is isolated from connection to a conductive element pad.

- 16. The stackable ball grid array package according to claim 5, wherein a portion of said plurality of conductive

- elements on each of two edges of said substrate is isolated from connection to a conductive element pad.

- 17. A stackable ball grid array package, comprising:

- a printed circuit board substrate having a first surface, a second surface, and a plurality of conductive element pads on said second surface;

- a semiconductor device mounted on said first surface of said printed circuit board substrate, said semiconductor device having a plurality of bond pads on a first surface thereof;

- at least one wire bond connecting at least one of said plurality of conductive element pads on said second surface of said printed circuit board substrate and at least one bond pad of said plurality of bond pads of said semiconductor device;

- encapsulant material placed on said at least one wire bond, said at least one of said plurality of conductive element pads of said printed circuit board substrate, and said at least one bond pad of said semiconductor device, said encapsulant material forming a first profile height; and

- a plurality of conductive elements located on said second surface of said printed circuit board substrate connecting said at least one conductive element pad of said plurality of conductive element pads of said printed circuit board substrate, said plurality of conductive elements having a second profile height having one of a height greater than said first profile height and a height at least substantially equal to said first profile height, said at least one conductive element is located along a portion of a perimeter of a surface of said substrate.

- 18. The stackable ball grid array package according to claim 17, wherein said printed circuit board substrate includes an aperture therein.

- 19. The stackable ball grid array package according to claim 18, wherein said at least one wire bond extends through said aperture in said printed circuit board substrate.

- **20**. The stackable ball grid array package according to claim 19, wherein said encapsulant material fills a portion of said aperture in said printed circuit board substrate.

- 21. The stackable ball grid array package according to claim 17, wherein said plurality of conductive elements is located along a perimeter of said second surface of said printed circuit board substrate.

- 22. The stackable ball grid array package according to claim 17, wherein said printed circuit board substrate includes a plurality of terminal pads on said first surface thereof.

- 23. The stackable ball grid array package according to claim 17, wherein said plurality of conductive elements includes a plurality of solder balls, a first portion of said plurality of solder balls aligning in a parallel row having a substantially uniform first pitch space.

- 24. The stackable ball grid array package according to claim 23, wherein a second portion of said plurality of solder balls aligns in a second parallel row having a second pitch space.

- 25. The stackable ball grid array package according to claim 24, wherein said first pitch space of said first portion

of said plurality of solder balls and said second pitch space of said second portion of said plurality of solder balls are substantially equal.

- 26. The stackable ball grid array package according to claim 22, wherein at least one predetermined terminal pad of said plurality of terminal pads of said printed circuit board substrate is connected to at least one predetermined bond pad of said plurality of bond pads through said printed circuit board substrate.

- 27. The stackable ball grid array package according to claim 17, wherein at least one of said plurality of conductive elements is isolated from connection to a conductive pad element

- **28**. The stackable ball grid array package according to claim 17, wherein a portion of said plurality of conductive elements is isolated from connection to a conductive element pad.

- 29. The stackable ball grid array package according to claim 17, wherein a portion of said plurality of conductive elements on each of two edges of said printed circuit board substrate is isolated from connection to a conductive element pad.

- 30. A stackable ball grid array package, comprising:

- a printed circuit board substrate having a first surface, a second surface, an aperture therethrough, and a plurality of conductive element pads on said second surface;

- at least one semiconductor device mounted within a first perimeter of said first surface of said printed circuit board substrate, said at least one semiconductor device having a plurality of bond pads on a first surface thereof:

- a plurality of wire bonds connecting at least some of said plurality of conductive element pads and some of said plurality of bond pads on said second surface of said printed circuit board substrate and extending through said aperture in said printed circuit board substrate;

- encapsulant placed along a portion of said aperture, said plurality of bond pads, and said plurality of wire bonds, said encapsulant forming a first profile height; and

- a plurality of conductive elements mounted along a second perimeter of said second surface, said second perimeter being greater than said first perimeter, said plurality of conductive elements connected to some of said plurality of conductive element pads on said second surface, said plurality of conductive elements having a second profile height of one of a height greater than said first profile height and a height substantially equal to said first profile height, said plurality of conductive elements located along portions of the perimeter of a surface of said substrate.

- 31. The stackable ball grid array package according to claim 30, wherein said first surface of said printed circuit board substrate further includes a plurality of terminal pads.

- 32. The stackable ball grid array package according to claim 30, wherein a first portion of said plurality of conductive elements aligns in a substantially parallel row having a first pitch spacing.

- **33.** The stackable ball grid array package according to claim 32, wherein a second portion of said plurality of conductive elements aligns in a second parallel row having a second pitch spacing.

- **34**. The stackable ball grid array package according to claim 31, wherein a predetermined number of said plurality of terminal pads are connected to a predetermined number of said plurality of bond pads through said printed circuit board substrate.

- 35. A stackable ball grid array package, comprising:

- a printed circuit board substrate having a first surface, having a second surface, having a plurality of conductive element pads on said first surface, and having a plurality of terminal pads on said second surface;

- a plurality of conductive elements, mounted along a first perimeter of said first surface of said printed circuit board substrate and coupled to at least one conductive element pad of said plurality of conductive element pads on said first surface and at least one terminal pad of said plurality of terminal pads, said plurality of conductive elements having a first profile height, said plurality of conductive elements located along portions of a perimeter of a surface of said substrate.

- **36**. The stackable ball grid array package according to claim 35, further comprising:

- a semiconductor device, mounted to said first surface, inside said first perimeter, said semiconductor device having a plurality of bond pads; and

- a plurality of wire bonds, at least one wire bond connected to at least one bond pad of said plurality of bond pads and at least one conductive element of said plurality of conductive elements.

- 37. The stackable ball grid array package according to claim 36, further comprising an encapsulant placed over said plurality of bond pads, said plurality of wire bonds, and a portion of said semiconductor device.

- **38**. The stackable ball grid array package according to claim 36, wherein said first surface of said printed circuit board substrate further comprises a plurality of solder ball bump pads.

- **39**. The stackable ball grid array package according to claim 35, wherein a first portion of said plurality of conductive elements aligns in a parallel row having a first pitch spacing.

- **40**. The stackable ball grid array package according to claim 39, wherein a second portion of said plurality of conductive elements aligns in a second parallel row having a second pitch spacing.

- 41. The stackable ball grid array package according to claim 37, wherein said encapsulant has a second profile height less than said first profile height.

- 42. A stackable ball grid array package, comprising:

- a printed circuit board substrate having a first surface, having a second surface, a plurality of terminal pads on said first surface, having an aperture, and having a plurality of conductive element pads on said second surface;

- a plurality of conductive elements, mounted along a first perimeter of said first surface of said printed circuit board substrate and coupled to some of said plurality of terminal pads on said first surface and some of said plurality of conductive element pads, said plurality of conductive elements having a first profile height, said plurality of conductive elements located along a portion of a perimeter of a surface of said substrate.

- **43**. The stackable ball grid array package according to claim 42, further comprising:

- a semiconductor device mounted to said second surface, inside said first perimeter, said semiconductor device having a plurality of bond pads mounted exposed to said aperture; and

- a plurality of wire bonds, connected to some of said plurality of bond pads and a portion of said plurality of terminal pads and passing through said aperture.

- 44. The stackable ball grid array package according to claim 43, further comprising encapsulant placed over said plurality of bond pads, said plurality of terminal pads, said plurality of wire bonds, and said aperture.

- **45**. The stackable ball grid array package according to claim 43, wherein said first surface of said printed circuit board substrate further comprises a plurality of conductive element pads.

- **46**. The stackable ball grid array package according to claim 44, wherein said encapsulant has a second profile height less than said first profile height of said plurality of conductive elements.

- 47. A ball grid array assembly comprising:

- a plurality of stackable ball grid array packages, each comprising:

- a printed circuit board substrate having a first surface, having a second surface, having an aperture, and having a plurality of conductive element pads on said second surface;

- a semiconductor device, mounted within a first perimeter of said first surface of said printed circuit board substrate and having a plurality of bond pads;

- a plurality of wire bonds connected to at least some of said plurality of conductive element pads on said second surface of said printed circuit board substrate and some of said plurality of bond pads passing through said aperture;

- encapsulant placed along said aperture, on said plurality of bond pads, and said plurality of wire bonds, forming a first profile height; and

- a plurality of conductive elements mounted along a second perimeter of said second surface, said second perimeter being greater than said first perimeter, and coupled to some of said plurality of conductive element pads on said second surface, said plurality of conductive elements having a second profile height greater than said first profile height, said plurality of conductive elements located along a portion of a perimeter of said substrate.;

- each of said plurality of stackable ball grid array packages aligned one atop another such that a plurality of conductive elements on a first ball grid array aligns with and couples to a plurality of conductive element pads on a second ball grid array.

- **48**. The ball grid array assembly according to claim 47, wherein a first part of said plurality of conductive elements on each of said plurality of stackable ball grid array packages aligns in a parallel row having a first pitch spacing.

- **49**. The ball grid array assembly according to claim 48, wherein a second part of said plurality of conductive elements aligns in a second parallel row having a second pitch spacing.

- **50**. The ball grid array assembly according to claim 47, wherein said encapsulant has a second profile height less than said first profile height.

- **51**. The ball grid array assembly according to claim 47, wherein a predetermined number of said plurality of conductive element pads are connected to a predetermined number of said plurality of bond pads through said printed circuit board substrate.

\* \* \* \* \*