(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년03월07일

(11) 등록번호 10-0810203

(24) 등록일자 2008년02월27일

(51) Int. Cl.

H01L 21/027 (2006.01)

(21) 출원번호 10-2006-7003310

(22) 출원일자 2006년02월17일

심사청구일자 2006년07월11일

번역문제출일자 2006년02월17일

(65) 공개번호 10-2006-0064650

(43) 공개일자 2006년06월13일

(86) 국제출원번호 PCT/US2004/014903

국제출원일자 2004년05월13일

(87) 국제공개번호 WO 2005/036625

국제공개일자 2005년04월21일

(30) 우선권주장

10/661,041 2003년09월12일 미국(US)

(56) 선행기술조사문헌

JP06026205 B

(뒷면에 계속)

전체 청구항 수 : 총 20 항

심사관 : 설관식

#### (54) 반도체 디바이스에서 피쳐를 패터닝하기 위한 기술

#### (57) 요 약

반도체 프로세싱 기술이 제공된다. 한가지 측면에 있어서, 반도체 디바이스내부에 하나 이상의 피쳐를 패터닝하기 위한 방법은 이하의 단계를 포함한다. 하나 이상의 피쳐의 적어도 하나의 임계 치수가 반사방지 물질의 예칭 동안에 감소된다. 리소그래픽 구조물이 또한 제공된다.

#### 대표도

(72) 발명자

홈즈, 스티븐, 제이.

미국, 뉴욕 12084, 길더랜드, #11 길더 레인 아파트 103

마호로월러, 아르판, 피.

미국, 뉴욕 10708, 브롱크스빌, 브롱크스빌 로드 475

파이퍼, 더크

미국, 뉴욕 10522, 도브스 페리, 메인 스트리트 애파트. 3C 24

와이즈, 리차드, 스테판

미국, 뉴욕 12553, 뉴 원저, 샌드게이트 드라이브 429

(56) 선행기술조사문현

JP13242630 A

KR100256137 B1

US05753418 A1

US6514867 A1

## 특허청구의 범위

### 청구항 1

반도체 디바이스내에 하나 이상의 피처(feature)를 패터닝하기 위한 방법에 있어서,

반사방지(antireflective) 물질의 예칭동안 상기 하나 이상의 피처의 적어도 하나의 임계 치수(critical dimension)를 감소시키는 단계를 포함하되, 상기 반사방지 물질의 예칭은 하나 이상의 중합체층의 플라즈마 중합체 증착(plasma polymer deposition)이 수반되며,

상기 반사방지 물질은 하나 이상의 무기 성분(inorganic moieties)을 포함하고, 상기 하나 이상의 피처의 임계 치수의 감소량을 조정하기 위하여 상기 하나 이상의 무기 성분의 양이 변경되는 방법.

### 청구항 2

삭제

### 청구항 3

삭제

### 청구항 4

제1항에 있어서,

상기 반사방지 물질은 M:탄소:수소:X의 구조식을 가지며, 상기 M은 금속을 포함하고 X는 무기 원소를 포함하는 방법.

### 청구항 5

제4항에 있어서,

상기 M은 실리콘(silicon), 티타늄(titanium), 게르마늄(germanium), 철(iron), 봉소(boron), 주석(tin) 및 이 상의 금속들중 적어도 하나를 포함하는 조합으로 구성되는 그룹으로부터 선택되는 금속을 포함하는 방법.

### 청구항 6

제4항에 있어서,

상기 X는 산소, 수소, 질소 및 이상의 무기 원소들중 적어도 하나를 포함하는 조합으로 구성되는 그룹으로부터 선택되는 무기 원소를 포함하는 방법.

### 청구항 7

제1항에 있어서,

상기 반사방지 물질은 실리콘:탄소:수소:산소 의 구조식을 갖는 방법.

### 청구항 8

제1항에 있어서,

상기 반사방지 물질은 가변 내에칭성 반사방지 코팅(tunable etch resistant antireflective coating)을 포함하는 방법.

### 청구항 9

제1항에 있어서,

상기 반사방지 물질은 스펀 온 프로세싱에 의해 기판상에 증착되는 방법.

### 청구항 10

제1항에 있어서,

상기 반사방지 물질은 플라즈마 강화 화학적 기상 증착을 이용하여 기판상에 증착되는 방법.

### 청구항 11

삭제

### 청구항 12

삭제

### 청구항 13

제1항에 있어서,

상기 하나 이상의 피처 각각은 컨택트 홀, 비아 패턴, 라인, 스페이스, 오벌(ovals) 및 이상의 피처들중 적어도 하나를 포함하는 조합으로 구성되는 그룹으로부터 선택되는 피처를 포함하는 방법.

### 청구항 14

삭제

### 청구항 15

제1항에 있어서,

상기 하나 이상의 피처중 임의의 하나의 임계 치수는 80 나노미터까지 감소되는 방법.

### 청구항 16

제1항에 있어서,

상기 반사방지 물질은 풀루오르카본 가스, 아르곤 가스, 산소 가스 및 질소 가스 중 최소한 하나를 포함하는 플라즈마 에칭을 이용하여 에칭되는 방법.

### 청구항 17

제16항에 있어서,

상기 하나 이상의 피처의 임계 치수의 원하는 감소를 얻기 위해 상기 풀루오르카본 가스, 상기 아르곤 가스, 상기 산소 가스 및 상기 질소 가스의 하나 이상의 양이 변경되는 방법.

### 청구항 18

제1항에 있어서,

상기 중합체 증착은 10 나노미터 내지 500 나노미터의 하나 이상의 중합체 층의 증착을 포함하는 방법.

### 청구항 19

제1항에 있어서,

상기 반사방지 물질상에 방사 감광성 이미지 층(radiation sensitive imaging layer)을 형성하는 단계를 더 포함하고, 상기 방사 감광성 이미지 층은 상기 반사방지 물질과 조성상 다른 방법.

### 청구항 20

제19항에 있어서,

상기 방사 감광성 이미지 층은 하나 이상의 유기 성분(organic moieties)을 포함하는 방법.

### 청구항 21

제1항에 있어서,

기판상에 상기 반사방지 물질을 증착하는 단계와,

상기 기판의 에칭동안 상기 하나 이상의 피처의 적어도 하나의 임계 치수를 감소시키는 단계를 더 포함하는 방법.

### 청구항 22

제1항에 있어서,

상기 반사방지 물질은 유전 물질을 포함하는 기판상에 증착되는 방법.

### 청구항 23

제1항에 있어서,

상기 반사방지 물질은 낮은-k 유전 물질을 포함하는 기판상에 증착되는 방법.

### 청구항 24

제1항에 있어서,

상기 반사방지 물질은 플루오르실리케이트(fluorosilicate) 클래스, 보로실리케이트(borosilicate) 클래스, 보로포스포실리케이트(borophosphorusilicate) 클래스 및 이상의 산화물 물질들중 적어도 하나를 포함하는 조합으로 구성되는 그룹으로부터 선택되는 산화물 물질을 포함하는 기판상에 증착되는 방법.

### 청구항 25

삭제

### 청구항 26

삭제

### 청구항 27

제1항에 있어서,

상기 하나 이상의 치수는 패터닝동안 얻어지는 하나 이상의 피처의 특성 치수를 포함하는 방법.

## 명세서

### 기술분야

<1> 본 발명은 반도체 프로세싱에 관한 것이며, 좀더 구체적으로는 반도체 디바이스에서 패터닝된 피처(feature)의 임계 치수(critical dimension)를 줄이기 위한 것이다.

### 배경기술

<2> 피처의 패터닝이 리소그래픽으로 가능한 것보다 더 작을 것이 종종 요구된다. 예를 들면, 컨택트 홀 및 비어와 같은 피처의 패터닝은 레지스트에서 리소그래픽으로 한정되는 것보다 작은 임계 치수를 가지며 기판에서 한정되는 피처가 바람직할 수 있다. 피처의 임계 치수는 이용하는 기술에 따라 얻어지는 피처의 특성 면적을 포함한다. 패터닝되는 피처의 임계 치수를 줄이기 위한 종래 기술이 존재하나 이러한 기술들은 여러가지 문제점을 갖고 있다.

<3> 임계 치수를 줄이기 위한 한가지 일반적인 기술은 레지스트 리플로우(resist reflow)와 코팅막(overcoat film)의 이용을 포함하며, 예를 들면, 화학적 쉬링크(RELACS) 처리에 의한 분해 강화 리소그래피가 있다. 레지스트 리플로우는 베이크 플레이트에 걸친 아주 작은 온도 변화에 의해 각각의 웨이퍼의 임계 치수에 큰 변화를 야기 시킬 수 있기 때문에 제어하는 것이 극도로 어렵다. 전형적인 민감도는 섭씨당 10 나노미터 정도이다( $\text{nm}/\text{C}$ ). 코팅막은 감광-현상된 화학적으로 증폭된 레지스트의 상단에서 스펜 온 될 수 있다. 광산(photoacid)은 레지스트로부터 코팅막으로 교차결합시키며 확산한다. 레지스트와 물리적 접촉이 없는 코팅막의 일부(예를 들면, 피처 바닥)는 교차결합되지 않으며, 따라서 현상될 수 있다. 레지스트 타입에 따라 특정되는, 이러한 기술은 구현하

기 어렵다. 더구나, 교차결합된 코팅막은 기판 애칭 공정중에 낮은 애칭 저항성을 가지며, 얻어진 임계 치수의 축소를 무효로 만든다. 또한, 실리레이팅 레지스트(silylating resist)가 레지스트 피처를 화학적으로 바이어스하는데 이용될 수 있으나, 크로스-웨이퍼 및 네스티드-격리된 바이어스 문제점이 있다. 상기 기술들은 날카롭지 않고 둥그런 코너를 갖는 피처를 만들 수 있다.

<4> 또 다른 일반적인 기술은 기판에서 테이퍼(taper)를 유도하여 피처 바닥에서 임계 치수를 줄이는 폴리머라이징 애칭 화학을 이용하는 것이다. 기판 상단에서 피처의 임계 치수는 오버레이 층(예를 들면, 반사방지 층(antireflective layer))을 애칭한 후에 얻어진 임계 치수와 거의 동일하다. 기판에 생성되는 피처 측벽은 약간 테이퍼되며, 이것은 많은 어플리케이션에 바람직하다. 예를 들면, 유전체 층내에 컨택트 홀 또는 비어가 패터닝 되후, 완전히 수직이 아닌 약간 테이퍼된 유전체 기판 측벽에 의해 구리 시드층 증착이 용이해진다. 그러나, 최대한의 임계 치수 감소는 견딜수 있는 측벽 테이퍼에 의존한다. 예로서, 유전체 층이 약 500 나노미터(nm) 두께이고 측벽이 수평에서 약 88.5도라면 피처 바닥은 피처 상단보다 약 20nm 정도 작을 것이다. 피처 상단의 임계 치수가 너무 크게 시작한다면 이 기술의 효과는 매우 제한적일 것이다.

<5> 그러므로, 넓은 범위의 임계 치수를 갖는 피처의 패터닝을 위하여 패터닝된 피처의 임계 치수를 줄이기 위한 효과적이고, 재현가능하고 다용도의 기술이 바람직할 것이다. 또한, 사용되는 레지스트의 타입에 상관없이 이용될 수 있으며 전체 웨이퍼에서 동일한 피처의 대량 생산을 제공할 수 있는 패터닝되는 피처의 임계 치수를 줄이기 위한 기술이 요구된다.

### 발명의 상세한 설명

<6> 본 발명은 반도체 프로세싱을 위한 기술을 제공한다. 본 발명의 일측면에 따라, 반도체 디바이스내의 하나 이상의 피처를 패터닝하기 방법은 이하의 단계를 포함한다. 하나 이상의 피처의 적어도 하나의 임계 치수가 반사방지 물질의 애칭동안 감소된다.

<7> 본 발명의 다른 측면에 따라, 리소그래피 구조물은 그 내부에 패터닝된 피처를 갖는 반사방지 물질을 포함하며, 상기 피처는 적어도 하나의 감소된 임계 치수를 갖는다.

<8> 이하의 상세한 설명 및 도면을 참조하여 본 발명의 이점과 특성을 보다 완전히 이해할 수 있을 것이다.

### 실시 예

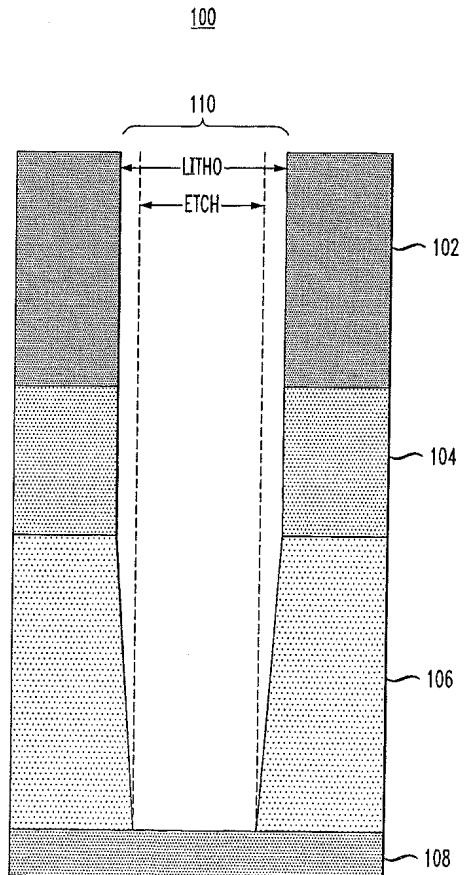

<13> 도 1은 종래의 기술을 이용하여 감소된 임계 치수를 갖는 피처가 있는 반도체 디바이스를 나타내는 도면이다. 도 1에 도시된 바와 같이, 반도체 디바이스(100)는 반사방지 물질(antireflective material)(104)상에 증착된 방사 감광성 이미지 층(radiation sensitive imaging layer)(102)을 포함한다. 반사방지 물질(104)은 기판(100)상에 증착된다. 기판(106)은 질화물 층(108)상에 증착된다. 피처(110)는 방사 감광성 이미지 층(102), 반사방지 물질(104)과 기판(106)으로 애칭된다.

<14> 반도체 디바이스내에서 애칭되는 피처의 임계 치수를 줄이기 위한 종래의 방법들에 따르면, 피처(110)의 임계 치수는 기판(106)내에서만 변경, 즉 감소된다. 이와 같이, 피처(110)의 임계 치수는 방사 감광성 이미지 층(102)과 반사방지 물질(104)의 애칭동안에는 변경되지 않는다. 반도체 디바이스(100)에는 흔히 있는 일이지만, 상기 두가지 층이 주로 유기물 종(species)을 포함한다면 방사 감광성 이미지 층(102)과 반사방지 물질(104)내의 피처(110)의 임계 치수의 감소는 실질적으로 불가능하다.

<15> 이하에서 설명되겠지만, 오직 기판의 애칭동안에만 감소될 수 있는 피처의 임계 치수의 총량은 제한된다. 기판과 같은 단일층내에서 피처의 임계 치수를 줄이려는 것은 상기 피처에 데미지를 주는 결과를 초래한다.

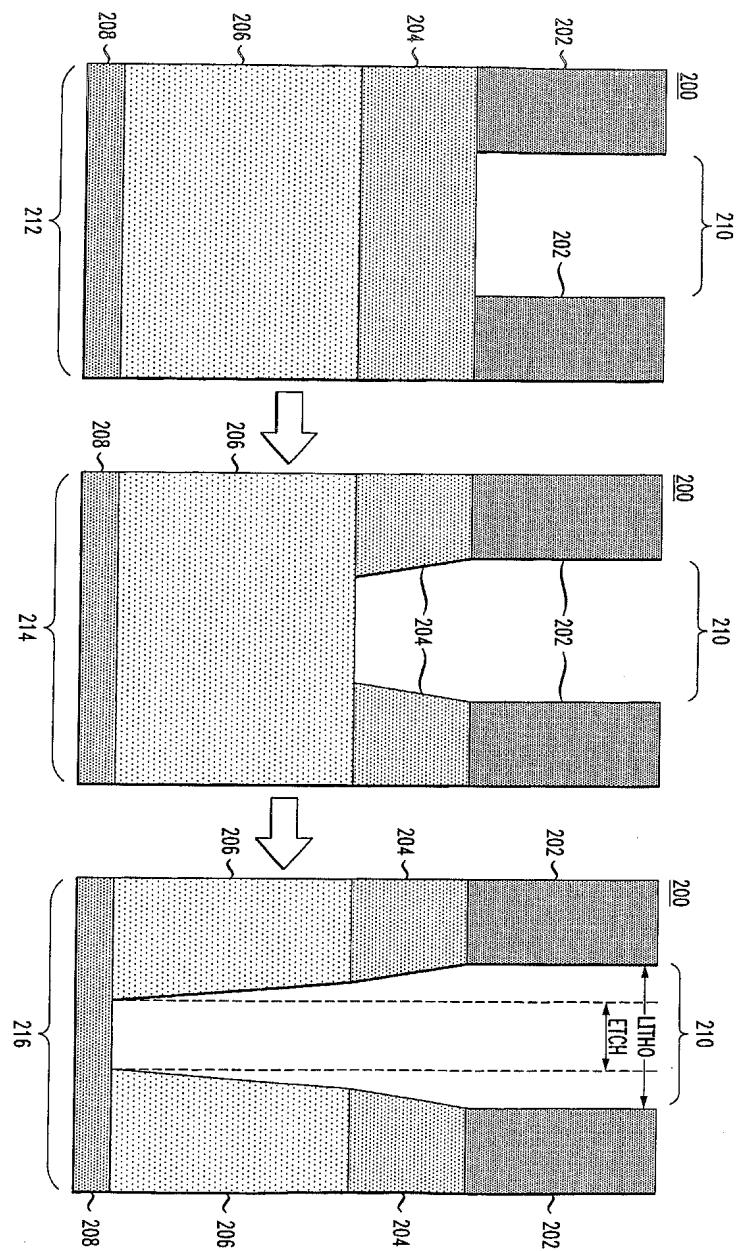

<16> 도 2는 반도체 디바이스의 피처의 임계 치수를 줄이기 위한 전형적인 기술을 나타내는 도면이다. 반도체 디바이스를 프로세싱할 때, 피처의 임계 치수는 이용되는 기술에 의해 얻어지는 피처의 특성 치수를 포함한다. 예를 들면, 피처가 컨택트 홀을 포함할 때, 이하에서 상세히 설명되겠지만, 상기 임계 치수는 생성된 컨택트 홀의 지름 값으로 표현될 수 있다.

<17> 또한, 피처의 임계 치수를 줄이기 위한 기술은 이하에서 상세히 설명될 피처의 임계 치수를 조정(tune)하는데 이용될 수 있다. 본 명세서에 사용되는 상기 용어 "조정"은 변경되는 임계 치수의 양을 제어하는 것과 관련된다.

<18> 도 2에 도시된 바와 같이, 반도체 디바이스(200)는 반사방지 물질(204)상에 증착되는 방사 감광성 이미지 층(202)을 포함한다. 기판(206)은 질화물 층(208)상에 증착된다. 피처(210)는 212, 214 그리고 216 단계들로 도시

되는 바와 같이 방사 감광성 이미지 층(202), 반사방지 물질(204) 그리고 기판(206)으로 예칭된다.

<19> 도 2의 212 단계에서, 피처(210)은 방사 감광성 이미지 층(202)으로 예칭된다. 방사 감광성 이미지 층(202)으로의 피처(210)의 예칭동안, 이하에서 상세히 설명되는 바와 같이, 피처(210)의 임계 치수는 변경되거나 또는 동일하게 유지될 수 있다. 예를 들면, 도 2의 212 단계에서 피처(210)의 임계 치수는 변경되지 않는다.

<20> 이하에서 더욱 상세히 설명하자면, 중간의 예칭 선택성의 바람직한 레벨을 얻기 위하여 방사 감광성 이미지 층(202)은 반사방지 물질(204)과 조성상에서 달라야 한다. 방사 감광성 이미지 층(202)은 스판 온 증착 및/또는 플라즈마 강화 화학적 기상 증착(PECVD)을 포함하는(단, 이것에 한정되는 것은 아님) 종래의 증착 기술을 이용하여 증착될 수 있다.

<21> 피처(210)는 리소그래피 기술에 의해 반도체 디바이스에 도입될 수 있는 임의의 구조물을 포함할 수 있다. 전형적인 구조물(단, 이것에 한정되는 것은 아님)은 컨택트 홀, 비아 패턴, 라인, 스페이스, 오벌(ovals) 및 이상의 피처들중 적어도 하나를 포함하는 조합들을 포함한다. 도 3 및 4의 설명과 함께 이하에서 상세히 설명되는 바와 같이, 전형적인 피처(210)는 컨택트 홀을 포함한다.

<22> 본 명세서에서 개시되는 바와 같이, 피처(210)의 임계 치수가 감소된다. 예를 들면, 피처(210)가 컨택트 홀을 포함할 때, 본 발명에 따른 기술이 컨택트 홀의 지름을 줄이는데 이용될 수 있다. 피처(210)가 라인과 스페이스를 포함할 때, 본 발명에 따른 기술은 라인간의 스페이싱을 줄이는데 이용될 수 있다.

<23> 도 2의 214 단계에서, 피처(210)는 기판(206)상에 증착되는 반사방지 물질(204)로 예칭된다. 반사방지 물질(204)은 하나 이상의 무기성 성분(inorganic moieties)을 포함한다.

<24> 전형적인 실시예에서, 반사방지 물질(204)은 M:C:H:X 구조식을 갖는다. 심볼 'M'은 실리콘(Si), 티타늄(Ti), 게르마늄(Ge), 철(Fe), 붕소(B), 주석(Sn) 및 이상의 금속 원소중 적어도 하나를 포함하는 조합을 포함하는(단, 이것에 한정되는 것은 아님) 금속 원소를 나타낸다. 심볼 'C'는 탄소 원소를 나타낸다. 심볼 'H'는 수소 원소를 나타낸다. 심볼 'X'는 산소(O), 수소, 질소(N) 및 이상의 무기 원소중 적어도 하나를 포함하는 조합들을 포함하는(단, 이것에 한정되는 것은 아님) 무기 원소를 나타낸다. 전형적인 실시예에서, 반사방지 물질(204)은 Si:C:H:O 구조식을 갖는다.

<25> 반사방지 물질(204)은 임의의 종래 증착 기술에 의해 기판(206)상에 증착될 수 있다. 전형적인 실시예에서, 반사방지 물질(204)은 스판 온 프로세싱에 의해 기판(206)상에 증착된다. 예를 들면, 반사방지 물질(204)이 실리콘을 포함할 때, 반사방지 물질(204)은 스판 온 프로세싱에 의해 기판(206)상에 증착될 수 있다. 또 다른 전형적인 실시예에서, 반사방지 물질(204)은 PECVD를 이용하여 기판(206)상에 증착될 수 있다. 예를 들면, 반사방지 물질은 Si, C, O 그리고 H를 포함하는 가변 내에칭성 반사방지(TERA) 코팅을 포함한다. 반사방지 물질(204)이 TERA 코팅을 포함할 때, 반사방지 물질(204)은 PECVD에 의해 기판(206)상에 증착될 수 있다. PECVD 필름은 공형이기 쉽다. 따라서, 반사방지 물질(204)은 공형적으로 증착된 물질을 포함할 수 있다. 공형적으로 증착되는 물질은 그것이 적용되는 표면의 외곽에 합치한다. 반사방지 물질(204)이 공형적으로 증착된 물질을 포함할 때, 반사방지 물질(204)은 전형적으로 PECVD를 이용하여 증착된다.

<26> 반사방지 물질(204)의 두께는 반사방지 물질의 조성에 따른다. 예를 들면, 반사방지 물질(204)이 실리콘을 포함하고, 스판 온 프로세싱을 이용하여 기판(206)상에 증착될 때 반사방지 물질(204)의 두께는 약 80나노미터와 동일하거나 이보다 클 수 있다. 전형적인 실시예에서, 기판(206)상에 증착되는 반사방지 물질(204)은 반사방지 특성을 최적화하기 위하여 스판 온 프로세싱을 이용하여 약 80 나노미터, 약 130 나노미터 또는 그보다 크거나 약 190 나노미터와 동일한 두께를 갖는다.

<27> 피처(210)의 임계 치수는 반사방지 물질(204)의 예칭동안 감소된다. 반사방지 물질(204)의 예칭동안 피처(210)의 임계 치수를 일부분 감소하는 것이 유리하며, 후속하는 예칭 단계(즉, 기판(206)의 예칭)중에만 피처(210)의 임계 치수를 완전히 줄이려고 하는 것(상기에서 설명한 도 1을 참조)은 피처에 데미지를 발생시킬 수 있다. 예를 들면, 기판의 예칭동안에만 피처의 임계 치수를 줄이려고 하는 것은 인접한 피처들간의 전기적 단락과 같은 바람직하지 못한 결과를 야기시키는 피처의 과도한 테이퍼링을 일으킬 수 있다.

<28> 반사방지 물질(204)의 예칭동안 피처(210)의 임계 치수를 줄이기 위하여, 프라즈마 예칭 기술이 이용될 수 있다. 플라즈마 예칭 기술은 플루오르카본 가스, 아르곤 가스, 산소 가스, 질소 가스 및 이상의 가스들중 적어도 하나를 포함하는 조합들(단, 이것에 한정되는 것은 아님)을 포함하는 가스들로 구성되는 플라즈마를 포함한다. 전형적인 실시예에서, 플라즈마 중합화 예칭 화학(이하에서는 "플라즈마 중합화 예칭"이라 한다)이 이용될

수 있다. 플라즈마 중합화 에칭은, 예를 들면 식각액(etchant) 및 중합체 종(species)으로서의 C<sub>4</sub>F<sub>6</sub>, C<sub>4</sub>F<sub>8</sub> 및/또는 CH<sub>3</sub>F, 플라즈마 상태를 변경시키는 중합화 반응 에이드(polymerization reaction aid)로서의 질소 가스, 중합화 반응 제어로서의 산소 가스, 중합화 및 증착의 과도한 양을 막기 위해 형성되는 플루오르폴리머의 일부를 제거하기 위해 필요한 아르곤 이온의 소스로서의 아르곤 가스와 같은 플루오르카본 가스중 적어도 하나를 포함한다.

<29> 본 명세서에서 기술하는 것에 따르는, 전형적인 플라즈마 중합화 에칭은 아르곤 가스 볼륨(volume) 약 300 파트(parts), 질소 가스 볼륨 약 150 파트, C<sub>4</sub>F<sub>8</sub> 가스 볼륨 약 5 파트, 산소 가스 볼륨 약 5 파트, CH<sub>3</sub>F 가스 볼륨 약 5 파트를 포함한다.

<30> 플라즈마 중합화 에칭은 에칭동안 피처(210)의 벽(wall)상에 중합체 물질을 일반적으로 층(layer)의 형식으로 증착한다(이하에서 "중합체 층"이라 한다). 증착되는 중합체 층의 전체 두께는 상기 플라즈마 중합화 식각액 종이 중합체 층을 통해 확산되고 반사방지 물질(204)을 에칭할 수 있도록 제어되어야 한다. 증착되는 중합체 층의 두께는 중합 물질의 조성과 특정 표면이 이온 충격(bombardment)을 필요로 하는지 여부에 따라 달라진다. 예를 들면, 피처(210)의 에칭동안, 방사 감광성 이미지 층(202)의 에칭동안 증착되는 중합체 층의 두께는 반사방지 물질(204)의 에칭동안 증착되는 중합체 층의 두께보다 더 크다. 전형적인 실시예에서, 방사 감광성 이미지 층(202)의 에칭동안 증착되는 중합체 층의 전체 두께는 가장 두꺼운 부분에서 약 4 나노미터에 이른다. 예를 들면, 방사 감광성 이미지 층(202)의 에칭동안 증착되는 중합체 층의 전체 두께는 가장 두꺼운 부분에서 약 1에서 약 3 나노미터 사이이다. 플라즈마 중합화 에칭은 반사방지 물질의 에칭동안 피처의 임계 치수를 약 80 나노미터까지 줄이기 위해 이용될 수 있다.

<31> 도 2의 214 단계에서, 증착된 중합체 층은 피처(210)의 벽이 점점 가늘어지도록 함으로써 피처(210)의 임계 치수를 감소시킨다. 그러나 피처(210)의 감소 또는 '초킹(choking)'은 증착된 중합체 층이 피처의 임계 치수를 줄이기만 하면 중합체 층이 점차적으로 테이퍼된 구조으로 형성될 것을 요구하지는 않는다.

<32> 도 2의 216 단계에서, 피처(210)는 기판(206)으로 에칭된다. 기판(206)은 질화물 층(208)상에 증착된다. 질화물 층(208)은 에칭 프로세스를 정지시키는 층으로서 역할을 한다. 질화물 층(208)은 실리콘 질화물(Si<sub>3</sub>N<sub>4</sub>)을 포함한다. 기판(206)은 플루오르실리케이트 글래스, 보로실리케이트 글래스, 보로포스포리스릴리케이트 글래스 및 이상의 산화물 물질중 적어도 하나를 포함하는 조합들을 포함하는 산화물 물질(단, 이것에 한정되는 것은 아님)을 포함하는 유전 물질을 포함할 수 있다. 기판(206)은 낮은-k 유전 물질을 더 포함할 수 있다. 적절한 낮은-k 유전 물질은 Novellus의 등록 상표인 CORAL, Dow Chemical의 등록 상표인 SiLK, Honeywell의 등록 상표인 FLARE 와 이상의 낮은-k 유전 물질중 적어도 하나를 포함하는 조합들을 포함한다(단, 이것에 한정되는 것은 아님).

<33> 기판(206)은 종래 증착 기술을 이용하여 질화물 층(208)상에 증착될 수 있다. 예를 들면, 기판(206)이 CORAL을 포함할 때, 기판(206)은 PECVD 증착될 수 있다. 또한, 기판(206)이 SiLK 및/또는 FLARE를 포함할 때, 기판(206)은 스펀 온 프로세싱을 이용하여 증착될 수 있다.

<34> 피처(210)의 임계 치수는 기판의 에칭동안 더 감소될 수 있다. 플라즈마 중합화 에칭은 또한 반사방지 물질(204)내의 피처(210)의 임계 치수를 줄이기 위해 사용된 것과 유사한 방식으로 기판(206)내의 피처(210)의 임계 치수를 줄이기 위해 이용될 수 있다. 용어 "Litho"와 수반되는 양측으로의 화살표는 리소그래피(lithography)중에 생성된 피처(210)의 임계 치수를 나타내는데 사용되고, 용어 "Etch"와 수반되는 양측으로의 화살표는 에칭 프로세스중에 생성된 피처(210)의 임계 치수를 나타내는데 사용된다.

<35> 전술한 바와 같이, 방사 감광성 이미지 층(202)은 2개의 층사이의 강화되는 에칭 선택성을 제공하기 위하여 반사방지 물질(204)과 조성상으로 다른 것이 바람직하다. 전형적인 실시예에서, 방사 감광성 이미지 층(202)은 유기 성분(organic moieties)을 포함한다. 즉, 방사 감광성 이미지 층(202)은 주로 C, H, O 와 일정 경우에는 플루오린(F)을 포함한다. 방사 감광성 이미지 층은 Si 원자와 같은 금속 원자는 전혀 포함하지 않는다.

<36> 전술한 바와 같이, 본 명세서에서 개시하는 기술은 피처의 임계 치수를 조정하는데 이용될 수 있다(예를 들면, 임계 치수 변경되는 양을 제어). 피처의 임계 치수를 조정하기 위한 한가지 전형적인 기술은 반사방지 물질내에 존재하는 무기 성분의 양을 변화시키는 것이다. 즉, 반사방지 물질의 무기 성분을 증가하면 임계 치수의 감소가 증가할 것이다. 예를 들면, 본 명세서에서 설명되는 반사방지 물질은 약 4 원자 퍼센트 Si 까지 포함할 수 있다. 그러나, Si의 양은 피처의 임계 치수의 감소를 더 크게 얻기 위하여 증가될 수도 있다. 전형적인 실시예에서, 반사방지 물질은 약 10 원자 퍼센트 Si 까지 포함한다. 또 다른 전형적인 실시예에서, 반사방지 물질은 약

20 원자 퍼센트 Si까지 포함한다.

- <37> 피처의 임계 치수를 줄이기 위한 또 다른 기술은 반사방지 물질을 에칭하는데 이용되는 플라즈마 중합화 에칭의 조성을 변경시키는 것이다. 전술한 바와 같이, 전형적인 플라즈마 중합화 에칭은 아르곤 가스 볼륨(volume) 약 300 파트(parts), 질소 가스 볼륨 약 150 파트, C<sub>4</sub>F<sub>8</sub> 가스 볼륨 약 5 파트, 산소 가스 볼륨 약 5 파트, CH<sub>3</sub>F 가스 볼륨 약 5 파트를 포함한다. 그 내부의 가스 비율을 변화시키기 위하여 조성이 변경될 수 있다. 피처의 임계 치수 감소의 증가를 얻기 위해, 예를 들면, C<sub>4</sub>F<sub>8</sub>의 양은 약 6 파트로 증가될 수 있고, 산소 가스의 양은 약 4 파트로 줄일 수 있다.

- <38> 플라즈마 중합화 에칭의 공급량(flow)이 또한 피처의 임계 치수를 조정하기 위해 변경될 수 있다. 즉, 질소 가스의 공급량은 일반적으로 플루오르카본과 산소 가스 공급량보다 훨씬 크다. 반면에 상기에서 강조된 플라즈마 중합화 에칭의 공급량은 분당 약 50 표준 큐빅 센티미터(sccm)이고, 질소 가스 성분을 변경시켜서 약 300 sccm 까지 증가시킬 수 있다.

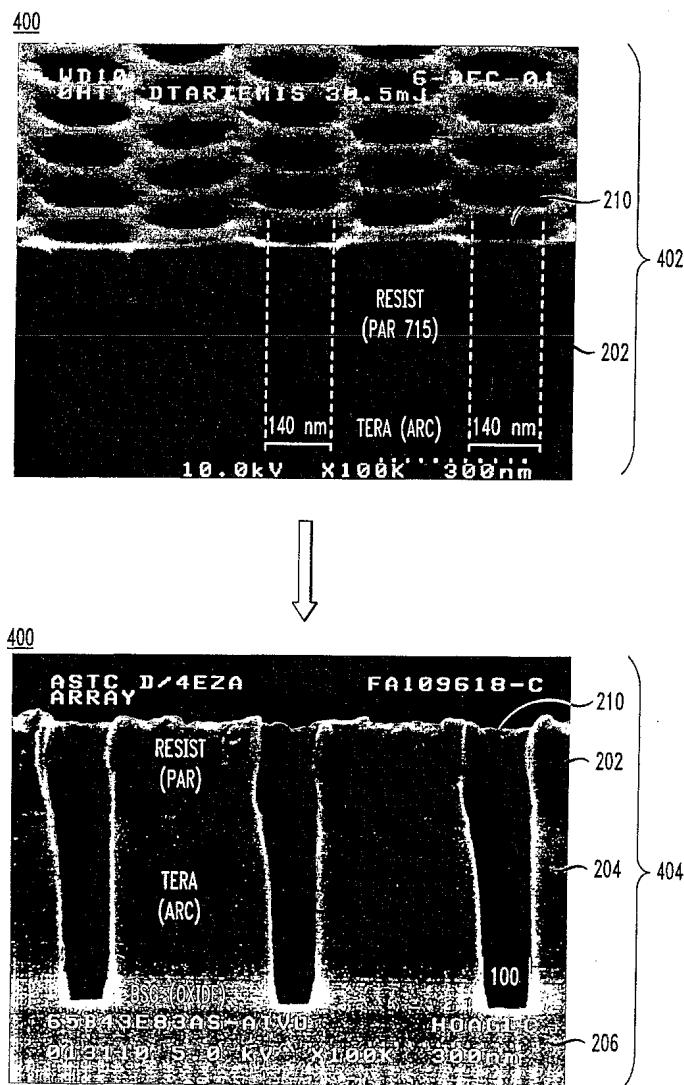

- <39> 도 3은 본 발명의 기술에 따른 반도체 디바이스내의 피처의 에칭을 나타낸다. 도 3에 도시된 바와 같이, 반도체 디바이스(300)는 반사방지 물질(204)상에 증착된 방사 감광성 이미지 층(202)을 포함한다. 피처(210)는 방사 감광성 이미지 층(202), 반사방지 물질(204) 및 기판(206)으로 에칭된다.

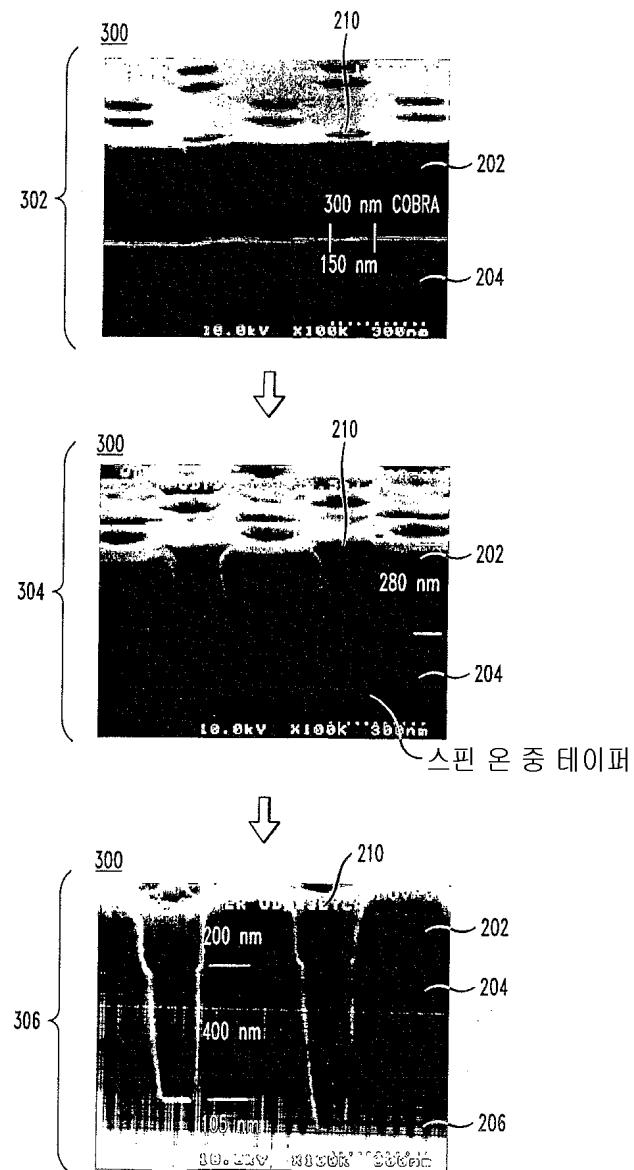

- <40> 특히, 도 3은 실리콘-함유 반사방지 물질을 이용한 컨택트 홀 피처의 진보적인 패터닝을 나타내는 이미지 집합이다. 도 3의 302 단계에서, 피처(210)(즉, 컨택트 홀)는 방사 감광성 이미지 층(202)으로 에칭된다. 피처(210)의 임계 치수는 방사 감광성 이미지 층(202)의 에칭동안에는 변경되지 않는다. 방사 감광성 이미지 층(202)은 반사방지 물질(204) 위에 형성된다.

- <41> 도 3의 304 단계에서, 피처(210)는 반사방지 물질로 더 에칭된다. 피처(210)의 임계 치수는 반사방지 물질(204)을 통해 테이퍼링됨에 의해 감소된다. 도 3의 306 단계에서, 피처(210)는 기판(206)으로 더 에칭된다. 피처(210)의 임계 치수는 기판(206)을 통해 테이퍼링됨에 의해 더 감소된다.

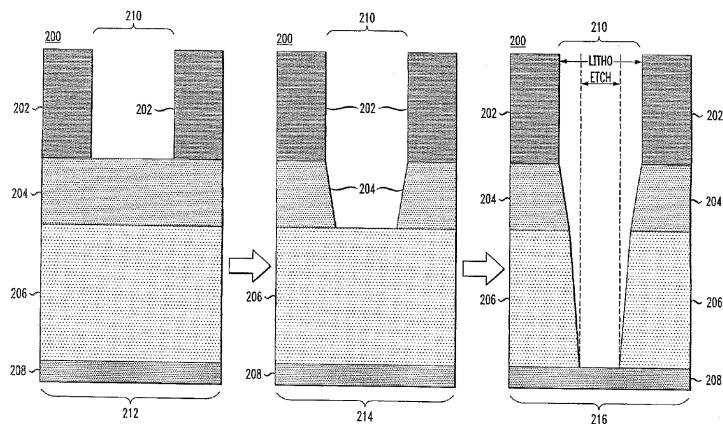

- <42> 이와 유사하게, 도 4는 본 발명의 기술에 따른 반도체 디바이스내의 피처의 에칭을 나타낸다. 도 4에 도시된 바와 같이, 반도체 디바이스(400)는 반사방지 물질(204)상에 증착된 방사 감광성 이미지 층(202)을 포함한다. 반사방지 물질(204)은 기판(206)상에 증착된다. 피처(210)는 방사 감광성 이미지 층(202), 반사방지 물질(204)과 기판(206)으로 에칭된다.

- <43> 특히, 도 4는 가변 내에칭성 반사방지(TERA) 물질을 이용하여 컨택트 홀 피처의 진보적인 패터닝을 나타내는 이미지의 집합이다. 도 4의 402단계에서, 피처(210)는 방사 감광성 이미지 층(202)으로 에칭된다. 피처(210)의 임계 치수는 방사 감광성 이미지 층(202)의 에칭동안에는 변경되지 않는다. 즉, 컨택트 홀의 지름은 방사 감광성 이미지 층 전체에 있어 약 140 나노미터로 유지된다. 도 4의 404 단계에서, 피처(210)는 반사방지 물질(204)과 기판(206)으로 더 에칭된다. 피처(210)의 임계 치수는 반사방지 물질(204)의 에칭 및 기판(206)의 에칭동안 약 40 나노미터로 감소된다.

- <44> 따라서, 본 발명에 따른 기술은 개선된 리소그래피 구조물 생성의 결과를 가져온다. 리소그래피 구조물은 기판, 상기 기판위의 반사방지 물질과 상기 반사방지 물질 위의 방사 감광성 이미지 층을 포함할 수 있다. 반사방지 물질은 그 안에 패터닝된 피처를 갖는다. 피처는 감소된 임계 치수를 갖는다. 또한, 기판은 그 안에 패터닝된 피처를 가질 수 있다. 상기 피처 또한 감소된 임계 치수를 가질 수 있다.

- <45> 본 명세서에서는 실시예를 설명하는 것에 의해 본 발명을 나타내었지만, 본 발명은 상기 실시예들에 한정되는 것은 아니며, 당업자라면 본 발명의 범위 및 의도를 벗어나지 않는 범위에서 다양한 변경과 변화가 있을 수 있다는 것을 이해할 수 있을 것이다.

### 도면의 간단한 설명

- <9> 도 1은 종래의 기술을 이용하여 감소된 임계 치수를 갖는 피처가 있는 반도체 디바이스를 나타내는 도면이다.

- <10> 도 2는 본 발명의 일실시예에 따라 반도체 디바이스의 피처의 임계 치수를 줄이기 위한 전형적인 기술을 나타내는 도면이다.

- <11> 도 3은 본 발명의 일실시예에 따라 실리콘-함유 반사방지 물질을 이용하여 컨택트 홀 피처의 진보적인 패터닝을 나타내는 이미지 집합이다.

<12> 도 4는 본 발명의 일실시예에 따라 가변 내에칭성 반사방지(tunable etch resistant antireflective : TERA) 물질을 이용하여 컨택트 홀 패처의 진보적 패터닝을 나타내는 이미지 집합이다.

## 도면

### 도면1

도면2

## 도면3

도면4