(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6019329号

(P6019329)

(45) 発行日 平成28年11月2日(2016.11.2)

(24) 登録日 平成28年10月14日(2016.10.14)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| G09F 9/30 (2006.01)   | G09F 9/30 338   |

| H01L 29/786 (2006.01) | H01L 29/78 618B |

| H01L 21/336 (2006.01) | H01L 29/78 612D |

| G02F 1/1368 (2006.01) | G02F 1/1368     |

| H01L 51/50 (2006.01)  | H05B 33/14 A    |

請求項の数 15 (全 26 頁)

(21) 出願番号 特願2011-78493 (P2011-78493)

(22) 出願日 平成23年3月31日 (2011.3.31)

(65) 公開番号 特開2012-212077 (P2012-212077A)

(43) 公開日 平成24年11月1日 (2012.11.1)

審査請求日 平成26年3月7日 (2014.3.7)

(73) 特許権者 514188173

株式会社 J O L E D

東京都千代田区神田錦町三丁目23番地

(74) 代理人 110001357

特許業務法人つばさ国際特許事務所

(72) 発明者 諸沢 成浩

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 諸園 信博

最終頁に続く

(54) 【発明の名称】表示装置および電子機器

## (57) 【特許請求の範囲】

## 【請求項1】

基板上に、

表示素子と、

前記表示素子の駆動素子としてのトランジスタと、

映像信号に対応した電荷を保持する保持容量素子とを備え、

前記保持容量素子は、前記基板側から順に、第1導電膜と、酸化物半導体よりなる第1半導体層と、絶縁膜と、第2導電膜とを有し、

前記第1半導体層は、前記保持容量素子の誘電体として機能すると共に、前記トランジスタに対応する領域から延在して設けられ、

前記第1導電膜と前記第2導電膜とはそれぞれ、前記保持容量素子の電極として機能すると共に、前記トランジスタとは分離した選択的な領域に設けられている

表示装置。

## 【請求項2】

前記トランジスタは、前記基板側から順に、

酸化物半導体よりなる第2半導体層と、

前記第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に配設されたゲート電極と、

前記第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層とを有する

請求項1に記載の表示装置。

10

20

**【請求項 3】**

前記第1導電膜は、前記基板上の選択的な領域に配設され、

前記第1半導体層および前記第2半導体層は、同一材料により前記基板上に一体的に設けられ、

前記絶縁膜は、前記ゲート絶縁膜と同一材料により構成され、かつ

前記第2導電膜は、前記ゲート電極と同一材料により構成されている

請求項2に記載の表示装置。

**【請求項 4】**

前記第1半導体層および前記第2半導体層は、前記保持容量素子および前記ゲート電極の両方に非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、

10

前記ソース・ドレイン電極層は、前記低抵抗領域に電気的に接続されている

請求項2に記載の表示装置。

**【請求項 5】**

前記保持容量素子と、前記ゲート電極と、前記第1半導体層および前記第2半導体層の前記低抵抗領域とを覆って高抵抗膜が設けられている

請求項4に記載の表示装置。

**【請求項 6】**

前記表示素子として有機電界発光素子を有する

請求項1に記載の表示装置。

**【請求項 7】**

前記表示素子として液晶表示素子を有する

20

請求項1に記載の表示装置。

**【請求項 8】**

基板上に、

表示素子と、

前記表示素子の駆動素子としてのトランジスタと、

映像信号に対応した電荷を保持する保持容量素子と

を備え、

前記保持容量素子は、前記基板側から順に、酸化物半導体よりなる第1半導体層と、第

1導電膜と、絶縁膜と、第2導電膜とを有し、

30

前記トランジスタは、前記基板側から順に、

酸化物半導体よりなる第2半導体層と、

前記第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に配設されたゲート電極と、

前記第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層と

を有し、

前記第1半導体層および前記第2半導体層は、前記保持容量素子および前記ゲート電極のそれぞれに非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、

前記ソース・ドレイン電極層は、前記低抵抗領域に電気的に接続され、かつ

前記第1導電膜と前記第2導電膜とはそれぞれ、前記保持容量素子の電極として機能すると共に、前記トランジスタとは分離した選択的な領域に設けられている

40

表示装置。

**【請求項 9】**

前記第1半導体層および前記第2半導体層は、同一材料により前記基板上に一体的に設けられ、

前記絶縁膜と前記ゲート絶縁膜とが同一材料により構成され、かつ

前記第2導電膜と前記ゲート電極とが同一材料により構成されている

請求項8に記載の表示装置。

**【請求項 10】**

前記第1導電膜は、前記第1半導体層上の選択的な領域に設けられると共に、アルミニ

50

ウム(Al), モリブデン(Mo), チタン(Ti)のうちの1種よりなる単層膜または2種以上を積層した積層膜よりなり、

前記第1半導体層および前記第2半導体層は、酸化インジウムスズ亜鉛(ITZO), 酸化インジウム亜鉛(IZO), 酸化インジウムガリウム(IGO), 酸化インジウムガリウム亜鉛(IGZO)のうちのいずれかよりなる

請求項8に記載の表示装置。

**【請求項11】**

前記保持容量素子と、前記ゲート電極と、前記第1半導体層および前記第2半導体層の前記低抵抗領域とを覆って高抵抗膜が設けられている

請求項8に記載の表示装置。

10

**【請求項12】**

前記表示素子として有機電界発光素子を有する

請求項8に記載の表示装置。

**【請求項13】**

前記表示素子として液晶表示素子を有する

請求項8に記載の表示装置。

**【請求項14】**

基板上に、

表示素子と、

前記表示素子の駆動素子としてのトランジスタと、

20

映像信号に対応した電荷を保持する保持容量素子とを備え、

前記保持容量素子は、前記基板側から順に、第1導電膜と、酸化物半導体よりなる第1半導体層と、絶縁膜と、第2導電膜とを有し、

前記第1半導体層は、前記保持容量素子の誘電体として機能すると共に、前記トランジスタに対応する領域から延在して設けられ、

前記第1導電膜と前記第2導電膜とはそれぞれ、前記保持容量素子の電極として機能すると共に、前記トランジスタとは分離した選択的な領域に設けられている

表示装置を備えた電子機器。

**【請求項15】**

基板上に、

30

表示素子と、

前記表示素子の駆動素子としてのトランジスタと、

映像信号に対応した電荷を保持する保持容量素子と

を備え、

前記保持容量素子は、前記基板側から順に、酸化物半導体よりなる第1半導体層と、第1導電膜と、絶縁膜と、第2導電膜とを有し、

前記トランジスタは、前記基板側から順に、

酸化物半導体よりなる第2半導体層と、

前記第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、

前記ゲート絶縁膜上に配設されたゲート電極と、

40

前記第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層と

を有し、

前記第1半導体層および前記第2半導体層は、前記保持容量素子および前記ゲート電極のそれぞれに非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、

前記ソース・ドレイン電極層は、前記低抵抗領域に電気的に接続され、かつ

前記第1導電膜と前記第2導電膜とはそれぞれ、前記保持容量素子の電極として機能すると共に、前記トランジスタとは分離した選択的な領域に設けられている

表示装置を備えた電子機器。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本開示は、有機EL(Electroluminescence)表示装置および液晶表示装置に好適な表示装置およびこれを備えた電子機器に関する。

**【背景技術】****【0002】**

アクティブ駆動方式の液晶表示装置または有機EL表示装置では、薄膜トランジスタを駆動素子として用いると共に、映像を書き込むための信号電圧に対応する電荷を保持容量に保持させている。しかし、薄膜トランジスタのゲート電極とソース電極またはドレイン電極との交差領域に生じる寄生容量が大きくなると、信号電圧が変動してしまい、画質の劣化を引き起こす場合がある。

10

**【0003】**

特に有機EL表示装置では、寄生容量が大きい場合には保持容量も大きくする必要があり、画素のレイアウトにおいて配線等の占める割合が大きくなる。その結果、配線間のショート等の確率が増加し、製造歩留まりが低下してしまう。

**【0004】**

そこで、従来では、例えば酸化亜鉛(ZnO)または酸化インジウムガリウム亜鉛(IGZO)等の酸化物半導体をチャネルに用いた薄膜トランジスタについて、ゲート電極とソース電極またはドレイン電極との交差領域に形成される寄生容量を低減する試みがなされている。

20

**【0005】**

例えば特許文献1および非特許文献1では、酸化物半導体薄膜層のチャネル領域上に、ゲート電極およびゲート絶縁膜を同一形状に形成したのち、酸化物半導体薄膜層のゲート電極およびゲート絶縁膜に覆われていない領域を低抵抗化してソース・ドレイン領域を形成するセルファアライン(自己整合)トップゲート薄膜トランジスタが記載されている。また、非特許文献2には、ゲート電極をマスクとした裏面露光により酸化物半導体膜にソース領域およびドレイン領域を形成するセルファアライン構造のボトムゲート薄膜トランジスタが記載されている。

**【先行技術文献】****【特許文献】****【0006】**

30

**【特許文献1】特開2007-220817号公報****【非特許文献】****【0007】**

**【非特許文献1】**J.Park、外11名，“Self-aligned top-gate amorphous gallium indium zinc oxide thin film transistors”，Applied Physics Letters，American Institute of Physics，2008年，第93巻，053501

**【非特許文献2】**R. Hayashi、外6名，“Improved Amorphous In-Ga-Zn-O TFTs”，SID DIGEST，2008年，42.1，p. 621-624

**【発明の概要】****【発明が解決しようとする課題】**

40

**【0008】**

上記のような酸化物半導体を利用したトランジスタと共に基板上に設けられる保持容量素子において、所望の容量を保持して画質劣化を抑制することが望まれている。

**【0009】**

本開示はかかる問題点に鑑みてなされたもので、その目的は、画質劣化を抑制することが可能な表示装置および電子機器を提供することにある。

**【課題を解決するための手段】****【0010】**

本開示の第1の表示装置は、基板上に、表示素子と、表示素子の駆動素子としてのトランジスタと、映像信号に対応した電荷を保持する保持容量素子とを備えたものである。保

50

持容量素子は、基板側から順に、第1導電膜と、酸化物半導体よりなる第1半導体層と、絶縁膜と、第2導電膜とを有し、第1半導体層は、保持容量素子の誘電体として機能すると共に、トランジスタに対応する領域から延在して設けられ、第1導電膜と第2導電膜とはそれぞれ、保持容量素子の電極として機能すると共に、トランジスタとは分離した選択的な領域に設けられている。

#### 【0011】

本開示の第1の表示装置では、基板上に表示素子、トランジスタと共に設けられた保持容量素子が、第1導電膜および第2導電膜間に、酸化物半導体よりなる第1半導体層と絶縁膜とを挟み込んでなる積層構造により形成される。これにより、保持容量素子では、印加電圧に依存する容量変動が抑制される。

10

#### 【0012】

本開示の第2の表示装置は、基板上に、表示素子と、表示素子の駆動素子としてのトランジスタと、映像信号に対応した電荷を保持する保持容量素子とを備えたものである。保持容量素子は、基板側から順に、酸化物半導体よりなる第1半導体層と、第1導電膜と、絶縁膜と、第2導電膜とを有している。トランジスタは、基板側から順に、酸化物半導体よりなる第2半導体層と、第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、ゲート絶縁膜上に配設されたゲート電極と、第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層とを有する。第1半導体層および第2半導体層は、保持容量素子およびゲート電極のそれぞれに非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、ソース・ドレイン電極層は、低抵抗領域に電気的に接続され、かつ第1導電膜と第2導電膜とはそれぞれ、保持容量素子の電極として機能すると共に、トランジスタとは分離した選択的な領域に設けられている。

20

#### 【0013】

本開示の第2の表示装置では、基板上に表示素子、トランジスタと共に設けられた保持容量素子が、第1導電膜および第2導電膜間に絶縁膜を挟み込んでなる積層構造により形成される。これにより、保持容量素子では、印加電圧に依存する容量変動が抑制される。

#### 【0014】

本開示の第1の電子機器は、上記本開示の第1の表示装置を備えたものである。

#### 【0015】

本開示の第2の電子機器は、上記本開示の第2の表示装置を備えたものである。

30

#### 【発明の効果】

#### 【0016】

本開示の第1の表示装置および電子機器によれば、基板上に表示素子、トランジスタと共に設けられた保持容量素子が、第1導電膜および第2導電膜間に、酸化物半導体よりなる第1半導体層と絶縁膜とを挟み込んでなる積層構造により形成される。これにより、保持容量素子において、印加電圧に依存する容量変動を抑制し、所望の容量を保持することができるようになる。よって、画質劣化を抑制することが可能となる。

#### 【0017】

本開示の第2の表示装置および電子機器によれば、基板上に表示素子、トランジスタと共に設けられた保持容量素子が、第1導電膜および第2導電膜間に、絶縁膜を挟み込んでなる積層構造により形成される。これにより、保持容量素子において、印加電圧に依存する容量変動を抑制し、所望の容量を保持することができるようになる。よって、画質劣化を抑制することが可能となる。

40

#### 【図面の簡単な説明】

#### 【0018】

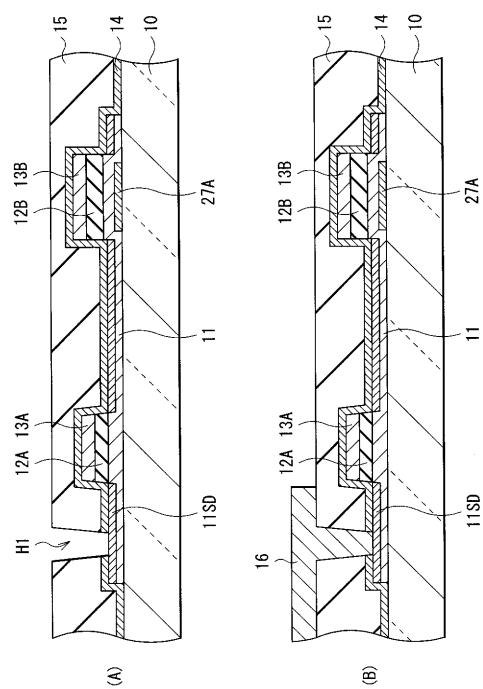

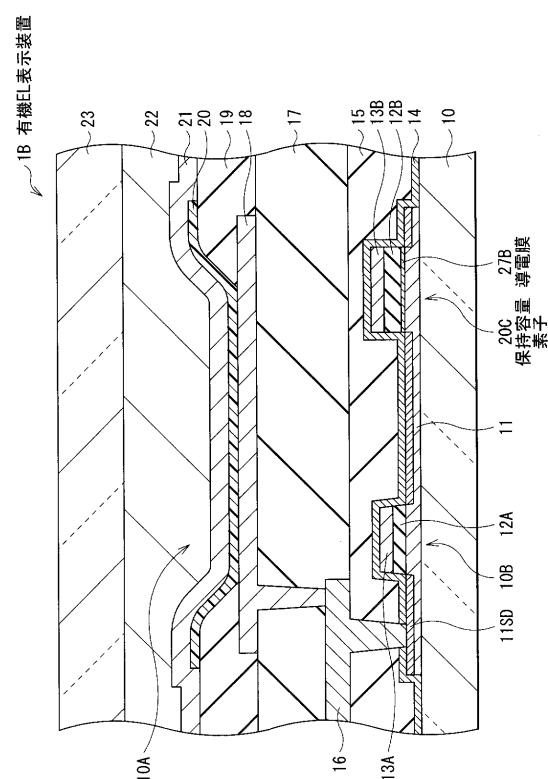

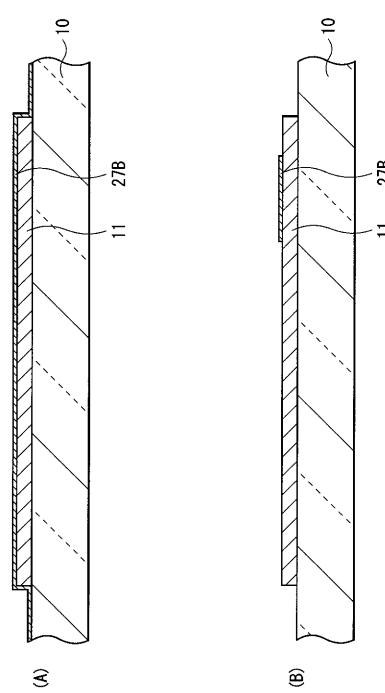

【図1】本開示の第1の実施の形態に係る有機EL表示装置の断面構造を表すものである。

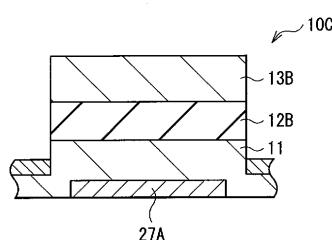

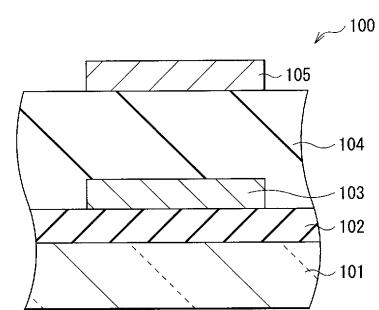

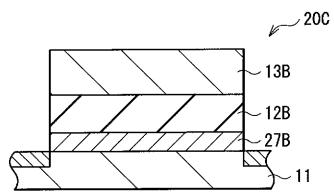

【図2】図1に示した保持容量素子の断面構造を拡大したものである。

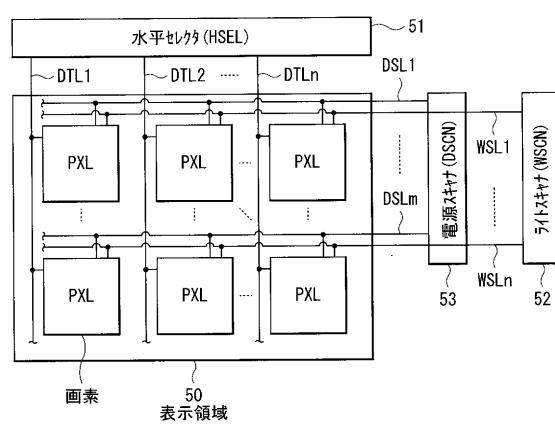

【図3】図1に示した有機EL表示装置の周辺回路を含む全体構成を表す図である。

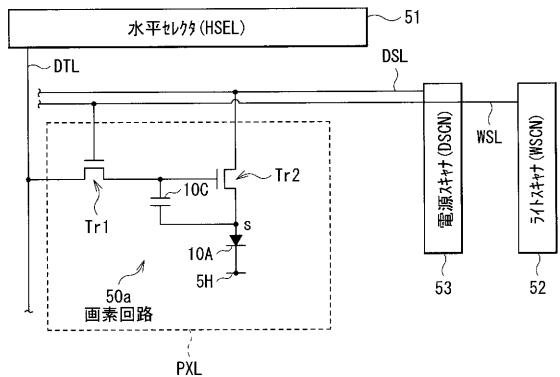

【図4】図3に示した画素の回路構成を表す図である。

50

【図5】図1に示した有機EL表示装置の製造方法を工程順に表す図である。

【図6】図5に続く工程を表す図である。

【図7】図6に続く工程を表す図である。

【図8】図7に続く工程を表す図である。

【図9】図8に続く工程を表す図である。

【図10】比較例1に係る保持容量素子の断面構造を表す模式図である。

【図11】比較例2に係る保持容量素子の断面構造を表す模式図である。

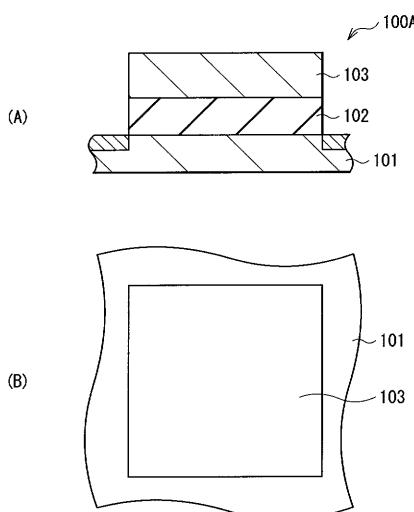

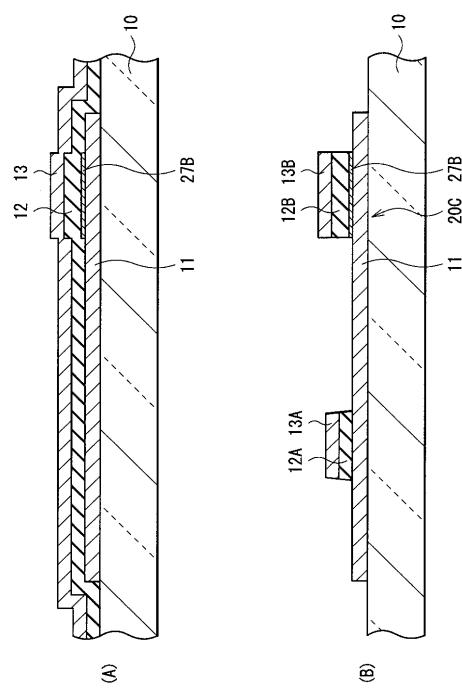

【図12】本開示の第2の実施の形態に係る有機EL表示装置の断面構造を表すものである。

【図13】図12に示した保持容量素子の断面構造を拡大したものである。 10

【図14】図12に示した有機EL表示装置の製造方法を説明するための図である。

【図15】図12に続く工程を表す図である。

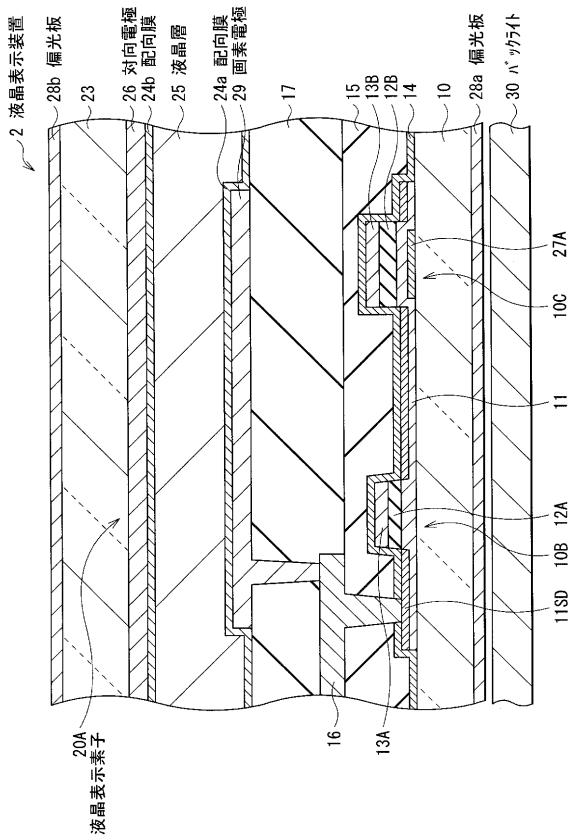

【図16】変形例に係る液晶表示装置の断面構造を表すものである。

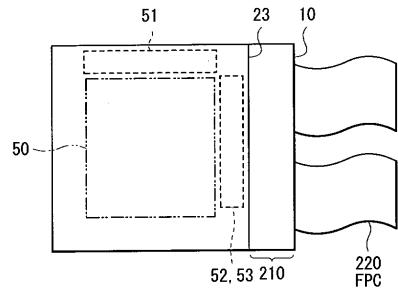

【図17】表示装置を含むモジュールの概略構成を表す平面図である。

【図18】適用例1の外観を表す斜視図である。

【図19】(A)は適用例2の表側から見た外観を表す斜視図であり、(B)は裏側から見た外観を表す斜視図である。

【図20】適用例3の外観を表す斜視図である。

【図21】適用例4の外観を表す斜視図である。

【図22】(A)は適用例5の開いた状態の正面図、(B)はその側面図、(C)は閉じた状態の正面図、(D)は左側面図、(E)は右側面図、(F)は上面図、(G)は下面図である。 20

#### 【発明を実施するための形態】

##### 【0019】

以下、本開示の実施の形態について図面を参照して詳細に説明する。尚、説明は以下の順序で行う。

1. 第1の実施の形態（一对の導電膜間に酸化物半導体層とゲート絶縁膜とが挟持されてなる（酸化物半導体層よりも下層に導電膜を有する）保持容量素子を備えた有機EL表示装置の例）

2. 第2の実施の形態（一对の導電膜間にゲート絶縁膜が挟持されてなる（酸化物半導体層よりも上層に導電膜を有する）保持容量素子を備えた有機EL表示装置の例） 30

3. 変形例（液晶表示装置の例）

4. 適用例（モジュール、電子機器の例）

##### 【0020】

#### <第1の実施の形態>

##### [構成]

図1は、本開示の第1の実施の形態に係る表示装置（有機EL表示装置1A）の断面構造を表すものである。有機EL表示装置1Aは、例えばアクティブマトリクス駆動方式によって駆動される複数の画素（有機EL素子10A）を有している。但し、図1には、1画素（サブピクセル）に対応する領域のみを示している。この有機EL表示装置1Aでは、駆動側基板10上に、例えばトランジスタ10Bおよび保持容量素子10Cが配設されており、これらの上層に有機EL素子10Aが形成されている。有機EL素子10Aは、例えば保護層22によって封止されており、この保護層22上に図示しない接着層を介して封止用基板23が貼り合わせられている。この有機EL表示装置1Aの発光方式は、いわゆるトップエミッション方式（上面発光方式）であってもよいし、ボトムエミッション方式（下面発光方式）であってもよい。以下、有機EL素子10A、トランジスタ10Bおよび保持容量素子10Cの具体的な構成について説明する。 40

##### 【0021】

##### (有機EL素子10A)

有機EL素子10Aでは、第1電極18上に、画素毎に開口を有する画素分離膜19が

50

設けられており、この画素分離膜 19 の開口部分に、有機層 20 が形成されている。この有機層 20 上に、第 2 電極 21 が設けられている。

#### 【0022】

第 1 電極 18 は、例えばアノードとして機能するものであり、画素毎に設けられている。第 1 電極 18 は、ボトムエミッション方式の場合には、透明導電膜、例えば酸化インジウム錫 (ITO)、酸化インジウム亜鉛 (IZO)、インジウム亜鉛オキシド (InZnO) 等のうちのいずれかよりなる単層膜またはそれらのうちの 2 種以上からなる積層膜により構成されている。この第 1 電極 18 は、トップエミッション方式の場合には、例えば、アルミニウム (Al)、マグネシウム (Mg)、カルシウム (Ca) およびナトリウム (Na) のうちの少なくとも 1 種からなる単体金属、またはこれらのうちの少なくとも 1 種を含む合金よりなる単層膜、あるいはこれらのうちの 2 種以上を積層した多層膜からなる。10

#### 【0023】

画素分離膜 19 は、各画素の発光領域を区画分離するためのものであり、例えばポリイミド、アクリル樹脂またはノボラック系樹脂などの感光性樹脂により構成されている。

#### 【0024】

有機層 20 は、有機電界発光層 (有機 EL 層) を含むものであり、駆動電流の印加によって発光を生じるものである。有機層 20 は、駆動側基板 10 の側から順に、例えば正孔注入層、正孔輸送層、有機 EL 層および電子輸送層 (いずれも図示せず) 等を積層したものである。有機 EL 層は、電界をかけることにより電子と正孔との再結合が起こり、光を発生するものである。この有機 EL 層の構成材料は、一般的な低分子または高分子有機材料であればよく、特に限定されない。また、例えば赤、緑、青の各色の発光層が画素毎に塗り分けられていてもよいし、白色発光層 (例えば赤、緑、青の各色発光層を積層したもの) が基板全面にわたって設けられていてもよい。正孔注入層は、正孔注入効率を高めると共に、リークを防止するために設けられる。正孔輸送層は、有機 EL 層への正孔輸送効率を高めるためのものである。これらの有機 EL 層以外の層は必要に応じて設けられていればよい。20

#### 【0025】

第 2 電極 21 は、例えばカソードとして機能するものであり、金属導電膜により構成されている。この第 2 電極 21 は、ボトムエミッション方式の場合には、反射性を有する金属膜、例えば、アルミニウム、マグネシウム、カルシウムおよびナトリウムのうちの少なくとも 1 種からなる単体金属、またはこれらのうちの少なくとも 1 種を含む合金よりなる単層膜、あるいはこれらのうちの 2 種以上を積層した多層膜からなる。あるいは、トップエミッション方式の場合には、ITO や IZO などの透明導電膜が用いられる。この第 2 電極 21 は、第 1 電極 18 と絶縁された状態で有機層 20 上に形成され、各画素に共通して設けられている。30

#### 【0026】

保護層 22 は、絶縁性材料または導電性材料のいずれにより構成されていてもよい。絶縁性材料としては、例えばアモルファスシリコン (a-Si)、アモルファス炭化シリコン (a-SiC)、アモルファス窒化シリコン (a-Si<sub>1-x</sub>N<sub>x</sub>)、アモルファスカーボン (a-C) 等が挙げられる。40

#### 【0027】

駆動側基板 10 および封止用基板 23 は、例えば、石英、ガラス、シリコンまたはプラスチックなどの板材である。後述のスパッタ法において、駆動側基板 10 を加熱することなく半導体層 11 を成膜するため、安価なプラスチックフィルムを用いることができる。プラスチック材料としては、例えば PET (ポリエチレンテレフタレート)、PEN (ポリエチレンナフタレート) などが挙げられる。この他にも、目的に応じて、ステンレス鋼 (SUS) などの金属基板が用いられてもよい。但し、トップエミッション方式の場合、封止用基板 23 は、ガラスやプラスチックなどの透明基板により構成され、また図示しないカラーフィルタや遮光膜などを有していてもよい。ボトムエミッション方式の場合には50

、駆動側基板 10 が透明基板により構成される。

**【0028】**

(トランジスタ 10B)

トランジスタ 10B は、例えば後述の画素駆動回路 50a におけるサンプリング用トランジスタ Tr1 または駆動トランジスタ 5B に相当するものであり、スタガ構造を有する（いわゆるトップゲート型の）薄膜トランジスタである。このトランジスタ 10B では、駆動側基板 10 上に、半導体層 11 が設けられ、この半導体層 11 上の選択的な領域にゲート絶縁膜 12A を介してゲート電極 13A が配設されている。これらの半導体層 11、ゲート絶縁膜 12A およびゲート電極 13A を覆って層間絶縁膜 15 が設けられている。層間絶縁膜 15 には、半導体層 11 に対向してコンタクトホール H1 が設けられており、この層間絶縁膜 15 上に、ソース・ドレイン電極層 16 がそのコンタクトホール H1 を埋め込むように配設されている。これにより、ソース・ドレイン電極層 16 が、半導体層 11 の所定の領域（後述のソース・ドレイン領域 11SD）に、電気的に接続されている。

10

**【0029】**

尚、本実施の形態では、半導体層 11 が、トランジスタ 10B から保持容量素子 10C に渡って形成されている。即ち、半導体層 11 のうち、トランジスタ 10B に対応する部分が「第2半導体層」、後述の保持容量素子 10C に対応する部分が「第1半導体層」に相当し、半導体層 11 は、これらの「第1半導体層」および「第2半導体層」が一体的に設けられた構成の一具体例に相当する。

20

**【0030】**

半導体層 11 は、ゲート電圧の印加によりチャネルを形成するものであり、例えばインジウム (In), ガリウム (Ga), 亜鉛 (Zn), シリコン (Si) およびスズ (Sn) のうちの少なくとも 1 種を含む酸化物半導体による。このような酸化物半導体としては、例えば、非晶質のものには、酸化インジウムスズ亜鉛 (ITZO), 酸化インジウムガリウム亜鉛 (IGZO, InGaZnO) が挙げられる。結晶質の酸化物半導体としては、酸化亜鉛 (ZnO), 酸化インジウム亜鉛 (IZO), 酸化インジウムガリウム (IGO), ITO, 酸化インジウム (InO) 等が挙げられる。この半導体層 11 では、ゲート電極 13A に対向する領域（チャネル領域 11A）に隣接して、ソース・ドレイン電極層 16 との接続領域となるソース・ドレイン領域 11SD が形成されている。この半導体層 11 の厚みは、例えば 50nm 程度である。尚、この半導体層 11 のうち、ゲート電極 13A および保持容量素子 10C に非対向な領域における上面側の一部は他の領域よりも低い電気抵抗率を有する低抵抗領域となっている。

30

**【0031】**

ソース・ドレイン領域 11SD は、上面から深さ方向における一部に設けられ、チャネル領域 11A に比べ、電気抵抗の低い低抵抗領域となっている。このソース・ドレイン領域 11SD は、例えば、後述の製造工程において、アルミニウム等の金属を反応させることにより、酸化物半導体中に拡散させて低抵抗化されている。これにより、トランジスタ 10B は、いわゆるセルファーライン（自己整合）構造を有すると共に特性を安定させることができ可能となっている。

40

**【0032】**

ゲート絶縁膜 12A は、例えばシリコン酸化膜 ( $\text{SiO}_x$ )、シリコン窒化膜 ( $\text{SiN}_x$ )、シリコン窒化酸化膜 ( $\text{SiON}$ ) および酸化アルミニウム膜 ( $\text{AlO}_x$ ) のうちの 1 種よりなる単層膜、またはそれらのうちの 2 種以上よりなる積層膜である。これらのうち、シリコン酸化膜または酸化アルミニウム膜は、酸化物半導体を還元させにくいので好みしい。このゲート絶縁膜 12A の厚みは、例えば 300nm 程度である。尚、本実施の形態では、後述するように、このゲート絶縁膜 12A と、保持容量素子 10C における絶縁膜 12B とが、同一工程において同一材料を用いて形成されるため、ゲート絶縁膜 12A の厚みと絶縁膜 12B の厚みは略等くなっている。保持容量素子 10C における容量（静電容量、キャパシタンス）は、絶縁膜 12B の厚みに依存するため、これを考慮してゲート絶縁膜 12A の厚みが設定される。

50

## 【0033】

ゲート電極13Aは、トランジスタ10Bに印加されるゲート電圧( $V_g$ )によって半導体層11中のキャリア密度を制御すると共に、電位を供給する配線としての機能を有するものである。このゲート電極13Aは、例えばモリブデン(Mo)、チタン(Ti)、アルミニウム、銀、ネオジウム(Nd)および銅(Cu)のうちの1種からなる単体もしくは合金、もしくはこれらのうちの2種以上からなる積層膜である。具体的には、アルミニウムや銀などの低抵抗金属をモリブデンまたはチタンにより挟み込んだ積層構造や、アルミニウムとネオジウムとの合金(AlNd合金)が挙げられる。このゲート電極13Aは、あるいはITO等の透明導電膜から構成されていてもよい。このゲート電極13Aの厚みは、例えば10nm～500nmである。

10

## 【0034】

層間絶縁膜15は、例えば、厚みが2μm程度であり、例えばシリコン酸化膜、シリコン窒化膜、シリコン窒化酸化膜および酸化アルミニウム膜のうちの1種よりなる単層膜、またはそれらのうちの2種以上よりなる積層膜である。この層間絶縁膜15としては、また、アクリル樹脂やポリイミド等の有機絶縁膜が用いられてもよい。特に、シリコン酸化膜および酸化アルミニウム膜の積層膜を用いることにより、半導体層11への水分の介入や拡散を抑え、トランジスタ10Bの電気的特性や信頼性を高めることが可能となる。

## 【0035】

ソース・ドレイン電極層16は、トランジスタ10Bのソース電極またはドレイン電極として機能するものである。このソース・ドレイン電極層16は、例えば、厚みが200nm程度であり、上記ゲート電極13Aにおいて列挙したものと同様の金属または透明導電膜により構成されている。このソース・ドレイン電極層16は、例えば、アルミニウムまたは銅などの低抵抗金属により構成されていることが好ましく、このような低抵抗金属を、チタンまたはモリブデンよりなるバリア層により挟み込んでなる積層膜であることがより好ましい。このような積層膜を用いることにより、配線遅延の少ない駆動が可能となる。また、ソース・ドレイン電極層16は、ゲート電極13Aの直上の領域を回避して設けられていることが望ましい。ゲート電極13Aとソース・ドレイン電極層16との交差領域に寄生容量が形成されることを防ぐためである。

20

## 【0036】

これらの層間絶縁膜15およびソース・ドレイン電極層16を覆って、平坦化膜17が設けられている。平坦化膜17は、例えばポリイミドまたはアクリル系樹脂よりなり、表示領域の全面に渡って形成されている。但し、この平坦化膜17には、トランジスタ10Bのソース・ドレイン電極層16と、有機EL素子10Aの第1電極18との電気的接続を確保するためのコンタクトホールH2が設けられている。第1電極18は、このコンタクトホールH2を埋め込むように、平坦化膜17上に配設されている。

30

## 【0037】

## (保持容量素子10C)

保持容量素子10Cは、例えば後述の画素駆動回路50aにおいて、映像信号に対応する電荷を保持する容量素子である。図2に、保持容量素子10Cの断面構造を拡大したものを示す。保持容量素子10Cは、トランジスタ10Bの半導体層11の一部を利用した積層構造により容量形成がなされるものである。具体的には、保持容量素子10Cは、駆動側基板10側から順に、導電膜27A、半導体層11、絶縁膜12Bおよび導電膜13Bを積層した構造を有している。本実施の形態では、半導体層11よりも下層(駆動側基板10の側)に、導電膜27Aが設けられている。この保持容量素子10Cでは、半導体層11が、トランジスタ10Bから延在して(一体的に)設けられており、導電膜27A、絶縁膜12Bおよび導電膜13Bについては、トランジスタ10Bから分離された選択的な領域に設けられている。

40

## 【0038】

尚、この保持容量素子10Cにおける導電膜27Aが、本開示の第1の表示装置における「第1導電膜」、導電膜13Bが「第2導電膜」の一具体例である。

50

## 【0039】

絶縁膜12Bは、例えばトランジスタ10Bのゲート絶縁膜12Aと同一材料からなり、互いに同一の工程においてそれぞれ形成することができる。導電膜13Bについても同様で、例えばゲート電極13Aと同一材料からなり、互いに同一の工程においてそれぞれ形成可能である。

## 【0040】

導電膜27Aは、例えばチタン、アルミニウムおよびモリブデンのうちの1種よりなる単層膜またはそれらのうちの2種以上を積層した積層膜により構成されており、厚みが例えば50nm程度である。詳細は後述するが、本実施の形態では、この導電膜27Aが、半導体層11よりも前の工程において形成されるようになっている。

10

## 【0041】

## (高抵抗膜14)

上記のような保持容量素子10Cと、トランジスタ10Bのゲート絶縁膜12Aおよびゲート電極13Aと、半導体層11上のゲート電極13Aおよび保持容量素子10Cにそれぞれ非対向な領域(低抵抗領域)を覆って、高抵抗膜14が形成されている。但し、高抵抗膜14のうち、ソース・ドレイン電極層16に対向する部分は選択的に除去されている。

## 【0042】

高抵抗膜14は、後述する製造工程において半導体層11の低抵抗領域(例えばソース・ドレイン領域11SD)に拡散される金属の供給源となる金属膜が、酸化膜となって残存したものである。このような高抵抗膜14は、例えば、酸化チタン、酸化アルミニウム、酸化インジウムまたは酸化スズ等により構成されている。この高抵抗膜14は、外気に対して良好なバリア性を有しているため、上記のようなプロセス上の役割の他、トランジスタ10Bにおける半導体層11の電気的特性を変化させる酸素や水分の影響を低減する機能をも有している。高抵抗膜14を設けることにより、トランジスタ10Bおよび保持容量素子10Cの電気特性を安定化させることが可能となり、層間絶縁膜15の効果をより高めることが可能となる。この高抵抗膜14の厚みは、例えば20nm以下である。

20

## 【0043】

## (周辺回路および画素回路の構成)

次に、上記のような有機EL表示装置1Aの周辺回路および画素回路の構成について説明する。図3は、有機EL表示装置1Aの周辺回路を含む全体構成を表すものである。このように、例えば駆動側基板10上には、有機EL素子10Aを含む複数の画素PXLがマトリクス状に配置されてなる表示領域50が形成され、この表示領域50の周辺に、信号線駆動回路としての水平セレクタ(HSEL)51と、走査線駆動回路としてのライトスキャナ(WSCN)52と、電源線駆動回路としての電源スキャナ(DSCN)53などが設けられている。

30

## 【0044】

表示領域50において、列方向には複数(整数n個)の信号線DTL1～DTLnが配置され、行方向には、複数(整数m個)の走査線WSL1～WSLmおよび電源線DSL1～DSLmがそれぞれ配置されている。また、各信号線DTLと各走査線WSLとの交差点に、各画素PXL C(R、G、Bに対応する画素のいずれか1つ)が設けられている。各信号線DTLは水平セレクタ51に接続され、この水平セレクタ51から各信号線DTLへ映像信号が供給されるようになっている。各走査線WSLはライトスキャナ52に接続され、このライトスキャナ52から各走査線WSLへ走査信号(選択パルス)が供給されるようになっている。各電源線DSLは電源スキャナ53に接続され、この電源スキャナ53から各電源線DSLへ電源信号(制御パルス)が供給されるようになっている。

40

## 【0045】

図4は、画素PXL Cにおける具体的な回路構成例を表したものである。各画素PXL Cは、有機EL素子10Aを含む画素回路50aを有している。この画素回路50aは、サンプリング用トランジスタTr1および駆動用トランジスタTr2と、保持容量素子1

50

0 C と、有機 E L 素子 1 0 A とを有するアクティプ型の駆動回路である。尚、サンプリング用トランジスタ Tr 1 ( または駆動用トランジスタ Tr 2 ) が、上記実施の形態等のトランジスタ 1 0 B に相当する。

#### 【 0 0 4 6 】

サンプリング用トランジスタ Tr 1 は、そのゲートが対応する走査線 W S L に接続され、そのソースおよびドレインのうちの一方が対応する信号線 D T L に接続され、他方が駆動用トランジスタ Tr 2 のゲートに接続されている。駆動用トランジスタ Tr 2 は、そのドレインが対応する電源線 D S L に接続され、ソースが有機 E L 素子 1 0 A のアノードに接続されている。また、この有機 E L 素子 1 0 A のカソードは、接地配線 5 H に接続されている。なお、この接地配線 5 H は、全ての画素 P X L C に対して共通に配線されている。10

#### 【 0 0 4 7 】

サンプリング用トランジスタ Tr 1 は、走査線 W S L から供給される走査信号 ( 選択パルス ) に応じて導通することにより、信号線 D T L から供給される映像信号の信号電位をサンプリングし、保持容量素子 1 0 C に保持するものである。駆動用トランジスタ Tr 2 は、所定の第 1 電位 ( 図示せず ) に設定された電源線 D S L から電流の供給を受け、保持容量素子 1 0 C に保持された信号電位に応じて、駆動電流を有機 E L 素子 1 0 A へ供給するものである。有機 E L 素子 1 0 A は、この駆動用トランジスタ Tr 2 から供給された駆動電流により、映像信号の信号電位に応じた輝度で発光するようになっている。20

#### 【 0 0 4 8 】

このような回路構成では、走査線 W S L から供給される走査信号 ( 選択パルス ) に応じてサンプリング用トランジスタ Tr 1 が導通することにより、信号線 D T L から供給された映像信号の信号電位がサンプリングされ、保持容量素子 1 0 C に保持される。また、上記第 1 電位に設定された電源線 D S L から駆動用トランジスタ Tr 2 へ電流が供給され、保持容量素子 1 0 C に保持された信号電位に応じて、駆動電流が有機 E L 素子 1 0 A ( 赤色、緑色および青色の各有機 E L 素子 ) へ供給される。そして、各有機 E L 素子 1 0 A は、供給された駆動電流により、映像信号の信号電位に応じた輝度で発光する。これにより、表示装置において、映像信号に基づく映像表示がなされる。

#### 【 0 0 4 9 】

##### ( 製造方法 )

上記のような有機 E L 表示装置 1 A は、例えば次のようにして製造することができる。まず、駆動側基板 1 0 上に、トランジスタ 1 0 B および保持容量素子 1 0 C を形成する。

#### 【 0 0 5 0 】

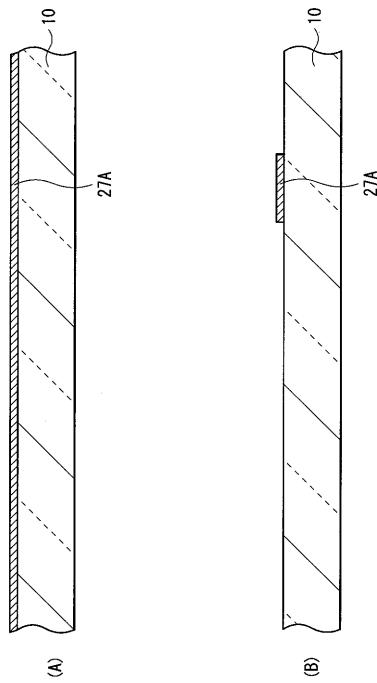

即ち、まず、図 5 ( A ) に示したように、駆動側基板 1 0 の全面に、例えばスパッタリング法により、上述した材料等よりなる導電膜 2 7 A を成膜する。この後、図 5 ( B ) に示したように、成膜した導電膜 2 7 A を、例えばフォトリソグラフィおよびエッチングによってパターニングし、駆動側基板 1 0 上の選択的な領域 ( 容量形成領域 ) に形成する。

#### 【 0 0 5 1 】

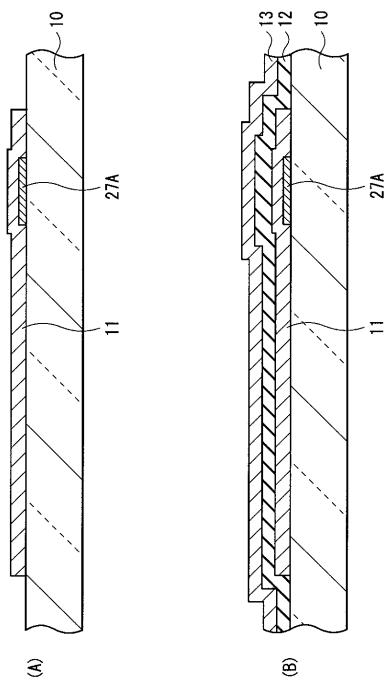

続いて、図 6 ( A ) に示したように、上述した酸化物半導体よりなる半導体層 1 1 を成膜する。具体的には、まず、駆動側基板 1 0 の全面に渡って導電膜 2 7 A を覆うように、例えばスパッタリング法により、半導体層 1 1 を成膜する。この際、ターゲットとしては、成膜対象の酸化物半導体と同一組成のセラミックを用いる。また、酸化物半導体中のキャリア濃度は、スパッタリングの際の酸素分圧に大きく依存するので、所望のトランジスタ特性が得られるように酸素分圧を制御する。この後、例えばフォトリソグラフィおよびエッチングにより、成膜した半導体層 1 1 を所定の形状にパターニングする。その際、リン酸と硝酸と酢酸との混合液を用いたウェットエッチングにより加工することが好ましい。リン酸、硝酸および酢酸の混合液は、下地との選択比を十分に大きくすることが可能であり、比較的容易に加工が可能となる。40

#### 【 0 0 5 2 】

10

20

30

40

50

続いて、図6(B)に示したように、駆動側基板10上の全面にわたって、例えばシリコン酸化膜よりなる絶縁膜12(ゲート絶縁膜12A, 絶縁膜12B)を、例えばプラズマCVD(Chemical Vapor Deposition; 化学気相成長)法により成膜する。シリコン酸化膜はプラズマCVD法のほか、反応性スパッタリング法により形成することも可能である。また、酸化アルミニウム膜を成膜する場合には、これらの反応性スパッタリング法、CVD法に加え、原子層成膜法を用いることも可能である。

#### 【0053】

その後、同じく図6(B)に示したように、絶縁膜12の全面に、例えばスパッタリング法により、例えばモリブデンまたはチタンとアルミニウムの積層膜よりなる導電膜13(ゲート電極13A, 導電膜13B)を成膜する。

10

#### 【0054】

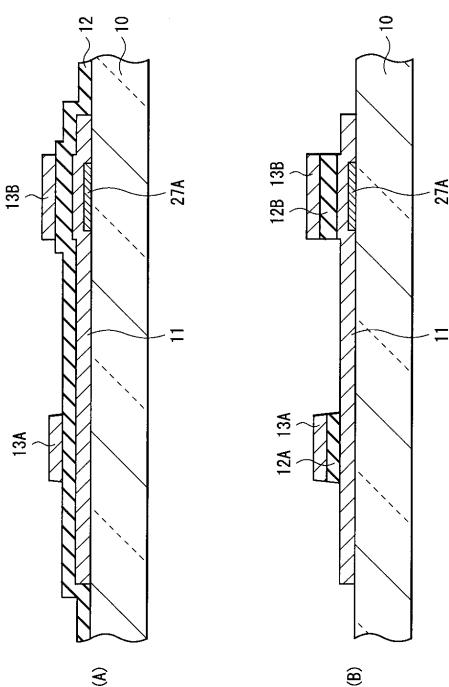

次いで、図7(A)に示したように、導電膜13を、例えばフォトリソグラフィおよびエッチングによりパターニングすることにより、半導体層11上の選択的な領域にゲート電極13Aおよび導電膜13Bをそれぞれ形成する。

#### 【0055】

この後、図7(B)に示したように、形成したゲート電極13Aおよび導電膜13Bをマスクとして絶縁膜12をエッチングする。この際、半導体層11をZnO, IZO, IGZO等の結晶性材料により構成した場合には、フッ酸等を用いて非常に大きなエッチング選択比を維持するようにすると、容易に加工することが可能となる。これにより、ゲート絶縁膜12Aがゲート電極13Aと略同一形状にパターニングされると共に、導電膜27A上に、絶縁膜12Bおよび導電膜13Bが形成される。このようにして、駆動側基板10上の選択的な領域に、導電膜27A、半導体層11、絶縁膜12Bおよび導電膜13Bの積層構造よりなる保持容量素子10Cを形成する。

20

#### 【0056】

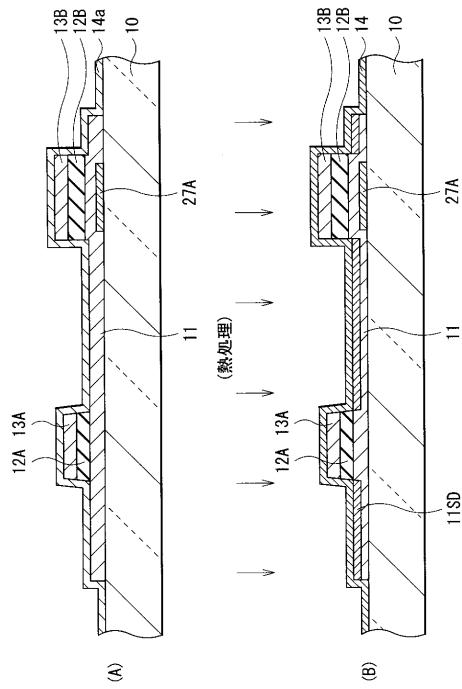

続いて、図8(A)に示したように、駆動側基板10上の全面に渡って、例えばスパッタリング法により、例えばチタン、アルミニウムまたはインジウム等の酸素と比較的低温で反応する金属よりなる金属膜14aを、例えば5nm以上10nm以下の厚みで成膜する。

#### 【0057】

この後、図8(B)に示したように、例えば300程度の温度で熱処理を行うことにより、金属膜14aが酸化され、これによって金属酸化膜からなる高抵抗膜14が形成される。この際、ゲート電極13Aおよび保持容量素子10Cに非対向な領域には、低抵抗領域(ソース・ドレイン領域11SDを含む)が形成される。この金属膜14aの酸化反応には、酸化物半導体に含まれる酸素の一部が利用されるため、金属膜14aの酸化の進行に伴って、半導体層11では、その金属膜14aと接する面側から酸素濃度が低下していく。一方、金属膜14aから、アルミニウム等の金属が半導体層11中に拡散する。この金属元素がドーパントとして機能し、金属膜14aと接する半導体層11の上面側の領域が低抵抗化される。これにより、電気抵抗の低いソース・ドレイン領域11SDが形成される。

30

#### 【0058】

尚、金属膜14aの熱処理としては、例えば300程度の温度でアニールすることが好みしい。その際、酸素等を含む酸化性のガス雰囲気でアニールを行うことで、上記低抵抗領域の酸素濃度が低くなりすぎるのを抑え、半導体層11に十分な酸素を供給することが可能となる。よって、後工程で行うアニール工程を削減することが可能となり、工程の簡略化が可能となる。

40

#### 【0059】

あるいは、次のようにして高抵抗膜14を形成してもよい。例えば、図8(A)に示した工程において、駆動側基板10の温度を200程度の比較的高い温度に保持して、金属膜14aを成膜するようにしてもよい。これにより、図8(B)に示した熱処理を行わずに、半導体層11の所定の領域を低抵抗化することが可能である。この場合には、半導

50

体層 11 のキャリア濃度をトランジスタとして必要なレベルに低減することが可能である。

#### 【 0 0 6 0 】

また、この金属膜 14a は、例えば 10 nm 以下の厚みで成膜することが好ましい。金属膜 14a の厚みを 10 nm 以下とすれば、熱処理によって金属膜 14a を完全に酸化させる（高抵抗膜 14 を形成する）ことができるからである。尚、金属膜 14a が完全に酸化されていない場合には、この未酸化の金属膜 14a をエッチングにより除去する工程が必要となる。金属膜 14a は、ゲート電極 13A 上などにも成膜されるため、十分に酸化されていないとリーク電流を生じさせる場合があるためである。金属膜 14a が完全に酸化され、高抵抗膜 14 が形成された場合には、そのような除去工程が不要であり、製造工程の簡略化が可能となる。つまり、エッチングによる除去工程を行わなくとも、リーク電流の発生を防止できる。尚、金属膜 14a を 10 nm 以下の厚みで成膜した場合、熱処理後の高抵抗膜 14 の厚みは、20 nm 以下程度となる。

10

#### 【 0 0 6 1 】

更に、金属膜 14a を酸化させる方法としては、上記のような熱処理のほか、水蒸気雰囲気での酸化、またはプラズマ酸化などの方法により酸化を促進させることも可能である。特にプラズマ酸化の場合、次のような利点がある。即ち、高抵抗膜 14 の形成後、層間絶縁膜 15 をプラズマ CVD 法により形成するが、金属膜 14a に対してプラズマ酸化処理を施した後、続けて（連続的に）、層間絶縁膜 15 を成膜可能である。このため、特に工程を増やす必要がないという利点がある。プラズマ酸化では、例えば、駆動側基板 10 の温度を 200 ~ 400 度にして、酸素および二窒化酸素の混合ガス等の酸素を含むガス雰囲気中でプラズマを発生させて処理することが望ましい。これにより、上述したような外気に対して良好なバリア性を有する高抵抗膜 14 を形成することができるからである。

20

#### 【 0 0 6 2 】

加えて、半導体層 11 の所定の領域を低抵抗化させる手法としては、上記のような金属膜 14a と半導体層 11 との反応による手法の他にも、プラズマ処理によって低抵抗化する手法、プラズマ CVD 法によりシリコン窒化膜を成膜し、このシリコン酸化膜からの水素拡散等により低抵抗化させる手法などを用いてもよい。

#### 【 0 0 6 3 】

30

次に、図 9 (A) に示したように、層間絶縁膜 15 を形成する。具体的には、まず、高抵抗膜 14 上の全面に渡って、上述したアクリル樹脂などの有機膜あるいはシリコン酸化膜や酸化アルミニウム膜などの無機膜、もしくは、それらの有機膜と無機膜との積層膜よりなる層間絶縁膜 15 を上述した厚みにより成膜する。その際、シリコン酸化膜などの無機膜を成膜する場合には、例えばプラズマ CVD 法により形成し、酸化アルミニウム膜を成膜する場合には、アルミニウムをターゲットとした DC または AC 電源による反応性スピッタリング法により形成することが望ましい。高速に成膜することが可能となるからである。また、有機膜を成膜する場合には、例えばスピントロート法やスリットコート法を用いて塗布形成する。

#### 【 0 0 6 4 】

40

この後、例えばフォトリソグラフィおよびエッチングにより、半導体層 11 のソース・ドレイン領域 11SD に対向する領域の一部において層間絶縁膜 15 および高抵抗膜 14 を貫通するコンタクトホール H1 を形成する。

#### 【 0 0 6 5 】

続いて、図 9 (B) に示したように、上述した材料等よりなるソース・ドレイン電極層 16 を、層間絶縁膜 15 上に、コンタクトホール H1 を埋め込むように、例えばスピッタリング法により成膜した後、フォトリソグラフィおよびエッチングにより所定の形状にパターニングする。これにより、ソース・ドレイン電極層 16 が、半導体層 11 のソース・ドレイン領域 11SD に電気的に接続されて形成される。上記のようにして、駆動側基板 10 上に、トランジスタ 10B および保持容量素子 10C を形成する。

50

## 【0066】

この後、層間絶縁膜15およびソース・ドレイン電極層16を覆うように、上述した材料よりなる平坦化膜17を、例えばスピンコート法やスリットコート法により成膜し、ソース・ドレイン電極層16に対向する領域の一部にコンタクトホールH2を形成する。

## 【0067】

続いて、この平坦化膜17上に、有機EL素子10Aを形成する。具体的には、平坦化膜17上に、そのコンタクトホールH2を埋め込むように、上述した材料よりなる第1電極18を例えばスパッタリング法により成膜した後、フォトリソグラフィおよびエッチングによりパターニングする。この後、第1電極18上に開口を有する画素分離膜19を形成した後、有機層20を例えば真空蒸着法により成膜する。続いて、有機層20上に、上述した材料よりなる第2電極21を例えばスパッタリング法により形成する。次いで、この第2電極21上に保護層22を例えばCVD法により成膜した後、この保護層22上に、封止用基板23を貼り合わせる。以上により、図1に示した有機EL表示装置1Aを完成する。

## 【0068】

## [作用、効果]

本実施の形態の有機EL表示装置1Aでは、例えばR,G,Bのいずれかに対応する各画素に、各色の映像信号に応じた駆動電流が印加されると、第1電極18および第2電極21を通じて、有機層20に電子および正孔が注入される。これらの電子および正孔は、有機層20に含まれる有機EL層においてそれぞれ再結合され、発光を生じる。このようにして、有機EL表示装置1Aでは、例えばR,G,Bのフルカラーの映像表示がなされる。

## 【0069】

この有機EL表示装置1Aでは、上記のような映像表示動作の際に、保持容量素子10Cの一端に、映像信号に対応する電位が印加されることにより、保持容量素子10Cには、映像信号に対応する電荷が蓄積される。本実施の形態では、上述のように、保持容量素子10Cが、導電膜27Aおよび導電膜13B間に、酸化物半導体よりなる半導体層11と絶縁膜12Bとを挟み込んだ積層構造を有する。

## 【0070】

ここで、図10に、本実施の形態の比較例(比較例1)に係る保持容量素子100の積層構造について示す。比較例1では、例えば駆動側基板101上に、トランジスタのゲート絶縁膜の一部を利用して絶縁膜102が設けられ、この絶縁膜102上(トランジスタのゲート電極と同層)に、導電膜103が配設されている。導電膜103上には、厚みの大きな層間絶縁膜104が設けられ、この層間絶縁膜104上のソースドレイン電極層と同層には、導電膜105が形成されている。このように、比較例1では、トランジスタのゲート電極およびソース・ドレイン電極とそれぞれ同層に設けられた導電膜103,105間に、層間絶縁膜104を挟み込んだ構造となっている。このような積層構造によっても、容量形成が可能である。ところが、このような保持容量素子100では、層間絶縁膜104の厚みが比較的大きい(マイクロオーダーである)ため、容量が小さくなり、寄生容量の影響を受け易くなる。

## 【0071】

一方、本実施の形態では、上記のように、保持容量素子10Cが、導電膜27Aおよび導電膜13B間に半導体層11および絶縁膜12Bを挟んだ積層構造により形成される。これにより、半導体層11および絶縁膜12B(ゲート絶縁膜12A)の厚みの総和は、層間絶縁膜15よりも小さくなることから、本実施の形態の保持容量素子10Cでは、上記比較例1に比べ大きな容量を確保することができる。

## 【0072】

また、ここで、図11に、本実施の形態の比較例(比較例2)に係る保持容量素子100Aの積層構造について示す。保持容量素子100Aでは、半導体層101上に、ゲート絶縁膜を利用した絶縁膜102を介して導電膜103が設けられており、このような積層

10

20

30

40

50

構造によって容量が形成されている。このような保持容量素子 100A では、本実施の形態と同様、比較的大きな容量を確保することができるが、半導体層 101 および導電膜 103 間に印加される電圧によって、容量が変動し易い。容量変動が生じると、画素回路の駆動条件によっては十分な容量を用いることができないことから、画質劣化を引き起こすことがある。

#### 【0073】

これに対し、本実施の形態の保持容量素子 10C は、半導体層 11 よりも下層に導電膜 27A を配設し、この導電膜 27A と、ゲート電極 13A を利用して設けられた導電膜 13B との間に、半導体層 11 と絶縁膜 12B とを挟み込んだ構造となっている。保持容量素子 10C へ供給される電圧は、半導体層 11 ではなく、導電膜 27A, 13B 間において保持されることから、上記のような印加電圧による容量変動が緩和される。10

#### 【0074】

以上説明したように、本実施の形態では、駆動側基板 10 上に有機 EL 素子 10A およびトランジスタ 10B と共に設けられた保持容量素子 10C が、導電膜 27A と、導電膜 13B (ゲート電極 13A と同一材料) との間に、酸化物半導体よりなる半導体層 11 と絶縁膜 12B (ゲート絶縁膜 12A と同一材料) とを挟んでなる積層構造を有する。これにより、保持容量素子 10C において、印加電圧に依存する容量変動を抑制し、所望の容量を保持することができるようになる。よって、画質劣化を抑制することが可能となる。

#### 【0075】

また、これにより、アクティブ駆動方式のディスプレイにおいて高品質な画像を表示することが可能となり、大画面化、高精細化、ハイフレームレート化に対応することが可能になる。更に、容量を比較的大きく確保可能であるため、画素レイアウトにおいても、配線の占有割合を低減でき、欠陥の少ない高歩留まりのパネルを製造することが可能となる。20

#### 【0076】

##### <第 2 の実施の形態>

図 12 は、本開示の第 2 の実施の形態に係る表示装置（有機 EL 表示装置 1B）の断面構造を表すものである。有機 EL 表示装置 1B は、上記第 1 の実施の形態の有機 EL 表示装置 1A と同様、例えばアクティブマトリクス駆動方式によって駆動される複数の画素（有機 EL 素子 10A）と、これを表示駆動するためのトランジスタ 10B および保持容量素子 20C とを有している。また、有機 EL 素子 10A は、保護層 22 および封止用基板 23 により封止されており、トランジスタ 10B は、酸化物半導体よりなる半導体層 11 を備えたトップゲート型の薄膜トランジスタである。尚、上記第 1 の実施の形態と同様の構成要素については同一の符号を付し適宜その説明を省略する。30

#### 【0077】

##### [構成]

保持容量素子 20C は、上記第 1 の実施の形態の保持容量素子 10C と同様、前述の画素駆動回路 50a において、映像信号に対応する電荷を保持する容量素子である。図 13 に、保持容量素子 20C の断面構造を拡大したものを示す。このように、保持容量素子 20C は、トランジスタ 10B における積層構造の一部を利用して設けられるものであるが、上記第 1 の実施の形態の保持容量素子 10C とは、その積層構造が異なっている。具体的には、保持容量素子 20C では、駆動側基板 10 の側から順に、半導体層 11、導電膜 27B、絶縁膜 12B および導電膜 13B が積層されており、半導体層 11 よりも上層（絶縁膜 12B の側）に、導電膜 27B が設けられている。即ち、保持容量素子 20C では、半導体層 11 上の選択的な領域に、導電膜 27B、絶縁膜 12B および導電膜 13B がこの順に形成されており、導電膜 27B, 13B 間に絶縁膜 12B が挟み込まれた積層構造によって、容量形成がなされるようになっている。40

#### 【0078】

尚、この保持容量素子 20C における導電膜 27B が、本開示の第 2 の表示装置における「第 1 導電膜」、導電膜 13B が「第 2 導電膜」の一具体例である。50

## 【0079】

このような構成においても、絶縁膜12Bは、例えばトランジスタ10Bのゲート絶縁膜12Aと同一材料からなり、互いに同一の工程においてそれぞれ形成することができる。また、導電膜13Bは、例えばゲート電極13Aと同一材料からなり、互いに同一の工程においてそれぞれ形成可能である。

## 【0080】

導電膜27Bは、例えばチタン、アルミニウムおよびモリブデンのうちの1種よりなる単層膜またはそれらのうちの2種以上を積層した積層膜により構成されており、厚みが例えば50nm程度である。本実施の形態では、この導電膜27Bは、半導体層11よりも後の工程において形成されるようになっている。

10

## 【0081】

上記のような有機EL表示装置1Bは、例えば次のようにして製造することができる。即ち、まず、駆動側基板10上に、トランジスタ10Bおよび保持容量素子20Cをそれぞれ形成する。具体的には、まず、図14(A)に示したように、駆動側基板10上に、半導体層11を、例えばスパッタリング法により成膜後、フォトリソグラフィ等により所定の形状にパターニングする。この後、駆動側基板10上の全面に渡って、例えばスパッタリング法により、上述した材料等よりなる導電膜27Bを成膜する。

## 【0082】

続いて、図14(B)に示したように、フォトリソグラフィおよびエッチングにより導電膜27Bをパターニングし、半導体層11上の選択的な領域に形成する。ここで、エッチングの際には、導電膜27Bおよび半導体層11のうちの導電膜27Bのみを選択的に除去する必要がある。例えば、導電膜27Bを、りん硝酢酸の薬液でウェットエッチングする場合には、半導体層11として、結晶質の酸化インジウムガリウム(IGO)や酸化インジウム亜鉛(IZO)等を用いるか、非晶質の酸化インジウムスズ亜鉛(ITZO)を用いることが望ましい。また、半導体層11として酸化インジウムガリウム亜鉛(IGZO)を用いる場合には、導電膜27Bをドライエッチングで加工することで半導体層11との間でエッチング選択性を確保することができる。尚、りん硝酢酸によりエッチング可能な導電膜27Bとしてはチタン、モリブデン、アルミニウム等が挙げられる。

20

## 【0083】

この後、図15(A)に示したように、駆動側基板10上の全面にわたって、例えばシリコン酸化膜や酸化アルミニウム等よりなる絶縁膜12(ゲート絶縁膜12A, 絶縁膜12B)を、上記第1の実施の形態と同様の手法により成膜する。続いて、この絶縁膜12の全面に、上記第1の実施の形態と同様の手法により、導電膜13(ゲート電極13A, 導電膜13B)を成膜する。

30

## 【0084】

次いで、図15(B)に示したように、導電膜13を、上記第1の実施の形態と同様の手法によりパターニングした後(ゲート電極13A, 導電膜13Bを形成した後)、絶縁膜12をエッチングする。この際、上記第1の実施の形態と同様、半導体層11をZnO, IZO, IGO等の結晶性材料により構成した場合には、フッ酸等のエッチング溶液を用いることで、加工が容易となる。これにより、ゲート絶縁膜12Aがゲート電極13Aと略同一形状にパターニングされると共に、導電膜27B上に、絶縁膜12Bおよび導電膜13Bが形成される。このようにして、半導体層11上の選択的な領域に、導電膜27B、絶縁膜12Bおよび導電膜13Bの積層構造よりなる保持容量素子20Cを形成する。

40

## 【0085】

上記のようにして保持容量素子20Cを形成した後、上記第1の実施の形態と同様にして、駆動側基板10の全面にわたって金属膜14a(図示せず)を成膜し、例えば熱処理を施すことにより、高抵抗膜14を形成すると共に、半導体層11の上面側の所定の領域にソース・ドレイン領域11SDを形成する。この後、上記第1の実施の形態と同様にして、層間絶縁膜15およびソース・ドレイン電極層16を形成することにより、トランジ

50

スタ 1 0 B を形成する。このようにしてトランジスタ 1 0 B および保持容量素子 2 0 C が形成された駆動側基板 1 0 上に、上記第 1 の実施の形態と同様にして、平坦化膜 1 7 、有機 E L 素子 1 0 A および保護層 2 2 を形成し、最後に封止用基板 2 3 を貼り合わせる。これにより、図 1 2 に示した有機 E L 表示装置 1 B を完成する。

#### 【 0 0 8 6 】

##### [ 作用・効果 ]

本実施の形態の有機 E L 表示装置 1 B においても、上記第 1 の実施の形態の有機 E L 表示装置 1 A と同様、各色の映像信号に応じた駆動電流が、第 1 電極 1 8 および第 2 電極 2 1 を通じて印加されると、有機層 2 0 において発光を生じる。これにより、例えば R , G , B のフルカラーの映像表示がなされる。また、この際、保持容量素子 2 0 C の一端には、映像信号に対応する電位が印加され、電荷が蓄積される。この際、保持容量素子 2 0 C が、導電膜 2 7 B および導電膜 1 3 B 間に、比較的厚みの小さな絶縁膜 1 2 B を挟み込んだ積層構造を有することにより、比較的大きな容量を確保することができ、寄生容量の影響を軽減することができる。また、導電膜 2 7 B と、ゲート電極 1 3 A を利用して設けられた導電膜 1 3 B との間に、ゲート絶縁膜 1 2 A を利用して設けられた絶縁膜 1 2 B を挟み込んだ構造となっている。保持容量素子 2 0 C へ供給される電圧は、半導体層 1 1 ではなく、導電膜 2 7 B , 1 3 B 間において保持されることから、印加電圧による容量変動が緩和される。

10

#### 【 0 0 8 7 】

以上のように、本実施の形態では、駆動側基板 1 0 上に有機 E L 素子 1 0 A 、トランジスタ 1 0 B と共に設けられた保持容量素子 2 0 C が、導電膜 2 7 B と、導電膜 1 3 B ( ゲート電極 1 3 A と同一材料 ) との間に、絶縁膜 1 2 B ( ゲート絶縁膜 1 2 A と同一材料 ) とが挟み込まれた積層構造を有する。これにより、保持容量素子 2 0 C では、上記第 1 の実施の形態と同様、印加電圧に依存する容量変動を抑制し、所望の容量を保持することができるようになる。よって、上記第 1 の実施の形態と同等の効果を得ることができる。

20

#### 【 0 0 8 8 】

また、本実施の形態の保持容量素子 2 0 C では、導電膜 2 7 B が半導体層 1 1 よりも上層に設けられているため、上記第 1 の実施の形態の保持容量素子 1 0 C と異なり、導電膜 2 7 B , 1 3 B 間には絶縁膜 1 2 B のみが挟み込まれた積層構造となっている。このため、上記第 1 の実施の形態の保持容量素子 1 0 C よりも、より大きな容量を確保することができ、寄生容量の影響をより効果的に軽減可能である。

30

#### 【 0 0 8 9 】

##### < 变形例 >

次に、本開示の変形例に係る表示装置 ( 液晶表示装置 2 ) について説明する。図 1 6 は、液晶表示装置 2 の断面構造を表すものである。液晶表示装置 2 は、上記第 1 の実施の形態の有機 E L 表示装置 1 A と同様、駆動側基板 1 0 上に、表示素子と、トランジスタ 1 0 B と、保持容量素子 1 0 C とを有するものであるが、表示素子として、有機 E L 素子ではなく液晶表示素子 2 0 A を含んでいる。即ち、液晶表示装置 2 では、駆動側基板 1 0 上に、トランジスタ 1 0 B および保持容量素子 1 0 C が配設されており、これらの上層に液晶表示素子 2 0 A を有している。また、駆動側基板 1 0 の下方には、バックライト 3 0 が備えられており、駆動側基板 1 0 のバックライト 3 0 側および封止用基板 2 3 上には、偏光板 2 8 a , 2 8 b が貼り合わせられている。尚、上記実施の形態と同様の構成要素については、同一の符号を付し、適宜その説明を省略する。また、ここでは、上記第 1 の実施の形態で説明した保持容量素子 1 0 C を例に挙げて説明するが、上記第 2 の実施の形態で説明した保持容量素子 2 0 C を用いることも可能である。

40

#### 【 0 0 9 0 】

液晶表示素子 2 0 A は、例えば、画素電極 2 9 と対向電極 2 6 との間に液晶層 2 5 を封止したものであり、画素電極 2 9 および対向電極 2 6 の液晶層 2 5 側の各面には、配向膜 2 4 a , 2 4 b が形成されている。画素電極 2 9 は、画素毎に配設されており、例えばトランジスタ 1 0 B のソース・ドレイン電極層 1 6 に電気的に接続されている。対向電極 2

50

6は、複数の画素に共通の電極として設けられ、例えばコモン電位に保持されている。液晶層25は、例えばV A (Vertical Alignment: 垂直配向) モード, T N (Twisted Nematic) モードあるいはI P S (In Plane Switching) モード等により駆動される液晶により構成されている。

#### 【0091】

バックライト30は、液晶層25へ向けて光を照射する光源であり、例えばL E D (Light Emitting Diode) やC C F L (Cold Cathode Fluorescent Lamp) 等を複数含むものである。このバックライト30は、図示しないバックライト駆動部によって、点灯状態および消灯状態が制御されるようになっている。

#### 【0092】

偏光板28a, 28b(偏光子, 検光子)は、例えば互いにクロスニコルの状態で配置されており、これにより、例えばバックライト30からの照明光を電圧無印加状態(オフ状態)では遮断、電圧印加状態(オン状態)では透過させるようになっている。

#### 【0093】

このような液晶表示装置2では、上記第1実施の形態の有機E L表示装置1Aと同様、保持容量素子10Cが、導電膜27A, 13B間に、半導体層11および絶縁膜12Bを挟み込んでなる積層構造を有している。これにより、本変形例においても、保持容量素子10Cにおいて、比較的大きな容量が確保されると共に、その電圧依存性が緩和される。即ち、本開示の表示装置としては、上述のような有機E L表示装置1Aに限らず、液晶表示装置2にも適用可能である。

#### 【0094】

##### <適用例>

以下、上記のような表示装置(有機E L表示装置1A, 1B, 液晶表示装置2)の電子機器への適用例について説明する。電子機器としては、例えばテレビジョン装置、デジタルカメラ、ノート型パーソナルコンピュータ、携帯電話等の携帯端末装置あるいはビデオカメラ等が挙げられる。言い換えると、上記表示装置は、外部から入力された映像信号あるいは内部で生成した映像信号を、画像あるいは映像として表示するあらゆる分野の電子機器に適用することが可能である。

#### 【0095】

##### (モジュール)

上記表示装置は、例えば図17に示したようなモジュールとして、後述の適用例1~5などの種々の電子機器に組み込まれる。このモジュールは、例えば、駆動側基板10の一辺に、封止用基板23から露出した領域210を設け、この露出した領域210に、水平セレクタ51、ライトスキャナ52および電源スキャナ53の配線を延長して外部接続端子(図示せず)を形成したものである。この外部接続端子には、信号の入出力のためのフレキシブルプリント配線基板(F P C; Flexible Printed Circuit)220が設けられていてもよい。

#### 【0096】

##### (適用例1)

図18は、テレビジョン装置の外観を表したものである。このテレビジョン装置は、例えば、フロントパネル310およびフィルターガラス320を含む映像表示画面部300を有しており、この映像表示画面部300が上記表示装置に相当する。

#### 【0097】

##### (適用例2)

図19は、デジタルカメラの外観を表したものである。このデジタルカメラは、例えば、フラッシュ用の発光部410、表示部420、メニュー/スイッチ430およびシャッターボタン440を有しており、この表示部420が上記表示装置に相当する。

#### 【0098】

##### (適用例3)

図20は、ノート型パーソナルコンピュータの外観を表したものである。このノート型

10

20

30

40

50

パーソナルコンピュータは、例えば、本体 510，文字等の入力操作のためのキーボード 520 および画像を表示する表示部 530 を有しており、この表示部 530 が上記表示装置に相当する。

**【0099】**

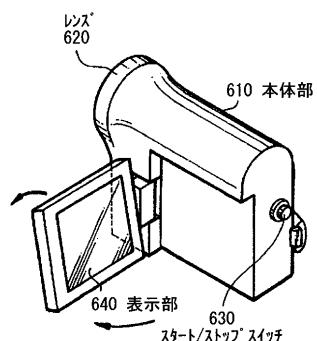

(適用例4)

図21は、ビデオカメラの外観を表したものである。このビデオカメラは、例えば、本体部 610，この本体部 610 の前方側面に設けられた被写体撮影用のレンズ 620，撮影時のスタート／ストップスイッチ 630 および表示部 640 を有している。この表示部 640 が上記表示装置に相当する。

**【0100】**

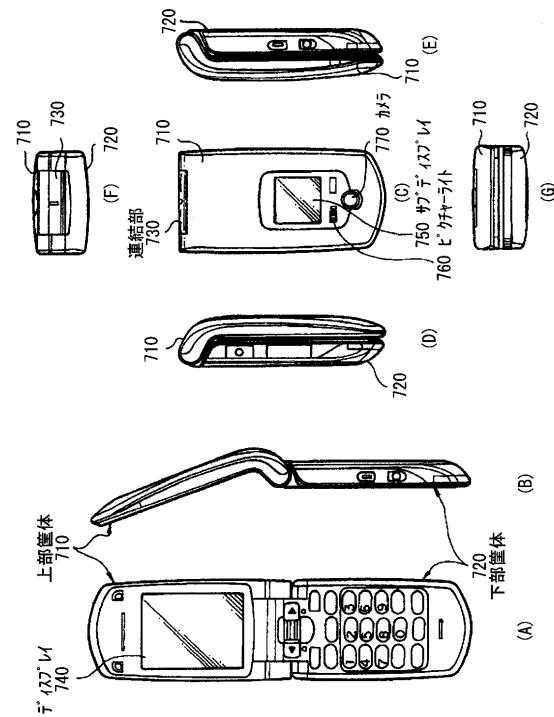

(適用例5)

図22は、携帯電話機の外観を表したものである。この携帯電話機は、例えば上側筐体 710 と下側筐体 720 とを連結部(ヒンジ部) 730 で連結したものであり、ディスプレイ 740，サブディスプレイ 750，ピクチャーライト 760 およびカメラ 770 を有している。そして、これらのうちのディスプレイ 740 またはサブディスプレイ 750 が、上記表示装置に相当する。

**【0101】**

以上、実施の形態および変形例を挙げて本開示を説明したが、本開示はこれらの実施の形態に限定されず、種々の変形が可能である。例えば、上記実施の形態等では、保持容量素子 10C, 20C における絶縁膜 12B が、トランジスタ 10B のゲート絶縁膜 12A と分離してパターニングされた構成を図示したが、これらのゲート絶縁膜 12A および絶縁膜 12B は必ずしも分離されていなくともよく、トランジスタ 10B から保持容量素子 10C にわたって連続的に形成されていてもよい。また、半導体層 11 についてはトランジスタ 10B から保持容量素子 10c, 20c にかけて一体的に(連続して)形成された構成を例示したが、トランジスタ 10B および保持容量素子 10c (20c) のそれぞれにおいて半導体層 11 が分離して設けられていてもよい。

**【0102】**

更に、上記実施の形態等では、高抵抗膜 14 を設けた構造を例に挙げて説明したが、この高抵抗膜 14 は設けられていなくともよい。但し、上述のように、高抵抗膜 14 を設けた場合の方が、トランジスタ 10B および保持容量素子 10C, 20C の電気特性を安定的に保持することができるため望ましい。

**【0103】**

加えて、上記実施の形態等では、半導体層 11 における所定の領域を低抵抗化させるための手法として、金属膜 14a と半導体層 11 との反応による手法を用いたが、この他にも、プラズマ処理によって低抵抗化する手法、プラズマ CVD 法によりシリコン窒化膜を成膜し、このシリコン酸化膜からの水素拡散等により低抵抗化させる手法などを用いてよい。

**【0104】**

尚、本開示の第1の表示装置は、以下の(1)～(7)に記載したような構成であってよい。

(1) 基板上に、表示素子と、前記表示素子の駆動素子としてのトランジスタと、映像信号に対応した電荷を保持する保持容量素子とを備え、前記保持容量素子は、前記基板側から順に、第1導電膜と、酸化物半導体よりなる第1半導体層と、絶縁膜と、第2導電膜とを有する表示装置。

(2) 前記トランジスタは、前記基板側から順に、酸化物半導体よりなる第2半導体層と、前記第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に配設されたゲート電極と、前記第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層とを有する上記(1)に記載の表示装置。

(3) 前記第1導電膜は、前記基板上の選択的な領域に配設され、前記第1半導体層および前記第2半導体層は、同一材料により前記基板上に一体的に設けられ、前記絶縁膜は、

10

20

30

40

50

前記ゲート絶縁膜と同一材料により構成され、かつ前記第2導電膜は、前記ゲート電極と同一材料により構成されている上記(2)に記載の表示装置。

(4) 前記第1半導体層および前記第2半導体層は、前記保持容量素子および前記ゲート電極のそれぞれに非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、前記ソース・ドレイン電極層は、前記低抵抗領域に電気的に接続されている上記(2)または(3)に記載の表示装置。

(5) 前記保持容量素子と、前記ゲート電極と、前記第1半導体層および前記第2半導体層の前記低抵抗領域とを覆って高抵抗膜が設けられている上記(2)～(4)のいずれかに記載の表示装置。

(6) 前記表示素子として有機電界発光素子を有する上記(1)～(5)のいずれかに記載の表示装置。 10

(7) 前記表示素子として液晶表示素子を有する上記(1)～(5)のいずれかに記載の表示装置。

#### 【0105】

また、本開示の第2の表示装置は、以下の(8)～(15)に記載したような構成であつてもよい。

(8) 基板上に、表示素子と、前記表示素子の駆動素子としてのトランジスタと、映像信号に対応した電荷を保持する保持容量素子とを備え、前記保持容量素子は、前記基板側から順に、酸化物半導体よりなる第1半導体層と、第1導電膜と、絶縁膜と、第2導電膜とを有する表示装置。 20

(9) 前記トランジスタは、前記基板側から順に、酸化物半導体よりなる第2半導体層と、前記第2半導体層上の選択的な領域に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に配設されたゲート電極と、前記第2半導体層に電気的に接続されて設けられたソース・ドレイン電極層とを有する上記(8)に記載の表示装置。

(10) 前記第1半導体層および前記第2半導体層は、同一材料により前記基板上に一体的に設けられ、前記絶縁膜と前記ゲート絶縁膜とが同一材料により構成され、かつ前記第2導電膜と前記ゲート電極とが同一材料により構成されている上記(9)に記載の表示装置。

(11) 前記第1導電膜は、前記酸化物半導体層上の選択的な領域に設けられると共に、アルミニウム(A1), モリブデン(Mo), チタン(Ti)のうちの1種よりなる単層膜または2種以上を積層した積層膜よりなり、前記第1半導体層および前記第2半導体層は、酸化インジウムスズ亜鉛(ITZO), 酸化インジウム亜鉛(IZO), 酸化インジウムガリウム(IGO), 酸化インジウムガリウム亜鉛(IGZO)のうちのいずれかよりなる上記(9)または(10)に記載の表示装置。 30

(12) 前記第1半導体層および前記第2半導体層は、前記保持容量素子および前記ゲート電極のそれぞれに非対向な領域に、他の領域よりも電気抵抗が低い低抵抗領域を有し、前記ソース・ドレイン電極層は、前記低抵抗領域に電気的に接続されている上記(9)～(11)のいずれかに記載の表示装置。

(13) 前記保持容量素子と、前記ゲート電極と、前記第1半導体層および前記第2半導体層の前記低抵抗領域とを覆って高抵抗膜が設けられている上記(9)～(12)のいずれかに記載の表示装置。 40

(14) 前記表示素子として有機電界発光素子を有する上記(8)～(13)のいずれかに記載の表示装置。

(15) 前記表示素子として液晶表示素子を有する上記(8)～(13)のいずれかに記載の表示装置。

#### 【符号の説明】

#### 【0106】

1A, 1B…有機EL表示装置、10A…有機EL素子、10B…トランジスタ、10C…保持容量素子、10…駆動側基板、27A, 27B…導電膜、11…半導体層、11S D…ソース・ドレイン領域、12A…ゲート絶縁膜、13A…ゲート電極、15…層間 50

絶縁膜、16...ソース・ドレイン電極層、12B...絶縁膜、13B...導電膜、14...高抵抗膜、17...平坦化膜、18...第1電極、19...画素分離膜、20...有機層、21...第2電極、22...保護層、23...封止用基板、2...液晶表示装置、20A...液晶表示素子、29...画素電極、24a, 24b...配向膜、25...液晶層、26...対向電極、27...バックライト、28a, 28b...偏光板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

(56)参考文献 特開2010-060683(JP,A)

特開2000-098409(JP,A)

特開2001-013518(JP,A)

特開2009-033145(JP,A)

特開2010-177223(JP,A)

特開2010-170110(JP,A)

特開2010-204239(JP,A)

特開2010-156963(JP,A)

特開2007-310352(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |   |             |

|--------|-------------|---|-------------|

| G 09 F | 9 / 3 0     | - | 9 / 4 6     |

| H 01 L | 2 7 / 3 2   |   |             |

| G 02 F | 1 / 1 3 4 3 | - | 1 / 1 3 4 5 |

|        | 1 / 1 3 5   |   |             |

| G 02 F | 1 / 1 3 6   | - | 1 / 1 3 6 8 |

| H 01 L | 5 1 / 5 0   |   |             |

| H 05 B | 3 3 / 0 0   | - | 3 3 / 2 8   |

| H 01 L | 2 1 / 3 3 6 |   |             |

|        | 2 9 / 7 8 6 |   |             |