(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7356088号

(P7356088)

(45)発行日 令和5年10月4日(2023.10.4)

(24)登録日 令和5年9月26日(2023.9.26)

(51)国際特許分類

|         |                  |     |         |         |   |

|---------|------------------|-----|---------|---------|---|

| G 0 1 R | 31/26 (2020.01)  | F I | G 0 1 R | 31/26   | A |

| G 0 1 R | 31/3161(2006.01) |     | G 0 1 R | 31/26   | B |

|         |                  |     | G 0 1 R | 31/3161 |   |

請求項の数 7 (全28頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2019-76005(P2019-76005)   |

| (22)出願日  | 平成31年4月12日(2019.4.12)       |

| (65)公開番号 | 特開2020-173197(P2020-173197) |

|          | A)                          |

| (43)公開日  | 令和2年10月22日(2020.10.22)      |

| 審査請求日    | 令和3年10月25日(2021.10.25)      |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 305040835<br>水上 俊彦<br>大阪府枚方市山之上北町 35 - 2   |

| (72)発明者  | 水上 俊彦<br>大阪府堺市堺区三宝町 4丁230番地<br>株式会社クオルテック内 |

| 審査官      | 島田 保                                       |

最終頁に続く

(54)【発明の名称】 半導体試験装置および半導体素子の試験方法

## (57)【特許請求の範囲】

## 【請求項 1】

第1の端子と第2の端子と第5の端子を有する半導体素子を試験する半導体素子試験装置であって、

第3の端子と第4の端子を有し、試験電流を供給する電源装置と、

誘導リアクタンス回路と、

前記第3の端子と前記第4の端子間に電気的に接続された第1のスイッチと、

前記半導体素子の前記第5の端子にゲート電圧を印加するドライバ回路と、

前記第1の端子と前記第2の端子間に、定電流を供給する定電流回路と、

前記第1の端子と前記第2の端子間の電圧を測定する電圧測定回路を具備し、

前記半導体素子の第1の端子は、前記第3の端子と電気的に接続され、

前記半導体素子の第2の端子は、前記第4の端子と電気的に接続され、

前記誘導リアクタンス回路は、前記第1の端子と前記第3の端子間に配置され、

前記誘導リアクタンス回路は、コイルあり経路とコイルなし経路を有し、前記試験電流は前記コイルあり経路または前記コイルなし経路を流れて前記半導体素子に供給され、

前記ゲート電圧のオフ時刻に同期して、前記第1のスイッチをオンさせて、前記第3の端子と前記第4の端子間の電荷を放電し、

前記半導体素子に前記試験電流を供給していない間に、前記定電流回路は前記第1の端子と前記第2の端子間に前記定電流を供給した状態で、前記電圧測定回路は前記第1の端子と前記第2の端子間の電圧を測定することを特徴とする半導体素子試験装置。

10

20

**【請求項 2】**

第 1 の端子と第 2 の端子と第 6 の端子と第 7 の端子と第 5 の端子を有する半導体素子を試験する半導体素子試験装置であって、

第 3 の端子と第 4 の端子を有し、試験電流を供給する電源装置と、

誘導リアクタンス回路と、

前記第 3 の端子と前記第 4 の端子間に電気的に接続された第 1 のスイッチと、

前記半導体素子の前記第 5 の端子にゲート電圧を印加するドライバ回路と、

前記第 6 の端子と前記第 7 の端子間に、定電流を供給する定電流回路と、

前記第 6 の端子と前記第 7 の端子間に、定電流を供給する定電流回路と、

前記第 6 の端子と前記第 7 の端子間に、定電流を供給する定電流回路と、

前記半導体素子の第 1 の端子は、前記第 3 の端子と電気的に接続され、

前記半導体素子の第 2 の端子は、前記第 4 の端子と電気的に接続され、

前記誘導リアクタンス回路は、前記第 1 の端子と前記第 3 の端子間に配置され、

前記誘導リアクタンス回路は、コイルあり経路とコイルなし経路を有し、前記試験電流

は前記コイルあり経路または前記コイルなし経路を流れて前記半導体素子に供給され、

前記ゲート電圧のオフ時刻に同期して、前記第 1 のスイッチをオンさせて、前記第 3 の端子と前記第 4 の端子間の電荷を放電し、

前記半導体素子間に前記試験電流が供給されていない期間に、前記定電流回路は第 7 の端子と前記第 6 の端子間に前記定電流を供給した状態で、前記電圧測定回路は前記第 7 の端子と前記第 6 の端子間の電圧を測定することを特徴とする半導体素子試験装置。

**【請求項 3】**

複数の前記半導体素子を有し、

前記半導体素子は順次選択されて、前記試験電流が前記半導体素子に供給されることを特徴とする請求項 1 または請求項 2 記載の半導体素子試験装置。

**【請求項 4】**

前記誘導リアクタンス回路のインダクタンスを可変できることを特徴とする請求項 1 または請求項 2 記載の半導体素子試験装置。

**【請求項 5】**

前記電源装置は、第 1 の試験電流を供給する第 1 の電源装置と第 2 の試験電流を供給する第 2 の電源装置を有し、前記第 1 の試験電流と前記第 2 の試験電流が加算されて前記半導体素子に供給されることを特徴とする請求項 1 または請求項 2 記載の半導体素子試験装置。

30

**【請求項 6】**

前記ゲート電圧は、周期時間、オン時間、オン電圧を設定できることを特徴とする請求項 1 または請求項 2 記載の半導体素子試験装置。

**【請求項 7】**

前記試験電流の停止後、1 m s 以内に、前記第 2 の端子と前記第 1 の端子間の電圧を測定することを特徴とする請求項 1 記載の半導体素子試験装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、IGBT、MOS-FET、GaN-FET、バイポーラトランジスタ等の半導体素子のパワーサイクル試験を行う半導体試験装置、半導体素子の試験方法等に関するものである。

40

**【0002】**

半導体素子の使用環境での故障モードに近いストレスを効率よく再現でき、高い信頼性でパワー半導体素子等の評価を行うことができる半導体試験装置および半導体素子の試験方法を提供する。

**【背景技術】****【0003】**

パワー半導体素子の寿命には、パワー半導体素子自体の発熱に起因した熱疲労現象によ

50

る寿命と、パワー半導体素子の外部環境の温度変化に起因した熱疲労現象による寿命とがある。また、パワー半導体素子のゲート絶縁膜への印加電圧による電圧疲労による寿命等がある。

なお、IGBTでは、エミッタ端子e、コレクタ端子cであるが、MOSトランジスタの場合は、ソース端子、ドレイン端子となる。

#### 【0004】

一般的に、パワー半導体素子の寿命試験は、パワー半導体に通電オンオフし、半導体素子の過熱冷却を繰り返すことが行われている。パワー半導体素子のエミッタ端子（ソース端子）、コレクタ端子（ドレイン端子）等に印加電圧および電流を設定し、ゲート端子に周期的なオンオフ信号（動作／非動作信号）を印加して試験が行われる。

10

#### 【0005】

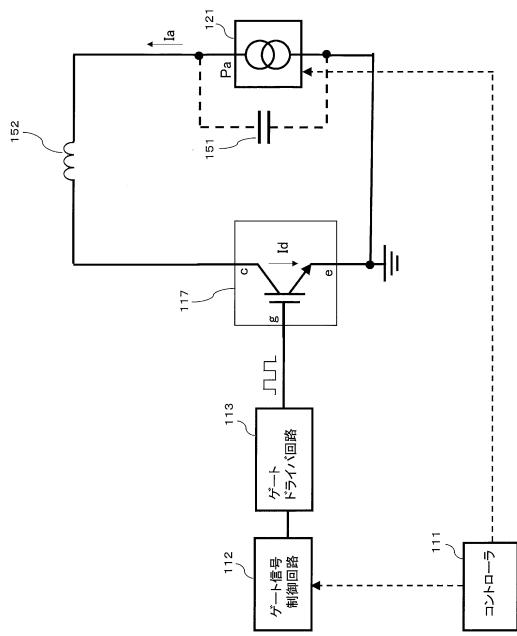

図15、図16は従来例としての半導体試験装置および半導体素子の試験方法の説明図である。パワー半導体素子としてのトランジスタ117のコレクタ端子cには定電流を出力する電流電源装置121が接続されている。トランジスタ117のエミッタ端子eは接地されている。トランジスタ117のゲート端子gには、ゲートドライバ回路113が接続されている。

#### 【0006】

ゲートドライバ回路113からは、設定された周波数、かつ、設定されたオン電圧時間のトランジスタ117のゲートをオンさせるオン電圧 $V_g$ が outputされる。オン電圧 $V_g$ に基づいて、トランジスタ117はオンオフされる。ゲートドライバ回路113はゲート信号制御回路112で制御される。

20

電流電源装置Pa121は定電流 $I_1 = I_a$ を出力し、スイッチSwaがオンすることにより、定電流 $I_a$ がトランジスタ117に印加される。

#### 【0007】

ゲートドライバ回路113から出力される $V_g$ s電圧により、トランジスタ117はオンオフ動作し、トランジスタ117がオンしている期間にトランジスタ117のチャンネル間に電流 $I_d$ が流れる。

#### 【0008】

トランジスタ117がオンするトランジスタ117のチャンネル電圧 $V_{ce}$ が順方向電圧 $V_n$ まで降下する。トランジスタ117がオフすると $V_{ce}$ 電圧は、電源電圧 $V_c$ まで上昇する。

30

トランジスタ117のチャンネル間電圧 $V_{ce}$ （図16（c））は、電流 $I_d$ が流れている時は、 $V_n$ 電圧となり、オフ状態では、 $V_c$ 電圧となる。

#### 【0009】

電流電源装置121には、内部に寄生容量成分である寄生容量リアクタンス151がある。また、試験回路の配線には誘導成分である寄生誘導リアクタンス152がある。

寄生容量リアクタンス151には、電流電源装置121により電荷がチャージされる。寄生誘導リアクタンス152は電流 $I_a$ を継続して流そうとする。

#### 【0010】

そのため、トランジスタ117がオフしても、一定期間の間は電流が流れ続けようとする。また、トランジスタ117のオン抵抗が次第に高くなるため、トランジスタ117の $V_c$ 電圧は上昇し、サージ電圧 $V_s$ が発生する（図16（d） $V_{ce}'$ ）。

40

#### 【0011】

また、寄生容量リアクタンス151は、トランジスタ117がオンする時に、トランジスタ117に大きな電流を供給し、突入電流 $I_s$ が発生する（図16（e） $I_d'$ ）。

サージ電圧 $V_s$ 、突入電流 $I_s$ は、トランジスタ117に電圧ストレスおよび電流ストレスを与え、トランジスタ117は信頼性が劣化する。

#### 【0012】

信頼性の劣化は、制御できない試験回路の誘導リアクタンス、容量性リアクタンスにより依存する。そのため、トランジスタ117の試験結果は、制御できないサージ電圧 $V_s$

50

、突入電流  $I_s$  の大きさなどに依存し、従来の試験装置で試験した結果から得られたトランジスタの寿命予測と、実際の回路で使用したトランジスタの寿命とが乖離しているという問題があった。

【先行技術文献】

【特許文献】

【0013】

【文献】特開2017-17822

【発明の概要】

【発明が解決しようとする課題】

【0014】

従来の半導体試験装置では、トランジスタ117をオンオフ動作させるとともに、定電流  $I_a$  をトランジスタのチャンネルに流すことにより、トランジスタの試験を実施している。

【0015】

試験は、トランジスタのオン周期、トランジスタのオン時間、トランジスタのオンオフ回数、トランジスタに流れる電流を設定することにより、トランジスタにストレスを与え、トランジスタの寿命予測あるいは試験トランジスタの劣化または破壊までの時間測定を行っていた。

【0016】

実使用状態において、トランジスタは、複数の電子デバイスと組み合わされて所定の動作をする回路が構成される。また、前記トランジスタには制御信号を入出力する接続ケーブルが接続される。

【0017】

試験時にトランジスタに突入電流  $I_s$  が流れると、トランジスタにストレスが与えられ寿命が短くなる。また、試験時にトランジスタのチャンネルにサージ電圧  $V_s$  が印加されるとトランジスタにストレスが与えられ、トランジスタの寿命が短くなる。

【0018】

トランジスタへの突入電流  $I_s$  、トランジスタのサージ電圧  $V_s$  の発生は、負荷としてのモータのインダクタンス、接続ケーブル等の誘導リアクタンス、容量性リアクタンスなどが影響するため、所定値にすることが難しい。

【0019】

従来の半導体試験装置および半導体素子の試験方法では、これらの寄生誘導リアクタンス、寄生容量性リアクタンスを制御できなかった。そのため、試験を行うトランジスタ117に突入電流  $I_s$  、サージ電圧  $V_s$  が印加され、また、突入電流  $I_s$  、サージ電圧  $V_s$  の大きさも調整することができなかった。

【0020】

従来の半導体試験装置および半導体素子の試験方法でトランジスタ117の試験を実施しても、実際の使用状態でのトランジスタ117の寿命の予測、トランジスタ破壊までの時間を予測できない、市場の不良実体との整合性がとれないという問題点があった。

【課題を解決するための手段】

【0021】

本発明の半導体試験装置は、トランジスタのチャンネルに流す第1の定電流に、突入電流に対応する第2の定電流を重畠できる電流制御回路を具備する。トランジスタに第1の定電流を印加する時間、印加周期を設定できる。また、第1の定電流に重畠する第2の定電流を印加する時間、印加周期を設定できる。

【0022】

本発明の半導体試験装置は、トランジスタの試験回路において、誘導リアクタンスまたはインダクタンスの値を変更あるいは設定できる誘導リアクタンス回路を具備する。トランジスタに第1の定電流を印加する時間、周期を設定できる。また、第1の定電流に重畠する第2の定電流を印加する時間、周期を設定できる。誘導リアクタンス回路の制御によ

10

20

30

40

50

り試験回路の誘導リアクタンス値を設定し、トランジスタに実回路に対応したサージ電圧を印加できる。また、トランジスタ 117 に流す電流  $I_d$  の遮断速度を変更あるいは設定できる。

【0023】

以上のように、本発明の半導体試験装置は、トランジスタのチャンネルに流す第1の定電流に突入電流に対応する第2の定電流を重畠できる電流制御回路と、誘導リアクタンス値を変更あるいは設定できる誘導リアクタンス回路のうち、少なくとも1つを具備する。

また、本発明の半導体デバイスの試験方法は、試験トランジスタなどに、所定の設定した突入電流  $I_s$ 、サージ電圧  $V_s$  を印加することができる。

【発明の効果】

【0024】

本発明は、試験するパワー半導体素子に突入電流  $I_s$ 、サージ電圧  $V_s$  の印加・無印加および印加タイミングを容易に設定できる。

したがって、パワー半導体素子に対して実際の使用環境、実際の使用回路を想定して信頼性を評価することができる。

【図面の簡単な説明】

【0025】

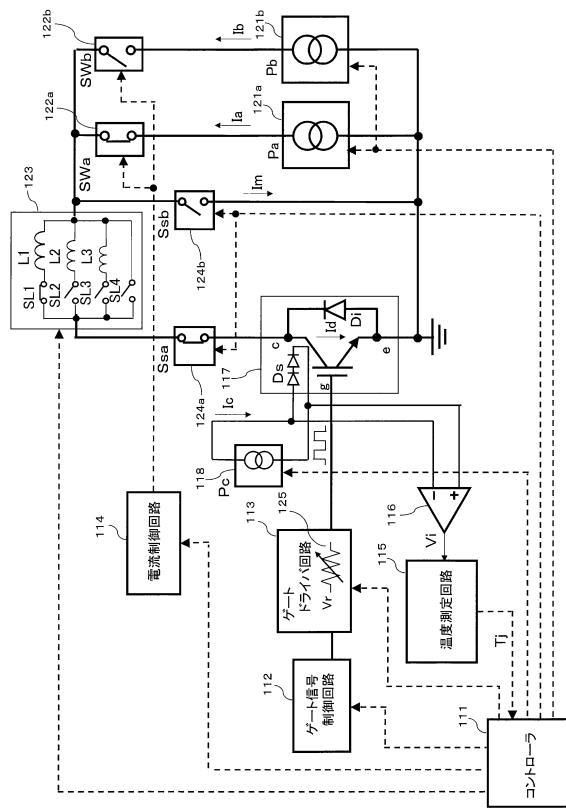

【図1】本発明の第1の実施例における半導体試験装置の説明図である。

【図2】本発明の半導体試験装置の構成図である。

【図3】本発明の第1の実施例における半導体素子の試験方法の説明図である。

20

【図4】本発明の第2の実施例における半導体素子の試験方法の説明図である。

【図5】本発明の半導体素子の試験方法の説明図である。

【図6】本発明の半導体素子の試験方法の説明図である。

【図7】本発明の第3の実施例における半導体素子の試験方法の説明図である。

【図8】本発明の第4の実施例における半導体素子の試験方法の説明図である。

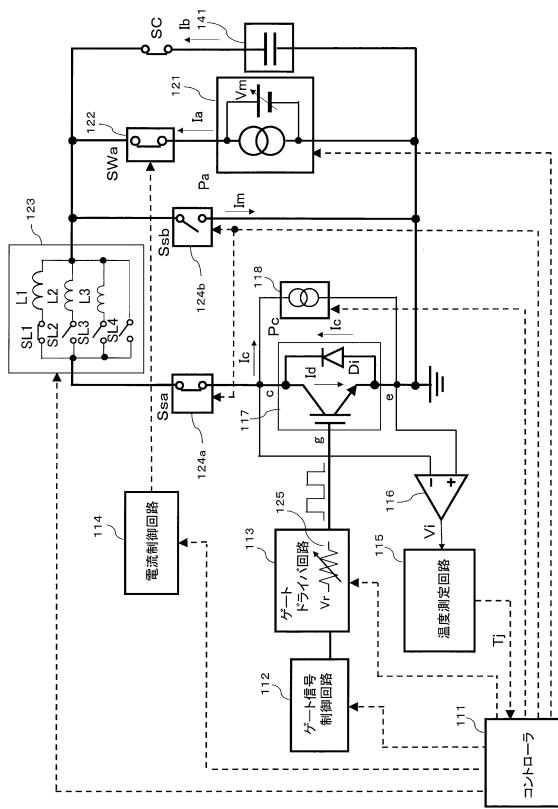

【図9】本発明の第2の実施例における半導体試験装置の説明図である。

【図10】本発明の第3の実施例における半導体試験装置の説明図である。

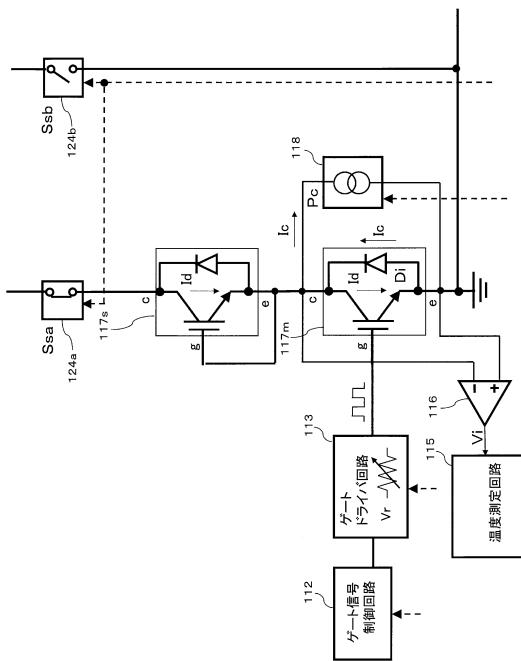

【図11】本発明の半導体試験装置の説明図である。

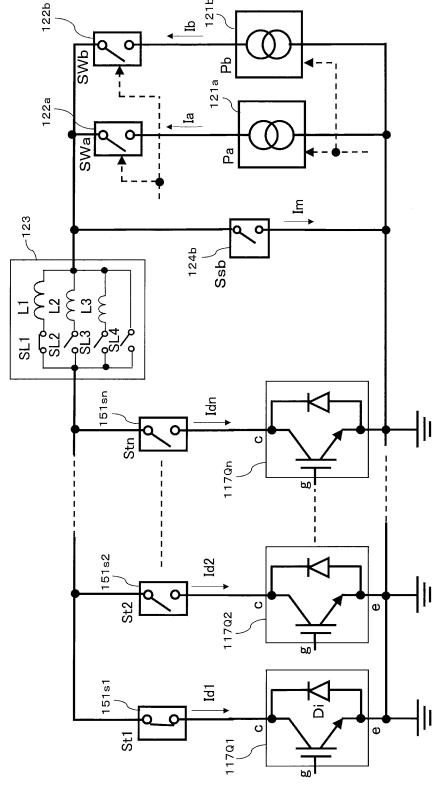

【図12】本発明の第4の実施例における半導体試験装置の説明図である。

【図13】本発明の第5の実施例における半導体素子の試験方法の説明図である。

30

【図14】パワーデバイスの説明図である。

【図15】従来の半導体試験装置の説明図である。

【図16】従来の半導体素子の試験方法の説明図である。

【発明を実施するための形態】

【0026】

以下、添付した図面を参照して、本発明の実施の形態に係るパワーサイクル試験装置および試験方法を説明する。

【0027】

明細書で記載する実施形態では、パワー半導体素子のうち、IGBTを例にとって説明するが、本発明は、IGBTに限定されるものではなく、MOSFET、JFET、トランジスタ等の各種のパワー半導体素子に適用することができる。また、トランジスタだけに適用されるものではなく、ダイオードなどの2端子素子にも本発明は適用できる。

40

また、パワー半導体素子に限定されるものではなく、低電力用の半導体素子にも本発明は適用できることは言うまでもない。

【0028】

発明を実施するための形態を説明するための各図面において、同一の機能を有する要素には同一の符号を付して説明を省略する場合がある。また、本発明の実施例は、それぞれを組み合わせることができる。

【0029】

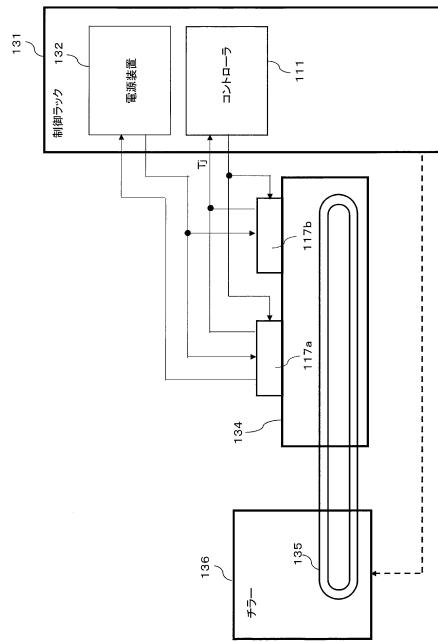

図2は本発明のパワーサイクル試験装置(半導体試験装置)の構成図である。パワーサ

50

イクル試験装置は、チラー（冷却・加温装置）136と、加熱冷却プレート134、加熱冷却プレート134とチラー136間を循環する循環水パイプ135を有する。

加熱冷却プレート134には、試験サンプルとしてのトランジスタ117が積載されている。

#### 【0030】

$T_j$  が一定になるように、電流  $I_d$ 、ゲート電圧  $V_g$ 、電圧  $V_{ce}$  を変化させて試験の条件を設定する。 $T_j$  が変化すると、トランジスタ117が劣化あるいは特性が変化していると判断し、トランジスタの信頼性を判定あるいは判定する。たとえば、電圧  $V_{ce}$  が 10 % アップまでの時間、電圧  $V_{ce}$  が 20 % アップまでの時間、トランジスタ117の破壊までの時間などが信頼性評価に使われる。

10

#### 【0031】

トランジスタ117の劣化あるいは特性変化にあわせて外部条件を変える。たとえば、トランジスタ117が発熱した場合は水温を下げる。水温を下げるとき、トランジスタ117に流れる電流を少なくすると、トランジスタ117の劣化、特性変化が進まず、結果、トランジスタ117の寿命が大幅に延びる。

#### 【0032】

また、チラー136の循環水を加温または冷却することにより、トランジスタ117の温度を規定値あるいは所定値に維持する。また、試験条件に対応してトランジスタ等の温度を周期的に変化させ、冷却し、加熱させる。また、試験トランジスタの  $T_j$  を測定し、測定した  $T_j$  を一定値に維持するように、チラー136を制御する。

20

#### 【0033】

制御ラック131には、トランジスタ117に試験電流、試験電圧を供給する電源装置132と、トランジスタ117を制御あるいは試験条件を設定する制御回路133を有している。

#### 【0034】

制御回路133には、トランジスタ117の温度情報  $T_j$  が入力され、温度情報  $T_j$  に基づいてチラー136を制御する。あるいは、温度情報  $T_j$  を所定温度にするように、チラー136を制御する。

#### 【0035】

なお、本明細書では循環水として説明するが、水に限定されるものではない。エチレングリコール、グリセリンなどでも良いし、強制空冷であってもよい。チラー136は循環水パイプ135内の液体を、例えば水温マイナス10からプラス100までの範囲で制御して試験ユニット3の加熱冷却プレート134に供給する。加熱冷却プレート134は十分に大きな熱容量を持っている。

30

#### 【0036】

上記実施形態では加熱冷却プレート134を使用したが、加熱プレートと冷却プレートを別体とし、加熱冷却プレート以外の熱源・冷熱源を用いて加熱・冷却するものであってもよい。

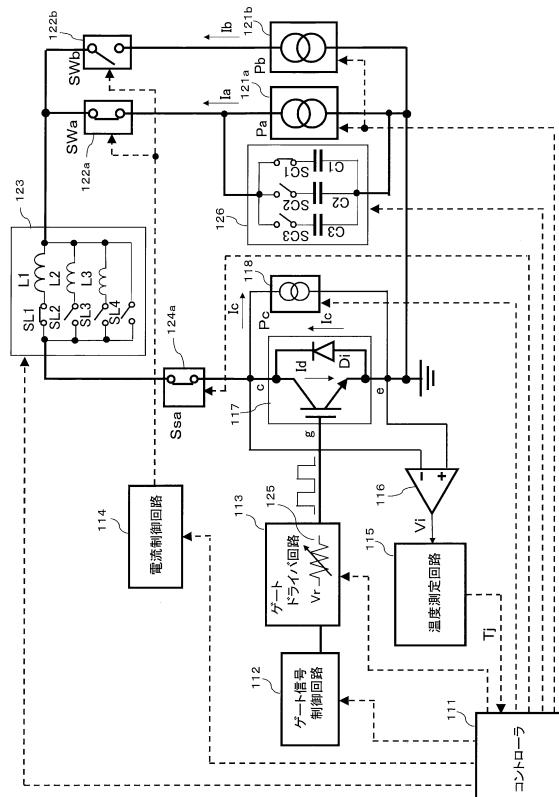

図1は本発明の第1の実施例における半導体試験装置（たとえば、パワートランジスタを試験するパワーサイクル試験装置）の構成図である。

40

#### 【0037】

電流電源装置121は、トランジスタ117を試験するための大電流の定電流を出力する。電流電源装置121は、コントローラ（パソコン用コンピュータ等）111からの制御信号に同期させて電力（電流、電圧）を供給すると共に、供給された電力を用いて前記負荷を設定された定電流または定電圧で駆動する。また、電流電源装置121は、出力する最大電圧値を設定することができる。

#### 【0038】

スイッチ122（SWa、SWb）は、電流電源装置121が出力する定電流の供給をオン（供給）オフ（遮断）させる。スイッチ122は電流制御回路114からの信号に基づき、オン（定電流を出力）またはオフ（定電流を遮断）に設定制御される。

50

## 【0039】

スイッチ SW a は電流電源装置 121a の電流経路に配置されている。スイッチ SW b は電流電源装置 121b の電流経路に配置されている。スイッチ 122 は、電流制御回路 114 からの信号に基づき、オン(定電流を出力)またはオフ(定電流を遮断)に設定制御される。

## 【0040】

図 1 などにおいて、2 台の電流電源装置 121 を図示している。電流電源装置 121 は 2 台に限定されるものではない。3 台以上の電流電源装置 121 を保有してもよい。電流電源装置 121 の台数が増加するほど、多種多様な電流波形 Id を発生させることができ 10 る。

## 【0041】

1 台の電流電源装置 121 が図 6 などで図示する電流 Id 信号を発生できる場合は、1 台の電流電源装置 121 を有すればよいことは言うまでもない。1 つの電流電源装置 121 が、定電流 I2 を出力し、t c 時間の経過後、定電流 I1 を出力し、t on の時間後、電流出力を 0 とできれば 1 台の電流電源装置 121 でよいことは言うまでもない。

## 【0042】

本発明の実施例において、電流電源装置 121 として説明するが、電流電源装置 121 は定電流を出力するものに限定されるものではない。たとえば、電流電源装置 121 が最大電圧を設定し、一定の条件で、設定された最大電圧において、所定の定電流を出力できるように機能させることができ。したがって、電流電源装置 121 は、定電流の出力する装置ではなく、電圧、電流を出力できる電源装置である。 20

## 【0043】

図 1 などの実施例において、電流電源装置 121 で電流 Id 信号を発生させるとして説明するが、図 6 などで図示する電流 Id は、トランジスタ 117 のオン抵抗の状態に応じて、印加電圧を調整することにより実現できる。したがって、本発明の半導体試験装置において、電流電源装置 121 に限定するものではなく、電圧出力の電源装置で構成しても良いことはいうまでもない。

## 【0044】

図 6 などに図示する電流 Id は、トランジスタ 117 のゲート電圧の電圧値の制御によつても実現できる。本明細書では、電流電源装置 121 の制御によって、トランジスタ 117 に所定の電流を印加するとして説明するが、これに限定するものではなく、トランジスタ 117 のゲート端子 g の電圧、トランジスタ 117 のコレクタ端子 c の電圧を調整あるいは制御してもよいことは言うまでもない。 30

## 【0045】

誘導リアクタンス回路 123 は、内部に複数の誘導リアクタンスあるいはインダクタンスとしてのコイル L を有している。また、前記コイルを試験回路に挿入するためのスイッチ SL を有している。複数のコイル L は、誘導リアクタンスが異なるものである。

## 【0046】

一例として、図 1 では、一例としてコイル L1、コイル L2、コイル L3 を図示している。また、コイルがない電流経路も形成している。また、抵抗素子を有する電流経路を設けても良いことは言うまでもない。また、配線などの寄生コンダクタンスを誘導リアクタンスとして利用してもよい。 40

## 【0047】

コイル L1 にはスイッチ SL1 が接続され、スイッチ SL1 がクローズすることにより、電流電源装置 121 が出力する定電流の経路にコイル L1 が挿入される。コイル L2 にはスイッチ SL2 が接続され、スイッチ SL2 がクローズすることにより、電流電源装置 121 が出力する定電流の経路にコイル L2 が挿入される。コイル L3 にはスイッチ SL3 が接続され、スイッチ SL3 がクローズすることにより、電流電源装置 121 が出力する定電流の経路にコイル L3 が挿入される。スイッチ SL4 の経路にはコイル L は配置されていない。 50

したがって、スイッチ S L 4 がクローズすることにより、電流電源装置 1 2 1 が出力する定電流は、コイル L を経由しないでトランジスタ 1 1 7 に供給される。

【 0 0 4 8 】

複数のスイッチ S L を同時にオンできるように構成してもよい。スイッチ S L のオンオフ（動作 / 非動作）制御は、コントローラ 1 1 1 からの制御信号に基づき、制御される。

【 0 0 4 9 】

本発明の実施例において、誘導リアクタンス回路 1 2 3 を設け、スイッチ S L をオンオフさせることにより、定電流が流れる経路に誘導リアクタンスとしてのコイル L を挿入するとした。しかし、本発明はこれに限定するものではない。

【 0 0 5 0 】

たとえば、誘導リアクタンスとしてのコイル L をネジ止めなどにより、定電流の経路に挿入してもよい。挿入するコイル L の誘導リアクタンスの値は、トランジスタ 1 1 7 への突入電流値を観察して設定する。

【 0 0 5 1 】

1 つのコイルの中間に多数のタップを設け、各タップと接続することにより、誘導リアクタンス値を設定できるように構成してもよい。誘導リアクタンスとしてのコイル L にスライダック構造を形成してリニア的にリアクタンス量を設定あるいは調整できるように構成してもよい。

【 0 0 5 2 】

容量リアクタンス回路 1 2 6 は、内部に複数の容量リアクタンスあるいはインダクタンスとしてのコンデンサ C を有している。コンデンサ C は容量が異なる。また、前記コンデンサ C を試験回路に挿入するためのスイッチ S C を有している。複数のコンデンサ C は、容量リアクタンスが異なるものである。

【 0 0 5 3 】

一例として、図 1 では、一例として、容量の異なるコンデンサ C 1 、コンデンサ C 2 、コンデンサ C 3 の 3 種類を図示している。コンデンサの種類個数は 1 つでも良いし、複数でも良い。また、コンデンサに限らず、電荷を一時的に蓄積できるものであればいずれの物でも良い。たとえば、電池でもよい。

【 0 0 5 4 】

コンデンサ C 1 にはスイッチ S C 1 が接続され、スイッチ S C 1 がクローズすることにより、電流電源装置 1 2 1 が出力する定電流の経路にコンデンサ C 1 が挿入される。コンデンサ C 2 にはスイッチ S C 2 が接続され、スイッチ S C 2 がクローズすることにより、電流電源装置 1 2 1 が出力する定電流の経路にコンデンサ C 2 が挿入される。コンデンサ C 3 にはスイッチ S C 3 が接続され、スイッチ S C 3 がクローズすることにより、電流電源装置 1 2 1 が出力する定電流の経路にコンデンサ C 3 が挿入される。

【 0 0 5 5 】

複数のスイッチ S C を同時にオンできるように構成してもよい。スイッチ S C のオンオフ（動作 / 非動作）制御は、コントローラ 1 1 1 からの制御信号に基づき、制御される。

【 0 0 5 6 】

本発明の実施例において、容量リアクタンス回路 1 2 6 を設け、スイッチ S C をオンオフさせることにより、電源装置 1 2 1 に並列経路に容量リアクタンスとしてのコンデンサ C を挿入するとした。しかし、本発明はこれに限定するものではない。

【 0 0 5 7 】

たとえば、容量リアクタンスとしてのコンデンサ C をネジ止めなどにより、定電流の経路に並列に挿入してもよい。挿入するコンデンサ C の容量リアクタンスの値は、トランジスタ 1 1 7 へのサージ波形を観察して設定する。

【 0 0 5 8 】

1 つのコンデンサの中間に多数のタップを設け、各タップと接続することにより、容量リアクタンス値を設定できるように構成してもよい。また空気コンデンサのように、2 つの電極の相対的な重なり度合を調整することにより、容量リアクタンスの値を可変できる

10

20

30

40

50

ように構成してもよい。

【0059】

電流電源装置121(Pa)は、一定の条件で、最大あるいは所定の電圧Vmを設定でき、所定の定電流を出力できるように機能させることができる。電流電源装置121は、定電流を出力するだけではなく、設定した電圧Vm、定電流Iaを出力できる電源装置である。

【0060】

電流電源装置121aに並列して、容量リアクタンス回路126を配置している。容量リアクタンス126のスイッチSCにより選択されたコンデンサCには、電流電源装置121が outputする電流Iaに伴う電圧あるいは設定された電圧Vmにより電荷がチャージされる。電荷により、図6に示すように、tcの期間、Is電流がトランジスタ117に印加される。

【0061】

ゲートドライバ回路113は、内部に可変抵抗Vr125を有している。可変抵抗Vrの値は、0( )から500( )間で、所定値に、あるいはステップ的に設定できるように構成されている。ゲート端子gの波形を観察しながら、コントローラ111からの制御信号により可変抵抗125の値を設定してもよい。また、トランジスタ117のゲート端子gとエミッタ端子eまたはコレクタ端子c間に抵抗(図示せず)を配置してもよい。

可変抵抗の値が大きい場合は、トランジスタ117のゲート端子に印加するトランジスタ117のゲート信号の立上/立下波形の傾斜が緩やかになる。

一方、可変抵抗の抵抗値が小さい場合は、ゲート信号の立上/立下波形の傾斜が急峻になる。

可変抵抗Vrの値を変更あるいは所定値に設定することにより、トランジスタ117のオン時間を調整できる。

【0062】

ゲートドライバ回路113は、立上波形の傾斜(立上り時間tr)と立下り波形の傾斜(立下り時間td)を設定できる。立上り時間trと立下り時間tdを別々に調整することによりトランジスタ117のオン時間等を任意に調整できる。

【0063】

可変抵抗Vrの抵抗値は、コントローラ111により設定する。設定は、一定値であることに限定されない。ゲートドライバ回路113の立上波形の傾斜(立上り時間tr)と立下り波形の傾斜(立下り時間td)を変化させてもよい。ゲート信号の立上時の抵抗値と、立下時の抵抗値とを変化させてもよい。また、リアルタイムに抵抗値を可変制御してもよい。抵抗値を可変制御することにより、トランジスタ117のオン時間が安定する。

【0064】

ゲート信号の立上時の抵抗値を小さくすると、トランジスタ117のゲート端子に印加されるオン電圧の波形が急峻になり、高速にトランジスタ117がオンする。ゲート信号の立上時の抵抗値を大きくすると、トランジスタ117のゲート端子に印加されるオン電圧の波形が緩やかになり、緩やかにトランジスタ117がオンする。

【0065】

ゲート信号の立下時の抵抗値を小さくすると、トランジスタ117のゲート端子に印加されるオン電圧の波形が急峻になり、高速にトランジスタ117がオフする。ゲート信号の立下時の抵抗値を大きくすると、トランジスタ117のゲート端子に印加されるオン電圧の波形が緩やかになり、緩やかにトランジスタ117がオフする。

【0066】

以上のように、トランジスタ117のゲート端子に接続された抵抗Vrの値、あるいはゲートドライバ回路113の立上り時間/立下り時間を制御あるいは調整または設定することにより、トランジスタ117に発生させる突入電流Is、サージ電圧Vsを変化あるいは変更することができる。以上のように、本発明は、ゲートドライバ回路113の機能により突入電流Is、サージ電圧Vsの大きさ、発生時間、変化速度を設定、調整、制御す

10

20

30

40

50

ることができる。

【0067】

また、電源装置121内のコンデンサ、外付けコンデンサ141の容量を切り替えて、突入電流 $I_s$ 、サージ電圧 $V_s$ を変化させる方法もある。図1では2台の電源装置121を保有する。電源装置121内のコンデンサ、外付けコンデンサ141の容量を切り替える方法は、電源装置121が1台の場合に有効である。

また、最大電源電圧を変化させ、試験デバイス通電中の電圧と定電流源の最大圧の差を変化させることで突入電流を調整することができる。

【0068】

以上のように、本発明の半導体試験装置および半導体の試験方法における突入電流 $I_s$ の調整方法は、電源装置121を複数台使用することにより、最大突入電流、突入電流の印加時間は任意に設定できる。また、コンデンサの容量を変えることにより、突入電流の印加時間、突入最大電流を設定できる。また、電源装置121を定電流源とし、最大電圧を変化させることにより、最大突入電流を任意に設定できる。

10

【0069】

トランジスタ117の動作は、トランジスタ117のゲート端子のオン電圧の制御だけでなく、電流電源装置121がトランジスタ117に供給する定電流 $I_d$ あるいは電圧 $V_m$ の値を変化あるいは設定できることは言うまでもない。

【0070】

ゲートドライバ回路113の可変抵抗125はコントローラ111により制御される。ゲートドライバ回路113が出力するゲート信号の周期時間 $t_{cycle}$ 、オン時間 $t_{on}$ はゲート信号制御回路が発生する。また、ゲート信号制御回路はコントローラ111により制御される。

20

【0071】

図1などにおいて、ゲートドライバ回路113の可変抵抗125の抵抗値は、可変としたがこれに限定するものではない。たとえば、可変抵抗125を外付け抵抗とし、抵抗をコネクタ(図示せず)などによりトランジスタ117のゲート端子に接続してもよいことは言うまでもない。接続する抵抗の値は、トランジスタ117のゲート端子の波形、チャンネル電流 $I_d$ の波形を観察して設定する。

【0072】

30

図1などにおいて、トランジスタ117のコレクタ端子cとエミッタ端子e間には定電流回路Pc118が接続されている。定電流回路118は、所定の定電流 $I_c$ を流す。定電流 $I_c$ はトランジスタ117の温度をモニターするためである。

【0073】

なお、IGBTを例示して本明細書は説明するため、トランジスタ117の端子はゲート端子g、コレクタ端子c、エミッタ端子eである。MOSトランジスタ117の場合は、トランジスタ117の端子はゲート端子g、ドレイン端子d、ソース端子sとなる。

【0074】

トランジスタ117には、ボディダイオードあるいはチャンネルダイオード $D_i$ が形成されている。なお、ダイオード $D_i$ は同一ダイに実装された別チップのダイオードであつてもよい。ダイオードはトランジスタ117の層構造により副次的に形成される。ダイオード $D_i$ は、構造上、トランジスタ117のチャンネル部の近傍に形成される。トランジスタ117のチャンネルに電流 $I_d$ が流れるとトランジスタ117はオン抵抗により発熱する。

40

【0075】

ダイオード $D_i$ はトランジスタ117の発熱により抵抗値が変化する。ダイオード $D_i$ に定電流 $I_c$ を流すと、ダイオード $D_i$ の抵抗値の変化に比例してダイオード $D_i$ の端子間の電圧が変化する。端子間の電圧をモニターすれば、トランジスタ117の温度または、温度の変化を知ることができる。

トランジスタ117の温度をダイオード $D_i$ の電圧からモニターするためには、温度係

50

数を予め取得しておく必要がある。

【0076】

温度係数は、トランジスタ117を恒温槽で所定温度に設定し、ダイオードDiに定電流Icを流して、ダイオードDiの端子電圧を測定する。前記所定温度を変化させ、かつダイオードDiの端子電圧を測定することにより、温度に対するダイオードの端子電圧を取得できる。したがって、温度に対するダイオードの端子電圧からトランジスタ117の温度係数Kを求めることができる。

【0077】

温度係数Kは、トランジスタ117の各生産ロットで異なる場合があるが、一般的には生産ロットで一定の値を示す。したがって、各生産ロットで、試験を行うトランジスタ117を抜き取り、温度係数Kを求めておけば他のトランジスタ117の温度係数Kにも使用できる。

10

【0078】

精度よく温度係数Kを取得するには、同じロットでも、各トランジスタ117の温度係数Kを個別に測定して試験をする。温度係数Kの測定は、恒温槽の使用に限定されない。たとえば、トランジスタ117を実装したヒートシンクに流す水温を変えて温度係数Kを取得する。

【0079】

試験時は、トランジスタ117に間欠的に、試験電流Idを印加する。試験電流Idをオフした直後あるいは、オフした後、短時間の所定時間の経過後、定電流回路118から、温度測定用の定電流Icを流す。定電流Icでトランジスタ117が発熱することを防止し、あるいは定電流Icの影響がないようにするために、定電流Icはトランジスタ117のチャンネルに流す定電流Idよりも十分に小さい電流値にする。定電流Idは、温度測定に影響を与える発熱しない程度の電流を流す。

20

【0080】

具体的には、定電流Icは試験時にトランジスタ117に流す電流Idの1/1000以下に設定する。好ましくは、トランジスタ117に流す電流Icは電流Idの1×10<sup>6</sup>の1以上1×10<sup>4</sup>の1以下にする。定電流Icは0.1mA以上100mA以下にする。

【0081】

30

チャンネル電流Idを変化させ、ダイオードDi電圧（トランジスタ117のコレクタ-エミッタ端子間電圧）を測定して、温度係数Kを求める。求められた温度係数Kは、温度測定回路115に記憶させる。

【0082】

温度を測定する時、ダイオードDiがトランジスタ117と同一チップ内に形成されている場合、ゲート電圧Vgによって飽和電圧のVf電圧が変化する場合がある。ゲート電圧Vgはゼロ電圧または負電圧（マイナス電圧）とすることが好ましい。

【0083】

図2に示すように、温度Tjに基づいて、コントローラ111はチラー136を制御する。チラー136は循環水（循環溶液）の温度を調整し、加熱冷却プレート134の温度を調整する。

40

以上の実施例では、予め、温度係数Kを求めるとしたが、本発明の半導体試験方法はこれに限定するものではない。

トランジスタ117と加熱冷却プレート134に密着して配置し、加熱冷却プレート134の温度が、トランジスタ117と略一致するように構成する。

【0084】

コントローラ111はチラー136を制御して、加熱冷却プレート134の温度を所定温度にし、トランジスタ117に定電流Icを印加して、ダイオードDiの端子電圧を測定する。測定結果から、温度係数Kを求める。加熱冷却プレート134の温度は、複数の温度に設定し、それぞれの温度での温度係数Kを求め、結果からより温度係数の値の精度

50

を向上させる。

〔 0 0 8 5 〕

温度係数は、トランジスタ 117 を加熱冷却プレート 134 で所定温度にし、ダイオード Di に定電流  $I_c$  を流して、端子電圧を測定する。前記所定温度を変化させ、かつダイオード Di の端子電圧を測定することにより、温度に対するダイオードの端子電圧を取得できる。したがって、温度に対するダイオードの端子電圧からトランジスタ 117 の温度係数 K を求めることができる。

〔 0 0 8 6 〕

トランジスタ 117 の試験時は、定電流  $I_c$  は、チャンネル電流  $I_d$  が流れていない時にダイオード  $D_i$  に流す。つまり、トランジスタ 117 がオンしていない時に、定電流  $I_c$  を流してダイオード  $D_i$  の端子間電圧を測定する。

10

オペアンプ回路(バッファ回路)116は、ダイオードD1の端子電圧Vi(端子c-端子e)を出力する。

〔 0 0 8 7 〕

温度測定回路 115 を保持されている温度係数  $K$  と電圧  $V_i$  から、試験を実施しているトランジスタ 117 の温度  $T_j$  を求める。求められた温度  $T_j$  はコントローラ 111 に送られる。コントローラ 111 は、温度  $T_j$  が所定設定値以上になった場合、トランジスタ 117 が所定のストレス状態となつたと判断して試験の停止などを行う。

〔 0 0 8 8 〕

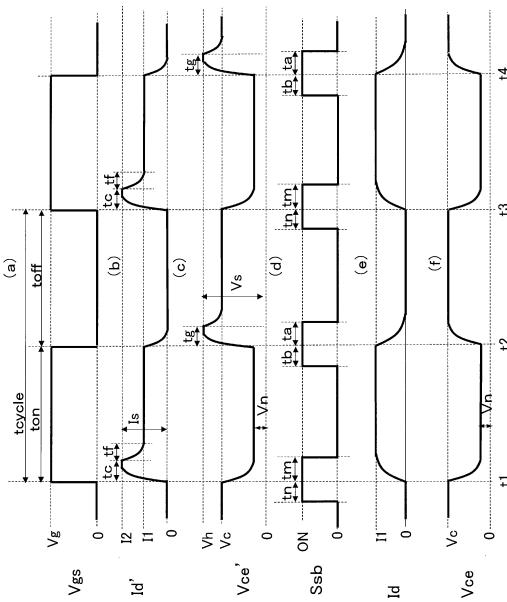

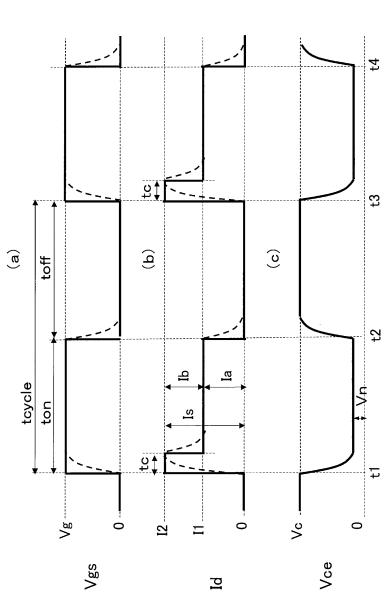

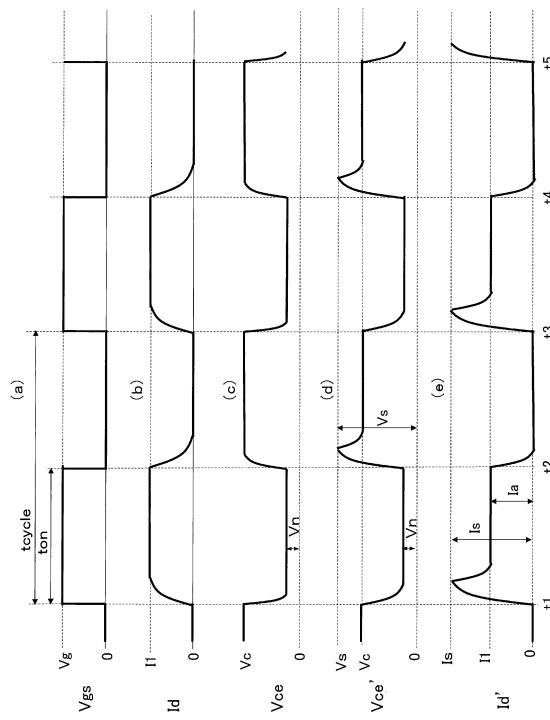

図3は、本発明の半導体素子の試験方法の説明図である。図3(a)に図示するように、ゲートドライバ回路113からゲートオン電圧信号 $V_{gs}$ がトランジスタ117のゲート端子gに印加される。ゲートオン電圧信号 $V_{gs}$ は周期時間 $t_{cycle}$ 、オン時間 $t_{on}$ である。周期時間 $t_{cycle}$ 、オン時間 $t_{on}$ はゲート信号制御回路112で任意の値に設定することができる。また、オン電圧 $V_{gs}$ も任意の電圧に設定することができる。

20

【 0 0 8 9 】

図3に図示する一定値の電流  $I_d$  をトランジスタ117に印加するには、電流電源装置121aだけを動作させ、トランジスタ117に電流  $I_d$  (=  $I_a$ ) を印加する。

〔 0 0 9 0 〕

また、ゲートドライバ回路 113 の可変抵抗 125 の抵抗値  $V_r$  も設定することができる。抵抗値を大きくすることにより、ゲートオン電圧信号  $V_{gs}$  の立上 / 立下波形は、点線のように変化させることができる。

30

〔 0 0 9 1 〕

図3は第1の実施例における半導体素子の試験方法の説明図である。図3に図示すように、パワー半導体素子としてのトランジスタ117のコレクタ端子cには定電流を出力する電流電源装置121が接続されている。図1の本発明の電流電源装置121aと121bのいずれかの電源装置を使用することにより、トランジスタ117のチャンネルに流す電流 $I_d$ を発生することができる。

〔 0 0 9 2 〕

なお、図1において、誘導リアクタンス回路123は、スイッチSL4がクローズされ、電流経路に挿入されるリアクタンス成分は「0」、または極力少ない状態にされている。

10

スイッチ 1 2 4 a ( S s a ) はクローズされ、図 1 には図示していないが、図 10 と同様のスイッチ 1 2 4 b ( S s b ) はオープンに設定される。

[ 0 0 9 3 ]

本発明の第1の半導体素子の試験方法の実施例では、説明を容易にするため、定電流  $I_a = I_d$  は電流電源装置 121a が発生するとし、定電流  $I_a$  の供給のオン / オフ（動作 / 非動作）はスイッチ 122a (SWa) により供給するとする。なお、定電流  $I_a$  は、電流電源装置 121a と電流電源装置 121b の両方を用いて供給してもよいことは言うまでもない。

[ 0 0 9 4 ]

トランジスタ 117 に流す電流  $I_d$  は電流電源装置 121 を動作させることにより供給

50

する。電流電源装置 121 はコントローラ 111 からの信号によりオン／オフ制御される。

【0095】

定電流  $I_a$  ( $= I_d$ ) は、スイッチ 122a をクローズすることにより供給される。スイッチ 122 の制御は電流制御回路 114 によって制御される。電流制御回路 114 はコントローラ 111 によりタイミング制御される。

トランジスタ 117 のエミッタ端子 e は接地されている。トランジスタ 117 のゲート端子 g には、ゲートドライバ回路 113 が接続されている。

【0096】

ゲートドライバ回路 113 からは、設定された周波数、かつ、設定されたオン電圧時間のトランジスタ 117 のゲートをオンさせるオン電圧  $V_g$  が出力される。図 3 の実施例では、図 3 (a) に図示するように、トランジスタ 117 のオンオフ周期は  $t_{cycle}$  であり、オン時間は  $t_{on}$ 、オフ時間は  $t_{off}$  である。

図 3 (a) のオン電圧  $V_g$  に基づいて、トランジスタ 117 はオンオフされる。ゲートドライバ回路 113 はゲート信号制御回路 112 で制御される。

【0097】

スイッチ 122a は電流制御回路 114 で制御される。電流制御回路 114、ゲート信号制御回路 112、電流電源装置 121 は、コンピュータ (PC) 111 で制御される。

電流電源装置 121 は定電流  $I_1 = I_a$  を出力し、スイッチ SWa がオンすることにより、定電流  $I_a$  がトランジスタ 117 に印加される。

【0098】

ゲートドライバ回路 113 から出力される  $V_g$  電圧により、トランジスタ 117 はオンオフ動作し、トランジスタ 117 がオンしている期間にトランジスタ 117 のチャンネル間に電流  $I_d$  が流れる。

【0099】

トランジスタ 117 がオンするトランジスタ 117 のチャンネル電圧  $V_{ce}$  は順方向電圧  $V_n$  まで降下する。トランジスタ 117 がオフすると  $V_{ce}$  電圧は、電流電源装置 121 が発生する電源電圧  $V_c$  まで上昇する。

トランジスタ 117 のチャンネル間電圧は、電流  $I_d$  が流れている時は、 $V_n$  電圧となり、オフ状態では、 $V_c$  電圧となる。

【0100】

電流電源装置 121 または試験回路には容量成分であるコンデンサ (図示せず) がある場合がある。また、試験回路の配線には誘導成分であるコイル (図示せず) がある場合がある。

【0101】

コンデンサには、電流電源装置 121 により電荷がチャージされる。コイルは電流  $I_a$  を継続して流そうとする。トランジスタ 117 がオフしても、一定期間の間は電流が流れ続けようとするため、トランジスタ 117 の  $V_{ce}$  電圧は上昇し、サージ電圧  $V_s$  が発生する (図 3 (c)  $V_{ce}'$ )。

【0102】

電流電源装置 121 にコンデンサ 141 がない場合であっても、サージ電圧  $V_s$  を発生させることができる。電流電源装置 121 は常に定電流を流そうとしているので、トランジスタ 117 をオフしても電流電源装置 121 は電流を供給し続けようとする。しかし、トランジスタ 117 がオフとなり、電流が流れなくなれば電流電源装置 121 は、設定された電源電圧の最大電圧が上がり電流がゼロになる。この時にインダクタンスがあると、電流が遮断される時間が長くなり、サージ電圧  $V_s$  が発生する。

【0103】

トランジスタ 117 がオフする時に流れている電流を  $I_a$  (A) とし、トランジスタ 117 のチャンネルに流れる電流が 0 (A) になるまでの時間を  $t_g$  ( $\mu$ 秒) とし、実回路の配線などによる等価的な誘導リアクタンスを  $L$  ( $\mu$ H) とすると、サージ電圧  $V_s$  (V) は、以下で示される。

10

20

30

40

50

$$V_s = -L \times I_a / t_g$$

なお、上式では、電流の方向性を考慮して、「-」記号を付加している。

#### 【0104】

誘導リアクタンスは、スイッチ SWa122a がオフした後も、コイル L に蓄えられた電流をトランジスタ 117 に印加しようとする。また、トランジスタ 117 が完全にオフするまでは、一定の期間を必要とする。したがって、コイル L の大きさに比例してサージ電圧が発生する。

#### 【0105】

たとえば、 $I_1 = I_a = 100$  (A)、 $t_g = 1$  ( $\mu$ s)、コイルの誘導リアクタンス  $L = 10$  ( $\mu$ H) とすれば、 $V_s = 10$  ( $\mu$ H)  $\times 100$  (A) / 1 ( $\mu$ s) = 1000 (V) となる。したがって、サージ電圧  $V_s = 1000$  (V) が発生する。

10

#### 【0106】

サージ電圧  $V_s$  は、トランジスタ 117 に電圧ストレスを与え、トランジスタ 117 は信頼性劣化する。トランジスタ 117 の試験結果は、サージ電圧  $V_s$  の大きさなどに依存する。

#### 【0107】

スイッチ 124b がオンすると、コンデンサ (図示せず) にチャージされた電荷による電流  $I_m$  がスイッチ 124b を介してグランド (接地電位) に流れる。誘導リアクタンス回路 123 のスイッチ SL4 がオンのため、試験回路の誘導リアクタンスも小さい。

20

#### 【0108】

図 3 (d) に図示するように、スイッチ Ssb はゲート電圧  $V_{gs}$  のオフ時刻に対して  $t_b$  時間前にオンさせる。 $t_b$  時間は 10m 秒以下 0m 秒以上の時間である。好ましくは、1m 秒以下 0m 秒以上の時間である。

#### 【0109】

図 3 (d) に図示するように、スイッチ Ssb はゲート電圧  $V_{gs}$  のオフ時刻に対して  $t_a$  時間後にオフさせる。 $t_a$  時間は 0m 秒以上 10m 秒以下の時間である。好ましくは、0m 秒以上 2m 秒以下の時間である。

トランジスタ 117 に電流  $I_d$  を供給していない時に、ダイオード Di の端子電圧を測定して、 $T_j$  を求める。

30

#### 【0110】

温度測定は、トランジスタ 117 に順方向電流が流れていないとときに測定する。順方向電流(加熱電流)がオフされると、チップ温度が低下するので通電停止後、速やかに温度の測定することが望ましい。好ましくは、温度の測定は 1m s 以内にする。

#### 【0111】

トランジスタ 117 の試験時は、定電流  $I_c$  は、チャンネル電流  $I_d$  が流れていないとときにダイオード Di に流す。トランジスタ 117 がオンしていない時に、定電流  $I_c$  を流してダイオード Di の端子間電圧 (トランジスタ 117 の e - c 端子間電圧) を測定する。

オペアンプ回路 (バッファ回路) 116 は、ダイオード Di の端子電圧  $V_i$  (端子 c - 端子 e) を出力する。

40

#### 【0112】

温度測定回路 115 を保持されている温度係数  $K$  と電圧  $V_i$  から、試験を実施しているトランジスタ 117 の温度  $T_j$  を求める。求められた温度  $T_j$  はコントローラ 111 に送られる。コントローラ 111 は、温度  $T_j$  が所定設定値以上になった場合、トランジスタ 117 が所定のストレス状態となったと判断して試験の停止などが停止すると低下する。

#### 【0113】

試験で劣化するのは主として、トランジスタ 117 内の接合部であることが多い。半導体そのものが劣化することではなく、トランジスタ 117 の接合部 (ボンディング、ダイボンドなど) が劣化し、接合部の抵抗値が高くなる。抵抗値が高くなることにより、電圧  $V_{ce}$  が高くなり、発熱してトランジスタ 117 の温度が上昇する。

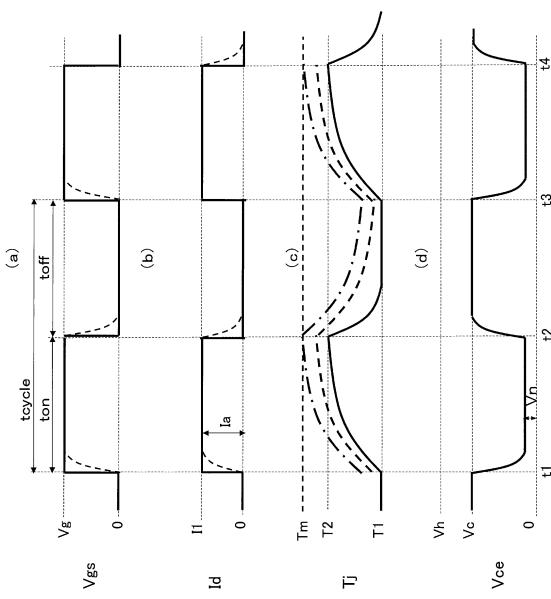

#### 【0114】

50

なお、半導体が劣化する場合は、トランジスタ 117 のゲート酸化膜（絶縁膜）の劣化である場合が多い。ゲート酸化膜の劣化が発生した場合は、酸化膜（絶縁膜）の短絡状態になり、電圧  $V_{ce}$  は下がる。または、トランジスタ 117 がオフ状態となり、トランジスタ 117 には電流は流れず、電圧  $V_{ce}$  は電源電圧の最大値まで上昇する。

#### 【0115】

温度  $T_j$  は、試験開始時は、最低温度  $T_1$  から最高温度  $T_2$  の間を変化する。試験によりトランジスタ 117 にストレスがかかると、トランジスタ 117 の  $V_{ce}$  電圧が変化し、通常は温度  $T_j$  が高くなる方向に変化する。

#### 【0116】

したがって、図 5 (c) に図示するように、最低温度は、温度  $T_1$  より上昇し、最高温度は  $T_m$  ( $T_{jmax}$ ) に近づく。本発明の半導体の試験方法では、試験の終了は下記のいずれかの条件で停止する。

- ・ 温度  $T_j$  が所定範囲内から外れた場合。

- ・ 電圧  $V_{ce}$  が所定の電圧範囲から外れた場合。

- ・ 熱抵抗が所定の範囲内から外れた場合。

図 1 の本発明の半導体試験装置は、所定のサージ電圧  $V_s$  を発生させてトランジスタ 117 の試験を実施することができる。

サージ電圧  $V_s$  の発生は、誘導リアクタンス回路 123 のいずれかのコイル  $L$  ( $L_1$ 、 $L_2$ 、 $L_3$ ) を選択することにより実施する。

#### 【0117】

誘導リアクタンス回路 123 には、一例としてコイル  $L_1$ 、コイル  $L_2$ 、コイル  $L_3$  を図示している。コイル  $L$  にはスイッチ  $S_L$  が接続され、スイッチ  $S_L$  がクローズすることにより、電流電源装置 121 が出力する定電流の経路にコイル  $L$  が挿入される。

#### 【0118】

サージ電圧  $V_s$  の大きさは、トランジスタ 117 がオフする時に流れている電流を  $I_a$  (A) とし、トランジスタ 117 のチャンネルに流れる電流が 0 (A) になるまでの時間を  $t_g$  ( $\mu$ 秒) とし、実回路の配線などによる等価的な誘導リアクタンスを  $L_s$  ( $\mu$ H) とすると、サージ電圧  $V_s$  (V) は、以下で示される。

$$V_s = -L_s \times I_a / t_g$$

#### 【0119】

コイル  $L$  のリアクタンス  $L_s$  に比例してサージ電圧  $V_s$  が大きくなる。したがって、トランジスタ 117 を使用する実回路で、リアクタンス  $L$  の容量を測定して、測定して得られたリアクタンスに設定することにより、実回路に近い試験条件でトランジスタ試験を実施することができる。

#### 【0120】

発生したサージ電圧、124b によって吸収することができる。したがって、発生させたサージ電圧のパルス幅は、所望の値になるように 124b で制御することができる。

#### 【0121】

以上の誘導リアクタンス回路 123 を使用すれば、トランジスタ 117 に印加されるチャンネル電圧  $V_{ce}$  は図 3 (c) の  $V_{ce}'$  となる。サージ電圧  $V_s$  はコイル  $L$  の選択、 $t_g$  時間の設定により設定できる。

#### 【0122】

図 3 はサージ電圧  $V_s$  を発生させて、サージ電圧  $V_s$  をトランジスタ 117 に印加する方法であった。またはサージ電圧  $V_s$  を発生させないでトランジスタ 117 の試験を行う方法である。

#### 【0123】

本発明は、図 1 に図示するようにスイッチ 124b (Ssb) を構成している。スイッチ 124a、124b はコントローラ 111 の制御によりオンオフ制御される。

#### 【0124】

スイッチ 124b がオンすると、試験回路の寄生コンデンサ (図示せず) にチャージさ

10

20

30

40

50

れた電荷による電流  $I_m$  がスイッチ 124b を介してグランド（接地電位）に流れる。

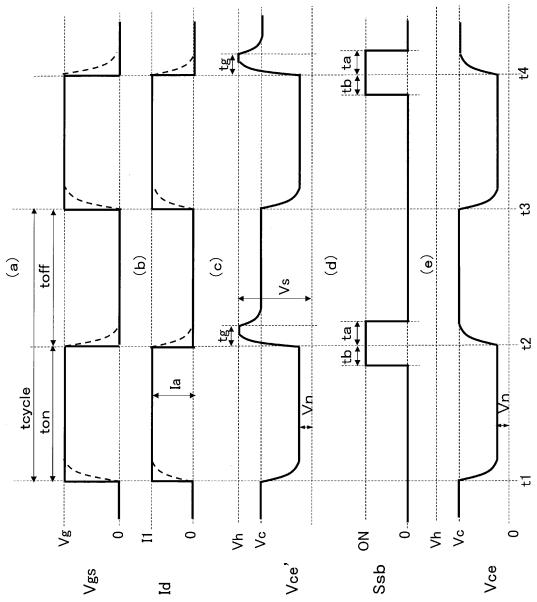

【0125】

図4(d)に図示するように、スイッチ Ssb はゲート電圧  $Vgs$  のオン時刻に対して  $t_n$  時間前にオンさせる。  $t_n$  時間は 10m秒以下 0m秒以上の時間である。好ましくは、1m秒以下 0m秒以上の時間である。

【0126】

図4(d)に図示するように、スイッチ Ssb はゲート電圧  $Vgs$  のオン時刻に対して  $t_m$  時間後にオンさせる。  $t_m$  時間は 0m秒以上 10m秒以下の時間である。好ましくは、0m秒以上 2m秒以下の時間である。

【0127】

スイッチ 124b がオンすると、コンデンサ（図示せず）にチャージされた電荷が放電される。したがって、図4(b)の突入電流  $I_s$  は発生せず。図4(e)に図示するように、安定したチャンネル電流  $I_d$  (=  $I_1$ ) がトランジスタ 117 に印加される。

図4は第2の実施例における半導体素子の試験方法の説明図である。図1に図示するようにスイッチ 124b (Ssb) を有している。

【0128】

スイッチ 124b がオンすると、コンデンサ（図示せず）にチャージされた電荷による電流  $I_m$  がスイッチ 124b を介してグランド（接地電位）に流れる。誘導リアクタンス回路 123 のスイッチ SL4 がオンのため、試験回路の誘導リアクタンスも小さい。

【0129】

図4(d)に図示するように、スイッチ Ssb はゲート電圧  $Vgs$  のオフ時刻に対して  $t_b$  時間前にオンさせる。スイッチ Ssb はゲート電圧  $Vgs$  のオフ時刻に対して  $t_a$  時間後にオフさせる。

【0130】

スイッチ 124b がオンすると、コンデンサ（図示せず）にチャージされた電荷が放電される。したがって、サージ電圧  $V_s$  は発生せず。図4(f)に図示するように、安定した  $V_{ce}$  電圧がトランジスタ 117 に印加される。

【0131】

図4(d)に図示するように、スイッチ Ssb はゲート電圧  $Vgs$  のオン時刻に対して  $t_n$  時間前にオンさせる。  $t_n$  時間は 10m秒以下 0m秒以上の時間である。好ましくは、1m秒以下 0m秒以上の時間である。

【0132】

図4(d)に図示するように、スイッチ Ssb はゲート電圧  $Vgs$  のオン時刻に対して  $t_m$  時間後にオンさせる。  $t_m$  時間は 0m秒以上 10m秒以下の時間である。好ましくは、0m秒以上 2m秒以下の時間である。

【0133】

スイッチ 124b がオンすると、コンデンサ（図示せず）にチャージされた電荷が放電される。したがって、図4(b)の突入電流  $I_s$  は発生せず。図4(e)に図示するように、安定したチャンネル電流  $I_d$  (=  $I_1$ ) がトランジスタ 117 に印加される。

【0134】

スイッチ 124b (Ssb) を所定タイミングでオンさせることにより、突入電流  $I_s$  の発生を抑制できる。スイッチ 124b をオンにすることにより、突入電流  $I_s$  を吸収し、突入電流  $I_s$  のパルス幅（印加時間）を制御することができる。

【0135】

実回路に基づく試験を行うためには、突入電流  $I_s$  を発生させて試験を行うことが適正である。トランジスタ 117 に流す突入電流  $I_s$  を実駆動状態に即して設定して試験を行うことにより、実施状態に応じた試験を行うことができる。

本発明の半導体試験装置は、電流電源装置 121a と電流電源装置 121b とを有することにより、精度よく、所定の突入電流  $I_s$  を発生させることができる。

【0136】

10

20

30

40

50

周期時間  $t_{cycle}$ 、オン時間  $t_{on}$  のゲート電圧  $V_{gs}$  が印加されることにより、トランジスタがオンオフ動作する。オンオフ動作にともなって、トランジスタにドレイン電流  $I_d$  (チャンネル電流) が流れる。

【0137】

トランジスタを現実に使用している状態を想定あるいは調査し、突入電圧  $I_s$  が発生するように試験装置を構成して、トランジスタ 117 に印加する電流を制御すればよい。

【0138】

図 6 は、本発明の突入電流  $I_s$  を発生させる方法の説明図である。トランジスタ 117 のチャンネルに流す試験電流  $I_d$  を図 6 (b) に示す。ベース電流  $I_1$  は電流電源装置 (Pa) 121a により定電流  $I_a$  としてトランジスタ 117 に供給される。

【0139】

トランジスタ 117 に供給される定電流  $I_a$  はスイッチ SWa 122a によりオンオフ制御される。また、オン時間  $t_{on}$  はトランジスタ 117 のゲート端子  $g$  に印加されるゲートオン電圧信号  $V_{gs}$  により規定される。

【0140】

$t_c$  の期間に、電流電源装置 121b から定電流  $I_b$  が outputされる。定電流  $I_b$  はスイッチ SWb 122b により印加時間が制御される。 $t_c$  期間は、スイッチ SWa とスイッチ SWb により制御あるいは設定される。

トランジスタ 117 には、電流電源装置 121a と電流電源装置 121b とが outputされる定電流が加算されて印加される。

【0141】

図 1 に図示するように、本発明の半導体試験装置は、第 1 の電流電源装置 (Pa) 121a と、第 2 の電流電源装置 (Pb) 121b とを具備する。また、第 1 の電流電源装置 121a が outputする定電流  $I_a$  をトランジスタ 117 に印加するスイッチ (SWa) 122a と、第 2 の電流電源装置 121b が outputする定電流  $I_b$  をトランジスタ 117 に印加するスイッチ (SWb) 122b とを具備する。

【0142】

スイッチ SWa 122a は、周期  $T_{cycle}$  の時間中、 $t_{on}$  の時間に定電流  $I_a$  をトランジスタ 117 に印加する。第 1 の電流電源装置 121a が定電流  $I_a$  を出力していない期間は、トランジスタ 117 のコレクタ端子  $c$  のコレクタ電圧は  $V_c$  に維持されるように制御する。

【0143】

第 2 の電流電源装置 121b が outputする定電流  $I_b$  は、第 1 の電流電源装置 121a が outputする定電流  $I_a$  と同期して、トランジスタ 117 に印加される。最初は、定電流  $I_a$  と定電流  $I_b$  は加算 (重畠) されてトランジスタ 117 に流れ、定電流  $I_b$  は  $t_c$  時間流れれる。

【0144】

突入電流  $I_s = I_a + I_b$  として、トランジスタ 117 の試験を実施する。図 6 では、 $I_1 = I_a$ 、 $I_2 = I_s = I_a + I_b$  としている。電流  $I_a$  の立上と電流  $I_b$  の立上は同時に、あるいは略一致させる。実際には、回路の容量成分などにより、電流波形は点線のようになる。ゲート端子に印加するオン電圧信号についても同様である。

【0145】

以上の実施例では、第 1 の電流電源装置 (Pa) 121a が定電流  $I_a$  を出力し、第 2 の電流電源装置 121b が定電流  $I_b$  を出力するとしたが、これに限定するものではない。

【0146】

図 6 (b) で図示する電流  $I_d$  を発生できるものであれば、いずれの電流電源装置であってもよい。たとえば、1 台の電流電源装置 121 で、定電流  $I_2$  を出力し、 $t_c$  時間の経過後、定電流  $I_1$  (A) を出力し、 $t_{on}$  の時間後、電流出力を 0 (A) とできればよい。

【0147】

10

20

30

40

50

スイッチ 124b (Ssb) を所定タイミングでオンさせることにより、突入電流  $I_s$  の発生を抑制できる。スイッチ 124b をオンにすることにより、突入電流  $I_s$  を吸収し、突入電流  $I_s$  のパルス幅 (印加時間) を制御することができる。

【0148】

なお、図 6 (b) の実線で図示する電流  $I_d$  波形は、回路などに存在する容量、トランジスタ 117 のオン抵抗の変化により波形が鈍り点線のような信号波形となる。

【0149】

突入電流  $I_s$  により、トランジスタ 117 に電流ストレスが印加される。突入電流  $I_s$  をトランジスタ 117 が使用される実回路と同等あるいは類似とすることにより、適正な試験を実施できる。

10

【0150】

図 1 の実施例では、主として電流電圧装置 121 が発生する電流を重畠等させることにより、突入電流  $I_s$  を発生させるとして説明したが、本発明はこれに限定するものではない。

【0151】

たとえば、第 1 の電流電源装置 (Pa) 121a と電圧電源装置 1 として定電圧  $V_1$  を発生させ、第 2 の電流電源装置 (Pb) 121b と電圧電源装置 2 として定電圧  $V_2$  を発生させ、定電圧  $V_1$  または定電圧  $V_2$  をトランジスタ 117 の端子 c に印加することにより、トランジスタ 117 に突入電流  $I_s$  を流すように構成してもよい。定電圧  $V_1$  は定電圧  $V_2$  より大きいという関係にする。

20

【0152】

定電圧  $V_1$  により、トランジスタ 117 に電流  $I_a$  がトランジスタ 117 に流れ、定電圧  $V_2$  の印加により電流  $I_b$  がトランジスタ 117 に流れる。したがって、定電圧  $V_1$  または定電圧  $V_2$  の加により、トランジスタ 117 に突入電流  $I_s$  が流すことができる。

【0153】

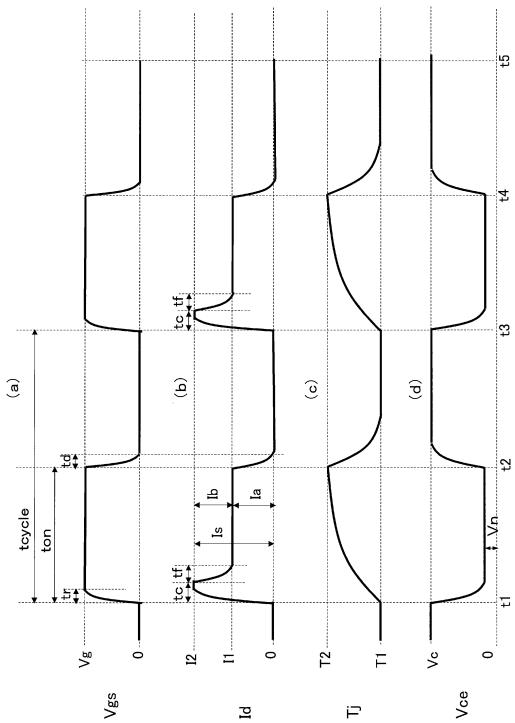

また、定電圧  $V_1$  を  $V_c$  電圧、定電圧  $V_2$  を  $V_h$  ( $V_s$ ) 電圧とすることにより、トランジスタ 117 にサージ電圧  $V_s$  を印加することができる。図 7 は、本発明の第 3 の実施例における半導体素子の試験方法の説明図である。図 7 において、電流電圧装置 121 により試験電流を発生させ、突入電流  $I_s$  を有する電流  $I_d$  がトランジスタ 117 に流れれる。

30

【0154】

以上のように、本発明は、試験するパワー半導体素子に突入電流  $I_s$  を容易に設定して試験を実施できる。したがって、パワー半導体素子に対して実際の使用環境、実際の使用回路を想定して信頼性評価することができる。

【0155】

図 8 は、本発明の第 4 の実施例における半導体素子の試験方法の説明図である。図 8 において、電流電圧装置 121 により試験電流を発生させ、図 8 (b) に図示するように突入電流  $I_s$  を有する電流  $I_d$  がトランジスタ 117 に流れれる。

【0156】

また、図 1 で説明したように、誘導リアクタンス回路 123 のコイル  $L$  を選択して、電流経路に挿入することにより、図 8 (d) に図示するように、サージ電圧  $V_s$  を発生させてトランジスタ 117 に印加する。

40

【0157】

以上のように、本発明は、試験するパワー半導体素子に突入電流  $I_s$ 、サージ電圧  $V_s$  を容易に設定して試験を実施できる。したがって、パワー半導体素子に対して実際の使用環境、実際の使用回路を想定あるいは実際の使用環境、実際の使用回路と同様にして信頼性評価することができる。

【0158】

図 9 は、第 2 の実施例における半導体試験装置の説明図である。図 1 に説明した第 2 の実施例との差異は、トランジスタ 117 に温度をセンシングするダイオード  $D_s$  が別途、

50

形成されている点である。他の構成、動作は図1の実施例で説明している構成、動作と同様であるので説明を省略する。

【0159】

図9において、トランジスタ117は温度をモニターするダイオードDsを内蔵している。センシングダイオードDsは、トランジスタ117を製造するプロセスで、トランジスタ117と同時に形成される。基本的には、ダイオードDsの半導体膜とトランジスタ117の半導体膜とは共通層で形成されている。したがって、トランジスタ117とダイオードDsの温度係数は同一である。

【0160】

定電流回路118の構造、動作などは図1で説明した定電流回路118と同様である。ダイオードDsには、定電流回路118が outputする定電流Icが供給される。オペアンプ116はダイオードDsの端子電圧を測定する。トランジスタ117の試験時に、ダイオードDsの端子電圧を測定して、Tjを求める。

図1のようにトランジスタ117のダイオードDiで、Tjを求める場合は、定電流Icは、チャンネル電流Idが流れていないう時にダイオードDiに流す。

【0161】

しかし、図9のように、センシングダイオードDsの場合は、トランジスタ117に電流Idが流れている時も、センシングダイオードDsに定電流Icを流し、センシングダイオードDsの端子電圧を測定することにより、温度Tjを求めることができる。

【0162】

しかし、センシングダイオードDsは半導体膜をトランジスタ117の半導体膜と同一プロセスで形成されている。したがって、トランジスタ117に電流Idが供給されている場合は、電位が不安定となる。したがって、電流Idが流れていないう時にセンシングダイオードDsの端子電圧を測定することが好ましい。

【0163】

温度測定回路115を保持されている温度係数Kと電圧Viから、試験を実施しているトランジスタ117の温度Tjを求める。求められた温度Tjはコントローラ111に送られる。コントローラ111は、温度Tjが所定設定値以上のなった場合、トランジスタ117が所定のストレス状態となつたと判断して試験の停止などが停止すると低下する。

【0164】

温度Tjは、試験開始時は、最低温度T1から最高温度T2の間を変化する。試験によりトランジスタ117にストレスがかかると、トランジスタ117のVce電圧が変化し、通常は温度Tjが高くなる方向に変化する。この温度の変化、変化量、変化速度等に基づいて、試験の終了などを判断する。他の部分は、図1あるいは他の実施例と同様あるいは類似であるので説明を省略する。

【0165】

図10は第3の実施例における半導体試験装置の説明図である。図1に説明した第1の実施例では、スイッチSWa、電流電源装置121aの第1の電流経路に配置され、スイッチSWb、電流電源装置121bの第2の電流経路に配置されている。

図10に示す第3の実施例における半導体試験装置では、定電流Iaを出力する電源装置121が配置されている。

【0166】

電流電源装置121(Pa)は、一定の条件で、最大あるいは所定の電圧Vmを設定でき、所定の定電流を出力できるように機能させることができる。電流電源装置121は、定電流を出力するだけではなく、設定した電圧Vm、定電流Iaを出力できる電源装置である。

【0167】

電流電源装置121に並列して、コンデンサ、電気二重層コンデンサあるいは蓄電池141を配置している。コンデンサ141等には、電流電源装置121が出力する電流Iaに伴う電圧あるいは設定された電圧Vmにより電荷がチャージされる。

10

20

30

40

50

## 【0168】

コンデンサ141は、スイッチSCに試験回路に接続と非接続を切り替えることができる。また、図1に図示するように、複数の容量の異なるコンデンサCを配置し、それぞれのコンデンサCをスイッチSCで選択できるように構成してもよいことは言うまでもない。

## 【0169】

スイッチSWa122は電流制御回路114で制御される。電流制御回路114、ゲート信号制御回路112、電流電源装置121は、コンピュータ(PC)111で制御される。

電流電源装置Pa121は定電流 $I_1 = I_a$ を出力し、スイッチSWaがオンすることにより、定電流 $I_a$ がトランジスタ117に印加される。

他の構成、動作は図1の実施例で説明している構成、動作と同様であるので説明を省略する。

## 【0170】

ゲートドライバ回路113から出力される $V_{gs}$ 電圧により、トランジスタ117はオンオフ動作し、トランジスタ117がオンしている期間にトランジスタ117のチャネル間に電流 $I_d$ が流れる。

## 【0171】

トランジスタ117がオンするトランジスタ117のチャネル電圧 $V_{ce}$ が順方向電圧 $V_n$ まで低下する。トランジスタ117がオフすると $V_{ce}$ 電圧は、電源電圧まで上昇する。

## 【0172】

図6、図7で説明した実施例では、電流 $I_d$ は第1の電流電源装置121aで定電流 $I_a$ を発生させ、第2の電流電源装置121bで定電流 $I_b$ を発生させるとした。したがって、2台の電流電源装置121を操作することに、トランジスタ117に流す試験電流 $I_d$ を発生させていた。トランジスタ117の試験で使用する突入電流 $I_s$ は、定電流 $I_a$ と定電流 $I_b$ を重畠させることにより発生させていた。

図10に示す第3の実施例の半導体試験装置は、試験で使用する突入電流 $I_s$ を電流電源装置121とコンデンサ141で発生させる。

## 【0173】

電流電源装置121を動作させ、スイッチSWaとオンさせると、電源装置121の端子電圧 $V_m$ が上昇し、電圧 $V_m$ の大きさにより、コンデンサ141に電荷がチャージされる。

## 【0174】

スイッチSSbをオフ状態、スイッチSSaがオン状態とする。試験を行うトランジスタ117のゲート端子gにオン電圧信号 $V_{gs}$ が印加されると、トランジスタ117がオンし、トランジスタ117のチャネルに電流 $I_d$ が流れる。

## 【0175】

図7(b)に図示するように、トランジスタ117にゲート電圧信号 $V_{gs}$ が印加されると、電流電源装置121は、定電流 $I_a$ を流す。また、コンデンサ141に充電された電荷は電流 $I_b$ となり、トランジスタ117のチャネルに流れる。

## 【0176】

突入電流 $I_s = I_a + I_b$ となり、試験のトランジスタ117に電流ストレスを印加される。トランジスタ117がオフすると、コンデンサ141には再び電荷が充電される。

## 【0177】

突入電流 $I_s$ の定電流 $I_a$ は電流電源装置121が outputする電流値の設定を調整する。突入電流 $I_s$ の定電流 $I_b$ はコンデンサ(電荷蓄積装置)114の容量値を設定する。コンデンサ141は可変容量タイプとすることにより、電流 $I_b$ の値を変更することができる。突入電流の傾斜(変化速度)は、たとえば、誘導リアクタンス回路123のスイッチSL4部に抵抗素子を配置または形成し、前記抵抗素子の抵抗値により、傾斜(変化速度)を変更することができる。

突入電流  $I_s$  は、試験を行うトランジスタ 117 の仕様に基づいて決定する。また、トランジスタ 117 が使用される回路構成により決定する。

【0178】

実回路に基づく試験を行うためには、突入電流  $I_s$  を発生させて試験を行うことが適正である。トランジスタ 117 に流す突入電流  $I_s$  を実回路での実駆動状態に即して設定して試験を行うことにより、実施状態に応じた試験を行うことができる。

【0179】

図 10 では 1 つのコンデンサ 141 を図示しているが、本発明はこれに限定するものではない。たとえば、複数の容量が異なるコンデンサ 141 を配置し、前記複数の容量の異なるコンデンサ 141 のうち少なくとも 1 つ以上のコンデンサ 141 を選択回路（図示せず）で選択できるように構成してもよい。選択するコンデンサ 141 を変更あるいは設定することにより、突入電流  $I_s$  の大きさ、印加時間を変更できる。

【0180】

また、図 10 では 1 つの電圧  $V_m$  の電圧発生装置を図示しているが、本発明はこれに限定するものではない。たとえば、複数の発生電圧が異なる電圧発生装置を配置し、前記電圧発生装置が発生する電圧を順次選択できるように構成してもよい。選択する電圧を変更あるいは設定することにより、サージ電圧  $V_s$  の大きさ、印加時間を変更できる。

【0181】

以上の事項は本明細書の他の実施例にも適用できる。また、他の実施例は相互に組み合わせることができることは言うまでもない。他の事項については、他の実施例で説明しているので説明を省略する。

【0182】

なお、スイッチ  $S_{sb}$  のオンオフにより、突入電流  $I_s$  、サージ電圧  $V_s$  を抑制あるいは防止することは、図 3 、図 4 で説明しているので説明を省略する。以上の事項は、図 1 、図 10 で説明した突入電流  $I_s$  を印加して実施する試験方法と組み合わせることができることは言うまでもない。

【0183】

以上の実施例では、1 つのトランジスタ 117 の試験を行う実施例であった。しかし、本発明の半導体試験装置および半導体素子の試験方法では、これに限定するものではない。

【0184】

図 11 は、本発明の第 4 の実施例における半導体試験装置の説明図である。図 11 は 2 個のトランジスタ 117 ( $117s$ 、 $117m$ ) を直列に接続して試験を行う場合の実施例である。

【0185】

トランジスタ 117m はオンオフさせて試験を行うトランジスタである。トランジスタ 117s はゲート端子  $g$  をエミッタ端子  $e$  と接続して、ダイオード接続状態としている。

トランジスタ 117m 、トランジスタ 117s の両方には電流  $I_d$  が流れるため、トランジスタ 117m とトランジスタ 117s とは同時に試験が実施される。

他の構成、動作は、本明細書の実施例で説明しているので説明を省略する。

【0186】

以上の実施例は、1 つのトランジスタ 117 に対して、1 台以上の電流電源装置 121 を配置して半導体試験を行う構成であった。そのため、多数のトランジスタ 117 を試験しようとすると多くの電流電源装置 121 を必要とし、多数の電流電源装置 121 を配置するためのコストが高くなるという問題点があった。

【0187】

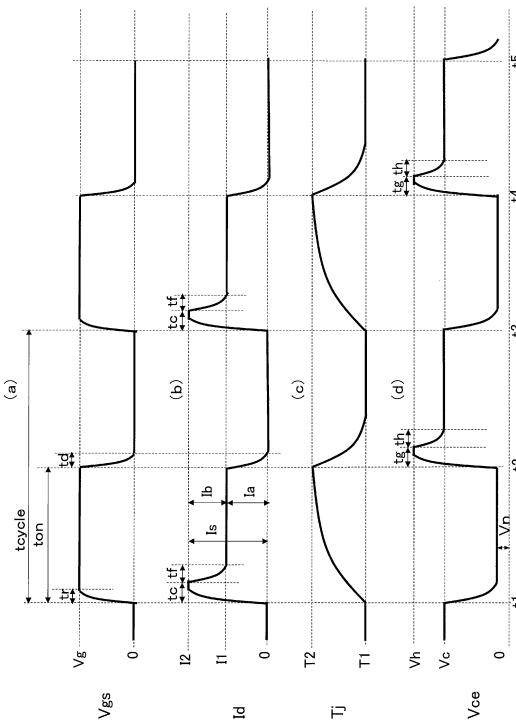

図 12 は、本発明の第 5 の実施例における半導体試験装置の説明図である。図 12 において、電流電源装置 121 に並列して、複数のトランジスタ 117 (トランジスタ 117 Q1 ~ トランジスタ 117 Qn) が接続されている。

【0188】

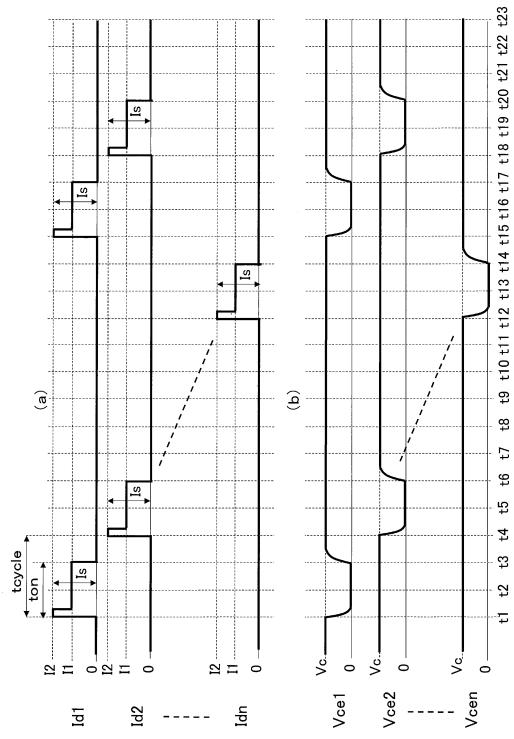

図 13 は、図 12 の動作を説明する本発明の第 5 の実施例における半導体素子の試験方

10

20

30

40

50

法の説明図である。なお、図13はトランジスタ117に突入電流 $I_s$ を流す実施例で説明するが、これに限定するものでない。たとえば、図3(b)で説明したように、トランジスタ117のオン時間に同期して電流 $I_d$ を流す試験方法でもよい。また、図8(d)に図示するように、周期的にサージ電圧 $V_s$ を印加する方法であってもよい。

#### 【0189】

図12において、電流電源装置121a、電流電源装置121bのうち少なくともいずれかは電流/電圧を発生する。スイッチ $S_{t1}$ ～スイッチ $S_{tn}$ は順次オンする。電流電源装置121a、電流電源装置121bの電源容量が必要電力を有する場合は、スイッチ $S_{t1}$ ～スイッチ $S_{tn}$ のうち、複数のスイッチが同時に、かつ順次オンする。

#### 【0190】

図13(a)に図示するように、スイッチ $S_{t1}$ (151s1)～スイッチ $S_{tn}$ (151s $n$ )がオンすることにより、トランジスタ117に定電流 $I_{d1}$ ～定電流 $I_{dn}$ が流れる。たとえば、定電流 $I_d$ の印加時間は $t_{on}$ であり、定電流 $I_{d1}$ と定電流 $I_{d2}$ とは時間 $t_{cycle}$ の間隔で順次トランジスタ117に印加される。トランジスタ117はオンすることにより、トランジスタ117のチャンネル電圧 $V_c$ が順次変化する(図13(b))。

#### 【0191】

したがって、定電流 $I_{d1}$ と定電流 $I_{d2}$ とは時間的に重なりがない。そのため、電流電源装置121の出力容量は、1つのトランジスタ117の試験に必要とする出力容量でよい。

他の構成、動作は他の実施例で説明している構成、動作と同様であるので説明を省略する。

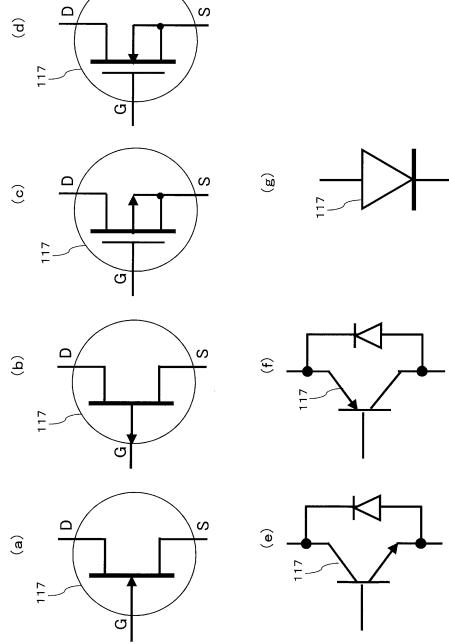

#### 【0192】

本発明の実施例において、トランジスタ117は、IGBTを例示して説明したが、これに限定するものではない。たとえば、NチャンネルのJFET(図14(a))、PチャンネルのJFET(図14(b))、NチャンネルのMOSFET(図14(c))、PチャンネルのMOSFET(図14(d))、NチャンネルのバイポーラFET(図14(e))、PチャンネルのバイポーラFET(図14(f))であっても良いことは言うまでもない。

#### 【0193】

また、3端子のデバイスに限定されるものではなく、図14(g)に図示するダイオードなどの2端子素子であってもよい。2端子素子では、ゲート電圧信号 $V_{gs}$ は必要がない。電流電圧装置121で定電流 $I_d$ を流して試験することにより、本発明の半導体試験装置、半導体素子の試験方法を適用できることは言うまでもない。

#### 【0194】

以上、本明細書において、実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。また、本明細書、図面で記載した事項は、相互に組み合わせることは言うまでもない。

#### 【産業上の利用可能性】

#### 【0195】

本発明は、上記事情に鑑みてなされたものであり、実際の環境下での故障モードに近いストレスを効率よく再現でき、高い信頼性でパワー半導体素子の評価を行うことができるパワーサイクル試験装置および試験方法を提供することができる。

#### 【符号の説明】

#### 【0196】

111 コンピュータ(コントローラ)

112 ゲート信号制御回路

113 ゲートドライバ回路

114 電流制御回路

10

20

30

40

50

- |       |              |

|-------|--------------|

| 1 1 5 | 温度測定回路       |

| 1 1 6 | オペアンプ回路      |

| 1 1 7 | パワートランジスタ    |

| 1 1 8 | 定電流回路        |

| 1 2 1 | 電流電源装置       |

| 1 2 2 | スイッチ回路       |

| 1 2 3 | 誘導リアクタンス回路   |

| 1 2 4 | スイッチ回路       |

| 1 2 5 | 可変抵抗器        |

| 1 2 6 | 容量リアクタンス回路   |

| 1 3 1 | 制御ラック        |

| 1 3 2 | 電源装置         |

| 1 3 4 | 加熱冷却プレート     |

| 1 3 5 | 循環水パイプ       |

| 1 3 6 | チラー（冷却・加温装置） |

| 1 4 1 | コンデンサ        |

| 1 5 1 | 寄生容量リアクタンス   |

| 1 5 2 | 寄生誘導リアクタンス   |

【 図面 】

【 図 1 】

【図2】

10

20

30

40

【図3】

【図4】

【図5】

【図6】

10

20

30

40

50

【 図 7 】

【 図 8 】

【 四 9 】

【図10】

【図 1 1】

【図 1 2】

10

20

30

40

【図 1 3】

【図 1 4】

50

【図 1 5】

【図 1 6】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開平07-027817 (JP, A)

特開2010-175509 (JP, A)

特開平06-281693 (JP, A)

特開2018-096755 (JP, A)

特開昭61-108978 (JP, A)

特開平11-014694 (JP, A)

特開2013-088146 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- G01R 31/26 - 31/3193

H01L 21/64 - 21/66