(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6192065号

(P6192065)

(45) 発行日 平成29年9月6日(2017.9.6)

(24) 登録日 平成29年8月18日(2017.8.18)

(51) Int.Cl.

G06F 1/12 (2006.01)

G06F 13/42 (2006.01)

F 1

G06F 1/12

G06F 13/42 350A

G06F 13/42 350B

請求項の数 38 (全 15 頁)

(21) 出願番号 特願2015-519327 (P2015-519327)

(86) (22) 出願日 平成25年6月20日 (2013.6.20)

(65) 公表番号 特表2015-522188 (P2015-522188A)

(43) 公表日 平成27年8月3日 (2015.8.3)

(86) 國際出願番号 PCT/GB2013/051608

(87) 國際公開番号 WO2014/001765

(87) 國際公開日 平成26年1月3日 (2014.1.3)

審査請求日 平成28年6月20日 (2016.6.20)

(31) 優先権主張番号 1211425.2

(32) 優先日 平成24年6月27日 (2012.6.27)

(33) 優先権主張国 英国(GB)

(73) 特許権者 513183153

ノルディック セミコンダクタ アーエス

アー

N o r d i c S e m i c o n d u c t o

r A S A

ノルウェー王国、エヌ-7004 トロン

ハイム、オットー ニールセンス ヴェー

グ 12

(74) 代理人 110001807

特許業務法人磯野国際特許商標事務所

(72) 発明者 イエアルテ、マルクス バッカ

ノルウェー王国、エヌ-0476 オスロ

、ベンツェブルガータ 5

最終頁に続く

(54) 【発明の名称】クロック・ドメイン間のデータ転送

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタル・システムにおいて、データ信号を第1クロック・ドメインから第2クロック・ドメインに転送する機構であつて、

該第1クロック・ドメインは、該第2クロック・ドメイン内の第2クロックの周波数よりも低い周波数の第1クロックを有し、

該機構は、

該データ信号を該第1クロック・ドメインから該第2クロック・ドメインに最初に転送し、

該第1クロックでの所定の遷移が、該データ信号を最初に転送した後の所定期間に内に発生するかどうかを、該第2クロックからクロック供給される検出手段を用いて検出し、そして、

該検出手段が、該第1クロックでの該所定の遷移を該所定期間に内に検出した場合、該データ信号を該第1クロック・ドメインから該第2クロック・ドメインへ再度転送する、ように構成されていることを特徴とする機構。

## 【請求項 2】

前記検出される所定の遷移が、正の遷移であること、を特徴とする請求項1に記載の機構。

## 【請求項 3】

前記データ信号が前記第1クロック・ドメインから前記第2クロック・ドメインへ前

10

20

記検出手段を経由しないで転送されること、を特徴とする請求項 1 又は 2 に記載の機構。

**【請求項 4】**

前記第 1 クロック・ドメインが第 1 バスを含み、前記第 2 クロック・ドメインが第 2 バスを含み、かつ、データは、該第 1 バスから該第 2 バスに最初に転送され、かつ、必要と判断された場合引き続いて転送されること、を特徴とする請求項 1、2、又は 3 に記載の機構。

**【請求項 5】**

前記第 1 バス、及び第 2 バスは、少なくとも 8 ビットであること、を特徴とする請求項 4 に記載の機構。

**【請求項 6】**

前記検出手段は、エッジ検出器を含むこと、を特徴とする、請求項 1 ~ 5 のいずれかの請求項に記載の機構。

**【請求項 7】**

前記検出は、前記第 2 クロックに基づく前記第 1 クロックの離散的サンプリングを含むこと、を特徴とする、請求項 1 ~ 6 のいずれかの請求項に記載の機構。

**【請求項 8】**

前記検出手段は、前記離散的サンプリングの複数のステップをカウントする手段を有すること、を特徴とする、請求項 7 に記載の機構。

**【請求項 9】**

前記離散的サンプリングの周波数が前記第 2 クロックの周波数に等しいこと、を特徴とする請求項 7 又は 8 に記載の機構。

**【請求項 10】**

前記所定期間は、前記第 2 クロックの 1 ~ 16 サイクルの間にであること、を特徴とする、請求項 1 ~ 9 のいずれかの請求項に記載の機構。

**【請求項 11】**

前記検出手段は、前記所定期間内のサイクル数をカウントする手段を備えること、を特徴とする、請求項 10 に記載の機構。

**【請求項 12】**

前記カウントする手段は、前記第 2 クロックによってクロック供給されること、を特徴とする、請求項 8 又は 11 項に記載の機構。

**【請求項 13】**

前記検出は、前記第 2 クロックの立ち上がりエッジで行われること、を特徴とする、請求項 1 ~ 12 のいずれかの請求項に記載の機構。

**【請求項 14】**

前記第 2 クロックの周波数は、前記第 1 クロックの周波数の少なくとも 4 倍の周波数であること、を特徴とする、請求項 1 ~ 13 のいずれかの請求項に記載の機構。

**【請求項 15】**

前記検出手段は、入力として前記第 1 クロックを有すること、を特徴とする、請求項 1 ~ 14 のいずれかの請求項に記載の機構。

**【請求項 16】**

前記検出手段は、フリップフロップを含むこと、を特徴とする、請求項 1 ~ 15 のいずれかの請求項に記載の機構。

**【請求項 17】**

前記所定期間を開始するための手段を含むこと、を特徴とする、請求項 1 ~ 16 のいずれかの請求項に記載の機構。

**【請求項 18】**

前記データ信号を記憶する手段を備えること、を特徴とする、請求項 1 ~ 17 のいずれかの請求項に記載の機構。

**【請求項 19】**

前記最初に転送されたデータ信号が前記第 2 クロック・ドメインによって読み取られ

10

20

30

40

50

ることを禁止する手段を備えること、を特徴とする、請求項 1 ~ 18 のいずれかの請求項に記載の機構。

**【請求項 20】**

デジタル・システムにおいてデータ信号を第1クロック・ドメインから第2クロック・ドメインへ転送するための方法であつて、

該第1クロック・ドメインが該第2クロック・ドメイン内の第2クロックの周波数よりも低い周波数の第1クロックを有し、

該データ信号を該第1クロック・ドメインから該第2クロック・ドメインに最初に転送するステップと、

所定の遷移が該第1クロックで発生するかどうかを、該第2クロックからクロック供給される検出手段を用いて、該データ信号を最初に転送した後の所定期間中、検出するステップと、そして、

該検出手段が該第1クロックでの該所定の遷移を該所定期間内に検出した場合に、該データ信号を該第1クロック・ドメインから該第2クロック・ドメインへ、再度転送するステップと、

を含んでいることを特徴とする方法。

**【請求項 21】**

前記検出される所定の遷移は、正の遷移であること、を特徴とする、請求項 20 に記載の方法。

**【請求項 22】**

前記データ信号を前記第1クロック・ドメインから、前記第2クロック・ドメインへ前記検出手段を経由しないで転送するステップを含むこと、を特徴とする、請求項 20 又は 21 に記載の方法。

**【請求項 23】**

前記第1クロック・ドメインは第1バスを含み、前記第2クロック・ドメインは第2バスを含み、該第1バスから該第2バスへ、データを最初に転送し、必要と判断される場合、引き続き転送するステップを含むこと、を特徴とする、請求項 20、21 又は 22 に記載の方法。

**【請求項 24】**

前記第1バス及び前記第2バスは、少なくとも 8 ビットであること、を特徴とする、請求項 23 に記載の方法。

**【請求項 25】**

前記検出手段は、エッジ検出器を含むこと、を特徴とする、請求項 20 ~ 24 のいずれかに記載の方法。

**【請求項 26】**

前記検出は、前記第2クロックに基づく前記第1クロックの離散的サンプリングを含むこと、を特徴とする、請求項 20 ~ 25 のいずれかに記載の方法。

**【請求項 27】**

前記検出するステップは、前記離散的サンプリングの複数のステップをカウントすること、を特徴とする、請求項 26 に記載の方法。

**【請求項 28】**

前記離散的サンプリングの周波数が前記第2クロックの周波数に等しいこと、を特徴とする、請求項 26 又は 27 に記載の方法。

**【請求項 29】**

前記所定期間は、前記第2クロックの 1 ~ 16 サイクルの間にであること、を特徴とする、請求項 20 ~ 28 のいずれかに記載の方法。

**【請求項 30】**

前記検出するステップは、前記所定期間内のサイクル数をカウントするステップを含むこと、を特徴とする、請求項 29 に記載の方法。

**【請求項 31】**

10

20

30

40

50

前記カウントするステップは、前記第2クロックによってクロック供給されること、を特徴とする、請求項27又は30に記載の方法。

【請求項32】

前記検出は、前記第2クロックの立ち上がりエッジで行われること、を特徴とする、請求項20～31のいずれかに記載の方法。

【請求項33】

前記第2クロックの周波数は、前記第1クロックの周波数の、少なくとも4倍の周波数であること、を特徴とする、請求項20～32のいずれかに記載の方法。

【請求項34】

前記検出手段は、入力として前記第1クロックを有していること、を特徴とする、請求項20～33のいずれかに記載の方法。 10

【請求項35】

前記検出手段はフリップフロップを含むこと、を特徴とする、請求項20～34のいずれかに記載の方法。

【請求項36】

前記所定期間を開始するステップを含むこと、を特徴とする、請求項20～35のいずれかに記載の方法。

【請求項37】

前記データ信号を記憶するステップを含むこと、を特徴とする、請求項20～36のいずれかに記載の方法。 20

【請求項38】

前記最初に転送するステップで最初に転送されたデータ信号が前記第2クロック・ドメインによって読みだされることを禁止するステップを含むこと、を特徴とする、請求項20から37のいずれかに記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デジタル・システム、特に、クロック・ドメインが同期されていないデジタル・システムにおいて、クロック・ドメイン間でデータ信号を転送するためのシステム及び方法に関する。 30

【背景技術】

【0002】

無線(例えば、Bluetooth(登録商標))システムなどの各種電子システムの多くでは、異なる周波数で動作するが、少なくとも散発的に相互通信が必要な複数のクロック・ドメインが存在する。例えば、中央プロセッサは高い周波数で動作するが、接続される1つ又は複数の周辺機器は低周波数で動作する場合がある。また、該クロック・ドメインの一つは、非アクティブな期間、例えば、スリープ・モード又はスタンバイ・モードに入ることがある。これは、未使用中に電力を節約するためである。このドメインは、通常高速なクロック・ドメインであり、低速クロック・ドメインは、この期間中はタイマとして使用されている。このような期間中には、2つのクロック・ドメイン間の通信はない。しかし、前記クロック・ドメインの一つがスリープ・モード又はスタンバイ・モードを終了するとき、該クロック・ドメインは、多くの場合、該低速クロック・ドメインと通信する必要がある。さらに、前記高速及び低速クロック・ドメインは、必ずしも相互の同期をとらなくてもよい。

【0003】

周波数が異なるクロック・ドメインを含むシステムでは、「ハンドシェイク」手順を使用することが知られている。該手順では、該クロック・ドメイン間でパラメータを交換して、低速クロック・ドメインが、高速クロック・ドメインへの転送中は、転送するデータ信号を変更しないことを、例えば、ビジー・フラグの使用によって保証する。これは、信号の低速クロック・ドメインからの転送を、低速クロック・ドメインの安全な期間、す 40

50

なわち、低速クロック・ドメインでの遷移（クロックの0から1への変化）から離れている時に、かつ、低速クロック・ドメインが転送するデータ信号を変更しない期間に行い、該信号の破壊又は該システムの準安定状態を回避するために必要である。この理由は、低速クロック・ドメイン内の値は、通常、低速クロックの遷移時に変化するからである。しかし、既知のハンドシェイク手順は比較的速度が遅い。この理由は、クロック・ドメイン間の同期を確立するために、該手順が低速クロック・ドメインの複数のサイクルを必要とするからである。速度が遅いだけでなく、かなりの量の電力を消費する。その理由は、該手順の間、高速クロック・ドメインが動作を継続する必要があるからである。また、多くのアプリケーションでは、低速クロック・ドメイン内の信号、例えば、継続的なカウントが必要なタイマを凍結することは望ましくない。この問題に対する既知の解決策は、補助的なシャドウ・レジスタを低速クロック・ドメイン内に設け、フラグと組み合わせることである。該フラグは、高速クロック・ドメインに、どのシャドウ・レジスタ・バンクが安定していると該高速クロック・ドメインが考えればよいかを、知らせる。しかし、これによって必要な論理量がかなり増加する。

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の目的は、異なる周波数の2つのクロック・ドメイン間の通信のための、改良されたシステム及び方法を提供することである。

【課題を解決するための手段】

【0005】

第1の側面から見ると、本発明は、デジタル・システムにおいて、データ信号を第1クロック・ドメインから第2クロック・ドメインへ転送するための機構を提供する。該第1クロック・ドメインは、該第2クロック・ドメイン内の第2クロックの周波数よりも低い周波数の第1クロックを有する。該機構は、

該データ信号を該第1クロック・ドメインから該第2クロック・ドメインに転送し、

所定の遷移が該第1クロックで所定期間内に発生するかどうかを、該第2クロックからクロック供給される検出手段を用いて検出し、そして、

該検出手段が該第1クロックでの該所定の遷移を該所定期間内に検出した場合、該データ信号を該第1クロック・ドメインから該第2クロック・ドメインへ再度転送する、よう構成されている。

【0006】

本発明は、また、デジタル・システムにおいて、データ信号を第1クロック・ドメインから第2クロック・ドメインへ転送するための方法であって、該第1クロック・ドメインが該第2クロック・ドメイン内の第2クロックの周波数よりも低い周波数を持つ第1クロックを有する。該方法は、

該第1クロック・ドメインからのデータ信号を該第2クロック・ドメインに転送するステップと、

所定期間内に所定の遷移が該第1クロックで発生するかどうかを、該第2クロックからクロック供給される検出手段を用いて検出するステップと、そして、

該検出手段が該所定の遷移を該第1クロックにおいて該所定期間内に検出した場合、該データ信号を該第1クロック・ドメインから該第2クロック・ドメインへ再び転送するステップと、を含んでいる。

【0007】

したがって、ハンドシェイク及び／又はビジー・フラグを使用する代わりに、本願発明に従い、前記データ信号は、単純に第1クロック・ドメインから第2クロック・ドメインへ転送されるが、クロックの遷移が該第1クロックにおいて該所定期間内に発生したかどうかについて確認が実行される。該遷移が検出された場合、該第1クロック・ドメインからの該データ信号を該第2クロック・ドメインへ再び転送し、そうでない場合、該信号の最初の転送が「安全」であった、すなわち、準安定状態のリスクはないとみなされる。

10

20

30

40

50

出願人は、上記の結果、データ信号の高速な転送を該第1クロック・ドメインから該第2クロック・ドメインに対して実行できたことを評価している。その理由は、該第2クロックによってクロック供給されている該第1クロックによって確認が行われるからである。例えば、ハンドシェイクを含む既知の機構では、同期時間及び転送時間は一般的には少なくとも第1クロックの2サイクル、すなわち、2低速クロック・サイクルであるが、これと比較して、本発明の実施形態における同期時間及び転送時間は、第2クロック数サイクル、すなわち、高速クロック、数サイクル相当に短くすることができる。第1クロックの遷移に続く前記データ信号の転送は、所定期間の終了時、例えば、第2クロックの対応する遷移になる可能性があるが、好ましくは、該第2クロックの後続する遷移のときに起きた方がよい。

10

#### 【0008】

前記検出手段の設定は、正及び／又は負の遷移を検出するように設定することができる。すなわち、第1クロック・ドメインにおけるデータ値は、使用されるシステムと実装技術に応じて、第1クロックの正及び負の遷移の一方又は両方において変化することができる。しかし、一連の実施形態では、検出される遷移は正の遷移とする。

#### 【0009】

前記第1クロックの確認を行う目的は、該クロックのサイクルが、一つの遷移、すなわち、0から1への正の遷移又は1から0への負の遷移から離れていて、第1クロック・ドメインから第2クロック・ドメインへのデータ信号の最初の転送が該第1クロックのサイクルにおける遷移と同時に起こらなかったことを確認するためである。この理由は、第1クロック・ドメインにおけるデータ値が、システムの実装技術に応じて、第1クロックの前記正及び負の遷移の一方又は両方において変更されるので、この時点で、すなわち、該第1クロックが変化している間に、該第1クロック・ドメインから値を転送すると、データの破壊又は準安定状態につながる可能性があるからである。

20

#### 【0010】

出願人は、前記第1クロックの確認によって、前記データ信号が安全に転送されていることを確認できるので、データ信号の最初又は後続の転送が、第1クロックである低速クロックのサイクルの安全な区間で起きることを評価した。いくつかの実施形態では、前記データ信号が第1クロック・ドメインから第2クロック・ドメインへ前記装置内の同期用構成要素、すなわち、検出手段のどれをも経由しないで転送される。また、該データ信号を該第2クロック・ドメインに同期させる必要もない。実施形態の特定の組では、第1クロック・ドメインから第2クロック・ドメインへのデータ信号の転送の間に1クロック・サイクルの時間遅延を引き起こす要因は存在しない。

30

#### 【0011】

上記は、単一のビット信号に対してある程度有利であるが、マルチ・ビット・バスに対して顕著な利点がある。この理由は、バス全体の信頼性の高い転送を第1クロックに対する確認に基づいて行うことができるからである。したがって、実施形態の一つの組では、第1クロック・ドメインが第1バスを含み、第2クロック・ドメインが第2バスを含み、かつ、データは第1バスから第2バスに転送される。該転送には、最初の転送及び、必要と判断された場合後続の転送が実行される。これの意味するところは、本発明の実施形態では、従来技術でクロック・ドメインの同期のために一般的に使用されていた、直列接続のフリップフロップ又は他の機構に起因する待ち時間を、追加する必要がないということである。

40

#### 【0012】

本発明のいくつかの実施形態では、データ・バスは、例えば、少なくとも8、16、又は32ビットを含んでいるが、当然のことながら、該バスは、任意の数の複数ビットを含んでよい。

#### 【0013】

更に有利な消費電力低減は、より迅速な転送によって実現することができる。この迅速な転送により、1つ又は両方のクロックがより迅速にスリープ状態に入ることが、適切

50

な場合に可能になる。例えば、公知のハンドシェイク手順は、完了するために複数の低速クロック・サイクルを必要とする。この間にも高速クロックは動作し続いている。これによって大量の不必要的電力が消費される可能性がある。特に、低速クロック・ドメインが低電力、低周波数のクロックを含み、高速クロック・ドメインが高電力である場合は、大量の不必要的電力消費の可能性が高い。上記は、低電力デバイスでの一般的な構成である。

#### 【 0 0 1 4 】

第1クロックにおける前記所定の遷移の確認は、前記所定期間を通じて行うことができる。ただし、実施形態の一つの組では、前記検出には、他のクロック、好ましくは、第2クロックに基づいた第1クロックの離散的サンプリングが含まれる。これによって、いくつかの実施形態では、データ信号を、必要に応じて、可能な限り迅速に再転送することが可能になる。すなわち、該離散的サンプリングによって、第1クロックの該所定の遷移を発生直後に検出することができ、データ信号をこの検出後に転送することができるようになる。実施形態の1つの組では、検出手段は、エッジ検出器、すなわち、正エッジ検出器を含む。これによって、例えば、離散的サンプリングの各時点において、第1クロックの値を第1クロックの前の値と比較することができ、第1クロックの遷移が該サンプリング期間に発生した場合は、検出することができるようになる。該エッジ検出器は、上述のように、都合よく、第2クロックによってクロック供給される。

#### 【 0 0 1 5 】

第1クロックでの遷移の検出は、一定の時間を必要とする。第1クロックの遷移は検出手手段に入力されなければならないで、結果として得られる論理信号群は、該検出手手段及び該信号群によって動作する任意の他の構成要素を通じて転送され、それによって第1クロック・ドメインと第2クロック・ドメイン間のデータ信号の転送が実行される。一般的に、前記検出手手段が第1クロックの遷移を検出するための所定期間は、第1クロック・ドメイン内の信号の変化が有効な値で安定するために要する時間、及び、該クロック遷移が該検出手手段を介して伝播するために要する時間よりも長い。例えば、離散的サンプリングのサンプリング点の数は、一般に、上記論理信号を必要な構成要素を経由して伝搬するために要する時間に関係する。実施形態の一つの組では、該所定期間は第2クロックの1～16サイクルの間に相当し、例えば、第2クロックの2～8サイクル、例えば、第2クロックの4サイクル分である。しかし、該所定期間が、第2クロックのサイクルの整数倍に相当する必要はない。例えば、異なるクロックによりクロック供給される場合がある。遷移が該所定期間内に検出されなかった場合、確実に想定できることは、第1クロック・ドメインから第2クロック・ドメインへのデータ信号の初期転送が、第1クロックの遷移と一緒に起きたということである。

#### 【 0 0 1 6 】

前記所定期間の経過は、任意の適切なタイミング機構、例えば、タイマ又はカウンタにより計時することができる。しかしながら、上述のように、いくつかの実施形態では、第1クロックの遷移の検出は多数のステップを含み、及び／又は多数の第2クロックのサイクルに亘って実行される。したがって、好ましくは、該検出手手段は、前記離散的サンプリングの複数のステップ及び／又は該所定期間のサイクル数をカウントする手段を備える方がよい。これは、ダウン・カウンタ、グレイ・コード・カウンタ、又は1つ又は複数の直列なフリップフロップのような構成要素とすることができます。好ましくは、該カウント手段は、第2クロックによってクロック供給される、すなわち、該検出手手段と同期する方がよい。

#### 【 0 0 1 7 】

実施形態の一つの組において、第1クロック・サイクルにおける前記所定の遷移の検出は、第2クロックの任意の遷移（正又は負のどちらか）で実行することができる。実施形態の一つの組では、該検出は、第2クロックの立ち上がりエッジ、すなわち正の遷移で行われ、例えば、これが、前記所定期間の開始の合図となる。上述のように、該検出は複数のステップを含み、後続のステップは、後続の、例えば、第2クロックの次の立ち上

10

20

30

40

50

リエッジで実行される。好ましくは、前記離散的サンプリングの周波数は、第2クロックの周波数に等しい方がよい。すなわち、該サンプリングは検出期間中に第2クロックのサイクル毎に行われ、可能な限り早く遷移を検出して、したがって、必要な場合にはデータ信号の可能な最速の再転送を可能にする（これは必須ではない。データの再転送は、常に前記所定期間の終了まで待つことができる）。データ信号が第1クロックの遷移の後に再転送される場合、第2クロックの周波数の第1クロックに対する比率は十分に大きくして、第1クロックの次の遷移が、該データ信号の第1クロック・ドメインから第2クロック・ドメインへの転送の実行に要する時間の間に発生しないことを保証する必要がある。

#### 【0018】

第2クロックの周波数は、第1クロックの周波数の整数倍であり、及び／又は固定された位相を有する可能性があるが、一般には、同期や特定の関係は、本発明に従う場合は必要ない。さらに、本発明の実施形態では、第1及び／又は第2クロック・ドメインがスリープ又はスタンバイ・モードに入りそして他のクロック・ドメインに対して非同期的に再起動されることが許容される。

10

#### 【0019】

実施形態の一つの組では、第2クロックの周波数は、第1クロックの周波数の少なくとも4倍の周波数、例えば、少なくとも10倍の周波数、例えば、少なくとも100倍の周波数、例えば、少なくとも1000倍の周波数にすることができる。前記クロック周波数の比に関して前記の利点及び目的が満たされるのみならず、上記によって保証されることは、十分な時間をかけて、前記所定の遷移の検出と処理、及び、該データの再転送を、さらなる遷移が生じるリスク、及びこれに伴うデータの破損又は準安定状態のリスクなしに行えることである。前記検出手段は、第2クロックによってクロック供給されるので、これは一般的には、前記所定期間（第2クロック・サイクル数サイクル分）が第1クロックのサイクルよりもはるかに短いことを意味し、第1クロックの遷移に続いて、必要な論理信号すべてが前記機構を通過して、該データを第1クロック・ドメインから第2クロック・ドメインへ再転送し、その後に第1クロックの次の遷移が起こり、第1クロック・ドメイン内のデータ値を再度変更することができるようになる。これは、また、さまざまなクロック・ドメインが商業製品に存在することを反映している。一連の例示的な実施形態では、第1クロックの周波数は32kHzであり、第2クロックの周波数は16MHzである。

20

#### 【0020】

上述のように、前記検出手段は、一つの入力における値を連續したクロック・サイクルで比較するように構成されたエッジ検出手段を含むことができる。しかし、前記確認の性質に応じて任意の適切な機構、すなわち、第1クロックの遷移を検出することができる任意の構成要素又は機構を具備することができる。このため、一般的には、該検出手段は、入力として第1クロックを持つことになる。実施形態の別の組では、該検出手段は、Dタイプ・フリップフロップのようなフリップフロップ、又は、比較器を含む。複数のフリップフロップを直列に備えて、該フリップフロップによって実行される前記確認の確実性を向上することができる。該フリップフロップからの出力が不安定な状態になることは稀である。該不安定な状態は、例えば、該確認が第1クロックの遷移の最中に実行される場合に起こり、解消するためにある程度の時間が必要になる。しかしながら、この出力が、さらにもう一つのフリップフロップの入力に供給される場合は、不安定な状態が両方のフリップフロップを通過する可能性は非常に小さい、すなわち、その確率は倍数的に減少するからである。

30

#### 【0021】

実施形態の一つの組では、前記第1クロックの遷移の確認は、常時継続して、例えば、第2クロックのサイクル毎に実行することができる。しかしながら、実施形態の別の組においては、該システムは前記所定期間を開始するための手段を含む。この手段は、該所定期間を開始するために送信される専用の信号でありうる。又は、該システム内の他の信号又はサイクルと組み合わされることもありうる。例えば、該所定期間は、該入力信号の

40

50

変化によって、又は、システム又は第2クロック・ドメインがスタンバイ又はスリープ・モードに入る又は出ることによって、又は、中央処理装置(CPU)が第1クロック・ドメインから読み出されるデータを要求することによって、起動することができる。該検出が起動によって実行され、継続的に実行されるのではない実施形態が有利である理由は、この実施形態では、該確認が必要なときにのみ実行されるので、システムの消費電力削減の助けになる。そして、第2クロック・ドメインがスリープ・モードに入ることが、該信号が転送されてからデータ信号の次の転送が必要になるまでの期間の間、可能になり、こうして電力節約ができる。本発明の実施形態が特に適している動作モードは、第2クロック・ドメインが、第1クロック・ドメインにデータ信号の転送を要求するモード、例えば、第2クロック・ドメインがスリープ・モード又はスタンバイ・モードを終了し、特定のデータ信号、例えば、時刻を要求する動作モードであろう。該時刻は、前記所定期間を開始するための信号を提供する。

#### 【0022】

上述のように、前記所定期間は、通常、一定であり、開始してから第2クロックの設定されたサイクル数の間継続する。しかしながら、想定されている実施形態では、該遷移の検出は、一旦第1クロックの遷移が検出され、該検出を示すために必要な論理信号が前記機構を通過すると、すなわち、該所定期間の満了前に、終了する。この理由は、データ信号を第1クロック・ドメインから第2クロック・ドメインに再び転送することが安全であることが一度示された後は、第1クロックが第2クロックより遅いという事実によって、データ信号を再び転送するときに、第1クロックがさらに遷移を起こすことがないことが保証されているからであり、これ以上、該検出を継続することは無駄であるからである。

#### 【0023】

本発明の実施形態によれば、前記転送されたデータ信号は、同期期間中、すなわち、前記所定期間中の任意の時点で変化可能であり、同期プロセス、又は、必要な場合、結果としての第1クロック・ドメインから第2クロック・ドメインへのデータ信号の再転送に、例えば、出力信号の準安定性を引き起こすことによって、影響を与えることがない。これは従来のハンドシェイク手順とは対照的である。従来の手順では、凍結が、第1クロック・ドメインから転送されるデータ信号に対してなされる。例えば、ビジー・フラグを使用することにより、第1及び第2クロック・ドメイン間の同期がとられる。これは明らかに該転送に必要な時間を増大させ、したがってシステムによって消費される電力を増大させる。本発明はこれらの制限を取り除き、結果としてデータ信号転送の高速化をもたらし、消費電力の削減に寄与することを理解されたい。

#### 【0024】

前記の実施形態の組において、前記検出手段へのクロック供給を第2クロックによって行い、第1クロックを入力とすることにより、前記機構は、単純に「安全な」同期信号を生成する。この目的は、データを再度第1クロック・ドメインから第2クロック・ドメインへ転送する必要があるか否かを判定することである。したがって、該データ信号の状態に関しては問題ではなく、該データ信号は、前記所定期間の間でも変化できる。すなわち、第1クロック・ドメイン内のデータ信号の、該所定期間の終了時又は該所定期間中の他の時刻における値が、第1クロック・サイクルに遷移があった場合に第2クロック・ドメインに転送される値である。このことは、一般に、該データ信号の値が変化するであろうことを意味する。もし、該所定期間中に第1クロック・サイクルの遷移がない場合、該データ信号は最初に転送された値のままであり、一般的な意味としては、該データ信号は値をえていないことになる。しかし、第1クロックの遷移が検出された場合には、第1クロック・ドメイン内の最新のデータ信号は、該遷移に続き、第2クロック・ドメインへ転送される。

#### 【0025】

前記所定期間の間に第1クロック・ドメイン内のデータ信号が変更可能であるといふこのような自由度は、従来の方法とは対照的である。従来の方法では、転送されるデータ

10

20

30

40

50

信号が 2 つのクロック・ドメインの同期中に変更されることは許可されていない。この理由は、該同期プロセス、例えばハンドシェイク及び / 又はビジー・フラグの使用は、転送されるデータ信号の確認だけでなく、該クロック・サイクルにも関係している。これは、システム全体とその使用に制限を加えることになる。例えば、CPU は、同期が完了した時をシステムに知らせるフラグをポーリングする必要がある。本発明のシステムはこのような制限がなく、その使用とアーキテクチャにより大きな自由度を与える。

#### 【 0 0 2 6 】

実施形態の一つの組では、前記システムは前記データ信号を記憶する手段、すなわち、記憶装置又は記憶部を含み、また、前記方法は該データ信号を記憶するステップを含む。これによって、該データ信号の一時的な記憶が、第 2 クロック・ドメインに出力するまで、前記初期転送及び必要に応じて後続する転送のいずれか又は両方の間、可能になる。10

該データ信号は、また、該所定期間の間、すなわち、前記第 1 クロックの確認がなされて前期論理信号が前記検出手段を通過している間、記憶しておくことができる。

#### 【 0 0 2 7 】

前記第 1 クロック・ドメインからの入力信号を記憶する手段は、データ記憶用の任意の適切な構成要素、機構、又はデバイスを含むことができる。該手段は、該データ信号を、第 1 クロック・サイクルの危険な期間及び / 又は前期所定期間中、記憶しておくことができ、前記確認を開始したとき及び / 又は、該第 1 クロックの前記確認が実行された後に、該データ信号を第 2 クロック・ドメインに出力する準備ができている。該手段は、レジスタ、例えばフリップフロップ又はラッチで構成できる。マルチビット・バスを転送するように構成されたシステムでは、複数の構成要素をバスのサイズに応じて設けてもよく、例えば、複数のフリップフロップを並列に設けることができる。このような構成要素は、該入力信号を、例えば、前記検出手段から、該入力信号の第 2 クロック・ドメインへの転送が安全であることを示す信号を受信するまで、記憶しておくことができる。さらに、該記憶手段の中のデータ信号を保留状態にして、データ転送の発生を該所定期間が経過するまで抑止することができる。該記憶手段は、前記第 1 クロック・ドメインから該データ信号を受信することができる、すなわち、該記憶手段と該第 1 クロック・ドメインは、別々の構成要素を含むことができる。一つは該入力信号を受信する構成要素であり、一つは該入力信号を記憶する構成要素である。しかしながら、該機能は、また、該第 1 クロック・ドメインによって実行することもできる。該ドメインは、該データ信号を、転送されるまで受信・記憶する。20

#### 【 0 0 2 8 】

データ信号が最初に転送されたとき、このデータ信号は、前記システムが使用しても安全であるかどうか、まだ、わかっていない。すなわち、該初期転送は不確実な状態で希望観測的になされている。この希望的観測は、第 1 クロックが、自サイクルの安全な期間内、すなわち、第 1 及び第 2 クロック・ドメインの周波数の相対的関係に基づいて、ほぼ安全であろう時間にあった、というものである。しかし、該転送が第 1 クロックの遷移時に行われた場合、該データ信号は壊れているか、準不安定な状態にある可能性がある。したがって、このような状況では、この信号をシステム全体の他の部分に伝播するのは良い考えではない。該伝播は、例えば、この信号が転送された先の第 2 バスを読み取ることによって行われる。したがって、実施形態の一つの組においては、前記機構は、最初に転送されたデータ信号の第 2 クロック・ドメインによる読み取りを禁止する手段を備えている。40

該データ信号の第 2 クロック・ドメインによる読み取りを禁止する該手段は、「レディ」信号を含むことができる。該信号は、例えば、該禁止手段が起動されたときに 0 に設定され、該データ信号が安全であり、かつ第 2 クロック・ドメインによって読み込み可能であると判定された場合に 1 に設定される。このレディ信号は、前記検出手段及び / 又は前記所定期間と連携することができる。例えば、該機構がタイマ又はカウンタを含む場合、該レディ信号は、該所定期間の終了時のように、該所定期間にに対して相対的な特定の時点で発行することができる。

#### 【 0 0 2 9 】

10

20

30

40

50

いったん、第1クロックの確認が行われ、前記所定期間が終了し、前記データ信号の最初の転送が安全であることの認識又は後続の転送（既に説明したように安全であることがわかっている）のいずれかが行われると、第2クロック・ドメインへの該データ信号読み出しの前記禁止手段を解除することができる。

【図面の簡単な説明】

【0030】

本発明の特定の実施形態の説明を、以降、例示のみの目的で、以下の添付図面を参照しながら行う。

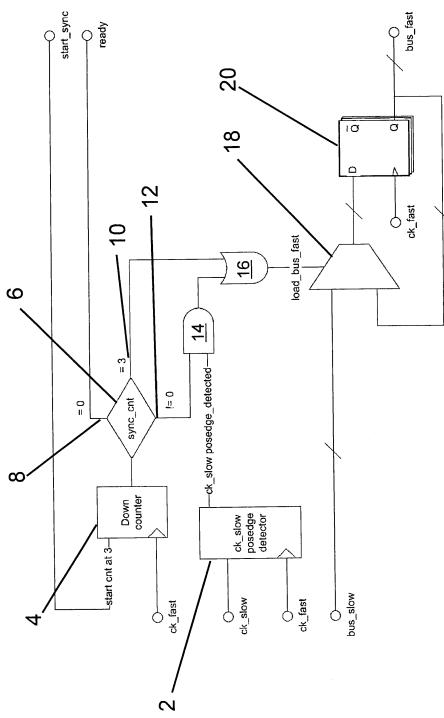

【図1】本発明による、論理回路の一実施形態を示す図である。

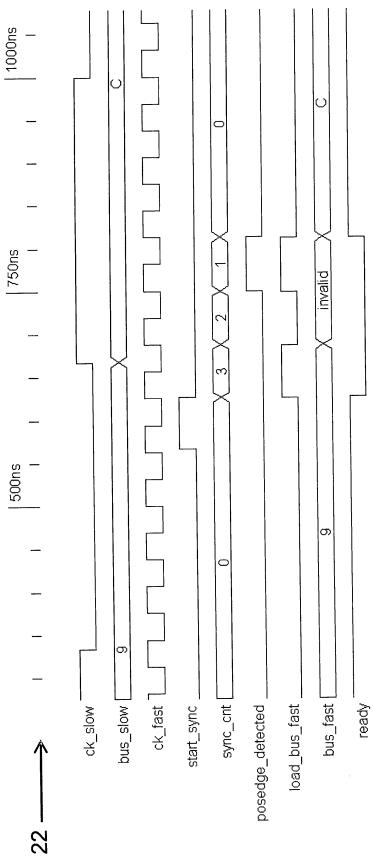

【図2】図1に示す回路図に関係づけられたタイミング図を示す。

10

【発明を実施するための形態】

【0031】

図1は、本発明を実装した機構に対応する模式的な論理回路図を示している。該機構は、データを、第1クロック・ドメイン内の第1バス、bus\_lowから、第2クロック・ドメイン内の第2バス、bus\_fastに転送するように構成されている。第1クロック、ck\_lowの周波数は第2クロック、ck\_fastの周波数よりも低く、典型的な周波数としては、第1クロック、ck\_lowは32kHzで、第2クロック、ck\_fastは16MHzである。

【0032】

前記機構は、第1クロック、ck\_lowの正エッジ検出器2を備える。該正エッジ検出器2は、該第1クロック、ck\_lowを入力として受け取る。該正エッジ検出器2の出力、posedge\_detectedは、第1クロック、ck\_lowに正エッジが検出された場合1になり、そうでない場合、0になる。第2クロック、ck\_fastは、正エッジ検出器2のクロック供給に使用され、第2クロックの立ち上がりエッジ毎に、該入力、ck\_lowの値がサンプリングされ、第2クロックの前の立ち上がりエッジの時の値と比較される。

20

【0033】

前記機構は、また、ダウン・カウンタ4を備える。該ダウン・カウンタ4は、入力として初期化信号、start\_syncを受け取る。該信号、start\_syncは、データを転送するために同期処理が開始されることを示す。前記ダウン・カウンタ4からの出力、sync\_countはカウントの値であり、カウント毎に1ずつ減少する整数である。図1に示す実施形態では、カウントは常に3から始まる。第2クロック、ck\_fastは、また、該ダウン・カウンタ4のクロック供給に使用されている。すなわち、第2クロックの立ち上がりエッジ毎に、該ダウン・カウンタはその出力sync\_countの値を1だけ減じる。

30

【0034】

前記ウン・カウンタ4からの出力、sync\_countは、判定ノード6に供給される。該判定ノード6からは3つの出力8、10、12があり、該ダウン・カウンタ4からの出力、sync\_countの値に基づいている。第1出力8は、ダウン・カウンタ4の出力、sync\_countが0に等しい場合、値1を持つ。第2出力10は、ダウン・カウンタ4の出力、sync\_countが3に等しい場合、値1を持つ。第3出力12は、ダウン・カウンタ4の出力、sync\_countが0に等しくない場合、値1を持つ。理解されるように、該判定ノード6からの第2と第3出力10、12の両方が値1を持つのは、すなわち、ダウン・カウンタ4からの出力sync\_countが値3を持つ場合である。ダウン・カウンタ4の出力値、sync\_countの値が0に等しい場合、信号、readyが前記システムに出力される。その指示内容は、第1バス、bus\_lowからのデータの転送が完了して、前記機構はさらに次の初期化信号、start\_syncを受信する用意ができていることを示している。

40

【0035】

正エッジ検出器2からの出力信号、posedge\_detectedは、判定ノー

50

ド6からの第3出力12とANDゲート14で組み合わせられる。該ANDゲート14からの出力は、前記判定ノード6からの第2出力10に、ORゲート16で組み合わせられる。該ORゲート16からの出力、load\_bus\_fastは、マルチプレクサ18の選択入力に供給される。該マルチプレクサ18への入力は、第1バスからのデータ信号、bus\_low、及び第2バスへの出力データ信号、bus\_fastである。該マルチプレクサ18からの出力は、Dタイプ・フリップフロップ20に供給される。該Dタイプ・フリップフロップ20は、第2クロック、ck\_fastによってクロック供給される。該フリップフロップ20のQ出力は、第2バス、bus\_fastへ出力される。

#### 【0036】

システムの動作について、図1ならびに図2を参照して説明する。図2は、該システムを通る論理信号のシーケンスを示している。説明用のタイム・スケール22は、50nsの小区分毎に示されている。図2に示すように及び説明目的のために、高周波の第2クロック・ドメイン4からの第2クロック、ck\_fastの周波数は16MHzとされており、低周波の第1クロック・ドメイン8の第1クロック、ck\_lowの周波数は1.5MHzとされている。実際にはこれらのクロックは、先に詳述したように、より大きく異なっている可能性が高い。しかし、ここでは、これらをより比較し易い値を選択して、説明上の便宜を図っている。

#### 【0037】

最初に、前記システムの状態は、マルチビット・データ、h9(16進数の値)が第1バス、bus\_lowにあり、かつ、第2バス、bus\_fastは未知、すなわち、直前の転送からの値となっている。該システムは、565ns時点で、初期化信号、start\_syncが0から1へ変化し、そして、同期処理の開始をトリガするまで、定常状態にある。典型的には、該初期化信号は、第2クロック・ドメイン(一般に高電力周辺機器を制御する)によって生成される。その生成時期は、第1クロック・ドメイン(一般に低電力タイミング回路)からのデータ転送を要求するためにスリープ・モードを終了したときである。625ns時点で、ダウン・カウンタ4は、第2クロック、ck\_fastの次の立ち上がりエッジでクロック駆動され、これによって、3からカウント・ダウンが開始される。すなわち、625nsで、ダウン・カウンタ4からの出力、sync\_countは3に変わる。該ダウン・カウンタ4が、3からカウント・ダウンすることが必要な理由は、前記正エッジ検出器2が、第2クロック、ck\_fastの2サイクルをかけて、正の遷移を検出する、すなわち、2サイクルをかけて必要な論理信号が該フリップフロップ群を通過するからである。

#### 【0038】

ダウン・カウンタ4からのsync\_countに対するこの出力値3によって、判定ノード6の第1出力8が値0になり、かつ、判定ノード6の第2及び第3出力10、12が値1になる。正エッジ検出器2の出力、posedge\_detectedにかかわらず、ORゲート16へのこれらの入力によって、ORゲート16からの出力、load\_bus\_fastは値が1になる。この値1は、マルチプレクサ18のセレクタ入力に供給され、これによって、第1バス、bus\_lowにおけるデータ信号h9がフリップフロップ20のD入力に供給され、第2クロック、ck\_fastの次の立ち上がりエッジで、データ信号h9が第2バス、bus\_fastに伝達される。

#### 【0039】

一方、第2クロック、ck\_fastの立ち上がりエッジ毎に、正エッジ検出器2は、第1クロック、ck\_lowのサイクルにおける正の遷移を検出する。670ns時点で、第1クロック、ck\_lowには正の遷移が起こっている。本例では、該遷移は、第1バス、bus\_lowにおける、データ信号のh9からhCへの変化と関係付けられる。しかし、他の状況では該データ信号は変わらない。750ns時点で、第2クロック、ck\_fast(該第2クロックが正エッジ検出器2にクロック供給する)のサイクルで2サイクル後の立ち上がりエッジにおいて、正エッジ検出器2からの出力、posedge\_detectedが1に変化して、第1クロック、ck\_lowの正の遷移

10

20

30

40

50

が検出されたことを示している。この値 1 が、判定ノード 6 の第 3 出力 12 からの値 1 ( すなわち、この時点で、ダウン・カウンタ 4 の出力、 sync\_count は 1 であり、 0 に等しくない ) と組み合わされて、 AND ゲート 14 の出力値が 1 になり、かつ、 OR ゲート 16 の出力、 load\_bus\_fast が値 1 になる。これの意味するところは、第 1 クロック、 ck\_slow での正の遷移が第 2 クロック、 ck\_fast の遷移中に発生し、該期間中に、当初は前記データ信号が、第 1 バス、 bus\_slow から第 2 バス、 bus\_fast に転送されていたので、第 1 バスの該データが再転送されるということである。

#### 【 0040 】

前述のように、 load\_bus\_fast の値 1 が、マルチプレクサ 18 の選択入力に供給されると、第 1 バス、 bus\_slow における前記データ信号 ( このとき hc になっている ) が、フリップフロップ 20 の D 入力に供給されることになり、第 2 クロック、 ck\_fast の次の立上がりエッジにおいて、データ信号 hc が第 2 バス、 bus\_fast に転送されるようになる。第 1 クロック、 ck\_slow の周波数は十分に低く、第 1 クロックでの次の正の遷移が発生する前に該データ信号の転送が完了することを保証できる。

#### 【 0041 】

812.5 ns 時点で、ダウン・カウンタ 4 からの出力、 sync\_count がゼロに達して、これにより判定ノード 6 からの出力 8 の値が 1 とされ、該システムは新しい初期化信号を受信する準備ができていることを示す。すなわち、信号、 ready が 1 になる。この時点で、いったん前記所定期間が終了したら、フリップフロップ 20 に格納されたデータ信号は、有効で安定した値であり、第 2 クロック、 ck\_fast に同期したデータとして、例えば、第 2 バス、 bus\_fast への出力として、第 2 クロック、 ck\_fast の該立ち上がりエッジで、該システムによって使用できる。これは、上述の通りである。判定ノード 6 からの第 2 と第 3 出力 10, 12 は、ダウン・カウンタ 4 からの出力、 sync\_count が 0 のとき 0 であり、このため、新たなデータ信号は、第 1 バス、 bus\_slow からフリップフロップ 20 に、この時点では、転送することができない。したがって、1つの実施形態 ( 図示せず ) で、正の遷移が、前記所定期間内、すなわち、ダウン・カウンタ 4 からの出力、 sync\_count のカウント・ダウン中には発生しないが、ダウン・カウンタ 4 からの出力、 sync\_count が 0 に達したときに検出される場合、該データ信号が前記所定の同期期間の開始時に最初に転送されてから、この条件下でデータの破壊又は準安定状態のリスクが起こらないために必要十分な時間が過ぎてしまっている。この理由は、第 1 クロック、 ck\_slow の正の遷移が該データ信号の最初の転送と同時には発生せず、第 1 バス、 bus\_slow におけるデータ値が第 1 クロック、 ck\_slow の正の遷移のときのみに変更される ( 準安定状態の原因 ) からである。

#### 【 0042 】

当業者には、上述の実施形態に対する多くの変形及び修正が、本明細書で述べた発明の様々な態様の範囲内で行うことができる事が理解されよう。例えば、最終段のフリップフリップは、前記転送されるデータ信号を第 2 バスへ出力するために設ける必要はなく、これは、他のデータ記憶用構成要素によって行うことができる、又は、ただ単に該回路を開門して、該入力信号を直接、第 1 バスから転送することも可能である。前記所定期間の長さは、異なる値にすることができる。特に、この長さが、第 1 クロックの遷移を検出するために使用される構成要素の種類に依存する場合、すなわち、この構成要素からある決定を得るために要する時間に依存する場合、又は、1つ又は複数の構成要素が前記第 2 クロックの両方の遷移でクロック供給される場合には、該期間の長さを異なる値にすることができる。

10

20

30

40

【図1】

【図2】

---

フロントページの続き

(72)発明者 ベルントセン、フランク

ノルウェー王国、エヌ 7089 ハイムダル、ルンドホグダ 14

審査官 佐賀野 秀一

(56)参考文献 特開2004-120587(JP,A)

特開2011-107737(JP,A)

米国特許第06359479(US,B1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 1 / 04 - 1 / 14

G 06 F 13 / 38 - 13 / 42

H 04 L 7 / 00 - 7 / 10