(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7022112号

(P7022112)

(45)発行日 令和4年2月17日(2022.2.17)

(24)登録日 令和4年2月8日(2022.2.8)

(51)国際特許分類

|        |                 |     |        |       |         |

|--------|-----------------|-----|--------|-------|---------|

| H 01 L | 25/18 (2006.01) | F I | H 01 L | 25/04 | Z       |

| H 01 L | 25/04 (2014.01) |     | H 01 L | 23/12 | 5 0 1 P |

| H 01 L | 23/12 (2006.01) |     | H 01 L | 23/30 | R       |

| H 01 L | 23/29 (2006.01) |     |        |       |         |

| H 01 L | 23/31 (2006.01) |     |        |       |         |

請求項の数 23 (全19頁)

(21)出願番号 特願2019-507767(P2019-507767)

(86)(22)出願日 平成29年8月14日(2017.8.14)

(65)公表番号 特表2019-525487(P2019-525487)

A)

(43)公表日 令和1年9月5日(2019.9.5)

(86)国際出願番号 PCT/US2017/046779

(87)国際公開番号 WO2018/031999

(87)国際公開日 平成30年2月15日(2018.2.15)

審査請求日 令和2年8月12日(2020.8.12)

(31)優先権主張番号 62/374,447

(32)優先日 平成28年8月12日(2016.8.12)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 517090646

コーポ ユーエス, インコーポレイティド

アメリカ合衆国, ノース カロライナ 2

7 4 0 9, グリーンズボロ, ソーンダイ

ク ロード 7 6 2 8

(74)代理人 100140109

弁理士 小野 新次郎

(74)代理人 100118902

弁理士 山本 修

(74)代理人 100106208

弁理士 宮前 徹

(74)代理人 100120112

中西 基晴

(74)代理人 100101373

弁理士 竹内 茂雄

最終頁に続く

(54)【発明の名称】 性能を向上させたウェーハレベルパッケージ

## (57)【特許請求の範囲】

## 【請求項1】

第1のデバイス層を含む第1の薄化ダイであって、前記第1のデバイス層は、ガラス材料から形成され、前記第1のデバイス層の底面に複数の第1のダイ接点を有する、前記第1の薄化ダイと、

第2のデバイス層と、前記第2のデバイス層の上の完全なシリコン基板とを含む第2の完全なダイであって、前記第2のデバイス層は、前記第2のデバイス層の底面に複数の第2のダイ接点を有する、前記第2の完全なダイと、

多層再分布構造であって、前記多層再分布構造の底面の複数のパッケージ接点と、前記複数のパッケージ接点を前記複数の第1のダイ接点のうちの特定の1つおよび前記複数の第2のダイ接点のうちの特定の1つに接続する再分布相互接続とを含み、前記再分布相互接続と前記複数の第1のダイ接点との間、および前記再分布相互接続と前記複数の第2のダイ接点との間の接続は無ハンダである、前記多層再分布構造と、

前記多層再分布構造の上に存在する第1のモールドコンパウンドであって、

前記第1のモールドコンパウンドは、前記第1の薄化ダイを取り囲むとともに、前記第1のモールドコンパウンド内に、かつ前記第1の薄化ダイの上に開口を画定するために前記第1の薄化ダイの上面を超えて延在し、前記第1の薄化ダイの前記上面は前記開口の底部にあり、

前記第1のモールドコンパウンドは、前記第2の完全なダイを封止する、

前記第1のモールドコンパウンドと、

前記開口を充填し、前記第1の薄化ダイの前記上面と接触している第2のモールドコンパウンドと

を備える装置。

【請求項2】

前記ガラス材料は、二酸化ケイ素(SiO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、超酸化リチウム(LiO<sub>2</sub>)、バリウム酸化物(BaO)、カリウム酸化物(K<sub>2</sub>O)、ナトリウム酸化物(Na<sub>2</sub>O)、ホウ素酸化物(B<sub>2</sub>O<sub>3</sub>)、マグネシウム酸化物(MgO)、ストロンチウム酸化物(SrO)及びカルシウム酸化物(CaO)からなる群のうちの少なくとも1種である、請求項1に記載の装置。

【請求項3】

前記第1のデバイス層は5μm～1000μmの厚さを有する、請求項1に記載の装置。

10

【請求項4】

前記第1のデバイス層は70μm～200μmの厚さを有する、請求項1に記載の装置。

【請求項5】

前記第1の薄化ダイはマイクロ電気機械システム(MEMS)構成要素を提供する、請求項1に記載の装置。

【請求項6】

前記第1の薄化ダイはMEMS構成要素を提供し、前記第2の完全なダイは、前記MEMS構成要素を制御する相補型金属酸化膜半導体(CMOS)コントローラを提供する、請求項1に記載の装置。

20

【請求項7】

前記第2のデバイス層は、誘電層と金属層との組み合わせから形成される、請求項1に記載の装置。

【請求項8】

前記第2のモールドコンパウンドは、1E6Ohm·cmを超える電気抵抗率を有する、請求項1に記載の装置。

【請求項9】

前記第1のモールドコンパウンドは、前記第2のモールドコンパウンドと同じ材料から形成される、請求項1に記載の装置。

【請求項10】

前記第1のモールドコンパウンドと前記第2のモールドコンパウンドとは、異なる材料から形成される、請求項1に記載の装置。

30

【請求項11】

前記開口の前記底部に露出された前記第1の薄化ダイの前記上面は、前記第1のデバイス層の上面である、請求項1に記載の装置。

【請求項12】

前記第2のモールドコンパウンドは、2W/m·Kを超える熱伝導率を有する熱可塑性材料または熱硬化性材料から形成される、請求項1に記載の装置。

【請求項13】

前記第1のデバイス層は70μm～1000μmの厚さを有する、請求項12に記載の装置。

40

【請求項14】

前記第2のモールドコンパウンドは有機エポキシ樹脂から形成される、請求項1に記載の装置。

【請求項15】

前記第1のデバイス層は5μm～1000μmの厚さを有する、請求項14に記載の装置。

【請求項16】

前記多層再分布構造は無ガラスである、請求項1に記載の装置。

【請求項17】

第1のダイと第1のモールドコンパウンドとを有するモールドウェーハを提供することで

50

あって、

前記第1のダイは、第1のデバイス層と、前記第1のデバイス層の上の第1のシリコン基板とを含み、前記第1のデバイス層は、ガラス材料から形成され、前記第1のデバイス層の底面に複数の第1のダイ接点を含み、

前記第1のダイの上面は前記第1のシリコン基板の上面であり、前記第1のダイの底面は前記第1のデバイス層の前記底面であり、

前記第1のモールドコンパウンドは、前記第1のダイの側面及び前記上面を封止し、前記第1のデバイス層の前記底面が露出される、

前記提供することと、

前記モールドウェーハの下に多層再分布構造を形成することであって、

前記多層再分布構造は、前記多層再分布構造の底面の複数のパッケージ接点と、前記複数のパッケージ接点を前記複数の第1のダイ接点のうちの特定の1つに接続する再分布相互接続とを含み、

前記再分布相互接続と前記複数の第1のダイ接点との間の接続は無ハンダである、

前記形成することと、

前記第1のモールドコンパウンドを薄化して前記第1のシリコン基板の前記上面を露出させることと、

第1の薄化ダイを提供し、前記第1のモールドコンパウンド内に、かつ前記第1の薄化ダイの上に開口を形成するために前記第1のダイの前記第1のシリコン基板を完全に除去することであって、前記第1のデバイス層の上面は前記第1の薄化ダイの上面であると共に、前記開口の底部に露出される、前記除去することと、

前記開口を実質的に充填し、前記第1の薄化ダイの前記上面と直接接触するように第2のモールドコンパウンドを塗布することと

を含む方法。

#### 【請求項18】

前記第1のダイはMEMS構成要素を提供する、請求項17に記載の方法。

#### 【請求項19】

前記第2のモールドコンパウンドは、2W/m·Kを超える熱伝導率を有する熱可塑性材料または熱硬化性材料から形成され、

前記第2のモールドコンパウンドは250psi～1000psiで塗布され、

前記第1のデバイス層は70μm～1000μmの厚さを有する、請求項17に記載の方法。

#### 【請求項20】

前記第2のモールドコンパウンドは有機エポキシ樹脂から形成され、

前記第2のモールドコンパウンドは100psi～1000psiで塗布され、

前記第1のデバイス層は5μm～1000μmの厚さを有する、請求項17に記載の方法。

#### 【請求項21】

前記モールドウェーハは、第2の完全なダイをさらに含み、

前記第2の完全なダイは、第2のデバイス層と、前記第2のデバイス層の上の第2のシリコン基板とを有し、前記第2のデバイス層は、前記第2のデバイス層の底面に複数の第2のダイ接点を有し、

前記第1のモールドコンパウンドは、前記第2の完全なダイの側面および上面を封止し、前記第2のデバイス層の前記底面が露出される、請求項17に記載の方法。

#### 【請求項22】

前記モールドウェーハの下に前記多層再分布構造を形成することは、前記再分布相互接続により、前記複数のパッケージ接点を前記複数の第2のダイ接点のうちの特定の1つに接続することをさらに含む、請求項21に記載の方法。

#### 【請求項23】

前記第2の完全なダイは、前記第1のダイよりも短く、それによって、前記第1のモールドコンパウンドを薄化して前記第1のシリコン基板の前記上面を露出させた後、前記第2

10

20

30

40

50

のシリコン基板は露出せず、前記第1のモールドコンパウンドによって依然として封止される、請求項22に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願は、2016年8月12日に出願された仮特許出願第62/374,447号の利益を主張するものであり、当該仮特許出願の開示は、その全体が参照によりここで本明細書に組み込まれる。

【0002】

本開示は、ウェーハレベルパッケージ及びそれを作製するためのプロセスに関し、より詳細には、電気的性能及び剛性性能を向上させたウェーハレベルパッケージ、ならびにウェーハレベルパッケージの電気的性能及び剛性性能を向上させるためのパッケージングプロセスに関する。

【背景技術】

【0003】

携帯及び無線デバイスの広範な利用により、無線周波数（RF）技術の急速な発展がもたらされている。表面上にRFデバイスが製作される基板は、RF技術で高度な性能を実現するのに重要な役割を果たす。従来のシリコン基板上にRFデバイスを製作することは、シリコン材料の低コスト化、大規模なウェーハ生産能力、十分に確立された半導体設計ツール、及び十分に確立された半導体製造技術から利益を得ることができる。

10

【0004】

RFデバイス製作のために従来のシリコン基板を使用する利益に関わらず、従来のシリコン基板は、RFデバイスにとって2つの望ましくない性質、すなわち、高調波歪み及び低い抵抗率値を有し得ることが産業界においてよく知られている。高調波歪みは、シリコン基板上に作られたRFデバイスにおいて高度な直線性を実現する上で大きな妨げとなる。加えて、シリコン基板内に低抵抗率が生じると、マイクロ電気機械システム（MEMS）または他の受動的構成要素のQ値（Q）が高周波で低下し得る。

20

【0005】

ウェーハレベルファンアウト（WLO）パッケージング技術及び埋設ウェーハレベルボールグリッドアレイ（EWLB）技術は、現在、可搬RFアプリケーションにおいて相当な注目を集めている。WLO及びEWLB技術は、構成要素となる半導体チップのサイズを増大させずに高密度な入出力ポート（I/O）及び低プロファイルのパッケージ高さを提供するように設計されている。チップ上のI/Oパッドサイズは小さいままであり、ダイサイズを最小に保つ。この能力により、単一のウェーハ内にRFデバイスを高密度にパッケージングすることが可能になる。

30

【0006】

従って、RFデバイスの有害な高調波歪みを低減し、かつWLO/EWLBパッケージング技術の利点を利用するため、性能を向上させた改良型のパッケージ設計を提供することが本開示の目的である。更に、パッケージサイズを増大させずにRFデバイスの性能向上させる必要もある。

40

【発明の概要】

【0007】

本開示は、電気的性能及び剛性性能を向上させたウェーハレベルパッケージ、及びそれを作製するためのパッケージングプロセスに関する。開示されたウェーハレベルパッケージは、第1の薄化ダイと、多層再分布構造と、第1のモールドコンパウンドと、第2のモールドコンパウンドとを備える。第1の薄化ダイは第1のデバイス層を含み、第1のデバイス層は、ガラス材料から形成され、第1のデバイス層の底面に複数の第1のダイ接点を有する。多層再分布構造は、多層再分布構造の底面に設けられた複数のパッケージ接点と、パッケージ接点を第1のダイ接点のうちの特定の1つに接続する再分布相互接続とを含む

50

。再分布相互接続と第1のダイ接点との間の接続は無ハンダである。加えて、第1のモールドコンパウンドは、多層再分布構造の上に、かつ第1の薄化ダイの周囲に存在し、第1のモールドコンパウンド内に、かつ第1の薄化ダイの上に開口を画定するために第1の薄化ダイの上面を超えて延在する。第1の薄化ダイの上面は開口の底部に露出される。第2のモールドコンパウンドは、開口を充填し、第1の薄化ダイの上面と接触している。

【0008】

ウェーハレベルパッケージの一実施形態において、ガラス材料は、二酸化ケイ素(SiO<sub>2</sub>)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、リチウム超酸化物(LiO<sub>2</sub>)、バリウム酸化物(BaO)、カリウム酸化物(K<sub>2</sub>O)、ナトリウム酸化物(Na<sub>2</sub>O)、ホウ素酸化物(B<sub>2</sub>O<sub>3</sub>)、マグネシウム酸化物(MgO)、ストロンチウム酸化物(SrO)及びカルシウム酸化物(CaO)からなる群のうちの少なくとも1種である。

10

【0009】

ウェーハレベルパッケージの一実施形態において、第1の薄化ダイはマイクロ電気機械システム(MEMS)構成要素を提供する。

【0010】

別の実施形態によれば、ウェーハレベルパッケージは、多層再分布構造の上に存在する第2の完全なダイを更に備える。本明細書において、第2の完全なダイは、第2のデバイス層と、第2のデバイス層の上の完全なシリコン基板とを有し、第1のモールドコンパウンドは、第2の完全なダイを封止する。

20

【0011】

ウェーハレベルパッケージの一実施形態において、第1の薄化ダイはMEMS構成要素を提供し、第2の完全なダイは、MEMS構成要素を制御する相補型金属酸化膜半導体(CMOS)コントローラを提供する。

【0012】

ウェーハレベルパッケージの一実施形態において、第2のデバイス層は、誘電層と金属層との組み合わせから形成される。

【0013】

ウェーハレベルパッケージの一実施形態において、第2のモールドコンパウンドは、1E60hm·cmを超える電気抵抗率を有する。

30

【0014】

ウェーハレベルパッケージの一実施形態において、第1のモールドコンパウンドは、第2のモールドコンパウンドと同じ材料から形成される。

【0015】

ウェーハレベルパッケージの一実施形態において、第1のモールドコンパウンドと第2のモールドコンパウンドとは、異なる材料から形成される。

【0016】

ウェーハレベルパッケージの一実施形態において、開口の底部に露出された第1の薄化ダイの上面は、第1のデバイス層の上面である。

【0017】

ウェーハレベルパッケージの一実施形態において、第2のモールドコンパウンドは、2W/m·Kを超える熱伝導率を有する熱可塑性材料または熱硬化性材料から形成される。ここで、第1のデバイス層は70μm~1000μmの厚さを有する。

40

【0018】

ウェーハレベルパッケージの一実施形態において、第2のモールドコンパウンドは有機エポキシ樹脂から形成される。ここで、第1のデバイス層は5μm~1000μmの厚さを有する。

【0019】

ウェーハレベルパッケージの一実施形態において、多層再分布構造は無ガラスである。

【0020】

例示的な工程に従って、第1のダイと第1のモールドコンパウンドとを有するモールドウ

50

エーハを提供する。第1のダイは、第1のデバイス層と、第1のデバイス層の上の第1のシリコン基板とを含む。第1のデバイス層は、ガラス材料から形成され、第1のデバイス層の底面に複数の第1のダイ接点を含む。第1のダイの上面は第1のシリコン基板の上面であり、第1のダイの底面は第1のデバイス層の底面である。第1のモールドコンパウンドは、第1のデバイス層の底面が露出されるように第1のダイの側面及び上部を封止する。次に、モールドウェーハの下に多層再分布構造を形成する。多層再分布構造は、多層再分布構造の底面に設けられた複数のパッケージ接点と、パッケージ接点を第1のダイ接点のうちの特定の1つに接続する再分布相互接続とを含む。再分布相互接続と第1のダイ接点との間の接続は無ハンダである。次いで、第1のモールドコンパウンドを薄化して第1のシリコン基板の上面を露出させる。第1の薄化ダイを提供し、第1のモールドコンパウンド内に、かつ第1の薄化ダイの上に開口を形成するために第1のダイの第1のシリコン基板を実質的に除去する。第1の薄化ダイの上面は、開口の底部に露出される。最後に、開口を実質的に充填し、第1の薄化ダイの上面と直接接觸するように第2のモールドコンパウンドを塗布する。

#### 【0021】

当業者は、添付図面に関連して好ましい実施形態に関する以下の詳細な説明を読んだ後、本開示の範囲を認識し、本開示の更なる態様を理解するであろう。

#### 【0022】

本明細書に組み込まれ、本明細書の一部を構成する添付図面は、本開示のいくつかの態様を例示するものであり、本説明と共に、本開示の原理を説明するのに役立つ。

#### 【図面の簡単な説明】

#### 【0023】

【図1】本開示の一実施形態に従った例示的なウェーハレベルパッケージを示す。

【図2】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図3】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図4】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図5】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図6】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図7】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図8】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図9】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図10】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図11】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図12】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

【図13】図1に示した例示的なウェーハレベルパッケージを製作するための工程を示す例示的なステップを提供する。

#### 【0024】

説明を分かりやすくするため、図1～13は縮尺に合わせて描かれていない場合があることが理解されよう。

【発明を実施するための形態】

【0025】

以下に記載された実施形態は、実施形態を実施することを当業者に可能にするために必要な情報を表し、実施形態を実施する際の最良の形態を示す。添付図面に照らして以下の説明を読むことにより、当業者は、本開示の概念を理解すると共に、本明細書において特に対象とされないこれらの概念の適用例を理解するであろう。これらの概念及び適用例は、本開示及び添付された特許請求の範囲内に含まれることが理解されるべきである。

【0026】

第1、第2などの用語が、各種要素を説明するために本明細書で使用され得るもの、これらの要素は、これらの用語によって限定されるべきではないことが理解されよう。これらの用語は、単に、1つの要素を別の要素と区別するために使用される。例えば、本開示の範囲から逸脱することなく、第1の要素を第2の要素と称することができ、同様に、第2の要素を第1の要素と称することができる。本明細書で使用される場合、用語「及び／または」は、列挙された関連項目のうちの1つ以上のいずれかの組み合わせ及び全ての組み合わせを含む。

10

【0027】

層、領域または基板などの要素が別の要素の「上に( on )」存在する、または「上へと( onto )」延在すると言及されるとき、その要素は、他の要素の上に直接存在する、もしくは他の要素の上へと直接延在することができ、または介在要素が存在してもよいことが理解されよう。これに対して、要素が別の要素の「上に( over )」存在する、または「上に( over )」延在すると言及されるとき、その要素は、他の要素の上に直接存在する、もしくは他の要素の上に直接延在することができ、または介在要素が存在してもよい。これに対して、要素が別の要素の「上に直接( directly on )」存在する、または「上へと直接( directly onto )」延在すると言及されるときには、介在要素が存在しない。同様に、層、領域または基板などの要素が別の要素の「上に( over )」存在する、または「上に( over )」延在すると言及されるとき、その要素は、他の要素の上に直接存在する、もしくは他の要素の上に直接延在することができ、または介在要素が存在してもよい。これに対して、要素が別の要素に「接続されている( connected )」または「結合されている( coupled )」と言及されるとき、その要素は、他の要素に直接接続もしくは結合することができ、または介在要素が存在してもよいことも理解されよう。これに対して、要素が別の要素に「直接接続されている( directly connected )」または「直接結合されている( directly coupled )」と言及されるときには、介在要素が存在しない。

20

30

30

【0028】

「下に( below )」または「上に( above )」または「上方に( upper )」または「下方に( lower )」または「水平に( horizontal )」または「垂直に( vertical )」などの相対的な用語は、図面に示されるように、1つの要素、層または領域と、別の要素、層または領域との関係を説明するために本明細書で使用され得る。これらの用語及び上述した用語は、図面に表された方向に加えて、デバイスの異なる方向を含むことが意図されることが理解されよう。

40

【0029】

本明細書で使用される用語は、特定の実施形態を説明するためのものに過ぎず、本開示を限定することを意図しない。本明細書で使用される場合、単数形「a」、「an」及び「the」は、文脈において特に明確な指示がない限り、複数形も含むことが意図される。用語「備える( comprises )」、「備えている( comprising )」、「含む( includes )」及び／または「含んでいる( including )」は、本明細書で使用されるとき、記載された特徴、整数、ステップ、動作、要素及び／または構成要素の存在を指定するが、1つ以上の他の特徴、整数、ステップ、動作、要素、構成要素及び／またはこれらの集合の存在も追加も排除しない。

【0030】

50

特に定義されない限り、本明細書で使用される全ての用語（技術用語及び科学用語を含む）は、本開示が属する技術分野の当業者によって一般に理解されるのと同じ意味を有する。本明細書で使用される用語は、本明細書及び関連技術分野の文脈におけるその意味と一致する意味を有するものとして解釈されるべきであり、本明細書でそのように明確に定義されない限り、理想的な意味または過度に形式的な意味には解釈されないことが更に理解されよう。

### 【 0 0 3 1 】

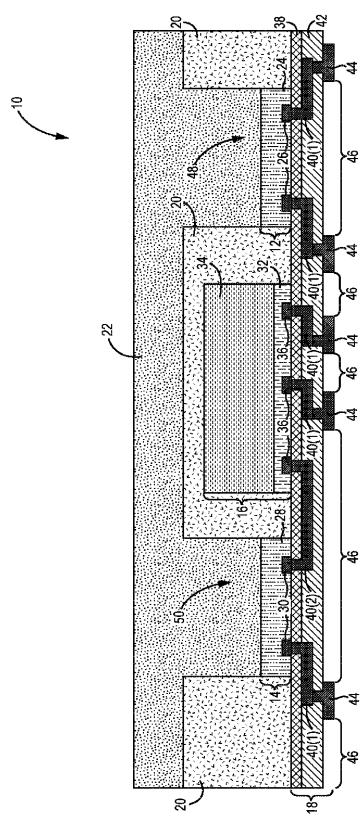

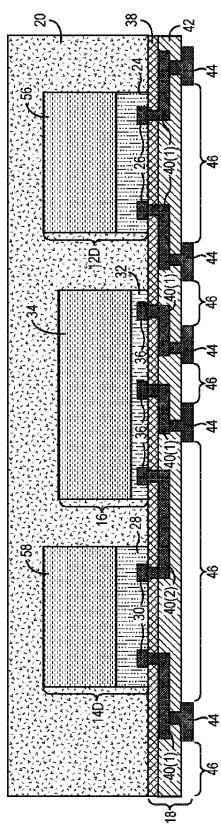

本開示は、電気的性能及び剛性性能を向上させたウェーハレベルパッケージ、及びそれを作製するためのパッケージングプロセスに関する。図1は、本開示の一実施形態に従った例示的なウェーハレベルパッケージ10を示す。この説明のために、例示的なウェーハレベルパッケージ10は、薄化ガラスベースダイ12、薄化マイクロ電気機械システム（MEMS）ダイ14、相補型金属酸化膜半導体（CMOS）コントローラダイ16、多層再分布構造18、第1のモールドコンパウンド20及び第2のモールドコンパウンド22を備える。種々の適用例において、ウェーハレベルパッケージ10は、より少ない、またはより多い薄化ガラスベース/MEMSダイを備えてもよい。例えば、いくつかの適用例において、ウェーハレベルパッケージ10は、薄化MEMSダイ及びCMOSコントローラダイのみを備える場合があり、いくつかの適用例において、ウェーハレベルパッケージ10は、薄化ガラスベースダイのみを備える場合がある。

10

### 【 0 0 3 2 】

詳細には、薄化ガラスベースダイ12は第1のデバイス層24を備える。この層は、二酸化ケイ素（SiO<sub>2</sub>）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）、リチウム超酸化物（LiO<sub>2</sub>）、バリウム酸化物（BaO）、カリウム酸化物（K<sub>2</sub>O）、ナトリウム酸化物（Na<sub>2</sub>O）、ホウ素酸化物（B<sub>2</sub>O<sub>3</sub>）、マグネシウム酸化物（MgO）、ストロンチウム酸化物（SrO）及びカルシウム酸化物（CaO）などのガラス材料から形成される。第1のデバイス層24で使用されるガラス材料は、無アルカリであってもよい。第1のデバイス層24は、複数の第1のダイ接点26、及び第1のダイ接点26に結合された少なくとも1つの電子的構成要素（図示せず）を含む。ここで、第1のダイ接点26は、第1のデバイス層24の底面にあるが、少なくとも1つの電子的構成要素（図示せず）は、第1のデバイス層24の上面に露出されていない。第1のデバイス層24は、通常は熱耐性が低いガラス材料から形成されるため、第1のデバイス層24内の少なくとも1つの電子的構成要素（図示せず）は、低電力フィルタ、低電力コンデンサなどの、低熱生成の構成要素である。第1のデバイス層24は、少なくとも100psiの成形圧力が必要となり得る5μm～1000μmの厚さを有してもよく、または、少なくとも750psiの成形圧力が必要となり得る70μm～1000μmの厚さを有してもよい（より詳細な事項については、以下の製作工程において説明する）。サイズ、コスト及び剛性の見地から、第1のデバイス層24は70μm～200μmの厚さを有してもよい。

20

### 【 0 0 3 3 】

薄化MEMSダイ14は第2のデバイス層28を含む。この層も、二酸化ケイ素（SiO<sub>2</sub>）、酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）、リチウム超酸化物（LiO<sub>2</sub>）、バリウム酸化物（BaO）、カリウム酸化物（K<sub>2</sub>O）、ナトリウム酸化物（Na<sub>2</sub>O）、ホウ素酸化物（B<sub>2</sub>O<sub>3</sub>）、マグネシウム酸化物（MgO）、ストロンチウム酸化物（SrO）及びカルシウム酸化物（CaO）などのガラス材料から形成される。第1のデバイス層24で使用されるガラス材料は、無アルカリであってもよい。第2のデバイス層28は、複数の第2のダイ接点30、及び第2のダイ接点30に結合されたMEMS構成要素（図示せず）を含む。ここで、第2のダイ接点30は、第2のデバイス層28の底面にあるが、MEMS構成要素は、第2のデバイス層28の上面に露出されていない。MEMS構成要素は、通常はスイッチであり、低熱を生成する。第2のデバイス層28は、少なくとも100psiの成形圧力が必要となり得る5μm～1000μmの厚さを有してもよく、または、少なくとも750psiの成形圧力が必要となり得る70μm～1000μmの厚さを有してもよい（より詳細な事項については、以下の製作工程において説明する）。サイズ

40

50

、コスト及び剛性の見地から、第2のデバイス層28は70μm～200μmの厚さを有してもよい。

【0034】

薄化ガラスベースダイ12と薄化MEMSダイ14とは共に薄化ダイを含み、このダイは、デバイス層、及びデバイス層の上の実質的に非シリコンの基板を有することに注意されたい。ここで、デバイス層の上の実質的に非シリコンの基板とは、デバイス層の上の最大でも2μmのシリコン基板を指す。所望の場合において、各薄化ダイは、各薄化ダイの上面がデバイス層の上面となるように、デバイス層の上のシリコン基板を全く含まない。他の場合において、1つの薄化ダイの上面は、薄いシリコン基板の上面であってもよい。

【0035】

CMOSコントローラダイ16は、第3のデバイス層32、及び第3のデバイス層32の上のシリコン基板34を含む。第3のデバイス層32は、薄化MEMSダイ14内のMEMS構成要素(図示せず)を制御するCMOSコントローラ(図示せず)、及びCMOSコントローラに結合され、第3のデバイス層32の底面にある複数の第3のダイ接点36を含んでもよい。第3のデバイス層32は、0.1μm～50μmの厚さを有し、誘電層と金属層との組み合わせ(酸化ケイ素、窒化ケイ素、アルミニウム、チタン、銅など)から形成されてもよい。CMOSコントローラダイ16は、完全なダイである。このダイは、25μm～250μmまたは10μm～750μmの厚さを有する完全なシリコン基板34を含む。

【0036】

本明細書において、多層再分布構造18は、上部の第1の誘電パターン38、複数の再分布相互接続40、第2の誘電パターン42及び複数のパッケージ接点44を含む。一実施形態において、薄化ガラスベースダイ12、薄化MEMSダイ14及びCMOSコントローラダイ16は、多層再分布構造18の上に直接存在する。従って、薄化ガラスベースダイ12の第1のデバイス層24、薄化MEMSダイ14の第2のデバイス層28及びCMOSコントローラダイ16の第3のデバイス層32は、第1の誘電パターン38と接触している。加えて、第1のデバイス層24の底面の第1のダイ接点26、第2のデバイス層28の底面の第2のダイ接点30及び第3のデバイス層32の底面の第3のダイ接点36は、第1の誘電パターン38を通じて露出される。

【0037】

この説明のために、再分布相互接続40は、5つの第1の再分布相互接続40(1)及び1つの第2の再分布相互接続40(2)を含む。種々の適用例において、再分布相互接続40は、より少ない、またはより多い第1の再分布相互接続40(1)/第2の再分布相互接続40(2)を含んでもよい。各第1の再分布相互接続40(1)は、1つのパッケージ接点44を第1、第2及び第3のダイ接点26、30及び36のうちの対応する1つに接続する。第2の再分布相互接続40(2)は、1つの第2のダイ接点30を対応する第3のダイ接点36に接続するために使用される。それにより、CMOSコントローラダイ16内のCMOSコントローラ(図示せず)は、薄化MEMSダイ14内のMEMS構成要素(図示せず)に電気的に接続される。本明細書において、各再分布相互接続40は、第1の誘電パターン38を通じて第1、第2及び第3のダイ接点26、30及び36のうちの少なくとも1つに電気的に結合され、第1の誘電パターン38の下に延在する。再分布相互接続40と第1、第2及び第3のダイ接点26、30及び36との間の接続は無ハンダである。

【0038】

第2の誘電パターン42は、第1の誘電パターン38の下に形成される。第2の誘電パターン42は、各第1の再分布相互接続40(1)を部分的に封止する。従って、各第1の再分布相互接続40(1)の一部は、第2の誘電パターン42を通じて露出される。更に、第2の誘電パターン42は、第2の再分布相互接続40(2)を完全に封止する。従つて、第2の再分布相互接続40(2)は、第2の誘電パターン42を通じて一部たりとも露出されない。種々の適用例において、第2の誘電パターン42を通じて再分布相互接続

10

20

30

40

50

4 0 に電気的に結合された追加の再分布相互接続（図示せず）が存在してもよく、追加の誘電パターン（図示せず）が、追加の再分布相互接続のそれぞれを部分的に封止するために第 2 の誘電パターン 4 2 の下に形成される。

【 0 0 3 9 】

この実施形態において、各パッケージ接点 4 4 は、多層再分布構造 1 8 の底面に設けられ、対応する第 1 の再分布相互接続 4 0 ( 1 ) に、第 2 の誘電パターン 4 2 を通じて電気的に結合される。従って、第 1 の再分布相互接続 4 0 ( 1 ) は、パッケージ接点 4 0 を第 1 、第 2 及び第 3 のダイ接点 2 6 、 3 0 及び 3 6 のうちの特定の 1 つに接続する。本明細書において、パッケージ接点 4 4 は、互いに隔離され、第 2 の誘電パターン 4 2 の下に延在する。それにより、空隙 4 6 が、各パッケージ接点 4 4 の周囲に形成される。空隙 4 6 は、薄化ガラスベースダイ 1 2 の下に、かつ／または薄化MEMSダイ 1 4 の下に延在し得る。

10

【 0 0 4 0 】

更に、多層再分布構造 1 8 は、ガラス纖維を含まなくともよく、または無ガラスであってもよい。ここで、ガラス纖維とは、より大きいグループになるように捩られた個々のガラスストランドを指す。次いで、これらのガラスストランドを編み込んで纖維にしてもよい。第 1 の誘電パターン 3 8 及び第 2 の誘電パターン 4 2 は、ベンゾシクロブテン ( BCB ) またはポリイミドによって形成されてもよい。再分布相互接続 4 0 は、銅または他の好適な金属によって形成されてもよい。パッケージ接点 4 4 は、銅、金、ニッケル及びパラジウムのうちの少なくとも 1 種によって形成されてもよい。多層再分布構造 1 8 は、 $2 \mu m \sim 300 \mu m$  の厚さを有する。

20

【 0 0 4 1 】

第 1 のモールドコンパウンド 2 0 は、多層再分布構造 1 8 の上面の上に存在し、薄化ガラスベースダイ 1 2 及び薄化MEMSダイ 1 4 の周囲に存在し、CMOSコントローラダイ 1 6 を封止する。更に、第 1 のモールドコンパウンド 2 0 は、薄化ガラスベースダイ 1 2 の上面を超えて延在して、第 1 のモールドコンパウンド 2 0 内に、かつ薄化ガラスベースダイ 1 2 の上に第 1 の開口 4 8 を画定し、薄化MEMSダイ 1 4 の上面を超えて延在して、第 1 のモールドコンパウンド 2 0 内に、かつ薄化MEMSダイ 1 4 の上に第 2 の開口 5 0 を画定する。ここで、薄化ガラスベースダイ 1 2 の上面は、第 1 の開口 4 8 の底部に露出され、薄化MEMSダイ 1 4 の上面は第 2 の開口 5 0 の底部に露出される。

30

【 0 0 4 2 】

第 2 のモールドコンパウンド 2 2 は、第 1 及び第 2 の開口 4 8 及び 5 0 を実質的に充填し、薄化ガラスベースダイ 1 2 の上面及び薄化MEMSダイ 1 4 の上面と接触している。第 2 のモールドコンパウンド 2 2 は、 $1 E 60 hm - cm$  を超える電気抵抗率を有し得る。第 2 のモールドコンパウンド 2 2 の電気抵抗率が大きいことにより、薄化MEMSダイ 1 4 のMEMS構成要素（図示せず）の高周波における Q 値 ( Q ) を改善することができる。

【 0 0 4 3 】

第 2 のモールドコンパウンド 2 2 は、PPS（ポリフェニルスルフィド）、窒化ホウ素またはアルミナ熱添加剤がドープされたオーバーモールドエポキシなどの、 $2 W / m \cdot K$  を超える熱伝導率を有する熱可塑性材料または熱硬化性材料によって形成されてもよい。第 2 のモールドコンパウンド 2 2 は、 $2 W / m \cdot K$  未満の熱伝導率を有する有機エポキシ樹脂系から形成されてもよい。第 2 のモールドコンパウンド 2 2 は、第 1 のモールドコンパウンド 2 0 と同じ、または異なる材料によって形成されてもよい。しかしながら、第 2 のモールドコンパウンド 2 2 とは異なり、第 1 のモールドコンパウンド 2 0 は電気抵抗率の要件を持たない。本明細書において、第 2 のモールドコンパウンド 2 2 の一部は、第 1 のモールドコンパウンド 2 0 の上面の上に存在してもよい。第 2 のモールドコンパウンド 2 2 は、第 1 のモールドコンパウンド 2 0 によって CMOSコントローラダイ 1 6 から隔離されていることに注意されたい。CMOSコントローラダイ 1 6 の上面は、第 1 のモールドコンパウンド 2 0 と接触している。

40

【 0 0 4 4 】

50

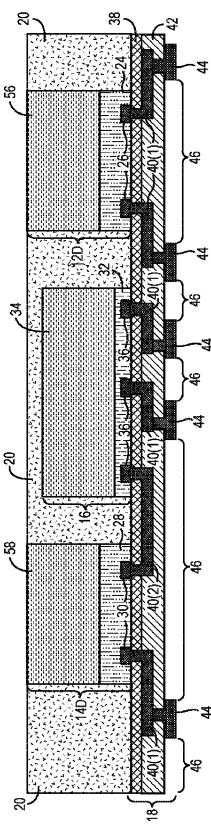

図2～13は、図1に示した例示的なウェーハレベルパッケージ10を製作するための例示的なステップを提供する。例示的なステップは連続的に示されているが、例示的なステップは必ずしも順序依存ではない。いくつかのステップは、提示された順序とは異なる順序で行われてもよい。更に、本開示の範囲内の工程は、図2～13に示したステップより少ない、またはより多いステップを含んでもよい。

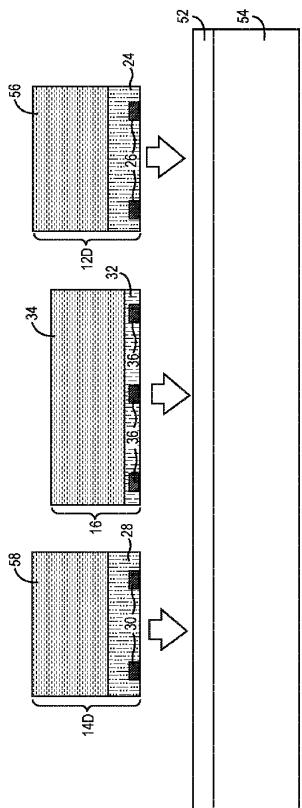

#### 【0045】

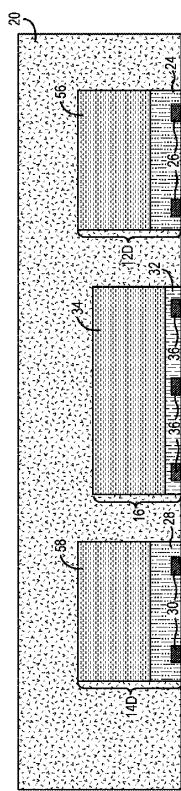

最初に、図2に示すように、支持体54の上面に粘着層52を塗布する。次いで、図3に示すように、ガラスベースダイ12D、MEMSダイ14D及びCMOSコントローラダイ16を粘着層52に取り付ける。種々の適用例において、粘着層52に取り付けられたダイは、より少なくともよく、またはより多くてもよい。例えば、いくつかの適用例において、粘着層52に取り付けられたガラスベースダイ12Dのみが存在してもよく、いくつかの適用例において、粘着層52に取り付けられたMEMSダイ14D及びCMOSコントローラダイ16のみが存在してもよい。

10

#### 【0046】

ガラスベースダイ12Dは、第1のデバイス層24、及び第1のデバイス層24の上の第1のシリコン基板56を含む。従って、第1のデバイス層24の底面はガラスベースダイ12Dの底面であり、第1のシリコン基板56の背面はガラスベースダイ12Dの上面である。第1のシリコン基板56は5μm～750μmの厚さを有する。ガラスベースダイ12Dは、75μm～250μmまたは10μm～1750μmの厚さを有する。

20

#### 【0047】

MEMSダイ14Dは、第2のデバイス層28、及び第2のデバイス層28の上の第2のシリコン基板58を含む。従って、第2のデバイス層28の底面はMEMSダイ14Dの底面であり、第2のシリコン基板58の背面はMEMSダイ14Dの上面である。第2のシリコン基板58は5μm～750μmの厚さを有する。MEMSダイ14Dは、75μm～250μmまたは10μm～1750μmの厚さを有する。この実施形態において、CMOSコントローラダイ16は、ガラスベースダイ12D及びMEMSダイ14Dより低くてもよい。種々の適用例において、CMOSコントローラダイ18は、ガラスベースダイ12D及びMEMSダイ14Dと同じ高さであってもよく、またはCMOSコントローラダイ18は、ガラスベースダイ12D及びMEMSダイ14Dより高くてもよい。

30

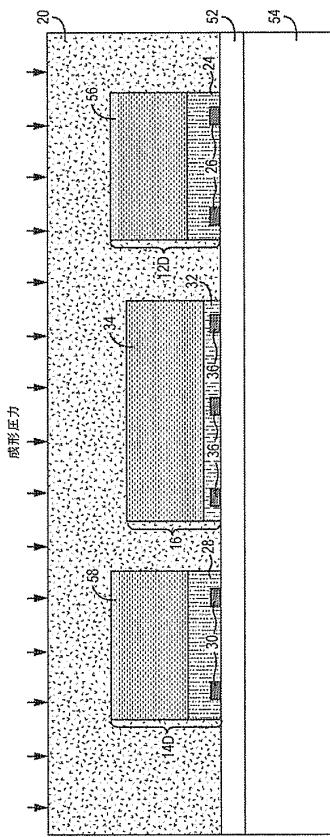

#### 【0048】

次に、図4に示すように、粘着層52の上に第1のモールドコンパウンド20を塗布して、ガラスベースのダイ12D、MEMSダイ14D及びCMOSコントローラダイ16を封止する。第1のモールドコンパウンド20は、シート成形、オーバーモールディング、圧縮成形、転写成形、ダムフィル封止またはスクリーン印刷封止などの各種手順によって塗布されてもよい。典型的な圧縮成形において、第1のモールドコンパウンド20を塗布するために用いられる成形圧力は100psi～1000psiである。ガラスベースダイ12D、MEMSダイ14D及びCMOSコントローラダイ16は比較的厚く、かつガラスベースダイ12D、MEMSダイ14D及びCMOSコントローラダイ16の底面は基本的に平坦であるため、この成形ステップ中、ガラスベースダイ12Dにも、MEMSダイ14Dにも、CMOSコントローラダイ16にも垂直変形は生じ得ない。

40

#### 【0049】

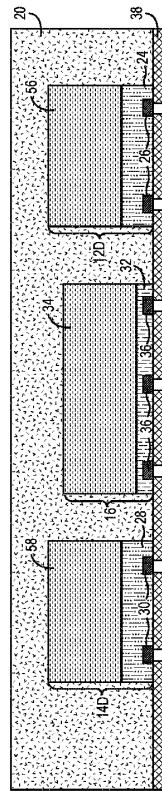

第1のモールドコンパウンド20は、有機エポキシ樹脂系などであってもよい。この樹脂系は、ガラスベースダイ12D、MEMSダイ14D及びCMOSコントローラダイ16を水酸化カリウム(KOH)、水酸化ナトリウム(NaOH)及びアセチルコリン(ACH)などのエッティング薬品から保護するためのエッティング液バリアとして使用することができる。次いで、硬化工程(図示せず)を利用して第1のモールドコンパウンド20を硬化させる。硬化温度は100～320である。この温度は、どの材料を第1のモールドコンパウンド20として使用するかに依存する。次いで、図5に示すように、粘着層52及び支持体54を除去して、第1のデバイス層24の底面、第2のデバイス層28の底面及び第3のデバイス層32の底面を露出させる。粘着層52及び支持体54の除去は、

50

粘着層 5 2 を加熱することによってなされてもよい。

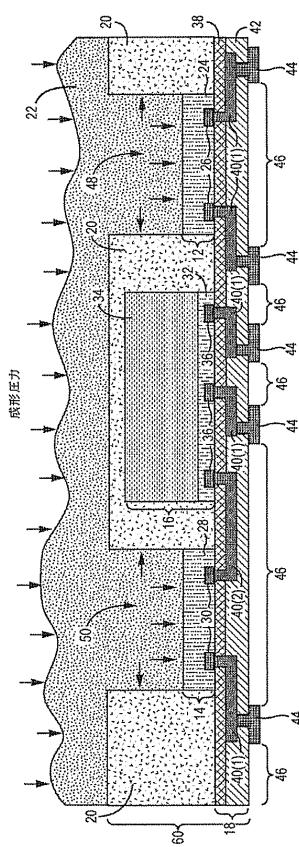

【 0 0 5 0 】

図 6 ~ 9 を参照すると、多層再分布構造 1 8 が、本開示の一実施形態に従って形成される。図 6 に示すように、ガラスベースダイ 1 2 D、MEMS ダイ 1 4 D 及び CMOS コントローラダイ 1 6 の下に第 1 の誘電パターン 3 8 を最初に形成する。従って、第 1、第 2 及び第 3 のダイ接点 2 6、3 0 及び 3 6 は、第 1 の誘電パターン 3 8 を通じて露出される。

【 0 0 5 1 】

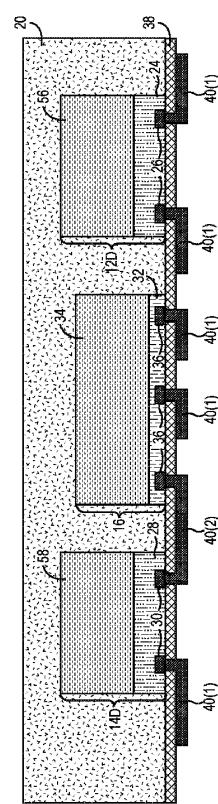

次に、再分布相互接続 4 0 を図 7 に示すように形成する。本明細書において、再分布相互接続 4 0 は、5 つの第 1 の再分布相互接続 4 0 ( 1 ) 及び 1 つの第 2 の再分布相互接続 4 0 ( 2 ) を含む。種々の適用例において、再分布相互接続 4 0 は、より少ない、またはより多い第 1 の再分布相互接続 4 0 ( 1 ) / 第 2 の再分布相互接続 4 0 ( 2 ) を含んでもよい。第 1 の再分布相互接続 4 0 ( 1 ) は、第 1 の誘電パターン 3 8 を通じて第 1、第 2 及び第 3 のダイ接点 2 6、3 0 及び 3 6 に電気的に結合され、第 1 の誘電パターン 3 8 の下に延在する。第 2 の再分布相互接続 4 0 ( 2 ) は、1 つの第 2 のダイ接点 3 0 を対応する第 3 のダイ接点 3 6 に接続するために使用される。それにより、CMOS コントローラダイ 1 6 内の CMOS コントローラ ( 図示せず ) は、薄化 MEMS ダイ 1 4 内の MEMS 構成要素 ( 図示せず ) に電気的に接続される。第 2 の再分布相互接続 4 0 ( 2 ) も、第 1 の誘電パターン 3 8 の下に延在し得る。再分布相互接続 4 0 と第 1、第 2 及び第 3 のダイ接点 2 6、3 0 及び 3 6 との間の接続は無ハンダである。

10

【 0 0 5 2 】

図 8 に示すように、第 2 の誘電パターン 4 2 を第 1 の誘電パターン 3 8 の下に形成して、各第 1 の再分布相互接続 4 0 ( 1 ) を部分的に封止する。従って、各第 1 の再分布相互接続 4 0 ( 1 ) の一部は、第 2 の誘電パターン 4 2 を通じて露出される。更に、第 2 の誘電パターン 4 2 は、第 2 の再分布相互接続 4 0 ( 2 ) を完全に封止する。従って、第 2 の再分布相互接続 4 0 ( 2 ) は、第 2 の誘電パターン 4 2 を通じて一部たりとも露出されない。最後に、図 9 に示すように、パッケージ接点 4 4 及び空隙 4 6 を形成する。各パッケージ接点 4 4 は、第 2 の誘電パターン 4 2 を通じて、対応する第 1 の再分布相互接続 4 0 ( 1 ) の露出部に結合される。従って、第 1 の再分布相互接続 4 0 ( 1 ) は、パッケージ接点 4 4 を第 1、第 2 及び第 3 のダイ接点 2 6、3 0 及び 3 6 のうちの特定の 1 つに接続する。加えて、パッケージ接点 4 4 は、互いに隔離され、第 2 の誘電パターン 4 2 の下に延在する。それにより、空隙 4 6 が、各パッケージ接点 4 4 の周囲に同時に形成される。

20

【 0 0 5 3 】

多層再分布構造 1 8 を形成した後、図 1 0 に示すように、第 1 のモールドコンパウンド 2 0 を薄化して、ガラスベースダイ 1 2 D の第 1 のシリコン基板 5 6 及び MEMS ダイ 1 4 D の第 2 のシリコン基板 5 8 を露出させる。薄化手順は、機械的研磨工程によって行われてもよい。CMOS コントローラダイ 1 6 は MEMS ダイ 1 4 D とガラスベースダイ 1 2 D との両方より高さが低いため、CMOS コントローラダイ 1 6 のシリコン基板 3 4 は露出せず、第 1 のモールドコンパウンド 2 0 によって依然として封止される。

30

【 0 0 5 4 】

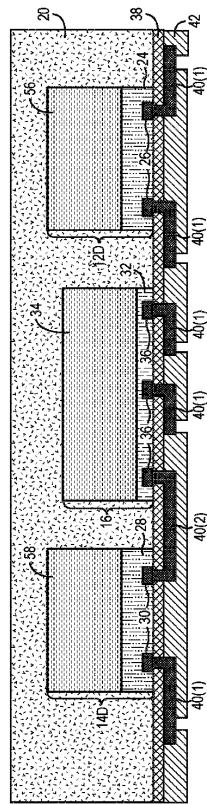

次に、図 1 1 に示すように、第 1 のシリコン基板 5 6 及び第 2 のシリコン基板 5 8 を実質的に除去して、先行パッケージ 6 0 を提供する。ガラスベースダイ 1 2 D から第 1 のシリコン基板 5 6 を除去することにより、薄化ガラスベースダイ 1 2 が提供され、第 1 のモールドコンパウンド 2 0 内に、かつ薄化ガラスベースダイ 1 2 の上に第 1 の開口 4 8 が形成される。MEMS ダイ 1 4 D から第 2 のシリコン基板 5 8 を除去することにより、薄化 MEMS ダイ 1 4 が提供され、第 1 のモールドコンパウンド 2 0 内に、かつ薄化 MEMS ダイ 1 4 の上に第 2 の開口 5 0 が形成される。ここで、シリコン基板を実質的に除去することとは、シリコン基板全体のうちの少なくとも 9 5 % を除去し、最大でも 2  $\mu$ m のシリコン基板を残すことを指す。所望の場合において、第 1 及び第 2 のシリコン基板 5 6 及び 5 8 は完全に除去される。それにより、薄化ガラスベースダイ 1 2 の第 1 のデバイス層 2 4 は第 1 の開口 4 8 の底部に露出され、薄化 MEMS ダイ 1 4 の第 2 のデバイス層 2 8 は第

40

50

2 の開口 5 0 の底部に露出される。

【 0 0 5 5 】

第 1 及び第 2 のシリコン基板 5 6 及び 5 8 を実質的に除去することは、湿式 / 乾式エッチング液薬品を用いたエッチング工程によってなされてもよく、このエッチング液薬品は、T M A H、K O H、A C H、N a O H などであってもよい。第 1 のデバイス層 2 4 と第 2 のデバイス層 2 8 とは共に、これらの湿式 / 乾式エッチング薬品に耐性のあるガラス材料から形成される。それにより、第 1 のデバイス層 2 4 内の電子的構成要素（図示せず）及び第 2 のデバイス層 2 8 内のM E M S 構成要素（図示せず）は、これらの湿式 / 乾式エッチング薬品による損傷を受けなくなる。第 1 のモールドコンパウンド 2 0 は、C M O S コントローラダイ 1 6 を封止し、これを湿式 / 乾式エッチング液薬品から保護する。いくつ 10

かの適用例において、保護層（図示せず）を多層再分布構造 1 8 の底面に配置して、パッケージ接点 4 4 をエッチング液薬品から保護してもよい。保護層は、エッチング工程の前に塗布され、エッチング工程の後に除去される。更に、C M O S コントローラダイ 1 6 のシリコン基板 3 4 が第 1 のモールドコンパウンド 2 0 によって封止されない場合（いくつ 20

かの適用例において、C M O S コントローラダイ 1 6 が、ガラスベースダイ 1 2 及びM E M S ダイ 1 4 と同じ高さを有する、またはそれより高い場合、C M O S コントローラダイ 1 6 のシリコン基板 3 4 は、薄化工程中に露出することになる）、C M O S コントローラダイ 1 6 を湿式 / 乾式エッチング液薬品から保護するために、シリコン基板 3 4 の上に配置された追加の保護層（図示せず）が存在してもよい。追加の保護層は、エッチング工程の前に塗布され、エッチング工程の後に除去される。

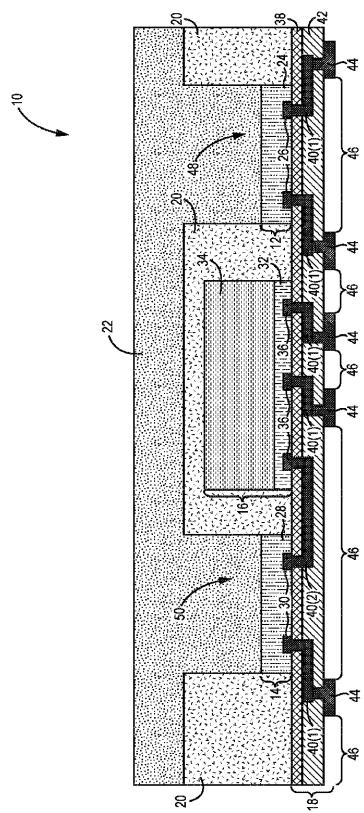

【 0 0 5 6 】

次いで、図 1 2 に示すように、第 2 のモールドコンパウンド 2 2 を塗布して、第 1 及び第 2 の開口 4 8 及び 5 0 を実質的に充填する。ここで、開口を実質的に充填することとは、開口全体のうちの少なくとも 7 5 % を充填することを指す。第 2 のモールドコンパウンド 2 2 は、薄化ガラスベースダイ 1 2 の上面及び薄化M E M S ダイ 1 4 の上面の上に直接存在する。第 1 のシリコン基板 5 6 が第 1 の開口 4 8 内に残らず、かつ第 2 のシリコン基板 5 8 が第 2 の開口 5 0 内に残らない場合、第 2 のモールドコンパウンド 2 2 は、第 1 のデバイス層 2 4 及び第 2 のデバイス層 2 8 の上に直接存在する。加えて、第 2 のモールドコンパウンド 2 2 は、更に、第 1 のモールドコンパウンド 2 0 の上に存在してもよい。いくつ 30

かの適用例において、第 2 のモールドコンパウンド 2 2 を塗布して第 1 及び第 2 の開口 4 8 及び 5 0 を実質的に充填する前に、先行パッケージ 6 0 を剛性支持体（図示せず）に取り付けてよい。剛性支持体（図示せず）は、先行パッケージ 6 0 の機械的支持を補助するのに役立つことができ、薄化ガラスベースダイ 1 2 及び薄化M E M S ダイ 1 4 の更なる变形を防ぐのに役立つことができる。

【 0 0 5 7 】

第 2 のモールドコンパウンド 2 2 は、シート成形、オーバーモールディング、圧縮成形、転写成形、ダムフィル封止及びスクリーン印刷封止などの各種手順によって塗布されてもよい。第 2 のモールドコンパウンド 2 2 の成形工程中、融解及び成形圧力は、先行パッケージ 6 0 全体にわたって同一ではない。薄化ガラスベースダイ 1 2 と薄化ガラスベースダイ 1 2 の直下の多層再分布構造 1 8 の第 1 の部分との第 1 の組み合わせ、及び薄化M E M S ダイ 1 4 と薄化M E M S ダイ 1 4 の直下の多層再分布構造 1 8 の第 2 の部分との第 2 の組み合わせは、先行パッケージ 6 0 の他の部分より大きい成形圧力を受ける場合がある。

【 0 0 5 8 】

一実施形態において、第 2 のモールドコンパウンド 2 2 は、2 W / m · K を超える熱伝導率を有する熱可塑性材料または熱硬化性材料から形成される。第 2 のモールドコンパウンド 2 0 を塗布するために用いられる典型的な成形圧力（圧縮成形）は 2 5 0 p s i ~ 1 0 0 0 p s i である。ここで、薄化ガラスベースダイ 1 2 の第 1 のデバイス層 2 4 は、少なくとも 7 5 0 p s i の成形圧力に耐えるように 7 0  $\mu$  m ~ 1 0 0 0  $\mu$  m の厚さを有し得る。従って、空隙 4 6 の第 1 の部分が薄化ガラスベースダイ 1 2 の垂直下方にあり、空隙 4 6 の第 1 の部分内に更なる機械的支持がない場合でも、薄化ガラスベースダイ 1 2 の垂直 40

50

変形は生じ得ない、または許容程度内であり得る。同様に、薄化MEMSダイ14の第2のデバイス層28は、少なくとも750psiの成形圧力に耐えるように70μm~100μmの厚さを有する。従って、空隙46の第2の部分が薄化MEMSダイ14の垂直下方にあり、空隙46の第2の部分内に更なる機械的支持がない場合でも、薄化MEMSダイ14の垂直変形は生じ得ない、または許容程度内であり得る。

#### 【0059】

薄化ガラスベースダイ12と薄化MEMSダイ14とは共に低熱生成のダイであるため、薄化ガラスベースダイ12及び薄化MEMSダイ14の上に直接存在する第2のモールドコンパウンド22は、高熱伝導性を有することを必要としない。別の実施形態において、第2のモールドコンパウンド22は、2W/m·K未満の熱伝導率を有する有機エポキシ樹脂系から形成されてもよい。第2のモールドコンパウンド20を塗布するために用いられる典型的な成形圧力（オーバーモールディング）は100psi~1000psiである。ここで、薄化ガラスベースダイ12の第1のデバイス層24は、少なくとも100psiの成形圧力に耐える5μm~1000μmの厚さを有し得る。従って、空隙46の第1の部分が薄化ガラスベースダイ12の垂直下方にあり、空隙46の第1の部分内に更なる機械的支持がない場合でも、薄化ガラスベースダイ12の垂直変形は生じ得ない、または許容程度内であり得る。同様に、薄化MEMSダイ14の第2のデバイス層28は、少なくとも100psiの成形圧力に耐える5μm~1000μmの厚さを有し得る。従つて、空隙46の第2の部分が薄化MEMSダイ14の垂直下方にあり、空隙46の第2の部分内に更なる機械的支持がない場合でも、薄化MEMSダイ14の垂直変形は生じ得ない、または許容程度内であり得る。

10

#### 【0060】

CMOSコントローラダイ16のシリコン基板34は、先行パッケージ60に残存し、第1のモールドコンパウンド20によって封止されることに注意されたい。従つて、CMOSコントローラダイ16の第3のデバイス層36は、垂直変形を回避するためにガラス材料から形成されることも、比較的厚い厚さを有することも必要としない。第3のデバイス層36は、誘電層と金属層との組み合わせ（酸化ケイ素、窒化ケイ素、アルミニウム、チタン、銅など）から形成されてもよく、0.1μm~50μmの厚さを有する。

20

#### 【0061】

続いて、硬化工程（図示せず）により、第2のモールドコンパウンド22を硬化させる。硬化温度は100~320である。この温度は、どの材料を第2のモールドコンパウンド22として使用するかに依存する。最後に、図13に示すように、第2のモールドコンパウンド22の上面を次いで平坦化して、ウェーハレベルパッケージ10を形成する。第2のモールドコンパウンド22が第1のモールドコンパウンド20の上面を覆っていない場合、第2のモールドコンパウンド22及び/または第1のモールドコンパウンド20の上面が、同一平面となるように平坦化される（図示せず）。平坦化のために機械的研磨工程を利用してもよい。ウェーハレベルパッケージ10をマーキングし、ダイシングし、個片化して、別々の構成要素にしてもよい（図示せず）。

30

#### 【0062】

当業者は、本開示の好ましい実施形態に対する改良及び修正を認めるであろう。このような全ての改良及び修正は、本明細書に開示された概念及び後続する特許請求の範囲内にあるとみなされる。

40

【図面】

【図 1】

FIG. 1

【図2】

FIG. 2

10

20

【 図 3 】

FIG. 3

【図4】

30

40

50

【図5】

FIG. 5

【図6】

FIG. 6

10

20

【図7】

FIG. 7

30

【図8】

FIG. 8

40

50

【 9 】

FIG. 9

【図10】

FIG. 10

【図 1 1】

FIG. 11

## 【図12】

10

20

30

40

50

【図 1 3】

FIG. 13

10

20

30

40

50

---

フロントページの続き

(74)代理人 100188329

弁理士 田村 義行

(72)発明者 ヴァンダミア・ジャン, エドワード

アメリカ合衆国ノース・カロライナ州 27284, カーナーズビル, ウェザーフィールド・レーン

279

(72)発明者 ハモンド, ジョナサン・ヘイル

アメリカ合衆国ノース・カロライナ州 27310, オーク・リッジ, オータム・ゲート・ドライブ

5808

(72)発明者 コスタ, ジュリオ・シー

アメリカ合衆国ノース・カロライナ州 27310, オーク・リッジ, アシュトン・パーク・ドライブ

6601

審査官 井上 和俊

(56)参考文献 米国特許出願公開第 2015/0262844 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 25/18

H01L 23/12

H01L 23/29