(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6278608号

(P6278608)

(45) 発行日 平成30年2月14日(2018.2.14)

(24) 登録日 平成30年1月26日(2018.1.26)

(51) Int.Cl.

F 1

H01L 21/76 (2006.01)

H01L 21/76

H01L 27/146 (2006.01)

H01L 27/146

H04N 5/369 (2011.01)

H04N 5/369

L

A

請求項の数 15 (全 13 頁)

(21) 出願番号

特願2013-80836 (P2013-80836)

(22) 出願日

平成25年4月8日(2013.4.8)

(65) 公開番号

特開2014-204047 (P2014-204047A)

(43) 公開日

平成26年10月27日(2014.10.27)

審査請求日

平成28年4月4日(2016.4.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体装置の製造方法であって、

第1面および第2面を有する半導体基板を用意する工程と、

前記第1面上に配された、第1開口を有するマスクを使用して前記半導体基板をエッチングすることによって、前記半導体基板に第1溝を形成する工程と、

前記第1溝を形成する工程の後に、前記第1面上に配された、第2開口を有するマスクを使用して前記半導体基板をエッチングすることによって、前記半導体基板に第2溝を形成する工程と、

前記第2溝を形成する工程の後に、前記第2開口を有するマスクを使用して前記半導体基板にイオンを注入する工程と、

前記イオンを注入する工程の後に、前記第1溝の中に空間が残るよう前記第2溝の中に絶縁体を充填することにより、前記空間および前記絶縁体で構成される素子分離を形成する工程と、

前記第1面と前記第2面との間に光電変換部を形成する工程と、を含み、

前記第2溝を形成する工程では、前記第2開口が前記第1溝の上に位置し、前記第1面に沿った方向における前記第2開口の幅が前記方向における前記第1開口の幅よりも大きく、

前記第2溝は前記第1溝よりも前記第1面に対して浅く形成され、

前記光電変換部は、第1導電型の第1半導体領域と、前記第1半導体領域と前記第1面

10

20

との間に位置し前記第1導電型とは反対の第2導電型の第2半導体領域と、前記第1半導体領域と前記第2面との間に位置する前記第2導電型の第3半導体領域と、を有し、

前記イオンを注入する工程では、前記絶縁体が形成されるべき領域と前記第1半導体領域との間に前記第2導電型の第4半導体領域が形成され、

前記第1半導体領域は、前記第2面に垂直な方向において、前記第4半導体領域と前記第2面との間に位置する部分を有する、

ことを特徴とする半導体装置の製造方法。

**【請求項2】**

前記絶縁体で取り囲まれた半導体素子を形成する工程を更に含む、

ことを特徴とする請求項1に記載の半導体装置の製造方法。 10

**【請求項3】**

前記第1開口の上に第3開口を有するマスクを、前記第1開口を有する前記マスクの上に形成し、

前記第3開口を有する前記マスクを使用して前記第1開口を有する前記マスクのうち前記第3開口に露出している部分を除去して前記第2開口を形成する、

ことを特徴とする請求項1または2に記載の半導体装置の製造方法。

**【請求項4】**

前記第3開口に露出している前記部分の除去は前記第1溝の形成における前記半導体基板のエッチングとともに行われる、

ことを特徴とする請求項3に記載の半導体装置の製造方法。 20

**【請求項5】**

前記第2溝を通して前記半導体基板における前記第2溝と前記第2面との間に位置する領域にイオンを注入する工程を更に含む、

ことを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

**【請求項6】**

前記第2溝を形成する工程の後に、

前記半導体基板の中に半導体領域を形成する工程と、

前記半導体基板を前記第2面の側から薄化する工程と、を更に含み、

前記半導体基板を薄化する工程は、前記半導体基板の前記第1面とは反対側の面上に前記半導体領域が露出するようになされる、 30

ことを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

**【請求項7】**

前記半導体基板を前記第2面の側から薄化する工程を更に含み、

前記半導体基板を薄化する工程は、前記半導体基板の前記第1面とは反対側の面上に前記第1溝が露出するようになされる、

ことを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

**【請求項8】**

前記半導体基板を前記第2面の側から薄化する工程を更に含み、

前記半導体基板を薄化する工程は、前記半導体基板の前記第1面とは反対側の面上に前記第1溝が露出しないようになされる、 40

ことを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

**【請求項9】**

前記半導体基板を薄化する工程の後に、前記半導体基板の前記第1面とは反対側の前記面上に膜を形成する工程を更に含み、前記膜を形成する工程の後に前記第1溝の中に空間が残る、

ことを特徴とする請求項6乃至8のいずれか1項に記載の半導体装置の製造方法。

**【請求項10】**

第1面および第2面を有する半導体基板と、

前記半導体基板に対して前記第1面の側に配置された配線構造と、

前記半導体基板に設けられ、前記第1面に沿った方向において第1の幅を有する部分と 50

、前記第1の幅を有する前記部分よりも前記第2面の側に位置し、前記第1の幅よりも小さい第2の幅を有する部分と、を有する溝と、

前記溝の前記第1の幅を有する前記部分の中に配置された絶縁体と、

前記半導体基板に配置された光電変換部と、を備え、

前記第2の幅を有する前記部分の中に空間を有し、前記絶縁体および前記空間によって素子分離が形成され、

前記光電変換部は、第1導電型の第1半導体領域と、前記第1半導体領域と前記第1面との間に位置し前記第1導電型とは反対の第2導電型の第2半導体領域と、前記第1半導体領域と前記第2面との間に位置する前記第2導電型の第3半導体領域と、を有し、

前記第1半導体領域は、前記第2面に垂直な方向において、前記絶縁体と前記第2面との間に位置する部分を有し、前記第2面に垂直な方向における前記絶縁体と前記第1半導体領域の前記部分との間には、前記絶縁体に接するように前記第2導電型の第4半導体領域が配置されている、

ことを特徴とする半導体装置。

#### 【請求項11】

前記第3半導体領域は、前記第2面に垂直な方向において、前記絶縁体と前記第2面との間に位置する部分を有する、

ことを特徴とする請求項10に記載の半導体装置。

#### 【請求項12】

前記半導体基板に対して前記第2面の側に配置された光透過性の膜を更に備え、

前記膜は前記空間に面するように前記第2面および前記溝を覆う、

ことを特徴とする請求項10又は11に記載の半導体装置。

#### 【請求項13】

前記半導体基板には、

前記光電変換部で発生した電荷が転送されるフローティングディフュージョンと、

前記フローティングディフュージョンの電位をリセットする、あるいは、前記フローティングディフュージョンの電位に応じた信号を出力するトランジスタと、が配置されており、

前記フローティングディフュージョンと前記トランジスタとの間に前記溝が位置している、

ことを特徴とする請求項10乃至12のいずれか1項に記載の半導体装置。

#### 【請求項14】

前記半導体基板に対して前記第2面の側に配置されたマイクロレンズ層を更に備える、

ことを特徴とする請求項10乃至13のいずれか1項に記載の半導体装置。

#### 【請求項15】

請求項10乃至14のいずれか1項に記載の半導体装置と、

前記半導体装置から出力される信号を処理する処理部と、

を備えることを特徴とするカメラ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体装置およびその製造方法に関する。

##### 【背景技術】

##### 【0002】

特許文献1には、固体撮像装置などの半導体装置の製造方法が記載されている。該方法では、フォトダイオードなどの半導体素子がそれぞれ形成された複数の単結晶シリコン層が空隙によって分離された構造を準備し、該複数の単結晶シリコン層の上にタンゲステン膜などの遮光膜、平坦化層、カラーフィルタおよびマイクロレンズを形成する。

##### 【先行技術文献】

##### 【特許文献】

10

20

30

40

50

**【0003】**

【特許文献1】特開2012-15316号公報

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

特許文献1に記載された方法では、複数の単結晶シリコン層の間に形成された空隙を埋めることなく、該複数の単結晶シリコン層の上にタンゲステン膜などの遮光膜を形成する。したがって、空隙の中にも遮光膜としての導電膜が形成される可能性がある。また、空隙の中に遮光膜が形成される度合いが、基板内の位置によって異なる可能性、又は、基板間で異なる可能性がある。そのために、固体撮像装置などの半導体装置の特性にはらつきが生じうる。

10

**【0005】**

本発明は、半導体装置に素子の分離のために形成される複数の空間のばらつきを低減するために有利な技術を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

本発明の1つの側面は、半導体装置の製造方法に係り、前記製造方法は、第1面および第2面を有する半導体基板を用意する工程と、前記第1面上に配された、第1開口を有するマスクを使用して前記半導体基板をエッチングすることによって、前記半導体基板に第1溝を形成する工程と、前記第1溝を形成する工程の後に、前記第1面上に配された、第2開口を有するマスクを使用して前記半導体基板をエッチングすることによって、前記半導体基板に第2溝を形成する工程と、前記第2溝を形成する工程の後に、前記第2開口を有するマスクを使用して前記半導体基板にイオンを注入する工程と、前記イオンを注入する工程の後に、前記第1溝の中に空間が残るように前記第2溝の中に絶縁体を充填することにより、前記空間および前記絶縁体で構成される素子分離を形成する工程と、前記第1面と前記第2面との間に光電変換部を形成する工程と、を含み、前記第2溝を形成する工程では、前記第2開口が前記第1溝の上に位置し、前記第1面に沿った方向における前記第2開口の幅が前記方向における前記第1開口の幅よりも大きく、前記第2溝は前記第1溝よりも前記第1面に対して浅く形成され、前記光電変換部は、第1導電型の第1半導体領域と、前記第1半導体領域と前記第1面との間に位置し前記第1導電型とは反対の第2導電型の第2半導体領域と、前記第1半導体領域と前記第2面との間に位置する前記第2導電型の第3半導体領域と、を有し、前記イオンを注入する工程では、前記絶縁体が形成されるべき領域と前記第1半導体領域との間に前記第2導電型の第4半導体領域が形成され、前記第1半導体領域は、前記第2面に垂直な方向において、前記第4半導体領域と前記第2面との間に位置する部分を有する。

20

**【発明の効果】****【0007】**

本発明によれば、半導体装置に素子の分離のために形成される複数の空間のばらつきを低減するために有利な技術が提供される。

30

**【図面の簡単な説明】****【0008】**

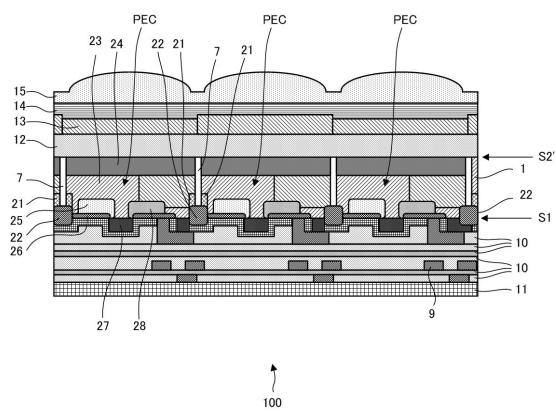

【図1】第1実施形態の固体撮像装置の画素アレイの一部分の断面図。

40

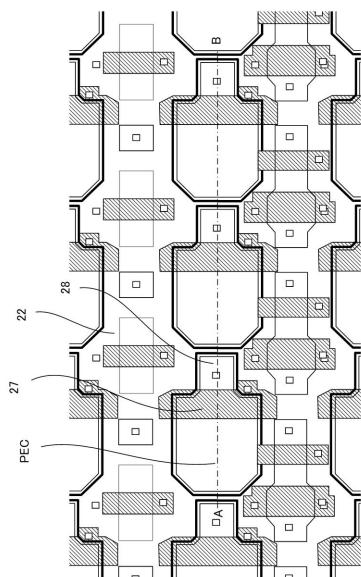

【図2】第1実施形態の固体撮像装置の画素アレイの一部分の平面図。

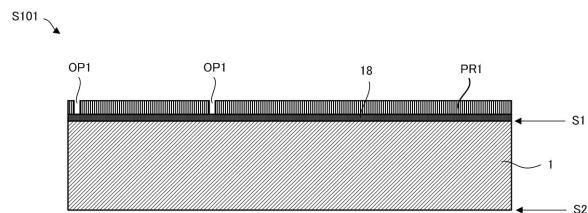

【図3】第1実施形態の固体撮像装置の製造方法を説明する断面図。

【図4】第1実施形態の固体撮像装置の製造方法を説明する断面図。

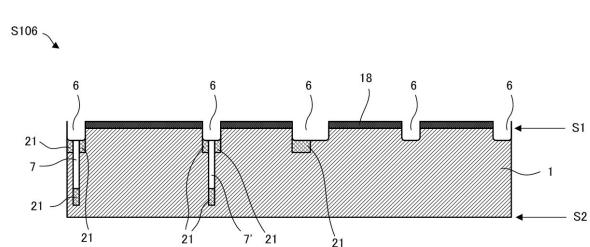

【図5】第1実施形態の固体撮像装置の製造方法を説明する断面図。

【図6】第1実施形態の固体撮像装置の製造方法を説明する断面図。

【図7】第1実施形態の固体撮像装置の製造方法を説明する断面図。

【図8】第2実施形態の固体撮像装置の画素アレイの一部分の断面図。

【図9】第2実施形態の固体撮像装置の製造方法を説明する断面図。

50

**【発明を実施するための形態】**

**【0009】**

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。なお、以下では、本発明を固体撮像装置に適用した例を説明するが、本発明の1つの側面は、素子分離の構造およびその製造方法に特徴を有するのであり、したがって、本発明の当該側面は、固体撮像装置以外の半導体装置にも適用可能である。

**【0010】**

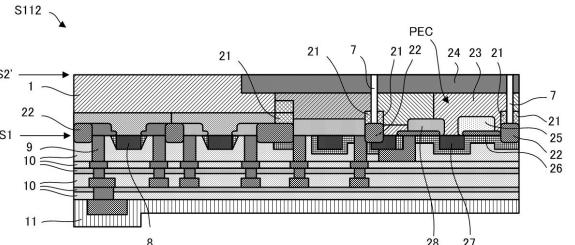

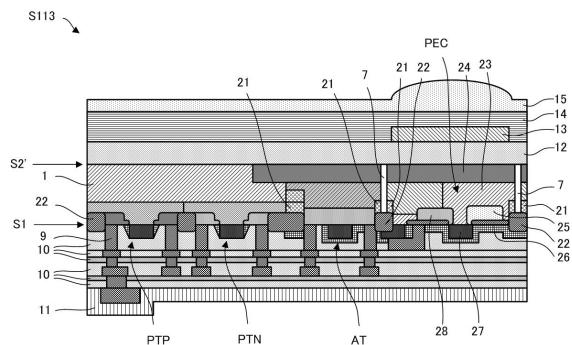

図1は、本発明の第1実施形態の固体撮像装置100の画素アレイの一部分の断面図である。図2は、固体撮像装置100の画素アレイの一部分を示す平面図である。なお、図1は、図2のA-B線に沿った概略断面図であり、3つの光電変換部PECが示されている。

10

**【0011】**

固体撮像装置100は、第1面S1および第2面S2'を有する半導体基板1と、半導体基板1における第1面S1の側に配置された絶縁体22と、半導体基板1の中で絶縁体22から第2面S2'の側に伸びた空間7とを備えうる。固体撮像装置100はまた、第1面S1と第2面S2'との間に形成された複数の素子とを備えうる。該複数の素子は、例えば、光電変換部PEC、フローティングディフェュージョン28、転送ゲート27を含みうる。該複数の素子は、その他、フローティングディフェュージョン28の電位をリセットするリセットトランジスタ、および、フローティングディフェュージョン28の電位に応じた信号を列信号線に出力する増幅トランジスタを含みうる。リセットトランジスタおよび増幅トランジスタは、個々の光電変換部PECに対して設けられてもよいし、複数の光電変換部PECあるいは複数の画素によって共有されてもよい。固体撮像装置100の各画素は、少なくとも1つの光電変換部PECを含む。固体撮像装置100は、絶縁体22および空間7に隣接する位置に形成されたチャネルストップ21を備えうる。

20

**【0012】**

絶縁体22は、例えば、STI(Shallow Trench Isolation)を構成する。空間7は、気体で満たされてもよいし、減圧状態または真空状態に維持されてもよい。絶縁体22および空間7によって、素子と素子とを分離する素子分離が形成されている。素子と素子との分離とは、例えば、相互に隣接する光電変換部PECと光電変換部PECとの分離でありうる。あるいは、素子と素子との分離とは、画素と画素との分離でありうる。あるいは、素子と素子との分離とは、相互に隣接する光電変換部PECとトランジスタ(例えば、リセットトランジスタ、増幅トランジスタ)との分離でありうる。複数の素子(例えば光電変換部PEC)のうち隣接する素子を隔てる方向における空間7の幅(図1における横方向の幅)は、当該方向における絶縁体22の幅より小さい。空間7の幅は、半導体基板1の深さ方向(第1面S1の側から第2面S2'の側に向かう方向)に沿って一定であってもよいし、第1面S1から離れる従って大きくなっても小さくなってもよい。以下では、幅は、複数の素子(例えば光電変換部PEC)のうち隣接する素子を隔てる方向における寸法を意味するものとする。

30

**【0013】**

図2に例示されるように、素子分離を構成する絶縁体22は、光電変換部PECなどの各素子を取り囲むように配置されている。該素子分離を構成する空間7も、光電変換部PECなどの各素子を取り囲むように配置されている。

40

**【0014】**

光電変換部PECは、例えば、第1導電型の半導体領域で構成される電荷蓄積領域25、電荷蓄積領域25に接するように配置された第1導電型の半導体領域23、半導体領域23に接するように配置された第2導電型の半導体領域24を含みうる。光電変換部PECは、電荷蓄積領域25と第1面S1との間に第2導電型の半導体領域26を含んでもよい。第1導電型がn型である場合は第2導電型はp型であり、第1導電型がp型である場合は第2導電型はn型である。転送ゲート27は、ゲート電極である。転送ゲート27、電荷蓄積領域25およびフローティングディフェュージョン28は、MOS構造を構成して

50

いる。

**【0015】**

半導体基板1の第1面の側には、複数の層間絶縁膜10および複数の配線層9で構成される配線構造と、該配線構造の上に配置されたパッシベーション膜11とが配置されうる。半導体基板1の第2面の側には平坦化膜12、カラーフィルタ層13、キャッピング層14、マイクロレンズ層15が積層されうる。なお、平坦化膜12を構成する材料は、空間7には殆ど侵入しない。

**【0016】**

図1および図2に例示される固体撮像装置100は、配線構造が配置された第1面の側と反対側、即ち第2面の側に光を入射させるように構成された裏面照射型の固体撮像装置である。マイクロレンズ層15のマイクロレンズを通った光は、カラーフィルタ層13を通して半導体基板1の第2面S2'に入射し、光電変換部PECで電荷を発生させる。発生した電荷は、電荷蓄積領域25に蓄積され、転送ゲート27によって形成されるチャネルを通してフローティングディフュージョン28に転送される。フローティングディフュージョン28の電位は、転送されてきた電荷の量に応じて変化する。增幅トランジスタは、フローティングディフュージョン28の電位に応じた信号を列信号線に出力する。

10

**【0017】**

半導体基板1がシリコンで構成され、絶縁体22がシリコン酸化物で構成される場合、シリコン酸化物および空間7の屈折率はシリコンより小さい。よって、光電変換部PECに入射した光は、空間7と光電変換部PECとの界面および絶縁体22と光電変換部PECとの界面で反射される。これにより、1つの画素の光電変換部PECに入射した光が隣接する画素の光電変換部PECおよび/またはフローティングディフュージョン28に侵入することを低減することができる。これにより混色を低減したり、画像の解像度を向上させたりすることができる。

20

**【0018】**

以下、図3～図7を参照しながら固体撮像装置100の製造方法を例示的に説明する。ここで、図3～図7には、1つの画素の光電変換部PECおよびトランジスタAT(例えば、リセットトランジスタ、増幅トランジスタ)、ならびに、周辺回路のNMOSトランジスタPTNおよびPMOSトランジスタPTPに相当する部分が示されている。

**【0019】**

30

工程S101～S105は、第1面S1および第2面S2を有する半導体基板1の第1面S1を処理することによって、空間(第1部分)7および第2部分6を有する溝Tを形成する工程である。典型的には、半導体基板1は、シリコン基板である。

**【0020】**

工程S101では、半導体基板1の第1面の上に積層膜18を形成する。積層膜18は、例えば、半導体基板1の第1面S1の上に形成されたシリコン酸化膜、該シリコン酸化膜の上に形成されたポリシリコン膜、および、該ポリシリコン膜の上に形成されたシリコン窒化膜を含みうる。該シリコン酸化膜は、例えば、厚さが5nm～30nmの範囲内であり、例えば、常圧の熱酸化によって形成されうる。熱酸化は、例えば、温度700～1150で、酸素、または、水素/酸素混合気体中で行うことができる。該ポリシリコン膜は、例えば、厚さが10nm～100nmの範囲内であり、例えば、温度600～700、圧力5Pa～100Paで、モノシラン(SiH<sub>4</sub>)を使って成膜されうる。該シリコン窒化膜は、例えば、厚さが30nm～200nmの範囲内であり、温度700～900、圧力5Pa～100Paで、アンモニアとモノシランまたはジクロロシラン(Si<sub>2</sub>H<sub>2</sub>Cl<sub>2</sub>)との混合気体を使って成膜されうる。

40

**【0021】**

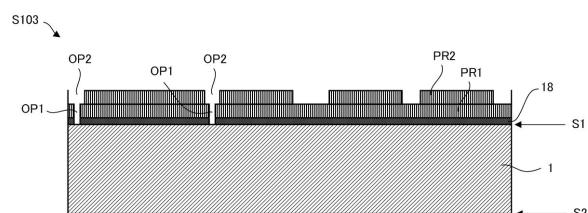

また、工程S101では、更に、積層膜18の上に、第1開口OP1を有する第1フォトレジストPR1を形成する。第1開口OP1を有する第1フォトレジストPR1は、フォトリソグラフィー工程によって形成されうる。第1開口OP1は、空間(第1部分)7の領域(即ち、幅および該幅に直交する方向の寸法)を規定する。

50

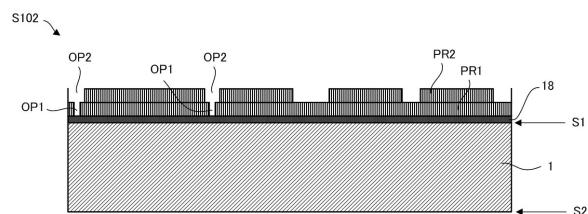

## 【0022】

工程S102では、第2開口OP2を有する第2フォトレジストPR2を第1フォトレジストPR1の上に形成する。第2開口OP2を有する第2フォトレジストPR2は、フォトリソグラフィー工程によって形成されうる。第2開口OP2は、第2部分6の領域(即ち、幅および該幅に直交する方向の寸法)を規定する。

## 【0023】

工程S103では、第1フォトレジストPR1および第2フォトレジストPR2をエッティングマスクとして使用して半導体基板1の上の積層膜18をエッティングする。工程S104では、第1フォトレジストPR1および第2フォトレジストPR2をエッティングマスクとして使用して半導体基板1をエッティングする。

10

## 【0024】

ここで、積層膜18は、前述のとおり、半導体基板1の側から順に、シリコン酸化膜、ポリシリコン膜、シリコン窒化膜を含みうる。シリコン窒化膜は、例えば、四フッ化メタン( $\text{CF}_4$ )、二フッ化メタン( $\text{CH}_2\text{F}_2$ )、三フッ化メタン( $\text{CHF}_3$ )、六フッ化イオウ( $\text{SF}_6$ )などのフロン系ガスを用いてプラズマエッティングされうる。該フロン系ガスは、単独または他のフロン系ガスと組み合わせて、および/または、アルゴンまたはヘリウムなどの不活性ガスまたは水素と混合して用いられてもよい。

## 【0025】

ポリシリコン膜は、臭化水素(HBr) / 塩素( $\text{Cl}_2$ ) / 酸素の混合気体を用いてプラズマエッティングされうる。該混合気体は、アルゴンまたはヘリウムなどの不活性ガスと混合して用いられてもよい。シリコン酸化膜は、シリコン窒化膜と同様のフロン系ガスを酸素と混合して用いてプラズマエッティングされうる。この混合気体は、単独または他のフロン系ガスと組み合わせて、および/または、アルゴンやヘリウムなどの不活性ガスと混合して用いられてもよい。

20

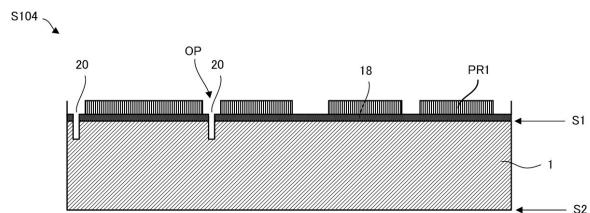

## 【0026】

工程S104では、第1開口OP1を通して半導体基板1をエッティングして半導体基板1に第1開口OP1の幅に従う溝20を形成する。また、工程S104では、溝20を形成するとともに、第1フォトレジストPR1のうち第2開口OP2に露出している部分を除去して第1フォトレジストPR1に第2開口OP2の寸法に従う開口OPを形成する。工程S104では、誘導結合プラズマ(ICP)装置を用いて六フッ化イオウとフロン $\text{C}_1\text{F}_8$ ( $\text{C}_4\text{F}_8$ )を交互に流してエッティングを行なうボッシュプロセスが採用されうる。一例において、溝20の幅は $0.1\mu\text{m}$ 、溝20の深さは $3\mu\text{m} \sim 5\mu\text{m}$ の範囲内にされうる。工程S104では、六フッ化イオウ/酸素混合気体を用いてダイポールリングマグネットロン(DRM)方式のプラズマエッティングを行ってもよい。この場合には、レジストエッチバック技術によって、素子形成領域のレジストパターンのみが残されうる。

30

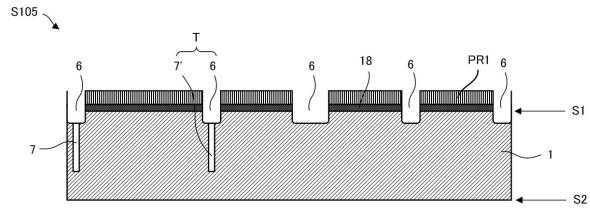

## 【0027】

工程S105では、第1フォトレジストPR1に形成された開口OPを通して積層膜18、更には半導体基板1をエッティングすることにより半導体基板1に第1部分7'および第2部分6を形成する。ここで、第1部分7'は開口OPによって規定され、第2部分6は溝20によって規定される。したがって、第1部分7'の領域(即ち、幅および該幅に直交する方向の寸法)は、第1フォトレジストPR1に形成されていた第1開口OP1によって規定される。また、第2部分6の領域(即ち、幅および該幅に直交する方向の寸法)は、第2フォトレジストPR2に形成されていた第2開口OP2によって規定される。積層膜18のエッティングの条件は、工程S103における積層膜18のエッティングの条件に従いうる。半導体基板1は、例えば、臭化水素(HBr) / 塩素( $\text{Cl}_2$ ) / 酸素の混合気体を用いてプラズマエッティングされうる。該混合気体は、アルゴンまたはヘリウムなどの不活性ガスと混合して用いられてもよい。半導体基板1の第1面S1からの第2部分6の底部までの深さは、例えば、 $200\text{nm} \sim 300\text{nm}$ とされうる。

40

## 【0028】

第1部分7'および第2部分6で構成される溝Tの側面の少なくとも一部には、光電変

50

換部 P E C の電荷蓄積領域 2 5 に蓄積される電荷に対するバリアとなる半導体領域を形成してもよい。

#### 【 0 0 2 9 】

工程 S 1 0 6 では、第 1 部分 7' の下にチャネルストップ 2 1 を形成する。チャネルストップ 2 1 は、例えば、第 1 フォトレジスト PR 1 をマスクとして用いて、第 2 導電型の半導体領域を形成するためのイオンを注入することによって形成されうる。第 2 導電型が p 型である場合は、例えば、ホウ素イオンを加速電圧 2 5 k e V 、ドーズ量  $3.0 \times 10^{12} \text{ ions/cm}^2 \sim 2.5 \times 10^{13} \text{ ions/cm}^2$  で半導体基板 1 に対して斜め方向より注入することによってチャネルストップ 2 1 が形成されうる。チャネルストップ 2 1 は、第 1 部分 7' の下にも形成されうる。

10

#### 【 0 0 3 0 】

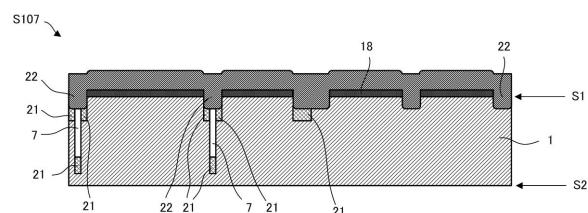

工程 S 1 0 7 では、第 1 部分 7' に空間 7 が残りかつ溝 T が閉塞されるように第 2 部分 6 の中に絶縁体 2 2 を充填する。ここで、第 2 部分 6 の中に絶縁体 2 2 を充填する前に、溝 T 内のエッジを平滑化するために酸化処理を行ってもよい。該酸化処理には、例えば、温度 9 0 0 ~ 1 1 0 0 、圧力 0 . 8 k P a ~ 2 . 0 k P a の水素 / 酸素混合気体中のラジカル酸化、または、常圧の酸素中での熱酸化などを適用することができる。絶縁体 2 2 は、例えばシリコン酸化物であり、絶縁体 2 2 の充填は、例えば高密度プラズマ C V D 技術によって行われうる。より具体的には、絶縁体 2 2 の充填は、 I C P 装置を用いて、温度 5 5 0 ~ 7 0 0 、圧力 0 . 4 P a ~ 1 . 3 P a 、モノシラン / 酸素 / ヘリウム混合気体中でなされうる。この条件では、溝 T の内部には殆どシリコン酸化膜が形成されず、溝 T の内部が減圧状態のままで、溝 T の上に絶縁体 2 2 としてのシリコン酸化物が堆積する。第 1 部分 7' の内部に絶縁体 2 2 を充填せずに空間 7 を残すには、例えば、第 1 部分 7' のアスペクト比（高さ / 幅）が 3 0 ~ 5 0 とし、かつ、第 1 部分 7' の幅をサブミクロンオーダーとすることが好ましい。絶縁体 2 2 の厚さは、例えば、積層膜 1 8 の上において 5 0 0 n m ~ 8 0 0 n m の範囲内にされうる。

20

#### 【 0 0 3 1 】

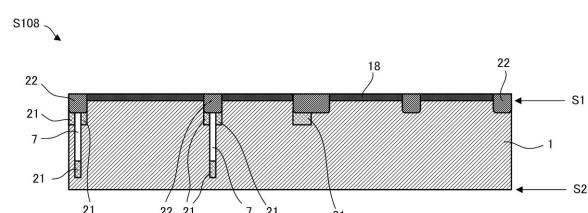

工程 S 1 0 8 では、積層膜 1 8 の上に絶縁体（シリコン酸化物）2 2 を除去しつつ絶縁体 2 2 を平坦化する。この工程において、例えば、絶縁体 2 2 をプラズマエッチングした後に、窒素雰囲気中で温度 9 0 0 、2 0 分 ~ 9 0 分の熱処理を行なうことができる。これにより、絶縁体（シリコン酸化物）2 2 を焼き締めて特性を安定化させるとともに、チャネルストップ 2 1 を活性化させることができる。その後、絶縁体（シリコン酸化物）2 2 をシリカ、セリアをそれぞれ研磨剤とした 2 段階の C M P ( C h e m i c a l M e c h a n i c a l P o l i s h ) によって平坦化しうる。

30

#### 【 0 0 3 2 】

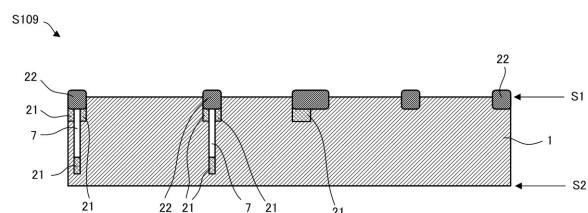

工程 S 1 0 9 では、積層膜 1 8 を除去して、素子形成領域の半導体基板 1 の表面（第 1 面 S 1 ）を露出させる。積層膜 1 8 の除去には、工程 S 1 0 3 と同様の条件を最小することができる。

#### 【 0 0 3 3 】

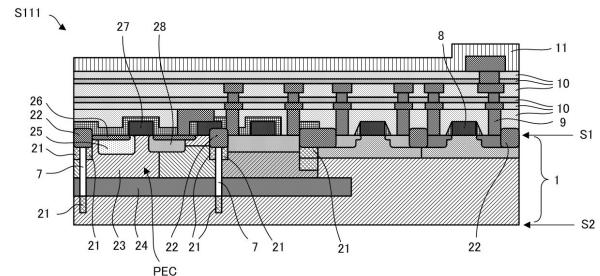

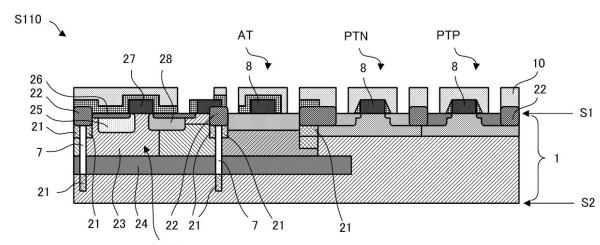

工程 S 1 1 0 では、半導体基板 1 の第 1 面 S 1 と第 2 面 S 2 との間に素子を形成する。素子の一部は、第 1 面 S 1 の上に形成されてもよい。また、他の素子が第 1 面 S 1 の上に形成されてもよい。ここで、図 6 には、画素を構成する素子として、光電変換部 P E C 、転送ゲート 2 7 、フローティングディフュージョン 2 8 、および、トランジスタ A T （例えば、リセットトランジスタ、増幅トランジスタ）が示されている。図 6 にはまた、周辺回路の N M O S トランジスタ P T N および P M O S トランジスタ P T P が示されている。トランジスタ A T 、N M O S トランジスタ P T N および P M O S トランジスタ P T P は、ゲート 8 が示されている。素子は、例えば、F E O L ( F r o n t - E n d O f L i n e ) プロセスによって形成されうる。工程 S 1 1 0 では、更に、第 1 層の層間絶縁膜 1 0 を形成する。

40

#### 【 0 0 3 4 】

工程 S 1 1 1 では、複数の層間絶縁膜 1 0 および複数の配線層 9 で構成される配線構造

50

を完成させ、更に、該配線構造の上にパッシベーション膜11を形成する。配線層9は、例えば、Cuによって形成されうる。層間絶縁膜10は、例えば、シリコン酸化膜の他、Cuの拡散防止膜や、エッチングストップとなるシリコン窒化膜を含みうる。配線層9は、Cu以外の材料、例えばAlで形成されてもよい。

#### 【0035】

工程S112では、空間7が露出するように半導体基板1を第2面S2の側から薄化する。半導体基板1の薄化は、例えば、グラインダなどによる研削、またはCMPなどによって行いうる。その他、この他、3次元実装やTSV(貫通電極)形成プロセスなどで採用されている公知の基板薄膜化技術を適用することが可能である。薄化の後の第2面は、第2面S2'として示されている。

10

#### 【0036】

薄化は、半導体基板1の第1面S1の側に、プラスチックなどの樹脂、ガラスまたはシリコンなどを主材料とした支持基板を結合した状態で行われうる。半導体基板1に対する支持基板の結合は、例えば、エポキシ樹脂などの接着剤が使用されうる。半導体基板1に対する支持基板の結合のために接着剤を使用する場合、配線構造の形成後に半導体基板1の薄化を行うことが好ましい。

#### 【0037】

工程S113では、半導体基板1の第2面S2'の側に光透過性の平坦化膜12、カラーフィルタ層13、キャッピング層14およびマイクロレンズ層15を形成する。

#### 【0038】

以上の製造方法を経て半導体装置の一例としての固体撮像装置100が得られる。この製造方法によれば、空間7および絶縁体22で構成される素子分離のアライメントと、光電変換部PECおよびトランジスタなどの素子のアライメントとを半導体基板1の同一面(第1面S1)に形成されるアライメントマークを使って行うことができる。よって、レイアウトに要求されるマージンを小さくすることができ、高集積化に有利である。

20

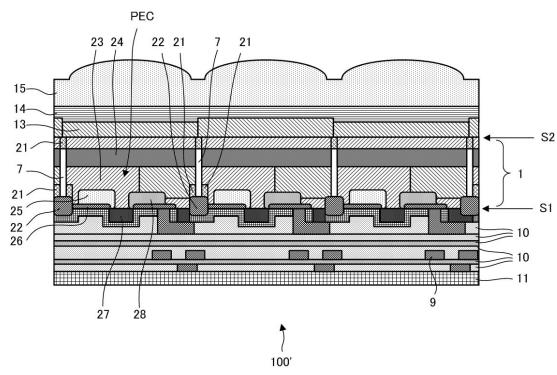

#### 【0039】

以下、本発明の第2実施形態を説明する。なお、第2実施形態として言及しない事項は、第1実施形態に従いうる。図8は、本発明の第2実施形態の固体撮像装置100'の画素アレイの一部分の断面図である。第2実施形態の固体撮像装置100'では、空間7(第1部分)が半導体基板1の第2面S2まで到達しておらず、平坦化膜12が省略されている。第2実施形態では、空間7の第2面S2側の端部と第2面S2との間では、空間7による素子分離はなされていない。しかしながら、画素内の光電変換部PECおよびフローティングディフュージョン28は、他の画素から空間7および絶縁体22によって分離されている。

30

#### 【0040】

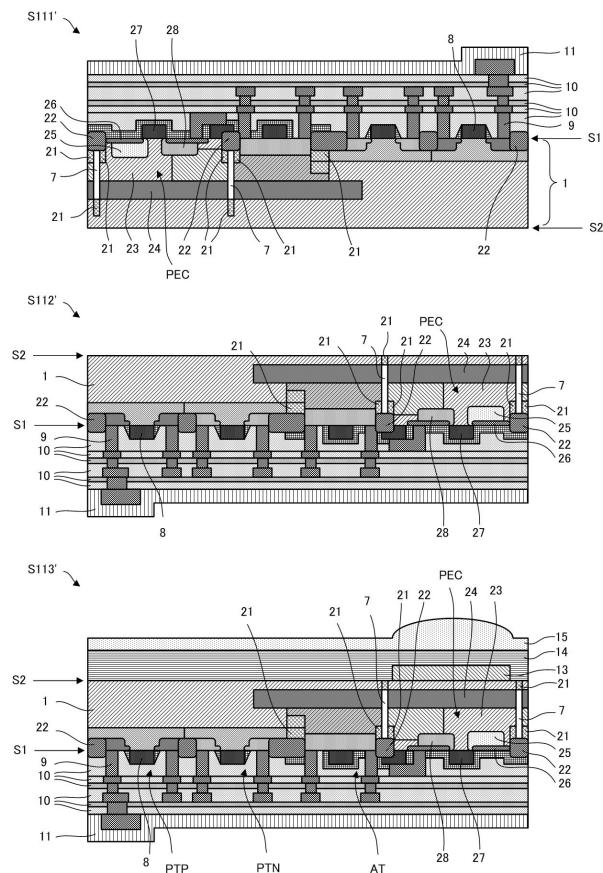

以下、図9を参照しながら固体撮像装置100の製造方法を例示的に説明する。ここで、図9には、1つの画素の光電変換部PECおよびトランジスタAT(例えば、リセットトランジスタ、増幅トランジスタ)、ならびに、周辺回路のNMOSトランジスタPTNおよびPMOSトランジスタPTPに相当する部分が示されている。

#### 【0041】

工程S111'の終了までは、第1実施形態における工程S111の終了までと同様である。工程S112'では、半導体基板1を第2面S2の側から薄化するが、空間7を露出させない。薄化は、例えば、空間7の第2面S2側に存在するチャネルトップ21が露出した時点で終了することができる。半導体基板1の最終的な厚さ(薄化後の厚さ)は、カラーフィルタ層13の形成プロセスを行なう際の平坦性確保など、目的に応じて適宜設定できる。薄化は、半導体基板1に支持基板を結合した状態で行うことができる。

40

#### 【0042】

工程S113では、半導体基板1の第2面S2'の側にカラーフィルタ層13、キャッピング層14、マイクロレンズ層15を形成する。第2実施形態では、薄化工程において空間7を露出させないので、平坦化膜12を形成する必要がない。

50

## 【 0 0 4 3 】

以下、上記の各実施形態に係る固体撮像装置の応用例として、該固体撮像装置が組み込まれたカメラについて例示的に説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、該固体撮像装置から出力される信号を処理する処理部とを含む。該処理部は、例えば、A / D 変換器、および、該 A / D 変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 國米 和夫

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 柴山 将隆

(56)参考文献 特開昭60-021540(JP,A)

特開2006-344644(JP,A)

特開2012-178429(JP,A)

米国特許出願公開第2010/0144114(US,A1)

特開2011-151121(JP,A)

特開2012-028790(JP,A)

特開2012-038981(JP,A)

特開2011-119558(JP,A)

特開平11-017002(JP,A)

特表2009-503814(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 27/146

H04N 5/369