(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6299322号

(P6299322)

(45) 発行日 平成30年3月28日(2018.3.28)

(24) 登録日 平成30年3月9日(2018.3.9)

(51) Int.Cl.

G O 1 D 21/00 (2006.01)

G O 1 P 15/125 (2006.01)

F 1

G O 1 D 21/00

G O 1 P 15/125M

V

請求項の数 24 (全 21 頁)

(21) 出願番号 特願2014-62506 (P2014-62506)

(22) 出願日 平成26年3月25日 (2014.3.25)

(65) 公開番号 特開2015-184208 (P2015-184208A)

(43) 公開日 平成27年10月22日 (2015.10.22)

審査請求日 平成29年3月21日 (2017.3.21)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 村嶋 憲行

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72) 発明者 米澤 岳美

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

最終頁に続く

(54) 【発明の名称】物理量検出センサー、電子機器、移動体および電子回路

## (57) 【特許請求の範囲】

## 【請求項 1】

物理量検出センサー素子と、

前記物理量検出センサー素子に接続された I C と、

を有し、

前記 I C は、

ロジック回路と、

アナログ回路と、

電源電圧に基づいてロジック電源電圧を生成し、前記ロジック回路に前記ロジック電源電圧を供給する第1レギュレータと、

イネーブルに設定されている時に前記電源電圧に基づいて生成されるアナログ電源電圧を、前記アナログ回路に供給する第2レギュレータと、

前記第2レギュレータがディスイネーブルに設定されている時に、前記第1レギュレータを前記アナログ回路に接続するスイッチと、を含むことを特徴とする物理量検出センサー。

## 【請求項 2】

請求項 1において、

前記第2レギュレータを前記ディスイネーブルに設定するディスイネーブル信号により、前記スイッチがオフからオンに切替えられることを特徴とする物理量検出センサー。

## 【請求項 3】

10

20

請求項 1 または 2 において、

前記ロジック電源電圧の電圧レベルと前記アナログ電源電圧の電圧レベルとが実質的に等しいことを特徴とする物理量検出センサー。

**【請求項 4】**

請求項 1 乃至 3 のいずれか一項において、

前記物理量検出センサー素子は静電容量型センサー素子であり、

前記アナログ回路は、前記静電容量型センサー素子からの電荷を電圧に変換する電荷 - 電圧変換回路を含み、

前記第 2 レギュレータがディスイネーブルに設定されている時に、前記電荷 - 電圧変換回路はディスイネーブルに設定されることを特徴とする物理量検出センサー。 10

**【請求項 5】**

請求項 4 において、

前記アナログ回路は、前記電荷 - 電圧変換回路からの出力信号を、設定されたゲインで増幅するプログラマブルゲインアンプをさらに有し、

前記第 2 レギュレータがディスイネーブルに設定されている時に、前記プログラマブルゲインアンプはディスイネーブルに設定されることを特徴とする物理量検出センサー。

**【請求項 6】**

請求項 5 において、

前記アナログ回路は、前記プログラマブルゲインアンプからの出力信号を、アナログ - デジタル変換するアナログ - デジタル変換器をさらに有し、 20

前記第 2 レギュレータがディスイネーブルに設定されている時に、前記アナログ - デジタル変換器はディスイネーブルに設定されることを特徴とする物理量検出センサー。

**【請求項 7】**

請求項 6 において、

外部トリガーに基づいて前記アナログ回路が前記物理量検出センサーからの信号を処理する処理期間が設定され、前記処理期間内に前記第 2 レギュレータはイネーブルに設定され、前記処理期間外では前記アナログ回路はディスイネーブルに設定され、

前記プログラマブルゲインアンプおよび前記アナログ - デジタル変換器の少なくとも一方は、前記処理期間内に設定された休止期間にディスイネーブルに設定されることを特徴とする物理量検出センサー。 30

**【請求項 8】**

請求項 1 乃至 7 のいずれか一項において、

前記第 1 レギュレータは、

非反転入力端子と反転入力端子との間に、仕事関数差電圧によるオフセット電圧を有する差動型の増幅回路と、

前記増幅回路の出力ノードと第 1 の電源ノードとの間に直列に設けられる第 1 の抵抗及び第 2 の抵抗と、

前記第 1 の抵抗と前記第 2 の抵抗の接続ノードに一端が接続される位相補償用キャパシターと、

を含み、 40

前記接続ノードの信号が、前記増幅回路の前記非反転入力端子に帰還され、前記出力ノードの信号が、前記増幅回路の前記反転入力端子に帰還されることを特徴とする物理量検出センサー。

**【請求項 9】**

請求項 8 において、

前記第 1 レギュレータは、

前記第 1 レギュレータの起動時と、前記第 2 レギュレータがイネーブルに設定される過負荷時に電流を生成する電流源と、

前記電流源に流れる電流と等しい電流を前記第 1 レギュレータに増加させるカレントミラー回路と、 50

をさらに有することを特徴とする物理量検出センサー。

**【請求項 10】**

請求項 1 乃至 9 のいずれか一項において、

前記第 2 レギュレータは、

バンドギャップリファレンス回路と、

前記バンドギャップリファレンス回路からのバンドギャップリファレンス電圧を増幅するアンプと、

前記アンプの負帰還経路に設けられた分圧回路と、

を有し、

前記バンドギャップリファレンス電圧を基準電圧として、前記分圧回路の電圧と前記バンドギャップリファレンス電圧との電位が一致するように、前記アンプにより負帰還制御されていることを特徴とする物理量検出センサー。 10

**【請求項 11】**

請求項 1 乃至 10 のいずれか一項において、

前記第 1 レギュレータは、前記ロジック電源電圧よりも大きい検査電圧を生成し、前記スイッチを介して前記検査電圧を前記アナログ回路に供給することを特徴とする物理量検出センサー。 20

**【請求項 12】**

請求項 1 乃至 11 のいずれか一項記載の物理量検出センサーを有することを特徴とする電子機器。 20

**【請求項 13】**

請求項 1 乃至 11 のいずれか一項記載の物理量検出センサーを有することを特徴とする移動体。

**【請求項 14】**

物理量検出センサー素子に接続される電子回路であって、

ロジック回路と、

アナログ回路と、

電源電圧に基づいてロジック電源電圧を生成し、前記ロジック回路に前記ロジック電源電圧を供給する第 1 レギュレータと、

イネーブルに設定されている時に前記電源電圧に基づいて生成されるアナログ電源電圧を、前記アナログ回路に供給する第 2 レギュレータと、 30

前記第 2 レギュレータがディスイネーブルに設定されている時に、前記第 1 レギュレータを前記アナログ回路に接続するスイッチと、 を含むことを特徴とする電子回路。

**【請求項 15】**

請求項 14 において、

前記第 2 レギュレータを前記ディスイネーブルに設定するディスイネーブル信号により、前記スイッチがオフからオンに切替えられることを特徴とする電子回路。 20

**【請求項 16】**

請求項 14 または 15 において、

前記ロジック電源電圧の電圧レベルと前記アナログ電源電圧の電圧レベルとが実質的に等しいことを特徴とする電子回路。 40

**【請求項 17】**

請求項 14 乃至 16 のいずれか一項において、

前記第 1 レギュレータは、前記ロジック電源電圧よりも大きい検査電圧を生成し、前記スイッチを介して前記検査電圧を前記アナログ回路に供給することを特徴とする電子回路。 20

**【請求項 18】**

請求項 14 乃至 17 のいずれか一項において、

前記物理量検出センサー素子は静電容量型センサー素子であり、

前記アナログ回路は、前記静電容量型センサー素子からの電荷を電圧に変換する電荷 - 50

電圧変換回路を含み、

前記第2レギュレータがディスイネーブルに設定されている時に、前記電荷-電圧変換回路はディスイネーブルに設定されることを特徴とする電子回路。

**【請求項19】**

請求項18において、

前記アナログ回路は、前記電荷-電圧変換回路からの出力信号を、設定されたゲインで増幅するプログラマブルゲインアンプをさらに有し、

前記第2レギュレータがディスイネーブルに設定されている時に、前記プログラマブルゲインアンプはディスイネーブルに設定されることを特徴とする電子回路。

**【請求項20】**

10

請求項19において、

前記アナログ回路は、前記プログラマブルゲインアンプからの出力信号を、アナログ-デジタル変換するアナログ-デジタル変換器をさらに有し、

前記第2レギュレータがディスイネーブルに設定されている時に、前記アナログ-デジタル変換器はディスイネーブルに設定されることを特徴とする電子回路。

**【請求項21】**

請求項20において、

外部トリガーに基づいて前記アナログ回路が前記物理量検出センサー<sup>素子</sup>からの信号を処理する処理期間が設定され、前記処理期間内に前記第2レギュレータはイネーブルに設定され、前記処理期間外では前記アナログ回路はディスイネーブルに設定され、

20

前記プログラマブルゲインアンプおよび前記アナログ-デジタル変換器の少なくとも一方は、前記処理期間内に設定された休止期間にディスイネーブルに設定されることを特徴とする電子回路。

**【請求項22】**

請求項14乃至21のいずれか一項において、

前記第1レギュレータは、

非反転入力端子と反転入力端子との間に、仕事関数差電圧によるオフセット電圧を有する差動型の増幅回路と、

前記増幅回路の出力ノードと第1の電源ノードとの間に直列に設けられる第1の抵抗及び第2の抵抗と、

30

前記第1の抵抗と前記第2の抵抗の接続ノードに一端が接続される位相補償用キャパシターと、

を含み、

前記接続ノードの信号が、前記増幅回路の前記非反転入力端子に帰還され、前記出力ノードの信号が、前記増幅回路の前記反転入力端子に帰還されることを特徴とする電子回路。

**【請求項23】**

請求項22において、

前記第1レギュレータは、

前記第1レギュレータの起動時と、前記第2レギュレータがイネーブルに設定される過負荷時とに電流を生成する電流源と、

40

前記電流源に流れる電流と等しい電流を前記第1レギュレータに増加させるカレントミラー回路と、

をさらに有することを特徴とする電子回路。

**【請求項24】**

請求項14乃至23のいずれか一項において、

前記第2レギュレータは、

バンドギャップリファレンス回路と、

前記バンドギャップリファレンス回路からのバンドギャップリファレンス電圧を増幅するアンプと、

50

前記アンプの負帰還経路に設けられた分圧回路と、

を有し、

前記バンドギャップリファレンス電圧を基準電圧として、前記分圧回路の電圧と前記バンドギャップリファレンス電圧との電位が一致するように、前記アンプにより負帰還制御されていることを特徴とする電子回路。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、物理量検出センサー、電子機器、移動体および電子回路等に関する。

**【背景技術】**

**【0002】**

特許文献1では、電源遮断が行われない内部電源Vint0と、電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWを設けている。

**【0003】**

特許文献2では、第1のロジック回路に第1の電源電圧を供給する第1のレギュレータと、第2のロジック回路に第2の電源電圧を供給する第2のレギュレータとを設けている。低消費電力動作モードでは、第2のレギュレータはオフされる。

**【0004】**

特許文献3では、メインレギュレータとスリープ用のサブレギュレータが設けられている。スリープ状態ではメインレギュレータはオフされる。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】**特開2011-151824号公報（要約、0040）

**【特許文献2】**特開2011-120058号公報

**【特許文献3】**特開2012-108585号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

特許文献1のスイッチSWは、内部電源Vint1の電源遮断時にオフされるものである。特許文献1でスイッチSWを設けた理由は、内部電源Vint0, Vint1を精度よく同電位することにある。

**【0007】**

特許文献2では、スタンバイ状態においてもBGRが動作するため消費電力を要する。特許文献3では、ロジック電源のみに限定されている。

**【0008】**

本発明の幾つかの態様は、アナログ回路及アナログ電源回路をディスイネーブルとして消費電力を低減しながら、アナログ回路をイネーブル状態に復帰させる時間を短縮できる物理量検出センサー、電子機器、移動体および電子回路を提供することを目的とする。

**【課題を解決するための手段】**

**【0009】**

(1) 本発明の一態様は、物理量検出センサー素子と、前記物理量検出センサー素子に接続されたICと、を有し、前記ICは、ロジック回路と、アナログ回路と、電源電圧に基づいて生成されるロジック電源電圧を、前記ロジック回路に供給する第1レギュレータと、イネーブルまたはディスイネーブルに切り替えられ、イネーブル時に前記電源電圧に基づいて生成されるアナログ電源電圧を、前記アナログ回路に供給する第2レギュレータと、前記第2レギュレータが前記ディスイネーブルの時に、前記ロジック電源電圧を前記アナログ回路に供給するスイッチと、を含む物理量検出センサーに関する。

**【0010】**

本発明の一態様によれば、物理量を検出している時にアナログ回路を動作させ、アナロ

10

20

30

40

50

グ回路をディスイネーブルにした休止期間では消費電力を低減することができる。ディスイネーブル状態のアナログ回路をイネーブル状態に復帰させるにも電圧が必要である。その際、第2レギュレータをイネーブルとしてアナログ回路にアナログ電源電圧を供給すると、時間をする。本発明の一態様では、アナログ回路の休止期間中には第1レギュレータからのロジック電源電圧を、スイッチを介してアナログ回路に供給することで、イネーブル状態への復帰動作を短縮できる。

#### 【0011】

(2) 本発明の一態様では、前記スイッチのオンまたはオフの切替信号は、前記第2レギュレータを前記ディスイネーブルに設定するディスイネーブル信号に基づいて生成することができる。

10

#### 【0012】

スイッチのオンまたはオフと、アナログ回路のディスイネーブルまたはイネーブルとは相関があるので、スイッチのオンまたはオフ切替信号は、第2レギュレータをディスイネーブルに設定するディスイネーブル信号に基づいて生成することができる。

#### 【0013】

(3) 本発明の一態様では、前記ロジック電源電圧の電圧レベルと前記アナログ電源電圧の電圧レベルとを実質的に等しくすることができる。

#### 【0014】

ロジック電源電圧とアナログ電源電圧との電圧レベルに差があると、復帰動作時に電圧ドロップやリンギングが発生し易いことからである。ただし、アナログ回路が正常に復帰動作する限り、異なる電圧レベルとしても良い。

20

#### 【0015】

(4) 本発明の一態様では、前記第1レギュレータは、前記ICの検査時に、前記ロジック電源電圧よりも大きい検査電圧を生成し、前記スイッチを介して前記検査電圧を前記アナログ回路に供給することができる。

#### 【0016】

第1レギュレータは、レジスタ設定変更等により例えば可変抵抗の抵抗値を可変する等して、第1レギュレータの出力電圧レベルを高電圧レベルに変更し、過負荷を与える検査電圧を生成することができる。

#### 【0017】

(5) 本発明の一態様では、前記物理量検出センサー素子は静電容量型センサー素子であり、前記アナログ回路は、前記静電容量型センサー素子からの電荷を電圧に変換する電荷・電圧変換回路を含み、前記第2レギュレータがディスイネーブルの時に、前記電荷・電圧変換回路はディスイネーブルに設定されることができる。

30

#### 【0018】

第2レギュレータがディスイネーブルの時に電荷・電圧変換回路はディスイネーブルにして消費電力を低減する一方で、アナログ回路である電荷・電圧変換回路には第1レギュレータからのロジック電源電圧が、スイッチを介して供給されるので、イネーブル状態への復帰動作を短縮できる。

#### 【0019】

(6) 本発明の一態様では、前記アナログ回路は、前記電荷・電圧変換回路からの出力信号を、設定されたゲインで増幅するプログラマブルゲインアンプをさらに有し、前記第2レギュレータがディスイネーブルの時に、前記プログラマブルゲインアンプはディスイネーブルに設定されることがある。

40

#### 【0020】

第2レギュレータがディスイネーブルの時にプログラマブルアンプはディスイネーブルにして消費電力を低減する一方で、アナログ回路であるプログラマブルアンプには第1レギュレータからのロジック電源電圧が、スイッチを介して供給されるので、イネーブル状態への復帰動作を短縮できる。

#### 【0021】

50

(7) 本発明の一態様では、前記アナログ回路は、前記プログラマブルゲインアンプからの出力信号を、アナログ - デジタル変換するアナログ - デジタル変換器をさらに有し、前記第2レギュレータがディスイネーブルの時に、前記アナログ - デジタル変換器はディスイネーブルに設定されることができる。

**【0022】**

第2レギュレータがディスイネーブルの時にアナログ - デジタル変換器はディスイネーブルにして消費電力を低減する一方で、アナログ回路であるアナログ - デジタル変換器には第1レギュレータからのロジック電源電圧が、スイッチを介して供給されるので、イネーブル状態への復帰動作を短縮できる。

**【0023】**

(8) 本発明の一態様では、外部トリガーに基づいて前記アナログ回路が前記物理量検出センサー素子からの信号を処理する処理期間が設定され、前記処理期間内に前記第2レギュレータはイネーブルとされ、前記処理期間外では前記アナログ回路はディスイネーブルとされ、前記プログラマブルゲインアンプまたは前記アナログ - デジタル変換器は、前記処理期間内に設定された休止期間にディスイネーブルとされることができる。

**【0024】**

処理期間外ではアナログ回路がディスイネーブルとされ、処理期間内でもプログラマブルゲインアンプまたはアナログ - デジタル変換器は休止期間にディスイネーブルとされるので、消費電力を低減できる一方で、アナログ回路のディスイネーブル中に第2レギュレータがディスイネーブルとなつても、アナログ回路には第1レギュレータからのロジック電源電圧が、スイッチを介して供給されるので、イネーブル状態への復帰動作を短縮できる。

**【0025】**

(9) 本発明の一態様では、前記第1レギュレータは、非反転入力端子と反転入力端子の間に、仕事関数差電圧によるオフセット電圧を有する差動型の増幅回路と、前記増幅回路の出力ノードと第1の電源ノードとの間に直列に設けられる第1の抵抗及び第2の抵抗と、前記第1の抵抗と前記第2の抵抗の接続ノードに一端が接続される位相補償用キャパシターと、含み、前記第1、第2の抵抗の接続ノードの信号が、前記増幅回路の前記非反転入力端子に帰還され、前記増幅回路の出力ノードの信号を、前記増幅回路の前記反転入力端子に帰還することができる。

**【0026】**

この第1レギュレータによれば、増幅回路の非反転入力端子と反転入力端子の間のオフセット電圧と第1、第2の抵抗の抵抗比により決まる定電圧が生成される。第1、第2の抵抗の接続ノードには位相補償用キャパシターが設けられ、この接続ノードの信号が増幅回路の非反転入力端子に帰還されると共に、増幅回路の出力ノードの信号が反転入力端子に帰還される。これにより、安定した回路動作で定電圧を生成できる第1レギュレータを構築できる。

**【0027】**

(10) 本発明の一態様では、前記第1レギュレータは、前記第1レギュレータの起動時と、前記第2レギュレータがイネーブルである過負荷時に電流を生成する電流源と、前記電流源に流れる電流と等しい電流を前記第1レギュレータに増加させるカレントミラーアンプと、をさらに有することができる。

**【0028】**

こうすると、カレントミラーアンプの動作によって、特に負荷の大きい第1レギュレータの起動時及び第2レギュレータがイネーブルである過負荷時の能力を高めることができる。

**【0029】**

(11) 本発明の一態様では、前記第2レギュレータは、バンドギャップリファレンス回路と、前記バンドギャップリファレンス回路からのバンドギャップリファレンス電圧を增幅するアンプと、前記アンプの負帰還経路に設けられた分圧回路と、を有し、前記バン

10

20

30

40

50

ドギャップリファレンス電圧を基準電圧として、前記分圧回路の電圧と前記バンドギャップリファレンス電圧との電位が一致するように、前記アンプにより負帰還制御することができる。

**【0030】**

こうして、バンドギャップリファレンス電圧を増幅して、アナログ電源電圧を生成することができる。

**【0031】**

(12) 本発明の他の態様は、(1)～(11)に記載の物理量検出センサーを有する電子機器に関する。

**【0032】**

(13) 本発明のさらに他の態様は、(1)～(11)に記載の物理量検出センサーを有する移動体に関する。

**【0033】**

(14) 本発明のさらに他の態様は、物理量検出センサー素子に接続される電子回路であって、(1)～(11)に記載のICが備える構成を有する電子回路に関する。

**【図面の簡単な説明】**

**【0034】**

【図1】本発明の一実施形態に係る物理量検出センサーの一例である加速度センサーを示す図である。

【図2】図2(A)(B)は、加速度センサー素子の一例である差動容量型センサー素子を示す図である。

**【図3】加速度センサーのブロック図である。**

**【図4】ICの電源系のブロック図である。**

**【図5】連続計測時のモード遷移を示す図である。**

**【図6】間欠(一回)計測時のモード遷移を示す図である。**

【図7】外部トリガーをハードウェアトリガーとしてICに入力させる例を示すブロック図である。

【図8】外部トリガーをソフトウェアトリガーとしてICに入力させる例を示すブロック図である。

**【図9】加速度センサーの動作タイミングチャートである。**

**【図10】外部トリガーの二重入力の禁止を説明するためのタイミングチャートである。**

**【図11】1回測定モードの計測シーケンスを示す図である。**

**【図12】第1レギュレータの回路図である。**

**【図13】図12の第1レギュレータを改良した回路図である。**

**【図14】第2レギュレータの回路図である。**

【図15】電子機器の一具体例としてのスマートフォンの構成を概略的に示す概念図である。

【図16】電子機器の他の具体例としてのデジタルスチルカメラの構成を概略的に示す概念図である。

**【図17】移動体の一具体例としての自動車の構成を概略的に示す概念図である。**

**【発明を実施するための形態】**

**【0035】**

以下、添付図面を参照しつつ本発明の一実施形態を説明する。なお、以下に説明する本実施形態は、特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

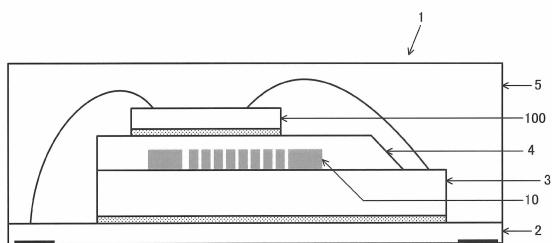

**【0036】**

**(1) 加速度センサー(物理量検出センサー)**

図1は、本発明の一実施形態に係る物理量検出センサーの一例である加速度センサーを示す。加速度センサー1は、例えば、インターポーラ基板2と、インターポーラ基板2上に形成されたガラス基板3と、ガラス基板3上に例えばSi(シリコン)等の半導体

10

20

30

40

50

材料を用いたMEMS (Micro Electro Mechanical Systems) により形成された加速度センサー素子10と、MEMS キャップ4と、MEMS キャップ4上に形成された加速度検出回路(電子回路)である集積回路(ΙC)100とを有する。ΙC100はインターポーラー基板2及びガラス基板3上に形成された電極部に例えばワイヤーボンディング接続されている。インターポーラー基板2上に搭載物3, 10, 4, 100はモールド5により封止されている。

#### 【0037】

##### (2) 加速度センサー素子

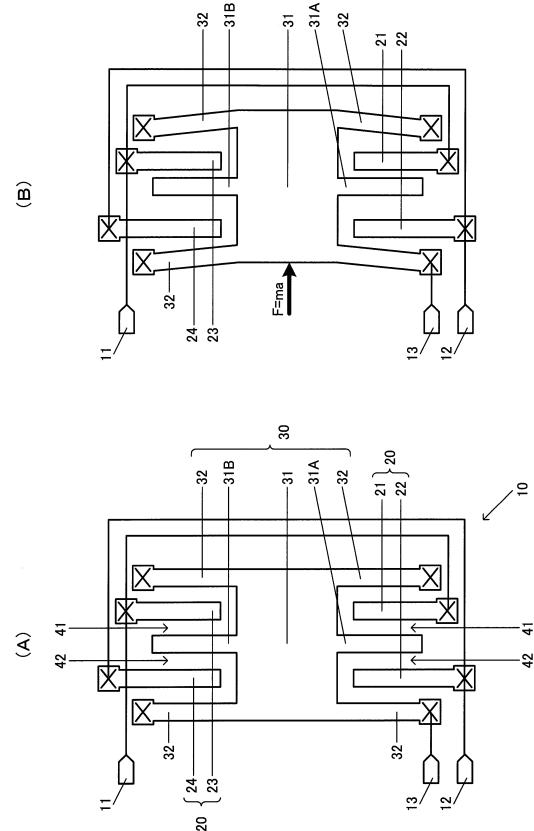

図2(A)は、図1の加速度センサー素子10として用いられる例えば差動容量型センサー素子の構造を例示する図である。差動容量型加速度センサー素子10は、固定部20と可動部30とを有する。固定部20は、基板(図示略)に固定されている部材である。可動部30は、加速度に応じて変位する構造体の一例であり、錐部31とばね部32とを有する。ばね部32の一端は基板に固定されており、他端は錐部31に接続されている。錐部31は、ばね部32により支持されている。図2(B)に示すように差動容量型加速度センサー素子10に加速度aが加えられると、質量mの錐部31には、 $F = m a$ の力が働く。この力により、ばね部32は変形し、錐部31は固定部20に対して相対的に変位する。

#### 【0038】

錐部31は、可動電極31Aおよび可動電極31Bを有する。固定部20は、固定電極21～24を有する。可動電極31Aは固定電極21, 22の間に配置され、可動電極31Bは固定電極23, 24の間に配置される。差動容量型加速度センサー素子10は、例えば、Si(シリコン)等の半導体材料と、半導体加工技術を用いたMEMS(Micro Electro Mechanical Systems)で形成される。

#### 【0039】

ここで、可動電極31Aと固定電極21とのペアと、可動電極31Bと固定電極23とのペアとを、第1容量形成部41と称する。同様に、可動電極31Aと固定電極22とのペアと、可動電極31Bと固定電極24とのペアとを、第2容量形成部42と称する。差動容量型加速度センサー素子10は、第1容量形成部41の一端11と、第2容量形成部42の一端12と、第1, 第2容量形成部41, 42の共通端13とを含む。図2(B)に示す加速度aが作用したとき、第1容量形成部41の容量値は減少する一方で、第2容量形成部42の容量値は増大する。このため、共通端13に電荷を供給した状態で錐部31に加速度aが作用すると、第1, 第2容量形成部41, 42の一端11, 12からそれぞれ出力される電荷(信号)は絶対値が等しく符号が逆の差動信号対となる。

#### 【0040】

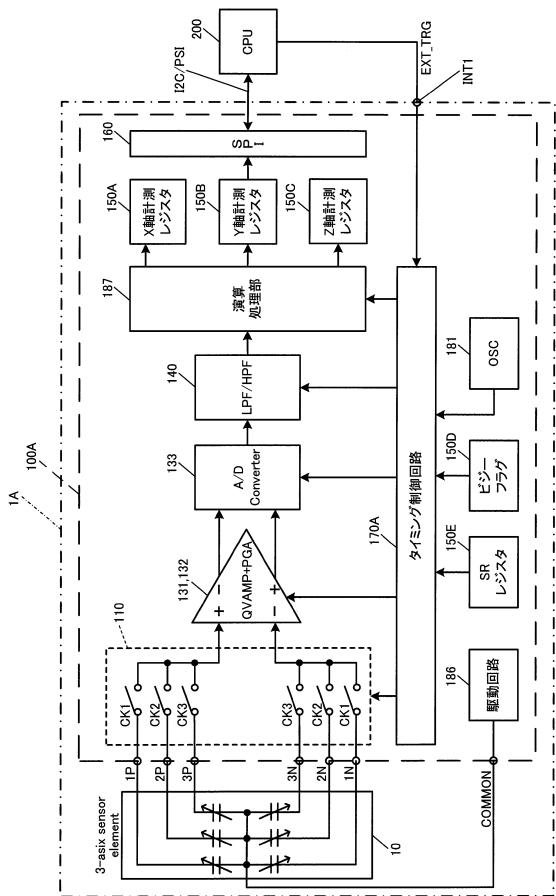

##### (3) 加速度センサーの回路図

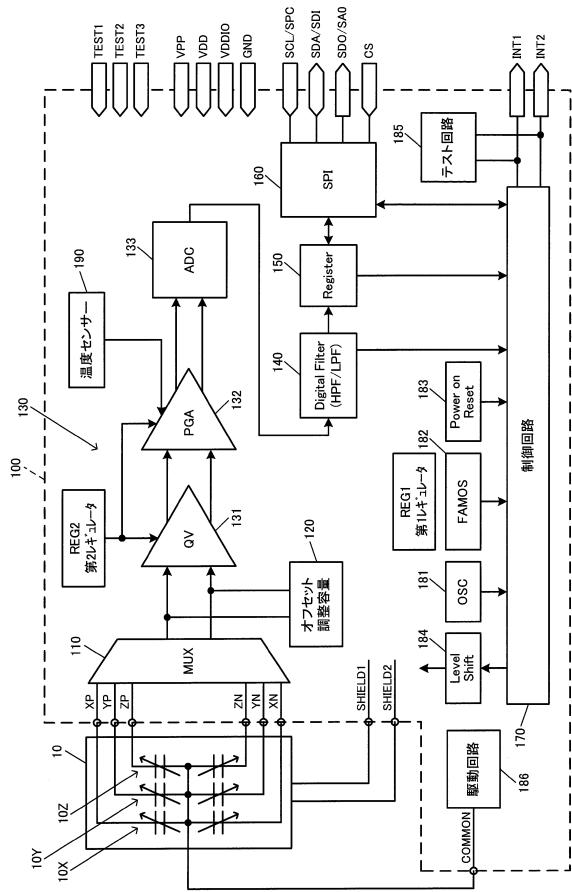

図2(B)は、加速度aが作用する一軸方向の加速度を検出する例について説明した。図3に示すか速度センサー1には、検出軸をN(Nは2以上の整数)軸とし、例えばN=3とする場合の直交三軸(広義には交差N軸)であるX軸、Y軸およびZ軸をそれぞれの検出軸とする第1～第3の差動容量型加速度センサー素子10X, 10Y, 10Zが設けられている。

#### 【0041】

第1～第3の差動容量型加速度センサー素子10X, 10Y, 10Zの各々は、図2(A)に示す第1, 第2容量形成部41, 42を有し、第1, 第2容量形成部41, 42の固定容量間には軸毎に異なるオフセットがある。オフセットがあるまま加速度を検出すると、加速度が作用しない時でも加速度が存在する値が出力されてしまう。そこで、オフセット調整(キャリブレーション)が必要となる。

#### 【0042】

ΙC100は、可変容量であるオフセット調整容量120が設けられている。オフセット調整容量120は、第1容量形成部41および第2容量形成部42の各々の固定容量間でのオフセット量に基づく容量値に軸毎にリセットされる

10

20

30

40

50

**【 0 0 4 3 】**

I C 1 0 0 には、第 1 ~ 第 3 の差動容量型加速度センサー素子 1 0 X , 1 0 Y , 1 0 Z から時分割で電荷が入力される。この時分割駆動のために、スイッチング駆動されるマルチプレクサー ( M U X ) 1 1 0 が設けられている。

**【 0 0 4 4 】**

マルチプレクサー 1 1 0 の後段には、アナログ回路である容量検出回路（広義には信号処理部）1 3 0 として、例えば電荷 - 電圧変換 ( Q V ) アンプ 1 3 1 、プログラマブルゲインアンプ ( P G A ) 1 3 2 及びアナログ - デジタル変換器 ( A D C ) 1 3 3 等を有する。Q V アンプ 1 3 1 は、時分割入力される差動容量型加速度センサー素子 1 0 X , 1 0 Y , 1 0 Zからの電荷を電圧に変換する。差動容量型加速度センサー素子 1 0 X , 1 0 Y , 1 0 Zからの出力は差動信号であるから、Q V アンプ 1 3 1 は差動増幅回路として機能する。P G A 1 3 2 は、Q V アンプ 1 3 1 の出力を、各軸毎に設定されたゲインで増幅する。A D C 1 3 3 は、P G A 1 3 2 の出力をアナログ - デジタル変換する。10

**【 0 0 4 5 】**

A D C 1 3 3の後段には、デジタルフィルター 1 4 0 、レジスタ 1 5 0 、シリアル - パラレルインターフェイス回路 ( S P I ) 1 6 0 が設けられている。容量検出回路 1 3 0 により検出された容量に基づく加速度信号は、S P I 1 6 0 を介して出力される。

**【 0 0 4 6 】**

なお、I C 1 0 0 には温度センサー 1 9 0 を設けることができる。温度センサー 1 9 0 からの温度信号は、P G A 1 3 2 で増幅された後に、A D C 1 3 3 でデジタル信号に変換される。20

**【 0 0 4 7 】**

I C 1 0 0 は、制御回路 1 7 0 を有する。制御回路 1 7 0 には、発振回路 ( O S C ) 1 8 1 、F A M O S ( フローティングゲート型アバランシェ・インジェクションM O S ) 等の不揮発性メモリ 1 8 2 、パワーオンリセット回路 1 8 3 、レベルシフター 1 8 4 、テスト回路 1 8 5 、駆動回路 1 8 6 や、上述したデジタルフィルター 1 4 0 及びレジスタ 1 5 0 等が接続される。予め測定されたオフセット容量値を設定するデータは、S P I 1 6 0 を介して外部から入力され、制御回路 1 7 0 により不揮発性メモリ 1 8 2 に格納される。加速度センサー 1 の起動時に、制御回路 1 7 0 により不揮発性メモリ 1 8 2 から読み出されたオフセット容量値設定用のデータは、レジスタ 1 5 0 に格納される。レジスタ 1 5 0 は、設定されたデータに基づいて、例えば電圧制御型のオフセット調整容量 1 2 0 に電圧を設定して、オフセット調整容量 1 2 0 を各軸のオフセット容量値に設定することができる。30

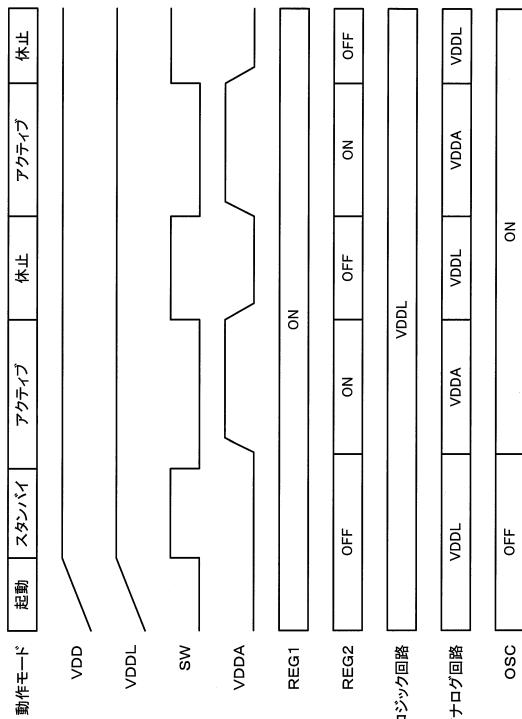

**【 0 0 4 8 】**

I C 1 0 0 には、外部から電源電圧 V D D , G N D が入力される。I C 1 0 0 には、電源電圧 V D D ( 例えは 3 V ) を降圧してロジック電源電圧 V D D L ( 例えは 1 . 8 V ) を生成する第 1 レギュレータ R E G 1 と、電源電圧 V D D を降圧してアナログ電源電圧 V D D A ( 例えは 1 . 8 V ) を生成する第 2 レギュレータ R E G 2 とが設けられている。なお、第 1 レギュレータ R E G 1 は、加速度センサー 1 の起動によりイネーブルとなり、加速度センサー 1 が稼働している間 ( スタンバイ、休止期間等を含む ) に亘ってロジック電源電圧 V D D L を生成するロジック電源回路である。一方、第 2 レギュレータ R E G 2 は、イネーブルまたはディスイネーブルに切り替えられるアナログ電源回路であり、イネーブル期間のみアナログ電源電圧 V D D A を生成する。40

**【 0 0 4 9 】**

I C 1 0 0 は、電源端子 ( V D D , V P P , V D D I O , G N D ) 、入出力端子 ( S C L / S P C , S D A / S D I , S D O / S A O , C S ) 、テスト端子 ( T E S 1 - 3 ) の他に、割り込み端子 ( I N T 1 , I N T 2 ) を有することができる。

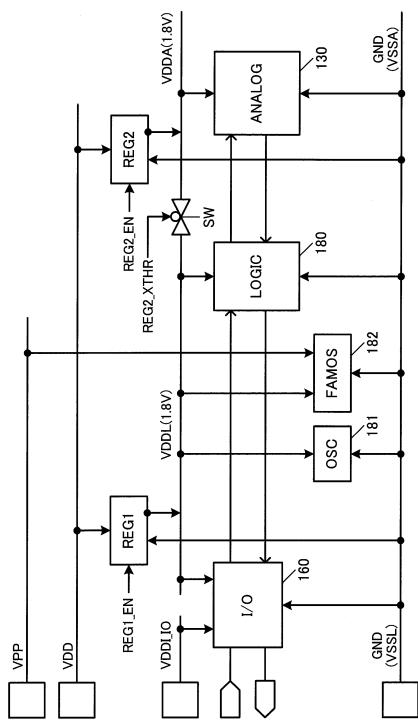

**【 0 0 5 0 】****( 4 ) I C の電源回路系**

図 4 は、図 3 に示す I C 1 0 0 の電源回路系を示すブロック図である。なお、図 4 では50

電圧供給対象として、デジタル電源電圧で駆動される回路をロジック回路180と総称している。また、他の回路として、OSC181と不揮発性メモリ(FAMOS)182を図示している。

#### 【0051】

図4において、イネーブル信号REG1\_ENでイネーブルとなる第1レギュレータREG1は、電源電圧VDDを降圧したロジック電源電圧VDDLをI/O160、ロジック回路180、OSC181及び不揮発性メモリ(FAMOS)182等に供給する。イネーブル信号REG2\_ENでイネーブルとなる第2レギュレータREG2は、電源電圧VDDを降圧したアナログ電源電圧VDDAをアナログ回路130に供給する。

#### 【0052】

ここで、ロジック電源電圧VDDLの電源線とアナログ電源電圧VDDAの電源線との間には、スイッチSWが設けられている。後述する図6に示す通り、休止期間(休止モード)が設定される。スタンバイモードや休止モードでは、イネーブル信号REG2\_ENにより第2レギュレータREG2はディスイネーブルとなり、アナログ電源電圧VDDAの供給が遮断される。加速度を検出している時にアナログ回路130を動作させ、休止期間ではアナログ回路130をディスイネーブルにして消費電力を低減することができる。

#### 【0053】

休止期間では、REG2\_ENがディスイネーブルの時にイネーブルとなるREG2\_XTHRにより、スイッチSWがオンされて、ロジック電源電圧VDDLの電源線とアナログ電源電圧VDDAの電源線とが接続される。それにより、アナログ電源電圧が生成されないスタンバイ期間や休止期間では、第1レギュレータREG1よりスイッチSWを介してアナログ回路130にロジック電源電圧VDDLが供給される。

#### 【0054】

ここで、ディスイネーブル状態のアナログ回路130をイネーブル状態に復帰させるにも電圧が必要である。その際、第2レギュレータREG2をイネーブルとしてアナログ回路130にアナログ電源電圧VDDAを供給すると、時間を要する。本実施形態では、スタンバイモードや休止モードでは、第1レギュレータREG1からのロジック電源電圧VDDLをスイッチSWを介してアナログ回路130に供給することで、イネーブル信号に基づきアナログ回路130をイネーブル状態へと短期間で復帰させる動作を短縮できる。

#### 【0055】

なお、本実施形態ではロジック電源電圧VDDLとアナログ電源電圧VDDAとの電圧レベルを共に等しく(例えば1.8V)としているが、アナログ回路130が正常に復帰動作する限り、異なる電圧レベルとしても良い。ただし、ロジック電源電圧VDDLとアナログ電源電圧VDDAとの電圧レベルに差があると、復帰動作時に電圧ドロップやリングングが発生し易いことから、ロジック電源電圧VDDLとアナログ電源電圧VDDAとの電圧レベルは実質的に等しいことが好ましい。

#### 【0056】

##### (5) 外部トリガーによる間欠(1回)計測モード

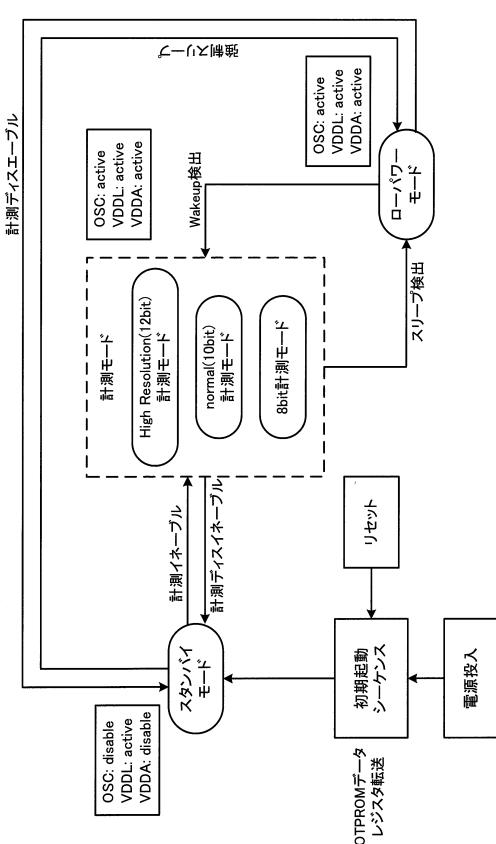

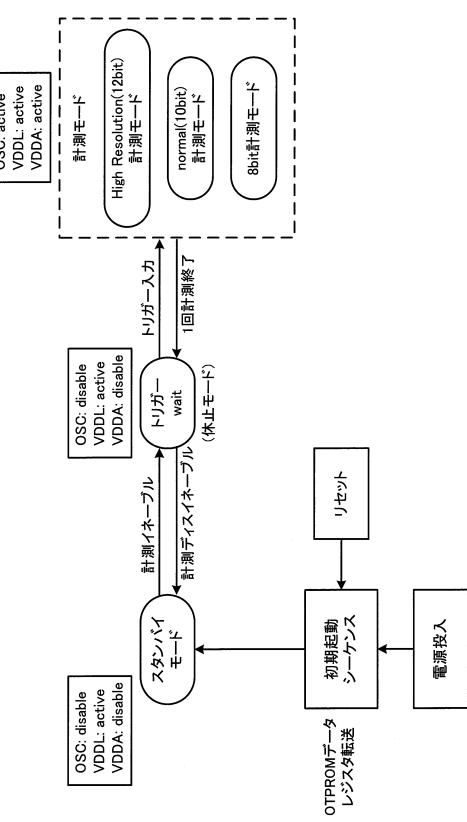

本実施形態では、内部トリガーによる連続計測モードと、外部トリガーによる間欠(1回)計測モードのいずれかに設定することができる。図5は連続計測時のモード遷移を示す図であり、図6は間欠(一回)計測時のモード遷移を示す図である。図5にはスタンバイモードと計測モードが示されている。図5ではさらにローパワーモードが追加され、図6ではスタンバイモードと計測モードとの間に、休止モードとしてトリガー待ちの状態が設定される。

#### 【0057】

スタンバイモードとは、電源投入により初期起動シーケンスが実施された後に設定される待機モードである。初期起動シーケンスが実施されるとレジスタ150がリセットされ、ワンタイムプログラマブルROMに記憶された制御データ等がレジスタ150に転送される。スタンバイモードでは、第1レギュレータREG1がイネーブルで第2レギュレータREG2はディスイネーブルとなり、上述した通り図4のスイッチSWがオンとなって

10

20

30

40

50

アナログ回路 130 にはロジック電源電圧 VDDL が供給される。

#### 【0058】

計測モードとして、加速度信号のデジタル変換分解能が異なる 3 つのモード（例えば 12 ビット、10 ビット及び 8 ビット）を信号により選択できるようになっている。計測モードでは、第 1 レギュレータ REG1 及び第 2 レギュレータ REG2 が共にイネーブルとなり、上述した通り図 4 のスイッチ SW がオフとなってアナログ回路 130 にはアナログ電源電圧 VDDA が供給される。

#### 【0059】

図 5 のローパワーモードとは、加速度が検出されない時に設定されるスリープ状態を検出ことで設定され、スリープが解除された状態が検出されるウェイクアップ検出時まで継続される。ローパワーモードは、デジタル変換分解能は 8 ビット固定となり、10 ビットまたは 12 ビットを選択した場合よりも低消費電力となる。計測モードに対して出力データ周波数（例えば図 7 及び図 8 の SR レジスタで設定されるサンプリングレート）を低くすることで、より低消費電力とすることができます。

10

#### 【0060】

図 6 の間欠（1 回）計測時では、測定モードにて X 軸、Y 軸及び Z 軸の加速度計測が所定回数例えば 1 回だけ行われる。間欠（1 回）計測モードが終了すると休止モードとなり、次の外部トリガーを待機することになる。それにより、測定モードは間欠的に実施される。休止モード（休止期間）では、スタンバイモードと同じく、第 1 レギュレータ REG1 がイネーブルで第 2 レギュレータ REG2 はディスイネーブルとなり、上述した通り図 4 のスイッチ SW がオンとなってアナログ回路 130 にはロジック電源電圧 VDDL が供給される。

20

#### 【0061】

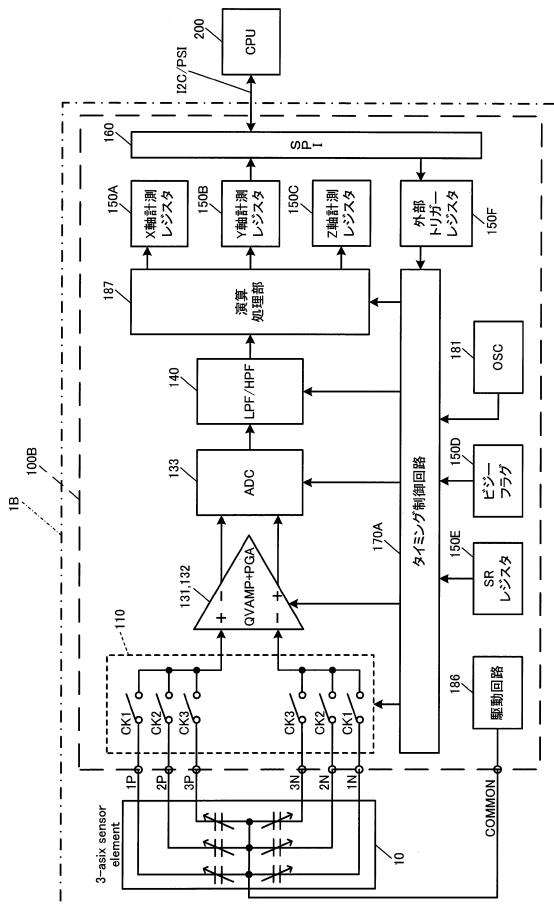

図 7 及び図 8 は、間欠（1 回）計測モードを設定する 2 つの方式を示している。なお、図 7 及び図 8 では、図 3 に示す制御回路 170 に設けられるタイミング制御回路 170A が示されている。また、図 7 及び図 8 では、図 3 に示すレジスタ 150 を機能別レジスタ 150A ~ 150F として示している。つまり、図 3 に示すレジスタ 150 は、図 7 または図 8 に示す X 軸計測レジスタ 150A、Y 軸計測レジスタ 150B、Z 軸計測レジスタ 150C、ビジーフラグ用レジスタ 150D、SR（サンプリングレート）設定レジスタ 150E、外部トリガーレジスタ 150F を含んでいる。さらに、図 7 及び図 8 では、図 4 に示すデジタルフィルター 140 とレジスタ 150 との間に、演算処理部 187 が追加されている。

30

#### 【0062】

図 7 はハードウェアトリガーの方式を示し、図 8 はソフトウェアトリガーの方式を示している。ハードウェアトリガーを設定する端として、I C 100A の例えば割り込み端子 INT1 等の外部端子が用いられる。図 7 の加速度センサー 1A が接続される CPU200 は、例えばタイマー等から外部トリガーを割り込み端子 INT1 に出力する。図 8 は、CPU200 から所定の通信プロトコルに従って送信される外部トリガーが、I C 100B のシリアル - パラレルインターフェイス 160 に入力され、外部トリガーレジスタ 150F に格納される。

40

#### 【0063】

制御回路 170 は、図 7 のハードウェアトリガー方式と、図 8 のソフトウェアトリガー方式とを、信号設定により選択させても良い。図 7 のハードウェアトリガー方式は、CPU200 の負担が少ない点で優れている。図 8 のソフトウェアトリガー方式は、兼用される割り込み端子 INT1 を他の用途に使用する機会を減少させない点で優れている。

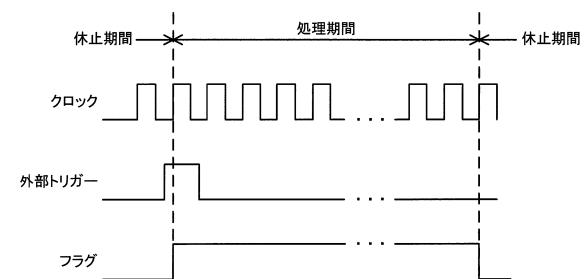

#### 【0064】

制御回路 170 は、図 5 に示す連続計測モードか、図 6 に示す間欠（1 回）計測モードであるかは、フラグなどにより認識している。図 9 は、間欠（1 回）計測モードでの制御回路 170 の制御により設定される各部のタイミングチャートである。起動と同時に第 1 レギュレータ REG1 がイネーブルとなってロジック電源電圧 VDDL は生成されるが、

50

第2レギュレータREG2は動作モード(計測モード)がアクティブの時のみアナログ電源電圧VDDAを生成する。動作モード(計測モード)がアクティブでないスタンバイモード及び休止モードでは、スイッチSWがオンして、アナログ回路130にはロジック電源電圧VDDLが供給される。

#### 【0065】

図7及び図8に示すSRレジスタは、デジタル分解能を設定するサンプリングレートを設定するものである。図7及び図8に示すビジーフラグ用レジスタ150Dは、例えば休止期間中にアクティブとなるフラグがタイミング制御回路170Aにより設定される。図10に示すように、外部トリガーがアクティブである時にクロックの立ち上がりで休止期間がスタートする。休止期間は所定クロック数(例えば156クロック)をカウントアップして終了する。ビジーフラグは、休止期間中に亘ってアクティブとなる。ビジーフラグがアクティブである期間に入力された外部トリガーは、タイミング制御回路170Aにより無視される。それにより、間欠(1回)計測モードの途中で同一モードが再スタートされることを防止できる。

10

#### 【0066】

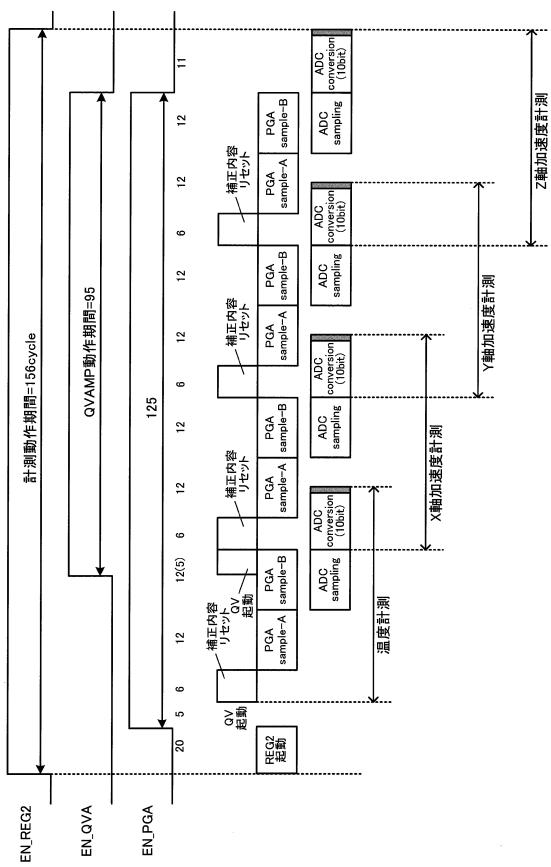

##### (6) アナログ回路のイネーブル/ディスイネーブル

図11は、間欠(1回)測定モードでのタイミングチャートである。上述した外部トリガーにより、間欠(1回)測定モードが開始される。1回測定モードの場合、計測動作期間はクロックの例えば156サイクルである。1回測定モードに設定されると、第2レギュレータREG2が起動される。その後、必要によりQV回路131をイネーブルとしてもよい。オフセット調整容量120がリセットされる。

20

#### 【0067】

1回計測モードは、図11に示すように、温度計測、X軸加速度計測、Y軸加速度計測及びZ軸加速度計測が、シーケンシャルに実施される。4回の計測期間の各々にて、PGA132及びADC133が計測に必要な期間だけイネーブルとされる。なお、図11に示す例では、ADC133は分解能が10ビットのデジタル信号に変換している。分解能が低ければ計測期間は短縮され、分解能が高ければ計測期間は増大する。PGA132及びADC133は、温度、X軸加速度、Y軸加速度及びZ軸加速度のように異なる物理量を検出した後に、一旦ディスイネーブルとされている。それにより、消費電力を低減している。

30

#### 【0068】

また、PGA132のイネーブル期間は、サンプルA期間とサンプルB期間とに二分される。同様に、ADC133の動作期間は、サンプリング期間と比較期間とに二分される。PGA132のサンプルB期間は、ADC133のサンプリング期間と時間軸上で重複して設定できる。また、ADC133の比較期間は、PGA132のサンプルA期間と時間軸上で重複して設定できる。それにより、温度計測、X軸加速度計測、Y軸加速度計測及びZ軸加速度計測の各期間を短縮でき、トータルの1回計測期間も短縮される。

#### 【0069】

X軸加速度計測の前に、QVアンプ131がイネーブルとなって起動される。QVアンプ131は、図11に示すようにクロックの例えば95サイクルの期間に亘ってイネーブル状態が維持される。また、QVアンプ131の起動後であって、X軸加速度計測、Y軸加速度計測及びZ軸加速度計測が開始される前に、オフセット調整容量120が各軸のオフセット調整容量値にリセットされる。オフセット調整容量120のリセット期間は、PGA132のディスイネーブル期間を利用して設定される。

40

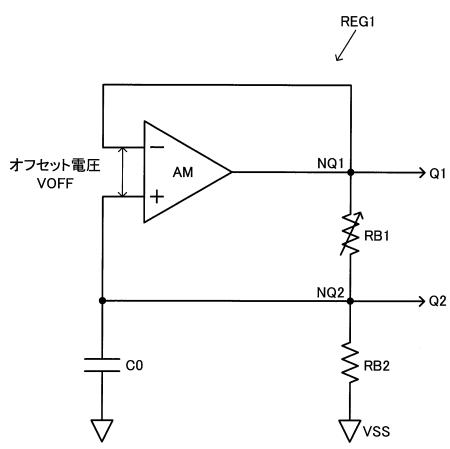

#### 【0070】

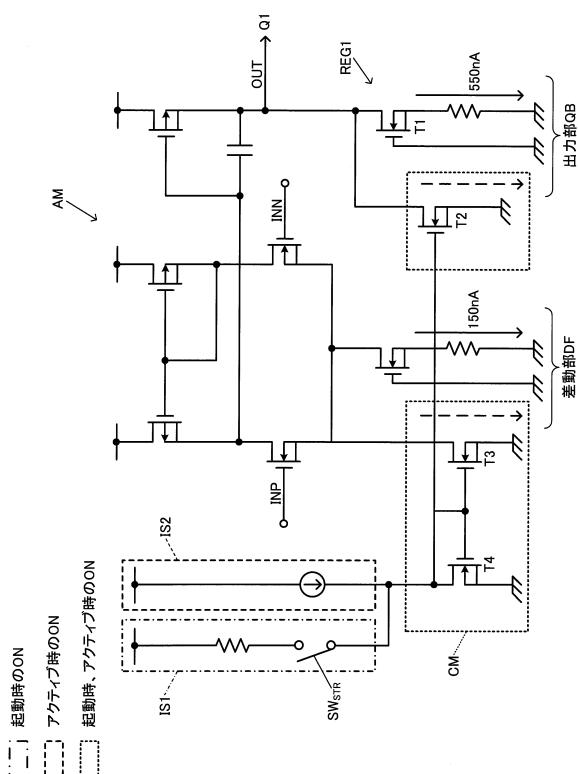

##### (7) 第1レギュレータREG1

図12に、第1レギュレータREG1の一例を示す。第1レギュレータREG1は、非反転入力端子と反転入力端子の間に、仕事関数差電圧によるオフセット電圧VOFFを有する差動型の增幅回路AMと、増幅回路AMの出力ノードNQ1と第1の電源ノードVS Sとの間に直列に設けられる第1の抵抗RB1及び第2の抵抗RB2と、第1の抵抗RB

50

1と第2の抵抗R B 2の接続ノードN Q 2に一端が接続される位相補償用キャパシターC 0を含む。第1、第2の抵抗R B 1、R B 2の接続ノードN Q 2の信号が、增幅回路A Mの非反転入力端子に帰還され、增幅回路A Mの出力ノードN Q 1の信号が、增幅回路A Mの反転入力端子に帰還される。

#### 【0071】

この第1レギュレータREG 1によれば、増幅回路A Mの非反転入力端子と反転入力端子の間のオフセット電圧と第1、第2の抵抗R B 1、R B 2の抵抗比により決まる定電圧が生成される。第1、第2の抵抗R B 1、R B 2の接続ノードには位相補償用キャパシターコが設けられ、この接続ノードの信号が増幅回路A Mの非反転入力端子に帰還されると共に、増幅回路A Mの出力ノードの信号が反転入力端子に帰還される。これにより、安定した回路動作で定電圧を生成できる第1レギュレータREG 1を構築できる。10

#### 【0072】

また、図12に示す第1の抵抗R B 1は可変抵抗とすることができます。加速度センサーゾンセイソクス10及びIC100の検査工程などでは、1.8V系に対して例えば3V程度の高電圧(検査電圧)が印加される。レジスタ設定変更により第1の抵抗R B 1の抵抗値を可変して、第1レギュレータREG 1の出力電圧レベルを高電圧レベルに変更することができる。

#### 【0073】

図13に示す第1レギュレータREG 1では、図12の増幅回路A Mの破線で囲まれた個所に素子または回路を増設し、起動時とアクティブ時に増幅回路A Mに流れる動作電流IOPを増大させ、能力を増大させている。図13に示すように、増幅回路A Mの出力部QBの接地端側に設けられた出力トランジスタT1と並列にトランジスタT2を追加した。増幅回路A Mの差動部DFに増設したトランジスタT3と、トランジスタT3と同一ゲート電圧が印加されるトランジスタT4とで、カレントミラー回路CMを構成している。カレントミラー回路CMの電流源として、起動時に動作する第1電流源IS1と、アクティブ時に動作する第2電流源IS2とが追加されている。起動時に動作する第1電流源IS1では、起動によりスタートスイッチST<sub>STR</sub>がオンされて、カレントミラー回路CMに電流を流す。20

#### 【0074】

スタンバイ時ではカレントミラーCMに電流が流れず、増幅回路A Mは弱反転領域で動作して、差動部DFに例えば150nAが流れ、出力部QBに例えば550nAが流れ、動作電流IOPとして700nAが流れる。起動時にスタートスイッチST<sub>STR</sub>がオンすると、カレントミラー回路CMの動作によって、増設されたトランジスタT2及びT3に破線の矢印で示すように20μAが流れ、動作電流IOPを50μAまで増大させることができる。なお、スタートスイッチST<sub>STR</sub>はパワーオンリセット信号を用いて、起動後の所定時間経過後にオフされる。第2レギュレータREG 2がイネーブルとなったアクティブ時には、第1電流源IS1に代わって第2電流源IS2がオンされ、動作電流IOPを例えば30μAまで増大させることができる。こうして、第1レギュレータREG 1の起動時及びアクティブ時(過負荷時)の能力を高めることができる。30

#### 【0075】

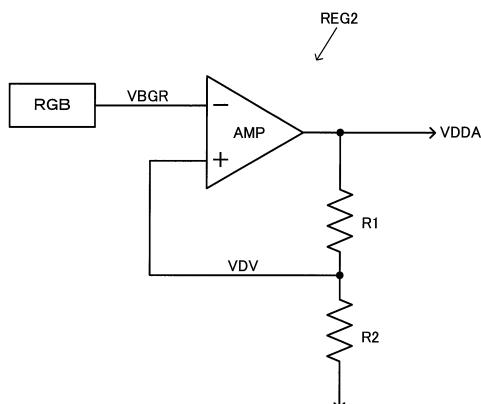

##### (8) 第2レギュレータREG 2

図14に、バンドギャップリファレンス回路を利用した第2レギュレータREG 2を示す。図14において、第2レギュレータREG 2のアンプAMPの負端子に、バンドギャップリファレンス回路BGRが発生するバンドギャップリファレンス電圧VBGR(例えば1.21V)が入力される。アンプAMPの正端子には、アンプAMPの出力電圧VD<sub>DA</sub>が分圧抵抗R1、R2により構成される分圧回路で分圧された電圧VDVが入力される。アンプAMPは、バンドギャップリファレンス電圧VBGRを基準電圧として、分圧回路R1、R2の電圧VDVとバンドギャップリファレンス電圧VBGRとの電位が一致するように、負帰還制御している。こうして、バンドギャップリファレンス電圧VBGRを増幅して、例えば1.8Vのアナログ電源電圧VDDAを生成することができる。4050

## 【0076】

## (9) 電子機器および移動体

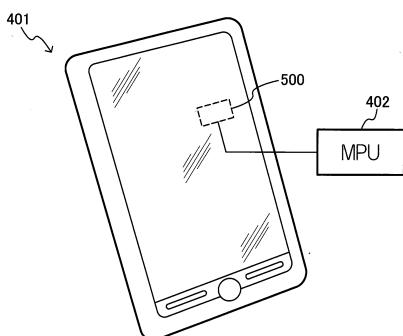

図15は電子機器の一具体例としてのスマートフォン401を概略的に示す。スマートフォン401には図3に示す三軸加速度センサー1に加え、三軸ジャイロセンサーおよびそれに接続される検出回路を備えた物理量検出装置500が組み込まれる。物理量検出装置500はスマートフォン401の姿勢を検出することができる。いわゆるモーションセンシングが実施される。物理量検出装置500の検出信号は例えばマイクロコンピューターチップ(MPU)402に供給されることができる。MPU402はモーションセンシングに応じて様々な処理を実行することができる。その他、こういったモーションセンシングは、携帯電話機、携帯型ゲーム機、ゲームコントローラー、カーナビゲーションシステム、ポインティングデバイス、ヘッドマウンティングディスプレイ、タブレットパソコン等の電子機器で利用されることができる。モーションセンシングの実現にあたって物理量検出装置500は組み込まれることができる。

## 【0077】

図16は電子機器の他の具体例としてのデジタルスチルカメラ(以下「カメラ」という)403を概略的に示す。カメラ403には物理量検出装置500が組み込まれる。物理量検出装置500はカメラ403の姿勢を検出することができる。物理量検出装置500の検出信号は手ぶれ補正装置404に供給されることがある。手ぶれ補正装置404は物理量検出装置500の検出信号に応じて例えばレンズセット405内の特定のレンズを移動させることができる。こうして手ぶれは補正されることがある。その他、手ぶれ補正是デジタルビデオカメラで利用されることがある。手ぶれ補正の実現にあたって物理量検出装置500は組み込まれることができる。

## 【0078】

図17は移動体の一具体例としての自動車406を概略的に示す。自動車406には物理量検出装置500が組み込まれる。物理量検出装置500は車体407の姿勢を検出することができる。物理量検出装置500の検出信号は車体姿勢制御装置408に供給されることがある。車体姿勢制御装置408は例えば車体407の姿勢に応じてサスペンションの硬軟を制御したり個々の車輪409のブレーキを制御したりすることができる。その他、こういった姿勢制御は二足歩行ロボットや航空機、ヘリコプター等の各種移動体で利用されることがある。姿勢制御の実現にあたって物理量検出装置500は組み込まれることができる。

## 【0079】

本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。したがって、このような変形例はすべて本発明の範囲に含まれる。例えば、明細書または図面において、少なくとも一度、より広義または同義な異なる用語とともに記載された用語は、明細書または図面のいかなる箇所においても、その異なる用語に置き換えられることができる。また、アナログ回路130、ロジック回路180、第1レギュレータREG1、第2レギュレータREG2等の構成および動作も本実施形態で説明したものに限定されず、種々の変形が可能である。また、本発明が適用される電子回路またはIC(物理量検出回路)は、デジタル出力するものに限らず、ADC133を有しないアナログ出力にも適用することができる。物理量検出センサーとしては、加速度センサーに限らず、例えば、角速度センサー、圧力センサーなど、物理量を検出する各種センサーに適用できる。

## 【符号の説明】

## 【0080】

1 物理量検出センサー(加速度センサー)、10 物理量検出センサー素子(加速度センサー素子)、100 IC(電子回路)、130 アナログ回路、131 QVアンプ(電荷-電圧変換回路)、132 プログラマブルアンプ(PGM)、133 アナログ-デジタル変換器(ADC)、180 ロジック回路、AM 増幅回路、AMP アンプ、BGR バンドギャップリファレンス回路、C0 位相補償用キャパシター、CM

10

20

30

40

50

カレントミラー回路、I S 1 , I S 2 電流源、R 1 , R 2 分圧回路、R B 1 , R B 2

第1, 第2抵抗、R E G 1 ロジック電源回路(第1レギュレータ)、R E G 2 アナログ電源回路(第2レギュレータ)、S W スイッチ、V D D A アナログ電源電圧、V D D L ロジック電源電圧

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

---

フロントページの続き

審査官 岡田 卓弥

(56)参考文献 特開2011-120058(JP,A)

特開2007-36216(JP,A)

特開2002-310735(JP,A)

(58)調査した分野(Int.Cl., DB名)

G01D21/00 - 21/02

G08C13/00 - 25/04

G01P15/00 - 15/18