(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6021504号

(P6021504)

(45) 発行日 平成28年11月9日(2016.11.9)

(24) 登録日 平成28年10月14日(2016.10.14)

|                     |                |

|---------------------|----------------|

| (51) Int.Cl.        | F 1            |

| H05K 1/02 (2006.01) | H05K 1/02 Q    |

| H05K 3/34 (2006.01) | H05K 3/34 501Z |

| H05K 3/46 (2006.01) | H05K 3/46 U    |

請求項の数 10 (全 17 頁)

(21) 出願番号 特願2012-175887 (P2012-175887)

(22) 出願日 平成24年8月8日 (2012.8.8)

(65) 公開番号 特開2014-36085 (P2014-36085A)

(43) 公開日 平成26年2月24日 (2014.2.24)

審査請求日 平成27年8月7日 (2015.8.7)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100082337

弁理士 近島 一夫

(74) 代理人 100141508

弁理士 大田 隆史

(72) 発明者 大平 正治

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 内田 勝久

最終頁に続く

(54) 【発明の名称】プリント配線板、プリント回路板及びプリント回路板の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体パッケージが実装される第1表層に配置された第1導体パターンと、前記第1表層とは反対側の第2表層に配置された第2導体パターンと、前記第1表層と前記第2表層との間の内層に配置された内層導体パターンと、を備え、前記第1表層、前記内層及び前記第2表層を貫通する第1スルーホール及び第2スルーホールが形成され、

前記第1導体パターンは、第1のプレーン状の導電パターンと、前記第1のプレーン状の導電パターンに周りを囲まれ、前記第1のプレーン状の導電パターンと隙間を介して配置された第1のランド状の導電パターンと、を有し、

前記第2導体パターンは、第2のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンに周りを囲まれ、前記第2のプレーン状の導電パターンと隙間を介して配置された第2のランド状の導電パターンと、を有し、

前記第1のプレーン状の導電パターンと前記第2のランド状の導電パターンとは、前記第1スルーホールに形成された第1導体膜により接続されており、

前記第2のプレーン状の導電パターンと前記第1のランド状の導電パターンとは、前記第2スルーホールに形成された第2導体膜により接続されており、

前記第1のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンとは、前記第1スルーホールに形成された前記第1導体膜、前記内層導体パターン、及び前記第2スルーホールに形成された前記第2導体膜を介して接続されていることを特徴とするブ

リント配線板。

**【請求項 2】**

前記第1のプレーン状の導電パターンは、前記第1のランド状の導電パターンよりも大きく、前記第2のプレーン状の導電パターンは、前記第2のランド状の導電パターンよりも大きいことを特徴とする請求項1に記載のプリント配線板。

**【請求項 3】**

プリント配線板と、

前記プリント配線板に実装された半導体パッケージと、を備え、

前記プリント配線板は、

前記半導体パッケージが実装された第1表層に配置された第1導体パターンと、

10

前記第1表層とは反対側の第2表層に配置された第2導体パターンと、

前記第1表層と前記第2表層との間の内層に配置された内層導体パターンと、を有しており、

前記プリント配線板には、前記第1表層、前記内層及び前記第2表層を貫通する第1スルーホール及び第2スルーホールが形成されており、

前記第1導体パターンは、前記半導体パッケージの導電部材にはんだにより接合された第1のプレーン状の導電パターンと、前記第1のプレーン状の導電パターンに周りを囲まれ、前記第1のプレーン状の導電パターンと隙間を介して配置された第1のランド状の導電パターンと、を有し、

前記第2導体パターンは、第2のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンに周りを囲まれ、前記第2のプレーン状の導電パターンと隙間を介して配置された第2のランド状の導電パターンと、を有し、

20

前記第1のプレーン状の導電パターンと前記第2のランド状の導電パターンとは、前記第1スルーホールに形成された第1導体膜により接続されており、

前記第2のプレーン状の導電パターンと前記第1のランド状の導電パターンとは、前記第2スルーホールに形成された第2導体膜により接続されており、

前記第1のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンとは、前記第1スルーホールに形成された前記第1導体膜、前記内層導体パターン、及び前記第2スルーホールに形成された前記第2導体膜を介して接続されていることを特徴とするプリント回路板。

30

**【請求項 4】**

前記第1のプレーン状の導電パターンは、前記第1のランド状の導電パターンよりも大きく、前記第2のプレーン状の導電パターンは、前記第2のランド状の導電パターンよりも大きいことを特徴とする請求項3に記載のプリント回路板。

**【請求項 5】**

前記第1のプレーン状の導電パターンは、前記半導体パッケージと対向する領域に形成されていることを特徴とする請求項3又は4に記載のプリント回路板。

**【請求項 6】**

前記第1のプレーン状の導電パターンと前記第1のランド状の導電パターンとは、前記半導体パッケージと対向する領域に形成されており、

40

前記第2のプレーン状の導電パターンは、前記プリント配線板の面に垂直な方向から見て、前記半導体パッケージの外周よりも外側に広がって形成されていることを特徴とする請求項3乃至5のいずれか1項に記載のプリント回路板。

**【請求項 7】**

前記はんだは、少なくとも前記半導体パッケージの導電部材と前記第1のプレーン状の導電パターンとの間と、前記第2スルーホールの中に設けられていることを特徴とする請求項3乃至6のいずれか1項に記載のプリント回路板。

**【請求項 8】**

前記内層導体パターンが、前記半導体パッケージの電源端子に電気的に接続される電源パターン、及び前記半導体パッケージのグラウンド端子に電気的に接続されるグラウンド

50

パターンのうち、いずれか一方の導体パターンであることを特徴とする請求項3乃至7の

いずれか1項に記載のプリント回路板。

**【請求項9】**

請求項1又は2に記載のプリント配線板における前記第1導体パターンにはんだペーストを塗布する工程と、

前記はんだペーストの上に、前記半導体パッケージの前記プリント配線板と対向する面に形成された導電部材が位置するように前記半導体パッケージを配置する工程と、

前記はんだペーストを加熱して溶融させることで、前記第1導体パターンのうち前記第1のプレーン状の導電パターンと前記導電部材とのはんだを介した接続状態を維持したまま、前記第1導体パターンのうち前記第1のランド状の導体パターンと前記導電部材との間のはんだが前記第2スルーホールに流動する工程と、

前記溶融したはんだを冷却する工程と、を備えたことを特徴とするプリント回路板の製造方法。

**【請求項10】**

プリント配線板が、半導体パッケージが実装される第1表層に配置された第1導体パターンと、前記第1表層とは反対側の第2表層に配置された第2導体パターンと、を有しており、

前記第1表層及び前記第2表層を貫通する第1スルーホール及び第2スルーホールが形成され、

前記第1導体パターンが、第1のプレーン状の導電パターンと、前記第1のプレーン状の導電パターンに周りを囲まれ、前記第1のプレーン状の導電パターンと隙間を介して配置された第1のランド状の導電パターンと、を有し、

前記第2導体パターンが、第2のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンに周りを囲まれ、前記第2のプレーン状の導電パターンと隙間を介して配置された第2のランド状の導電パターンと、を有し、

前記第1のプレーン状の導電パターンと前記第2のランド状の導電パターンとが、前記第1スルーホールに形成された第1導体膜により接続されており、

前記第2のプレーン状の導電パターンと前記第1のランド状の導電パターンとが、前記第2スルーホールに形成された第2導体膜により接続されている前記プリント配線板に、前記半導体パッケージを実装して製造するプリント回路板の製造方法であって、

前記プリント配線板における前記第1導体パターンにはんだペーストを塗布する工程と、

前記はんだペーストの上に、前記半導体パッケージの前記プリント配線板と対向する面に形成された導電部材が位置するように前記半導体パッケージを配置する工程と、

前記はんだペーストを加熱して溶融させることで、前記第1導体パターンのうち前記第1のプレーン状の導電パターンと前記導電部材とのはんだを介した接続状態を維持したまま、前記第1導体パターンのうち前記第1のランド状の導体パターンと前記導電部材との間のはんだが前記第2スルーホールに流動する工程と、

前記溶融したはんだを冷却する工程と、を備えたことを特徴とするプリント回路板の製造方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、放熱板を備えた半導体パッケージが実装する少なくとも3層のプリント配線板、プリント配線板を備えたプリント回路板及びプリント回路板の製造方法に関する。

**【背景技術】**

**【0002】**

プリント配線板に実装されるIC等の半導体パッケージにおいて、半導体パッケージ本体の裏面に放熱板が設けられたものがある。これは近年、半導体パッケージにおける信号処理の高速化に伴い、半導体パッケージの発熱が増加傾向にあり、半導体パッケージの放

10

20

30

40

50

熱を効率的に行う必要が生じているためである。この半導体パッケージを効率よく放熱させるために、半導体パッケージの放熱板とプリント配線板の実装面にある導体パターンとを半田によって接合するものが知られている（特許文献1参照）。

#### 【0003】

実装面にある導体パターンは、半導体パッケージの放熱板に対向させて半導体パッケージのピンに干渉しない大きさにする必要があり、また、プリント配線板に用いられる絶縁体は導体パターンよりも熱伝導率が低いため、導体パターンに熱がこもりやすい。そのため、特許文献1では、プリント配線板の実装面に対する反対面にも放熱用の導体パターンが設けられており、スルーホールにより実装面の導体パターンと反対面の導体パターンとを熱的に接続している。これにより、半導体パッケージのダイで発生した熱は、放熱板、半田、実装面の導体パターン、スルーホール及び反対面の導体パターンに順次伝導して、反対面の導体パターンから大気へ放熱させている。10

#### 【0004】

ところで、放熱板と実装面の導体パターンとをはんだ接合するリフロー工程において、溶融した半田がスルーホールに吸い込まれてしまうと、半田の接合不良が生じ、半導体パッケージの実装性が低下し、また、放熱性も低下する。

#### 【0005】

そこで、特許文献1では、実装面の導体パターンをソルダーレジストで分割し、その中央部の半田付けしないエリアにスルーホールを配置している。このソルダーレジストをリフロー工程における溶融した半田に対する防波堤として機能させ、スルーホールに半田が流れ込むのを防止しようとしている。20

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

#### 【特許文献1】特開2006-80168号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

しかしながら、上記特許文献1の構造のように放熱用の導体パターンが分割され、その中央部の半田付けしないエリアにスルーホールを設けても、スルーホールは半導体パッケージの放熱板に対向する位置にある。また、リフロー工程終了後においても、反対面の導体パターンの余熱がスルーホールを介して実装面の導体パターンに伝導しやすい。これによって、実装面の導体パターンに伝導した余熱で半田が溶融となり、半田が放熱板により押しつぶされて流動することにより、ソルダーレジストを超えてスルーホールに流れ込んでしまう。したがって、上記特許文献1の構成では、半田接合不良を効果的に解消することができなかつたため、さらなる改良が求められていた。30

#### 【0008】

そこで、本発明は、半田接合不良の発生が低減するプリント配線板、プリント回路板及びプリント回路板の製造方法を提供することを目的とするものである。

#### 【課題を解決するための手段】

#### 【0009】

本発明のプリント配線板は、半導体パッケージが実装される第1表層に配置された第1導体パターンと、前記第1表層とは反対側の第2表層に配置された第2導体パターンと、前記第1表層と前記第2表層との間の内層に配置された内層導体パターンと、を備え、前記第1表層、前記内層及び前記第2表層を貫通する第1スルーホール及び第2スルーホールが形成され、前記第1導体パターンは、第1のプレーン状の導電パターンと、前記第1のプレーン状の導電パターンに周りを囲まれ、前記第1のプレーン状の導電パターンと隙間を介して配置された第1のランド状の導電パターンと、を有し、前記第2導体パターンは、第2のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンに周りを囲まれ、前記第2のプレーン状の導電パターンと隙間を介して配置された第2のランド状40

の導電パターンと、を有し、前記第1のプレーン状の導電パターンと前記第2のランド状の導電パターンとは、前記第1スルーホールに形成された第1導体膜により接続されており、前記第2のプレーン状の導電パターンと前記第1のランド状の導電パターンとは、前記第2スルーホールに形成された第2導体膜により接続されており、前記第1のプレーン状の導電パターンと、前記第2のプレーン状の導電パターンとは、前記第1スルーホールに形成された前記第1導体膜、前記内層導体パターン、及び前記第2スルーホールに形成された前記第2導体膜を介して接続されていることを特徴とする。

【発明の効果】

【0010】

本発明によれば、第2導体パターンが第1導体膜の第2表層側の端部を切り離したパターンに形成されているので、リフロー工程時の加熱による第2導体パターンから第1導体膜への熱伝導が効果的に低減され、第1導体膜の温度上昇を抑制できる。したがって、第1スルーホールに半田が流れ込むのを抑制することができ、半田接合不良の発生を低減することができる。

10

【図面の簡単な説明】

【0012】

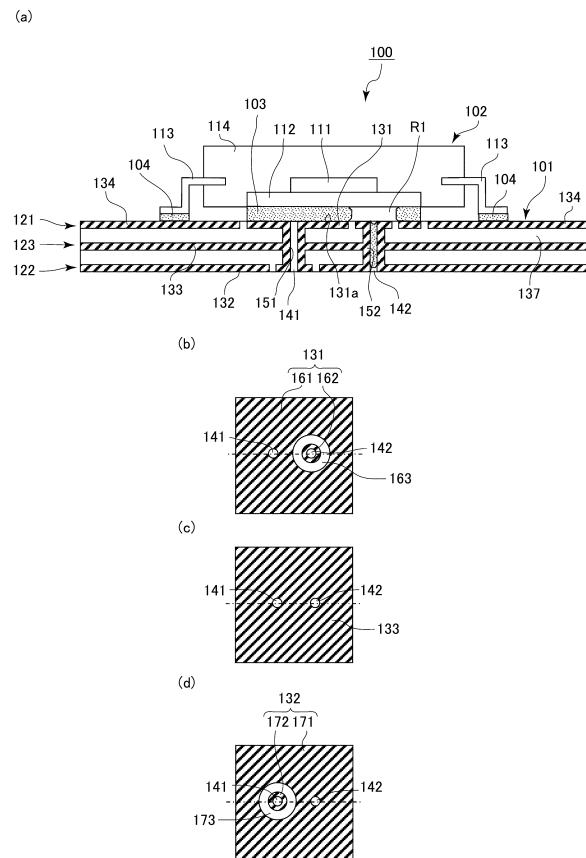

【図1】本発明の第1実施形態に係るプリント回路板の概略構成を示す説明図である。

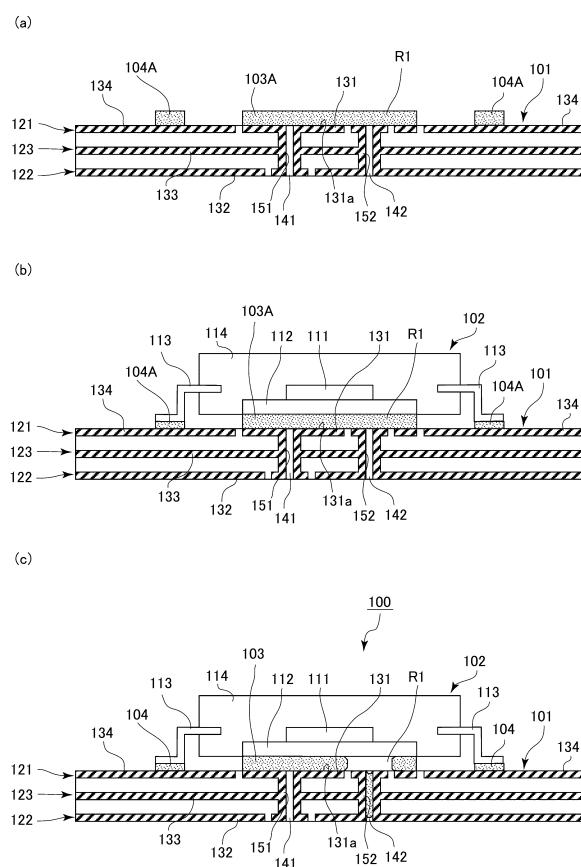

【図2】プリント回路板の製造方法における各工程を示す説明図である。

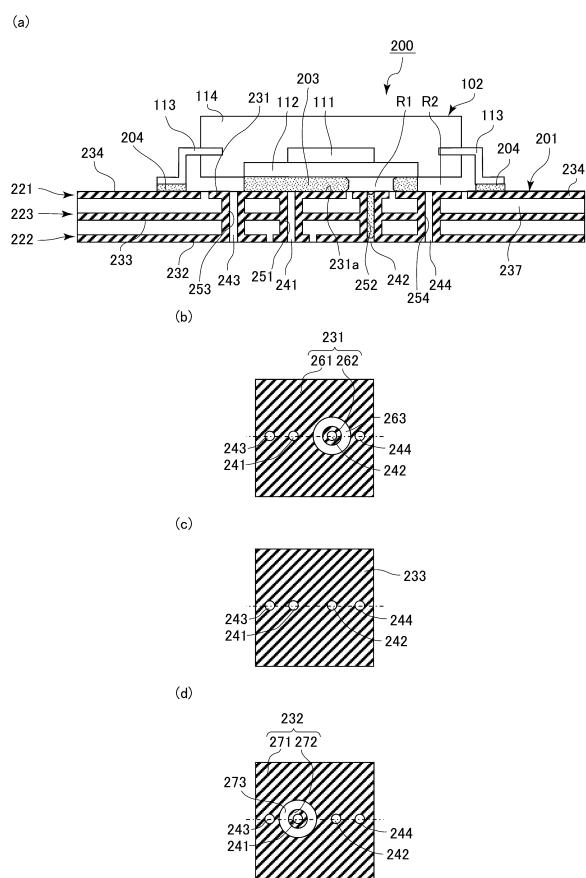

【図3】本発明の第2実施形態に係るプリント回路板の概略構成を示す説明図である。

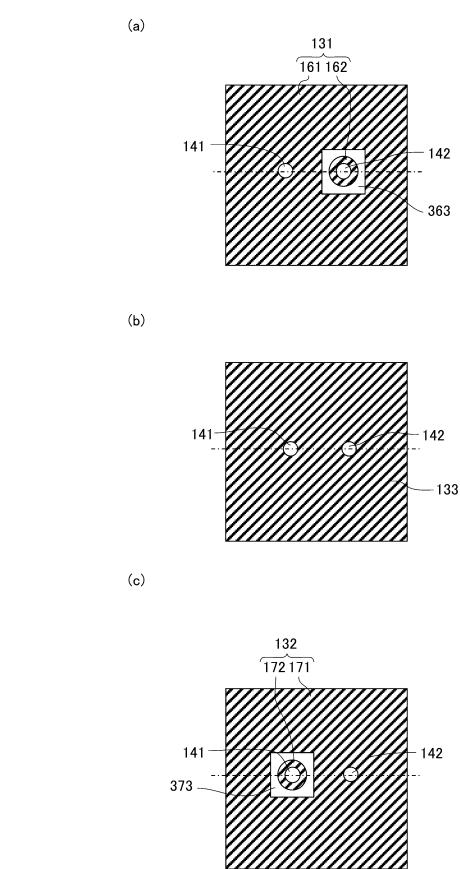

【図4】本発明の第3実施形態に係るプリント回路板の概略構成を示す説明図である。

20

【図5】本発明の第4実施形態に係るプリント回路板の概略構成を示す説明図である。

【図6】比較例のプリント回路板の概略構成を示す説明図である。

【図7】比較例のプリント回路板の製造方法における各工程を示す説明図である。

【発明を実施するための形態】

【0013】

以下、本発明を実施するための形態を、図面を参照しながら詳細に説明する。

【0014】

[第1実施形態]

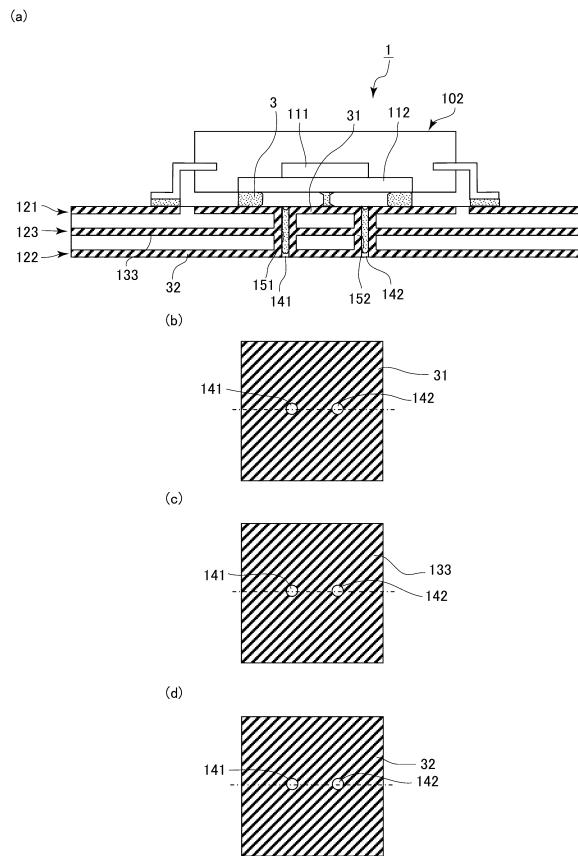

図1は、本発明の第1実施形態に係るプリント回路板の概略構成を示す説明図である。図1(a)はプリント回路板の断面図、図1(b)はプリント配線板の第1導体パターンの平面図、図1(c)はプリント配線板の内層導体パターンの平面図、図1(d)はプリント配線板の第2導体パターンの平面図である。

30

【0015】

図1(a)に示すように、プリント回路板100は、プリント配線板101と、プリント配線板101に実装された半導体パッケージ102と、を備えている。半導体パッケージ102は、本第1実施形態では、QFP型、QFN型若しくはBGA型の半導体パッケージであり、図1では、QFP型の半導体パッケージを図示している。

【0016】

半導体パッケージ102は、半導体素子であって発熱源であるダイ111と、ダイ111に熱的に接続された放熱板112と、ダイ111に不図示のワイヤで電気的に接続されたりード113と、を備えている。これらダイ111、放熱板112の一部及びリード113の一部は、モールド樹脂114でモールドされている。

40

【0017】

プリント配線板101は、半導体パッケージ102が実装される第1表層である表層121と、表層121とは反対側の第2表層である表層122と、表層121と表層122との間の内層123とが、絶縁層を介して積層された3層プリント配線板である。絶縁層には、絶縁体137が設けられている。

【0018】

プリント配線板101は、表層121に配置された第1導体パターンである放熱用パターン131と、表層122に配置された第2導体パターンである放熱用パターン132と

50

、内層 123 に配置された内層導体パターン 133 と、を備えている。また、プリント配線板 101 は、表層 121 に配置され、半導体パッケージ 102 のリード 113 に電気的に接続される信号線パターン 134 を備えている。本第 1 実施形態では、放熱用パターン 131 と信号線パターン 134 とは絶縁体 137 を介して電気的に絶縁されている。これらパターン 131, 132, 133, 134 は、例えば銅で形成されている。

#### 【0019】

放熱用パターン 131 は、半導体パッケージ 102 の放熱板 112 に対向する対向領域 R1 に配置された、半田 103 で放熱板 112 に接合される接合部分 131a を有しており、本第 1 実施形態では、放熱用パターン 131 の表面全体が接合部分 131a となる。この接合部分 131a と放熱板 112 とは半田 103 で接合されている。放熱用パターン 131 は、外周が半導体パッケージ 102 のリード 113 で囲われてあり、リード 113 に接触しない形状（例えば外形が四角形状）に形成されている。なお、半導体パッケージ 102 のリード 113 と信号線パターン 134 とは半田 104 で接合されている。放熱用パターン 132 は、放熱用パターン 131 よりも広い面積のパターンである。

#### 【0020】

プリント配線板 101 には、表層 121、内層 123 及び表層 122 を貫通する、第 1 スルーホールとしてのスルーホール 141 と、第 2 スルーホールとしてのスルーホール 142 とが形成されている。本第 1 実施形態では、第 1 スルーホール及び第 2 スルーホールがそれぞれ 1 つの場合について説明する。スルーホール 141, 142 は、本第 1 実施形態では、対向領域 R1 に配置されている。

#### 【0021】

スルーホール 141 の内壁には、第 1 導体膜としての導体膜 151 が設けられており、スルーホール 142 の内壁には、第 2 導体膜としての導体膜 152 が設けられている。これら導体膜 151, 152 は、例えば銅で形成されている。

#### 【0022】

導体膜 151 は、スルーホール 141 の第 1 表層側である表層 121 側の端部からスルーホール 141 の第 2 表層側である表層 122 側の端部まで延びるように形成されている。同様に、導体膜 152 は、スルーホール 142 の表層 121 側の端部からスルーホール 142 の表層 122 側の端部まで延びるように形成されている。

#### 【0023】

本第 1 実施形態では、放熱用パターン 131 は、表層 121 において、図 1 (b) に示すように、スルーホール 141 の導体膜 151 に物理的に接続されたベタの導体パターン 161 を有している。また、放熱用パターン 131 は、表層 121 において、スルーホール 142 の導体膜 152 に物理的に接続された導体ランド 162 を有している。導体パターン 161 と導体ランド 162との間には、クリアランス 163 が設けられており、導体パターン 161 と導体ランド 162 とは表層 121 において非接触である。そして、導体ランド 162 は、導体パターン 161 よりも面積が小さい。

#### 【0024】

また、本第 1 実施形態では、放熱用パターン 132 は、表層 122 において、図 1 (d) に示すように、スルーホール 142 の導体膜 152 に物理的に接続されたベタの導体パターン 171 を有している。また、放熱用パターン 132 は、表層 122 において、スルーホール 141 の導体膜 151 に物理的に接続された導体ランド 172 を有している。導体パターン 171 と導体ランド 172 との間には、クリアランス 173 が設けられており、導体パターン 171 と導体ランド 172 とは表層 122 において非接触である。そして、導体ランド 172 は、導体パターン 171 よりも面積が小さい。

#### 【0025】

つまり、導体膜 151 の表層 121 側の端部は、表層 121 において、図 1 (b) に示すように、導体パターン 161 に物理的に接続されており、これにより導体パターン 161 に電気的及び熱的に接続されている。導体膜 151 の中央部は、内層 123 において、図 1 (c) に示すように、内層導体パターン 133 に物理的に接続されており、これによ

10

20

30

40

50

り内層導体パターン133に電気的及び熱的に接続されている。また、導体膜151の表層122側の端部は、表層122において、図1(d)に示すように、導体ランド172に物理的に接続されており、これにより導体ランド172に電気的及び熱的に接続されている。

#### 【0026】

また、導体膜152の表層122側の端部は、表層122において、図1(d)に示すように、導体パターン171に物理的に接続されており、これにより導体パターン171に電気的及び熱的に接続されている。導体膜152の中央部は、内層123において、図1(c)に示すように、内層導体パターン133に物理的に接続されており、これにより内層導体パターン133に電気的及び熱的に接続されている。また、導体膜152の表層121側の端部は、表層121において、図1(b)に示すように、導体ランド162に物理的に接続されており、これにより導体ランド162に電気的及び熱的に接続されている。10

#### 【0027】

放熱用パターン131は、導体パターン161と導体ランド162とにクリアランス163によって分離したパターン、即ち導体膜152の表層121側の端部を切り離したパターンに形成されている。また、放熱用パターン132は、導体パターン171と導体ランド172とにクリアランス173によって分離したパターン、即ち導体膜151の表層122側の端部を切り離したパターンに形成されている。20

#### 【0028】

これにより、スルーホール141の導体膜151の表層122側の端部は、導体パターン171に対して空隙により分離されており、表層122において、導体パターン171の熱が導体膜151の表層122側の端部に伝導しにくい。また、スルーホール142の導体膜152の表層121側の端部は、導体パターン161に対して空隙により分離されており、表層121において、導体膜152の熱が導体パターン161に伝導しにくい。20

#### 【0029】

クリアランス163, 173を大きくするほど、放熱板112の下部のプリント配線板101の導体の面積が小さくなり、またスルーホール141とスルーホール142との間隔も広がる。したがって、クリアランス163, 173を大きくするほど、半導体パッケージ102の動作時の放熱性が低下する。そのため、クリアランス163, 173は、信号線パターン134と同程度の太さが望ましい。30

#### 【0030】

半導体パッケージ102の動作時の放熱性の観点から、スルーホール141の導体膜151とスルーホール142の導体膜152とは、ベタパターンで接続されていることが好ましく、できるだけ広く接続されていることが望ましい。つまり、内層導体パターン133は、内層123に配置された導体パターンであればよいが、ベタの導体パターンであるのが好ましい。ベタの導体パターンとしては、直流の電源電圧が印加される電源パターン及びグラウンド電圧(0V)が印加されるグラウンドパターンがあり、内層導体パターン133は、電源パターン及びグラウンドパターンのうちの一方の導体パターンとするのが好ましい。本第1実施形態では、内層導体パターン133は、グラウンドパターンである。このように、内層導体パターン133が、グラウンドパターンであるので、導体膜151と導体膜152との接続のためにグラウンドパターンのほかに別途導体パターンを設けなくてよい。なお、内層導体パターン133が電源パターンである場合も同様に、別途導体パターンを設けなくてもよい。40

#### 【0031】

本第1実施形態では、ダイ111のグラウンド端子を放熱板112に電気的に接続しており、放熱板112は半導体パッケージ102のグラウンド端子を兼ねている。したがって、半導体パッケージ102のグラウンド端子である放熱板112は、スルーホール141の導体膜151を介してグラウンドパターンである内層導体パターン133に電気的に接続されていることとなる。50

**【0032】**

なお、内層導体パターン133が放熱用パターンである場合には、ダイ111の電源端子を放熱板112に電気的に接続して、放熱板112を半導体パッケージ102の電源端子として機能させてもよい。この場合も、放熱板112と接合部分131aとを半田103で接合すればよい。

**【0033】**

次に、プリント回路板100の製造方法について説明する。図2は、プリント回路板の製造方法における各工程を示す説明図であり、図2(a)は塗布工程、図2(b)はマウント工程、図2(c)はリフロー工程を示している。

**【0034】**

図2(a)に示すように、プリント配線板101における放熱用パターン131の接合部分131aに半田ペースト103Aを塗布する(塗布工程)。この塗布工程では、半導体パッケージ102のリード113に対応する部分にも半田ペースト104Aを塗布する。この塗布工程では、不図示のマスクを用いてスクリーン印刷により半田ペースト103A, 104Aを表層121に塗布する。

**【0035】**

次に、図2(b)に示すように、半導体パッケージ102を表層121にマウントする(マウント工程)。このとき、半導体パッケージ102の放熱板112を半田ペースト103Aに接触させると共に、半導体パッケージ102のリード113を半田ペースト104Aに接触させている。

**【0036】**

次に、図2(c)に示すように、半田ペースト103Aに放熱板112を接触させ、且つ半田ペースト104Aにリード113を接触させた状態で半田ペースト103A, 104Aを加熱する(リフロー工程)。これにより、半田ペースト103A, 104Aが溶融され、加熱終了後、放熱板112と接合部分131aとの半田103による半田接合が完了し、プリント回路板100が得られる。このリフロー工程における加熱では、プリント回路板100の外周面が内部よりも温度が高い状態となる。

**【0037】**

本第1実施形態では、リフロー工程後、放熱用パターン132の導体パターン171の余熱が、クリアランス173によりスルーホール141の導体膜151へ直接伝導されるのが低減されている。また、スルーホール141の導体膜151とスルーホール142の導体膜152とは、内層導体パターン133で接続されているが、導体パターン132, 133の熱抵抗は、スルーホールの導体膜151, 152の熱抵抗や外気への熱抵抗よりも大きい。したがって、放熱用パターン132の導体パターン171の余熱の大部分は、外気に放散され、残りの余熱が、スルーホール142の導体膜152へ伝導される。この導体膜152へ伝導された熱は、内層導体パターン133へはほとんど伝導されないため、導体パターン171の余熱が、スルーホール141の導体膜151へ伝導されるのが抑制される。

**【0038】**

これにより、スルーホール141の内部の温度上昇が抑制されるため、スルーホール141近傍の半田の溶融を抑制することができ、スルーホール141の内部に半田が濡れ広がって流れ込むのを抑制することができる。

**【0039】**

また、放熱用パターン132の導体パターン171の余熱は、スルーホール142の導体膜152を介して表層121の導体ランド162に伝導されるが、クリアランス163が設けられているため、導体パターン161へ伝導されるのが抑制されている。したがって、半田103の溶融は、導体ランド162の近傍のみで済み、スルーホール142への半田の吸い込み量は従来よりも低減される。

**【0040】**

したがって、放熱板112と放熱用パターン131と間に隙間が生じて半田接合不良が

10

20

30

40

50

発生するのを低減することができる。

#### 【0041】

次に、クリアランス 163, 173 を設けていない比較例のプリント回路板について説明する。図 6 は、比較例のプリント回路板の概略構成を示す説明図である。図 6 (a) はプリント回路板の断面図、図 6 (b) はプリント配線板の第 1 導体パターンの平面図、図 6 (c) はプリント配線板の内層導体パターンの平面図、図 6 (d) はプリント配線板の第 2 導体パターンの平面図である。プリント回路板 1において、図 1 のプリント回路板 100 と異なるのは、クリアランス 163, 173 が設けられていない点である。つまり、表層 121 の放熱用パターン 31 は、スルーホール 141, 142 の導体膜 151, 152 に直接接続されており、表層 122 の放熱用パターン 32 は、スルーホール 141, 142 の導体膜 151, 152 に直接接続されている。

10

#### 【0042】

図 7 は、比較例のプリント回路板の製造方法における各工程を示す説明図であり、図 7 (a) はマウント工程、図 7 (b) はリフロー工程を示している。

#### 【0043】

図 7 (a) に示すリフロー工程前では半田ペースト 3A は放熱板 112 と放熱用パターン 31との間に充填されている。図 7 (b) に示すリフロー工程の終了後は、放熱用パターン 32 の余熱によりスルーホール 141, 142 の内部が熱せられて半田 3 が溶融する。溶融した半田 3 がスルーホール 141, 142 に流れ込んでしまい、放熱板 112 と放熱用パターン 31 との半田接合面積が減少し、半田接合不良が発生する。このように、比較例のプリント回路板 1 では、半田 3 の接合不良が発生しているため、ダイ 111 で発生した熱は、放熱板 112 へ伝導されるが、放熱板 112 へ伝導された熱は、放熱用パターン 31 へ効率的に伝導させることができない。その結果、半導体パッケージ 102 に熱がこもることとなる。

20

#### 【0044】

以上、本第 1 実施形態によれば、製造工程のリフロー工程終了後においては、放熱用パターン 132 の導体パターン 171 からスルーホール 141 の導体膜 151 への熱伝導が妨げられ、スルーホール 141 の内部の温度上昇を抑制することができる。したがって、スルーホール 141 への半田の吸い込みを防止することができる。

#### 【0045】

また、導体パターン 171 の余熱は、スルーホール 142 の導体膜 152 を介して導体ランド 162 に伝導されるが、クリアランス 163 により導体パターン 161 へは伝導されにくいため、スルーホール 142 に吸い込まれる半田の量を低減できる。

30

#### 【0046】

したがって、放熱板 112 と接合部分 131a との半田接合不良の発生を低減することができる。

#### 【0047】

また、半導体パッケージ 102 の動作時に発生した定的な熱は、半田 103、放熱用パターン 131 の導体パターン 161、導体膜 151、内層導体パターン 133、導体膜 152 及び放熱用パターン 132 の導体パターン 171 へと順次伝導される。導体パターン 171 に伝導した熱は、導体パターン 171 から外気へ放熱される。したがって、半導体パッケージ 102 の動作時の放熱性が損なわれることはない。

40

#### 【0048】

また、スルーホール 141, 142 を対向領域 R1 に配置したので、スルーホール 141, 142 同士が近接し、内層導体パターン 133 における熱抵抗が小さくなり、効率よく半導体パッケージ 102 を放熱することができる。

#### 【0049】

##### [第 2 実施形態]

次に、本発明の第 2 実施形態に係るプリント回路板について説明する。図 3 は、本発明の第 2 実施形態に係るプリント回路板の概略構成を示す説明図である。図 3 (a) はプリ

50

ント回路板の断面図、図3( b )はプリント配線板の第1導体パターンの平面図、図3( c )はプリント配線板の内層導体パターンの平面図、図3( d )はプリント配線板の第2導体パターンの平面図である。

#### 【 0 0 5 0 】

図3( a )に示すように、プリント回路板200は、プリント配線板201と、プリント配線板201に実装された上記第1実施形態と同様の半導体パッケージ102と、を備えている。

#### 【 0 0 5 1 】

プリント配線板201は、半導体パッケージ102が実装される第1表層である表層221と、表層221とは反対側の第2表層である表層222と、表層221と表層222との間の内層223とが、絶縁層を介して積層された3層プリント配線板である。絶縁層には、絶縁体237が設けられている。

#### 【 0 0 5 2 】

プリント配線板201は、表層221に配置された第1導体パターンである放熱用パターン231と、表層222に配置された第2導体パターンである放熱用パターン232と、内層223に配置された内層導体パターン233と、を備えている。また、プリント配線板201は、表層221に配置され、半導体パッケージ102のリード113に電気的に接続される信号線パターン234を備えている。本第2実施形態では、放熱用パターン231と信号線パターン234とは絶縁体237を介して電気的に絶縁されている。これらパターン231, 232, 233, 234は、例えば銅で形成されている。

#### 【 0 0 5 3 】

放熱用パターン231は、半導体パッケージ102の放熱板112に対向する対向領域R1に配置された、半田203で放熱板112に接合される接合部分231aを有しており、第2実施形態では、放熱用パターン231の表面の中央部が接合部分231aとなる。この接合部分231aと放熱板112とは半田203で接合されている。放熱用パターン231は、外周が半導体パッケージ102のリード113で囲われてあり、リード113に接触しない形状(例えば外形が四角形状)に形成されている。なお、半導体パッケージ102のリード113と信号線パターン234とは半田204で接合されている。放熱用パターン232は、放熱用パターン231よりも広い面積のパターンである。

#### 【 0 0 5 4 】

プリント配線板201には、表層221、内層223及び表層222を貫通する、第1スルーホールとしてのスルーホール241と、第2スルーホールとしてのスルーホール242と、第3スルーホールとしてのスルーホール243, 244とが形成されている。本第2実施形態では、第1スルーホールと第2スルーホールがそれぞれ1つであり、第3スルーホールが複数ある場合について説明する。

#### 【 0 0 5 5 】

スルーホール241の内壁には、第1導体膜としての導体膜251が設けられており、スルーホール242, 243, 244の内壁には、それぞれ第2導体膜としての導体膜252, 253, 254が設けられている。これら導体膜251～254は、例えば銅で形成されている。

#### 【 0 0 5 6 】

導体膜251は、スルーホール241の第1表層側である表層221側の端部からスルーホール241の第2表層側である表層222側の端部まで延びるように形成されている。同様に、導体膜252は、スルーホール242の表層221側の端部からスルーホール242の表層222側の端部まで延びるように形成されている。また、導体膜253は、スルーホール243の表層221側の端部からスルーホール243の表層222側の端部まで延びるように形成されている。また、導体膜254は、スルーホール244の表層221側の端部からスルーホール244の表層222側の端部まで延びるように形成されている。

#### 【 0 0 5 7 】

10

20

30

40

50

放熱用パターン231は、表層221において、図3(b)に示すように、スルーホール241, 243, 244の導体膜251, 253, 254に物理的に接続されたベタの導体パターン261を有している。また、放熱用パターン231は、表層221において、スルーホール242の導体膜252に物理的に接続された導体ランド262を有している。導体パターン261と導体ランド262との間には、クリアランス263が設けられており、導体パターン261と導体ランド262とは表層221において非接触である。そして、導体ランド262は、導体パターン261よりも面積が小さい。

#### 【0058】

また、放熱用パターン232は、表層222において、図3(d)に示すように、スルーホール242, 243, 244の導体膜252, 253, 254に物理的に接続されたベタの導体パターン271を有している。また、放熱用パターン232は、表層222において、スルーホール241の導体膜251に物理的に接続された導体ランド272を有している。導体パターン271と導体ランド272との間には、クリアランス273が設けられており、導体パターン271と導体ランド272とは表層222において非接触である。そして、導体ランド272は、導体パターン271よりも面積が小さい。

10

#### 【0059】

つまり、導体膜251の表層221側の端部は、表層221において、図3(b)に示すように、導体パターン261に物理的に接続されており、これにより導体パターン261に電気的及び熱的に接続されている。導体膜251の中央部は、内層223において、図3(c)に示すように、内層導体パターン233に物理的に接続されており、これにより内層導体パターン233に電気的及び熱的に接続されている。また、導体膜251の表層222側の端部は、表層222において、図3(d)に示すように、導体ランド272に物理的に接続されており、これにより導体ランド272に電気的及び熱的に接続されている。

20

#### 【0060】

また、導体膜252の表層222側の端部は、表層222において、図3(d)に示すように、導体パターン271に物理的に接続されており、これにより導体パターン271に電気的及び熱的に接続されている。導体膜252の中央部は、内層223において、図3(c)に示すように、内層導体パターン233に物理的に接続されており、これにより内層導体パターン233に電気的及び熱的に接続されている。また、導体膜252の表層221側の端部は、表層221において、図3(b)に示すように、導体ランド262に物理的に接続されており、これにより導体ランド262に電気的及び熱的に接続されている。

30

#### 【0061】

このように、放熱用パターン231は、導体パターン261と導体ランド262とにクリアランス263によって分離したパターン、即ち導体膜252の表層221側の端部を切り離したパターンに形成されている。また、放熱用パターン232は、導体パターン271と導体ランド272とにクリアランス273によって分離したパターン、即ち導体膜251の表層222側の端部を切り離したパターンに形成されている。

#### 【0062】

40

これにより、スルーホール241の導体膜251の表層222側の端部は、導体パターン271に対して空隙により分離されており、表層222において、導体パターン271の熱が導体膜251の表層222側の端部に伝導しにくい。また、スルーホール242の導体膜252の表層221側の端部は、導体パターン261に対して空隙により分離されており、表層221において、導体膜252の熱が導体パターン261に伝導しにくい。

#### 【0063】

本第2実施形態では、スルーホール241, 242, 243, 244のうち、スルーホール241, 242は、対向領域R1に配置され、スルーホール243, 244は、対向領域以外の領域R2に配置されている。したがって、プリント回路板200の製造工程における塗布工程では、スルーホール241, 242上には、半田ペーストは塗布されるが

50

、スルーホール 243, 244 上には、半田ペーストは塗布されない。

**【0064】**

したがって、本第2実施形態では、スルーホール 243, 244 に半田ペーストが吸い込まれる可能性が低いため、スルーホール 243, 244 の導体膜 253, 254 の両端部は、それぞれ導体パターン 261, 271 に接続されている。

**【0065】**

半導体パッケージ 102 の動作時の放熱性の観点から、スルーホール 241 ~ 244 の導体膜 251 ~ 254 同士は、ベタパターンで接続されていることが好ましく、できるだけ広く接続されていることが望ましい。つまり、内層導体パターン 233 は、内層 223 に配置された導体パターンであればよいが、ベタの導体パターンであるのが好ましい。10 ベタの導体パターンとしては、直流の電源電圧が印加される電源パターン及びグラウンド電圧(0V)が印加されるグラウンドパターンがあり、内層導体パターン 233 は、電源パターン及びグラウンドパターンのうちの一方の導体パターンとするのが好ましい。本第2実施形態では、内層導体パターン 233 は、グラウンドパターンである。このように、内層導体パターン 233 が、グラウンドパターンであるので、導体膜 251 ~ 254 の接続のためにグラウンドパターンのほかに別途導体パターンを設けなくてよい。なお、内層導体パターン 233 が電源パターンである場合も同様に、別途導体パターンを設けなくてもよい。

**【0066】**

本第2実施形態では、ダイ 111 のグラウンド端子を放熱板 112 に電気的に接続しており、放熱板 112 は半導体パッケージ 102 のグラウンド端子を兼ねている。したがって、半導体パッケージ 102 のグラウンド端子である放熱板 112 は、スルーホール 241 の導体膜 251 を介してグラウンドパターンである内層導体パターン 233 に電気的に接続されていることとなる。20

**【0067】**

なお、内層導体パターン 233 が電源パターンである場合には、ダイ 111 の電源端子を放熱板 112 に電気的に接続して、放熱板 112 を半導体パッケージ 102 の電源端子として機能させてもよい。この場合も、放熱板 112 と接合部分 231a とを半田 203 で接合すればよい。

**【0068】**

以上、本第2実施形態によれば、製造工程のリフロー工程終了後においては、放熱用パターン 232 の導体パターン 271 からスルーホール 241 の導体膜 251 への熱伝導が妨げられ、スルーホール 241 の内部の温度上昇を抑制することができる。したがって、スルーホール 241 への半田の吸い込みを防止することができる。30

**【0069】**

また、導体パターン 271 の余熱は、スルーホール 242 の導体膜 252 を介して導体ランド 262 に伝導されるが、クリアランス 263 により導体パターン 261 へは伝導されにくいため、スルーホール 242 に吸い込まれる半田の量を低減できる。

**【0070】**

したがって、放熱板 112 と接合部分 231a との半田接合不良の発生を低減することができる。40

**【0071】**

また、半導体パッケージ 102 の動作時に発生した定的な熱は、半田 203、放熱用パターン 231 の導体パターン 261、導体膜 251、内層導体パターン 233、導体膜 252 及び放熱用パターン 232 の導体パターン 271 に順次伝導される。或いは、放熱用パターン 231 の導体パターン 261 に伝導した熱が、スルーホール 243, 244 の導体膜 253, 254 を介して放熱用パターン 232 の導体パターン 271 へと伝導される。導体パターン 271 に伝導した熱は、導体パターン 271 から外気へ放熱される。したがって、半導体パッケージ 102 の動作時の放熱性が損なわれることはない。

**【0072】**

また、スルーホール 241, 242 を対向領域 R1 に配置したので、スルーホール 241, 242 同士が近接し、内層導体パターン 233 における熱抵抗が小さくなり、効率よく半導体パッケージ 102 を放熱することができる。

#### 【0073】

また、対向領域 R1 にスルーホール 242 を配置すると共に、領域 R2 にもスルーホール 243, 244 を配置したので、上記第1実施形態よりも放熱性がさらに向上する。

#### 【0074】

なお、本第2実施形態では、対向領域 R1 においてスルーホール 242 が形成されている場合について説明したが、スルーホール 242 を省略して、領域 R2 にのみ第3スルーホールであるスルーホール 243, 244 が形成されている場合であってもよい。 10

#### 【0075】

##### 【第3実施形態】

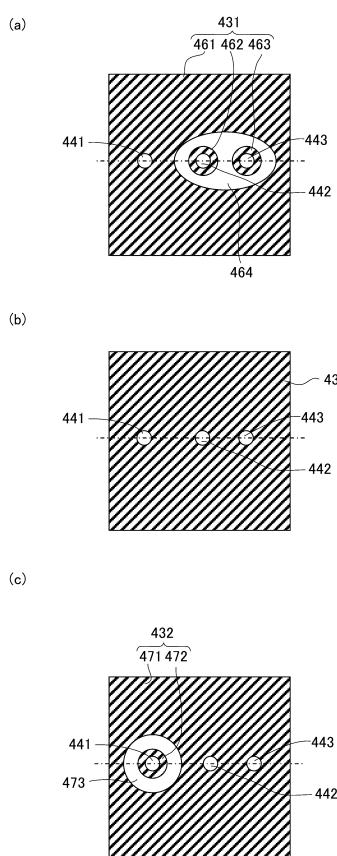

次に、本発明の第3実施形態に係るプリント回路板について説明する。図4は、本発明の第3実施形態に係るプリント回路板の概略構成を示す説明図である。図4(a)はプリント配線板の第1導体パターンの平面図、図4(b)はプリント配線板の内層導体パターンの平面図、図4(c)はプリント配線板の第2導体パターンの平面図である。

#### 【0076】

上記第1実施形態では、スルーホール 142 に対応するクリアランス 163 が円形であり、スルーホール 141 に対応するクリアランス 173 が円形である場合について説明したが、円形に限定するものではない。本第3実施形態では、図4に示すように、四角形のクリアランス 363, 373 であってもよい。即ち、導体パターン 161 と導体ランド 162、導体パターン 171 と導体ランド 172 に分割されていればよく、クリアランスの形状は、円形や四角形以外に、三角形など、どのような形状のものであってもよい。 20

#### 【0077】

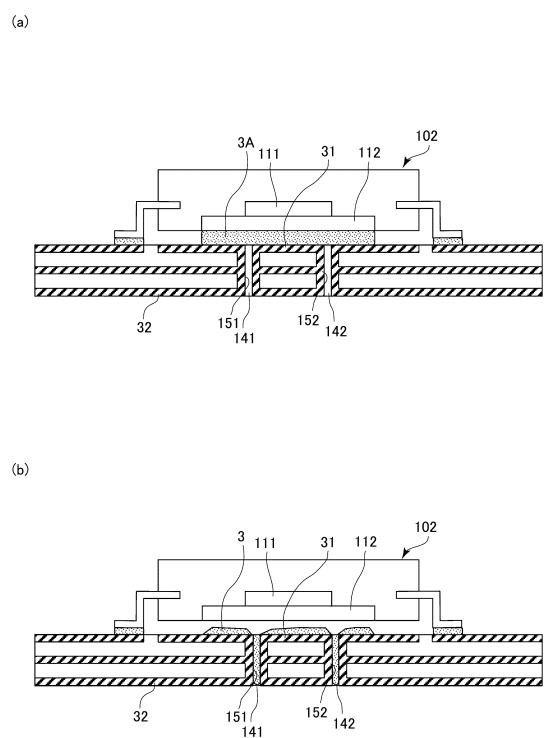

##### 【第4実施形態】

次に、本発明の第4実施形態に係るプリント回路板について説明する。図5は、本発明の第4実施形態に係るプリント回路板の概略構成を示す説明図である。図5(a)はプリント配線板の第1導体パターンの平面図、図5(b)はプリント配線板の内層導体パターンの平面図、図5(c)はプリント配線板の第2導体パターンの平面図である。

#### 【0078】

第1スルーホールの数は、単数であってもよいし、複数であってもよい。また、第2スルーホールの数も、単数であってもよいし、複数であってもよい。そして、第2スルーホールは、対向領域 R1 に配置するのが好ましいが、対向領域 R1 以外の領域 R2(図3)に配置してもよい。

#### 【0079】

さらに半導体パッケージ 102 の放熱効果としては、第1スルーホールと第2スルーホールとの数の比が1対1であるのが望ましいが、これに限るものでない。図5では、第1スルーホールの数と第2スルーホールの数との比が、2対1の場合について図示している。図5(a)～図5(c)に示すように第1スルーホールであるスルーホール 441 と第2スルーホールであるスルーホール 442, 443 との数の比が、2対1 であっても良い。 40

#### 【0080】

本第4実施形態では、放熱用パターン 431 は、第1表層において、図5(a)に示すように、スルーホール 441 の導体膜に物理的に接続されたベタの導体パターン 461 を有している。また、放熱用パターン 431 は、第1表層において、スルーホール 442, 443 の導体膜に物理的に接続された導体ランド 462, 463 を有している。導体パターン 461 と導体ランド 462, 463 との間には、クリアランス 464 が設けられており、導体パターン 461 と導体ランド 462, 463 とは第1表層において非接触である。そして、導体ランド 462, 463 は、導体パターン 461 よりも面積が小さい。

#### 【0081】

また、本第4実施形態では、放熱用パターン432は、第2表層において、図5(c)に示すように、スルーホール442, 443の導体膜に物理的に接続されたベタの導体パターン471を有している。また、放熱用パターン432は、第2表層において、スルーホール441の導体膜に物理的に接続された導体ランド472を有している。導体パターン471と導体ランド472との間には、クリアランス473が設けられており、導体パターン471と導体ランド472とは第2表層において非接触である。そして、導体ランド472は、導体パターン471よりも面積が小さい。

#### 【0082】

また、内層導体パターン433は、内層において、スルーホール441, 442, 443の導体膜に物理的に接続されている。

10

#### 【0083】

以上、本第4実施形態のスルーホール442, 443のように、スルーホール(この場合は、第2スルーホール)が複数である場合には、図5(a)に示すように、複数のスルーホール442, 443でクリアランス464が兼用されていてもよい。

#### 【0084】

なお、本発明は、以上説明した実施形態に限定されるものではなく、多くの変形が本発明の技術的思想内で当分野において通常の知識を有する者により可能である。

#### 【0085】

上記第1～第4実施形態では、スルーホールの導体膜に接続される導体ランドが形成されており、放熱用パターンが導体パターンと導体ランドとが切り離されている場合について説明したが、導体ランドが省略されている場合であってもよい。この場合、放熱用パターンとスルーホールの導体膜の端部とが直接切り離されていることになる。

20

#### 【0086】

また、上記第1～第4実施形態では、プリント配線板が、3層のプリント配線板である場合について説明したが、4層以上のプリント配線板であってもよい。

#### 【符号の説明】

#### 【0087】

100…プリント回路板、101…プリント配線板、102…半導体パッケージ、103…半田、111…ダイ(半導体素子)、112…放熱板、121…表層(第1表層)、122…表層(第2表層)、123…内層、131…放熱用パターン(第1導体パターン)、132…放熱用パターン(第2導体パターン)、133…内層導体パターン、141…スルーホール(第1スルーホール)、142…スルーホール(第2スルーホール)、151…導体膜(第1導体膜)、152…導体膜(第2導体膜)、161…導体パターン(第1のプレーン状の導電パターン)、162…導体ランド(第1のランド状の導電パターン)、171…導体パターン(第2のプレーン状の導電パターン)、172…導体ランド(第2のランド状の導電パターン)

30

【 図 1 】

【 図 2 】

【 四 3 】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(56)参考文献 米国特許出願公開第2009/0002950(US,A1)

特開2005-340233(JP,A)

実開平04-080086(JP,U)

(58)調査した分野(Int.Cl., DB名)

H05K 1/00 ~ 1/02

H05K 3/32 ~ 3/34

H05K 3/46