(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5276094号

(P5276094)

(45) 発行日 平成25年8月28日(2013.8.28)

(24) 登録日 平成25年5月24日(2013.5.24)

(51) Int.Cl.

G06F 9/46 (2006.01)

G06F 9/52 (2006.01)

F 1

G06F 9/46 430

G06F 9/46 472B

請求項の数 17 (全 11 頁)

(21) 出願番号 特願2010-510519 (P2010-510519)

(86) (22) 出願日 平成20年5月30日 (2008.5.30)

(65) 公表番号 特表2010-529540 (P2010-529540A)

(43) 公表日 平成22年8月26日 (2010.8.26)

(86) 国際出願番号 PCT/US2008/065312

(87) 国際公開番号 WO2008/151013

(87) 国際公開日 平成20年12月11日 (2008.12.11)

審査請求日 平成23年5月18日 (2011.5.18)

(31) 優先権主張番号 11/809,514

(32) 優先日 平成19年6月1日 (2007.6.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 500046438

マイクロソフト コーポレーション

アメリカ合衆国 ワシントン州 9805

2-6399 レッドmond ワン マイ

クロソフト ウェイ

(74) 復代理人 100115624

弁理士 濱中 淳宏

(74) 復代理人 100156971

弁理士 稲 綾子

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

最終頁に続く

(54) 【発明の名称】トランザクション・メモリ・システムにおけるトランザクション・コード・ブロックを効果的に検索する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ソフトウェア・トランザクショナル・メモリを実装するソフトウェア・トランザクショナル・メモリ・アプリケーションを有するコンピューターに、

前記ソフトウェア・トランザクショナル・メモリ・アプリケーションの関数のうち、トランザクションセーフとしてマークされた各関数について、非トランザクションから呼び出される第1のバージョンのコードと、トランザクションから呼び出される第2のバージョンのコードを作成するステップと、

前記ソフトウェア・トランザクショナル・メモリ・アプリケーションの関数のうち、トランザクションセーフとしてマークされていない各関数について、非トランザクションから呼び出される第1のバージョンのコードを作成するステップと、

前記トランザクションセーフとしてマークされた各関数の前記第1のバージョンのコードのスタブポインターに前記第2のバージョンのコードのエントリポイントを書き込み、前記第2のバージョンのコードのスタブポインターにエラールーチンのエントリポイントを書込むステップと

を含む処理を実行させるためのプログラムを記録したコンピューター読取り可能な記録媒体。

## 【請求項 2】

前記第1のバージョンのコードの前記スタブポインターは、前記第1のバージョンのコードの本文の前に格納されることを特徴とする請求項1に記載のコンピューター読取り可

能な記録媒体。

【請求項 3】

前記トランザクションセーフとしてマークされていない各関数の前記第1のバージョンのコードの前記スタブポインターは、エラールーチンを示すことを特徴とする請求項1に記載のコンピューター読取り可能な記録媒体。

【請求項 4】

前記トランザクションセーフとしてマークされていない各関数の前記第1のバージョンのコードは、エラールーチンを示すスタブポインターを有することを特徴とする請求項1に記載のコンピューター読取り可能な記録媒体。

【請求項 5】

コンピューターが、ソフトウェア・トランザクショナル・メモリにおけるトランザクショナル・コード・ブロックを検索する方法であって、前記コンピューターは、前記ソフトウェア・トランザクショナル・メモリを実装するソフトウェア・トランザクショナル・メモリ・アプリケーションを有し、前記方法は、

前記ソフトウェア・トランザクショナル・メモリ・アプリケーションの特定の関数がトランザクションセーフとしてマークされていると判断するステップと、

前記特定の関数について、非トランザクションにおいて使用される第1のバージョンの関数コードと、トランザクションにおいて使用される第2のバージョンの関数コードとを含む2つのバージョンの関数を作成するステップと、

前記第2のバージョンの関数コードを示すスタブポインターを前記第1のバージョンの関数コードに格納し、エラールーチンのエントリポイン트を示すスタブポインターを前記第2のバージョンの関数コードに格納するステップと

を備えることを特徴とする方法。

【請求項 6】

実行コンテキストに応じたバージョンの前記特定の関数を呼び出すステップをさらに備えたことを特徴とする請求項5に記載の方法。

【請求項 7】

前記実行コンテキストが、前記特定の関数への直接呼び出しを用いる非トランザクショナルコンテキストであるとき、前記実行コンテキストに応じたバージョンの前記特定の関数を呼び出すステップは、前記第1のバージョンの関数コードを呼び出すことを含むことを特徴とする請求項6に記載の方法。

【請求項 8】

前記実行コンテキストが、前記特定の関数への直接呼び出しを用いるトランザクショナルコンテキストであるとき、前記実行コンテキストに応じたバージョンの前記特定の関数を呼び出すステップは、前記第2のバージョンの関数コードを呼び出すことを含むことを特徴とする請求項6に記載の方法。

【請求項 9】

前記実行コンテキストが、前記特定の関数へのポインター呼び出しを用いる非トランザクショナルコンテキストであるとき、前記実行コンテキストに応じたバージョンの前記特定の関数を呼び出すステップは、前記ポインター呼び出しにより、前記第1のバージョンの関数コードを呼び出すことを含むことを特徴とする請求項6に記載の方法。

【請求項 10】

前記実行コンテキストが、前記特定の関数への仮想呼び出しを用いる非トランザクショナルコンテキストであるとき、前記実行コンテキストに応じたバージョンの前記特定の関数を呼び出すステップは、前記仮想呼び出しにより前記第1のバージョンの関数コードを呼び出すことを含むことを特徴とする請求項6に記載の方法。

【請求項 11】

前記特定の関数がトランザクションセーフとしてマークされていると判断することは、前記特定の関数のソースコードの属性に基づいて行われることを特徴とする請求項5に記載の方法。

10

20

30

40

50

## 【請求項 1 2】

前記特定の関数の前記 2 つのバージョンはコンパイラによって作成されることを特徴とする請求項 5 に記載の方法。

## 【請求項 1 3】

前記第 2 のバージョンの関数コードを示すスタブポインターは、前記第 1 のバージョンの関数コードのエントリポイントに格納されることを特徴とする請求項 5 に記載の方法。

## 【請求項 1 4】

コンピューターに請求項 5 に記載の方法を実行させるためのプログラムを記録したコンピューター読み取り可能な記録媒体。

## 【請求項 1 5】

ソフトウェア・トランザクショナル・メモリにおいて使用する関数について、トランザクションから呼び出される第 2 のバージョンのコードおよび非トランザクションから呼び出される第 1 のバージョンのコードを作成する方法であって、前記ソフトウェア・トランザクショナル・メモリを実装するソフトウェア・トランザクショナル・メモリ・アプリケーションを有するコンピューターが、

コンパイル時に、前記ソフトウェア・トランザクショナル・メモリ・アプリケーションの複数の関数にスタブポインターを割当てるステップと、

前記複数の関数のうちトランザクションセーフとしてマークされていない個々の関数毎に、トランザクションセーフとしてマークされていない個々の関数の第 1 のバージョンのコードを生成し、該第 1 のバージョンのコードの前記スタブポインターにランタイム・エラー・ルーチンのエントリポイントを書込むステップと、

前記複数の関数のうちトランザクションセーフとしてマークされた個々の関数毎に、トランザクションセーフとしてマークされた個々の関数の第 1 のバージョンのコードおよび第 2 のバージョンのコードを作成するステップと、

前記第 1 のバージョンのコードの前記スタブポインターに、前記第 2 のバージョンのコードのエントリポイントを書込むステップと、

前記第 2 のバージョンのコードの前記スタブポインターに、ランタイム・エラー・ルーチンのエントリポイントを書込むステップと

を含むことを特徴とする方法。

## 【請求項 1 6】

前記ソフトウェア・トランザクショナル・メモリ・アプリケーションにおける各関数の各呼び出しサイトに対して、実行コンテキストに応じた関数の呼び出しを行うステップをさらに備えたことを特徴とする請求項 1 5 に記載の方法。

## 【請求項 1 7】

コンピューターに、請求項 1 5 に記載の方法を実行させるためのプログラムを記録したコンピューター読み取り可能な記録媒体。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、トランザクション・メモリ・システムに関し、より詳細には、トランザクション・メモリ・システムにおけるトランザクション・コード・ブロック (transactional code block) を効果的に検索する方法に関する。

## 【背景技術】

## 【0 0 0 2】

ソフトウェア・トランザクション・メモリ (STM) は、並列計算における共有メモリへのアクセスを制御するためのデータベーストランザクションに似ている同時実行制御機構である。トランザクションメモリという状況におけるトランザクションは、共有メモリに対して一連の読み取りかつ書き込みを実行する 1 つのコードである。STM を、従来のロック機構に対する代替手段として用いる。プログラマは、コードブロックの前後に宣言の注釈 ( 例えは、アトミック ) を記入して、コードブロックが他の保護されたコード領域に関

10

20

30

40

50

してアトミックに実行されることを、プログラマが必要としあるシステムが自動的に保証する安全のプロパティを示す。ソフトウェア・トランザクション・メモリ・プログラミング・モデル (software transactional memory programming model) は、ロックベースの優先度逆転問題およびデッドロック問題を防ぐ。

#### 【0003】

ソフトウェア・トランザクション・メモリ (STM) システムは、あるシーケンシャルプログラムを取得し、シーケンシャルプログラムの部分に対して、トランザクションを使用して同時に（例えば、並列に）実行することを許可することができる。通常、プログラマは、種々の種類のプログラミング言語のうちの 1 つを使用して、シーケンシャルプログラムのソースコードを書く。通常、ソースコードは、後にコンピューターにより実行されるロジックを含む 1 つまたは複数の関数の中に埋め込まれる。用語「関数」を、関数、メソッド、プロシージャ、ステートメントブロック、および / またはコンピューターにより実行されるロジックの他の部分を含むこととして、本明細書において広く使用する。ソフトウェア・トランザクション・メモリ・システムによって、トランザクションコンテキストから呼び出しをすることができるすべての関数は、2 つのバージョンを有するべきである。1 つのバージョンは、トランザクションから呼び出しをすることができ、およびもう 1 つのバージョンは、トランザクションなしで呼び出しをすることができる。呼び出しをする関数についてどのバージョンを決定するかは、コンテキスト依存である。バージョンの決定は、実行時間において、仮想関数に対してまたは関数ポインターによって、呼び出しをするために行われるべきである。

10

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0004】

トランザクション・メモリ・システムにおけるトランザクション・コード・ブロックの作成および / または検索のために、種々の技術および技法を開示する。例えばソフトウェア開発者等のユーザーは、識別子によって個別の関数をデコレートして、個別の関数がトランザクションセーフであることを示すことができる。ノーマルバージョンおよびトランザクションバージョンを、トランザクションセーフとしてマークされたソフトウェアアプリケーションの各関数に対して作成する。ノーマルバージョンを、トランザクションセーフとしてマークされていない各関数に対して作成する。トランザクションセーフとしてマークされた各関数のノーマルバージョンに対して、ノーマルバージョンの中のスタブポインター (stub pointer) より、トランザクションバージョンを示す。関数に適切なバージョンを、アプリケーションコンテキストに依存して、呼び出しをする。

30

#### 【課題を解決するための手段】

#### 【0005】

一実施例において、コンパイラは、トランザクション・メモリ・システムが使用するための関数についてのトランザクションバージョンおよびトランザクションなしのバージョンを生成する。コンパイルするときに、スタブポインターは、ソフトウェアアプリケーションの中の各関数に割当てられる。トランザクションセーフの関数としてマークされていない、それぞれの関数に対して、それぞれの関数についてのノーマルバージョンを生成し、およびランタイム・エラー・ルーチンのエントリポイントによってスタブポインターに書込む。トランザクションセーフの関数としてマークされた、それぞれの関数に対して、コードを、トランザクションセーフであるそれぞれの関数についてのノーマルバージョンおよびトランザクションバージョンとして作成する。ノーマルバージョンのスタブポインターにおいて、エントリポイントを、トランザクションバージョンに対して書込む。トランザクションバージョンのスタブポインターにおいて、エントリポイントを、ランタイム・エラー・ルーチンに対して書込む。

40

#### 【0006】

本発明の概念を提供して、発明を実施するための形態において、さらに、以下に記述される概念についての選択を、簡略化された形式において紹介した。本発明の概要は、主張

50

される主題についての重要な特徴または基本的な特徴を識別することを意図せず、主張される主題の範囲の決定における補助として用いられることを意図しない。

【図面の簡単な説明】

【0007】

【図1】本発明の一実施例に係るコンピューターシステムを表す図である。

【図2】本発明の一実施例に係る図1のコンピューターシステムの演算についてのトランザクション・メモリ・アプリケーションを表す図である。

【図3】本発明の一実施例に係る図1のコンピューターシステムの高水準処理のフローチャートである。

【図4】本発明の一実施例に係る図1のコンピューターシステムについての、トランザクション関数とトランザクションなしの関数とのコードを生成し、およびコンパイル処理とリンク処理との少なくとも一方の一部としてスタブポインターに書込むコードジェネレーターの使用にかかるステージを例示する処理のフローチャートである。 10

【図5】本発明の一実施例に係る図1のコンピューターシステムについての、関数に適切なバージョンを選択し、実行コンテキストに依存して呼び出しをするデシジョンツリーを例示する図である。

【図6】本発明の一実施例に係る、1つの関数がちょうどノーマルバージョンを有し、もう一方の関数がノーマルバージョンとトランザクションバージョンとを有する2つの仮想的な関数を例示する図である。

【発明を実施するための形態】

【0008】

本発明の原理の理解を促進する目的のため、図面において例示する実施形態を参照し、および特定の言語を使用して同一のことを説明する。それにもかかわらず範囲の限定を意図しないことが理解されるだろう。説明される実施形態におけるあらゆる交替、さらなる変更、本明細書において説明する原理のあらゆるさらなる応用は、当事業者が普通は気づくであろうと同程度に予想される。

【0009】

システムを、トランザクション・メモリ・システムとして一般的な文脈において説明するが、システムは、追加として他の目的に役立つ。一実施例において、本明細書にて説明する1つまたは複数の技法を、例えば本願発明の特許出願人のフレームワーク製品等のフレームワークプログラム内の機能として、または開発者にプラットホームを提供してソフトウェアアプリケーションを開発するプログラムもしくはサービスの他のあらゆる種類からの機能として、実装することができる。別の実施例において、本明細書にて説明する1つまたは複数の技法を、並列環境にて実行されるアプリケーションの開発を取り扱う他のアプリケーションによる機能として、実装することができる。 30

【0010】

一実施例において、トランザクションセーフとしてマークされた各関数の2つのバージョンを、詳細には関数のノーマルバージョンおよび関数のトランザクションバージョンをプログラム的に作成するトランザクション・メモリ・システムを提供する。トランザクションセーフとしてマークされていない関数に対して、ノーマルバージョンのみを作成し、およびノーマルバージョンのエントリポイントにおけるスタブポインターを、エラールーチンに向ける。トランザクションセーフとしてマークされた関数に対して、ノーマルバージョンのエントリポイントのスタブポインターを、関数のトランザクションバージョンに向ける。トランザクションバージョンのエントリポイントにおけるスタブポインターを、エラールーチンに向ける。トランザクションセーフとしてマークされていない関数に対して、ノーマルバージョンのエントリポイントにおけるスタブポインターは、エラールーチンを示す。関数に適切なバージョンを、実行コンテキストに依存して、呼び出しをする。 40

【0011】

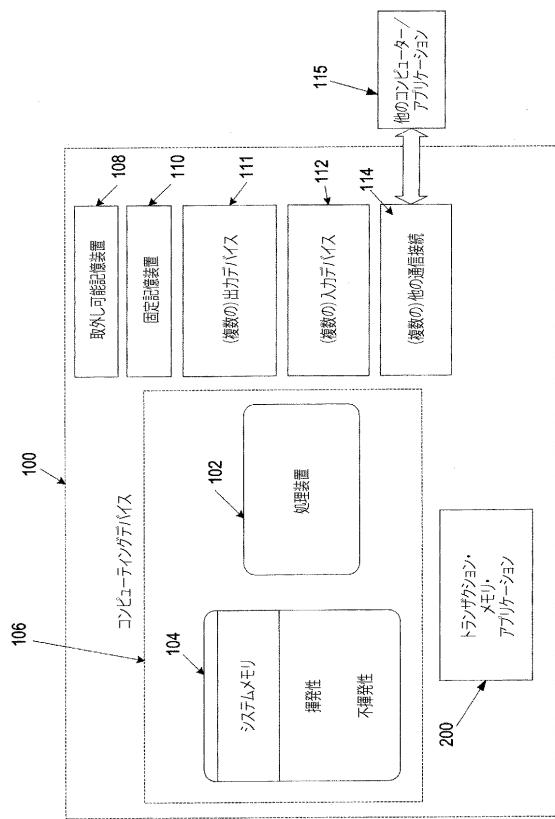

図1を参照すると、1つまたは複数のシステムのパートを実装するために使用する例示的コンピューターシステムは、例えばコンピューティングデバイス100等のコンピュー 50

ティングデバイスを含む。通常、最も基本的な構成において、コンピューティングデバイス 100 は、少なくとも 1 つの処理装置 102 およびメモリ 104 を含む。コンピューティングデバイスの正確な構成および種類に依存して、メモリ 104 は、揮発性メモリ（例えば、RAM 等）、不揮発性メモリ（例えば、ROM、フラッシュメモリ等）または 2 つの何れかの組合せとすることができます。図 1 において、最も基本的な構成を、破線 106 によって例示する。

#### 【0012】

加えて、デバイス 100 は、追加の機能 / 機能性を有することができる。例えば、デバイス 100 は、限定されないが、磁気もしくは光ディスクまたは磁気もしくは光テープを含んでいる、追加の（取外し可能および / または固定の）記憶装置を含むことができる。図 1 において、追加の記憶装置を、取外し可能記憶装置 108 および固定記憶装置 110 によって例示する。コンピューター記憶メディアは、例えばコンピューター読み取り可能な命令、データ構造、プログラムモジュール、または他のデータ等の情報を格納するあらゆる方法または技術に実装される揮発性および不揮発性の、取外し可能および固定のメディアを含む。メモリ 104、取外し可能記憶装置 108、および固定記憶装置 110 は、すべてコンピューター記憶メディアの例である。コンピューター記憶メディアは、限定されないが、RAM、ROM、EEPROM、フラッシュメモリもしくは他のメモリ技術、CD-ROM、デジタル多用途ディスク（DVD）もしくは他の光記憶装置、磁気カセット、磁気テープ、磁気ディスク記憶装置もしくは他の磁気記憶装置、または望ましい情報の格納に使用することができる他のあらゆるメディアおよびデバイス 100 によってアクセスすることができる他のあらゆるメディアを含む。

#### 【0013】

コンピューティングデバイス 100 は、コンピューティングデバイス 100 に他のコンピューター / アプリケーション 115 との通信を可能にする、1 つまたは複数の通信接続 114 を含む。デバイス 100 は、例えば、キーボード、マウス、ペン、音声入力デバイス、タッチ入力デバイス等、（複数の）入力デバイス 112 を有することができる。（複数の）出力デバイス 111 を、例えば、ディスプレイ、スピーカー、プリンター等を含むことができる。上記デバイスは、本技術分野においてよく知られており、本明細書において詳細に論ずる必要がない。一実施例において、コンピューティングデバイス 100 は、トランザクション・メモリ・アプリケーション（transactional memory application）200 を含む。図 2 において、トランザクション・メモリ・アプリケーション 200 を、さらに詳細に説明することにする。

#### 【0014】

図 2 を参照して、図 1 の参照を続けつつ、コンピューティングデバイス 100 上において動作するトランザクション・メモリ・アプリケーション 200 を、説明する。トランザクション・メモリ・アプリケーション 200 は、コンピューティングデバイス 100 に属するアプリケーションプログラムの 1 つである。しかしながら、代替としてまたは追加として、トランザクション・メモリ・アプリケーション 200 を、1 つまたは複数のコンピューター上に、および / または図 1 に示す種々のバリエーションにおいて、コンピューター実行可能な命令として含むことができる。代替としてまたは追加として、トランザクション・メモリ・アプリケーション 200 の 1 つまたは複数のパーツを、他のコンピューター / アプリケーション 115 上の、またはコンピューターソフトウェア技術者が気づくような他のバリエーション上のシステムメモリ 104 のパーツであるとすることができる。

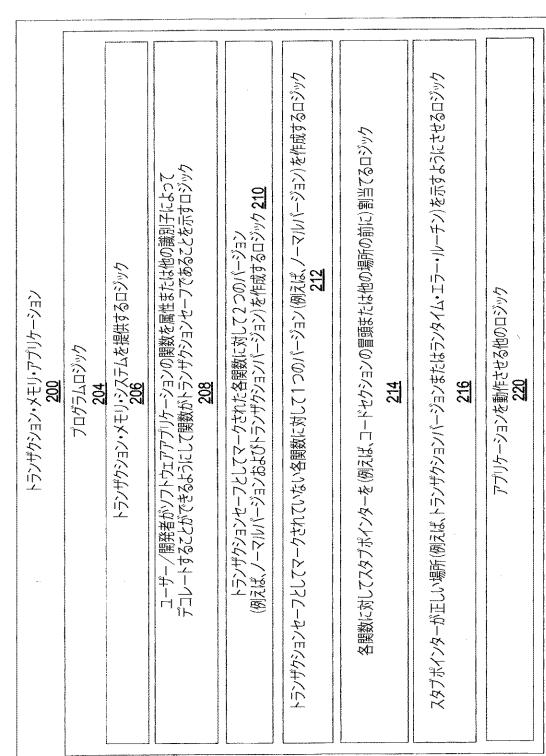

#### 【0015】

トランザクション・メモリ・アプリケーション 200 は、プログラムロジック 204 を含む。プログラムロジック 204 は、本明細書において説明される技法のいつかまたはすべての実行を担当する。プログラムロジック 204 は、トランザクション・メモリ・システムを提供するロジック 206、ユーザー / 開発者がソフトウェアアプリケーションの関数を属性または他の識別子によってデコレートすることができるようにして、関数がトランザクションセーフであることを示すロジック 208、トランザクションセーフとしてマ

10

20

30

40

50

ークされた各関数に対して2つのバージョン（例えば、ノーマルバージョンおよびトランザクションバージョン）を作成するロジック210、トランザクションセーフとしてマークされていない各関数に対して1つのバージョン（例えば、ノーマルバージョン）を作成するロジック212、各関数に対してスタブポインターを（例えば、コードセクションの冒頭または他の場所の前に）割当てるロジック214、スタブポインターが正しい場所（例えば、トランザクションバージョンまたはランタイム・エラー・ルーチン）を示すようにさせるロジック216、およびアプリケーションを動作させる他のロジック220を含む。一実施例において、プログラムロジック204を、例えば、プログラムロジック204においてプロシージャに対して単一の呼び出しを使用すること等、別のプログラムからプログラム的に呼び出しをするのに使用可能である。

10

#### 【0016】

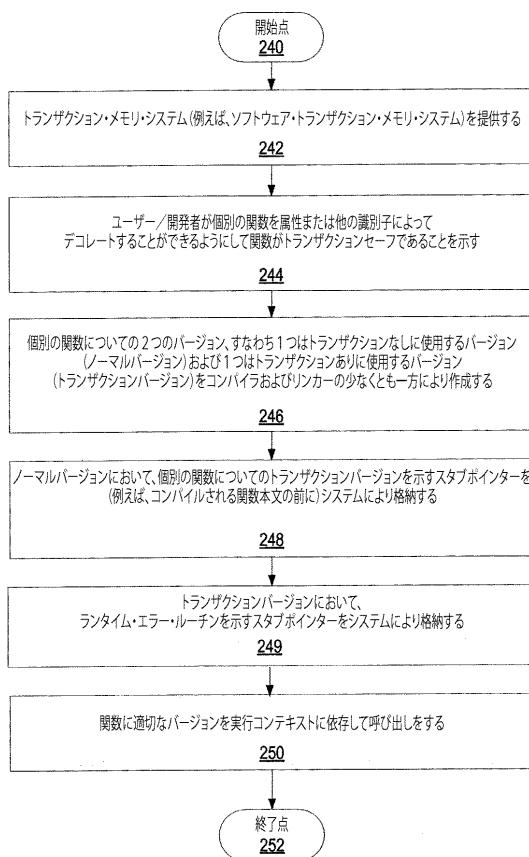

図3～6を参照して、図1～2の参照を続けつつ、トランザクション・メモリ・アプリケーション200の1つまたは複数の実施例を実施するステージを、より詳細に説明する。図3は、トランザクション・メモリ・アプリケーション200の高水準処理のフローチャートである。1つのフォームにおいて、図3の処理を、コンピューティングデバイス100の動作ロジックに少なくとも部分的に実装する。処理は、開始点240において始まり、トランザクション・メモリ・システム（例えば、ソフトウェア・トランザクション・メモリ・システム）を提供する（ステージ242）。システムは、ユーザー／開発者が個別の関数を属性または他の識別子によってデコレートすることができるようにして、関数がトランザクションセーフであることを示す（ステージ244）。コンパイラおよびリンクの少なくとも一方は、個別の関数についての2つのバージョンを作成する。1つは、トランザクションなしに使用するバージョンであり（例えば、ノーマルバージョン）、および1つは、トランザクションありに使用するバージョンである（例えば、トランザクションバージョン）（ステージ246）。ノーマルバージョンにおいて、システムは、個別の関数についてのトランザクションバージョンを示すスタブポインターを格納する（ステージ248）。一実施例において、本明細書において説明される（複数の）スタブポインターは、それぞれコンパイルされる関数本文の前に格納される。他の実施例において、スタブポインターがそれぞれの関数のバージョンに関連付けられていれば、スタブポインターを、他の位置に格納することができる。トランザクションバージョンにおいて、システムは、ランタイム・エラー・ルーチンを示すスタブポインターを格納する（ステージ249）。関数に適切なバージョンを、実行コンテキストに依存して、呼び出しをする（ステージ250）。処理は、終了点252において終了する。

20

#### 【0017】

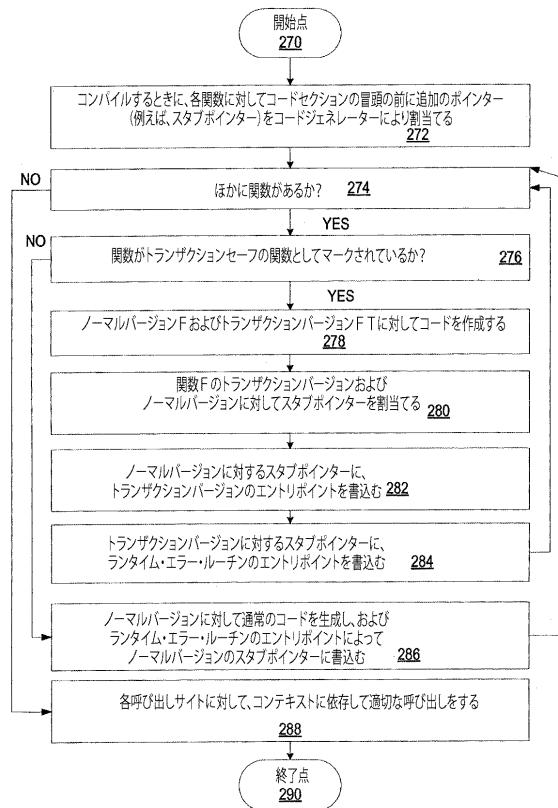

図4は、トランザクション関数とトランザクションなしの関数とのコードを生成し、およびコンパイル処理とリンク処理との少なくとも一方の一部としてスタブポインターに書込むコードジェネレーターの使用にかかるステージの一実施例を例示する。1つのフォームにおいて、図4の処理を、コンピューティングデバイス100の動作ロジックに少なくとも部分的に実装する。処理は、開始点270において始まり、コードジェネレーターが、コンパイルするときに、各関数に対して追加のポインター（例えば、スタブポインター）を割当てる（ステージ272）。各関数に対して（すなわち、関数がある間）（判断ポイント274）、種々のタスクを実行する。例えば、関数がトランザクションセーフの関数としてマークされていないと（判断ポイント276）、システムは、関数に対してノーマルバージョン（すなわち、通常のコード）を生成し、およびランタイム・エラー・ルーチンのエントリポイントによってノーマルバージョンのスタブポインターに書込む（ステージ286）。

30

#### 【0018】

関数がトランザクションセーフの関数としてマークされると（判断ポイント276）、システムは、ノーマルバージョンFおよびトランザクションバージョンFTに対して、コードを作成する（ステージ278）。システムは、関数Fのトランザクションバージョンおよびノーマルバージョンに対してスタブポインターを割当てる（ステージ280）。ノ

40

50

ーマルバージョンに対するスタブポインターに、トランザクションバージョンのエントリポイントを書込む（ステージ 282）。トランザクションバージョンに対するスタブポインターに、ランタイム・エラー・ルーチンのエントリポイントを書込む（ステージ 284）。上記ステージを、各関数に対して適切に繰返す。各呼び出しサイトに対して、システムは、コンテキストに依存して、適切な呼び出しをする（ステージ 288）。図 5において、呼び出しサイトの判断処理を、さらに詳細に説明する。処理は、終了点 290において終了する。

#### 【0019】

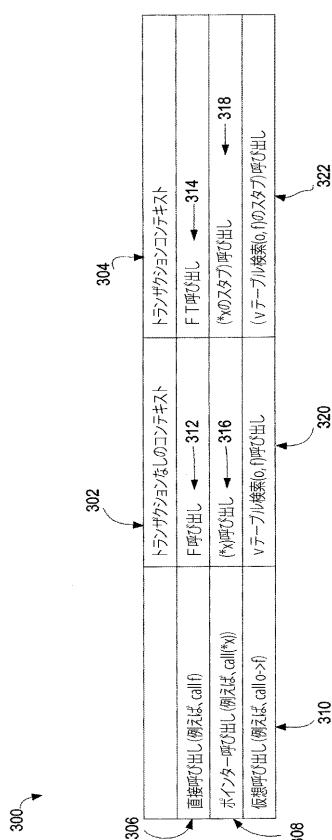

図 5 を参照すると、図 1 のシステムの一実施例に係る図 300 は、関数に適切なバージョンを選択し、実行コンテキストに依存して呼び出しをするのに適しているデシジョンツリーを例示する。1つのフォームにおいて、図 5 の判断処理を、コンピューティングデバイス 100 の動作ロジックに少なくとも部分的に実装する。トランザクションなしのコンテキスト 302 における直接呼び出し 306 に対して、ノーマルバージョンのエントリポイントを、関数 312 に対し直接的に呼び出しをする。トランザクションコンテキスト 304 における直接呼び出し 306 に対して、トランザクションバージョンのエントリポイントを、関数 314 に対し呼び出しをする。トランザクションなしのコンテキスト 302 におけるポインター呼び出し 308 に対して、呼び出しは、関数 316 に対し同様である。トランザクションコンテキスト 304 におけるポインター呼び出し 308 に対して、スタブ関数を示すワードのアドレスを、関数ポインターの値の逆参照から計算し、およびアドレスを、呼び出し 318 において使用する。スタブ関数は、トランザクションバージョンのエントリポイントへのポインターによって格納されるので、正確なバージョンが実行される。トランザクションなしのコンテキスト 302 における仮想呼び出しありはインターフェース呼び出し 310 は、影響を受けず、および呼び出し 320 も同様に影響を受けない。トランザクションコンテキスト 304 における仮想呼び出しありはインターフェース呼び出し 310 は、v テーブル検索を実行し、および関数 322 のトランザクションバージョンについてのスタブ関数のエントリポイントを計算する。計算されたエントリポイントを、呼び出しをするのに使用する。

#### 【0020】

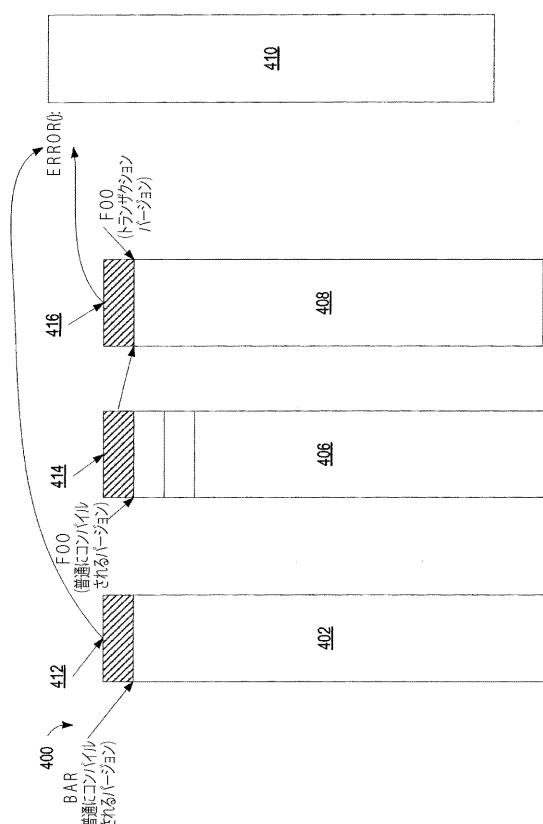

図 6 は、1つの関数がちょうどノーマルバージョンを有し、およびもう一方の関数がノーマルバージョンとトランザクションバージョンとを有する2つの仮想的な関数を例示する一実施例の論理的な図 400 である。「BAR」関数 402 は、ソースコードにおいてトランザクションセーフとしてマークされていなかった関数である。上述のように、関数 402 に対するエントリポインター 412 は、エラールーチン 410 を示す。「FOO」関数 414 は、元のソースコードにおいてトランザクションセーフとしてマークされていた関数であり、結果として、普通にコンパイルされるバージョン（ノーマルバージョン）を、トランザクションバージョン 408 とともに、関数 406 に提供する。FOO 関数 406 のノーマルバージョンについてのエントリポイント 414 は、FOO 関数 408 のトランザクションバージョンを示す。FOO 関数 408 のトランザクションバージョンについてのエントリポイント 416 は、エラールーチン 410 を示す。一実施例において、上記エラールーチンを上記関数のスタブ（エントリポイント）に埋め込み、エラーを、不適切な使用に直面するときのランタイム時に見つけることを可能にする。

#### 【0021】

主題を、構造的な機能および / または方法論的な動作に固有の言語において説明してきたが、添付のクレームにおいて明確にされる主題は、上記の特定の機能または動作を必ずしも限定されないことが理解される。適切に言えば、上記の特定の機能および動作を、クレームを実施する形式の例として開示する。本明細書において説明される実施例の精神のおよび / または次に述べるクレームによる範囲内にある、すべての等価、修正、および変更は、保護されることを望む。

#### 【0022】

例えば、コンピューターソフトウェア分野の当事業者は、本明細書において論じた実施

10

20

30

40

50

例にて説明されたのと同程度に、クライアント配置および／またはサーバ配置を、ユーザーインターフェースの画面コンテンツおよび／またはデータ配置を、1つまたは複数のコンピューターに異なった構成をして、実施例において表されたのよりも、より少ないオプションもしくは追加のオプションまたはより少ない機能もしくは追加の機能を含むことができるだろう。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 デイヴィッド キャラハン

アメリカ合衆国 98052 ワシントン州 レッドモンド ワン マイクロソフト ウェイ マ

イクロソフト コーポレーション インターナショナル パテンツ内

(72)発明者 ピノッド ケー.グローバー

アメリカ合衆国 98052 ワシントン州 レッドモンド ワン マイクロソフト ウェイ マ

イクロソフト コーポレーション インターナショナル パテンツ内

審査官 田中 幸雄

(56)参考文献 米国特許出願公開第2008/0120590(US, A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 46

G 06 F 9 / 52