(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2019년02월25일

(11) 등록번호 10-1951663

(24) 등록일자 2019년02월19일

- (51) 국제특허분류(Int. Cl.)

*H03M 13/09* (2015.01)

(21) 출원번호 10-2012-0146359

(22) 출원일자 2012년12월14일

심사청구일자 2017년12월01일

(65) 공개번호 10-2014-0077492

(43) 공개일자 2014년06월24일

(56) 선행기술조사문헌

CRC-aided decoding of polar code (IEEE communications letters, 2012년 10월)

- (73) 특허권자

**삼성전자주식회사**

경기도 수원시 영통구 삼성로 129 (매탄동)

**성균관대학교산학협력단**

경기도 수원시 장안구 서부로 2066 (천천동, 성균

관대학교내)

(72) 발명자

**정홍실**

서울 영등포구 여의대방로43나길 25, 102동 2003

호 (신길동, 삼환아파트)

**김상효**

서울 강남구 압구정로 313, 61동 203호 (

압구정동, 한양아파트)

(뒷면에 계속)

(74) 대리인

**윤동열**

전체 청구항 수 : 총 14 항

심사관 : 조춘근

(54) 발명의 명칭 **CRC 부호와 극 부호에 의한 부호화 방법 및 장치****(57) 요약**

CRC 부호와 극 부호에 의한 부호화 방법 및 장치가 개시된다. CRC 부호화는 입력 정보비트 중 미리 설정된 CRC 부호화 비트수에 해당하는 정보비트에 대해 수행되고, CRC 부호화된 정보비트 및 CRC 부호화된 정보비트를 제외한 나머지 정보비트를 극 부호화한다.

**대 표 도** - 도6

$$\mathbf{M} = (m_0, m_1, \dots, m_{k-1}) \quad \mathbf{M}_\alpha = (m_0, \dots, m_{k-1}, c_0, \dots, c_{\alpha-1}) \quad \mathbf{X} = (X_0, X_1, \dots, X_{N-1})$$

(72) 발명자

김종환

경기 수원시 장안구 화산로187번길 20-9, 206호 (울전동, 드림빌)

류대현

경기 성남시 분당구 돌마로486번길 7, 202동 702호 (서현동, 효자촌동아아파트)

---

명세호

서울 강남구 선릉로69길 20, 108동 502호 (역삼동, 역삼e-편한세상)

## 명세서

### 청구범위

#### 청구항 1

입력 정보비트 중 미리 설정된 CRC 부호화 비트수에 해당하는 정보비트를 CRC 부호화하는 단계; 및 상기 CRC 부호화된 정보비트 및 상기 CRC 부호화된 정보비트를 제외한 나머지 정보비트를 각 부호화하는 단계; 를 포함하는 것을 특징으로 하는 부호화 방법.

#### 청구항 2

제 1항에 있어서,

미리 설정된 각 부호화의 정보집합 및 상기 미리 설정된 각 부호화의 해밍 웨이트(Hamming weight)의 기준 값을 기초로 상기 CRC 부호화 비트수를 결정하는 단계를 더 포함하는 것을 특징으로 하는 부호화 방법.

#### 청구항 3

제 2항에 있어서,

상기 CRC 부호화 비트수는 상기 정보집합을 기초로 생성된 각 부호 부분 생성행렬 중 해밍 웨이트의 값이 상기 해밍 웨이트 기준값 이하인 행의 개수에서 상기 CRC 부호화를 위해 미리 설정된 부호 길이를 뺀 값을 결정되는 것을 특징으로 하는 부호화 방법.

#### 청구항 4

제 2항에 있어서,

상기 CRC 부호화 비트수를 결정하는 단계는,

상기 정보집합의 원소들로부터 각각 이진 확장 벡터를 생성하는 단계;

상기 정보집합에서 상기 이진 확장 벡터에 포함된 1의 개수가 상기 해밍 웨이트 기준값의 이진로그 이하인 원소의 개수를 계산하는 단계; 및

상기 계산된 원소의 개수에서 상기 CRC 부호화를 위해 미리 설정된 부호 길이를 뺀 값을 상기 CRC 부호화 비트수로 결정하는 단계; 를 포함하는 것을 특징으로 하는 부호화 방법.

#### 청구항 5

제 1항에 있어서,

상기 CRC 부호화하는 단계에서 상기 입력 정보비트의 첫 번째 정보비트로부터 상기 CRC 부호화 비트수에 해당하는 정보비트를 순차적으로 선택하여 CRC 부호화하는 것을 특징으로 하는 부호화 방법.

#### 청구항 6

제 1항에 있어서,

상기 각 부호화하는 단계에서 상기 CRC 부호화된 정보비트를 각 부호화의 행 벡터 중 미리 설정된 부분집합의 원소에 대응하는 성분과 맵핑하는 것을 특징으로 하는 부호화 방법.

#### 청구항 7

제 6항에 있어서,

상기 부분집합은 미리 설정된 각 부호화의 정보집합의 원소들 중 각 원소로부터 생성된 이진 확장 벡터에 포함된 1의 개수가, 상기 미리 설정된 각 부호화의 해밍 웨이트의 기준값의 이진로그 이하인 원소로 구성된 것을 특징으로 하는 부호화 방법.

**청구항 8**

입력 정보비트 중 미리 설정된 CRC 부호화 비트수에 해당하는 정보비트를 CRC 부호화하는 CRC 부호화부; 및 상기 CRC 부호화된 정보비트 및 상기 CRC 부호화된 정보비트를 제외한 나머지 정보비트를 극 부호화하는 극 부호화부;를 포함하는 것을 특징으로 하는 부호화 장치.

**청구항 9**

제 8항에 있어서,

미리 설정된 극 부호화의 정보집합 및 상기 미리 설정된 극 부호화의 해밍 웨이트의 기준값을 기초로 상기 CRC 부호화 비트수를 결정하는 제어부를 더 포함하는 것을 특징으로 하는 부호화 장치.

**청구항 10**

제 9항에 있어서,

상기 CRC 부호화 비트수는 상기 정보집합을 기초로 생성된 극 부호 부분 생성행렬 중 해밍 웨이트의 값이 상기 해밍 웨이트 기준값 이하인 행의 개수에서 상기 CRC 부호화를 위해 미리 설정된 부호 길이를 뺀 값으로 결정되는 것을 특징으로 하는 부호화 장치.

**청구항 11**

제 9항에 있어서,

상기 제어부는 상기 정보집합의 원소들로부터 각각 이진 확장 벡터를 생성하고, 상기 정보집합에서 상기 이진 확장 벡터에 포함된 1의 개수가 상기 해밍 웨이트 기준값의 이진로그 이하인 원소의 개수를 계산하고, 상기 계산된 원소의 개수에서 상기 CRC 부호화를 위해 미리 설정된 부호 길이를 뺀 값을 상기 CRC 부호화 비트수로 결정하는 것을 특징으로 하는 부호화 장치.

**청구항 12**

제 8항에 있어서,

상기 CRC 부호화부는 상기 입력 정보비트의 첫 번째 정보비트로부터 상기 CRC 부호화 비트수에 해당하는 정보비트를 순차적으로 선택하여 CRC 부호화하는 것을 특징으로 하는 부호화 장치.

**청구항 13**

제 8항에 있어서,

상기 극 부호화부는 상기 CRC 부호화된 정보비트를 극 부호화의 행 벡터 중 미리 설정된 부분집합의 원소에 대응하는 성분과 맵핑하는 것을 특징으로 하는 부호화 장치.

**청구항 14**

제 13항에 있어서,

상기 부분집합은 미리 설정된 극 부호화의 정보집합의 원소들 중 각 원소로부터 생성된 이진 확장 벡터에 포함된 1의 개수가, 상기 미리 설정된 극 부호화의 해밍 웨이트의 기준값의 이진로그 이하인 원소로 구성된 것을 특징으로 하는 부호화 장치.

**발명의 설명****기술 분야**

[0001] 본 발명은 CRC-a 부호화기와 극 부호화기가 연접된 부호화기에 의해 입력 정보비트를 부호화하는 방법에 관한 것이다.

**배경 기술**

[0002] 무선 통신 시스템에서는 채널의 여러 가지 잡음(noise)과 페이딩(fading) 현상 및 심볼간 간섭(inter-symbol interference, ISI)에 의해 링크(link)의 성능이 현저히 저하된다. 따라서, 차세대 이동 통신, 디지털 방송 및 휴대 인터넷과 같이 높은 데이터 처리량과 신뢰도를 요구하는 고속 디지털 통신 시스템들을 구현하기 위해서 잡음과 페이딩 및 ISI에 대한 극복 기술을 개발하는 것이 필수적이다. 최근에는 정보의 왜곡을 효율적으로 복원하여 통신의 신뢰도를 높이기 위한 방법으로서 오류정정부호(error-correcting code)에 대한 연구가 활발히 이루어지고 있다.

[0003] 순환 중복 검사(Cyclic Redundancy Check, CRC) 부호는 송신하는 블록의 데이터에 부가되어 전송됨으로써 수신측에서의 오류 판정에 사용되며, 극 부호(polar code)는 2009년 Arikan에 의해 개발된 오류정정부호로서 이론적으로 이진 입력 무기억 대칭 채널(Binary-input memoryless symmetric channel)의 용량을 달성하는 것이 증명된 부호이다.

[0004] 극 부호는 기본적으로 CRC 부호를 연접하지 않고 독립적으로 동작하는 부호이나, 극 부호의 복호를 위해 연속 제거 리스트( Successive Cancellation List, SCL) 복호기를 사용하는 경우에는 극 부호를 독립적으로 사용하여 부호화하는 것보다 CRC 부호와 극 부호를 연접하여 사용하면 큰 오율(error rate) 성능 이득을 얻을 수 있다. 그리고 현재까지 진행된 연구에 의하면 CRC 부호와 극 부호를 연접하여 부호화한 후 SCL 복호기로 복호했을 때 극 부호의 최대 성능을 얻을 수 있으며, 터보 LDPC(Low Density Parity Check) 부호에 근접한 성능을 보이는 것으로 알려져 있다.

## 발명의 내용

### 해결하려는 과제

[0005] 본 발명이 이루고자 하는 기술적 과제는, CRC-a 부호화기와 극 부호화기가 연접된 부호화기에서 짧은 CRC 부호 길이로 인해 오류 마루 현상이 나타나는 경우에 CRC 부호화를 효과적으로 적용하여 오율 성능을 향상시키는 방법을 제공하는 데 있다.

### 과제의 해결 수단

[0006] 상술한 과제를 달성하기 위하여, 본 발명의 일 실시 예에 따르는 CRC 부호와 극 부호에 의한 부호화 방법은, 입력 정보비트 중 미리 설정된 CRC 부호화 비트수에 해당하는 정보비트를 CRC 부호화하는 단계와, 상기 CRC 부호화된 정보비트 및 상기 CRC 부호화된 정보비트를 제외한 나머지 정보비트를 극 부호화하는 단계를 포함한다.

[0007] 또한, 본 발명의 다른 실시 예에 따르는 CRC 부호와 극 부호에 의한 부호화 장치는, 입력 정보비트 중 미리 설정된 CRC 부호화 비트수에 해당하는 정보비트를 CRC 부호화하는 CRC 부호화부와, 상기 CRC 부호화된 정보비트 및 상기 CRC 부호화된 정보비트를 제외한 나머지 정보비트를 극 부호화하는 극 부호화부를 포함한다.

## 발명의 효과

[0008] 본 발명의 일 실시예에 따르면, 입력 정보비트의 일부만을 CRC 부호화함으로써 오류 마루가 발생하는 부호의 오율 성능을 개선할 수 있다.

### 도면의 간단한 설명

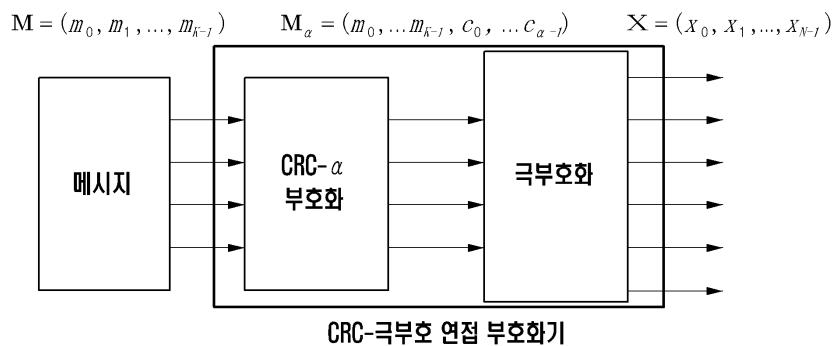

[0009] 도 1은 종래 CRC-극부호 연접 부호화기의 구조를 도시한 도면,

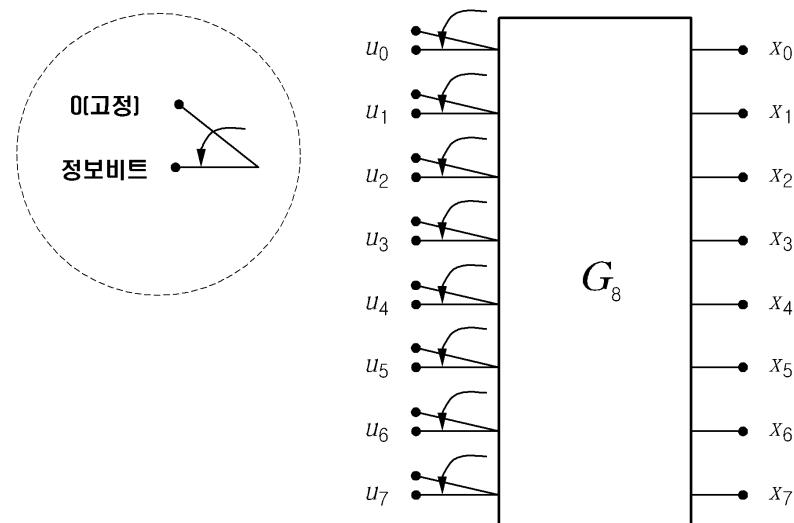

도 2는 극 부호화 과정을 도시한 도면,

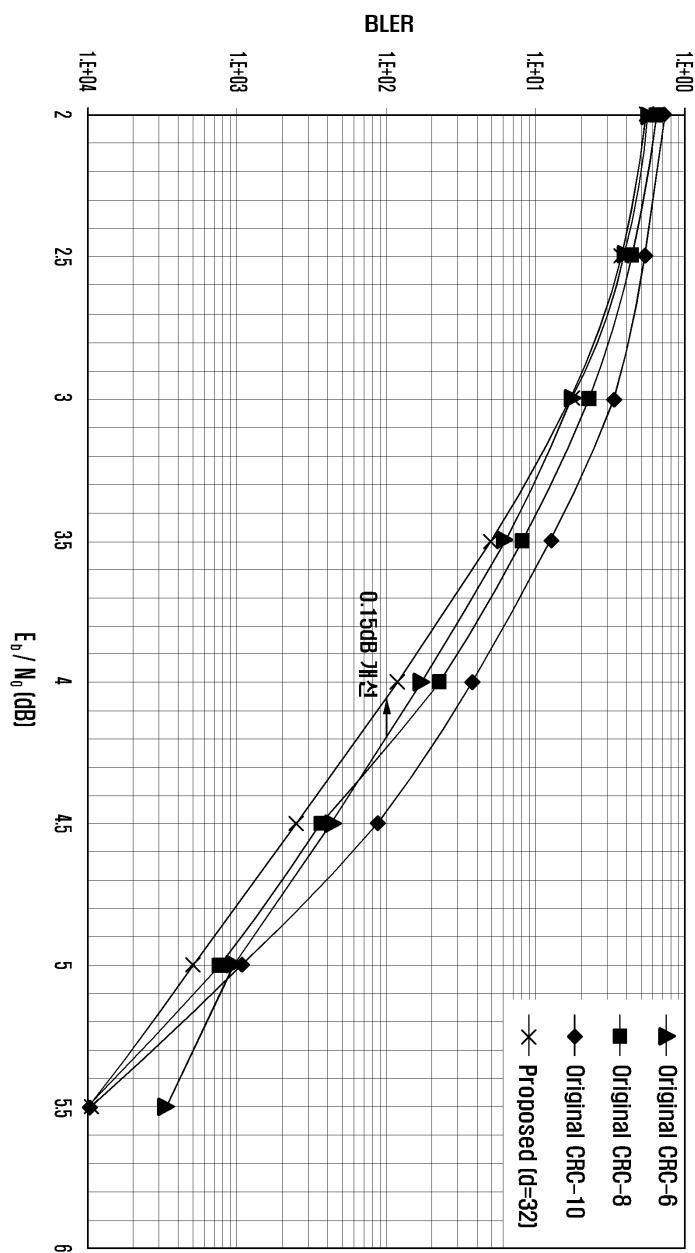

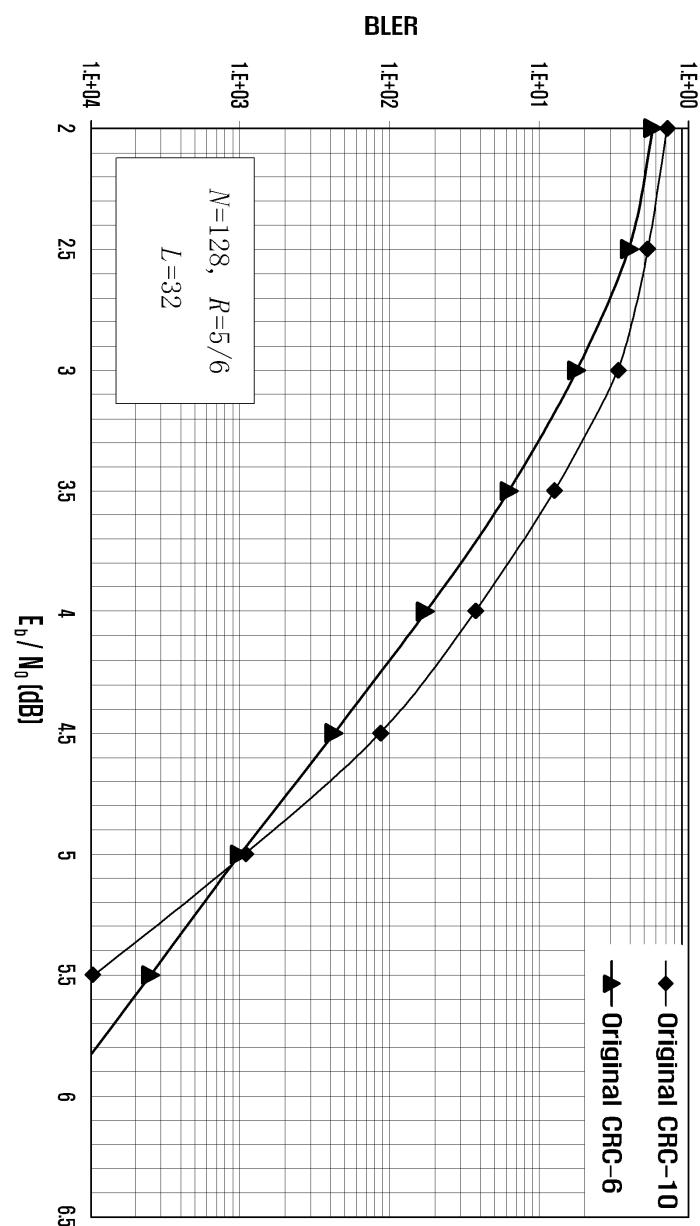

도 3은 종래 CRC-극부호 연접 시스템의 성능을 도시한 도면,

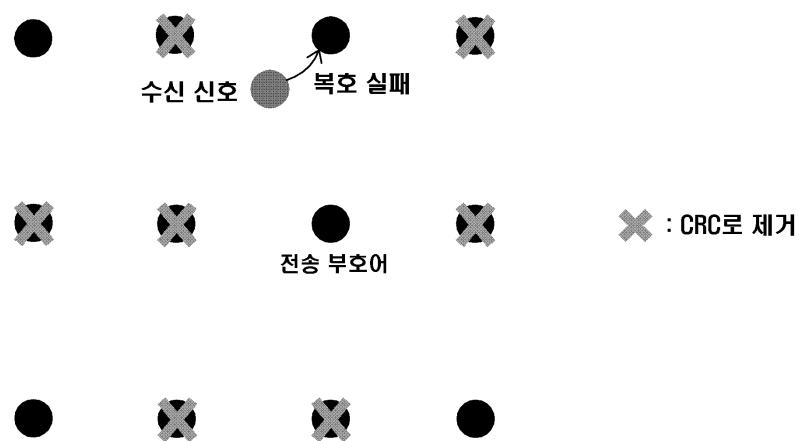

도 4는 종래기술에 따라 CRC 부호화를 적용한 경우의 SCL 복호 과정을 설명하기 위한 도면,

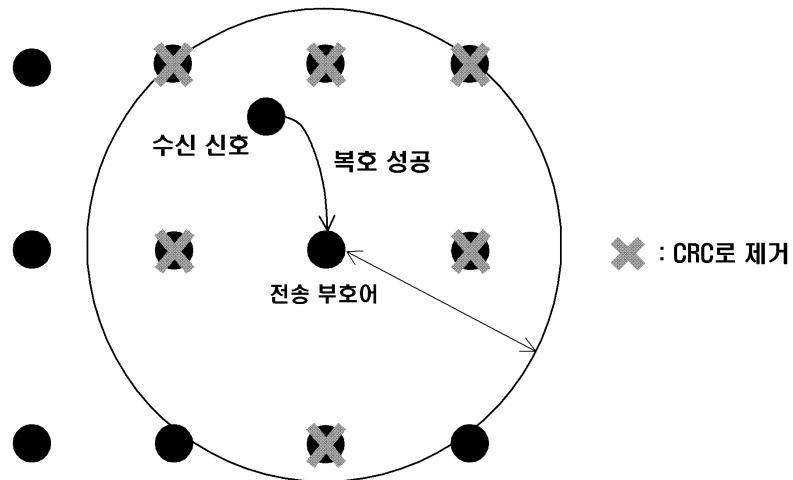

도 5는 본 발명에 따라 CRC 부호화를 적용한 경우의 SCL 복호 과정을 설명하기 위한 도면,

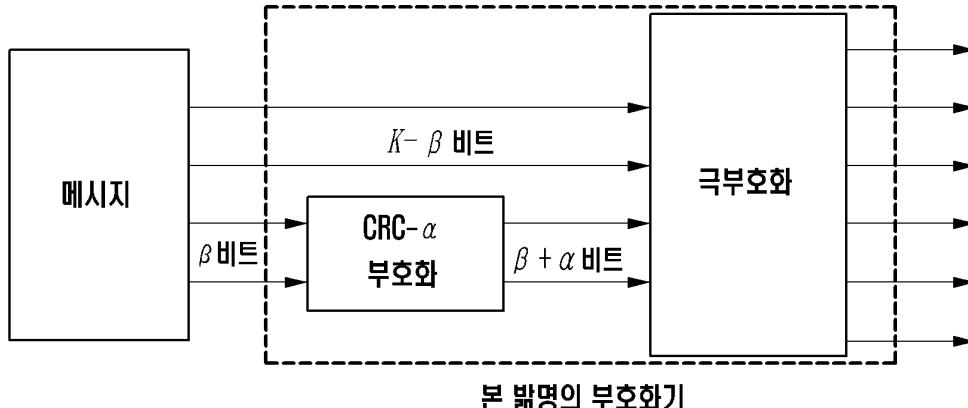

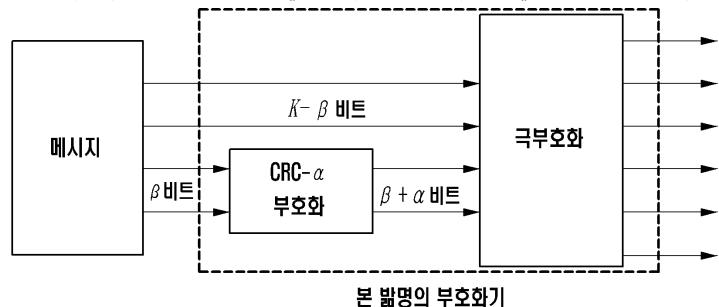

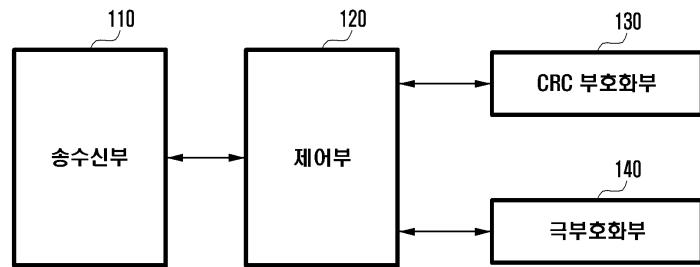

도 6은 본 발명에 따른 CRC-극 부호 연접 부호화기의 구조를 도시한 도면,

도 7은 본 발명에서 CRC 부호화를 수행하는 과정을 도시한 도면,

도 8은 CRC 부호화를 적용할 비트수인  $\beta$ 를 산출하는 과정을 도시한 도면,

도 9는 본 발명에서 극 부호화를 수행하는 과정을 도시한 도면,

도 10은 극 부호화기 입력 비트와 U 벡터의 일대일 맵핑 관계를 도시한 도면,

도 11은 본 발명에 따른 부호화 과정을 수행할 수 있는 부호화 장치의 구성을 도시한 도면

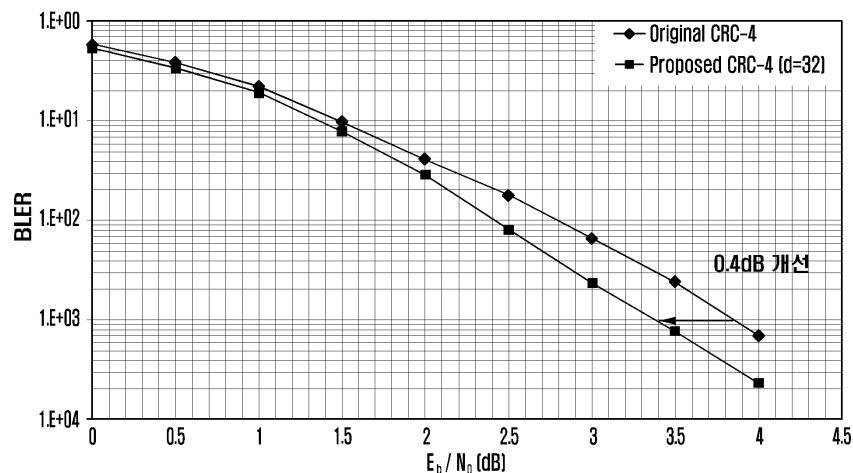

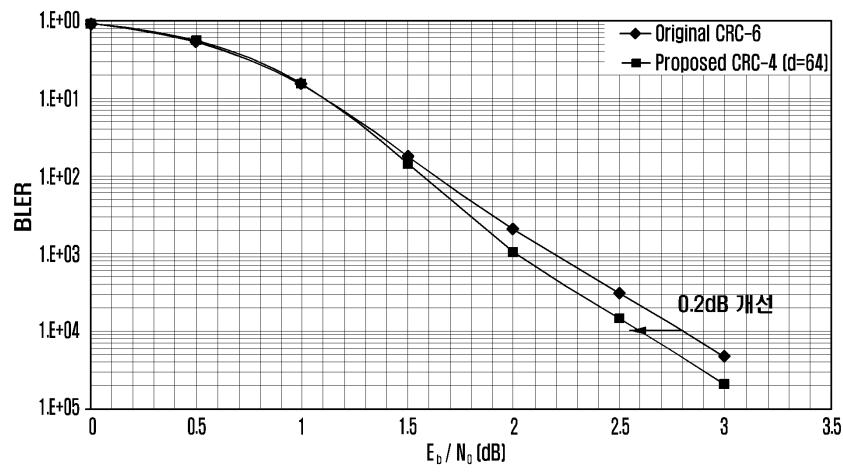

도 12는 CRC 부호 길이가 정보비트 개수에 비하여 부족한 경우의 본 발명의 성능을 도시한 도면, 그리고,

도 13은 본 발명이 관심 있는 블록 오율 영역에서 가장 우수한 성능을 보이는 경우를 도시한 도면이다.

### 발명을 실시하기 위한 구체적인 내용

- [0010] 이하, 본 발명의 실시 예를 첨부된 도면을 참조하여 상세하게 설명한다.

- [0011] 실시 예를 설명함에 있어서 본 발명이 속하는 기술 분야에 익히 알려져 있고 본 발명과 직접적으로 관련이 없는 기술 내용에 대해서는 설명을 생략한다. 이는 불필요한 설명을 생략함으로써 본 발명의 요지를 흐리지 않고 더욱 명확히 전달하기 위함이다.

- [0012] 마찬가지 이유로 첨부 도면에 있어서 일부 구성요소는 과장되거나 생략되거나 개략적으로 도시되었다. 또한, 각 구성요소의 크기는 실제 크기를 전적으로 반영하는 것이 아니다. 각 도면에서 동일한 또는 대응하는 구성요소에는 동일한 참조 번호를 부여하였다.

- [0013] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시 예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 수 있으며, 단지 본 실시 예들은 본 발명의 개시가 완전하도록 하고, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다.

- [0014] 이하, 본 발명의 구성을 설명하기에 앞서 CRC- $a$  부호화기와 극 부호화기, 그리고 그에 대응되는 SCL 복호기에 관하여 설명한다. 본 발명과 같이 CRC- $a$  부호화기와 극 부호화기가 연접되어 있는 부호화기를 CRC-극부호 연접 부호화기라 한다.

- [0015] 도 1은 종래 CRC-극 부호 연접 부호화기의 구조를 도시한 도면이다.

- [0016] 도 1에 나타난  $M$ ,  $M_a$ ,  $X$ 는 모두 0과 1로 구성된 이진 행 벡터(binary row vector)이다. CRC-극부호 연접 부호화기의 입력은  $M$ 으로 나타내며 길이는  $K$ 이고, 출력은  $X$ 로 나타내며 길이는  $N$ 이다( $N=2^n$ ,  $n$ 은 자연수,  $N>K$ ). 여기서  $M$ 은 송신단에서 전송하고자 하는 정보비트(information bits)이며,  $X$ 는  $M$ 이 부호화된 것으로 부호어(codeword)라 한다. 도 1과 같은 경우에 CRC-극부호 연접 부호화기의 실효 부호율  $R$ 은  $K/N$ 이다. 도 1을 통해 알 수 있듯이 CRC-극부호 연접 부호화는 CRC- $a$  부호화와 극 부호화가 연접된 형태로 구성되며, 각각에 대하여 설명하면 다음과 같다.

- [0017] 먼저, CRC- $a$  부호화기의 입력은  $K$ 개의 비트를 갖는  $M$ 이며, 출력은  $K+a$  개의 비트를 갖는  $M_a$ 이다. CRC- $a$  부호화기는 주어진 CRC 부호 생성 다항식(generator polynomial)에 기반하여, 입력으로 들어온  $M$ 에 대한 이진 패리티 벡터  $C=(c_0, c_1, \dots, c_{a-1})$ 를 생성하고  $C$ 를  $M$ 에 연접하여  $M_a$ 를 생성한다.

- [0018] 다음으로 극 부호화기의 입력은  $K+a$  개의 비트를 갖는  $M_a$ 이며 출력은  $N$ 개의 비트를 갖는  $X$ 이다. 극 부호화를 설명하기 위해 필요한 기호들을 정의하면 다음의 표 1과 같다.

## 표 1

| 기호              | 의미                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $G_N$           | <ul style="list-style-type: none"> <li>- <math>N \times N</math> 크기의 극 부호 생성행렬(generator matrix)이며, <math>N=2^n</math></li> <li>- <math>G_N = B_N F^{\otimes n}</math> 으로 정의됨. <math>B_N</math>은 Arikan<sup>o</sup> 제안한 <math>N \times N</math> 크기의 비트-반전(Bit-reversal) 행렬이며, <math>F = \begin{bmatrix} 1 &amp; 0 \\ 1 &amp; 1 \end{bmatrix}</math>, <math>\otimes^n</math> 은 n차 Kronecker 곱 연산을 의미함.</li> <li>- 극 부호의 생성행렬로서 <math>G_N^{\text{Non}} = F^{\otimes n}</math> 또한 사용 가능함.</li> <li>- <math>B_N</math> 행렬의 의미는 이후 예시를 통해 설명함.</li> <li>- 본 발명에서는 <math>G_N</math>을 극 부호 생성행렬로 주로 고려하며, <math>G_N^{\text{Non}}</math>을 생성행렬로 사용하는 경우에도 적용 가능함.</li> </ul> |

| $I$             | <ul style="list-style-type: none"> <li>- 극 부호의 정보집합(information set)</li> <li>- <math>K+a</math>의 크기를 가지는 집합으로 <math>\{0, 1, 2, \dots, N-1\}</math>의 부분집합.</li> <li>- <math>I</math>는 채널 양극화(channel polarization) 현상에 기반하여 생성되는 집합이며, <math>I</math>를 생성하는 구체적인 방법에 대한 설명은 생략함.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| $G_N(I)$        | <ul style="list-style-type: none"> <li>- <math>(K+\alpha) \times N</math> 크기의 극 부호 부분 생성행렬</li> <li>- 모든 <math>i \in I</math>에 대하여, <math>G_N</math> 행렬에서 <math>i+1</math>번째 행들로 구성된 부분 생성행렬</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\mathbf{U}(I)$ | <ul style="list-style-type: none"> <li>- <math>\mathbf{U}</math>는 <math>N \times 1</math> 크기의 행벡터 <math>\mathbf{U} = (u_0, u_1, \dots, u_{N-1})</math></li> <li>- <math>\mathbf{U}(I) = (u_i : i \in I)</math>로 정의되며, <math>\mathbf{U}</math>의 부분 벡터</li> <li>- <math>\mathbf{U}(I)</math> 벡터 내 성분들의 순서는 <math>\mathbf{U}</math> 벡터 내 성분들의 순서를 따름</li> </ul>                                                                                                                                                                                                                                                                                                         |

[0020] 부호 길이가  $N$ 인 모든 극 부호화는 생성행렬  $G_N(I)$ 로 표현할 수 있다.  $K+a$ 의 크기를 가지는 정보집합  $I$ 에 대하여 극 부호화를 식으로 나타내면 다음 수학식 1과 같다. 이때 곱셈은 이진 연산으로 수행된다.

## 수학식 1

$$\mathbf{M}_\alpha \times G_N(I) = \mathbf{X}$$

[0022]  $\mathbf{M}_a$ 가  $K+a$ 의 크기를 갖는 행 벡터이고, 부분 생성행렬  $G_N(I)$ 가  $(K+\alpha) \times N$ 의 크기를 가지므로  $\mathbf{X}$ 는  $N \times 1$  크기의 이진 벡터가 된다.  $\mathbf{X}$ 가 극 부호의 부호어이며,  $\mathbf{X}$ 가 신호로 변조되어 채널을 통과하게 된다.

[0023] 극 부호화기의 동작 과정에 대한 예시를 들면 다음과 같다.  $N$ 이 8이라고 가정하면,  $8 \times 8$  크기의  $G_8$ 은 아래 두 개의 행렬 중 왼쪽의 행렬과 같다. 참고로 오른쪽 행렬은  $G_8^{\text{Non}}$ 로서,  $G_8$ 의 행들을 비트-반전 순서로 재배열하면 만들 수 있고,  $G_8$ 은 다시  $G_8^{\text{Non}}$ 의 행들을 비트-반전 순서로 재배열하면 만들 수 있다.

$$G_8 = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix} \quad G_8 = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

[0024]

[0025] 비트-반전 순서로 행들을 재배열하는 것은 다음과 같다. 먼저  $G_8^{\text{Non}}$  행렬의 첫 행부터 마지막 행까지의 인덱스로 0부터 7까지 차례대로 부여한다.  $N=8$ 이므로, 각 인덱스를 3비트로 이진 확장하면 (000), (001), (010), (011), (100), (101), (110), (111)가 된다.

[0026] 행 인덱스 순서를 유지하면서 각 비트의 앞뒤 순서를 반전시키면 (000), (100), (010), (110), (001), (101), (011), (111)가 된다. 이 이진 확장 값들을 다시 정수로 변환하면 0, 4, 2, 6, 1, 5, 3, 7가 된다. 즉,  $G_8$ 행렬은  $G_8^{\text{Non}}$  행렬 행들을 0, 4, 2, 6, 1, 5, 3, 7 행 인덱스 순으로 재배열하면 생성된다. 마찬가지로  $G_8$ 행렬을 bit-reversal 순서로 재배열하면  $G_8^{\text{Non}}$  행렬이 생성된다.

[0027] 본 발명의 일 실시예로서, 위의 두 행렬 중  $G_8$ 을 고려한다.  $G_8$  행렬에서 집합 I의 크기 및 원소에 따라 부분 생성행렬  $G_8(I)$ 가 결정된다. 만약  $K+a=4$ 이고 극 부호의 정보집합  $I=\{3, 5, 6, 7\}$ 이면,  $G_8$  행렬에서 부분 생성행렬  $G_8(I)$ 를 생성하는데 사용되는 행은 I의 각 성분에 1을 더한 것에 해당하는 행들이다. 즉 4, 6, 7, 8번째 행들이  $G_8(I)$  행렬을 구성하는 데 사용되며, 다음과 같이 크기가  $4 \times 8$ 인 행렬이 된다.

$$G_8(I) = \begin{bmatrix} 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

[0028]

[0029]  $G_8(I)$ 의 행렬을 통해  $K+a$  개의 정보비트가 극 부호화되며, 이 과정은 다음 수학식 2와 같이 표현할 수 있다(정보비트를  $b_i$ 로 표현).

## 수학식 2

$$\begin{aligned} & (b_0 \ b_1 \ b_2 \ b_3) \times G_8(I) \\ &= (x_0 \ x_1 \ x_2 \ x_3 \ x_4 \ x_5 \ x_6 \ x_7) \\ &= (b_0 + b_1 + b_2 + b_3 \ b_1 + b_2 + b_3 \ b_0 + b_2 + b_3 \ b_2 + b_3 \ b_0 + b_1 + b_3 \ b_1 + b_3 \ b_0 + b_3 \ b_3) \end{aligned}$$

[0030]

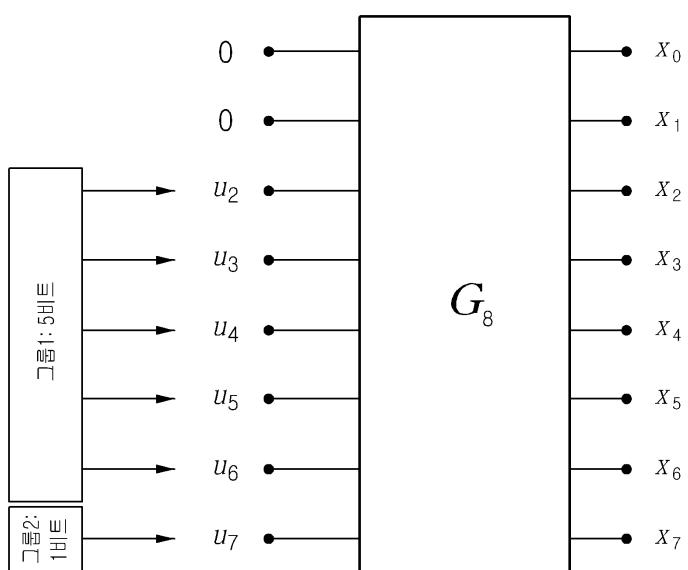

[0031] 도 2는 이상에서 설명한 극 부호화 과정을 도시한 도면이다.

[0032] 도 2에서 오른쪽 블록은  $G_8$ 을 이용한 극 부호화기를 나타내고 있다. 극 부호화기의 좌측으로는 8개의 입력  $\mathbf{U}=(u_0, u_1, \dots, u_7)$ 이 들어가고, 출력은 위에 언급한  $\mathbf{X}$ 가 된다. 단,  $\mathbf{U}$ 의 각 원소는 스위치로 동작하며, 고정값을 전송하는 모드 또는 정보비트를 전송하는 모드로 동작하게 된다. 도 2는 고정값이 0인 경우이다.

[0033] 앞의 예시와 같이  $I=\{3, 5, 6, 7\}$ 인 경우에는  $\mathbf{U}(I)=(u_0, u_1, u_2, u_4)$ 를 통해 항상 고정 값 0을 보내고 나머지 위치  $\mathbf{U}(I)=(u_3, u_5, u_6, u_7)$ 를 통해 정보비트를 전송하게 된다. 4개의 정보비트는  $u_3, u_5, u_6, u_7$  비트와 일대일 맵핑 관계를 갖는다. 정보비트와  $\mathbf{U}(I)$ 의 일대일 맵핑 관계는 어떻게 정의해도 관계없으며, 본 발명에서는 간단하게  $\mathbf{M}_a$ 의  $i$  번째 원소와  $\mathbf{U}(I)$ 의  $i$  번째 원소가 일대일로 대응된다고 가정한다.

[0034] 다음은 본 발명에서 고려하는 복호기인 SCL 복호기에 대한 설명이다.

[0035] SCL 복호기는 2011년 Tal과 Vardy에 의해 제안된 복호기로, 기존의 극 부호 연속 제거(successive cancellation: SC) 복호 성능을 향상시킨 복호기이다. 특히 SCL 복호기는 CRC 부호와 극 부호를 연접하였을 때, 연접하지 않은 경우보다 더 우수한 성능을 보이는 것으로 알려져 있다. CRC 부호가 극 부호와 연접되었을 때와 연접되지 않았을 때, SCL 복호가 어떻게 동작하는지 살펴보면 다음과 같다.

[0036] CRC 부호가 연접되지 않은 극 부호의 경우, SCL 복호기는 수신 신호 벡터를 받아 L개의 부호어 후보를 생성하고 (L개의 부호어 후보 집합을 리스트(list)라 함), 리스트에 속한 부호어 중 가장 우도(likelihood)가 높은 부호

어 1개를 선택한다.

[0037] 한편, CRC 부호가 연접된 극 부호의 경우, SCL 복호기는 수신 신호 벡터를 받아 L개의 부호어 후보를 생성하고, 리스트에 속한 부호어 모두에 대하여 CRC 부호로 오류가 있는지 여부를 검사하고, 오류가 없는 부호어 중 가장 우도(likelihood)가 높은 부호어 1개를 선택한다.

[0038] 이상에서 설명한 바와 같은 CRC-극 부호 연접 부호화기에서는 극 부호의 다양한 부호 길이 또는 다양한 부호율에 맞는 CRC 부호 길이  $a$ 를 결정하는 것이 중요하다.  $a$ 가 너무 길면 정보비트가 아닌 비트를 많이 전송하게 되는 것이기 때문에, 부호율 손실에 의한 성능 열화가 발생하고,  $a$ 가 너무 짧으면 CRC 부호가 오류를 높은 확률로 찾지 못하게 되어 성능 열화가 발생하게 된다. 결론적으로, 극 부호의 부호 길이  $N$ 과 부호율  $R$ 에 따라 적절한 길이  $a$ 의 CRC 부호를 사용하는 것이 중요하다.

[0039] 도 3은 종래 CRC-극부호 연접 시스템의 성능을 도시한 도면이다.

[0040] 도 3의 그래프의 y축은 블록 오율(block error rate) 성능이며, x축은  $E_b / N_0$ (dB)이다. 극 부호의 부호 길이  $N=128$ 이며, 부호율  $R=5/6$ , SCL 복호기의  $L=32$ 이다. 도 3에서 비교하는 두 부호는 같은 부분 생성행렬  $G_N(I)$ 로 생성된 부호이며,  $a$  값만 6과 10으로 상이하다. 도 3에서  $a=6$ 인 부호는 original CRC-6으로 표기되어 있으며,  $a=10$ 인 부호는 original CRC-10으로 표기되어 있다.

[0041] 도 3을 참조하면, original CRC-6 부호는 낮은  $E_b / N_0$ (dB)에서 우수한 성능을 보이지만, 높은  $E_b / N_0$ (dB)로 갈수록 original CRC-10 부호에 비해 열화된 성능을 보임을 확인할 수 있다.

[0042]  $a=6$ 인 부호의 성능 기울기가  $a=10$ 인 부호의 성능 기울기보다 완만한 것은 CRC 부호의 특성상 피할 수 없는 특성이다. CRC 부호의 길이가 짧을 때 오율 성능의 기울기가 완만한 이유는 리스트 안에 있는 부호어 중에서 오류가 있는 부호어를 높은 확률로 찾지 못하기 때문이다. 또한 오류를 높은 확률로 찾지 못하는 이유는 CRC 부호의 길이에 비해 많은 정보비트를 CRC 부호화하기 때문이다.

[0043] 따라서 본 발명은 짧은 CRC 부호 길이로 인한 오류 마루 현상, 즉 오율 감소 기울기가 낮아지는 현상이 나타나는 경우에 CRC 부호화를 효과적으로 적용하여 오율 성능을 향상시키기 위한 것을 목적으로 한다.

[0044] 도 4는 종래기술에 따라 CRC 부호화를 적용한 경우의 SCL 복호 과정을 설명하기 위한 도면이다.

[0045] 도 4와 같이 종래기술에 따라 K개의 정보비트 전체에 CRC 부호화를 적용하는 것은 수신단에서 CRC 부호로 오류 검사를 할 때 전송 부호어가 아닌 모든 부호어를 CRC 부호로 제거하기 위한 것이다. 따라서 CRC 부호 길이가 정보비트 수에 비해 충분하지 않다면 오류 마루가 발생하게 된다. 즉, 도 4에 도시된 바와 같이 CRC 부호 길이가 불충분하여 리스트 내의 12개의 부호어 중 전송 부호어가 아닌 모든 부호어를 제거하지 못하면 복호 실패의 가능성성이 높아지게 되는 것이다.

[0046] 도 5는 본 발명에 따라 CRC 부호화를 적용한 경우의 SCL 복호 과정을 설명하기 위한 도면이다.

[0047] 본 발명은 전송 부호어와 가까이에 있는 부호어들을 CRC 부호로 제거하기 위한 것으로, 구체적으로 파라미터  $d$ 의 값을 조절하면서 전송 부호어로부터 해밍 거리(Hamming Distance)가  $d$  이내인 부호어들을 제거할 수 있도록 CRC 부호화를 적용한다. 이와 같이 CRC 부호화를 적용하기 위해서는 K개의 모든 정보비트에 CRC 부호화를 적용하는 것이 아닌 K개의 정보비트 중 일부 비트에 CRC 부호화를 적용한다.

[0048] 이하, 본 발명에 따른 부호화 방법에 대하여 상세히 설명한다.

[0049] 앞에서도 언급한 바와 같이 종래기술에서는 K개의 정보비트 모두에 대해 CRC 부호화를 적용하지만, 본 발명에서는 K개의 정보비트 중  $\beta$  ( $0 < \beta < K$ )개의 정보비트에 대해 CRC부호화를 적용한다. 이때  $\beta$  값은 CRC-극부호 연접 부호화기에서 사전에 정의되는  $G_N(I)$  와  $d$  값에 의해 결정된다.

[0050] 구체적으로,  $\beta$  값을 산출하기 위해 필요한 파라미터는 다음과 같다.

[0051] N : 극 부호의 부호 길이

[0052] I : 극 부호의 정보집합이며 크기는  $K+a$  이다.

[0053] d: CRC- $a$  부호로 오류 검사 가능한, 전송 부호어로부터의 최대 해밍 거리

[0054] a : CRC 부호의 길이

[0055]  $G_N(I)$  :  $(K+a) \times N$ 크기의 극 부호 부분 생성행렬

$$G_N(I) = \begin{bmatrix} 1 & \cdots & 0 & 0 \\ 1 & \ddots & 1 & 0 \\ \vdots & 0 & \ddots & \vdots \\ 1 & \cdots & 1 & 1 \end{bmatrix}$$

[0056] [0057] 극 부호의 부호화는  $G_N(I)$  행렬로 표현 가능하다. 즉, 부호 길이가  $N$ 이고 부호율이  $R$ 인 모든 극 부호화는  $G_N(I)$  행렬로 나타낼 수 있다.

[0058]  $G_N(I)$  와  $d$ 가 주어졌을 때,  $G_N(I)$ 의 행들 중에서 행의 해밍 웨이트(Hamming weight)가  $d$ 보다 작거나 같은 행의 개수가  $\beta+a$ 가 된다. 여기서 한 행의 해밍 웨이트는 그 행에 속한 0이 아닌 원소의 수를 의미한다. 따라서  $\beta$ 는 해밍 웨이트가  $d$ 보다 작거나 같은 행의 개수에서  $a$ 를 뺀 값이 된다.

[0059] 이상에서 설명한  $\beta$ 를 구하는 방법은 극 부호 생성행렬이  $G_N$ 이든  $G_N^{\text{Non}}$ 이든 관계없이  $G_N$ 만 주어지면 적용 가능하다. 또한  $G_N(I)$  행렬이 아닌 정보집합  $I$ 만 주어지더라도  $\beta$ 를 구할 수 있다.  $I$ 를 통해  $\beta$ 를 구하는 방법은 극 부호 생성행렬이  $G_N$ 이든  $G_N^{\text{Non}}$ 이든 관계없이 동일하게 적용할 수 있는 방법이다.

[0060] 부호길이  $N=2^d$ 와 정보집합  $I$ ,  $d$ ,  $a$ 가 주어졌을 때,  $\beta$ 를 구하는 방법은 다음과 같다.

[0061] 먼저  $i \in I$ 에 대하여  $n$ 비트 이진 확장 벡터(binary expansion vector)를 구한다. 각  $i$ 에 해당하는 이진 확장 벡터를  $B_i$ 로 정의한다. 다음으로 모든  $i \in I$ 에 대하여,  $B_i$ 에 속한 1의 개수를 구하고, 1의 개수가  $\log_2 d$ 보다 같거나 작은  $i$ 의 개수를 세면  $\beta+a$ 가 된다. 따라서  $\beta$ 를 구할 수 있다. 이때, 모든  $i \in I$ 에 대하여  $B_i$ 에 속한 1의 개수가  $\log_2 d$  보다 같거나 작은 모든  $i$ 의 집합을  $I_d$ 로 정의한다.

[0062] 예를 들면,  $N=8$ 이고 정보집합  $I=\{3, 5, 6, 7\}$ ,  $d=4$ ,  $a=2$ 가 주어졌을 때,  $\beta$ 를 구하는 방법은 다음과 같다.

[0063] 먼저, 모든  $i \in I$ 에 대하여 3비트 이진 확장 벡터를 구하면 다음과 같다.

$$B_3 = (0 \ 1 \ 1), B_5 = (1 \ 0 \ 1), B_6 = (1 \ 1 \ 0), B_7 = (1 \ 1 \ 1)$$

[0064] 다음으로, 모든  $i \in I$ 에 대하여,  $B_i$ 에 속한 1의 개수를 구하고, 1의 개수가  $\log_2 4$ 보다 작거나 같은  $i$ 의 개수를 세면 3이다. 따라서  $\beta=3-a=3-2=1$ 과 같이  $\beta$  값을 구할 수 있다.

[0065] 이상에서 설명한 방법으로  $\beta$ 를 구한 후,  $K$ 개의 정보비트 중  $\beta$ 개의 비트에 대해 CRC 부호화를 적용한다.

[0066] 도 6은 본 발명에 따른 CRC-극 부호 연접 부호화기의 구조를 도시한 블록도이다. 도 6으로부터 알 수 있는 바와 같이 본 발명에서는  $K$ 개의 입력 정보비트 중  $\beta$ 개의 비트에 대하여만 CRC 부호화를 적용하고, CRC 부호화된  $\beta+a$ 개의 비트와 CRC 부호화되지 않은  $K-\beta$ 비트에 극 부호화를 적용한다.

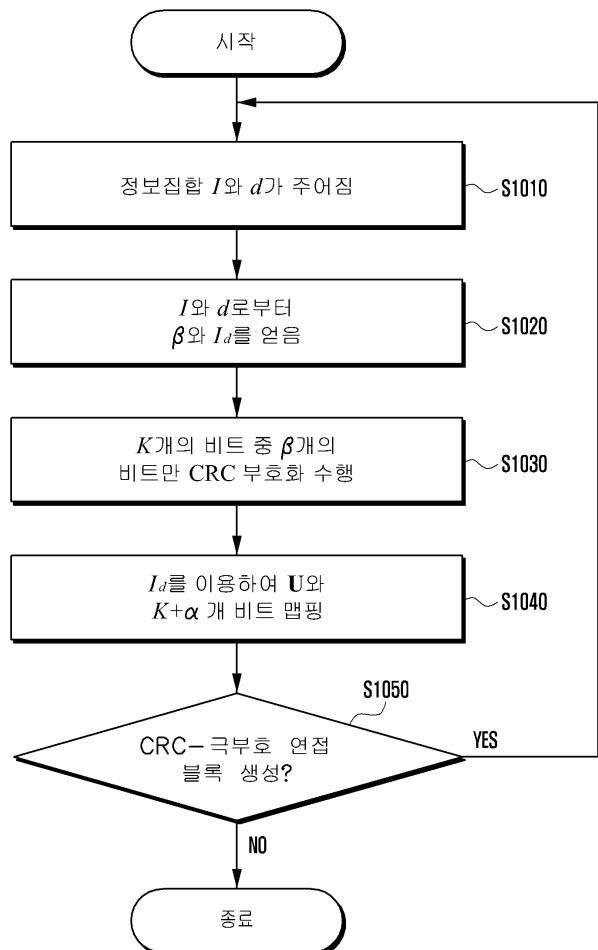

[0067] 도 7은 본 발명에서 CRC 부호화 및 극 부호화를 수행하는 과정을 도시한 도면이다.

[0068] 도 7을 참조하면, S1010 단계에서, 극 부호의 정보집합  $I$ 와 파라미터  $d$ 의 값이 사전에 주어진다. 다음으로 S1020 단계에서, 주어진  $I$ 와  $d$ 로부터 이상에서 설명한 방법에 의해  $\beta$ 와  $I_d$ 를 얻는다. 이하, 이 과정을 구체적으로 설명한다.

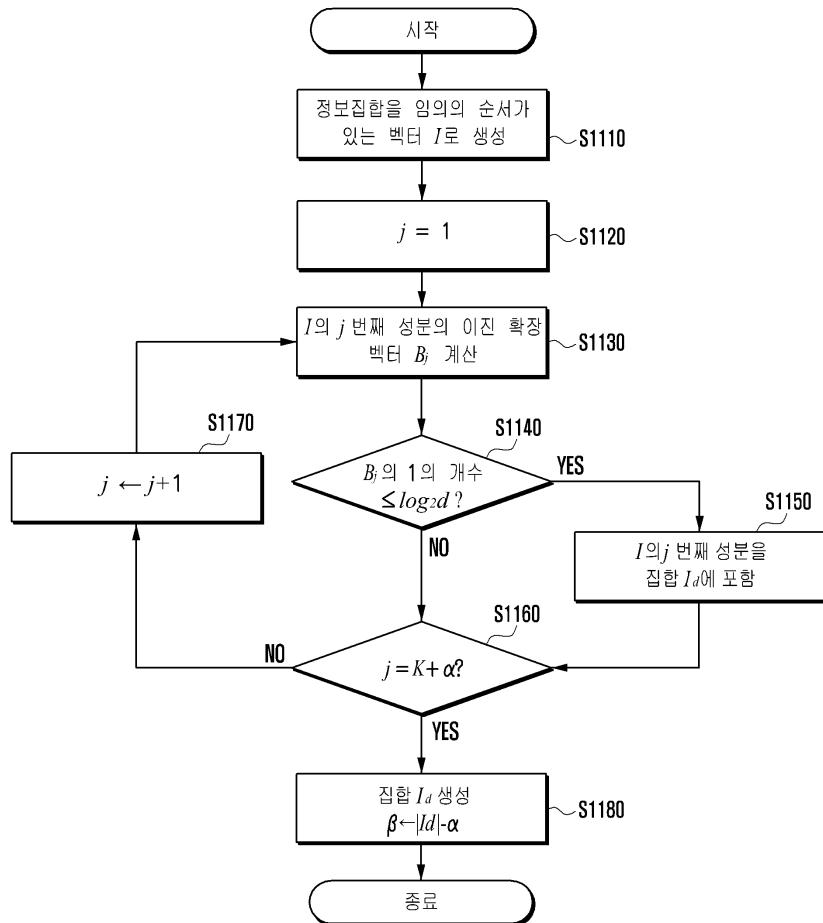

[0069] 도 8은 CRC 부호화를 적용할 비트수인  $\beta$ 를 산출하는 과정을 도시한 도면이다.

[0070] 도 8을 참조하면, S1110 단계에서, 정보집합  $I$ 를 임의의 순서가 있는 벡터  $I$ 로 생성하고, S1120 단계에서 초기 값  $j=1$ 을 설정한다.

[0071] 다음으로 S1130 단계에서  $I$ 의  $j$ 번째 성분의 이진 확장 벡터  $B_j$ 를 계산하고, S1140 단계에서  $B_j$ 에 포함된 1의 개수가  $\log_2 d$  이하인지 여부를 판단한다.  $B_j$ 의 1의 개수가  $\log_2 d$ 보다 작거나 같으면, S1150 단계에서  $I$ 의  $j$ 번째 성분을 집합  $I_d$ 에 포함시킨다.

- [0073] S1160 단계에서,  $j$ 가  $K+a$ 와 동일한지 여부를 판단한다. 즉, 정보집합의 모든 원소에 대하여 위 과정이 적용되었는지 여부를 판단하고, 아직  $j$ 가  $K+a$ 에 도달하지 않았으면 S1170 단계에서  $j$ 의 값을 1 증가시켜 이진 확장 벡터  $B_j$ 를 계산하고 위 과정을 반복한다. 정보집합의 모든 원소에 대하여 위 과정이 수행되었으면, S1180 단계에서 집합  $I_d$ 를 생성하고,  $\beta$ 의 값을  $|I_d|-a$ 와 같이 결정한다.

- [0074] 다시 도 7을 참조하면, S1030 단계에서 입력 정보비트의 전체  $K$ 개의 비트 중 앞에서 결정된  $\beta$ 에 해당하는 비트의 정보비트에 대해 CRC 부호화를 수행한다. 이때  $K$ 개의 정보비트 중에서 CRC 부호화를 적용할 어떠한  $\beta$  개의 비트를 임의로 선택할 수 있으며, 일 실시예로서  $K$ 개의 정보비트  $M$ 의 첫 번째 성분부터 순차적으로  $\beta$  개 비트를 선택할 수 있다.

- [0075] 다음으로 S1040 단계에서,  $I_d$ 를 이용하여  $U$ 와  $K+a$  개의 비트를 맵핑하는 극 부호화를 수행한다. 이하, 극 부호화 과정을 상세히 설명한다.

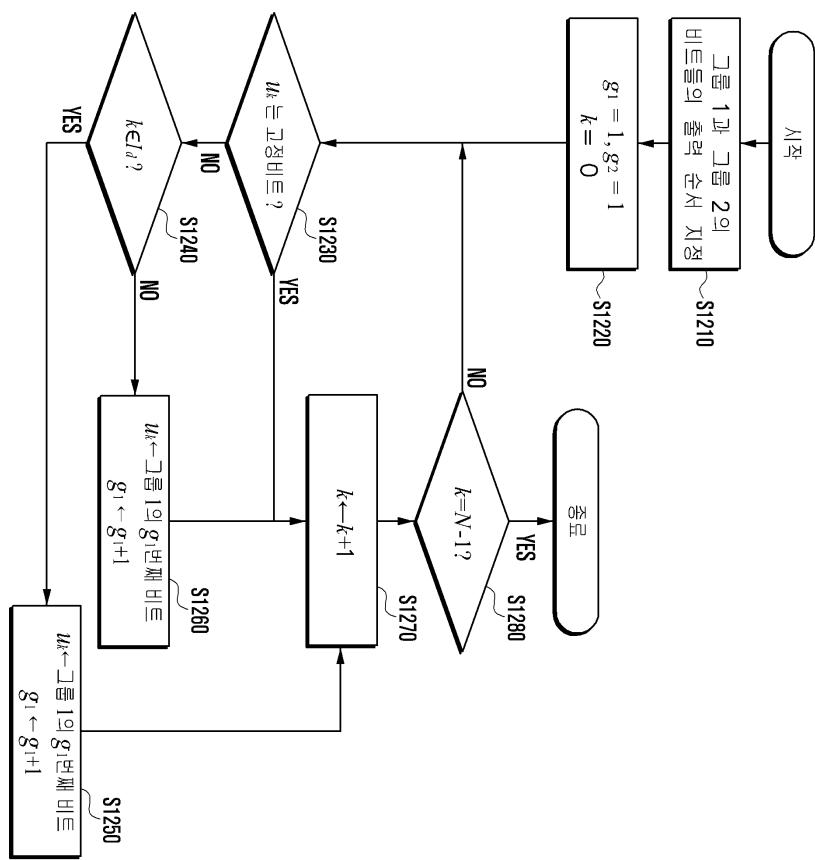

- [0076] 도 9는 본 발명에서 극 부호화를 수행하는 과정을 도시한 도면이다.

- [0077] 극 부호화기의 입력으로 들어오는  $K+a$  개의 비트  $M_a$ 는 CRC- $a$  부호화기를 통과한  $\beta+a$  개의 비트와 CRC- $a$  부호화기를 통과하지 않은  $K-\beta$  개의 비트로 구분된다.  $\beta+a$  개 비트 그룹을 그룹 1로 지칭하고,  $K-\beta$  개 비트 그룹을 그룹 2로 지칭한다. CRC 부호화가 적용된 그룹 1의 비트들은 극 부호화기에서  $U(I_d)$ 와 일대일로 맵핑되며, 그룹 2의 비트들은  $U(I-I_d)$ 와 일대일로 맵핑된다. 여기서의 맵핑 또한 역시 임의로 정의될 수 있다.

- [0078] S1210 단계에서, 그룹 1과 그룹 2의 비트들의 출력 순서가 지정된다. 출력 순서는 각 그룹의 비트들이 스택 또는 큐에 저장되었다고 가정하여 정해질 수 있다.

- [0079] S1220 단계에서, 극 부호화를 위한 파라미터들의 초기값이 다음과 같이 설정된다.

- [0080]  $g_1=1$ ,  $g_2=1$ ,  $k=0$

- [0081] S1230 단계에서,  $u_k$ 가 고정비트인지 여부를 판단하고, 고정비트가 아니면 S1240 단계에서  $k$ 가  $I_d$ 에 속하는지 여부를 판단한다.  $k$ 가  $I_d$ 에 속하면 S1250 단계에서  $u_k$ 에 그룹 1의  $g_1$  비트를 매핑하고,  $g_1$ 의 값을 1 증가시킨다.  $k$ 가  $I_d$ 에 속하지 않으면 S1260 단계에서  $u_k$ 에 그룹 2의  $g_2$  비트를 매핑하고,  $g_2$ 의 값을 1 증가시킨다.

- [0082] 위 S1250 단계 또는 S1260 단계를 수행하거나 S1230 단계에서  $u_k$ 가 고정비트인 것으로 판단되면, S1270 단계에서  $k$ 의 값을 1 증가시키고, S1280 단계에서  $k$ 의 값이  $N-1$ 에 도달하였는지 판단하고, 도달하지 않았으면 S1230 단계로 되돌아가 위 과정을 반복 수행한다.  $k$ 의 값이  $N-1$ 에 도달하였으면 극 부호화 과정이 종료된다.

- [0083] 다시 도 7을 참조하면, 마지막으로 S1050 단계에서, CRC-극부호 연접 블록이 생성되면 부호화 과정이 종료된다.

- [0084] 이하, 본 발명의 일 실시예로서 비트-반전  $G_8$  행렬에 대하여 다음과 같은 조건들이 주어졌을 때 본 발명의 동작을 설명한다.

- [0085]  $N=8$ ,  $K=4$ ,  $a=2$ ,  $d=4$ ,  $I=\{2, 3, 4, 5, 6, 7\}$

- $$G_8 = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

- [0086]

$$G_8(I) = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

[0087]

[0088] 본 실시예에서는  $I=\{2, 3, 4, 5, 6, 7\}$ 이므로,  $G_8(I)$ 는  $G_8$  행렬에서 1번째, 2번째 행이 제거된 행렬이 된다. 그리고  $G_8(I)$ 에서 해밍 웨이트가  $d=4$ 보다 같거나 작은 행은 5개이기 때문에  $\beta=5-\alpha=3$ 이다. 또한  $d=4$ 보다 같거나 작은 행들로부터  $I_d$ 를 구하면  $I_d=\{2, 3, 4, 5, 6\}$ 이 된다.

[0089]

$\beta=3$ 이기 때문에, 4개의 정보비트로 구성된 **M** 중 첫 번째 성분부터 순차적으로 선택된 3개의 비트는 CRC-2 부호화기를 통과하게 되고, 나머지 한 비트는 직접 즉 부호화기의 입력으로 들어간다. CRC-2 부호화기를 통하여 5비트가 된 그룹 1 비트는  $U(I_d)$  비트와 일대일로 맵핑되며, 그룹 2 비트는  $U(I-I_d)$  비트와 일대일로 맵핑된다. 그룹 1 비트 및 그룹 2 비트와 **U** 벡터의 일대일 맵핑 관계를 도 10에 도시하였다.

[0090]

도 11은 본 발명에 따른 부호화 과정을 수행할 수 있는 부호화 장치의 구성을 도시한 도면이다.

[0091]

도 11을 참조하면, 본 발명에 따른 부호화 장치는 송수신부(110), 제어부(120), CRC 부호화부(130) 및 즉 부호화부(140)를 구비할 수 있다.

[0092]

송수신부(110)는 부호화될 입력 정보비트를 입력받고, 본 발명에 따라 부호화된 정보비트를 외부로 출력하는 기능을 수행한다.

[0093]

제어부(120)는 CRC 부호화부(130)와 즉 부호화부(140)의 부호화 동작을 제어하며, 부호화에 필요한 파라미터들을 산출한다. 예를 들면, 제어부(120)는 입력 정보비트 중 CRC 부호화부(130)에 의해 부호화될 비트수  $\beta$ 를 산출하여 CRC 부호화되도록 할 수 있다. 또한 제어부(120)는  $I_d$ 를 산출하여 즉 부호화부(140)에 제공함으로써 CRC 부호화가 수행된 정보비트 그룹 및 CRC 부호화가 수행되지 않은 정보비트 그룹과  $U(I)$ 의 일대일 맵핑이 이루어지도록 할 수 있다.

[0094]

CRC 부호화부(130)와 즉 부호화부(140)는 제어부(120)의 제어에 따라 앞에서 설명한 CRC 부호화 및 즉 부호화 과정을 각각 수행한다.

[0095]

본 발명의 효과를 검증하기 위해 CRC 부호의 길이가 정보비트 개수에 비하여 부족한 경우에 본 발명이 어느 정도 성능 향상을 보이는지 확인하고, 본 발명이 관심 있는 블록 오율 영역에서 가장 우수한 성능을 보이는 경우도 성능 그래프로 확인하였다.

[0096]

도 12는 CRC 부호 길이가 정보비트 개수에 비하여 부족한 경우의 본 발명의 성능을 도시한 도면이다.

[0097]

도 12의 (a)는  $N=128$ ,  $K=64$ ,  $R=0.5$ , CRC-4인 경우이며,  $d=32$ 로 하였을 때 본 발명이 종래기술에 비해 블록 오율  $10^{-3}$  기준으로 약 0.4dB의 성능 이득을 얻게 된다. 도 12의 (b)는  $N=1024$ ,  $K=512$ ,  $R=0.5$ , CRC-6인 경우이며,  $d=64$ 로 하였을 때 본 발명이 종래기술에 비해 블록 오율  $10^{-4}$  기준으로 약 0.2dB 성능 이득을 얻게 된다.

[0098]

도 13은 본 발명이 CRC 부호 길이에 무관하게 관심 있는 블록 오율 영역에서 가장 우수한 성능을 보이는 경우를 도시한 도면이다. 도 13의 경우,  $N=128$ ,  $K=106$ ,  $R=0.83$ , 그리고  $d=32$ 이다. 도 13을 참조하면, 본 발명은 종래기술보다 블록 오율  $10^{-2}$  기준으로 약 0.15dB의 성능 이득을 얻게 된다. 이 성능 이득은 CRC 부호 길이를 다르게 한 부호들과 비교하여 얻은 이득이므로 의미 있는 성능 이득이다.

[0099]

본 발명이 속하는 기술분야의 통상의 지식을 가진 자는 본 발명이 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술한 실시 예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구의 범위에 의하여 나타내어지며, 특허청구의 범위의 의미 및 범위 그리고 그 균등 개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

[0100]

한편, 본 명세서와 도면에는 본 발명의 바람직한 실시 예에 대하여 개시하였으며, 비록 특정 용어들이 사용되었

으나, 이는 단지 본 발명의 기술 내용을 쉽게 설명하고 발명의 이해를 돋기 위한 일반적인 의미에서 사용된 것 이지, 본 발명의 범위를 한정하고자 하는 것은 아니다. 여기에 개시된 실시 예 외에도 본 발명의 기술적 사상에 바탕을 둔 다른 변형 예들이 실시 가능하다는 것은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 자명한 것이다.

### 부호의 설명

[0101] 110 - 송수신부                    120 - 제어부

130 - CRC 부호화부                    140 - 극 부호화부

### 도면

#### 도면1

#### 도면2

도면3

도면4

도면5

도면6

$$\mathbf{M} = (m_0, m_1, \dots, m_{k-l}) \quad \mathbf{M}_\alpha = (m_0, \dots, m_{k-l}, c_0, \dots, c_{\alpha-l}) \quad \mathbf{X} = (x_0, x_1, \dots, x_{N-l})$$

## 도면7

## 도면8

도면9

도면10

도면11

도면12

(a)

(b)

도면13