(19) INSTITUTO NACIONAL

DA PROPRIEDADE INDUSTRIAL

PORTUGAL

(11) *Número de Publicação: PT 91582 B*

(51) *Classificação Internacional: (Ed. 6)*

G06G007/163 A

G06J001/00 B

(12) **FASCÍCULO DE PATENTE DE INVENÇÃO**

(22) *Data de depósito:* 1989.08.30

(30) *Prioridade:* 1988.08.31 EP 88114225

(43) *Data de publicação do pedido:*

1990.03.08

(45) *Data e BPI da concessão:*

03/95 1995.03.15

(73) *Titular(es):*

SIEMENS AKTIENGESELLSCHAFT

WITTELSBACHERPLATZ 2 D-8000 MUNIQUE 2

DE

(72) *Inventor(es):*

RICHARD STEPP DE

(74) *Mandatário(s):*

JOÃO DE ARANTES E OLIVEIRA

RUA DO PATROCÍNIO 94 1350 LISBOA PT

(54) *Epígrafe:* MULTIPLICADOR DE QUATRO QUADRANTES COM VÁRIAS ENTRADAS

(57) *Resumo:*

[Fig.]

Descrição referente à patente de invenção de SIEMENS AKTIENGESELLSCHAFT, alemã, industrial e comercial, com sede em Wittelsbacherplatz 2, D-8000 Munique, República Federal Alemã, (inventor:Richard Stepp, residente na Alemanha Ocidental), para "MULTIPLICADOR DE QUATRO QUADRANTES COM VÁRIAS ENTRADAS".

D E S C R I Ç Ã O

A presente invenção refere-se a um multiplicador de quatro quadrantes com várias entradas, com mais de duas entradas de sinal, para efectuar a multiplicação de um sinal de entrada por vários outros sinais de entrada, em cuja saída se combinam aditivamente os vários resultados individuais das multiplicações, de acordo com o preâmbulo da reivindicação 1.

Tais multiplicadores são necessários por exemplo, no caso da modulação por vários sinais de uma portadora comum ou da detecção de sinais com frequências diferentes que modularam uma portadora comum.

Os multiplicadores de quatro quadrantes com duas entradas de sinal lineares, bem como o seu modo de funcionamento estão descritos, entre outros locais, no "Data-Acquisition Databook 1984, Vol. 1 Integrated Circuits" da Analog Devices, Inc., nas páginas 6-9 a 6-16, bem como no livro "Halbleiterschaltungstechnik", Auflage 1980, de U.Tietpe, Ch Schenk nas páginas 227 e seguintes, em especial no capítulo

11.41. Trata-se aqui de multiplicadores que são construidos com base nas chamadas células de Gilbert ou circuitos de Gilbert.

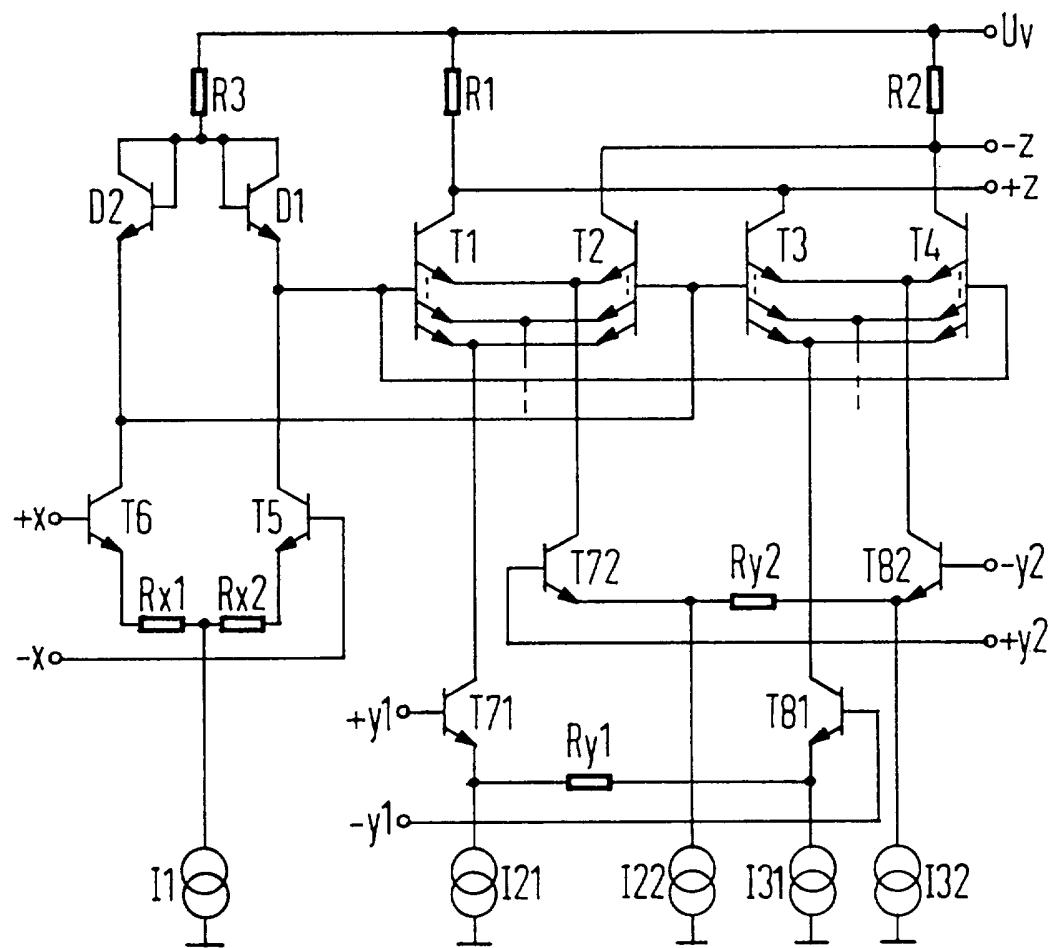

A fig. 1 representa um tal circuito conhecido. Um primeiro e um segundo transistores (T1) e (T2), bem como um terceiro e um quarto transistores (T3) e (T4) formam, respectivamente, um par de amplificadores diferenciais, com emissores ligados directamente. O terminal de ligação do colector do primeiro transistor está interligado com o terminal de ligação do colector do terceiro transistor (T3) e, através de uma primeira resistência ( $R_1$ ), com um potencial de alimentação ( $U_v$ ), e forma um terminal de saída do sinal ( $+z$ ). Da mesma maneira, o terminal de ligação do colector do segundo transistor (T2) está interligado com o terminal de ligação do colector do quarto transistor (T4), ligado através de uma segunda resistência ( $R_2$ ) com o potencial de alimentação ( $U_v$ ), e forma um outro terminal de saída do sinal ( $-z$ ), que, juntamente com o terminal de saída do sinal  $+z$ , pode preparar um sinal de saída simétrico. Como os terminais de ligação dos emissores dos transistores (T1) e (T2), bem como (T3) e (T4) estão ligados entre si, sem qualquer resistência de contra-reacção, os terminais de ligação da base destes transistores não representam qualquer entrada de sinal linear. Para se obter uma entrada de sinal linear, interligam-se o terminal de ligação da base do primeiro transistor (T1) com o terminal de ligação da base do quarto transistor (T4), bem como ao terminal de ligação do colector do quinto transistor (T5) e, através de um primeiro diodo (D1), a uma fonte de corrente, que, em especial, liga uma terceira resistência ( $R_3$ ), ligada com um outro terminal, ao potencial de alimentação ( $U_v$ ). Analogamente, o terminal de ligação da base do segundo transistor (T2) está ligado com o terminal da base do terceiro transistor (T3) e ao terminal de ligação do colector de um sexto transistor (T6) e, através de um segundo diodo (D2), à referida terceira resistência ( $R_3$ ) ou à referida fonte de corrente, respectivamente. Os terminais de ligação dos emissores do quinto transistor (T5) e do sexto transistor (T6) estão ligados quer entre si, através

de uma resistência, quer cada um deles, através de uma fonte de corrente própria, ao potencial de referência, ou então, como se mostra na fig. 1, através de uma quarta resistência ( $R_{x1}$ ) e uma quinta resistência ( $R_{x2}$ ), ligadas entre si, estando o nó de ligação das resistências ( $R_{x1}$ ) e ( $R_{x2}$ ) ligado, através de uma primeira fonte de corrente constante ( $I_1$ ), ao potencial de referência (massa). O terminal de ligação da base do sexto transistor ( $T_6$ ) forma portanto o primeiro terminal de entrada (+x) e o terminal de ligação da base do quinto transistor ( $T_5$ ) forma um segundo terminal de entrada (-x) do multiplicador. Através dos terminais -x e -x é possível a alimentação de um sinal de entrada simétrico, tendo o multiplicador, relativamente a esta entrada do sinal, características de transmissão linear. Os terminais de ligação dos emissores dos transistores ( $T_1$ ) e ( $T_2$ ) estão ligados com o terminal de ligação do colector do sétimo transistor ( $T_7$ ). Os terminais de ligação dos emissores dos transistores ( $T_3$ ) e ( $T_4$ ) estão ligados com o terminal de ligação do colector de um oitavo transistor ( $T_8$ ). Os terminais de ligação dos emissores dos transistores ( $T_7$ ) e ( $T_8$ ) estão interligados através de uma resistência de acoplamento ( $R_y$ ). O terminal do emissor do sétimo transistor ( $T_7$ ) está ligado através de uma segunda fonte de alimentação constante ( $I_2$ ) ao potencial de referência e o terminal de ligação do emissor do transistor ( $T_8$ ) está ligado ao potencial de referência através de uma terceira fonte de corrente constante ( $I_3$ ). O terminal de ligação da base do transistor ( $T_7$ ) forma o terceiro terminal de entrada +y e o terminal de ligação da base do oitavo transistor ( $T_8$ ) forma o quarto terminal de entrada -y do multiplicador. Através dos terminais +y e -y é possível a introdução de um sinal de entrada simétrico, apresentando o multiplicador, em consequência da contra-reacção provocada pela resistência de acoplamento ( $R_y$ ), também características de transmissão lineares relativamente a esta entrada do sinal.

Os circuitos deste género são apropriados, em particular, para a multiplicação de pelo menos um sinal de entrada digital por um outro sinal de entrada. A fim de obter um multiplicador correspondente com amis de duas en-

de sinal, podendo multiplicar um sinal de entrada por vários outros sinais de entrada e adicionar-se os vários resultados individuais das multiplicações, poderíamos interligar um número correspondente de tais multiplicadores conhecidos. Esta interligação de vários multiplicadores tem no entanto certos inconvenientes, que se mostram negativos em especial no caso da utilização como detector ou modulador.

Os transistores ou diodos fabricados numa mesma fase de trabalho e numa micropastilha são em grande medida análogos, respectivamente, mas o comportamento insignificantemente diferente com sinais de grande amplitude, a dispersão dos factores de amplificação, etc. dos vários transistores, em especial quando há muitos transistores interligados de maneira apropriada, proporcionam, entre outras coisas, desequilibrios de tensões contínuas diferentes nos vários andares de amplificação e, além disso, as várias entradas dos sinais do circuito global do multiplicador adquirem pesos diferentes. Como o desequilíbrio das tensões contínuas é nesses circuitos um tanto problemático, a sobreposição de vários desequilibrios de tensão contínua diferentes é particularmente negativa.

Outros inconvenientes de um tal circuito são o grande consumo de espaço na micropastilha e as capacidades dos trajectos condutores, eventualmente perturbadores no caso das altas frequências.

O objecto da presente invenção consiste em proporcionar um multiplicador de um sinal de entrada por vários outros sinais de entrada, combinando-se aditivamente os vários resultados das multiplicações, no qual não aparecem estes inconvenientes ou os mesmos são reduzidos numa medida em que se tornam não perturbadores.

Este problema é resolvido por meio de um circuito de acordo com a reivindicação 1, bem como por um circuito de acordo com a reivindicação 2.

Formas de realização aperfeiçoadas vantajosas são objecto das reivindicações secundárias.

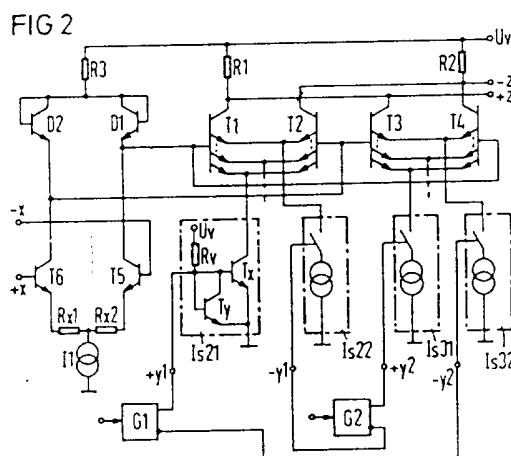

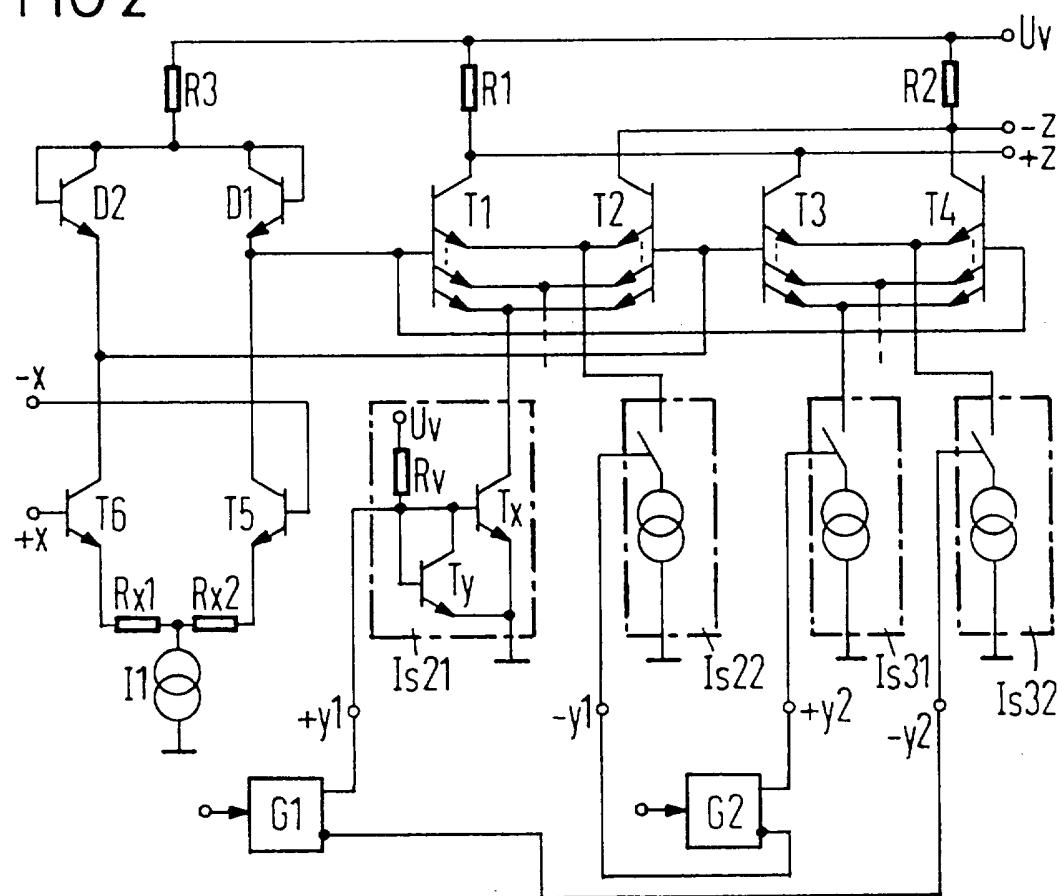

A fig. 2 representa o circuito que é o objecto da reivindicação 1, apropriado em especial para o processamento de sinais rectangulares ou digitais.

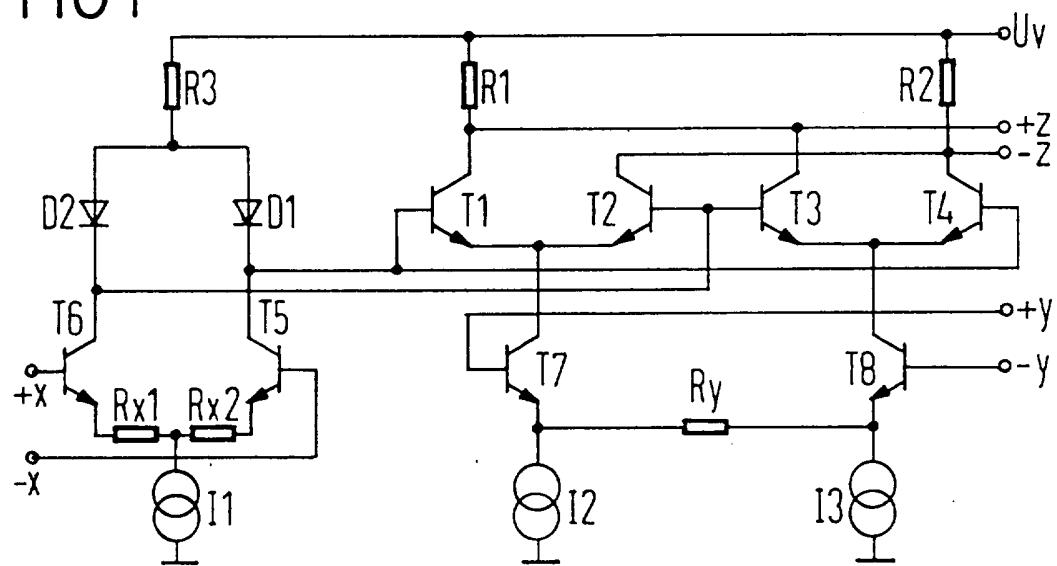

A fig. 3 representa o circuito que é o objecto da reivindicação 2.

Os elementos dos circuitos que são iguais ou desempenham funções idênticas nas fig. 1, 2 e 3 têm os mesmos números de referência.

O modo de funcionamento de princípio dos circuitos representados e descritos nas reivindicações 1 e 2 é análogo ao do circuito da fig. 1, bem conhecido dos especialistas da matéria.

A vantagem especial dos circuitos segundo a presente invenção baseia-se no facto de que os transistores (T1), (T2), (T3) e (T4) ligados num circuito de comando apropriado, sob a forma de um circuito de Gilbert, são formados como transistores com vários emissores para esta aplicação especial. Por isso, a complicaçāo dos circuitos, bem como a área necessária numa micropastilha para os circuitos segundo a presente invenção pouco maiores são que os de um multiplicador de um só andar.

O sinal de entrada, que é introduzido nos terminais de entrada  $+x/-x$ , é de uma maneira conhecida, misturado multiplicativamente, ou multiplicado, na faixa de comando linear, pelos sinais de entrada que são introduzidos nos terminais  $+y_1/-y_1$ ,  $+y_2/-y_2$ . Como as correntes de colector dos transistores (T1), (T2), (T3) e (T4) contêm, respectivamente, a soma das suas correntes de emissor, os produtos individuais das multiplicações são combinados aditivamente nos terminais de saída  $+z/-z$ , onde são preparados.

Se o produto da multiplicação do sinal de entrada introduzido na entrada  $+x/-x$  por um sinal de entrada introduzido numa outra entrada de sinais é adicionado a, ou subtraído dos restantes produtos das multiplicações que são formados a partir do sinal de entrada da entrada  $+x/-x$  e dos sinais de entrada das restantes entradas de sinais, depende

apenas do sinal algébrico do sinal de entrada em questão. Trocando os terminais de entrada, por exemplo +yl com -yl, pode mudar-se o sinal algébrico.

O circuito representado na fig.3 e descrito na reivindicação 2 é particularmente apropriado para as aplicações em que se pretende que o comportamento de transmissão do multiplicador, relativamente às várias entradas individuais, seja linear. Este comportamento de transmissão linear relativamente às entradas  $+y_1/-y_1$ ,  $+y_2/-y_2$ , ... é garantido em especial pelo acoplamento mútuo provocado pelas resistências ( $R_{y1}$ ), ( $R_{y2}$ )..

Para os circuitos segundo a presente invenção não é relevante saber se os emissores dos transistores ( $T_5$ ), ( $t_6$ ), ( $T_7$ ), ( $T_8$ ), ( $T_{71}$ ), ( $T_{81}$ ), ( $T_{72}$ ), ( $T_{82}$ ),... estão respectivamente ligados, através de uma resistência ( $R_{y1}$ ), com o emissor do transistor correspondente, se estão ligados através de uma fonte de corrente própria ao potencial de referência ou se estes emissores estão ligados entre si através de duas resistências em série ( $R_{x1}, R_{x2}$ ),... e em cada caso apenas o nó de ligação destes resistências está ligado através de uma fonte de corrente constante ao potencial de referência . Como pode deduzir-se do livro "Halbleiter-Schaltungstechnik" x 4<sup>a</sup> Edição 1978, por U. Tietze, Ch. Schenk, nas páginas 64 e 65, estas formas de realização são equivalentes. Na sua acção diferem apenas pelo facto de no caso de duas fontes de corrente e uma resistência por cada par de emissores, esta corrente não ser atravessada por corrente, no estado de repouso, de modo que uma variação do ganho não tem aqui como consequência qualquer perturbação do potencial em repouso. A escolha da forma de realização correspondente do circuito é portanto independente das exigências postas em cada caso pelos circuitos integrados monolíticos, mas muito pouco críticas.

Quando as entradas de sinais indicadas nas figuras com  $+y/-y, +y_1/-y_1$  forem previstas para aplicação de sinais rectangulares, é particularmente vantajoso um circuito multiplicador como o da fig. 2, descrito na reivindicação 1.

Neste caso pode ser suficiente que as fontes de corrente ( $I_{S21}$ ), ( $I_{S22}$ ), ... ( $I_{S31}$ ), ( $I_{S32}$ ), ... sejam formadas como fontes de corrente constantes usuais, que são ligadas ou desligadas em função do nível do sinal a introduzir. Quando se previr como entrada de corrente destas fontes de corrente comandáveis ( $I_{S21}$ ), ... o colector de um transistor ( $tx$ ), cujo emissor está ligado a um outro potencial, em especial o potencial de referência, e simultaneamente ao emissor de um outro transistor ( $Ty$ ), estando o terminal de ligação da base do transistor ( $Tx$ ) ligado ao terminal de ligação da base e ao terminal de ligação do colector do transistor ( $Tx$ ) e fornecendo a entrada de comando desta fonte de corrente e estando esta entrada de comando ligada através de uma resistência ( $R_V$ ) ao potencial de alimentação  $U_V$ , pode, por exemplo, a entrada de comando da fonte de corrente assim constituida ser atacada directamente a partir da saída de uma porta lógica, em especial de uma porta  $I^2L$  ( $G_1$ ), ( $G_2$ ), ...

A fim de obter flancos nítidos do sinal rectangular, pode então aceder-se a um terminal de entrada de inversão  $-y_1$ ,  $-y_2$ , ... com o sinal de saída de uma porta lógica ( $G_1$ ), ( $G_2$ ), ... e um terminal de entrada de não inversão  $+y_1$ ,  $+y_2$ , ... com o sinal de saída inverso deste sinal desta porta lógica ( $G_1$ ), ( $G_2$ ), ...

#### R E I V I N D I C A Ç Õ E S

- 1<sup>a</sup>-

Multiplicador de quatro quadrantes sob a forma de um circuito electrónico integrado monolítico constituído por um primeiro transistor ( $T_1$ ), cujo terminal de ligação do colector está interligado com o terminal de ligação do colector de um terceiro transistor ( $T_3$ ) e, através de uma primeira resistência ( $R_1$ ), está ligado com um potencial de alimentação ( $U_V$ ) e forma um terminal de saída do sinal ( $+z$ ), sendo além disso constituído por um segundo transistor ( $T_2$ ), cujo terminal do colector está interligado com o terminal de

ligaçāo do colector de um quarto transistor (T4) e ligado através de uma segunda resistēcia (R2) com o potencial de alimentação (Uv) formando um outro terminal de saída do sinal (-z), estando o terminal de ligação da base do primeiro transistor (T1) interligado com o terminal de ligação da base do quarto transistor (T4), bem como ao terminal de ligação do colector de um quinto transistor (T5) e ao anodo de um primeiro díodo (D1) estando o terminal de ligação da base do segundo transistor (T2) interligado com o terminal de ligação da base do terceiro transistor (T3) e com o terminal de ligação do colector de um sexto transistor (T6), bem como com o ânodo de um segundo díodo (D2), estando o cátodo do primeiro díodo (D1), juntamente com o cátodo do segundo díodo (D2), ligados através de uma terceira resistēcia ao potencial de alimentação (Uv), estando o terminal de ligação do emissor do quinto transistor (T5) e o do sexto transistor (T6) ligados entre si através de um circuito em série constituído por uma quarta resistēcia (Rx1) e uma quinta resistēcia (Rx2), estando o nō de ligação destas resistēncias (Rx1) e (Rx2) ligado através de uma primeira fonte de corrente (I1) ao potencial de referēcia (massa) e formando o terminal de ligação da base do sexto transistor (T6) o primeiro terminal de entrada (+ x) e o terminal de ligação da base do quinto transistor (T5) e segundo terminal de entrada (-x) do multiplicador, caracterizado por se preverem como primeiro como segundo, como terceiro, e como quarto transistores (T1, T2, T3, T4) transistores com emissores multiplos de construção idêntica, por cada emissor do primeiro transistor (T1) estar ligado com cada emissor do segundo transistor (T2) e com a entrada de corrente de uma fonte de corrente comandável correspondente ( $I_{s21}, I_{s22}, \dots$ ), por a saída de corrente respectiva destas fontes de corrente comandáveis ( $I_{s21}, I_{s22}, \dots$ ) estar ligada ao potencial de referēcia (massa), por as entradas de comando destas fontes de corrente comandáveis ( $I_{s21}, I_{s22}, \dots$ ) serem previstas como terminais de entrada não inversores ( $+y_1, +y_2, \dots$ ), por cada emissor do terceiro transistor (T3) estar interligado com cada um dos emissores respectivo do quarto transistor (T4) e com a entrada de corrente de uma fonte de corrente comandável respectiva ( $I_{s31}, I_{s32}, \dots$ ) por a saída

de corrente respectiva destas fontes de corrente comandáveis ( $I_{S1}, I_{S2}$ ), estar ligada ao potencial de referência (massa) e por as entradas respectivas destas fontes de corrente comandáveis ( $I_{S1}, I_{S2}, \dots$ ) serem previstas como terminais de entrada inversora ( $-y_1, -y_2, \dots$ ).

Multiplicador de quatro quadrantes de acordo com a reivindicação 1, caracterizado por como primeiro, como segundo, como terceiro e como quarto transistores ( $T_1, T_2, T_3, T_4$ ) se preverem transistores com emissores múltiplos de construção idêntica, por cada emissor do primeiro transistor ( $T_1$ ) estar interligado respectivamente com o emissor do segundo transistor ( $T_2$ ) e com o colector de um sétimo ou outros transistores ( $T_{71}, T_{72}, \dots$ ), por cada emissor do terceiro transistor ( $T_3$ ) estar interligado com um emissor respectivo de um oitavo ou outros transistores ( $T_{81}, T_{82}, \dots$ ), por o emissor de cada um dos transistores ( $T_{71}, T_{72}, \dots$ ) ligados com o seu colector a um emissor do primeiro transistor ( $T_1$ ) estar ligado, através de uma resistência de acoplamento respectiva ( $R_{y1}, R_{y2}, \dots$ ), com um emissor respectivo de um transistor ( $T_{81}, T_{82}, \dots$ ) ligado com o seu colector a um emissor respectivo ligados respectivamente com a primeira saída de uma porta  $i^2L$  respectiva ( $G_1, G_2, \dots$ ), por pelo menos todos os terminais de entradas inversoras ( $-y_1, -y_2, \dots$ ) excepto o segundo terminal de entrada ( $-x$ ) estarem ligados com a segunda saída respectiva de uma destas portas  $i^2L$  ( $G_1, G_2, \dots$ ) que conduzem o sinal inverso ao sinal preparado na primeira saída, e por cada uma das entradas destas portas  $i^2L$  ( $G_1, G_2, \dots$ ) ser prevista para ataque por um sinal rectangular referido ao potencial de referência.

A requerente reivindica a prioridade do pedido de Patente Europeia apresentado em 31 de Agosto de 1988, sob o No. 88114225.1.

Lisboa, 30 de Agosto de 1989

**O AGENTE OFICIAL DA PROPRIEDADE INDUSTRIAL**

## R E S U M O

### "MULTIPLICADOR DE QUATRO QUADRANTES COM VÁRIAS ENTRADAS"

Para a multiplicação de vários sinal por um outro sinal igual é utilizado um multiplicador de quatro quadrantes com base no circuito de Gilbert, no qual os transistores dos dois pares de amplificadores diferenciais acoplados de uma entrada comandada, no sentido do circuito de Gilbert, através de trajectos com um diodo e um transistor, no multiplicador interior, são realizados como transistores com emissores multiplos e podendo cada um dos pares de emissores do ramo da direita e do ramo da esquerda do multiplicador ser comandado respectivamente através de uma fonte de corrente comandável ou de um circuito de um transistor ligado em série com uma fonte de corrente, respectivamente, em oposição. Para o processamento de sinais rectangulares, propõe-se a utilização, como fonte de corrente comandável, de uma fonte de corrente comutável que pode em especial ser comandada através de portas  $i^2L$ .

Figura 2

FIG 1

FIG 2

FIG 3