### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-192995 (P2008-192995A)

(43) 公開日 平成20年8月21日(2008.8.21)

| (51) Int.Cl. |            | F 1        |              | テーマコード(参考) |

|--------------|------------|------------|--------------|------------|

| HO1L 27/10   | (2006.01)  | HO1L 27/10 | 451          | 5F083      |

| HO1L 45/00   | (2006.01)  | HO1L 45/0  | $\mathbf{Z}$ |            |

| HO1L 49/00   | (2006, 01) | HO1L 49/0  | $\sim$ $Z$   |            |

審査請求 未請求 請求項の数 19 OL (全 38 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2007-28452 (P2007-28452)<br>平成19年2月7日 (2007.2.7) | (71) 出願人 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地 |

|-----------------------|----------------------------------------------------|------------------------------------------------------|

|                       |                                                    | (74)代理人 100107641                                    |

|                       |                                                    | 弁理士 鎌田 耕一                                            |

|                       |                                                    | (74)代理人 100115152                                    |

|                       |                                                    | 弁理士 黒田 茂                                             |

|                       |                                                    | (72) 発明者 小田川 明弘                                      |

|                       |                                                    | 大阪府門真市大字門真1006番地 松下                                  |

|                       |                                                    | 電器産業株式会社内                                            |

|                       |                                                    | F ターム (参考) 5F083 FZ10 GA11 JA35 JA36 JA37            |

|                       |                                                    | JA38 JA39 JA43 JA60 KA01                             |

|                       |                                                    | MAO5 MAO6 PR40 ZA21                                  |

|                       |                                                    |                                                      |

|                       |                                                    |                                                      |

|                       |                                                    |                                                      |

(54) 【発明の名称】抵抗変化素子とその製造方法ならびにそれを用いた抵抗変化型メモリ

# (57)【要約】

【課題】優れた抵抗変化特性を有するとともに電気抵抗値の保持特性に優れる抵抗変化素子とその製造方法を提供する。

【解決手段】基板と基板上に配置された多層構造体とを含み、多層構造体が、上部電極および下部電極と、上部電極と下部電極との間に配置された抵抗変化層とを含み、上部電極と下部電極との間の電気抵抗値が異なる2以上の状態が存在し、上部電極と下部電極との間に駆動電圧または電流を印加することにより、上記2以上の状態から選ばれる1つの状態から他の状態へと変化する抵抗変化素子であって、抵抗変化層が式M(Fe<sub>2-x</sub>A<sub>x</sub>)0<sub>4</sub>で示される酸化物を含む素子とする。上記式において、MはMn、Co、Ni、CuおよびZnから選ばれる少なくとも1種の元素。AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも1種の元素であってMとは異なる元素。xは式0<x 0.5を満たす数値である。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

基板と、前記基板上に配置された多層構造体とを含み、

前記多層構造体が、上部電極および下部電極と、前記上部電極と前記下部電極との間に配置された抵抗変化層と、を含み、

前記上部電極と前記下部電極との間の電気抵抗値が異なる2以上の状態が存在し、

前記上部電極と前記下部電極との間に駆動電圧または電流を印加することにより、前記

2 以上の状態から選ばれる 1 つの状態から他の状態へと変化する抵抗変化素子であって、前記抵抗変化層が、式 M ( F e 。, 、A 、 ) O 』で示される酸化物を含む抵抗変化素子。

ただし、前記式において、MはMn、Co、Ni、CuおよびZnから選ばれる少なくとも 1 種の元素であり、AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも 1 種の元素であってMとは異なる元素であり、Xは式 0 < X 0 . 5 を満たす数値である。

# 【請求項2】

×が、式0.05 × 0.5を満たす数値である請求項1に記載の抵抗変化素子。

# 【請求項3】

前記抵抗変化層が、前記式で示される第1の酸化物からなる第1の抵抗変化膜と、前記式で示され、前記第1の酸化物とは組成が異なる第2の酸化物からなる第2の抵抗変化膜と、を有する請求項1に記載の抵抗変化素子。

### 【請求項4】

前記第1および第2の抵抗変化膜の膜厚が互いに異なる請求項3に記載の抵抗変化素子

### 【請求項5】

前記第1および第2の抵抗変化膜から選ばれる少なくとも1つの抵抗変化膜が、前記下部電極および前記上部電極から選ばれる少なくとも1つの電極と接している請求項3に記載の抵抗変化素子。

# 【請求項6】

前記第1の抵抗変化膜が前記上部電極に、前記第2の抵抗変化膜が前記下部電極に接している請求項5に記載の抵抗変化素子。

# 【請求項7】

前記抵抗変化層が、FegO<sub>4</sub>からなる抵抗膜を有する請求項1に記載の抵抗変化素子。

# 【請求項8】

前記抵抗変化層が、前記式で示される第1の酸化物からなる第1の抵抗変化膜と、前記式で示され、前記第1の酸化物とは組成が異なる第2の酸化物からなる第2の抵抗変化膜と、を有し、

前記抵抗膜が、前記第1および第2の抵抗変化膜により狭持されている請求項7に記載の抵抗変化素子。

### 【請求項9】

前記抵抗変化層が、前記式で示される酸化物からなる一対の抵抗変化膜を有し、前記抵抗膜が、前記一対の抵抗変化膜により狭持されており、

前記一対の抵抗変化膜の膜厚が互いに異なる請求項7に記載の抵抗変化素子。

#### 【請求項10】

前記一対の抵抗変化膜から選ばれる少なくとも1つの抵抗変化膜が、前記下部電極および前記上部電極から選ばれる少なくとも1つの電極と接している請求項9に記載の抵抗変化素子。

# 【請求項11】

前記抵抗変化層が、当該層の厚さ方向に組成勾配を有する請求項1に記載の抵抗変化素子。

# 【請求項12】

前記基板上に、前記多層構造体が多段に配置されている請求項1に記載の抵抗変化素子

10

20

30

40

【請求項13】

請 求 項 1 ~ 1 2 の い ず れ か に 記 載 の 抵 抗 変 化 素 子 を 備 え る 抵 抗 変 化 型 メ モ リ 。

### 【請求項14】

前記抵抗変化素子に、情報の記録および読出時に前記素子を選択するための選択素子が直列接続されている請求項13に記載の抵抗変化型メモリ。

#### 【請求項15】

請求項1に記載の抵抗変化素子の製造方法であって、

基板上に下部電極を形成する下部電極形成工程と、

前記下部電極上に、式M(Fe<sub>2-x</sub>A<sub>x</sub>)O<sub>4</sub>で示される酸化物を含む抵抗変化層を形成する抵抗変化層形成工程と、

前記抵抗変化層上に、前記下部電極とともに前記抵抗変化層を狭持する上部電極を形成する上部電極形成工程と、を含む抵抗変化素子の製造方法。

ただし、前記式において、MはMn、Co、Ni、CuおよびZnから選ばれる少なくとも 1 種の元素であり、AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも 1 種の元素であってMとは異なる元素であり、Xは式 X0 X1 を満たす数値である。

# 【請求項16】

前記抵抗変化層形成工程において、前記式で示される第1の酸化物からなる第1の抵抗変化膜と、前記式で示され、前記第1の酸化物とは組成が異なる第2の酸化物からなる第 2の抵抗変化膜とを形成して、前記第1および第2の抵抗変化膜を有する抵抗変化層を形成する、請求項15に記載の抵抗変化素子の製造方法。

#### 【請求項17】

前記形成した抵抗変化層を500 以下の温度において熱処理し、当該層の厚さ方向に組成勾配を有する前記抵抗変化層とする、請求項16に記載の抵抗変化素子の製造方法。

### 【請求項18】

前記抵抗変化層形成工程において、室温以上500 以下の温度範囲で成膜温度を変化させながら前記抵抗変化層を形成する、請求項15に記載の抵抗変化素子の製造方法。

# 【請求項19】

前記抵抗変化層形成工程において、前記式で示される酸化物からなる抵抗変化膜と、Fe<sub>3</sub>O<sub>4</sub>からなる抵抗膜とを形成して、前記抵抗変化膜および前記抵抗膜を有する抵抗変化層を形成する、請求項15に記載の抵抗変化素子の製造方法。

【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、駆動電圧または電流の印加により抵抗値が変化する抵抗変化素子と、その製造方法とに関する。本発明は、また、上記抵抗変化素子を用いた抵抗変化型メモリに関する。

#### 【背景技術】

# [0002]

メモリ素子は、情報化社会を支える重要な基幹電子部品として幅広い分野に用いられている。近年、情報携帯端末の普及に伴い、メモリ素子の微細化の要求が高まっているが、DRAMなどの従来のメモリ素子は電荷の蓄積により情報を記録するため、微細化による悪影響を受けやすい。現在、このような悪影響を受けにくいメモリ素子として、電気抵抗値の変化により情報を記録する抵抗変化型メモリ素子が注目されており、このようなメモリ素子として、電圧または電流の印加により電気抵抗値が変化する抵抗変化素子の開発が進められている。

#### [00003]

抵抗変化素子は、通常、抵抗変化層と、抵抗変化層を狭持する一対の電極とを有する。この素子は、電気抵抗値が異なる2以上の状態をとることができ、上記一対の電極間に駆

10

20

30

40

動電圧または駆動電流を印加することにより、上記状態を変化させることができる。素子において選択された 1 つの上記状態は、駆動電圧または電流を再印加するなどの所定の操作が素子に加わらない限り基本的に保持されるため、抵抗変化素子により不揮発性のメモリを構築できる。

# [0004]

抵抗変化素子の電気抵抗値に関する上記現象は、一般に、巨大抵抗変化(CER:Colossal Electro-Resistance)効果と呼ばれる。CER効果には、いわゆる「微細化に伴うサイズの問題」が無く、また、CER効果では非常に大きい抵抗変化が得られることから、抵抗変化素子を、より一層の微細化を実現した次世代の不揮発性メモリ(抵抗変化型ランダムアクセスメモリ:ReRAM)とする期待が高まっている。

[0005]

このような抵抗変化素子として、特許文献1には、スピネル型酸化物であるXFe₂О₄(ただし、Xは、Mn、Fe、Co、Ni、CuおよびZnから選ばれる少なくとも1種の元素)からなる抵抗変化層を有する素子が開示されており、スピネル型酸化物がCER効果の発現に適した材料であることが示されている。また、特許文献2には、化合物A、Bで区分される2種類の元素を含む、スピネル型酸化物を含む各種の酸化物に、遷移金属を5%未満でドープした材料を抵抗変化層に用いた素子が開示されている。

【特許文献1】特開2004-261921号公報

【特許文献2】特表2002-537627号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

不揮発性メモリを構築するためには、優れた抵抗変化特性、例えば高い抵抗変化比、を有するとともに、抵抗値の保持特性に優れる素子であることが重要である。しかし、特許文献1に開示の素子のように、スピネル型酸化物であるXFe<sub>2</sub>O<sub>4</sub>からなる抵抗変化層を有する素子では、十分な保持特性が実現されているとは言えず、その特性向上が求められている。また、特許文献2に開示されているような酸化物に単に遷移金属元素をドープした抵抗変化層では、却って素子の特性が劣化することがある。

[0007]

そこで本発明は、上記従来の抵抗変化素子とは異なる構成を有し、優れた抵抗変化特性を有するとともに電気抵抗値の保持特性に優れる抵抗変化素子と、その製造方法を提供することを目的とする。

【課題を解決するための手段】

[0008]

本発明の抵抗変化素子は、基板と前記基板上に配置された多層構造体とを含み、前記多層構造体は、上部電極および下部電極と、前記上部電極と前記下部電極との間の電気抵抗値が異なる2以上の状態が存在し、前記上部電極と前記下部電極との間に駆動電圧または電流を印加することにより、前記2以上の状態から選ばれる1つの状態から他の状態へと変化する素子である。前記抵抗変化層は、式M(Fe₂--xΑェ)〇₄で示される酸化物を含む。ただし、前記式において、MはMn、Co、Ni、CuおよびZnから選ばれる少なくとも1種の元素であり、AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも1種の元素であり、AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも1種の元素であってMとは異なる元素であり、xは式0<×0.5を満たす数値である。

[0009]

本発明の抵抗変化型メモリは、上記本発明の抵抗変化素子を備える。

[0010]

本発明の抵抗変化素子の製造方法は、上記本発明の抵抗変化素子の製造方法であって、基板上に下部電極を形成する下部電極形成工程と、前記下部電極上に、式M(Fe<sub>2-x</sub>A<sub>x</sub>)O<sub>4</sub>で示される酸化物を含む抵抗変化層を形成する抵抗変化層形成工程と、前記抵抗変

10

20

30

40

化層上に、前記下部電極とともに前記抵抗変化層を狭持する上部電極を形成する上部電極形成工程とを含む。ただし、前記式において、MはMn、Co、Ni、CuおよびZnから選ばれる少なくとも1種の元素であり、AはTi、V、Nb、Ta、Cr、Mn、CoおよびRhから選ばれる少なくとも1種の元素であってMとは異なる元素であり、×は式0<x0.5を満たす数値である。

# 【発明の効果】

#### [0011]

本発明の抵抗変化素子は、単なるスピネル型酸化物からなる抵抗変化層、あるいは、スピネル型酸化物に遷移金属元素を単にドープした材料からなる抵抗変化層を有する従来の素子とは異なり、優れた抵抗変化特性を有するとともに電気抵抗値の保持特性に優れる。

[0012]

また、このような素子を備える本発明の抵抗変化型メモリは、不揮発性に優れ、安定したメモリ特性を有する。

【発明を実施するための最良の形態】

### [0013]

以下、図面を参照しながら、本発明の実施の形態について説明する。以下の説明において、同一の部材に同一の符号を付して、重複する説明を省略する場合がある。

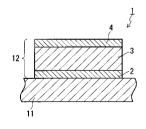

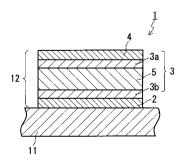

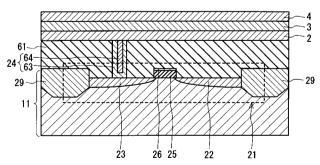

#### [0014]

「抵抗変化素子]

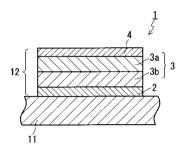

図1に示す抵抗変化素子1は、基板11と、下部電極2および上部電極4からなる一対の電極と、下部電極2および上部電極4により狭持された抵抗変化層3とを備える。下部電極2、抵抗変化層3および上部電極4は、多層構造体(積層体)12として上記順に基板11上に配置されている。

[0015]

抵抗変化層 3 は、抵抗変化材料として式 M ( F  $e_{2-x}$   $A_x$ )  $O_4$  で示される酸化物を含む。ただし、上記式において、M は M n、C o、N i、C u および Z n から選ばれる少なくとも 1 種の元素であり、A は T i、V、N b、T a、C r、M n、C o および R h から選ばれる少なくとも 1 種の元素であって M とは異なる元素であり、X は式 0 < X X 0 . 5 を満たす数値である。

[0016]

素子1には、抵抗変化層3の電気抵抗値、即ち、下部電極2と上部電極4との間の電気抵抗値、が異なる2以上の状態が存在する。駆動電圧または電流を抵抗変化層3に、具体的には下部電極2と上部電極4との間に、印加することにより、素子1は、上記2以上の状態から選ばれる1つの状態から他の状態へと変化する。素子1に電気抵抗値が異なる2つの状態(相対的に高抵抗である高抵抗状態、および、相対的に低抵抗である低抵抗状態)が存在する場合、駆動電圧または電流の印加により、素子1は、高抵抗状態から低抵抗状態へ、あるいは、低抵抗状態から高抵抗状態へと変化する。

[0017]

このような素子 1 は、単なるスピネル型酸化物からなる抵抗変化層、あるいは、スピネル型酸化物に遷移金属元素を単にドープした材料からなる抵抗変化層を有する従来の素子とは異なり、優れた抵抗変化特性、例えば高い抵抗変化比、を有するとともに、その電気抵抗値の保持特性に優れている。なお、抵抗変化比とは、素子の抵抗変化特性の指標となる数値であり、素子が示す最大電気抵抗値を $R_{MAX}$ 、最小電気抵抗値を $R_{MIN}$ としたときに、式( $R_{MAX}$  -  $R_{MIN}$ )/  $R_{MIN}$ により求められる値である。

[ 0 0 1 8 ]

このような効果が得られる原理は未だ明確ではないが、上記酸化物における元素Mおよび元素Aが取り得るイオンの価数が影響を与えている可能性がある。

#### [0019]

例えば、元素 M が F e である F e ( F e )  $_2$  O  $_4$  酸化物の場合、当該酸化物はイオン価数による表記では F e  $^{3+}$  ( F e  $^{2+}$  , F e  $^{3+}$  ) ( O  $^{2-}$  )  $_4$  と書き下せるが、この状態から抵抗

10

20

30

40

変化を引き起こす電子の取り出しを行うと、 $Fe^{2+}$ が $Fe^{3+}$ になるともに電荷中性化が進んで、イオン価数による表記では $Fe^{3+}$ ( $Fe^{3+}$ )( $O^{2-}$ ) $_4$ と書き下せる $Fe_{2.67}$  $O_4$ ( $=Fe_2O_3$ )への変化が起こる。このとき、電荷中性化に際して酸素イオンの移動が起こると考えられる。つまり、このCER効果による抵抗変化は、Feイオン価数に影響を与える電子の移動と、酸素イオンの移動との 2 つの機構が関与して引き起こされていると考えられる。良好な保持特性の確保には、熱的な安定性が必須であるが、もともと酸素イオン移動を伴うCER効果では、高温にて容易に酸素イオンが移動することから、抵抗変化層 3、即ち、素子 1 としての電気抵抗値の保持特性の劣化が生じ易いと考えられる

# [0020]

また例えば、元素MがZnであるZn(Fe) $_2$ O $_4$ 酸化物の場合、当該酸化物はイオン価数による表記ではZn $^{2+}$ (Fe $^{3+}$ ,Fe $^{3+}$ )( $O^{2-}$ ) $_4$ と書き下せるが、この状態から抵抗変化を引き起こす電子の取り出しを行おうとしても、当該酸化物には価数配置を変更できるサイトが存在しないため、抵抗変化自体を起こすことが困難であると考えられる。また価数の変動が殆ど無いため、酸素量の変動もあまりないと考えられる。ただし、実際には、Zn(Fe) $_2$ O $_4$ 酸化物からなる抵抗変化層とした場合においても、その元素配置の揺らぎなどに起因する小さな抵抗変化比が得られることがある。

#### [0021]

#### [0022]

この原理によれば、 $MFe_2O_4$ におけるFeを置換する元素Aには、Feが 2 価および 3 価の価数配置をとることに起因する酸素イオンの移動を抑制するための適切な価数配置が存在する。本発明では、元素A は、T i、V 、N b 、T a 、C r 、M n 、C o およびR h から選ばれる少なくとも 1 種であり、これらの元素は、イオン価数として 3 価および 4 価(あるいは 5 価)をとることができるため、上記効果が得られると考えられる。

# [ 0 0 2 3 ]

上記酸化物における元素Mと元素Aとの組み合わせは特に限定されない。例えば、以下のような組み合わせが考えられる。元素MがZnであり、元素AがCr、Nb、MnおよびCoから選ばれる少なくとも1種、より好ましくはCr、である;このとき、保持特性により優れる素子1とすることができる。あるいは、元素MがCuであり、元素AがMnである;このとき、保持特性により優れる素子1とすることができる。

#### [0024]

これらの組み合わせの具体的な組成の一例として、Z n (F  $e_{1.8}$  C  $r_{0.2}$ )  $O_4$ 、あるいは、C u (F  $e_{1.6}$  M  $n_{0.4}$ )  $O_4$ を挙げることができる。

# [0025]

上記酸化物は式 M ( F e  $_{2-x}$  A  $_x$  ) O  $_4$  を満たす組成を有していればよく、この式において、 x は、式 0 < x 0 . 5 を満たす数値であり、式 0 . 0 5 x 0 . 5 を満たす数値であることが好ましい。また、元素 M と元素 A との組み合わせによっても異なるが、 x は、式 0 . 2 x 0 . 4 を満たす数値であることがより好ましい。

#### [0026]

抵抗変化層3の構成は、上記酸化物を含む限り特に限定されない。例えば、上記式で示される1種類の酸化物からなる抵抗変化層3であってもよい。また例えば、抵抗変化層3

10

20

30

40

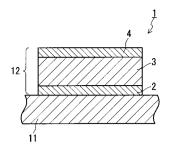

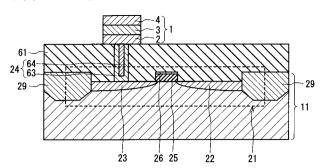

が、上記式で示される酸化物であって、互いに組成が異なる酸化物を2以上の種類含んでいてもよい。このような抵抗変化層3を含む本発明の素子1の一例を図2に示す。

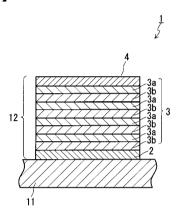

# [0027]

図2に示す素子1は、図1に示す素子1と同様に、基板11と、下部電極2および上部電極4からなる一対の電極と、下部電極2および上部電極4により狭持された抵抗変化層3とを備える。ここで抵抗変化層3は、上記式で示される第1の酸化物からなる第1の抵抗変化膜3aと、上記式で示され、第1の酸化物とは組成が異なる第2の酸化物からなる第2の抵抗変化膜3bとを有する。

# [0028]

抵抗変化膜3aと3bとでは、その組成が異なるために、膜としての電気抵抗値が互いに異なる。このような抵抗変化層3a、3bを有する抵抗変化層3では、当該層へ駆動電圧または電流を印加した際に、抵抗値が相対的に高い抵抗変化膜への分配電圧を高くでき、素子1としての抵抗変化の制御がより容易となる。

# [0029]

なお、第1の酸化物を式 M( $Fe_{2-x}A_x$ ) $O_4$ により示した場合、第2の酸化物は、式 M( $Fe_{2-y}A_y$ ) $O_4$ (ただし、y は、式 0 < y 0 . 5 および式 y x を満たす数値)により示すことができる。例えば、第1および第2の酸化物の具体的な組成の一例として、 Z n ( $Fe_{1.8}C$   $r_{0.2}$ ) $O_4$  / Z n ( $Fe_{1.5}C$   $r_{0.5}$ ) $O_4$ 、あるいは、C u ( $Fe_{1.6}M$   $n_{0.4}$ ) $O_4$  / C u ( $Fe_{1.8}M$   $n_{0.2}$ ) $O_4$ などを挙げることができる。その他の具体的な組成の例は、実施例に後述する。

#### [0030]

図2に示す例では、第1の抵抗変化膜3 a が上部電極4 側に、第2の抵抗変化膜3 b が下部電極2 側に配置されているが、双方の抵抗変化膜の上記一対の電極に対する配置は逆であってもよい。なお、本発明の素子における「下部電極」および「上部電極」の「下部」および「上部」は、抵抗変化層3を狭持する一対の電極のそれぞれを区別するために便宜的に付けた名称であり、物理的な上下関係を意味しない。

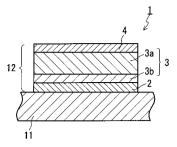

# [0031]

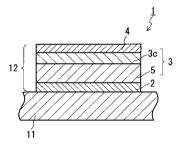

図2に示す例では、第1の抵抗変化膜3aの膜厚と、第2の抵抗変化膜3bの膜厚とがほぼ等しいが、図3に示すように、抵抗変化層3が有する第1の抵抗変化膜3aの膜厚と、第2の抵抗変化膜3bの膜厚とが互いに異なっていてもよい。この場合、抵抗変化層3へ駆動電圧または電流を印加した際に、双方の膜への分配電圧を互いに異なる状態にでき、素子1としての抵抗変化の制御がより容易となる。

#### [0032]

抵抗変化層3が第1の抵抗変化膜および第2の抵抗変化膜を有する場合、第1の抵抗変化膜および第2の抵抗変化膜から選ばれる少なくとも1つの抵抗変化膜が、下部電極2および上部電極4から選ばれる少なくとも1つの電極に接していることが好ましい。このとき、素子1における抵抗変化をより容易に起こすことができる。

### [0033]

抵抗変化層 3 が第 1 の抵抗変化膜および第 2 の抵抗変化膜を有する場合、第 1 および第 2 の抵抗変化膜のいずれもが下部電極または上部電極と接していること、即ち、第 1 の抵抗変化膜が上部(下部)電極と接し、第 2 の抵抗変化膜が下部(上部)電極と接していること、がより好ましい。このとき、下部電極 2 に接する抵抗変化膜と、上部電極 4 に接する抵抗変化膜とは、互いに異なる組成を有する上記酸化物からなる、ともいえる。図 2 、3 に示す例では、第 1 の抵抗変化膜 3 a が上部電極 4 に、第 2 の抵抗変化膜 3 b が下部電極 2 に接している。

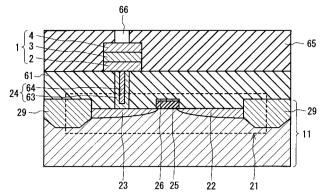

# [0034]

抵抗変化層 3 が第 1 の抵抗変化膜および第 2 の抵抗変化膜を有する場合、それぞれの膜の数は特に限定されず、例えば、図 4 に示すように、 2 以上の抵抗変化膜 3 a および 3 b を有する抵抗変化層 3 であってもよい。なお、この場合においても、抵抗変化膜 3 a および 3 b のいずれもが、下部電極または上部電極と接していることが好ましい。図 4 に示す

10

20

30

40

例では、第1の抵抗変化膜3aが上部電極4に、第2の抵抗変化膜3bが下部電極2に接している。

# [0035]

抵抗変化層3が第1および第2の抵抗変化膜を有する場合、抵抗変化層3が有する抵抗変化膜の種類は第1および第2の抵抗変化膜の2種類に限定されない。例えば、抵抗変化層3は、上記式で示される酸化物であって、第1および第2の酸化物とは異なる組成を有する酸化物からなる抵抗変化膜をさらに含んでいてもよい。

### [0036]

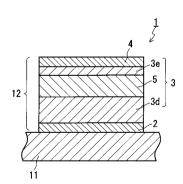

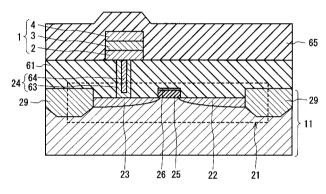

本発明の素子の抵抗変化層 3 は、上記酸化物以外の材料を含んでいてもよく、例えば、上記酸化物以外の材料からなる膜を有していてもよい。より具体的には、例えば、抵抗変化層 3 は、 F e 3 O 4 からなる抵抗膜を有していてもよい。

#### [0037]

図 5 に、抵抗膜を有する抵抗変化層 3 を含む本発明の素子の一例を示す。図 5 に示す素子 1 は、図 1 に示す素子 1 と同様に、基板 1 1 と、下部電極 2 および上部電極 4 からなる一対の電極と、下部電極 2 および上部電極 4 により狭持された抵抗変化層 3 とを備える。ここで抵抗変化層 3 は、上記式で示される酸化物からなる抵抗変化膜 3 c と、Fe<sub>3</sub>O<sub>4</sub>からなる抵抗膜 5 とを有する。

# [0038]

図 5 に示す素子 1 では、抵抗変化層 3 が抵抗膜 5 を有することにより、素子 1 の初期抵抗値の設計の自由度を高くできる。なお、素子 1 の初期抵抗値の値を変化させるためには、例えば、抵抗変化膜 3 c と抵抗膜 5 との膜厚を調整すればよい。

#### [0039]

また、抵抗変化層 3 が抵抗膜 5 を有する場合、抵抗変化層 3 のプロセス加工上の自由度を高くできる。例えば、抵抗変化材料のみからなる数 n m の膜厚の抵抗変化層を形成するのにはプロセス加工上の困難さを伴うが、抵抗膜を加えることで抵抗変化層としての膜厚を増大でき、このような困難さを低減させることができる。

# [0040]

Fe<sub>3</sub>O<sub>4</sub>からなる抵抗膜 5 は、バルク抵抗率が数m ・ c m ~ 数十m ・ c m と比較的小さいため、このような効果をより確実に得ることができる。

#### [0041]

なお、 $Fe_3O_4$ はスピネル型酸化物であり、いわゆる抵抗変化材料の 1 種であるが、本発明の素子では、駆動電圧または電流の印加によってもその電気抵抗値がほぼ変化しない抵抗膜として扱うことができる。これは、駆動電圧または電流の印加時に、抵抗変化層を構成する、上記式 M ( $Fe_{2-x}A_x$ ) $O_4$ で示される酸化物からなる抵抗変化膜に主体的に電圧が印加される、即ち、抵抗変化が M ( $Fe_{2-x}A_x$ ) $O_4$ 膜に優先的に引き起こされることによると考えられる。

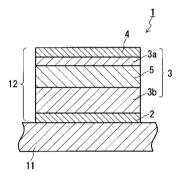

# [0042]

図 6 に、抵抗膜を有する抵抗変化層を含む本発明の素子の別の一例を示す。図 6 に示す素子 1 では、抵抗変化層 3 は、上記式で示される第 1 の酸化物からなる第 1 の抵抗変化膜 3 a と、上記式で示され、第 1 の酸化物とは組成が異なる第 2 の酸化物からなる第 2 の抵抗変化膜 3 b と、Fe<sub>3</sub>O<sub>4</sub>からなる抵抗膜 5 とを有する。このように、抵抗変化層 3 は、上記式で示される酸化物であって、互いに組成が異なる酸化物を 2 以上の種類と、上記酸化物以外の材料とを含んでいてもよい。

# [0043]

このように抵抗変化層 3 が抵抗膜 5 を有する場合においても、抵抗変化層 3 は上述した第 1 の抵抗変化膜 3 a および第 2 の抵抗変化膜 3 b を有してもよく、このとき、抵抗変化層 3 が有する双方の抵抗変化膜に対しては上述した説明を適用できる。

#### [0044]

例えば、第1の抵抗変化膜および第2の抵抗変化膜から選ばれる少なくとも1つの抵抗 変化膜が、下部電極2および上部電極4から選ばれる少なくとも1つの電極に接している 10

20

30

40

ことが好ましく、第1および第2の抵抗変化膜のいずれもが下部電極または上部電極と接していること、即ち、第1の抵抗変化膜が上部(下部)電極と接し、第2の抵抗変化膜が下部(上部)電極と接していること、がより好ましい。図6に示す例では、第1の抵抗変化膜3aが上部電極4に、第2の抵抗変化膜3bが下部電極2に接している。このとき、抵抗膜5は、抵抗変化膜3aおよび3bに狭持された状態にある。

## [0045]

換言すれば、図 6 に示す素子 1 では、抵抗変化層 3 が、上記式で示される第 1 の酸化物からなる第 1 の抵抗変化膜 3 a と、第 1 の酸化物とは組成が異なる第 2 の酸化物からなる第 2 の抵抗変化膜 3 b と、Fe<sub>3</sub>O<sub>4</sub>からなる抵抗膜 5 とを有し、抵抗膜 5 が、第 1 および第 2 の抵抗変化膜 3 a および 3 b により狭持されている。

[0046]

また例えば、図7に示す素子1のように、第1の抵抗変化膜3aの膜厚と、第2の抵抗変化膜3bの膜厚とが互いに異なっていてもよい。図7に示す素子1は、抵抗変化膜3aおよび3bの膜厚が互いに異なる以外は、図6に示す素子1と同様の構造を有する。

### [0047]

図8に、抵抗膜を有する抵抗変化層を含む本発明の素子のまた別の一例を示す。図8に示す素子1では、抵抗変化層3は、 $Fe_3O_4$ からなる抵抗膜5と、上記式で示される酸化物からなる一対の抵抗変化膜3d、3eと、を有する。抵抗膜5は、抵抗変化膜3d、3eにより狭持されている。抵抗変化膜3d、3eは、その組成は互いに同一であるが、その膜厚は互いに異なっている。

[ 0 0 4 8 ]

このような素子1においても、抵抗変化層3へ駆動電圧または電流を印加した際に、双方の抵抗変化膜への分配電圧を互いに異なる状態にでき、素子1としての抵抗変化の制御がより容易となる。

#### [0049]

抵抗変化層3が上記一対の抵抗変化膜3d、3eを有する場合、当該一対の抵抗変化膜から選ばれる少なくとも1つの抵抗変化膜が、下部電極2および上部電極4から選ばれる少なくとも1つの電極に接していることが好ましい。このとき、素子1における抵抗変化をより容易に起こすことができる。

[0050]

抵抗変化層3が上記一対の抵抗変化膜3d、3eを有する場合、双方の抵抗変化膜のいずれもが下部電極または上部電極と接していることがより好ましい。

[0051]

抵抗変化層3が上記一対の抵抗変化膜3d、3eを有する場合、抵抗変化層3が有する抵抗変化膜の種類は当該一対の抵抗変化膜に限定されない。例えば、抵抗変化層3は、上記式で示される酸化物からなる、抵抗変化膜3d、3eとは異なる組成を有する抵抗変化膜をさらに含んでいてもよい。

[0052]

本発明の抵抗変化素子では、抵抗変化層が、当該層の厚さ方向に組成勾配を有していて もよい。組成勾配は連続的であっても、段階的であってもよく、その構成によっては、素 子の抵抗変化特性および / または保持特性をより向上できる。また、このような組成勾配 を有する素子は、例えば、後述する本発明の製造方法により形成できる。

[0053]

本発明の抵抗変化素子では、下部電極 2 、抵抗変化層 3 および上部電極 4 を含む多層構造体 1 2 が、基板 1 1 上に多段に配置されていてもよい。この場合、素子 1 を多値化できる。

[0054]

下部電極 2 は、基本的に導電性を有していればよく、例えば、 A u (金)、 P t (白金)、 R u (ルテニウム)、 I r (イリジウム)、 T i (チタン)、 A l (アルミニウム)、 C u (銅)、 T a (タンタル)、 I r - T a (イリジウム - タンタル合金)、スズ添加

10

20

30

40

インジウム酸化物(ITO)など、あるいは、これらの合金、酸化物、窒化物、弗化物、炭化物、硼化物、シリサイドなどからなればよい。半導体製造プロセスとの親和性の観点からは、下部電極2が、Ir、Ru、Ir-O(酸化イリジウム)、Ru-O(酸化ルテニウム)、Ti、A1、Ti-A1合金、あるいは、これらの窒化物などからなることが好ましい。下部電極2は、上述した材料から選ばれる2以上の異なる材料の積層体からなってもよく、例えば、Ir-OとTi-A1-N(窒化チタンアルミニウム)との積層体などであってもよい。なお、Ti-A1-Nを用いる場合には、その導電性を確保するために、A1比、即ち、Ti+A1の総量に対するA1の量の比が50原子%以下であることが好ましい。

# [0055]

上部電極4は、基本的に導電性を有していればよく、例えば、Au、Pt、Ru、Ir、Ti、Al、Cu、Ta、Re(レニウム)、Os(オスミウム)、Rh(ロジウム)、Ir-Ta、ITOなど、あるいは、これらの合金、酸化物、窒化物、弗化物、炭化物、硼化物などからなればよい。半導体製造プロセスとの親和性の観点からは、上部電極4が、酸化されにくい材料、または、酸化後も導電性を保持できる材料からなることが好ましく、例えば、Ir、Ru、Re、Os、Rh、Pt、Auなどからなることが好ましい。同様の理由から、上部電極4が、Ir-O、Ru-O、Re-O(酸化レニウム)、Os-O(酸化オスミウム)、Rh-O(酸化ロジウム)などの酸化物からなることが好ましく、また、Ti-N(窒化チタン)、Fe-N(窒化鉄)、Ti-A1-Nなどの窒化物からなることが好ましい。上部電極4は、上述した材料から選ばれる2以上の異なる材料の積層体からなってもよい。なお、Ti-A1-Nを用いる場合には、その導電性を確保するために、A1比が50原子%以下であることが好ましい。

#### [0056]

下部電極2および上部電極4は、非磁性体であってもよい。

#### [0057]

基板11は、例えば半導体基板、典型的にはシリコン(Si)基板であればよく、この場合、本発明の抵抗変化素子と半導体素子とを組み合わせが容易となり、例えば、同一基板上に本発明の素子と半導体素子とを形成できる。基板11における下部電極2に接する表面が酸化されていてもよく、基板11の表面に酸化膜が形成されていてもよい。なお、本明細書における「基板」には、トランジスタあるいはコンタクトプラグなどが形成された基板も含まれる。

# [0058]

駆動電圧または電流は、下部電極2および上部電極4を介して素子1に印加すればよい。駆動電圧または電流の印加により、素子1における上記状態が、例えば、高抵抗状態から低抵抗状態へと変化するが、変化後の状態は、素子1に駆動電圧または電流が再び印加されるまで保持される。素子1の上記状態は、駆動電圧または電流を素子1に印加することにより、再び変化させる(例えば、低抵抗状態から高抵抗状態へ)ことができる。

### [0059]

素子1に印加する駆動電圧または電流は、素子1が高抵抗状態にあるときと、低抵抗状態にあるときとの間で必ずしも同一でなくてもよく、その大きさ、印加方向などは、素子1の状態により異なっていてもよい。即ち、本明細書における「駆動電圧または電流」とは、素子1がある状態にあるときに、当該状態とは異なる他の状態へと変化できる「電圧または電流」であればよい。

# [0060]

このように素子1では、特定の電気抵抗値を示す素子の状態を、素子1に駆動電圧または電流を印加するまで保持できる。このため、素子1と、素子1における上記状態を検出する機構(即ち、素子1の電気抵抗値を検出する機構)とを組み合わせることにより、不揮発性の抵抗変化型メモリを構築できる。2以上の素子1を用いることにより、2以上のメモリ素子が配列したメモリアレイの構築も可能である。このメモリでは、素子1の上記各状態に対してビット、例えば、高抵抗状態に対して「0」を、低抵抗状態に対して「1

10

20

30

40

」を割り当てればよい。素子1の上記状態の変化は少なくとも2回以上繰り返して行うことができるため、信頼性のある不揮発性ランダムアクセスメモリを得ることもできる。また、素子1の上記各状態に対して「ON」または「OFF」を割り当てることにより、素子1をスイッチング素子へ応用することも可能である。

# [0061]

素子1に印加する駆動電圧または電流は、パルス状であることが好ましい。駆動電圧(駆動電流)をパルス状とすることにより、素子1を用いて構築したメモリなどのデバイスにおける消費電力の低減やスイッチング効率の向上を図ることができる。パルスの形状は、特に限定されず、例えば、正弦波状、矩形波状および三角波状から選ばれる少なくとも1つの形状であってもよい。パルスの幅は、通常、数ナノ秒~数ミリ秒程度の範囲であればよい。

[0062]

デバイスの駆動をより簡便に行うためには、パルスの形状が三角波状であることが好ましい。素子1の応答をより高速にするためには、パルスの形状が矩形波状であることが好ましく、この場合、数ナノ秒~数マイクロ秒程度の応答を図ることができる。簡便な駆動、消費電力の低減、および、早い応答速度などを達成するためには、パルスの形状が、正弦波状、あるいは、矩形波状の立ち上がり部/立ち下がり部に適度なスロープを設けた台形状であることが好ましい。正弦波状や台形状のパルスは、素子1の応答速度を、数十ナノ秒~数百マイクロ秒程度とする場合に適しており、三角波状のパルスは、素子1の応答速度を、数十マイクロ秒~数ミリ秒程度とする場合に適している。

[0063]

素子1には電圧を印加することが好ましく、この場合、素子1の微細化や、素子1を用いて構築したデバイスの小型化がより容易となる。電気抵抗値に関する2つの状態が存在する素子1の場合、下部電極2と上部電極4との間に電位差を発生させる電位差印加機構を素子1に接続し、下部電極2の電位に対して上部電極4の電位が正となるようなバイアス電圧(正バイアス電圧)を素子1に印加することにより、例えば、素子1を高抵抗状態から低抵抗状態へと変化させ、下部電極2の電位に対して上部電極4の電位が負となるようなバイアス電圧(負バイアス電圧)を素子1に印加することにより(即ち、先ほどとは極性を反転させた電圧を印加することにより)、例えば、素子1を低抵抗状態から高抵抗状態へと変化させてもよい。電位差印加機構としては、例えば、パルスジェネレータが挙げられる。

[0064]

本発明の抵抗変化素子は、下部電極、抵抗変化層および上部電極以外の任意の層を含んでいてもよい。

[0065]

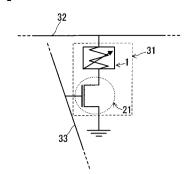

「抵抗変化型メモリー

本発明の抵抗変化素子を、半導体素子、例えば、ダイオード、あるいは、MOS電界効果トランジスタ(MOS-FET)などのトランジスタなど、と組み合わせることにより、抵抗変化型メモリを構築できる。

[0066]

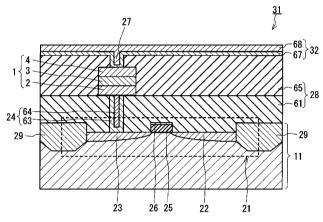

本発明の抵抗変化素子とMOS-FETとを組み合わせた、抵抗変化型メモリ(メモリ素子)の一例を図9に示す。

[0067]

図9に示す抵抗変化型メモリ素子31は、抵抗変化素子1とトランジスタ21とを備えており、素子1は、トランジスタ21およびビット線32と電気的に接続されている。トランジスタ21のゲート電極はワード線33に電気的に接続されており、トランジスタ21の残る1つの電極は接地されている。このようなメモリ素子31では、トランジスタ21をスイッチング素子として、素子1における上記状態の検出(即ち、素子1の電気抵抗値の検出)、および、素子1への駆動電圧または電流の印加が可能となる。例えば、素子1が、電気抵抗値が異なる2つの状態をとる場合、図9に示すメモリ素子31を、1ビッ

10

20

30

40

トの抵抗変化型メモリ素子とすることができる。

[0068]

トランジスタ21は、例えば、MOS-FETとして一般的な構成であればよい。

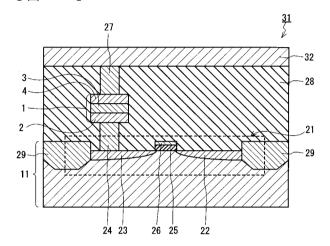

[0069]

本発明の抵抗変化型メモリ(メモリ素子)の具体的な構成の一例を図10に示す。図10に示すメモリ素子31では、トランジスタ21が形成された基板11上に抵抗変化素子1が形成されており、素子1とトランジスタ21とが一体化されている。

[0070]

以下、図10のメモリ素子31の構成を具体的に説明する。基板11にはソース電極22およびドレイン電極23が形成されており、ドレイン電極23は、プラグ24を介して素子1の下部電極2と電気的に接続されている。ソース電極22は、図示していないが、別途、接地電位などに接続されていればよい。基板11におけるソース電極22とドレイン電極23との間には、ゲート絶縁膜25およびゲート電極26が形成されている。素イ1の下部電極2上には、抵抗変化層3および上部電極4が上記順に積層されている。ゲート電極26は、ワード線(図示せず)と電気的に接続され、上部電極4はプラグ27を介してビット線32と電気的に接続されている。基板11上には、基板11の表面、ならびに、トランジスタ21および素子1の全体を覆うように層間絶縁層28が配置されており、層間絶縁層28によって、各電極間における電気的なリークの発生が防止されている。なお、基板11上の符号29で示された部分は、素子分離部29である。

[0071]

層間絶縁層 28 は、 $SiO_2$ や  $A1_2O_3$ などの絶縁材料からなればよく、2 以上の種類の材料の積層体であってもよい。絶縁材料には、 $SiO_2$ や  $A1_2O_3$ などの無機材料の他、レジスト材料のような有機材料を用いてもよい。絶縁材料に有機材料を用いた場合、平坦でない表面上に層間絶縁層 28 を形成する場合においても、スピナーコーティング法などを用いることによって、自らの表面が平坦な層間絶縁層 28 を容易に形成できる。有機材料としては、例えば、感光性樹脂であるポリイミドのような材料が好ましい。

[0072]

図10に示す例では、抵抗変化素子とMOS-FETとを組み合わせることにより抵抗変化型メモリ素子が構築されているが、本発明の抵抗変化型メモリの構成は図10に示す例に限定されず、例えば、本発明の抵抗変化素子と、情報の記録および読出時に素子を選択するための選択素子として、その他の種類のトランジスタやダイオードなど、任意の半導体素子とを組み合わせてもよい。このとき、本発明の抵抗変化素子と選択素子とが直列接続されていることが好ましい。

[0073]

また、図10に示すメモリ素子31では、トランジスタ21の直上に抵抗変化素子1が配置されているが、トランジスタ21と抵抗変化素子1とを互いに離れた場所に配置し、下部電極2とドレイン23とを引き出し電極により電気的に接続してもよい。メモリ素子31の製造プロセスを容易にするためには、素子1とトランジスタ21とを互いに離して配置することが好ましい。一方、図10に示すように、トランジスタ21の直上に素子1を配置することにより、メモリ素子31の占有面積を小さくでき、より高密度な抵抗変化型メモリアレイを実現できる。

[0074]

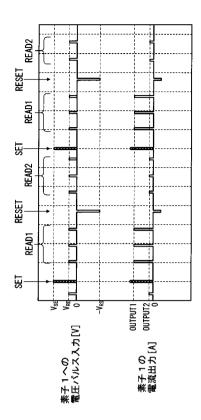

メモリ素子31への情報の記録は、素子1への駆動電圧または電流の印加により行えばよく、素子1に記録した情報の読出は、例えば、情報の記録時とは異なる大きさの電圧(電流)を素子1に印加することにより行えばよい。情報の記録および読出方法として、パルス状の電圧を素子1に印加する方法の一例について、図11を用いて説明する。

[0075]

図11に示す例では、抵抗変化素子1は、ある閾値(V。)以上の大きさを有する正バイアス電圧の印加により、高抵抗状態から低抵抗状態へと変化し、ある閾値(V。・)以上の大きさを有する負バイアス電圧の印加により、低抵抗状態から高抵抗状態へと変化す

10

20

30

40

10

20

30

40

50

る抵抗変化特性を有する。各バイアス電圧の大きさは、下部電極 2 と上部電極 4 との間の電位差の大きさに相当する。

# [0076]

抵抗変化素子1の初期状態が、高抵抗状態であるとする。下部電極2と上部電極4との間にパルス状の正バイアス電圧 $V_{SE}(\mid V_{SE}\mid V_0)$ を印加すると、素子1は高抵抗状態から低抵抗状態へと変化する(図11に示すSET)。このとき印加する正バイアス電圧をSET電圧とする。

# [0077]

ここで、SET電圧よりも小さく、大きさが $V_0$ 未満の正バイアス電圧を素子1に印加することにより、素子1の電気抵抗値を、素子1の電流出力として検出できる(図11に示すREAD1およびOUTPUT1)。素子1の電気抵抗値の検出は、素子1に、大きさが $V_0$ ・未満の負バイアス電圧を印加することによっても行うことができ、これら、素子1の電気抵抗値を検出するために印加する電圧をREAD電圧( $V_{RE}$ )とする。READ電圧は、図11に示すようにパルス状であってもよく、この場合、SET電圧をパルス状とした時と同様に、メモリ素子31における消費電力の低減やスイッチング効率の向上を図ることができる。READ電圧の印加では、素子1の状態は変化しないため、複数回READ電圧を印加した場合においても、同一の電気抵抗値を検出できる。

# [0078]

次に、下部電極 2 と上部電極 4 との間にパルス状の負バイアス電圧  $V_{RS}(\ |\ V_{RS}|\ V_0$  )を印加すると、素子 1 は低抵抗状態から高抵抗状態へと変化する(図 1 1 に示す R E S E T )。このとき印加する負バイアス電圧を R E S E T 電圧とする。

#### [0079]

ここで、素子1にREAD電圧を印加すれば、素子1の電気抵抗値を、素子1の電流出力として検出できる(図11に示すREAD2およびOUTPUT2)。この場合も、READ電圧の印加では、素子1の状態は変化しないため、複数回READ電圧を印加した場合においても、同一の電気抵抗値を検出できる。

#### [0800]

このように、パルス状の電圧の印加により、素子1を備えるメモリ素子31への情報の記録および読出を行うことができる。読出によって得られる素子1の出力電流の大きさは、素子1の状態に対応して異なる。ここで、相対的に出力電流の大きい状態(図11におけるOUTPUT1)を「1」、相対的に出力電流の小さい状態(図11におけるOUTPUT2)を「0」とすれば、メモリ素子31を、SET電圧により情報「1」が記録され、RESET電圧により情報「0」が記録される(情報「1」が消去される)メモリ素子とすることができる。

# [0081]

図10に示すメモリ素子31において、抵抗変化素子1にパルス状の電圧を印加するためには、ワード線によりトランジスタ21をON状態とし、ビット線32を介して電圧を印加すればよい。

# [0082]

R E A D電圧の大きさは、S E T電圧およびR E S E T電圧の大きさに対して、通常、 $1/2 \sim 1/1000$ 程度の範囲にあることが好ましい。S E T電圧およびR E S E T電圧の具体的な値は、抵抗変化素子1の構成にもよるが、通常、 $0.1V \sim 10V$ 程度の範囲であり、 $1V \sim 5V$ 程度の範囲が好ましい。

# [0083]

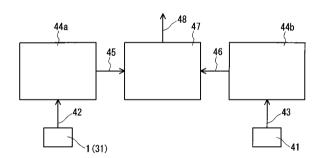

素子1、即ち、メモリ素子31の電気抵抗値は、素子1(31)の抵抗値(または出力電流値)と、参照素子の参照抵抗値(または参照出力電流値)との差分に基づいて算出することが好ましい。参照抵抗値は、例えば、検出する素子とは別に参照素子を準備し、参照素子に対しても素子1(31)と同様にREAD電圧を印加して得ることができる。このような方法により素子1(31)の電気抵抗値を得るための回路の構成の一例を図12に示す。

10

20

30

40

50

### [0084]

図12に示す回路では、素子1(あるいはメモリ素子31)からの出力42を負帰還増幅回路44aにより増幅した出力45と、参照素子41からの出力43を負帰還増幅回路44bにより増幅した出力46とを差動増幅回路47に入力する。そして、差動増幅回路47から得られた出力信号48を用いて、素子1(31)の抵抗を求めることができる。【0085】

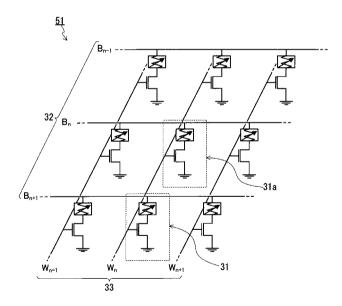

図13に示すように、2以上のメモリ素子31をマトリクス状に配列することにより、不揮発性でランダムアクセス型の抵抗変化型メモリ(メモリアレイ)51を構築できる。メモリ51では、2以上のビット線32から選ばれる1つのビット線( $B_n$ )と、2以上のワード線33から選ばれる1つのワード線( $W_n$ )とを選択することにより、座標( $B_n$ 、 $W_n$ )に位置するメモリ素子31aへの情報の記録およびメモリ素子31aからの情報の読出が可能となる。

#### [0086]

図 1 3 に示すように、 2 以上のメモリ素子をマトリクス状に配列する場合、少なくとも 1 つのメモリ素子を参照素子としてもよい。

#### [0087]

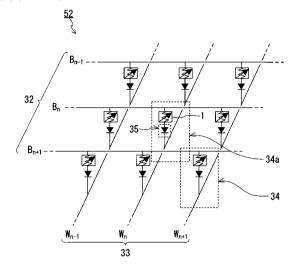

図14に示すように、本発明の抵抗変化素子1に、非線形の電流電圧特性を有する選択素子35(図14では一例としてダイオード)が直列接続されたメモリ素子34とし、2以上の当該メモリ素子34をマトリクス状に配列することによっても、不揮発性でランダムアクセス型の抵抗変化型メモリ(メモリアレイ)52を構築できる。メモリ52では、2以上のビット線32から選ばれる1つのビット線(Bn)と、2以上のワード線33から選ばれる1つのワード線(Wn)とを選択することにより、座標(Bn、Wn)に位置するメモリ素子34aへの情報の記録と、メモリ素子34aからの情報の読出が可能となる

### [ 0 0 8 8 ]

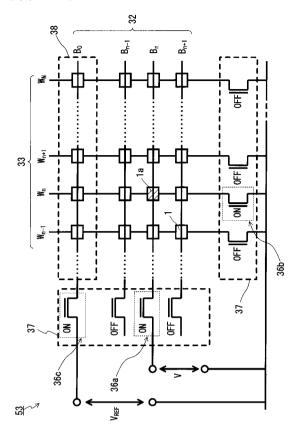

図15に示すように、パストランジスタ36を用い、2以上の抵抗変化素子1をマトリクス状に配列することによっても、不揮発性でランダムアクセス型の抵抗変化型メモリ(メモリアレイ)53を構築できる。メモリ53では、ビット線32は素子1の上部電極4に接続され、ワード線33は素子1の下部電極2に接続されている。メモリ53では、2以上のビット線32から選ばれる1つのビット線(Bn)に接続されたパストランジスタ36aと、2以上のワード線33から選ばれる1つのワード線(Wn)に接続されたパストランジスタ36bとを選択的にON状態とすることによって、座標(Bn、Wn)に位置する抵抗変化素子1aへの情報の記録、および、抵抗変化素子1aからの情報の読出が可能となる。素子1aの情報を読出すためには、例えば、素子1aの電気抵抗値に対応する電圧である、図15に示す電圧Vを測定すればよい。

# [0089]

また、抵抗変化素子1の代わりに、メモリ素子34のような非線形の電流電圧特性を有する素子を用いた場合も、この構成により不揮発性でランダムアクセス型のメモリアレイを構築できる。さらに、このメモリ構成は、メモリアレイを多層にした場合にも適用することができ、この場合、パストランジスタ群37にさらにスイッチを設け、各メモリアレイ層にその都度アクセス可能な構成とすればよい。

#### [0090]

なお、図15に示すメモリ53には参照素子群38が配置されている。参照素子群38に接続されたビット線( $B_0$ )に対応するパストランジスタ36cを選択的にON状態とし、図15に示す電圧 $V_{REF}$ を測定することによって、素子1aの出力と、参照素子群38の出力との差分を検出できる。

### [0091]

また、図15に示すメモリ53では、パストランジスタにより選択されなかった非選択の素子1を参照素子として利用することも可能である。この方法では、パストランジスタにより選択された素子1a周辺の素子の状態を検証しながら、参照素子を適宜設定する必

要があるため、メモリアレイとしての動作がやや遅くなることがあるが、メモリアレイの 構成をより簡便にできる。

# [0092]

[抵抗変化素子の製造方法]

本発明の製造方法では、基板上に下部電極を形成した後に、形成した下部電極上に、式 $M(Fe_{2-x}A_x)O_4$ で示される酸化物を含む抵抗変化層を形成する。次に、形成した抵抗変化層上に、下部電極とともに当該抵抗変化層を狭持するように上部電極を形成する。ただし、上記式において、M はM n、C o、N i、C u およびZ n から選ばれる少なくとも 1 種の元素であり、A はT i、V 、N b、T a、C r、M n、C o および R h から選ばれる少なくとも 1 種の元素であってM とは異なる元素であり、X は式 X く X の X 5 を満たす数値である。本発明の製造方法によれば、上述した本発明の抵抗変化素子を形成できる。

[0093]

本発明の製造方法では、抵抗変化層形成工程において、上記式で示される第1の酸化物からなる第1の抵抗変化膜と、上記式で示され、第1の酸化物とは組成が異なる第2の酸化物からなる第2の抵抗変化膜とを形成して、第1および第2の抵抗変化膜を有する抵抗変化層を形成してもよい。この方法では、例えば、図2~4、6および7に示す素子1を形成できる。

[0094]

この場合、形成した第1および第2の抵抗変化膜を有する抵抗変化層を500 以下の温度において熱処理し、自層の厚さ方向に組成勾配を有する抵抗変化層としてもよい。

[0095]

また、このような熱処理により、例えば、所望の組成 M(Fe $_{2-x}$ A $_x$ )O $_4$ を有する酸化物を含む抵抗変化層の形成がより容易となる。具体的には、式 M(Fe $_{2-x1}$ A $_{x1}$ )O $_4$ で示される酸化物からなる第 1 の抵抗変化膜と、式 M(Fe $_{2-x2}$ A $_{x2}$ )O $_4$ で示される酸化物からなる第 2 の抵抗変化膜(ただし、0 < x 1 < x < x 2 0 . 5 )とを有する抵抗変化層を形成した後に、当該抵抗変化層を熱処理すればよい。熱処理により、双方の抵抗変化膜の間で元素の相互拡散が起こり、式 M(Fe $_{2-x}$ A $_x$ )O $_4$ で示される酸化物を含む抵抗変化層を形成できる。

[0096]

抵抗変化層の熱処理は、抵抗変化層を形成した後の任意の時点で行うことができ、例えば、抵抗変化層を形成後、上部電極を形成する前の時点で、あるいは、素子全体を形成した後に、行ってもよい。

[0097]

本発明の製造方法では、抵抗変化層形成工程において、室温以上 5 0 0 以下の温度範囲で成膜温度を変化させながら抵抗変化層を形成してもよい。成膜温度が変化すると、抵抗変化層を構成する材料、例えば、上記式で示される酸化物、の粒径が変化する。このため、この方法では、自層の厚さ方向に粒径分布を有する抵抗変化層を形成できる。

[0098]

本発明の製造方法では、抵抗変化層形成工程において、上記式で示される酸化物からなる抵抗変化膜と、 $Fe_3O_4$ からなる抵抗膜とを形成して、抵抗変化膜および抵抗膜を有する抵抗変化層を形成してもよい。この方法では、例えば、図 5 ~ 7 に示す素子 1 を形成できる。

[0099]

本発明の製造方法では、下部電極形成工程、抵抗変化層形成工程および上部電極形成工程の各工程間に任意の工程が加えられていてもよい。

[0100]

本発明の抵抗変化素子 1 を構成する各層は、半導体の製造プロセスを応用し、一般的な薄膜形成プロセスおよび微細加工プロセスにより形成すればよい。例えば、パルスレーザーデポジション(PLD)、イオンビームデポジション(IBD)、クラスターイオンビ

10

20

30

40

10

20

30

40

50

ーム、およびRF、DC、電子サイクロトン共鳴(ECR)、ヘリコン、誘導結合プラズマ(ICP)、対向ターゲットなどの各種スパッタリング法、分子線エピタキシャル法(MBE)などの蒸着法、イオンプレーティング法などを用いればよい。これらPVD(Physical Vapor Deposition)法、MOCVD(Metal Organic Chemical Vapor Deposition)法、MOCVD(Metal Organic Decomposition)法、あるいは、ゾルゲル法などを用いてもよい。

### [0101]

各層の微細加工には、例えば、半導体製造プロセスや磁性デバイス(GMRやTMRなどの磁気抵抗素子など)製造プロセスに用いられる方法を適用できる。具体的には、イオンミリング、RIE(Reactive Ion Etching)、FIB(Focused Ion Beam)などの物理的あるいは化学的エッチング法、および、微細パターン形成のためのステッパー、EB(Electron Beam)法などを用いたフォトリソグラフィー技術を組み合わせて用いればよい。各層の表面の平坦化には、例えば、CMP(Chemical Mechanical Polishing)、クラスター・イオンビームエッチングなどを用いればよい。

# [0102]

本発明の抵抗変化素子を備えるメモリなどの電子デバイスについても、上記方法によって、あるいは、上記方法と他の公知の方法とを組み合わせることによって、形成できる。 【 0 1 0 3 】

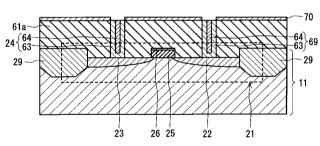

本発明の抵抗変化素子の製造方法の一例を、本発明の抵抗変化素子が組み込まれたメモリ素子の一例として、図16A~図16Hに示す。

### [0104]

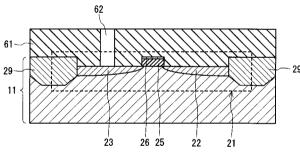

最初に、図16Aに示すように、トランジスタ21が形成された基板11の表面に、トランジスタ21を覆うように保護絶縁膜61を堆積し、堆積した保護絶縁膜61の表面を СMPなどにより平坦化した後に、保護絶縁膜61に対して選択的にエッチングを行って プラグ用開口部62を形成する。

### [0105]

保護絶縁膜 6 1 は、例えば、SiO<sub>2</sub>からなればよく、より具体的にはTEOS(テトラエチルオルトシリケート)およびO<sub>3</sub>(オゾン)から形成したSiO<sub>2</sub>膜(TEOS膜)であってもよい。基板 1 1 表面へのトランジスタ 2 1 の形成方法は、一般的な手法によればよい。図 1 6 Aに示すトランジスタ 2 1 は、ソース電極 2 2 、ドレイン電極 2 3 、ゲート絶縁膜 2 5 、ゲート電極 2 6 および素子分離部 2 9 を備える一般的なMOS - FETである。プラグ用開口部 6 2 は、トランジスタ 2 1 のドレイン電極 2 3 が露出するように形成すればよい。

# [0106]

次に、図16Bに示すように、保護絶縁膜61の表面にバリアメタル63およびプラグメタル64を順に堆積する。バリアメタル63には、プラグメタル64の拡散を抑制したり、周囲の絶縁層との密着性を高めたりする作用を有する材料、あるいは、プラグメタル64をメッキにより形成する場合にはシードとしての作用を有する材料を用いればよく、例えば、チタン(Ti)膜と窒化チタン(Ti・N)膜とからなる積層体や、タンタル(Ta)膜と窒化タンタル(Ta・N)膜とからなる積層体などを用いればよい。プラグメタル64には基本的に導電性に優れる材料を用いればよく、例えば、タングステン、アルミニウム、銅などを用いればよい。プラグメタル64は、プラグ用開口部62を充填するように堆積すればよい。

# [0107]

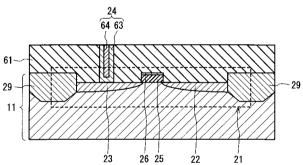

次に、図16Cに示すように、堆積したバリアメタル63およびプラグメタル64における保護絶縁膜61上の部分をCMPなどにより除去し、ドレイン電極23と電気的に接続されたプラグ24を形成する。

# [0108]

次に、図16Dに示すように、プラグ24および保護絶縁膜61の表面に、下部電極2、抵抗変化層3および上部電極4を順に形成する。下部電極2は、プラグ24との間に電

気的な接続が確保されるように形成すればよい。

### [0109]

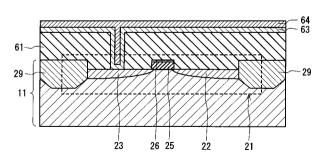

次に、図16Eに示すように、形成した下部電極2、抵抗変化層3および上部電極4を 所定の形状に微細加工し、抵抗変化素子1とする。

### [0110]

次に、図16Fに示すように、保護絶縁膜61上に、下部電極2、抵抗変化層3および上部電極4の積層体を覆うように、保護絶縁膜65を堆積する。保護絶縁膜65は、例えば、上述したTEOS膜からなればよい。

### [0111]

次に、図16Gに示すように、保護絶縁膜65の表面をCMPなどにより平坦化した後、保護絶縁膜65に対して選択的にエッチングを行ってプラグ用開口部66を形成する。 プラグ用開口部66は、上部電極4が露出するように形成すればよい。

### [0112]

次に、図16日に示すように、保護絶縁膜65の表面に密着用メタル67および配線用メタル68を順に堆積し、ビット線32と、ビット線32および上部電極4を電気的に接続するプラグ27とを形成する。密着用メタル67には、周囲の絶縁層との密着性を高める作用を有する材料、あるいは、配線用メタル68をメッキにより形成する場合にはシードとしての作用を有する材料を用いればよく、例えば、チタン(Ti)膜と窒化チタン(Ti・N)膜とからなる積層体や、タンタル(Ta)膜と窒化タンタル(Ta・N)膜とからなる積層体や、タンタル(Ta)膜と窒化タンタル(Ta・N)膜とこのようにはよい。配線用メタル68には基本的に導電性に優れる材料を用いればよく、例えば、タングステン、銅、アルミニウムなどを用いればよい。配線用メタル68は、プラグ用開口部66を充填するように、かつ、ビット線32が形成されるように堆積すればよい。このようにして図10に示すといるとでは表子31を形成できる。なお、保護絶縁膜61および65は、図10に示す層間絶縁層28となる。

# [0113]

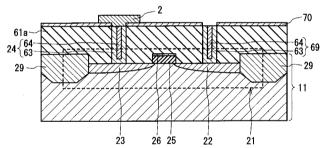

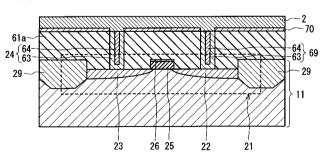

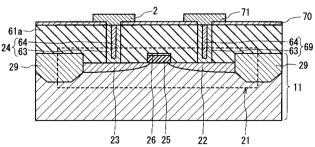

本発明の抵抗変化素子の製造方法の別の一例を、本発明の抵抗変化素子が組み込まれた メモリ素子の製造方法の一例として、図17A~図17Mに示す。

# [0114]

最初に、図16A~図16Cに示す工程と同様にして、図17Aに示すように、MOS-FETであるトランジスタ21が形成された基板11の表面に保護絶縁膜61aおよび水素バリア層70を堆積し、堆積した保護絶縁膜61aの一部の領域に、トランジスタ21のドレイン電極23と電気的に接続されたプラグ24、および、トランジスタ21のソース電極22と電気的に接続されたプラグ69を形成する。プラグ69は、プラグ24と同様に形成すればよい。水素バリア層70には、SiNあるいはTiA10などを好適に用いることができる。

# [0115]

次に、図17Bに示すように、水素バリア層70、プラグ24およびプラグ69上に下 部電極2を形成する。

### [0116]

次に、図17Cに示すように、下部電極2を、プラグ24の直上の部分を除いてエッチングなどにより除去する。

# [0117]

次に、図17Dに示すように、プラグ69の表面に、プラグ69との電気的な接続が確保されるように、ソース電極22と後に形成されるビット線32とを接続するための電極71を形成する。電極71は、基本的に、導電性を有する材料からなればよい。

#### [0118]

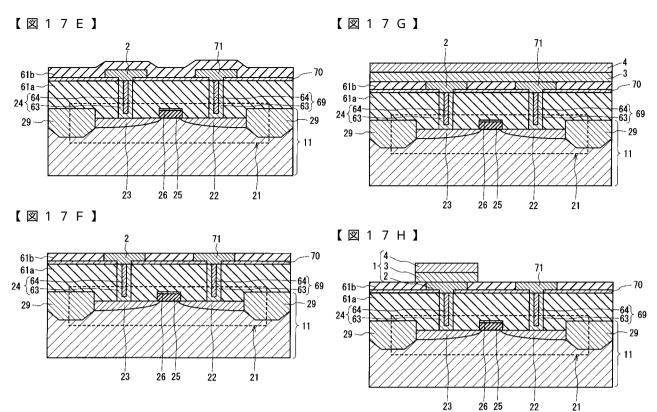

次に、図17Eに示すように、水素バリア層70上に、下部電極2および電極71を覆うように保護絶縁膜61bを堆積した後に、図17Fに示すように、保護絶縁膜61bの表面をCMPなどにより平坦化して、下部電極2および電極71を露出させる。

10

20

30

40

#### [0119]

次に、図17Gに示すように、保護絶縁膜61b、下部電極2および電極71上に、抵 抗変化層3および上部電極4を形成する。

### [0120]

次に、図17日に示すように、抵抗変化層3および上部電極4を、所定の形状に微細加 工し、抵抗変化層1とする。

#### [0121]

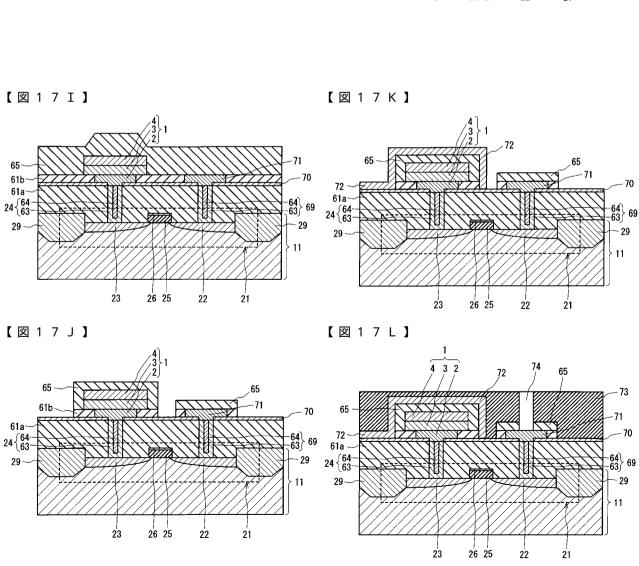

次に、図17Ⅰに示すように、保護絶縁膜61bおよび電極71上に、抵抗変化層3お よび上部電極4を覆うように、保護絶縁膜65を形成する。

# [0122]

次に、図17Jに示すように、保護絶縁膜61bおよび65のうち、素子1および電極 71の周囲以外の部分を、水素バリア層70が露出するようにエッチングにより除去する

# [0123]

次に、全体に水素バリア層72を堆積させた後、図17Kに示すように、水素バリア層 7 2 における素子 1 の周囲以外の部分をエッチングにより除去して、水素バリア層 7 0 お よび72により素子1を被覆する。水素バリア層72には、SiN、TiAlO、TiA 1N、TiA1ONなどを好適に用いることができる。

# [0124]

次に、全体に保護絶縁膜73を形成し、その表面をCMPなどにより平坦化した後、保 護 絶 縁 膜 7 3 に 対 し て 選 択 的 に エ ッ チ ン グ を 行 っ て プ ラ グ 用 開 口 部 7 4 を 形 成 す る ( 図 1 7L)。プラグ用開口部74は、電極71が露出するように形成すればよい。

### [0125]

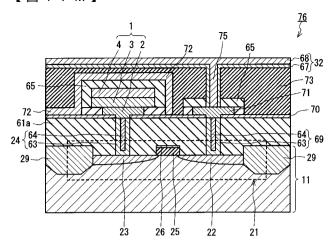

次に、図 1 7 M に示すように、保護絶縁膜 7 3 の表面に密着用メタル 6 7 および配線用 メ 夕 ル 6 8 を 順 に 堆 積 し 、 ビ ッ ト 線 3 2 と 、 ビ ッ ト 線 3 2 と 電 極 7 1 と を 電 気 的 に 接 続 す るプラグ75を形成して、メモリ素子76を形成できる。配線用メタル68は、プラグ用 開口部74を充填するように、かつ、ビット線32が形成されるように堆積すればよい。

#### [ 0 1 2 6 ]

メモリ素子76では、上部電極4は、プラグ24と同様に水素バリア70を貫通するプ ラグ(図示せず)によって、素子の下部にある電極(図示せず)に電気的に接続され、さ らに、水素バリア70および保護絶縁膜73を貫通する別のプラグ(図示せず)によって 、素子の表面に配置された別の電極配線に電気的に接続されている。

### [ 0 1 2 7 ]

図17A~図17Mに示す製造方法によって形成されたメモリ素子は、高いパッシベー ション効果を有する。このとき、下部電極2に、水素暴露に対する耐性が高い、Ti-A 1 合金の窒化物、あるいは、その積層体を用いることで、より高いパッシベーション効果 を得ることができる。

### 【実施例】

# [0128]

以下、実施例により、本発明をより詳細に説明する。本発明は、以下に示す実施例に限 定されない。

### [ 0 1 2 9 ]

# (実施例1)

実施例1では、図1に示す抵抗変化素子1を備え、図10に示す構成を有するメモリ素 子31を作製し、その抵抗変化特性を評価した。評価した素子サンプルは、上述した図1 6 A ~図16Hに示す方法により作製し、式Zn(Fe<sub>2 - x</sub>Cr<sub>x</sub>)0₄で示される酸化物 からなる抵抗変化層3とした。

# [0130]

保護絶縁膜61は、厚さ400nmのTEOS膜とした。バリアメタル63は、Ti膜 とTiN膜との積層体とし、プラグメタル64はタングステン膜とした。

10

20

30

40

### [0131]

下部電極 2 は基板 1 1 側から順にTiA1N膜およびPt膜を堆積させたTiA1N / Pt膜(合計の厚さ 1 0 0 n m)とした。TiA1N膜は、Ti $_{70}$  A 1  $_{30}$  合金をターゲットとして用い、マグネトロンスパッタリング法により、圧力 0 . 1 P a のアルゴン・窒素混合雰囲気下(窒素:アルゴン(分圧比)=約 4 : 1 )にて、Si基板の温度を 0 ~ 4 0 0 (主に 3 5 0 )とした上で、印加電力をDC4kWとして形成した。Pt膜は、TiA1N膜を形成したチャンバーと同じチャンバー内において、マグネトロンスパッタリング法により、圧力 0 . 7 P a のアルゴン雰囲気下にて、Si基板の温度を 2 7 とした上で、印加電力をRF100Wとして形成した。

# [0132]

### [0133]

上部電極 4 は、 P t 膜(厚さ 5 0 n m)とし、当該膜は、マグネトロンスパッタリング法により、圧力 0 . 7 P a のアルゴン雰囲気下にて、 S i 基板の温度を 2 7 とした上で、印加電力を R F 1 0 0 W として形成した。

### [0134]

保護絶縁膜 6 5 は厚さ 8 0 0 n m の T E O S 膜とした。密着用メタル 6 7 は厚さ 1 0 n m の T a N 膜とし、配線用メタル 6 8 は厚さ 3 0 0 n m の A 1 膜とした。

#### [ 0 1 3 5 ]

素子1の接合面積は0.2 $\mu$ m<sup>2</sup>とした。

### [0136]

なお、形成した抵抗変化層3の組成は、X線回折法、赤外吸収法、ラマン分光法、および、エネルギー分散型X線分析(EDX)により確認した。同様の手法により、形成した抵抗変化層3の結晶構造を評価したところ、以下の表1に示す全てのサンプルにおいて、抵抗変化層3を構成する材料がスピネル型の結晶構造を有することが確認できた。また、抵抗変化層3のシート抵抗値を評価したところ、xの値により、抵抗変化層のシート抵抗値が変化することが確認できた。

#### [0137]

上記のように作製したサンプルに対し、図11に示すようにパルス状のSET電圧、RESET電圧およびREAD電圧を印加し、素子1の抵抗変化比を評価した。

#### [0138]

抵抗変化比の評価は以下のようにして行った。ゲート電極26への電圧印加によってトランジスタ21をON状態とし、ソース電極22と上部電極4との間に、パルスジェネレータにより、SET電圧として2V(正バイアス電圧)、RESET電圧として・2V(負バイアス電圧、大きさ2V)、READ電圧として0.5V(正バイアス電圧)を印加した。印加する各電圧のパルス幅は100nsとした。SET電圧またはRESET電圧を印加した後、READ電圧の印加により読み出した電流値からサンプルの電気抵抗値を算出し、算出した電気抵抗値の最大値をR<sub>MAX</sub>、最小値をR<sub>MIN</sub>として、以下の式から抵抗変化比 Rを求めた。

### [0139]

抵抗変化比  $R = (R_{MAX} - R_{MIN}) / R_{MIN}$

抵抗変化比の評価結果を、各サンプルにおける×の値とともに表1に示す。なお、×の値が0であるサンプルA-1の抵抗変化層は、元素A(Cr)を含まない。

### [0140]

10

20

30

#### 【表1】

| サンプル No.  | ×     | ⊿R  |

|-----------|-------|-----|

| 1 – 1     | 0.05  | 19  |

| 1 – 2     | 0.10  | 40  |

| 1 – 3     | 0. 20 | 65  |

| 1 – 4     | 0.30  | 115 |

| 1 – 5     | 0.35  | 75  |

| 1 – 6     | 0.40  | 60  |

| 1 – 7     | 0.45  | 58  |

| 1 – 8     | 0. 50 | 25  |

| A-1 (比較例) | 0.00  | 8.5 |

| A-2 (比較例) | 0. 55 | 2   |

| A-3 (比較例) | 0.60  | 0   |

[0141]

表 1 に示すように、抵抗変化層 3 を構成する酸化物について、式 Z n(F e  $_{2-x}$  C  $r_x$ )  $O_{4 \ r_{a} \ r_{b} \ a}$  × の値が 0 . 0 5 以上 0 . 5 以下の範囲のサンプルにおいて、当該 × の値が 0 または 0 . 5 5 以上である比較例サンプルに対して高い抵抗変化比を得ることができた。特に × の値が 0 . 1 以上 0 . 4 5 以下の範囲のサンプルにおいて 4 0 以上の高い抵抗変化比が得られ、 × の値が 0 . 2 以上 0 . 4 以下の範囲のサンプルにおいて 0 以上のより高い抵抗変化比が得られた。

# [0142]

次に、サンプル1-1~1-5、および、比較例サンプルA-1~A-3について、その保持特性を評価した。保持特性は、1つのサンプル種に対して、RESET電圧あるいはSET電圧の印加により、高抵抗状態および低抵抗状態の素子をそれぞれ準備し、当該素子を125 の雰囲気下に保持したときに、高抵抗状態の抵抗値と低抵抗状態の抵抗値との差の絶対値が1/2になるまでの時間Tを指標とした。評価結果を以下の表2に示す

[0143]

なお、サンプルの抵抗変化比および保持特性の評価は、これ以降に示す各サンプルにおいても全て同様に行った。

[0144]

10

20

#### 【表2】

| サンプル No.  | ×     | T (時間) |

|-----------|-------|--------|

| 1 – 1     | 0.05  | 15     |

| 1 – 2     | 0.10  | 100    |

| 1 – 3     | 0. 20 | 120    |

| 1 – 4     | 0.30  | 285    |

| 1 – 5     | 0.35  | 75     |

| A-1 (比較例) | 0.00  | 1      |

| A-2(比較例)  | 0. 55 | 1      |

| A-3 (比較例) | 0.60  | 1      |

### [0145]

表 2 に示すように、抵抗変化層 3 を構成する酸化物について、式 Z n(F e  $_{2-x}$  C  $r_x$ ) O  $_4$ における x の値が 0 . 0 5 以上 0 . 3 5 以下の範囲のサンプルにおいて、当該 x の値が 0 または 0 . 5 5 以上である比較例サンプルに対して大幅に高い保持特性を得ることができた。特に、x の値が 0 . 1 以上 0 . 3 以下の範囲のサンプルにおいて時間 T は 1 0 0 時間以上となり、より高い保持特性が得られることがわかった。

### [0146]

これらの結果から、ZnFeッ0√におけるFeを元素A(Cr)により部分的に置換し た酸化物である Z n ( F e <sub>2 - x</sub> C r <sub>x</sub> ) O ₄: 0 < x 0 . 5 を抵抗変化層に用いることに より、素子の抵抗変化比だけではなく保持特性も向上できることがわかった。この理由に ついては、上述したように、Crイオンの価数が3価と4価との間で変化することが鍵に なっていると思われる。即ち、サンプル1‐1~1‐8では、抵抗変化層から電子の取り 出しが行われる際においてもFeの価数変化をCrにより補償することができ、酸素を関 与させることなく金属イオンの価数調整のみで電荷中性の保持が可能となる。また、Zn FeゥO₄内のFeサイトにてFeイオンがともに3価であるために抑制されていた電子伝 導 が、 Fe サイトへのCr 添 加 によって 2 価 、 3 価 お よ び 4 価 の イ オ ン が 混 在 す る こ と に より行われやすくなり、高抵抗状態から低抵抗状態への変化がよりスムーズになって抵抗 変化比が向上すると考えられる。即ち、スピネル型酸化物を抵抗変化層とする素子では、 当該素子の抵抗変化特性および保持特性を向上させようとすると、当該酸化物における被 置換元素(本発明ではFe)、置換元素(本発明では元素A)および元素Mの組み合わせ が重要であって、これらの組み合わせに関する知見は本発明により初めて得られたといえ る。 なお、 F e に対する C r (元素 A )の置換量が上記 x の値にして 0 . 5 を超えた場合 には、十分な抵抗変化特性および保持特性が得られなくなったが、これは、母材であるZ n F e <sub>2</sub> O <sub>4</sub>内の F e サイトにおいて、 F e イオンの量よりも置換元素のイオンの量の方が 多くなり、その伝導特性が変化したのが原因ではないかと推察される。

# [0147]

次に、サンプル 1-1-8 と同様にして、式 2 n(F e  $_{2-x}$  A  $_x$ )  $O_4$  で示される酸化物からなる抵抗変化層 3 を有するメモリ素子を、元素 A の種類を変えて 7 種類(サンプル 1-9-1-1 5)作製し、その抵抗変化比および保持特性を評価した。上記式における x の値は、元素 A が T a であるサンプル 1-1-1-1-1-1 5(x=0.1)を除き、全て x=0.3 とした。元素 x の種類とともに、その評価結果を以下の表 x に示す。なお、表 x では、元素 x が x であるサンプル x 1 x 4 の評価結果を併せて示す。

### [0148]

10

20

30

### 【表3】

| サンプル No. | 元素A | ×   | ⊿R  | 丁 (時間) |

|----------|-----|-----|-----|--------|

| 1 – 4    | Cr  | 0.3 | 115 | 285    |

| 1 – 9    | Τi  | 0.3 | 85  | 12     |

| 1 – 1 0  | V   | 0.3 | 28  | 10     |

| 1-11     | Nb  | 0.3 | 90  | 115    |

| 1 – 1 2  | Mn  | 0.3 | 150 | 190    |

| 1-13     | Со  | 0.3 | 58  | 140    |

| 1-14     | R h | 0.3 | 40  | 8      |

| 1-15     | Та  | 0.1 | 20  | 5      |

# [0149]

表 3 に示すように、サンプル1-4、1-9~1-15の全てのサンプルにおいて、比較例サンプルA-1~A-3に比べて高い抵抗変化比および保持特性を得ることができた

# [0150]

次に、サンプル1-1~1-8と同様にして、式Fe(Fe $_{2-x}$ С $_{1x}$ 0 $_{4}$ で示される酸化物からなる抵抗変化層3を有するメモリ素子(比較例A-4)、式 $_{2-x}$ W $_{x}$ 0 $_{4}$ で示される酸化物からなる抵抗変化層3を有するメモリ素子(比較例A-5)、および、式 $_{1x}$ 0 $_{1x}$ 1 $_{1x$

# [0151]

# 【表4】

| サンプル No. | 元素M | 元素A | x    |

|----------|-----|-----|------|

| A-4(比較例) | Fe  | Cu  | 0.05 |

| A-5(比較例) | Zn  | W   | 0.05 |

| A-6(比較例) | Cu  | Zn  | 0.05 |

#### [ 0 1 5 2 ]

評価の結果、比較例サンプルA - 4 ~ A - 6 は、抵抗変化特性そのものが発現しなかった。このことから、元素 M および元素 A には好ましい組み合わせが存在し、本発明の素子において発現する高い特性は、適した組み合わせの知見を得て初めて実現可能となったと考えられる。

# (実施例2)

実施例2では、図2に示す抵抗変化素子1を備え、図10に示す構成を有するメモリ素子31を、元素Mと元素Aとの組み合わせを変えて2種類(サンプル2-1~2-2)作製し、その抵抗変化特性を評価した。

### [0153]

評価した素子サンプルは、上述した図 1 6 A ~ 図 1 6 H に示す方法により作製し、サンプル 2 - 1 においては、式 Z n ( F e  $_{1.7}$  C r  $_{0.3}$  ) O  $_4$  で示される酸化物( x = 0 . 3 ) からなる第 2 の抵抗変化膜 3 b と、式 Z n ( F e  $_{1.8}$  C r  $_{0.2}$  ) O  $_4$  で示される酸化物( x

10

20

30

50

= 0 . 2 )からなる第 1 の抵抗変化膜 3 a とした。サンプル 2 - 2 においては、式 C u(F e  $_{1..7}$  M n  $_{0..3}$ ) O  $_4$  で示される酸化物(x = 0 . 3 )からなる第 2 の抵抗変化膜 3 b と、式 C u(F e  $_{1..8}$  M n  $_{0..2}$ ) O  $_4$  で示される酸化物(x = 0 . 2 )からなる第 1 の抵抗変化膜 3 a とした。下部電極 2 など、メモリ素子 3 1 における抵抗変化層 3 以外の各部分の構成は、素子の接合面積を含め、実施例 1 における各サンプルと同様とした。

## [0154]

抵抗変化層3(厚さ50nm)は、最初に下部電極2上に第2の抵抗変化膜3b(厚さ25nm)を形成した後に、さらに第1の抵抗変化膜3a(厚さ25nm)を形成して作製した。双方の抵抗変化膜の作製条件は、実施例1における抵抗変化層の作製条件と同様とした。

# [0155]

形成した各抵抗変化膜の組成は、実施例1と同様にして確認した。また、同様の手法により、形成した各抵抗変化膜の結晶構造を評価したところ、サンプル2-1、2-2ともに、スピネル型の結晶構造を有することが確認できた。また、各抵抗変化膜のシート抵抗値を評価したところ、×の値により、抵抗変化層のシート抵抗値が変化することが確認できた。

# [0156]

上記のように作製したサンプルに対し、実施例 1 と同様にして、その抵抗変化比および保持特性を評価した。評価結果を、各サンプルにおける元素 M、元素 A および x の値とともに以下の表 5 に示す。

# [ 0 1 5 7 ]

# 【表5】

| サンプル  |     |     | 2              | ×              |     | <b>T</b> |

|-------|-----|-----|----------------|----------------|-----|----------|

| No.   | 元素M | 元素A | 第1の抵抗<br>変化膜3a | 第2の抵抗<br>変化膜3b | ⊿R  | (時間)     |

| 2 – 1 | Zn  | Cr  | 0. 2           | 0.3            | 115 | 250      |

| 2-2   | Cu  | Mn  | 0. 2           | 0.3            | 55  | 120      |

# [0158]

表 5 に示すように、サンプル 2 - 1 では、 x の値が互いに異なる酸化物からなる 2 つの抵抗変化膜により抵抗変化層を構成することで、 1 つの酸化物から抵抗変化層を構成した場合(例えば、 x = 0 . 2 0 であるサンプル 1 - 3 ) よりも、抵抗変化比および保持特性を向上できた。この効果についても詳細な原理は不明であるが、双方の抵抗変化膜の界面における F e イオンおよび元素 A のイオン( C r イオン )の価数配置が微妙に異なるために、電子の移動に伴うイオンの価数変化が起こりやすくなっている可能性がある。

#### 【 0 1 5 9 】

また、表 5 に示すように、元素 M が C u 、元素 A が M n の場合においても、高い抵抗変化比および保持特性を得ることができた。

# [0160]

#### (実施例3)

実施例3では、図5に示す抵抗変化素子1を備え、図10に示す構成を有するメモリ素子31を、抵抗変化膜3cと抵抗膜5との厚さを変化させて5種類(実施例であるサンプル3-1~3-5)作製し、その抵抗変化特性を評価した。

# [0161]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、下部電極2など、メモリ素子31における抵抗変化層3以外の各部分の構成は、素子の接合面積を含め、実施例1における各サンプルと同様とした。また、式Zn(Fe<sub>1.7</sub>Cr<sub>0.3</sub>)

10

20

30

50

$O_4$ で示される酸化物( x = 0 . 3 )からなる抵抗変化膜 3 c とし、 F e  $_3O_4$ からなる抵抗膜 5 とした。

#### [0162]

抵抗変化層 3 は、最初に下部電極 2 上に抵抗膜 5 を形成した後に、抵抗変化膜 5 c を形成して作製した。抵抗変化膜 3 c および抵抗膜 5 の作製条件は、実施例 1 における抵抗変化層の作製条件と同様とした。形成した抵抗変化膜および抵抗膜の組成は、実施例 1 と同様にして確認した。また、同様の手法により、形成した抵抗変化膜の結晶構造を評価したところ、スピネル型の結晶構造を有することが確認できた。

### [0163]

サンプル3-1~3-5の作製とは別に、式Zn(Fe $_{1.7}$ Cr $_{0.3}$ )O $_4$ で示される酸化物からなる単層の抵抗変化層3を含む素子1(図1に準じる)を備え、抵抗変化層3の厚さを1~25nmの範囲で変化させたメモリ素子31を、実施例1における各サンプルと同様にして作製した。作製した当該素子1における下部電極2と上部電極4との間の電気抵抗値(初期抵抗値)を測定したところ、初期抵抗値は抵抗変化層3の厚さに応じて線形に変化することがわかった。しかし、抵抗変化層3の厚さが10nm以下になると、その実測値は予測値よりも小さくなり、抵抗変化層3自体のリークと考えられる現象が確認された。このことから、単層の抵抗変化層3では、抵抗変化層3を構成する材料にもよるが、その厚さがおよそ10nm以下程度になると、抵抗変化比が小さくなったり得られなくなったりする可能性があると考えられる。

# [0164]

サンプル3 - 1 ~ 3 - 5 に対し、実施例1 と同様にして、その抵抗変化比を評価した。評価結果を、各サンプルにおける抵抗変化膜3 c の厚さ、および、抵抗膜5 の厚さとともに以下の表6に示す。

#### [0165]

### 【表6】

|          | 抵抗変化膜3 c | 抵抗膜 5 |     |

|----------|----------|-------|-----|

| サンプル No. | の厚さ      | の厚さ   | ⊿R  |

|          | (nm)     | (nm)  |     |

| 3 – 1    | 10       | 20    | 90  |

| 3 – 2    | 10       | 30    | 85  |

| 3 – 3    | 5        | 50    | 100 |

| 3 – 4    | 2        | 75    | 115 |

| 3 – 5    | 1        | 100   | 90  |

#### [0166]

表 6 に示すように、抵抗変化膜 3 c の厚さが 1 0 n m 以下の場合においても、抵抗膜 5 の配置によりリークの発生を抑え、安定した抵抗変化特性が得られることがわかった。

# [0167]

なお、サンプル 3 - 1 ~ 3 - 5 のように、  $Fe_3O_4$ からなる抵抗膜 5 の上に抵抗変化膜 3 c を形成することにより、素子の抵抗変化特性の発現がより容易となった。実施例 1 の比較例 A - 1 では、素子形成後、抵抗変化を起こすための前処理として電気フォーミングと呼ばれるバルス電圧の印加を 1 0 0 ~ 1 0 0 回程度印加する必要があったが、サンプル 3 - 1 ~ 3 - 5 では、素子形成後、 1 回の R E S E T 電圧の印加により、すぐに抵抗変化を発現できた。

# [0168]

次に、図6に示す抵抗変化素子1を備え、図10に示す構成を有するメモリ素子31を

10

20

30

40

2 種類作製し(サンプル3 - 6 ~ 3 - 7 )、その抵抗変化比を評価した。

### [0169]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、下部電極2など、メモリ素子31における抵抗変化層3以外の各部分の構成は、素子の接合面積を含め、実施例1における各サンプルと同様とした。抵抗変化膜3a、3bおよび抵抗膜5は、サンプル3-1~3-5における抵抗変化膜3cおよび抵抗膜5と同様に形成した。抵抗変化膜3aおよび3bの厚さは、それぞれ10nmとし、抵抗膜5の厚さは20nmとした。

# [0170]

サンプル3 - 6 ~ 3 - 7 における抵抗変化比の評価結果を、各サンプルの抵抗変化膜の組成および抵抗膜の組成とともに、以下の表 7 に示す。

[0171]

# 【表7】

| サンプル No. | 抵抗変化膜3 a                                                 | 抵抗膜 5                          | 抵抗変化膜3 b                                                 | ⊿R  |

|----------|----------------------------------------------------------|--------------------------------|----------------------------------------------------------|-----|

| 3-6      | Zn (Fe <sub>1.8</sub> Cr <sub>0.2</sub> ) 0 <sub>4</sub> | Fe₃O₄                          | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub> | 125 |

| 3-7      | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub> | Fe <sub>3</sub> O <sub>4</sub> | Zn (Fe <sub>1.8</sub> Cr <sub>0.2</sub> ) 0 <sub>4</sub> | 106 |

#### [0172]

表7に示すように、下部電極2および上部電極4に対する抵抗変化膜3a、3bの配置位置は素子の抵抗変化特性にあまり影響を与えないことがわかった。ただし、RESET電圧の印加による抵抗変化の向きはサンプル3-6と3-7とで逆になることがわかった。即ち、サンプル3-6では、RESET電圧の印加により、素子は低抵抗状態から高抵抗状態へと変化し、SET電圧の印加により、素子は高抵抗状態から低抵抗状態へと変化し、サンプル3-7では、RESET電圧の印加により、素子は高抵抗状態から低抵抗状態へと変化し、この結果は、抵抗変化膜における電子の出入りが、抵抗変化現象と密接に関係していることを示している。

# [0173]

次に、図7に示す抵抗変化素子1を備え、図10に示す構成を有するメモリ素子31を2種類作製し(サンプル3-8~3-9)、その抵抗変化比を評価した。

# [0174]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、下部電極2など、メモリ素子31における抵抗変化層3以外の各部分の構成は、素子の接合面積を含め、実施例1における各サンプルと同様とした。抵抗変化膜3a、3bおよび抵抗膜5は、サンプル3-1~3-5における抵抗変化膜3cおよび抵抗膜5と同様に形成した。

### [0175]

サンプル 3 - 8 ~ 3 - 9 における抵抗変化比の評価結果を、各サンプルの抵抗変化膜の組成および厚さ、ならびに、抵抗膜の組成および厚さとともに、以下の表 8 に示す。

# [0176]

10

20

30

### 【表8】

| サンプル<br>No. | 抵抗変化膜 3 a                                                          | 抵抗膜5            | 抵抗変化膜 3 b                                                          | ⊿R |

|-------------|--------------------------------------------------------------------|-----------------|--------------------------------------------------------------------|----|

| 3-8         | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub><br>5 n m  | Fe₃0₄<br>10 n m | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub><br>20 n m | 88 |

| 3 – 9       | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub><br>20 n m | Fe₃0₄<br>10 n m | Zn (Fe <sub>1.7</sub> Cr <sub>0.3</sub> ) 0 <sub>4</sub><br>5 n m  | 72 |

10

### [0177]

表8に示すように、下部電極2および上部電極4に対する、膜厚の異なる抵抗変化膜3a、3bの配置位置は素子の抵抗変化特性にあまり影響を与えないことがわかった。ただし、RESET電圧の印加による抵抗変化の向きはサンプル3-8と3-9とで逆になることがわかった。即ち、サンプル3-8では、RESET電圧の印加により、素子は低抵抗状態から高抵抗状態へと変化するが、サンプル3-9では、RESET電圧の印加により、素子は高抵抗状態から低抵抗状態へと変化した。この結果は、抵抗変化膜における電子の出入りが、抵抗変化現象と密接に関係していることを示している。

#### [0178]

### (実施例4)

実施例 4 では、抵抗変化層 3 として、互いに組成が異なる 2 種類の抵抗変化膜 3 a 、 3 b を積層した後に熱処理した層を含む素子 1 を備え、図 1 0 に示す構成を有するメモリ素子 3 1 (サンプル 4 - 1)を作製し、その抵抗変化特性および保持特性を評価した。

#### [0179]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、式Zn(F $e_{1.95}$ С $r_{0.05}$ ) $O_4$ で示される酸化物(x = 0 . 0 5 )からなる第2の抵抗変化膜3 b と、式Z n(F $e_{1.5}$ С $r_{0.5}$ ) $O_4$ で示される酸化物(x = 0 . 5 )からなる第1の抵抗変化膜3 a とした。下部電極2など、メモリ素子31における抵抗変化層3以外の各部分の構成は、素子の接合面積を含め、実施例1における各サンプルと同様とした。

## [0180]

抵抗変化層 3 (厚さ 5 0 n m)は、以下のようにして作製した。最初に下部電極 2 上に第 2 の抵抗変化膜 3 b(厚さ 2 5 n m)を形成した後に、さらに第 1 の抵抗変化膜 3 a(厚さ 2 5 n m)を形成し、続いて室温~ 4 0 0 の範囲で、第 1 および第 2 の抵抗変化膜の積層体に熱処理を施して抵抗変化層 3 とした。双方の抵抗変化膜の形成条件は、実施例 1 における抵抗変化層の形成条件と同様とした。また、熱処理は、R T A(Rapid Therma I Annealing)装置を用いたランプ加熱により、窒素流下にて行った。熱処理温度と熱処理時間とは互いに関連し合っているが、典型的には、 4 0 0 で 1 分の熱処理を中心とした。

# [0181]

熱処理により形成した抵抗変化層3における元素A(Cr)の分布を透過型電子顕微鏡(TEM)およびEDXにより確認したところ、当該層の厚さ方向に、上記式におけるxの値にして0.05~0.5の範囲で元素Aの濃度勾配が生じていることがわかった。即ち、サンプル4-1の抵抗変化層3は、当該層の厚さ方向に組成勾配を有していることがわかった。この濃度勾配(組成勾配)は、熱処理によるCrの拡散に基づくと考えられる

[0182]

上記のように作製したサンプルに対し、実施例 1 と同様にして、その抵抗変化比および保持特性を評価した。評価結果を、熱処理前の第 1 および第 2 の抵抗変化膜の組成とともに以下の表 9 に示す。

20

30

# 【 0 1 8 3 】 【 表 9 】

| サンプル  | 抵抗変化膜3 a                                                 | 抵抗変化膜3 b                                                   | 4.0 | Т.   |

|-------|----------------------------------------------------------|------------------------------------------------------------|-----|------|

| No.   | (熱処理前)                                                   | (熱処理前)                                                     | ⊿R  | (時間) |

| 4 – 1 | Zn (Fe <sub>1.5</sub> Cr <sub>0.5</sub> ) 0 <sub>4</sub> | Zn (Fe <sub>1.95</sub> Cr <sub>0.05</sub> ) 0 <sub>4</sub> | 180 | 420  |

#### [0184]

表9に示すように、抵抗変化層3内に元素AであるCrの濃度勾配を設けたことにより、均一な組成を有する抵抗変化層とした場合よりも、抵抗変化比および保持特性を向上できることがわかった。この効果についても詳細な原理は不明であるが、元素Aの濃度勾配により、抵抗変化層3内に、抵抗変化特性および保持特性の発現に最も適した元素Aの濃度(=上記式における×の値)が実現した可能性が考えられる。

# [0185]

次に、元素 M および元素 A の種類を変えて、サンプル 4 - 1 と同様の検討を行った。その結果を、以下の表 1 0 に示す。

# [0186]

# 【表10】

| サンプル  | 抵抗変化膜3 a                                                 | 抵抗変化膜3 b                                                   | 4.0 | Т    |

|-------|----------------------------------------------------------|------------------------------------------------------------|-----|------|

| No.   | (熱処理前)                                                   | (熱処理前)                                                     | ⊿R  | (時間) |

| 4-2   | Zn (Fe <sub>1.5</sub> Nb <sub>0.5</sub> ) 0 <sub>4</sub> | Zn (Fe <sub>1.95</sub> Nb <sub>0.05</sub> ) 0 <sub>4</sub> | 95  | 120  |

| 4 – 3 | Zn (Fe <sub>1.5</sub> Ti <sub>0.5</sub> ) 0 <sub>4</sub> | Zn (Fe <sub>1.95</sub> Ti <sub>0.05</sub> ) 0 <sub>4</sub> | 100 | 20   |

| 4 – 4 | Zn (Fe <sub>1.5</sub> Mn <sub>0.5</sub> ) 0 <sub>4</sub> | Zn (Fe <sub>1.95</sub> Mn <sub>0.05</sub> ) 0 <sub>4</sub> | 200 | 200  |

| 4 – 5 | Cu (Fe <sub>1.5</sub> Mn <sub>0.5</sub> ) 0 <sub>4</sub> | Cu (Fe <sub>1.95</sub> Mn <sub>0.05</sub> ) 0 <sub>4</sub> | 60  | 120  |

| 4 – 6 | Cu (Fe <sub>1.5</sub> Rh <sub>0.5</sub> ) 0 <sub>4</sub> | Cu (Fe <sub>1.95</sub> Rh <sub>.05</sub> ) 0 <sub>4</sub>  | 50  | 20   |

| 4-7   | Ni (Fe <sub>1.5</sub> Co <sub>0.5</sub> ) 0 <sub>4</sub> | Ni (Fe <sub>1.95</sub> Co <sub>0.05</sub> ) 0 <sub>4</sub> | 80  | 20   |

| 4-8   | Mn (Fe <sub>1.5</sub> Co <sub>0.5</sub> ) 0 <sub>4</sub> | Mn (Fe <sub>1.95</sub> Co <sub>0.05</sub> ) 0 <sub>4</sub> | 60  | 25   |

| 4 – 9 | Co (Fe <sub>1.5</sub> Cr <sub>0.5</sub> ) 0 <sub>4</sub> | Co (Fe <sub>1.95</sub> Cr <sub>0.05</sub> ) 0 <sub>4</sub> | 45  | 40   |

# [0187]

表10に示すように、抵抗変化層3内に元素Aの濃度勾配を設けたことにより、均一な組成を有する抵抗変化層とした場合よりも、抵抗変化比および保持特性を向上できることがわかった。

# [0188]

#### (実施例5)

実施例 5 では、図 4 に示すように、互いに組成が異なる 2 種類の抵抗変化膜 3 a 、 3 b を、それぞれ複数積層した抵抗変化層 3 を含む素子 1 を備え、図 1 0 に示す構成を有するメモリ素子 3 1 (サンプル 5 - 1)を作製し、その抵抗変化特性および保持特性を評価した。

# [0189]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、素子1の構成は下部電極2側から順に、下部電極2/第2の抵抗変化膜3b/[第1の抵抗変化膜3a/第2の抵抗変化膜3b]⁴/上部電極4とした。[ ]⁴は、4回の繰り返しであることを示す。

20

10

30

### [0190]

第1の抵抗変化膜3a(厚さ10nm)は、式Zn(Fe $_{1.8}$ С  $_{0.2}$ )О $_4$ で示される酸化物( $_X$  = 0 . 2 )からなる膜とし、第2の抵抗変化膜3b(厚さ10nm)は、式Zn(Fe $_{1.7}$ С  $_{0.3}$ )О $_4$ で示される酸化物( $_X$  = 0 . 3 )からなる膜とし、双方の抵抗変化膜の作製条件は、実施例1における抵抗変化層の作製条件と同様とした。抵抗変化層3全体の厚さは90nmである。

#### [0191]

下部電極 2 など、メモリ素子 3 1 における抵抗変化層 3 以外の各部分の構成は、素子の接合面積を含め、実施例 1 における各サンプルと同様とした。

# [0192]

サンプル 5 - 1 の作製とは別に、サンプル 5 - 1 と同様にして抵抗変化層 3 を形成した後に、実施例 4 と同様にして熱処理を加えたサンプル(サンプル 5 - 2 )を別途作製した。サンプル 5 - 2 における抵抗変化層 3 以外の各部分の構成は、サンプル 5 - 1 と同様とした。

### [0193]

上記のように作製したサンプルに対し、実施例1と同様にして、その抵抗変化比および保持特性を評価した。評価結果を以下の表11に示す。

### [0194]

### 【表11】

| サンプル  | ************************************ | ⊿R  | Т    |

|-------|--------------------------------------|-----|------|

| No.   | 熱処理の有無                               |     | (時間) |

| 5 – 1 | 無                                    | 100 | 190  |

| 5 – 2 | 有                                    | 160 | 230  |

## [0195]

表11に示すように、互いに異なる組成を有する抵抗変化膜を複数積層した抵抗変化層 3とすることで、素子の抵抗変化特性および保持特性を向上できることがわかった。また、このような抵抗変化層にさらに熱処理を施して組成勾配を形成することにより、さらなる特性の向上が実現できることがわかった。

# [0196]

# (実施例6)

実施例6では、抵抗変化層3として、成膜温度を変化させながら形成した抵抗変化層を含む素子1を備え、図10に示す構成を有するメモリ素子31(サンプル6-1)を作製し、その抵抗変化特性および保持特性を評価した。

#### [0197]

評価した素子サンプルは、上述した図16A~図16Hに示す方法により作製し、下部電極2など、メモリ素子31における抵抗変化層3以外の各部分の構成は、素子の接合面積を含め、実施例1における各サンプルと同様とした。

#### [0198]

抵抗変化層 3 (厚さ 5 0 n m)は、式 Z n ( F e  $_{1.7}$  C r  $_{0.3}$  )  $_{4}$  で示される焼結体をターゲットとして用い、マグネトロンスパッタリング法により、圧力 0 . 6 P a のアルゴン雰囲気下にて、 S i 基板の温度を室温~ 5 0 0 の範囲で図 1 8 に示す温度プロファイルに従って変化させながら、印加電力を R F 3 0 0 W として形成した。

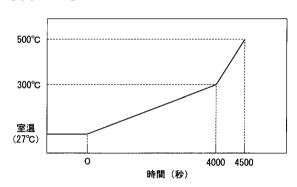

#### [0199]

形成した抵抗変化層3の組成を実施例1と同様にして確認したところ、Zn(Fe $_{1.7}$  Cr $_{0.3}$ )〇 $_4$ であった。また、抵抗変化層内の粒径をTEMにより観察したところ、抵抗変化層3における下部電極2側、即ち、成膜温度が低いときに形成された領域、に比べて、上部電極4側、即ち、成膜温度が高いときに形成された領域の方が大きくなっていた。

10

20

30

40

即ち、サンプル6-1の抵抗変化層3は、その厚さ方向に粒径分布を有していた。

# [0200]

上記のように作製したサンプルに対し、実施例1と同様にして、その抵抗変化比および保持特性を評価した。評価結果を以下の表12に示す。

# [0201]

# 【表12】

| サンプル  | 4.D | Т    |  |

|-------|-----|------|--|

| No.   | ⊿R  | (時間) |  |

| 6 – 1 | 220 | 350  |  |

10

#### [0202]

表12に示すように、成膜温度を変化させながら形成した抵抗変化層3とすることにより、同様の組成を有するサンプル1-4に比べて抵抗変化特性および保持特性を大幅に向上できた。これは、層を構成する材料の粒径など、層の膜質により元素Aの置換効果が異なるが、実施例4において検証した組成勾配を有する抵抗変化層の場合と同様に、層内に形成された粒径分布により、抵抗変化層3内に、抵抗変化特性および保持特性の発現に最も適した状態が実現した可能性が考えられる。

# [0203]

(実施例7)

実施例 7 では、実施例 1 で作製したメモリ素子 3 1 (サンプル 1 - 4 )を複数配列して、 5 × 5 のメモリアレイを作製し、その動作の検証を行った。

#### [ 0 2 0 4 ]

メモリアレイの動作確認は、選択した素子31におけるゲート25への電圧の印加によりトランジスタ21をON状態とし、ソース22と上部電極4との間に、SET電圧として2V(正バイアス電圧)、RESET電圧として・2V(負バイアス電圧、大きさ2V)、READ電圧として0.5V(正バイアス電圧)を印加して、サンプル1-4から出力される電流値を測定して行った。サンプル1-4に印加する各電圧のパルス幅は100nsとした。

30

20

# [0205]

動作確認の結果、上記メモリアレイでは、READ電圧の印加時に素子31から出力される電流値の測定により、任意のメモリ素子31に対してデータの記録および読出が可能であり、メモリアレイとして安定した動作が可能であることが確認できた。

# [0206]

(実施例8)

40

#### [0207]

評価した素子サンプルは実施例 1 と同様にして作製した。ただし、抵抗変化層 3 の作製にあたっては、ターゲットとして式 Z n ( F e  $_{2-x}$  M n  $_x$  )  $O_4$ で示される焼結体を用いた

# [0208]

形成した抵抗変化層3の組成は、実施例1と同様に確認した。また、実施例1と同様の手法により、形成した抵抗変化層3の結晶構造を評価したところ、以下の表13に示す全てのサンプルにおいて、抵抗変化層3を構成する材料がスピネル型の結晶構造を有することが確認できた。また、抵抗変化層3のシート抵抗値を評価したところ、×の値により、抵抗変化層のシート抵抗値が変化することが確認できた。

### [0209]

上記のように作製したサンプルに対し、実施例1と同様にして、その抵抗変化比および 保持特性を評価した。評価結果を、各サンプルにおけるxの値とともに以下の表13に示 す。

# [0210]

### 【表13】

| サンプル No. | ×     | ⊿R  | T (時間) |

|----------|-------|-----|--------|

| 8 – 1    | 0.05  | 35  | 25     |

| 8-2      | 0.10  | 50  | 30     |

| 8-3      | 0. 20 | 90  | 120    |

| 8 – 4    | 0.30  | 170 | 200    |

| 8-5      | 0.35  | 112 | 75     |

| 8-6      | 0.40  | 40  | 22     |

| 8 – 7    | 0.45  | 18  | 10     |

| 8-8      | 0.50  | 15  | 5      |

# [0211]

表 1 3 に示すように、抵抗変化層 3 を構成する酸化物について、式 Z n ( F e <sub>2-x</sub> M n <sub>x</sub> ) O<sub>4における</sub>×の値が 0 . 0 5 以上 0 . 5 以下の範囲のサンプルにおいて、高い抵抗変 化比を得ることができた。特に、×の値が0.2以上0.35以下の範囲のサンプルにお いて90以上のより高い抵抗変化比が得られた。

### [0212]

また、 表 1 3 に 示 す よ う に 、 抵 抗 変 化 層 3 を 構 成 す る 酸 化 物 に つ い て 、 式 Z n ( F e <sub>2 1</sub> <sub>∝</sub> M n <sub>∗</sub>) O ₄における × の値が 0 . 0 5 以上 0 . 5 以下の範囲のサンプルにおいて、高い 保持特性を得ることができた。特に、xの値が0.2以上0.3以下の範囲のサンプルに おいて時間Tは100時間以上となり、より高い保持特性が得られることがわかった。

# [0213]

これらの結果から、ZnFe<sub>2</sub>O<sub>4</sub>におけるFeを元素A(Mn)により部分的に置換し た酸化物である Z n ( F e <sub>2 - x</sub> M n <sub>x</sub> ) O ₄: 0 < x 0 . 5 を抵抗変化層に用いることに より、素子の抵抗変化比だけではなく保持特性も向上できることがわかった。この理由に ついては、上述したように、Mnイオンの価数が3価、4価および5価の間で変化するこ とが鍵になっていると思われる。

# 【産業上の利用可能性】

# [ 0 2 1 4 ]

以上説明したように、本発明によれば、抵抗変化特性および保持特性が従来よりも向上 した抵抗変化素子を得ることができる。このため、本発明の抵抗変化素子は信頼性が高く 、 不 揮 発 性 メ モ リ ヘ 好 適 に 適 用 で き る 。

# [0215]

本発明の抵抗変化素子は、メモリに限らず、様々な電子デバイスへの応用が可能であり 当該デバイスとして、例えば、情報通信端末などに使用されるスイッチング素子、セン サ、画像表示装置などへの応用が考えられる。

### 【図面の簡単な説明】

# [ 0 2 1 6 ]

【 図 1 】 本 発 明 の 抵 抗 変 化 素 子 の 一 例 を 模 式 的 に 示 す 断 面 図 で あ る 。

【図2】本発明の抵抗変化素子の別の一例を模式的に示す断面図である。

10

20

30

- 【図3】本発明の抵抗変化素子のまた別の一例を模式的に示す断面図である。

- 【図4】本発明の抵抗変化素子のさらにまた別の一例を模式的に示す断面図である。

- 【図5】本発明の抵抗変化素子の上記とは別の一例を模式的に示す断面図である。

- 【図6】本発明の抵抗変化素子の上記とは別の一例を模式的に示す断面図である。

- 【図7】本発明の抵抗変化素子の上記とは別の一例を模式的に示す断面図である。

- 【図8】本発明の抵抗変化素子の上記とは別の一例を模式的に示す断面図である。

- 【図9】本発明の抵抗変化素子を備える抵抗変化型メモリ(素子)の一例を示す模式図である。

- 【図10】本発明の抵抗変化素子を備える抵抗変化型メモリ(素子)の一例を模式的に示す断面図である。

- 【図 1 1 】本発明の抵抗変化素子を備える抵抗変化型メモリにおける情報の記録および読出方法の一例を説明するための図である。

- 【図12】本発明の抵抗変化素子を備える抵抗変化型メモリにおける情報の読出方法の一例を説明するための図である。

- 【図13】本発明の抵抗変化素子を備える抵抗変化型メモリ(アレイ)の一例を示す模式図である。

- 【図14】本発明の抵抗変化素子を備える抵抗変化型メモリ(アレイ)の別の一例を示す 模式図である。

- 【図 1 5 】本発明の抵抗変化素子を備える抵抗変化型メモリ(アレイ)のまた別の一例を示す模式図である。

- 【図16A】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16B】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16C】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16D】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16E】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16F】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16G】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図16H】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17A】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17B】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17C】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17D】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17E】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17F】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17G】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17日】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17Ⅰ】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17」】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17K】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17L】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図17M】本発明の抵抗変化型メモリの製造方法の一例を模式的に示す工程図である。

- 【図18】実施例6において抵抗変化層3を形成する際の成膜温度のプロファイルを示す図である。

# 【符号の説明】

- [0217]

- 1 抵抗变化素子

- 2 下部電極

- 3 抵抗变化層

- 3 a 、 3 b 、 3 c 、 3 d 、 3 e 抵抗変化膜

- 4 上部電極

10

20

30

40

10

20

30

40

```

5

抵抗膜

1 1

基 板

12 多層構造体(積層体)

21 トランジスタ

2 2

ソース

2 3

ドレイン

2 4

プラグ

2 5

ゲート絶縁膜

2 6 ゲート電極

プラグ

2 7

28 層間絶緣層

29 素子分離部

31、31a (抵抗変化型)メモリ素子

3 2

ビット線

3 3 ワード線

34、34a (抵抗変化型)メモリ素子

35 選択素子

3 6 、 3 6 a 、 3 6 b 、 3 6 c パストランジスタ

37 パストランジスタ群

38 参照素子群

4 1 参照素子

42 (メモリ素子31の)出力

4 3

(参照素子41の)出力

44a、44b 負帰還増幅回路

(負帰還増幅回路44aにより増幅した)出力

4 5

4 6

(負帰還増幅回路44bにより増幅した)出力

47 差動増幅回路

出力信号

4 8

5 1

(抵抗変化型)メモリアレイ

5 2

(抵抗変化型)メモリアレイ

5 3 (抵抗変化型)メモリアレイ

6 1

保護絶縁膜

6 2

プラグ用開口部

63 バリアメタル

6 4

プラグメタル

6 5

保護絶縁膜

プラグ用開口部

6 6

6 7

密着用メタル

6 8

配線用メタル

6 9

プラグ

70 水素バリア層

7 1

雷 極

7 2

水素バリア層

7 3 保護絶縁膜

7 4

```

プラグ用開口部

76 (抵抗変化型)メモリ素子

プラグ

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16A】

【図16C】

【図16B】

【図16D】

# 【図16G】

# 【図16F】

# 【図16H】

# 【図17A】

# 【図17C】

# 【図17B】

【図17D】

# 【図17M】

# 【図18】