## (12) 发明专利

(10) 授权公告号 CN 107766172 B

(45) 授权公告日 2022.06.28

(21) 申请号 201710376331.9

(51) Int.CI.

(22) 申请日 2017.05.25

G06F 11/10 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 107766172 A

(56) 对比文件

(43) 申请公布日 2018.03.06

CN 103839595 A, 2014.06.04

(30) 优先权数据

CN 101110048 A, 2008.01.23

62/375,381 2016.08.15 US

CN 103811076 A, 2014.05.21

15/286,460 2016.10.05 US

CN 101681283 A, 2010.03.24

(73) 专利权人 三星电子株式会社

US 5740188 A, 1998.04.14

地址 韩国京畿道水原市

审查员 薛聪帆

(72) 发明人 牛迪民 张牧天 郑宏忠 金炫中

宋元亨 崔璋石

(74) 专利代理机构 北京铭硕知识产权代理有限公司 11286

权利要求书2页 说明书12页 附图8页

(54) 发明名称

用于DDR SDRAM接口的DRAM辅助纠错方法

(57) 摘要

提供了用于DDR SDRAM接口的DRAM辅助纠错机制。一种使用双倍数据速率(DDR)接口来纠正动态随机存取存储器模块(DRAM)的存储器错误的方法包括：使用存储器控制器进行包括多个突发的存储器事务，以将数据从DRAM的数据芯片发送到存储器控制器；使用DRAM的ECC芯片检测一个或多个错误；使用DRAM的ECC芯片确定具有错误的突发的数量；确定具有错误的突发的数量是否大于阈值数量；确定错误的类型；基于确定的错误的类型来指引存储器控制器，其中，DRAM包括每个存储器通道单个ECC芯片。

1. 一种使用双倍数据速率接口来纠正动态随机存取存储器模块的存储器错误的方法，所述方法允许存储器控制器在来自动态随机存取存储器模块的辅助下识别芯片故障，同时使用减少的纠错码芯片开销或减少的内部预取尺寸，所述方法包括：

利用存储器控制器进行包括多个突发的存储器事务，以将数据从动态随机存取存储器模块的数据芯片发送到存储器控制器；

使用动态随机存取存储器模块的纠错码芯片来检测一个或多个错误；

使用动态随机存取存储器模块的纠错码芯片来确定具有错误的突发的数量；

确定具有错误的突发的数量是否大于阈值数量；

确定错误的类型；以及

基于所确定的错误的类型来指引存储器控制器，

其中，动态随机存取存储器模块包括每个存储器通道单个纠错码芯片。

2. 根据权利要求1所述的方法，其中，使用动态随机存取存储器模块的纠错码芯片检测一个或多个错误的步骤包括：使用纠错码芯片对每个突发执行奇偶校验。

3. 根据权利要求1所述的方法，所述方法还包括：当具有错误的突发的数量不大于阈值数量时，指引存储器控制器重试从动态随机存取存储器模块的存储器读取。

4. 根据权利要求3所述的方法，所述方法还包括：当存储器控制器重试存储器读取时检测另外的错误；以及

确定另外的错误是否具有与检测到的一个或多个错误相同的错误模式。

5. 根据权利要求4所述的方法，所述方法还包括：当确定另外的错误具有与检测到的一个或多个错误不同的错误模式时，指引存储器控制器再次重试从动态随机存取存储器模块的存储器读取。

6. 根据权利要求4所述的方法，所述方法还包括：当确定另外的错误具有与检测到的一个或多个错误相同的错误模式时，识别出硬错误；

指引存储器控制器辅助动态随机存取存储器模块进行纠错；以及

记录错误的地址。

7. 根据权利要求1所述的方法，所述方法还包括：当具有错误的突发的数量大于阈值数量时，确定所述一个或多个错误是否对应于同一芯片的同一引脚。

8. 根据权利要求7所述的方法，所述方法还包括：当确定所述一个或多个错误对应于动态随机存取存储器模块的同一芯片的同一引脚时，确定所述一个或多个错误对应于引脚故障；以及

当确定所述一个或多个错误不对应于同一芯片的同一引脚时，确定所述一个或多个错误对应于芯片故障。

9. 根据权利要求8所述的方法，其中，指引存储器控制器的步骤包括：当所述一个或多个错误对应于引脚故障或芯片故障时，指引存储器控制器辅助芯片删除检测。

10. 根据权利要求1所述的方法，所述方法还包括：当具有错误的突发的数量大于阈值数量时，确定所述一个或多个错误是否对应于动态随机存取存储器模块的一个以上的芯片；

当确定所述一个或多个错误对应于动态随机存取存储器模块的同一芯片时，将动态随机存取存储器模块的相应芯片标记为擦除；以及

当确定所述一个或多个错误对应于动态随机存取存储器模块的一个以上的芯片时,识别出致命的错误。

11.根据权利要求1所述的方法,所述方法还包括:当具有错误的突发的数量大于阈值数量时,确定动态随机存取存储器模块的另一个芯片是否先前已经被擦除;以及

当动态随机存取存储器模块的所述另一个芯片先前已经被擦除时,识别出致命的错误。

## 用于DDR SDRAM接口的DRAM辅助纠错方法

[0001] 本申请要求在美国专利商标局于2016年8月15日提交的美国临时申请62/375,381和于2016年10月5日提交的美国非临时申请15/286,460的优先权和权益,这些美国申请的全部内容通过引用包含于此。

### 技术领域

[0002] 根据本发明的实施例的一个或更多个方面涉及用于存储器纠错的方法和机制。

### 背景技术

[0003] 双倍数据速率同步动态随机存取存储器 (DDR SDRAM) 是计算机中使用的一种类型的存储器集成电路 (IC)。DDR SDRAM能够通过使用电子数据和时钟信号的时序控制来实现更快的传输速率,并且能够在时钟信号的上升沿和下降沿传输数据,从而与利用相同时钟频率的单倍数据速率 (SDR) SDRAM接口相比,有效地加倍数据总线带宽,并且实现几乎两倍的带宽。

[0004] 在数据存储期间,不同代的DRAM能够使用纠错码 (ECC) 存储器来检测并有时纠正常见类型的数据损坏。ECC存储器通过使用奇偶校验而不受单比特错误的影响。在DRAM系统中,奇偶校验通过以下操作来完成:存储表示存储在存储器(例如,存储在奇偶校验装置中,或者存储在DRAM模块的ECC芯片中)的数据(例如,一个字节的数据)的奇偶校验(奇数或偶数)的冗余奇偶校验位,独立地计算奇偶校验,并且将存储的奇偶校验与计算的奇偶校验进行比较来检测是否发生了数据错误/存储器错误。

[0005] 因此,为了确保可对应于数据字或数据符号的从DRAM模块(例如,双列直插式存储器模块 (DIMM))恢复的数据与写入DRAM模块的数据相同,ECC可以纠正当数据的一个或更多个位被翻转到错误状态时出现的错误。

[0006] 也就是说,通过使用ECC冗余,ECC芯片能够进行单纠错双检错 (SEC-DED),这意味着ECC芯片能够检测在单个突发中出现的两个错误的存在,并且在孤立地发生时也能够纠正单个错误比特。也就是说,如果一个数据芯片被损坏或丢失,则通过使用剩余的数据芯片的数据和ECC芯片的ECC数据,可以重构损坏或丢失的数据芯片的数据。

[0007] 另外,DRAM系统可以具有用于擦除或禁用非功能数据芯片的芯片删除 (chipkill) 机制。用于DDR4的各种芯片删除机制的每个存储器通道使用两个或更多个ECC装置/芯片来检测、定位和擦除非功能芯片。

[0008] 例如,正常DDR4具有8n的预取长度、突发长度8(即,每个存储器事务8个突发)以及64位的存储器通道宽度,其中,n是相应系统架构中使用的数据的接口宽度的位数(例如,如果接口宽度为4位,则相应DDR4系统的预取长度为32位)。因此,DDR4将针对每个存储器事务发送512位。

[0009] 为了继续增加DDR接口带宽,新的DDR接口可以增加预取长度。这种新的DDR接口可以具有16n的预取长度,这是当前DDR4接口的预取长度的两倍。因此,新的DDR接口针对每个存储器事务传输两倍通过DDR4系统传输的数据量。这种新的DDR接口也可以具有突发长度

16(即,在每个单独的存储器事务中16个数据突发)以及每个存储器通道32位的存储器通道宽度,并且因此也将每个存储器事务每个存储器通道传输512位。然而,这种DDR接口具有每个DIMM两个存储器通道,每个DIMM是在包括用于实现与计算机主板的连接的多个芯片引脚的电路板上具有多个DRAM芯片的模块。DDR DIMM的两个存储器通道有效地彼此独立地工作。

[0010] 尽管具有比DDR4更窄的存储器通道,但是利用被配置为存储和传输用于每个存储器通道的数据的八个数据装置(例如,4位数据芯片),新的DDR接口具有每个存储器通道32位的数据宽度。利用用于每个存储器通道的一个4位ECC芯片,这种新的DDR接口还具有每个存储器通道4位的ECC宽度。因此,为了补偿具有DDR4的存储器通道宽度的一半,这种新的DDR接口具有DDR4的两倍的突发长度。因为这种新的DDR接口具有两个存储器通道,每个存储器通道具有专用于存储数据的八个4位数据芯片,所以将存在每个突发总共六十四位的存储器数据。

[0011] 此外,与具有每个存储器通道两个ECC芯片的DDR4不同,这种新的DDR接口可具有每个存储器通道单个ECC芯片,或者甚至具有每个DIMM单个ECC芯片,以保护用于存储数据的16个数据芯片。因此,与DDR4相比,新的DDR接口可以具有减少的ECC开销。因此,如果新的DDR接口使用每个存储器通道一个ECC芯片,则对于每个突发,将存在对应于两个4位ECC芯片的8位ECC数据,DIMM的两个存储器通道的每个存储器通道中存在一个ECC芯片。因此,这样的新的DDR接口将针对每个突发传输72位数据。

[0012] 随着系统ECC开销随数据宽度的相应减小而增加,可能难以使用当前的DDR4技术来维持DDR可靠性、可用性和可服务性(RAS)。此外,由于每个DIMM的存储器通道的增加的数量,芯片删除技术需要额外的ECC开销。

[0013] 因此,以下做法会是有用的:提供纠错和数据恢复的新颖方法,并且提供能够在没有来自存储器控制器的辅助的情况下内部地纠正一些类型的存储器错误,并且能够指引存储器控制器对DRAM不能进行内部纠正的其它类型的错误进行辅助存储器纠错的DRAM DIMM。

## 发明内容

[0014] 本公开的实施例的多个方面旨在提供一种使用DRAM中的ECC来实现纠错的新型DDR接口。

[0015] 根据本发明的实施例,提供了一种使用双倍数据速率(DDR)接口来纠正动态随机存取存储器模块(DRAM)的存储器错误的方法,所述方法包括:利用存储器控制器进行包括多个突发的存储器事务,以将数据从DRAM的数据芯片发送到存储器控制器;使用DRAM的ECC芯片检测一个或更多个错误;使用DRAM的ECC芯片确定具有错误的突发的数量;确定具有错误的突发的数量是否大于阈值数量;确定错误的类型;以及基于所确定的错误的类型来指引存储器控制器,其中,DRAM包括每个存储器通道单个ECC芯片。

[0016] 使用DRAM的ECC芯片检测一个或更多个错误的步骤可以包括:使用ECC芯片对每个突发执行奇偶校验。

[0017] 所述方法还可以包括:当具有错误的突发的数量不大于阈值数量时,指引存储器控制器重试从DRAM的存储器读取。

[0018] 所述方法还可以包括:当存储器控制器重试存储器读取时,检测另外的错误,以及确定另外的错误是否具有与检测到的一个或更多个错误相同的错误模式。

[0019] 所述方法还可以包括:当确定另外的错误具有与检测到的一个或更多个错误不同的错误模式时,指引存储器控制器再次重试从DRAM的存储器读取。

[0020] 所述方法还可以包括:当确定另外的错误具有与检测到的一个或更多个错误相同的错误模式时,识别硬错误,指引存储器控制器辅助DRAM进行纠错,并且记录错误的地址。

[0021] 所述方法还可以包括:当具有错误的突发的数量大于阈值数量时,确定所述一个或更多个错误是否对应于同一芯片的同一引脚。

[0022] 所述方法还可以包括:当确定所述一个或更多个错误对应于DRAM的同一芯片的同一引脚时,确定所述一个或更多个错误对应于引脚故障;当确定所述一个或更多个错误不对应于同一芯片的同一引脚时,确定所述一个或更多个错误对应于芯片故障。

[0023] 指引存储器控制器的步骤可以包括:当所述一个或更多个错误对应于DQ故障或芯片故障时,指引存储器控制器辅助芯片删除检测。

[0024] 所述方法还可以包括:当具有错误的突发的数量大于阈值数量时,确定所述一个或更多个错误是否对应于DRAM的一个以上的芯片;当确定所述一个或更多个错误对应于DRAM的同一芯片时,将DRAM的相应芯片标记为擦除;当确定所述一个或更多个错误对应于DRAM的一个以上的芯片时,识别致命的错误。

[0025] 所述方法还可以包括:当具有错误的突发的数量大于阈值数量时,确定DRAM的另一个芯片是否先前已经被擦除;当DRAM的另一个芯片先前已经被擦除时,识别致命的错误。

[0026] 根据本发明的另一实施例,提供了一种被配置为经由双倍数据速率(DDR)接口与存储器控制器进行通信的动态随机存取存储器模块(DRAM),所述DRAM包括:两个存储器通道,每个存储器通道包括多个数据芯片和单个纠错码(ECC)芯片,所述多个数据芯片被配置为在其上存储数据,并且被配置为在对应于单个存储器事务的多个突发的每个的期间将数据传输到存储器控制器一次,ECC芯片被配置为确定对应于一个或更多个数据芯片的具有存储器错误的多个突发的数量。

[0027] ECC芯片可以被配置为检测错误,并且可以被配置为将检测到的错误的类型确定为DQ故障、芯片故障、软错误或硬错误中的一种。

[0028] ECC芯片可以被配置为根据确定的检测到的错误的类型指引存储器控制器辅助芯片删除检测或者辅助纠错。

[0029] ECC芯片可以被配置为当ECC芯片已经检测到错误时向存储器控制器发出命令,使得存储器控制器执行ECC芯片的信息读出。

[0030] DRAM还可以包括连接到ECC芯片的单个引脚,ECC芯片被配置为当ECC芯片通过使用1位ECC标志检测到错误时在存储器事务期间警告存储器控制器。

[0031] 数据芯片和ECC芯片可以被配置为在每个存储器事务期间向存储器控制器传送除了多个突发之外的额外的突发,以向存储器控制器提供ECC芯片的读出信息。

[0032] 根据本发明的另一实施例,提供了一种存储器系统,所述存储器系统包括:存储器控制器;动态随机存取存储器模块(DRAM),包括数据芯片和纠错码(ECC)芯片,其中,每个ECC芯片被配置为纠正DRAM的相应存储器通道的一些错误,其中,存储器控制器被配置为辅助ECC芯片纠正ECC芯片不能纠正的其它错误。

- [0033] 每个ECC芯片可以包括用于在检测到错误时向存储器控制器发送1位ECC标志的引脚。

- [0034] DRAM可以包括多个存储器通道，并且DRAM的每个存储器通道可以包括单个ECC芯片。

## 附图说明

- [0035] 将参照说明书、权利要求书和附图来领会和理解本发明的这些和其它方面，其中：

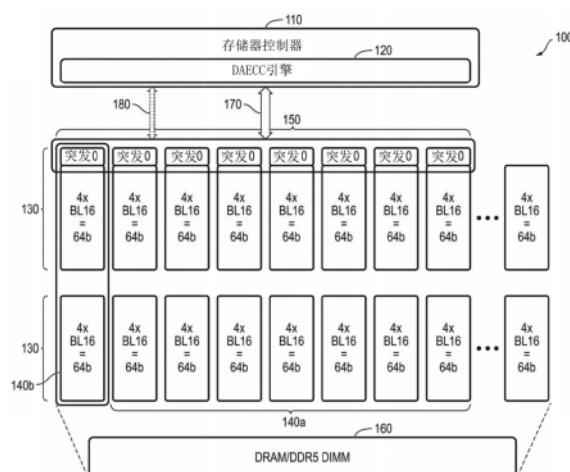

- [0036] 图1是根据本发明的实施例的描绘用于DDR接口的纠错机制的框图；

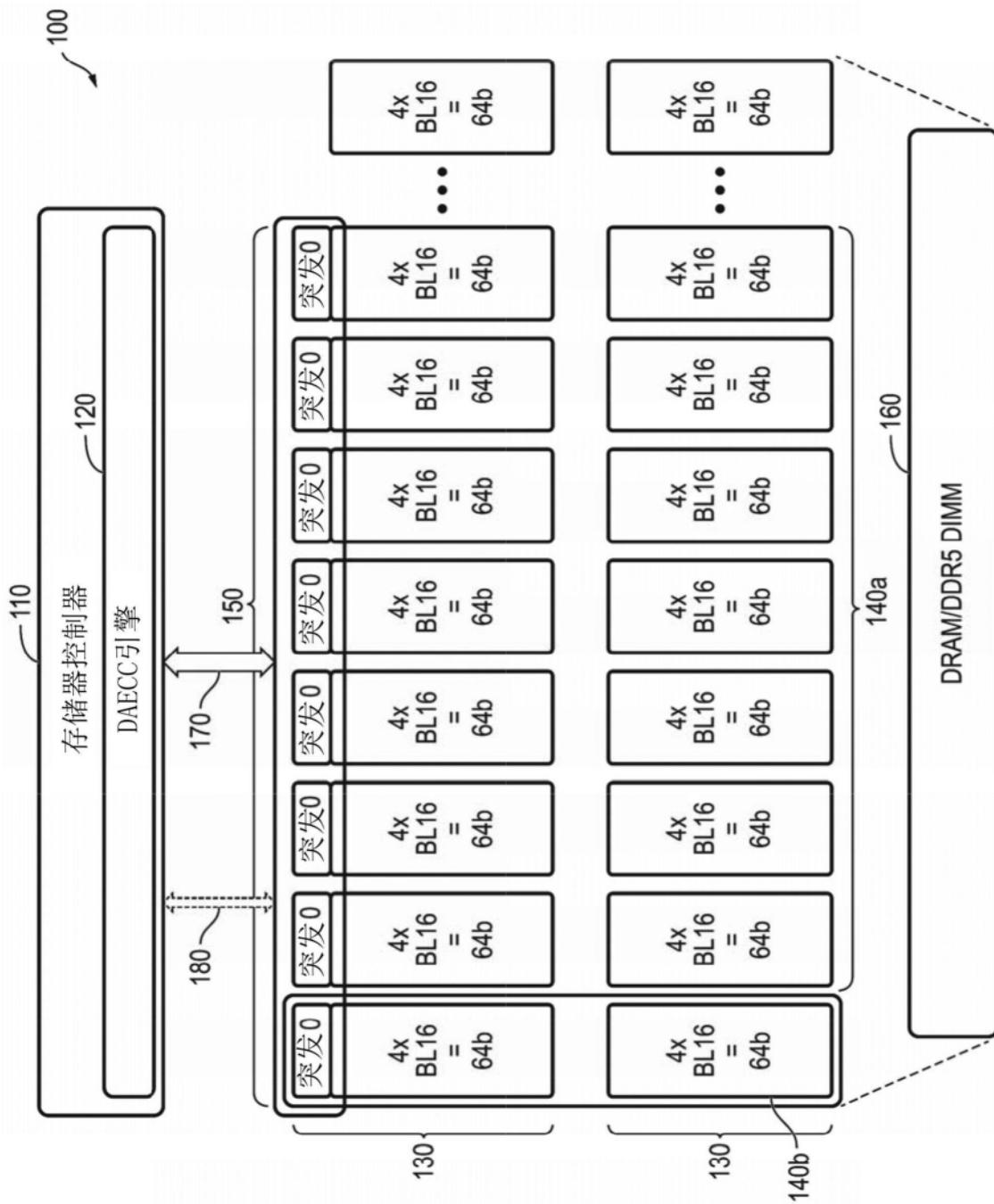

- [0037] 图2是根据本发明的另一实施例的描绘用于DDR接口的纠错机制的框图；

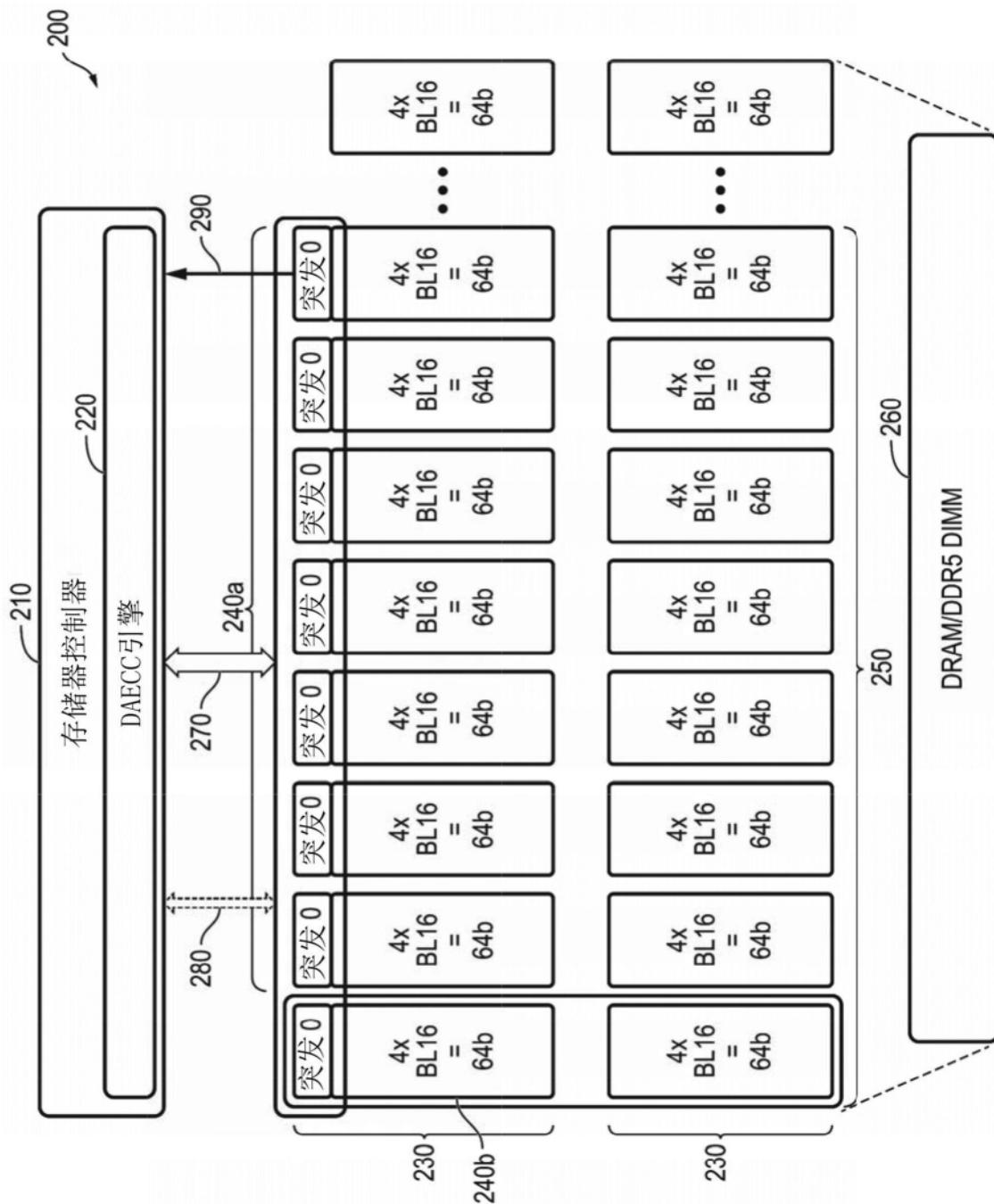

- [0038] 图3是根据本发明的又一实施例的描绘用于DDR接口的纠错机制的框图；

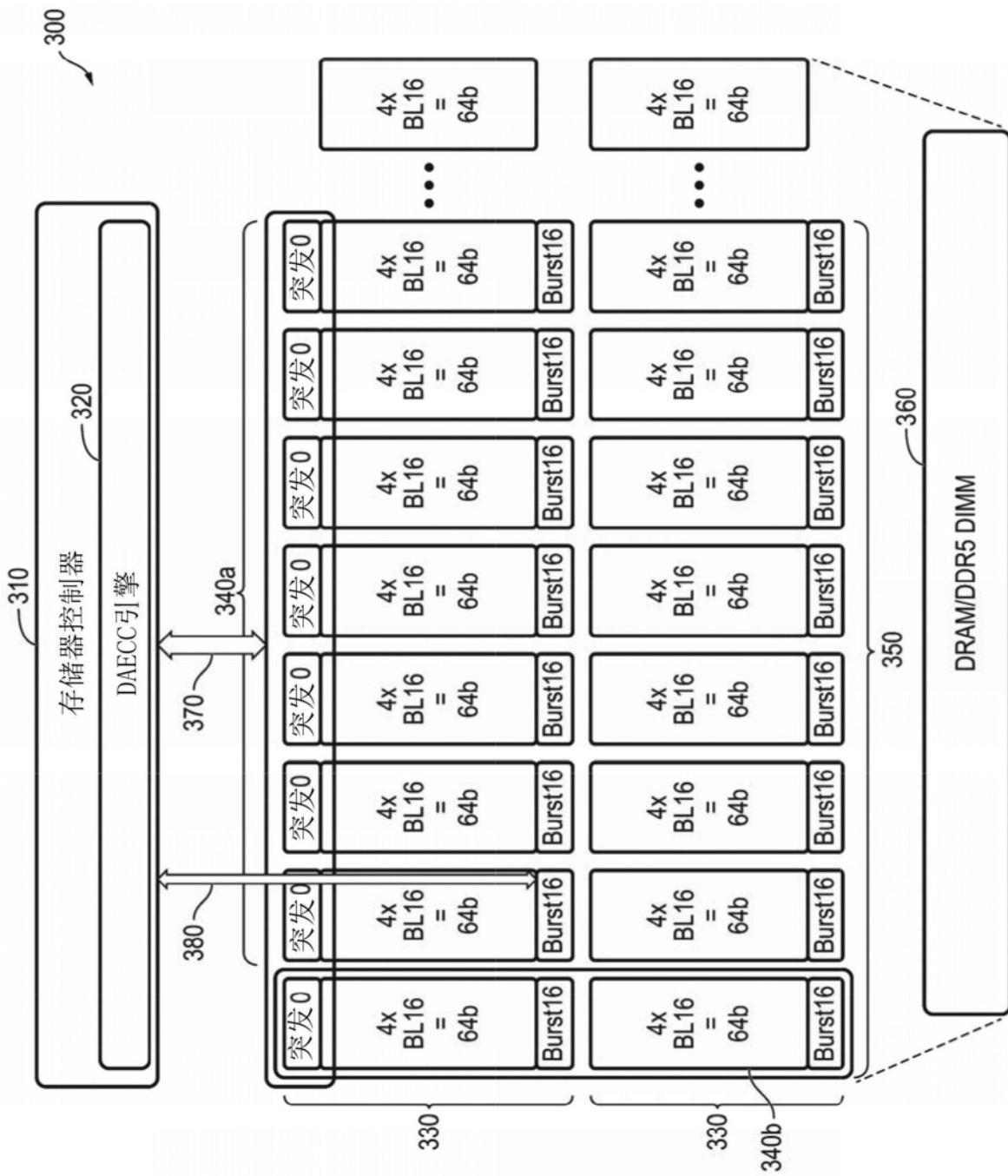

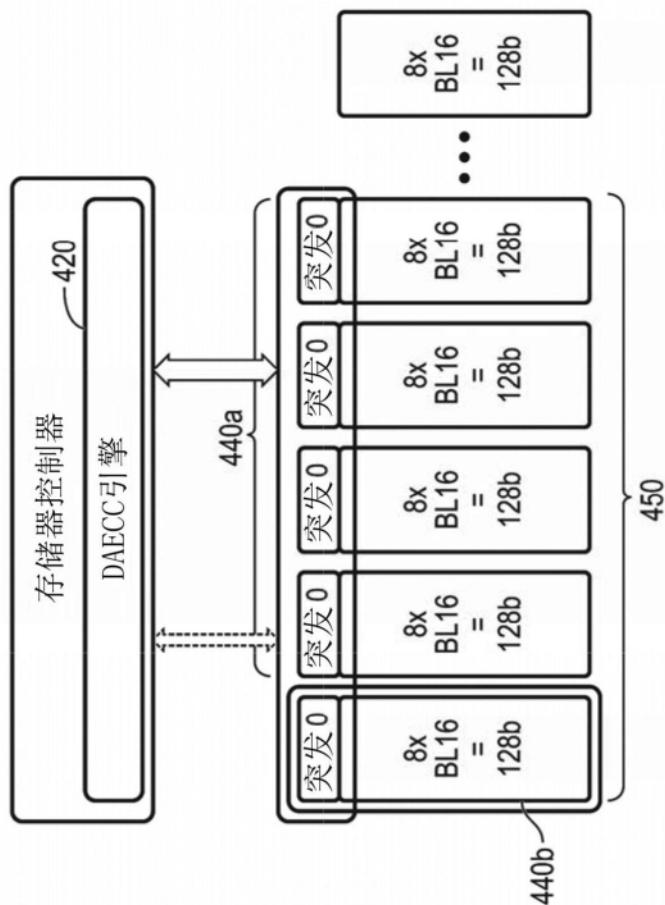

- [0039] 图4是根据本发明的又一实施例的描绘用于DDR接口的纠错机制的框图；

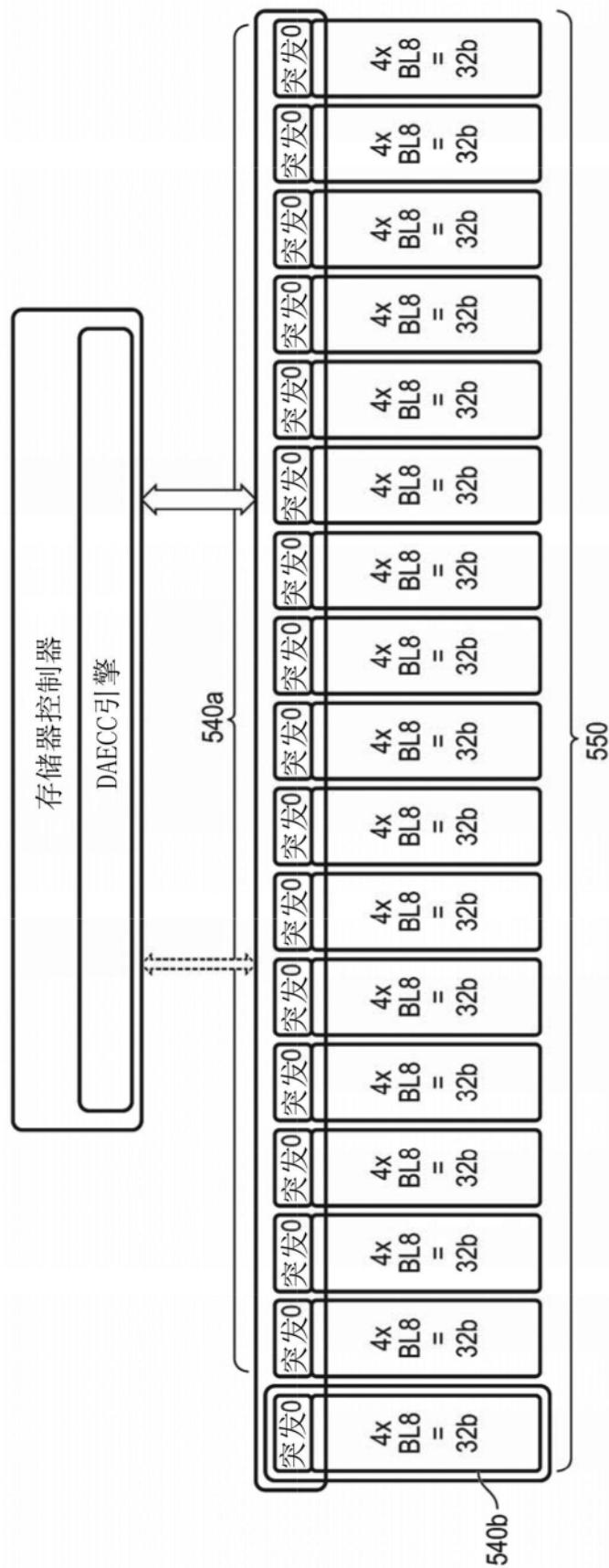

- [0040] 图5是根据本发明的又一实施例的描绘用于DDR接口的纠错机制的框图；

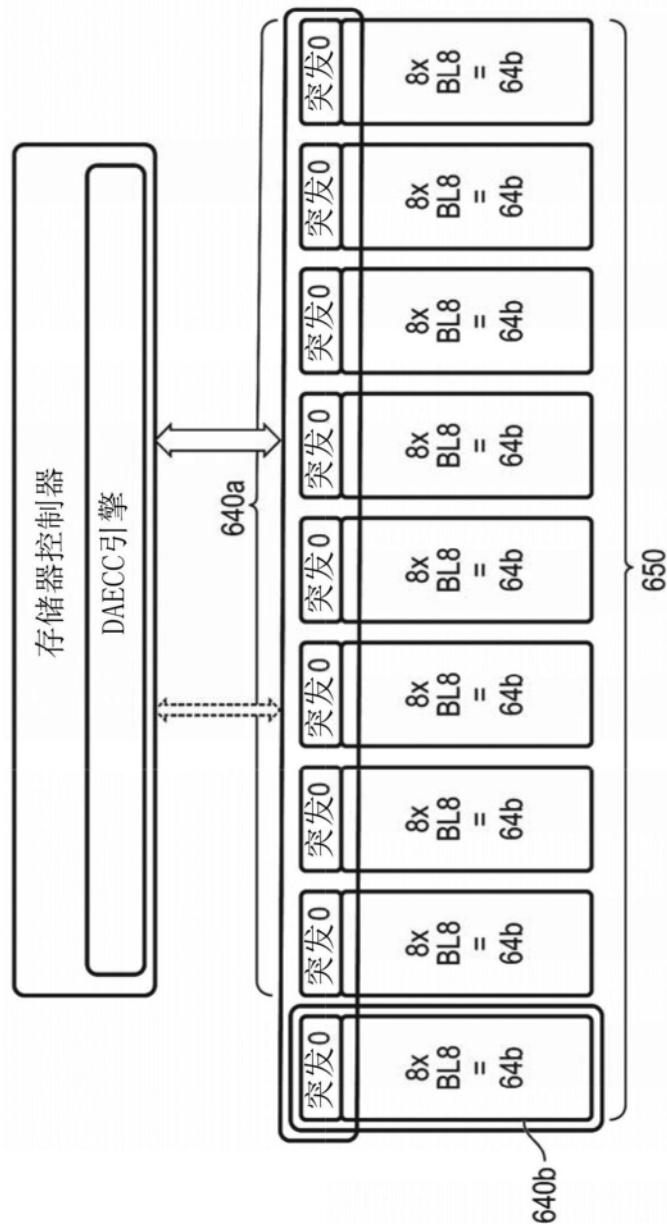

- [0041] 图6是根据本发明的又一实施例的描绘用于DDR接口的纠错机制的框图；

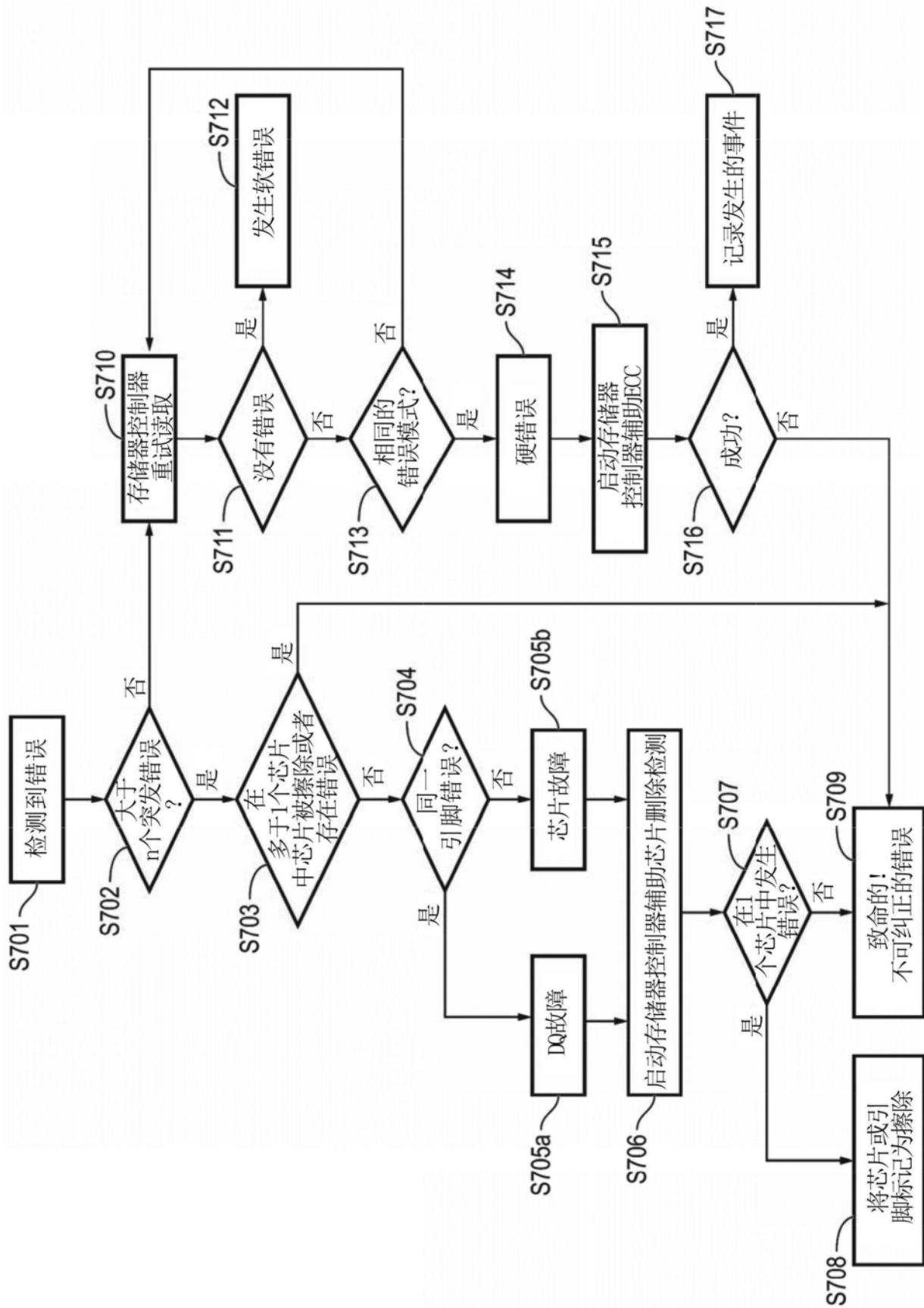

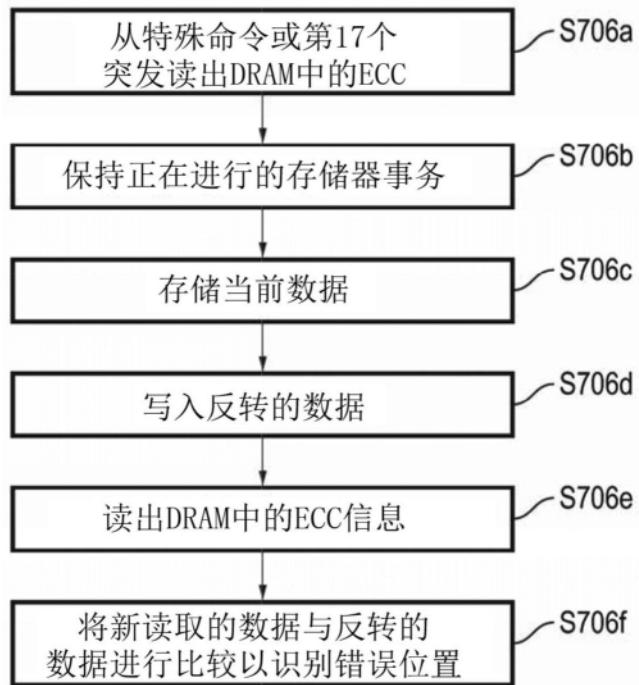

- [0042] 图7A和图7B是描述使用根据本发明的一个或更多个实施例的DRAM辅助纠错码(DAECC)机制来检测错误、确定错误的类型、处理错误的流程图。

## 具体实施方式

[0043] 通过参照以下实施例和附图的详细描述，可以更容易地理解发明构思的特征及其实现方法。在下文中，将参照附图更详细地描述示例实施例，在附图中，相同的附图标记始终表示相同的元件。然而，本发明可以以各种不同的形式实施，并且不应被解释为仅限于这里所示的实施例。相反，这些实施例被提供为示例，使得本公开将是彻底和完整的，并且将把本发明的多个方面和特征全面地传达给本领域技术人员。因此，可以不描述对于本领域普通技术人员完全理解本发明的多个方面和特征所不必要的工艺、元件和技术。除非另有说明，否则同样的附图标记在附图和书面描述中始终表示同样的元件，因此将不重复其描述。在附图中，为了清楚起见，可以夸大元件、层和区域的相对尺寸。

[0044] 应当理解的是，尽管术语“第一”、“第二”、“第三”等在这里可以用于描述各种元件、组件、区域、层和/或部分，但是这些元件、组件、区域、层和/或部分不应受这些术语的限制。这些术语用于将一个元件、组件、区域、层或部分与另一个元件、组件、区域、层或部分区分开。因此，在不脱离本发明的精神和范围的情况下，下面描述的第一元件、第一组件、第一区域、第一层或第一部分可以被称为第二元件、第二组件、第二区域、第二层或第二部分。

[0045] 为了便于解释，在这里可以使用例如“在……下面”、“在……下方”、“下面的”、“在……之下”、“在……之上”、“上面的”等的空间相对术语来描述如图中所示的一个元件或特征与另一个元件或特征的关系。应当理解的是，除了附图中描绘的方位之外，空间相对术语旨在包括装置在使用或操作中的不同方位。例如，如果附图中的装置被翻转，则被描述为“在”其它元件或特征“下方”或“下面”或“之下”的元件将随后被定位为在其它元件或特征“之上”。因此，“在……下方”和“之下”的示例术语可以包括上面和下面两种方位。装置可以被另外定位(例如，旋转90度或在其它方位)，并且应该相应地解释本文使用的空间相对描述语。

[0046] 应当理解的是，当元件、层、区域或组件被称作“在”另一元件、层、区域或组件

“上”、“连接到”或“结合到”另一元件、层、区域或组件时，该元件、层、区域或组件可以直接在另一元件、层、区域或组件上，直接连接到或直接结合到另一元件、层、区域或组件，或者可以存在一个或更多个中间元件、层、区域或组件。此外，还将理解的是，当元件或层被称为在两个元件或层之间时，所述元件或层可以是两个元件或层之间的唯一元件或层，或者也可以存在一个或更多个中间元件或层。

[0047] 在以下示例中，x轴、y轴和z轴不限于直角坐标系的三个轴，并且可以在更广泛的意义上被解释。例如，x轴、y轴和z轴可以彼此垂直，或者可以表示彼此不垂直的不同方向。

[0048] 这里使用的术语是仅用于描述具体示例实施例的目的，而不意图限制本发明。如这里所使用的，除非上下文另外清楚指出，否则单数形式的“一个(种)”也意图包括复数形式。还将理解的是，当在本说明书中使用术语“包含”和/或“包括”及其变型时，说明存在所陈述的特征、整体、步骤、操作、元件和/或组件，但不排除存在或附加一个或更多个其它特征、整体、步骤、操作、元件、组件和/或它们的组。如这里所使用的，术语“和/或”包括一个或更多个相关所列项的任意组合和所有组合。当诸如“……中的至少一个”的表述在一列元件(要素)之后时，修饰整列元件(要素)，而不修饰该列中的个别元件(要素)。

[0049] 如这里所使用的，术语“基本上”、“大约”和类似术语用作近似术语而不用作程度术语，并且旨在说明本领域普通技术人员将认识到的测量值或计算值的固有偏差。此外，在描述本发明的实施例时使用“可以”是指“本发明的一个或更多个实施例”。如这里所使用的，术语“使用”及其变型可以认为分别与术语“利用”及其变型同义。此外，术语“示例性”意图指示例或说明。

[0050] 当可以不同地实施特定实施例时，可以与所描述的顺序不同地执行具体的处理顺序。例如，两个连续描述的处理可以基本上同时执行，或者以与所描述的顺序相反的顺序执行。

[0051] 这里描述的根据本发明的实施例的电子或电气装置和/或任何其它相关装置或组件可以利用任何合适的硬件、固件(例如专用集成电路)、软件或软件、固件和硬件的组合来实施。例如，这些装置的各种组件可以形成在一个集成电路(IC)芯片上或单独的IC芯片上。此外，这些装置的各种组件可以在柔性印刷电路膜、载带封装件(TCP)、印刷电路板(PCB)上实施，或形成在一个基底上。此外，这些装置的各种组件可以是在一个或更多个计算装置中的一个或更多个处理器上运行的执行计算机程序指令并与执行这里所描述的各种功能的其它系统组件交互的进程或线程。计算机程序指令被存储在可以使用标准存储装置(例如，随机存取存储器(RAM))而在计算装置中实施的存储器中。计算机程序指令也可以存储在其它非暂时性计算机可读介质中，例如CD-ROM、闪存等。此外，本领域技术人员应该认识到，在不脱离本发明的示例性实施例的精神和范围的情况下，各种计算装置的功能可以被组合或集成到单个计算装置中，或者特定计算装置的功能可以分布遍及一个或更多个其它计算装置。

[0052] 除非另有定义，否则这里使用的所有术语(包括技术术语和科学术语)具有与本发明所属领域的普通技术人员所通常理解的含义相同的含义。还将理解的是，除非这里明确地如此定义，否则诸如在通用的字典中定义的术语应该被解释为具有与它们在相关领域和/或本说明书的上下文中的含义一致的含义，而不应以理想化或过于形式化的含义来解释。

[0053] 下面参照图1、图2和图3描述的本发明的实施例能够提供基本的芯片删除(chipkill)。尽管缺少与DDR4的芯片删除机制相同的覆盖范围,但是新的DDR接口能够在仅具有每个存储器通道一个ECC芯片的情况下提供单一裸片/芯片纠正。另外,下面描述的机制能够使用从ECC芯片提供的ECC信息来识别数据芯片何时故障。

[0054] 图1是描绘根据本发明的实施例的用于DDR接口的纠错机制的框图。本实施例使用每个存储器事务十六个突发,并且能够使用DRAM中的ECC在多个突发之内保护一个数据芯片中的数据。当DRAM中的ECC确定发生系统ECC错误时,本实施例还允许DRAM DIMM使用系统/存储器控制器ECC在一个或更多个突发内通过允许存储器控制器读出DRAM中的ECC的信息来保护来自多个芯片的数据。

[0055] 如图1中可见,本发明的实施例的系统100包括存储控制器110,存储器控制器110具有存储在其中的DRAM辅助纠错码(DAECC)引擎120。存储器控制器110能够将数据传输到双倍数据速率同步动态随机存取存储器双列直插式存储器模块(DDR DIMM)/DRAM 160的各种芯片140a,并且能够从双倍数据速率同步动态随机存取存储器双列直插式存储器模块(DDR DIMM)/DRAM 160的各种芯片140a接收数据。在图1中,示出了DRAM 160的一个存储器通道150。存储器控制器110进行存储器事务130,存储器事务130用于通过正常的读取和写入处理与DRAM 160交换“正常”数据170。在本实施例中,DRAM 160的每个芯片140a经由芯片的四个引脚提供四位信息。

[0056] DRAM 160的每个存储器通道150具有用于接收、存储和发送数据的八个4位数据芯片(例如,8个数据装置)140a。与使用每个DIMM/DRAM 的存储器通道两个ECC芯片的DDR4不同,本实施例的DRAM 160具有每个存储器通道150单个4位ECC芯片(例如,一个奇偶校验装置或奇偶校验芯片)140b,用于将ECC数据传输到存储器控制器110。尽管仅具有每个存储器通道单个ECC芯片140b,但是如以下将讨论的,本实施例的DRAM 160能够提供系统内纠错和基本芯片删除能力。

[0057] 在本实施例中,DRAM 160利用存储器控制器110使用突发进行存储器事务130,从而DRAM 160重复地发送数据,同时省略了在单独事务中发送每条数据另外通常需要的其它步骤。因此,尽管在特定条件下仅限于有限的时间段,但是DRAM 160能够比没有突发的情况更快速地传输数据。

[0058] 为了补偿DRAM 160的较窄的存储器通道宽度,DRAM 160具有突发长度16,该突发长度为利用DDR4的DIMM(具有突发长度8)的突发长度的两倍。也就是说,为了补偿两个存储器通道150中的每一个仅具有利用DDR4的存储器通道的数据宽度的一半,当与DDR4相比时,DRAM 160能够针对每个存储器事务130在内部预取两倍数量的存储在4位芯片140a中的每个上的数据的突发。

[0059] 因此,对于每个突发,每个存储器通道150发送36位(即,对于九个芯片140a和140b的每个,每个芯片为4位),数据宽度是每个存储器通道150为32位,ECC宽度是每个存储器通道150为4位。这对应于每个通道每个存储器事务130总共576位(即,36位/突发乘以16个突发/存储器事务130),整个数据块为512位,其余的64位对应于存储器通道150的ECC芯片140b的ECC数据。

[0060] 另外,与DDR4不同,本实施例的系统100能够在没有来自存储器控制器110的辅助的情况下在DRAM 160内部实现纠错。DRAM 160的DRAM中的ECC执行内部纠错而不与存储器

控制器110进行通信,以使得数据能够在多个突发内在一个数据芯片140a中被保护,而存储器控制器辅助纠错允许数据在一个或更多个突发内在多个数据芯片140a之中被保护。因此,通过使用存储器控制器110的ECC以及从DRAM 160的DRAM中的ECC内部提供的信息,系统100能够使用存储器控制器110和DRAM 160结合工作来执行纠错。

[0061] 对于DRAM中的每组128位,通过使用单个ECC芯片140b执行DRAM级(即,没有来自存储器控制器110的辅助)的内部错误检测,DRAM中的ECC能够使用在芯片内部生成的ECC位来纠正一位错误。本实施例不提供与DDR4的存储器应用不同的存储器应用的任何改变,并且不提供DRAM 160与存储器控制器110之间的不同接口。因此,通过提供内部ECC,错误恢复信息不包含在正常数据传输170内,并且不被传送到存储器控制器110。因此,通过ECC芯片140b的纠错将不会影响利用存储器控制器110的存储器事务130的速度或性能。

[0062] 然而,ECC芯片140b无法单独纠正某些类型的错误。当存储器控制器110检测到数据中的错误时(例如,当DRAM 160向存储器控制器110指示存在错误时),只有那时存储器控制器110才会向DRAM 160发出一些命令以尝试纠错。即,仅当系统/存储器控制器ECC错误发生时,存储器控制器110才将特殊命令发送到DIMM并从DRAM 160接收包含在DRAM中的ECC信息读出180中的信息。此后,存储器控制器110将确定相应的存储器通道150的八个数据芯片140a中的哪一个是检测到的错误的原因。下面参照图7A和图7B进一步描述存储器控制器110用于定位有故障的数据芯片的方法。

[0063] 图2是描绘根据本发明的另一实施例的用于DDR接口的纠错机制的框图。与前述实施例的纠错机制一样,本实施例进行每个存储器事务十六个突发。类似地,存储器控制器210具有存储在其中的DAECC引擎220,并且DRAM 260的每个存储器通道250具有用于交换正常数据270的八个数据芯片240a和一个ECC芯片240b。然而,与先前的实施例不同,DRAM 260通过经由额外的引脚向存储器控制器210发送1位ECC标志向存储器控制器210警告ECC错误。

[0064] 参照图2,本实施例的系统200类似于参照图1描述的实施例的系统100。然而,本实施例的DRAM/DDR DIMM 260实施单个额外的引脚290,使得DRAM 260能够容易地将ECC信息传送到存储器控制器210。与先前的实施例不同,DRAM 260内的不可纠正的错误总是立即暴露给存储器控制器210,这是因为当在包括十六个突发的存储器事务230期间发生错误时,DRAM 260能够发送由单个1位ECC标志组成的警告。因此,当发生错误时,信息从芯片的DRAM中的ECC芯片240b被提供至存储器控制器210。

[0065] 因此,当发生与八个数据芯片240a中的一个对应的存储器错误时,本实施例的ECC芯片240b的引脚290将用于设定1位ECC标志以向存储器控制器210警告已发生错误。在通过引脚290检测到1位ECC标志时,存储器控制器210将发出特殊命令以从DRAM 260获得关于错误的更详细的信息。存储器控制器210可以通过使用DRAM中的ECC信息读出280以类似于参照图1描述的实施例的系统100的方式从DRAM 260获得信息。

[0066] 与参照图1描述的系统100的实施例不同,在DRAM 260与存储器控制器210之间的DDR接口从DDR4修改。然而,性能不会受到负面影响,这是因为1位ECC标志经由引脚290与其它576位数据一起传输,因此不会增加每个存储器事务230的时间量。

[0067] 图3是描绘根据本发明的又一实施例的用于DDR接口的纠错机制的框图。

[0068] 参照图3,当与参照图1和图2分别描述的实施例的系统100和200相比较时,本实施

例具有其中存储有DAECC引擎320的存储器控制器310，并且DRAM 360的每个存储器通道350具有用于交换正常数据370的八个数据芯片340a和一个ECC芯片340b。然而，本实施例的系统300的每个存储器事务330具有对十七个突发的总突发长度有影响的额外的突发。然而，在存储器事务330的第十七个突发期间，在DRAM中的纠错期间确定的ECC信息在DRAM中的ECC信息读出380中从DRAM/DDR DIMM 360传输到存储器控制器310。因此，存储器控制器310能够以与每个存储器事务330的额外突发相关联的性能降低为代价在每个存储器事务330中识别DRAM中的ECC信息。

[0069] 因此，与图1的实施例的系统100不同，其中，存储器控制器110仅在发生系统/存储器控制器ECC错误(例如，不能由DRAM 160的ECC芯片140b纠正的错误)时进行DRAM中的ECC信息的信息读出180，本实施例的存储器控制器310通过额外的第十七个突发在每个存储器事务330中执行DRAM中的ECC信息读出380。另外，存储器控制器310将总是执行与DRAM中的ECC执行的系统级(例如，在DRAM 360中)操作相同的操作以纠正错误。

[0070] 虽然上述实施例描述了DAECC机制可以用于使用4位DRAM芯片的新的窄DDR接口，但是DAECC机制可以与使用新的DDR接口的其它DRAM架构一起使用，或者如果在DRAM芯片内部执行DRAM中的ECC，则DAECC机制可以用在类似DDR4的接口中。

[0071] 例如，图4示出了DAECC引擎420可以与具有8位DRAM芯片440a和440b的新的窄DDR接口结合使用。在这样的实施例中，每个通道450具有存储数据的四个8位DRAM芯片440a和存储系统ECC的一个8位DRAM芯片440b。因此，本实施例中的系统ECC开销是1/4或25%。

[0072] 作为另一示例，图5示出了DAECC引擎可以用于具有4位DRAM芯片540a和540b的DDR接口。在本实施例中，每个通道550具有存储数据的十六个4位DRAM芯片540a和存储系统ECC的一个4位DRAM芯片540b。因此，在这样的实施例中，系统ECC开销是1/16或6.25%，这是DDR4标准中的当前ECC开销的一半。

[0073] 作为又一示例，图6示出了DAECC引擎可以用于具有8位DRAM芯片640a和640b的DDR4接口。在这样的实施例中，每个通道650具有用于存储数据的八个8位DRAM芯片640a和用于存储系统ECC的一个8位DRAM芯片640b。因此，系统ECC开销是1/8或12.5%。

[0074] 总之，上述实施例的DAECC是这样的通用机制：使用单个额外的ECC DRAM芯片，并且使用DRAM中的ECC信息以对具有任意种类的组织的存储器系统提供基本的芯片删除覆盖。

[0075] 图7A和图7B是描绘使用根据本发明的一个或更多个实施例的DAECC机制来检测错误、确定错误的类型和处理错误的流程图。

[0076] 下面描述的流程图可以通过分别参照图1、图2、图3、图4、图5和图6描述的任意系统来实施。当存储器控制器意识到DRAM中出现错误时，存储器控制器可以寻求确定错误模式。根据错误模式，存储器控制器将能够确定错误是否对应于随机错误(非永久性错误)、永久性错误或芯片删除错误。在确定错误的类型时，系统可以执行纠错。

[0077] 在不同类型的错误中，一种类型的错误被称为芯片删除错误。芯片删除错误通常对应于超过位错误的阈值的单个芯片/裸片或芯片的永久故障。存储器通道的单个4位数据芯片的故障可能导致对应于数据芯片的大量的四位在存储器事务期间在大量突发中提供错误数据(例如，在对应于数据芯片的4位符号中的大量错误)。因此，本发明的实施例可以检测单个芯片何时发生故障，然后可以在仍然提供单个芯片纠正的同时停用该芯片。也就

是说，本发明的实施例可以将对应于单个芯片的4个重复的错误位分组为一个符号，并且可以使用基于符号的机制（例如，奇偶校验）来恢复对应于故障/失效/擦除芯片的数据。

[0078] 另一种类型的错误被称为DQ错误。如上所述，在所述实施例的DRAM中，每个芯片具有4个数据引脚，每个引脚用于输出存储在芯片上的四个位中的一个。每个引脚可以被称作DQ。如果单个芯片的引脚之一发生故障（与整个芯片的故障相反），则在每个突发中从该引脚提供的数据可能潜在是错误的。因此，引脚故障可以被称作DQ错误。

[0079] 所描述的实施例可以使用与每个芯片交错的简单奇偶校验算法。例如，所描述的实施例可以使用独立磁盘冗余阵列（RAID）配置（例如，类似于RAID 4的配置的组织）。RAID 4是使用专用奇偶校验磁盘和跨多个磁盘（例如，芯片）的块级条带化的RAID配置。磁盘条带化包括将一组数据划分成块，并将块扩展到两个或更多个存储装置（例如，数据芯片）。

[0080] 因此，存储在ECC芯片上的数据将对应于四个奇偶校验位，其中，来自八个数据芯片中的单个数据芯片的每个位对于由ECC芯片存储的不同的奇偶校验位起作用，其中，来自所有数据芯片的相应引脚的一个位对于奇偶校验位之一（例如，单个ECC组的ECC芯片）起作用。如果主机存储器控制器通过使用数据和ECC信息检测到与单个引脚相对应的单个1位错误重新出现，则主机存储器控制器将从四个可能的位的位置的位置识别出错误（即，ECC芯片的相同奇偶校验位将具有在若干突发中发生的错误）。如下所述，可以使用来检测到的错误模式的信息来确定错误在哪里（例如，八个数据芯片中的哪一个具有导致错误的引脚）。

[0081] 参照图7A，在S701中，检测到错误。可以通过以上参考图1、图2和图3所述的任意错误检测方法来检测错误（例如，由存储器控制器210经由额外的引脚290检测ECC标志，或者通过存储器控制器310在存储器事务330的第17个突发期间在DRAM中的ECC信息读出380中检测错误）和/或通过在主机存储器控制器中执行的系统ECC（例如，类似RAID的奇偶校验）来检测错误。

[0082] 一旦在S701中系统确定存在来自DRAM/DDR DIMM的某些错误，则在S702中确定有多少个突发具有错误。这可以通过对存储器事务的每个突发进行奇偶校验来执行。因为不同类型的故障具有不同的错误模式，所以可以使用阈值或参考数量“n”来分类检测到的错误类型。例如，尽管ECC错误将处于ECC芯片的相同引脚位置，但DQ故障将在存储器事务的许多或全部突发中仅具有1位奇偶校验错误。然而，芯片故障将可能在许多或全部突发中在多个位中具有奇偶校验错误（例如，4位奇偶校验错误）。另外，随机错误可能对应于少量的错误，使得在少数突发中将存在非常少的错误位（例如，在单个突发中的单个1位错误）。

[0083] 因此，如果检测到的错误的数量大于阈值，则可以预测已经发生DQ故障或芯片故障。然而，如果检测到的错误的数量小于或等于阈值，则可以预测已经发生来自一个或更多个单独的芯片的一个或更多个随机错误，这不可由DRAM中的ECC纠正，可能需要来自存储器控制器的辅助以纠正。

[0084] 因此，在S702中，可以确定针对给定存储器事务的具有错误的突发的数量是否超过阈值“n”。根据是否满足阈值，逻辑流程进行到S703或S710。即，如果确定足够数量的突发具有奇偶校验错误（例如，如果在给定存储器事务中具有错误的突发的数量高于阈值数量“n”），则更可能存在DQ故障或芯片故障，系统将进入芯片删除机制。然而，如果具有检测到的错误的突发的数量小于阈值数量“n”（例如，4个突发或更少），则在S701中检测到的错误

可能是来自单独芯片(或多个芯片)的随机故障的结果。这样的随机故障不能通过DRAM中的ECC来纠正,但由于错误不可能再发生,所以不使用芯片删除机制。

[0085] 应当注意,虽然使用4个突发的阈值数量作为示例,但是在本发明的其它实施例中可以使用不同的数量。此外,可以在其它实施例中调整数量(例如,对应于特定装置)。例如,如果对应的存储器装置具有相对较高的装置错误率,使得发生多个随机错误,则可以增大阈值数量。

[0086] 在S703中,一旦在S702中确定具有奇偶校验错误的突发的数量大于阈值数量(例如,大于4个突发),则系统确定八个数据芯片中的一个失效或被擦除,或者确定八个数据芯片中的一个以上的数据芯片中存在错误。

[0087] 如果在S703确定芯片先前已经被擦除,或者在八个数据芯片中的一个以上的数据芯片中存在错误,则系统可以在S709中确定已发生致命的不可纠正的错误。具有错误的芯片的数量可以通过使用特殊命令或者在存储器事务330的第17个突发期间在DRAM中的ECC信息读出180、280、380中由存储器控制器110、210、310检测。例如,如果芯片由于DQ故障、芯片故障、存储体故障或行故障而失效,则任何额外的DQ故障或芯片故障导致致命的故障,这是因为本实施例的系统仅具有每个存储器通道单个ECC芯片,因此将不再具有足够的资源来执行纠错。类似地,如果多个芯片具有错误,则发生致命的故障。

[0088] 然而,如果在S703中确定没有芯片被擦除,并且检测到的错误仅对应于单个数据芯片,则处理可以进行至S704。例如,如果尚没有芯片被擦除,并且如果检测到的错误仅对应于单个芯片,则系统能够识别故障的类型,并且存储器控制器可以记录故障类型并可能采取进一步的动作来纠正错误。

[0089] 在S704中,可以确定检测到的错误是否发生在同一引脚上。即,在S704中,系统针对每个突发确定检测到的错误是否发生在同一引脚。如果所有错误都对应于同一引脚,则在S705a中,DRAM中的系统可以向存储器控制器报告,使得存储器控制器可以将错误的故障类型记录为DQ故障。如果系统确定检测到的错误并非全部在同一引脚,则在S705b中,DRAM中的系统可以向存储器控制器报告,使得存储器控制器可以将故障类型记录为芯片故障。

[0090] 在S706中,在故障类型被记录为DQ故障或芯片故障之后,存储器控制器用于辅助芯片删除检测。在S706中,存储器控制器可以启动诊断程序来确定如何纠正错误。将参考图7B描述诊断程序。

[0091] 参照图7B,在S706a,存储器控制器已经读出在图7A的S703中从DRAM中的ECC提供的DRAM中的ECC信息(例如,由ECC芯片提供的ECC位的DRAM中的ECC信息读出180、280或380),使得存储器控制器此后可以执行错误检测。此后,在S706b中,存储器控制器将保持所有正在进行的存储器事务。然后,在S706c中,存储器控制器存储当前数据(例如,对应于八个4位数据芯片的当前数据D[511:0]的512位)。然后,在S706d中,存储器控制器将对应于当前数据的反转数据(例如,对应于反转数据D'[511:0]的512位)写入到八个4位数据芯片。然后,在S706e中,存储器控制器再次读出数据。然后,在S706f中,存储器控制器将新读取的数据与已知的反转数据进行比较,以识别错误的位置。

[0092] 参照图7A,在S706中存储器控制器辅助芯片删除检测之后,在S707中,存储器控制器确定所有检测到的错误是否对应于单个芯片。如果仅擦除单个数据芯片,或者如果检测到多个DQ错误,但是多个DQ错误的全部对应于同一芯片,则在S708中,存储器控制器将把数

据写回剩余的未擦除的芯片，并且所有随后的存储器事务将使用简单的奇偶校验算法的奇偶校验位来恢复对应于擦除的芯片的数据。例如，如果存储器控制器在读出数据时确定对应于一个数据芯片的多个位与在S706d中写入到数据芯片的反转数据的相应位不匹配，则存储器控制器在S708中将该数据芯片标记为擦除。然而，如果存储器控制器在读出数据时确定对应于一个数据芯片的一个引脚的仅一位与在S706d中写入到数据芯片的反转数据的相应位不匹配，则存储器控制器在S708中仅将所述一个芯片的单个引脚标记为擦除。

[0093] 然而，如果多于一个芯片被标记为擦除，则在S709中，存储器控制器将确定已发生致命的不可纠正的错误。即，如果在多于一个的芯片中存在错误，则DRAM将不再具有足够的资源来执行奇偶校验，这是因为将没有额外的芯片备用，并且任何额外的芯片错误将是需要更换DRAM的不可纠正的致命错误。

[0094] 返回到S702，如果确定错误的数量低于阈值数量（例如，只有少量的存储器事务的突发具有错误），则在S710中，存储器控制器通过从DRAM接收额外的突发来重试从数据芯片读取数据。

[0095] 在S710中重试读取数据之后，存储器控制器在S711确定是否仍然存在检测的错误。如果在S711中没有检测到另外的错误，则存储器控制器在S712中确定已发生软错误或瞬态错误，并且不需要进一步的纠正。然而，如果在S710中重试读取数据后在S711中检测到另外的错误，则在S713中确定错误是否具有与S701中最初检测到的错误相同的错误模式。通过确定错误是否具有相同的错误模式，可以忽略不匹配的软错误的情况（所述情况是在S701中最初检测到软错误），并且在存储器控制器在S710中重试读取期间检测到不同的后续软错误。

[0096] 如果在S713中检测到的错误不具有与在S701中最初检测到的错误相同的错误模式，则处理返回到S710，并且存储器控制器再次重试从数据芯片读取数据。因此，如果发生连续的且不相同的软错误，从而导致不同的错误模式，则存储器控制器可以继续尝试读取数据。然而，如果在S713中检测到的错误与在S701中最初检测到的错误具有相同的错误模式，则在S714中确定发生了硬错误（非瞬态错误）。

[0097] 在S714中确定存在硬错误（非瞬态错误），并且假设尚没有芯片被标记为擦除的情况下，在S715中，DRAM触发存储器控制器，以通过使用存储器控制器ECC机制来辅助硬错误的纠正。存储器控制器可以通过例如将错误的当前地址（例如，芯片和引脚地址）与存储在DRAM上的一个或更多个芯片中的错误寄存器中的错误地址进行比较来辅助纠错。存储器控制器还可以通过使用DRAM中的ECC信息来辅助纠错。例如，如果DRAM中的ECC信息指示只有一个芯片具有不可纠正的DRAM中的ECC错误，则存储器控制器可以使用ECC芯片来恢复错误。

[0098] 在S716中，确定存储器控制器是否已经成功地纠正了硬错误。如果纠错成功，则在S717中，操作系统可以记录错误事件，并且存储器控制器可以发出另一个特殊命令来擦除每个芯片中的DRAM中的ECC信息（例如，芯片错误寄存器）。然而，如果纠错不成功（例如，如果一个芯片已经被擦除，因此系统不再具有ECC能力），则存储器控制器将在S709中确定已发生致命错误。

[0099] 当存储器控制器在S709识别到致命的不可纠正的错误时，操作系统可以执行系统/应用级错误恢复。例如，操作系统可以通过将页面的内容重新定位到另一个物理页面来

退出对应的物理页面，并且可以将退出的页面放置在不会被虚拟存储器系统随后分配的物理页面的列表上。随着退出的物理页面的数量增加（例如，随着不可纠正的错误的数量增加），系统的有效存储器容量减小。

[0100] 因此，本发明的实施例提供了这样的架构，所述架构能够提供诸如由DDR4提供的基本芯片删除RAS特征，同时提供具有减小的（例如，最小的）ECC芯片开销（即，每个存储器信道一个ECC芯片）、减小的（例如，最小的）内部预取尺寸（预取尺寸是与DRAM中的ECC相同的尺寸）以及DDR接口与对应于DDR4的接口减小的（例如，最小的）变化的这些特征。另外，本发明的实施例为具有比DDR4更窄的通道宽度的新DDR接口提供12.5%的存储开销，支持基本芯片删除能力和系统ECC，并且支持存储器控制器辅助错误检测机制。

[0101] 此外，尽管本发明的实施例仅具有每个存储器通道一个ECC芯片，但是能够提供基本芯片删除能力和系统ECC。本发明的实施例还提供允许存储器控制器在DRAM装置的辅助下识别故障芯片的机制，提供读出DRAM中的ECC信息的机制（例如，通过使用额外的突发长度、额外的引脚或者从DRAM进行的寄存器读出），提供重试机制以识别错误类型（例如，软错误或硬错误），并通过使用单独或锁步存储器通道以及通过使用SEC-DEC或芯片删除ECC提供了不同的ECC能力。

[0102] 以上说明了示例实施例，但不应被解释为对示例实施例的限制。虽然已经描述了一些示例实施例，但是本领域技术人员将容易地理解，在实质上不脱离示例实施例的新颖教导和优点的情况下，可以在示例实施例中进行许多修改。因此，所有这样的修改意图被包括在如权利要求中限定的示例实施例的范围内。在权利要求中，装置加功能条款旨在将这里所描述的结构覆盖为执行叙述的功能，并且不仅是结构等同物，也是等同结构。因此，应当理解，以上说明了示例实施例，但不应被解释为受限于所公开的特定实施例，并且对公开的示例实施例的修改及其它示例实施例意图被包括在权利要求的范围内。本发明的构思由权利要求以及包括在其中的权利要求的等同物限定。

图1

图2

图3

图4

图5

图6

图7A

图7B