(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 601 00 779 T2 2004.07.15

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 199 724 B1

(21) Deutsches Aktenzeichen: 601 00 779.4

(96) Europäisches Aktenzeichen: 01 118 067.6

(96) Europäischer Anmeldetag: 25.07.2001

(97) Erstveröffentlichung durch das EPA: 24.04.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.09.2003

(47) Veröffentlichungstag im Patentblatt: 15.07.2004

(51) Int Cl.<sup>7</sup>: G11C 7/10

G11C 7/22, G11C 11/4093, G11C 11/4096

(30) Unionspriorität:

2000299384 29.09.2000 JP

2000374153 08.12.2000 JP

(84) Benannte Vertragsstaaten:

DE, FR

(73) Patentinhaber:

Mitsubishi Denki K.K., Tokio/Tokyo, JP

(72) Erfinder:

Yamauchi, Tadaaki, Tokyo 100-8310, JP; Kozaru,

Kunihiko, Tokyo 100-8310, JP

(74) Vertreter:

PRÜFER & PARTNER GbR, 81545 München

(54) Bezeichnung: Halbleiteranordnung mit einer unkomplizierten Schnittstelle sowie einer logischen Schaltung

und einer eingebauten Speicheranordnung

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelegt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG****Gebiet der Erfindung**

[0001] Die vorliegende Erfindung bezieht sich auf eine Halbleiterspeichereinrichtung und insbesondere auf eine Halbleiterspeichereinrichtung mit einer Logikschaltungsanordnung, die darin integriert ist, und ein Steuerverfahren dafür.

**Beschreibung der Hintergrundstechnik**

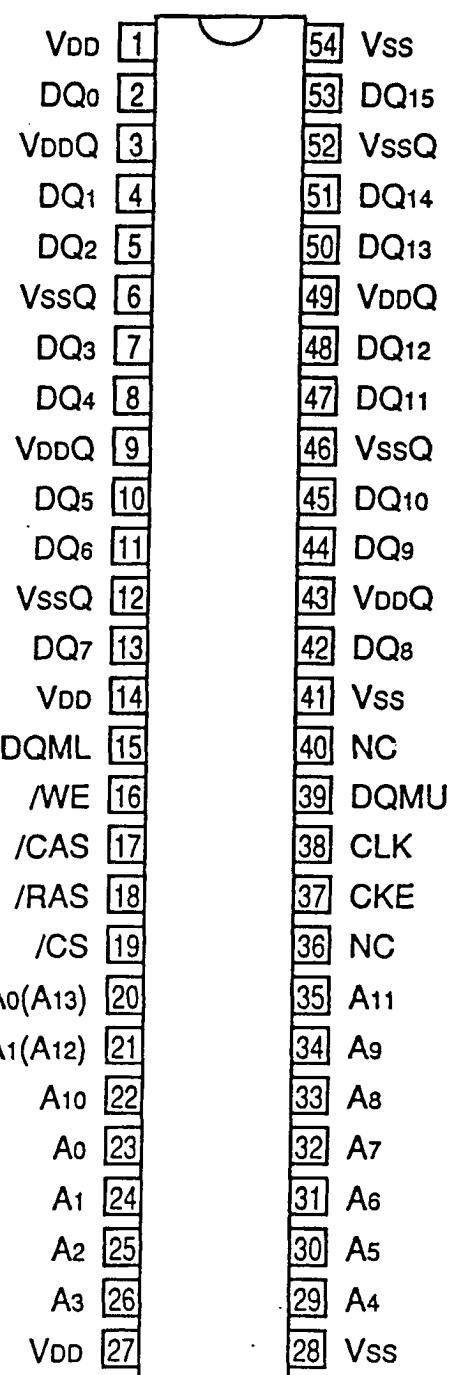

[0002] **Fig.** 101 ist eine Draufsicht, die eine Stiftkonfiguration eines 64 Mbit synchronen dynamischen Direktzugriffsspeicher (SDRAM) mit einer 16 Bit Wortkonfiguration darstellt.

[0003] **Fig.** 102 ist eine Tabelle, die Anschlußnamen des SDRAM und ihre Funktionen darstellt.

[0004] Bezug nehmend auf **Fig.** 101 und 102 ist ein SDRAM des Standes der Technik zum Beispiel in einem Gehäuse mit 54 Stiftanschlüssen aufgenommen, die einen Anschluß CLK, an den ein Mastertakt eingegeben wird, einen Anschluß CKE, an den ein Taktfreigabesignal eingegeben wird, einen Anschluß /CS, an den ein Chipauswahlsignal eingegeben wird, einen Anschluß /RAS, an den ein Zeilenadreßstrobesignal eingegeben wird, einen Anschluß /CAS, an den ein Spaltenadreßstrobesignal eingegeben wird, und einen Anschluß /WE, an den ein Schreibfreigabesignal eingegeben wird, enthalten.

[0005] Ein SDRAM des Standes der Technik weist weiter Anschlüsse DQ0 bis DQ15, die ein Daten-I/O-Signal liefern/empfangen, einen Anschluß DQM (U/L), durch den ein Ausgangssperrsignal/Schreibmaskierungssignal eingegeben/ausgegeben wird, Anschlüsse A0 bis A11, an die eine Adresse eingegeben wird, Anschlüsse BA0 und BA1, an die eine Bankadresse eingegeben wird, einen Anschluß VDD, der mit einer Leistungsquelle beliefert wird, einen Anschluß VDDQ, der mit einer Ausgangsleistungsquelle beliefert wird, einen Anschluß VSS, der mit einem Masspotential versehen ist, und einen Anschluß VSSQ, der mit einem Ausgangsmasspotential versehen ist, auf.

[0006] Die Anschlüsse sind derart aufgebaut, wie in **Fig.** 101 gezeigt ist, die Daten-I/O-Anschlüsse und die Leistungsquellen sind zwischen dem ersten und dreizehnten Stift und zwischen dem zweiundvierzigsten und vierundfünfzigsten Anschluß vorgesehen; die Steuersignale und das Taktsignal sind zwischen dem fünfzehnten und dem neunzehnten Stift und zwischen dem siebenunddreißigsten und dem neununddreißigsten Stift vorgesehen, und die Adreßstifte sind zwischen dem zwanzigsten und dem fünfunddreißigsten Stift vorgesehen. Solch eine Anschlußkonfiguration ist auf einem Niveau allgemeiner Vielseitigkeit und auch gut benutzt in einem Substrat, auf dem ein System mit einem Speicher angebracht ist.

[0007] **Fig.** 103 ist ein Blockschaltbild, das eine Konfiguration einer Logikschaltung integriert mit einem dynamischen Direktzugriffsspeicher (hier im folgenden als DRAM bezeichnet) des Standes der Technik darstellt.

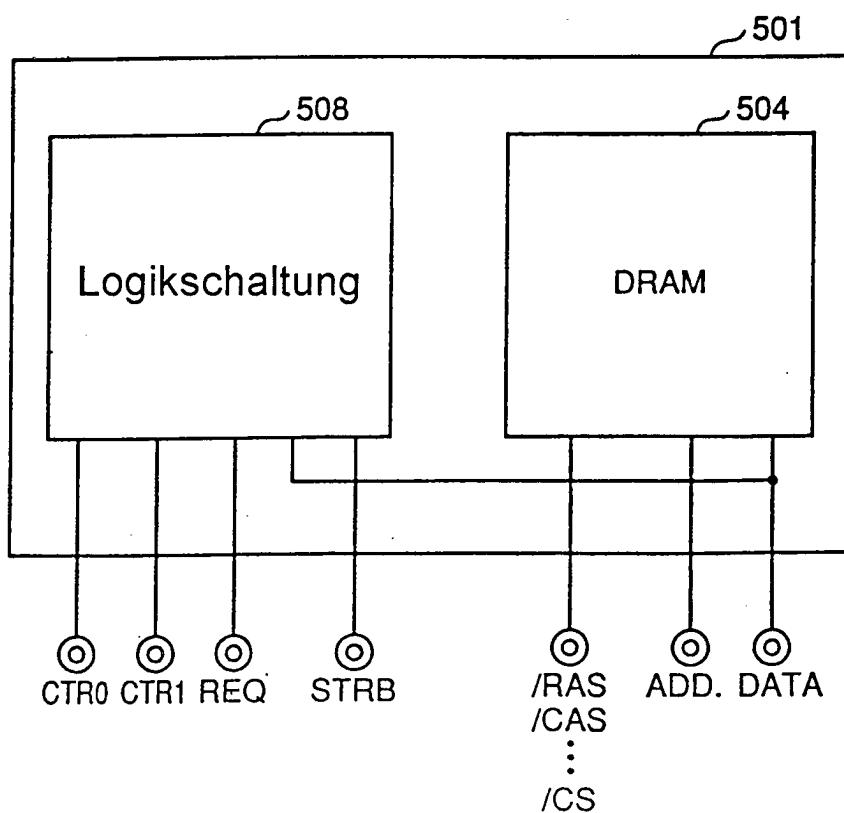

[0008] Bezug nehmend auf **Fig.** 103 sind ein DRAM **504** und eine Logikschaltung **508** auf einem Chip **501** integriert und mit Anschläßen zum Eingeben oder Ausgeben von Steuersignalen /RAS, /CAS, ..., /CS zum Zugriff auf den DRAM, eines Adreßsignales ADD und eines Datensignales DATA versehen.

[0009] In dem Chip **501** sind weiter Steuerstifte CTR0 und CTR1 eindeutig für die Logik, ein Anschluß, an dem ein Anforderungssignal REQ eingegeben wird, das Zugriff zu der Logikschaltung anfordert, und ein Anschluß zum Ausgeben eines Strobesignales STRB zum Benachrichtigen der Außenseite, daß die Logikschaltung eine Verarbeitung beendet, enthalten.

[0010] Da im Stand der Technik Stifte eindeutig für die Logikschaltung 508 zum Steuern der Logikschaltung **508** vorgesehen waren, nahm die Zahl der Stifte im Vergleich mit dem in **Fig.** 101 gezeigten Allgemeinwendung-DRAM zu; zum Zusammensetzen eines Systems auf einer Baugruppe mußte eine speziell zugeschnittene Steuerung zum Steuern eines integrierten Logik-DRAM vorgesehen werden. Folglich ging eine allgemeine Vielfalt, wie eine Verbindung mit einem gewöhnlichen Mikrocomputer, verloren, oder spezielle Befehle wurden in einem Mikrocomputer zum Steuern des Systems benötigt.

[0011] Aus der US 5,862,396 A kann eine integrierte Halbleiterschaltungsvorrichtung entnommen werden mit einem Hauptspeicher mit einer arithmetischen Logikverarbeitungsfähigkeit mit ersten Speichern, die mit einem Speicherbus verbunden sind, zum Speichern von Daten von zweiten Speichern mit einer arithmetischen Logikverarbeitungsfähigkeit, die ebenfalls mit dem Bus verbunden sind. Jeder der zweiten Speicher enthält einen Speicherabschnitt zum Speichern von Daten und einen arithmetischen Logikverarbeitungsabschnitt. Der arithmetische Logikverarbeitungsabschnitt führt eine erste Verarbeitung auf mindestens einem Teil der in dem Speicherabschnitt gespeicherten Daten als Reaktion auf einen ersten Befehl, der über den Speicherbus eingegeben ist, durch und ermöglicht, daß ein Resultat der ersten Verarbeitung auf den Speicherbus als Reaktion auf einen zweiten Befehl ausgegeben wird, der über den Speicherbus eingegeben wird.

[0012] Aus der US 4,835,733 kann eine integrierte Halbleiterschaltungsvorrichtung entnommen werden, die Verarbeitungsfähigkeit auf dem gleichen Chip enthält, auf einem oder auf beiden eines Adreßpfades und eines Datenpfades zwischen einem Satz von Zugriffsregistern und einem Speicherfeld so, daß eine Adresse erzeugt, geprüft und manipuliert werden kann, und/oder Daten manipuliert werden können oder mit Referenzmustern von Daten verglichen werden können.

[0013] Aus der US 5,953,738 kann eine integrierte Halbleiterschaltungsvorrichtung entnommen werden mit einem Speicher, der als ein einzelner integrierter Schaltungschip hergestellt ist und ein Feld von Speicherzellen und Schaltungsanordnung zum Zugreifen auf ausgewählte Speicherzellen in dem Feld enthält. Mindestens eine ALU ist zum Empfangen eines Datenzugriffs von ausgewählten Zellen des Feldes und Durchführen einer ausgewählten Operation darauf enthalten.

#### ZUSAMMENFASSUNG DER ERFINDUNG

[0014] Es ist folglich eine Aufgabe, eine integrierte Halbleiterschaltungsvorrichtung vorzusehen, auf der eine Speicherschaltungsanordnung und eine Logikschaltungsanordnung integriert sind, die durch ein Steuerverfahren ähnlich zu dem eines Allzweck-DRAM gesteuert werden können und die in der Lage sind, ein Resultat einer vorgeschriebenen Logikoperation zu liefern/zu empfangen, die auf Daten durchgeführt wird, die in der Speicherschaltung gespeichert sind, durch eine leicht zu handhabende Schnittstelle.

[0015] Solch eine Aufgabe wird gelöst durch eine integrierte Halbleiterschaltungsvorrichtung mit den Merkmalen des Anspruchs 1.

[0016] Das heißt, die vorliegende Erfindung ist eine integrierte Halbleiterschaltungsvorrichtung und enthält eine Anschlußgruppe, ein Speicherzellenfeld und Logikschaltungsanordnung.

[0017] Bevorzugte Ausgestaltungen der Erfindung sind in den abhängigen Ansprüchen definiert.

[0018] Folglich ist es ein Vorteil der vorliegenden Erfindung, daß die integrierte Logikschaltungsanordnung gemäß einer Sequenz ähnlich zu der gesteuert werden kann, gemäß der Daten, eine Adresse und ein Steuersignal an einen Allzweckspeicher gegeben werden, und das System kann ohne Änderung eines vorhandenen Systems erhalten werden, das gut und leicht zu steuern ist. Weiterhin ist ein Vorteil der vorliegenden Erfindung der, daß eine integrierte Halbleiterschaltung, auf der eine Speicherschaltungsanordnung und eine Logikschaltungsanordnung integriert sind, ein Resultat einer vorgeschriebenen Logikoperation auf Daten, die in der Speicherschaltungsanordnung gespeichert sind, mit einer hohen Geschwindigkeit durch eine Schnittstelle liefern/empfangen kann, die leicht extern zu handhaben ist.

[0019] Die vorangehenden und weiteren Aufgaben, Merkmale, Aspekte und Vorteile der folgenden Erfindung werden ersichtlicher aus der folgenden detaillierten Beschreibung der vorliegenden Erfindung, wenn sie in Zusammenhang mit den begleitenden Zeichnungen genommen wird.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

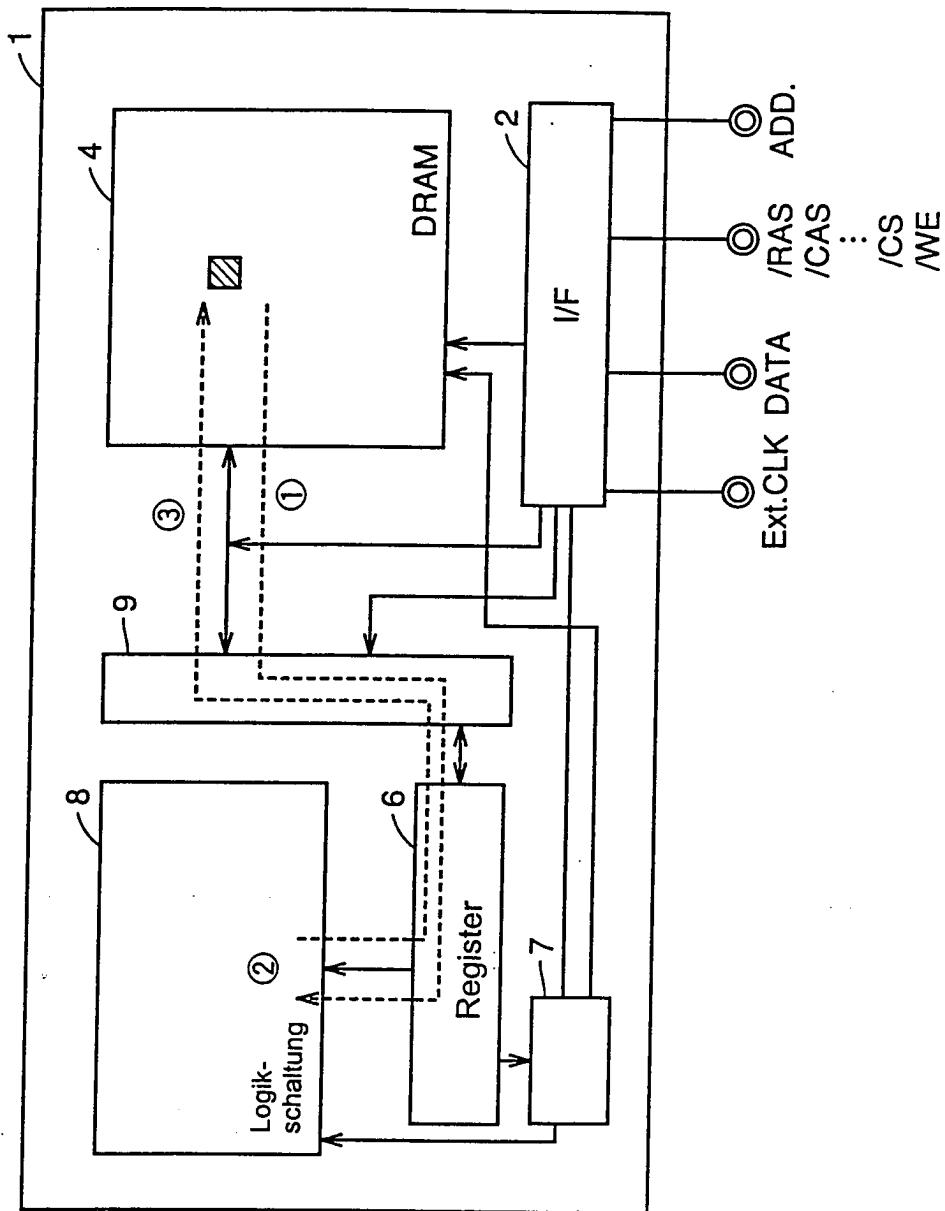

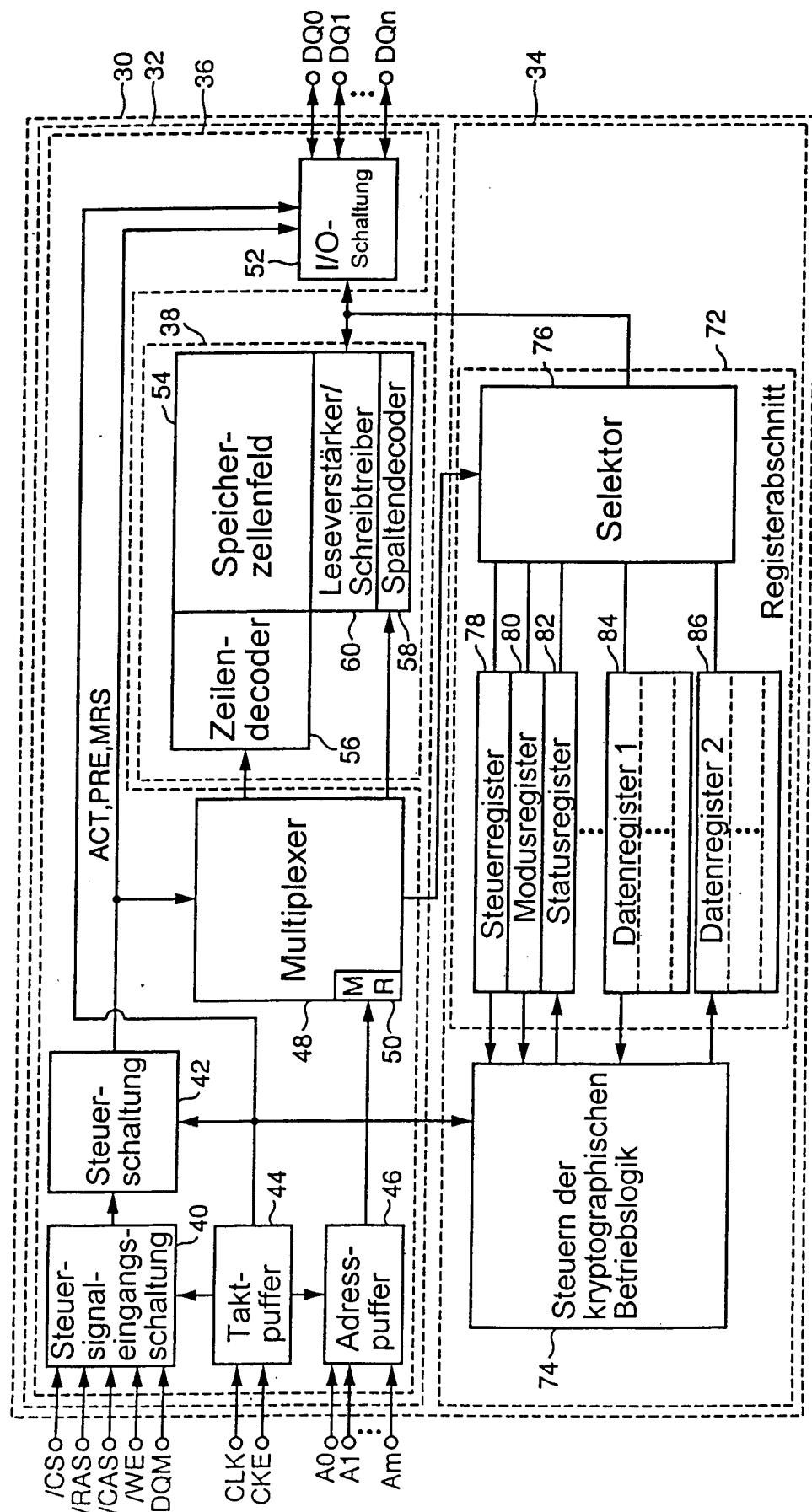

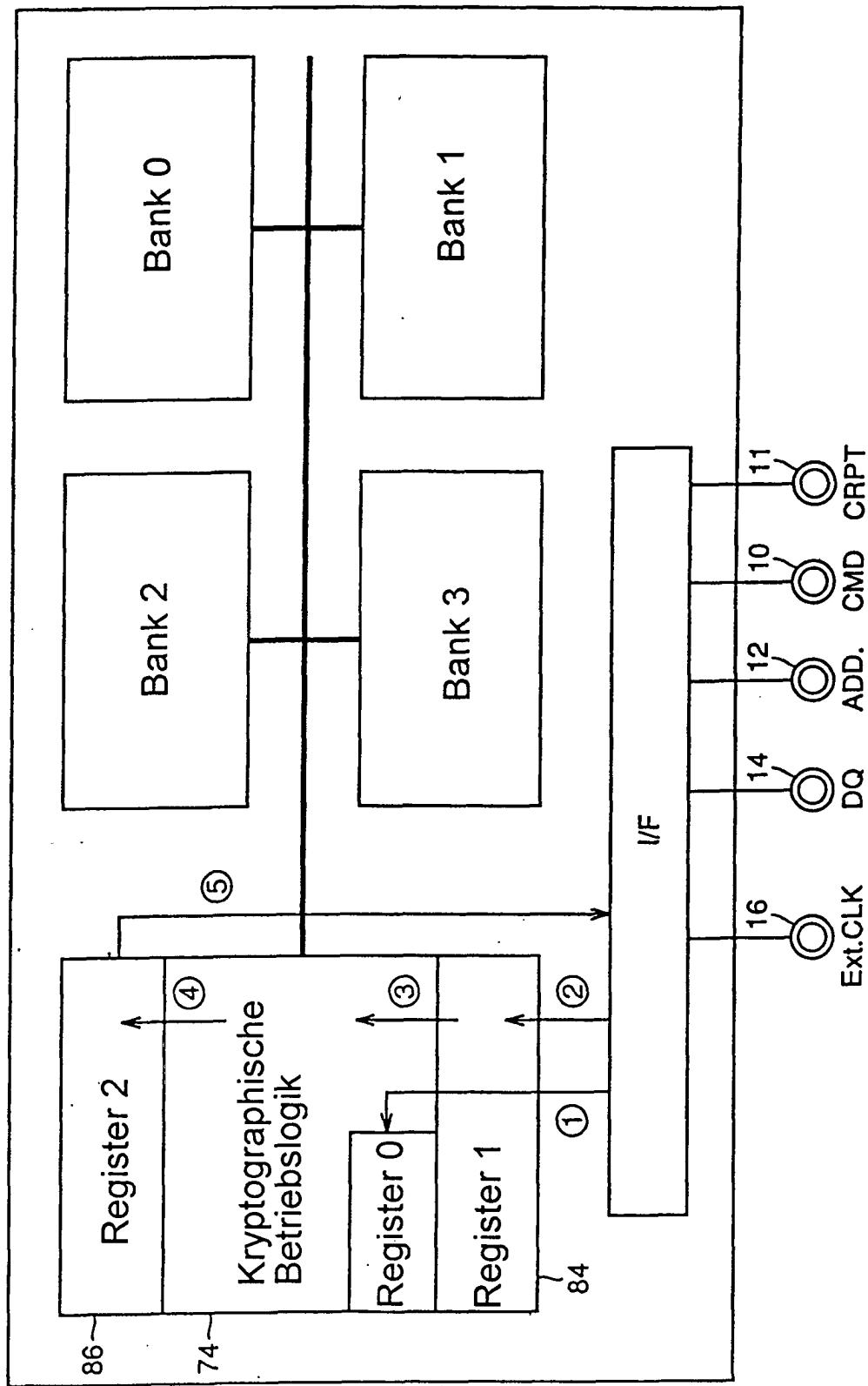

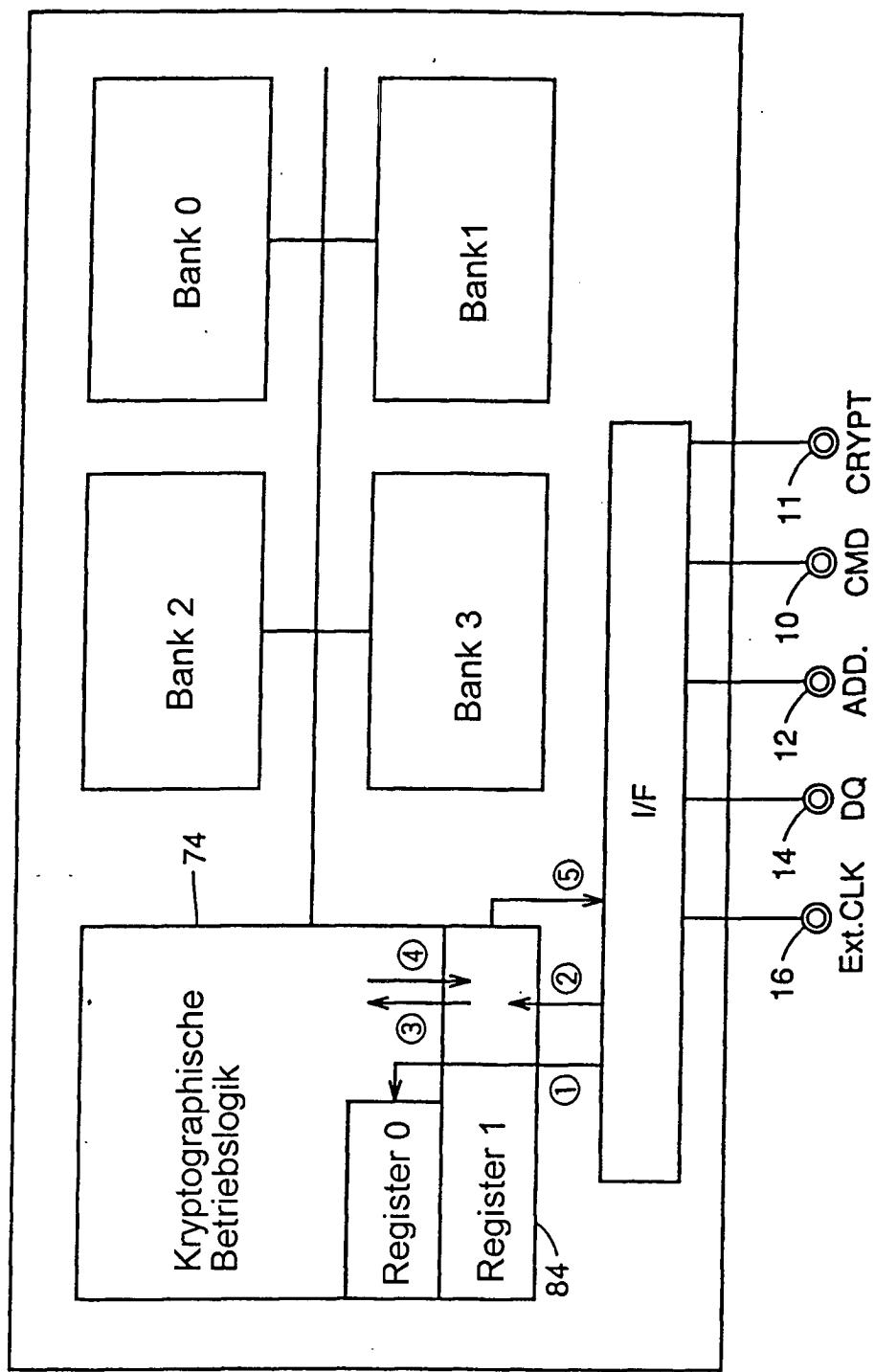

[0020] **Fig. 1** ist ein Blockschaltbild, das eine Konfiguration einer integrierten Halbleiterschaltungsvor-

richtung 1 eines ersten Beispieles der vorliegenden Erfindung darstellt;

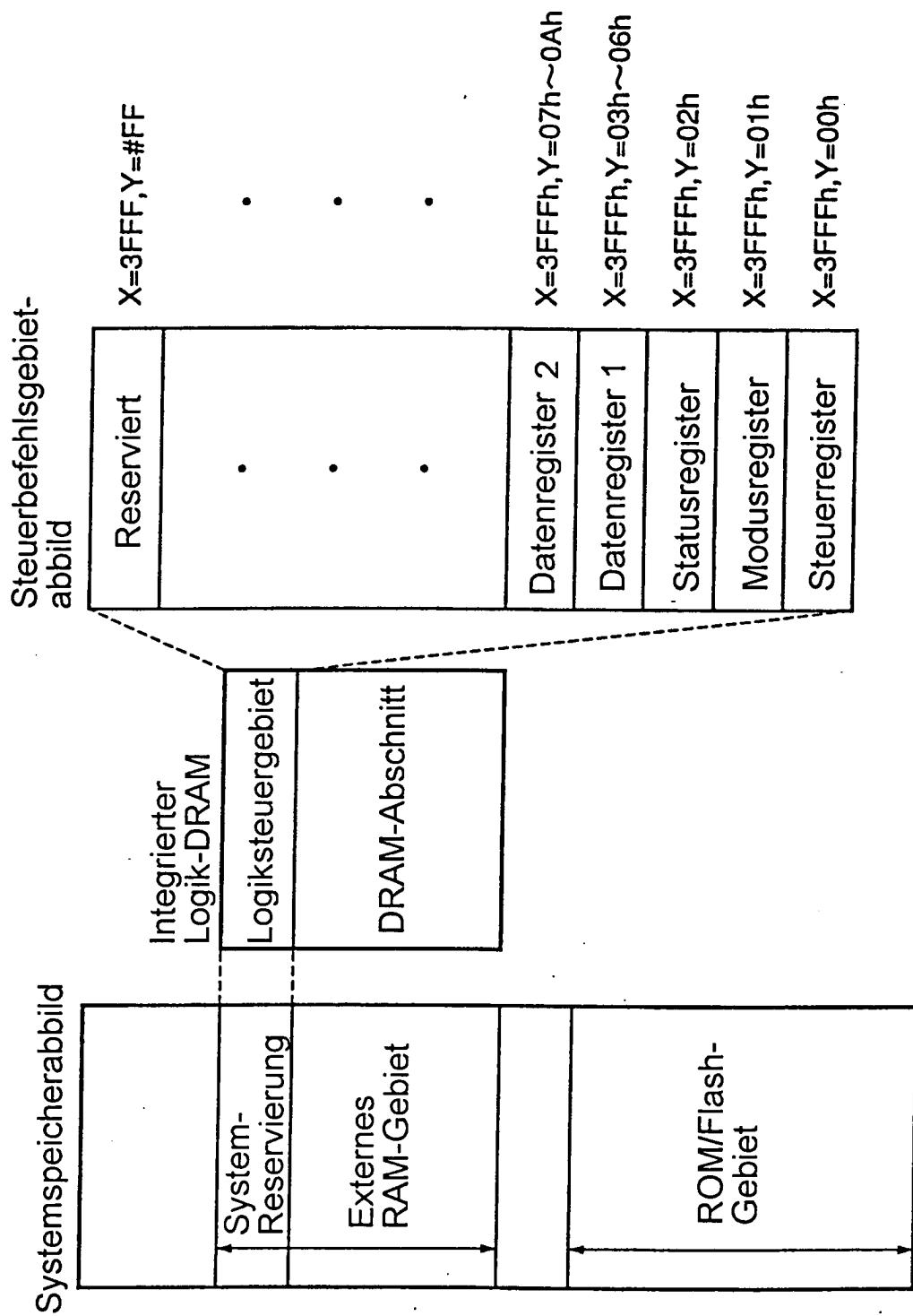

[0021] **Fig. 2** ist eine Zeichnung, die ein Speicherabbild einer integrierten Logikhalbleiterspeichereinrichtung des ersten Beispieles darstellt;

[0022] **Fig. 3** ist ein Blockschaltbild zum Beschreiben eines Weges, wie ein extern eingegebenes Signal zu einer Logikschaltung übertragen wird;

[0023] **Fig. 4** ist ein Blockschaltbild zum Beschreiben eines Betriebes in einem normalen Modus, einem von Betriebsmodi der integrierten Halbleiterschaltungsvorrichtung 1;

[0024] **Fig. 5** ist ein Blockschaltbild zum Beschreiben eines Betriebes eines Lesezugriffes in dem normalen Modus;

[0025] **Fig. 6** ist ein Blockschaltbild zum Beschreiben eines Betriebes in einem Blockmodus, einem anderen der Betriebsmodi der integrierten Halbleiterschaltungsvorrichtung 1;

[0026] **Fig. 7** ist ein Blockschaltbild zum Beschreiben eines Betriebes in einem Puffermodus, einem noch anderen der Betriebsmodi der integrierten Halbleiterschaltungsvorrichtung 1;

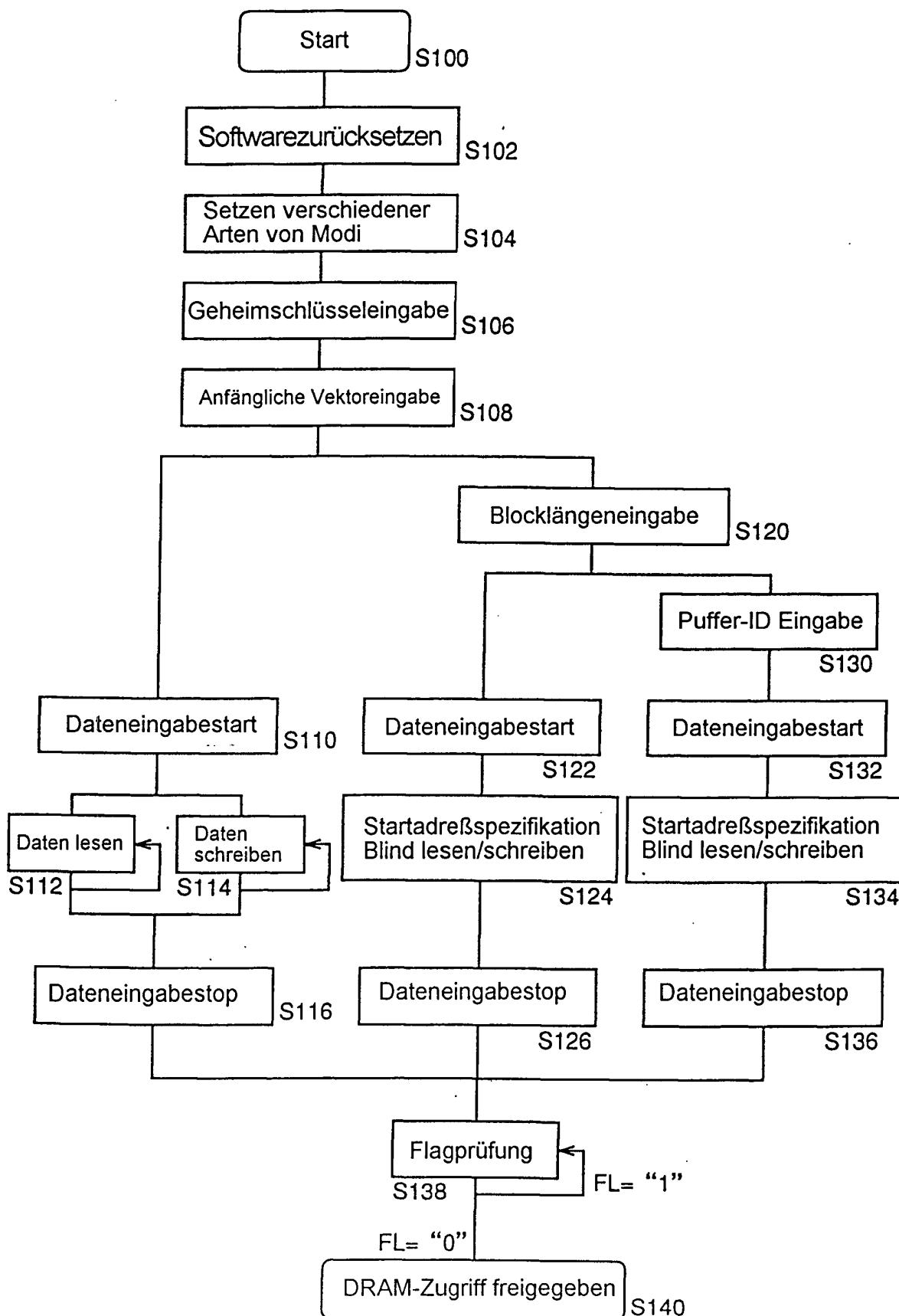

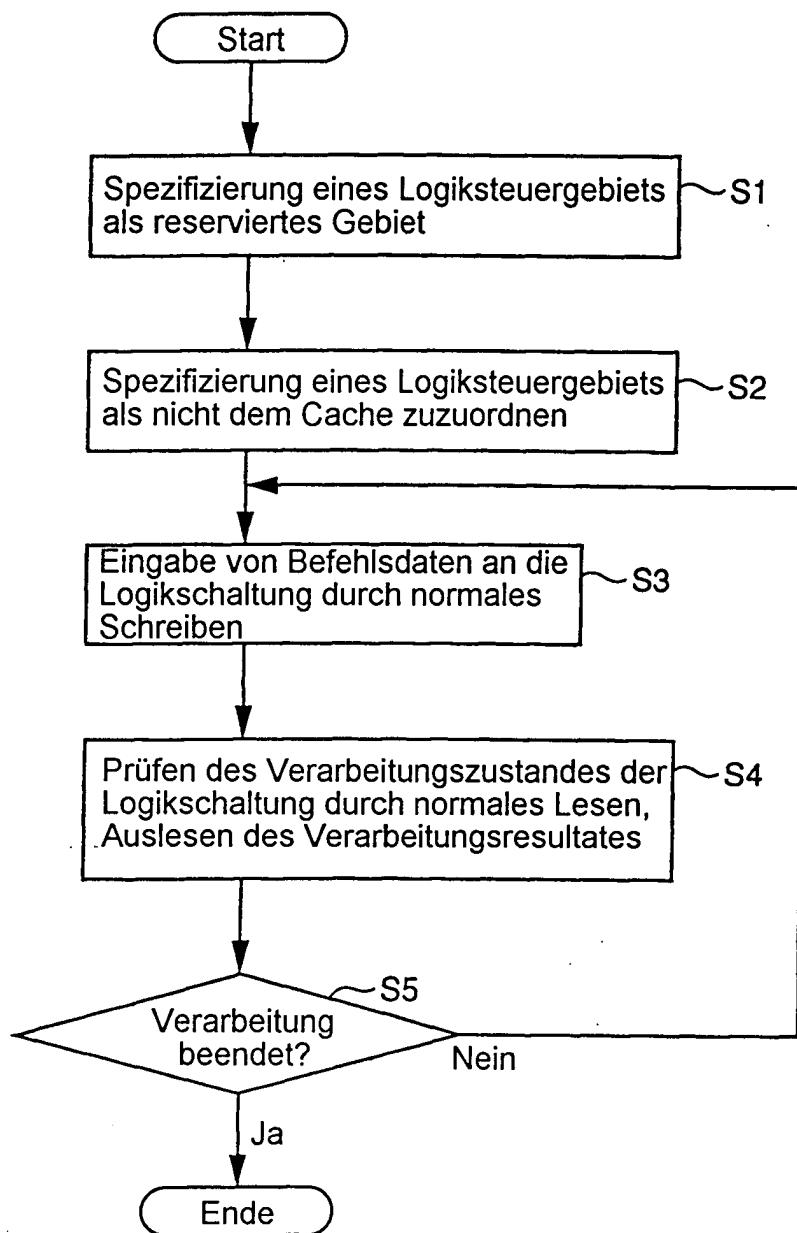

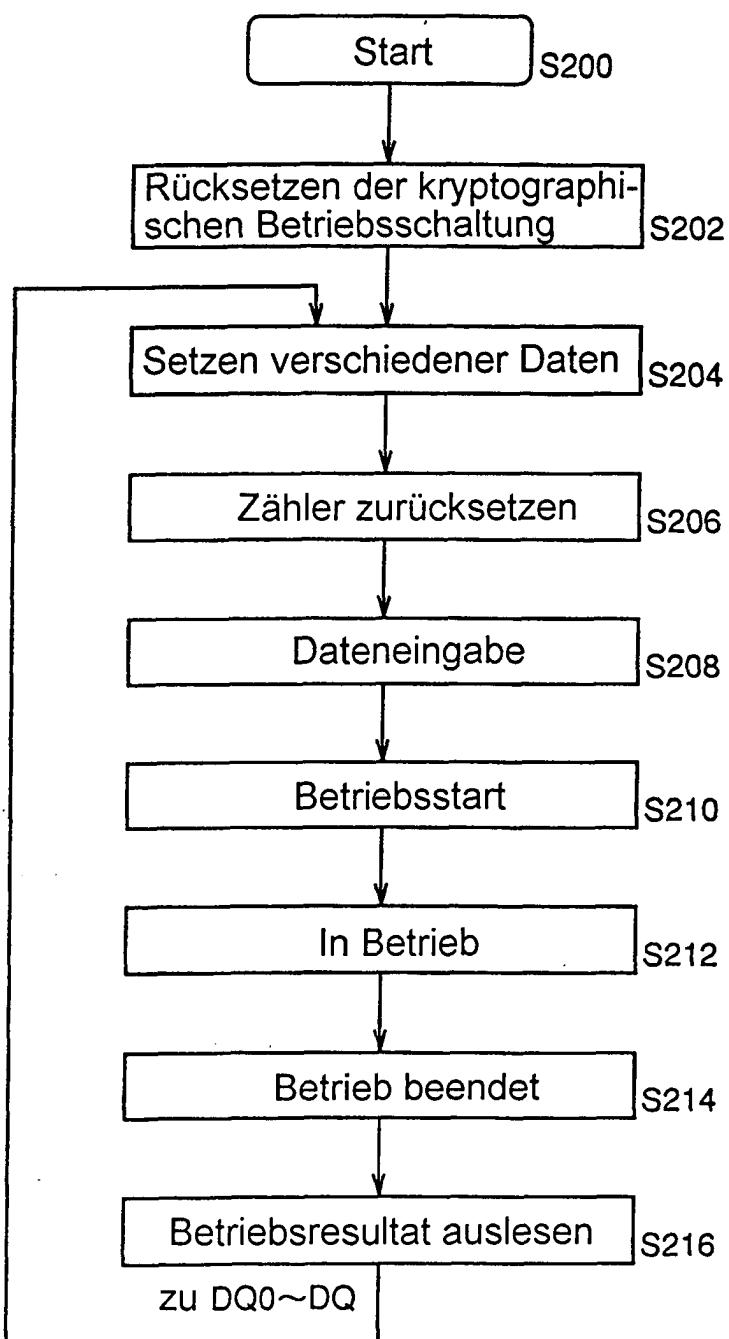

[0027] **Fig. 8** ist ein Flußdiagramm zum Beschreiben von Betrieben in den drei Modi;

[0028] **Fig. 9** ist eine Tabelle, die Beispiele von Kryptosystemen darstellt, die eine Logikschaltung 8 ausführen kann;

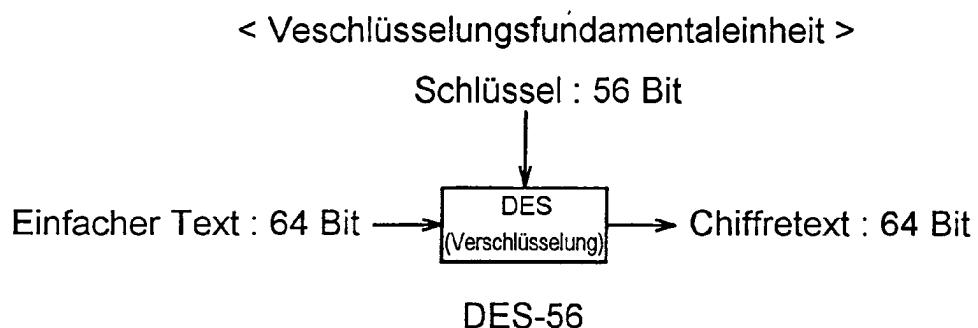

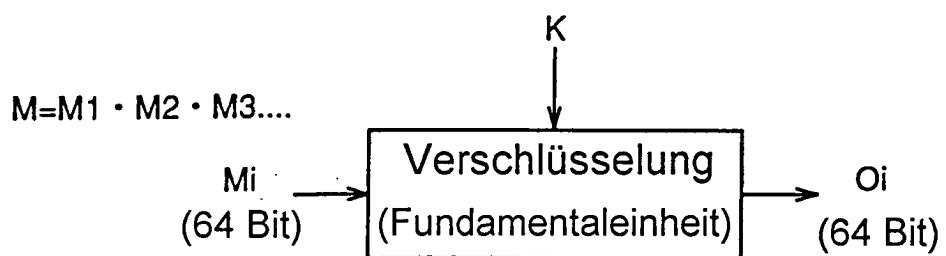

[0029] **Fig. 10** ist eine konzeptuelle Zeichnung, die eine Fundamenteinheit für DES-Verschlüsselung darstellt, die als ein Kryptosystem mit geheinem Schlüssel benutzt wird;

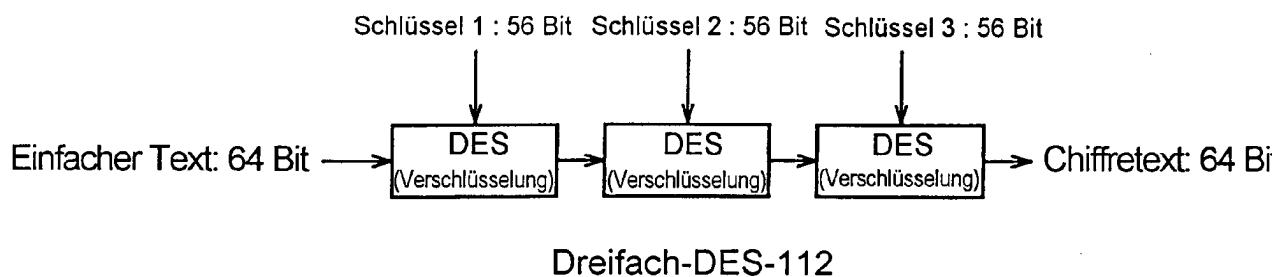

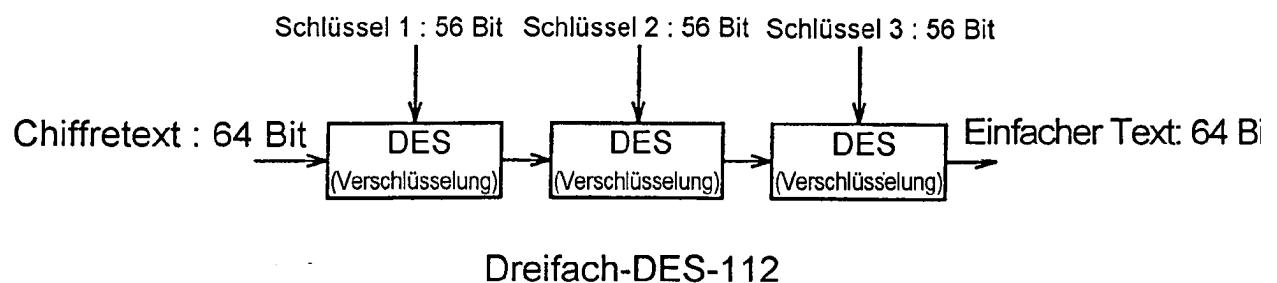

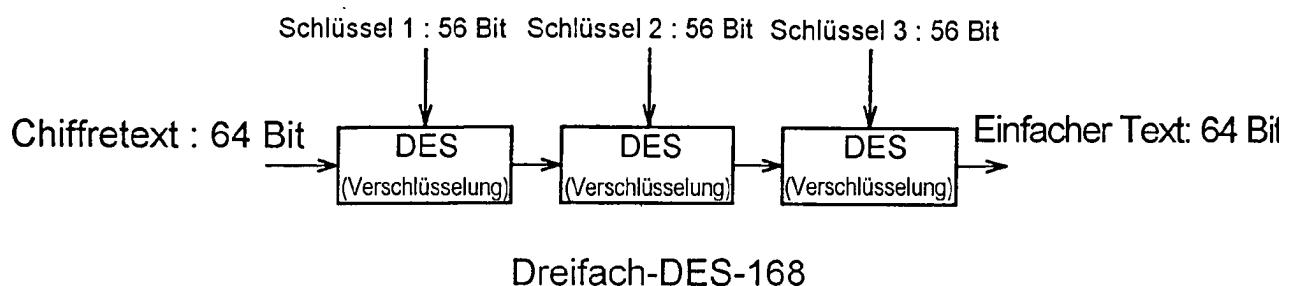

[0030] **Fig. 11** ist eine erste konzeptuelle Zeichnung, die ein Triple-DES-Verarbeitungssystem darstellt;

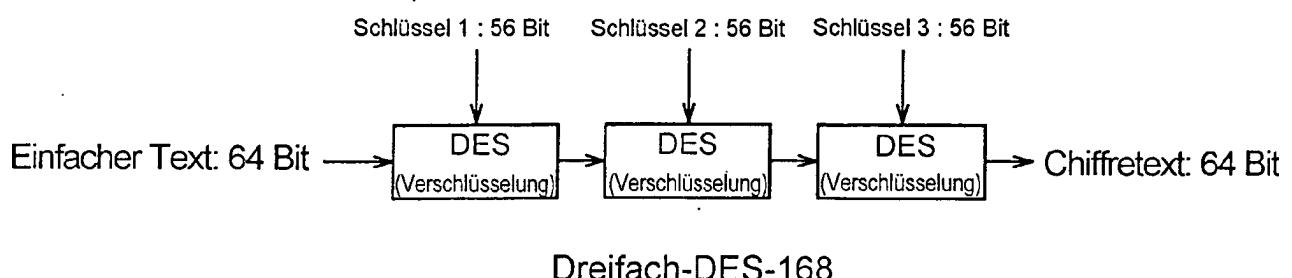

[0031] **Fig. 12** ist eine zweite konzeptuelle Zeichnung, die das Triple-DES-Verarbeitungssystem darstellt;

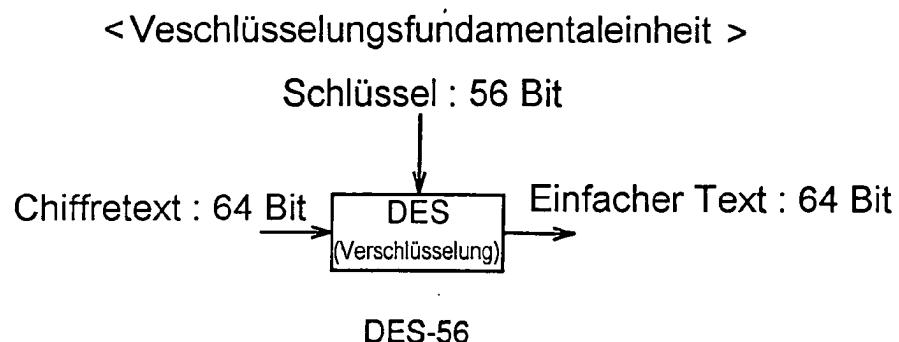

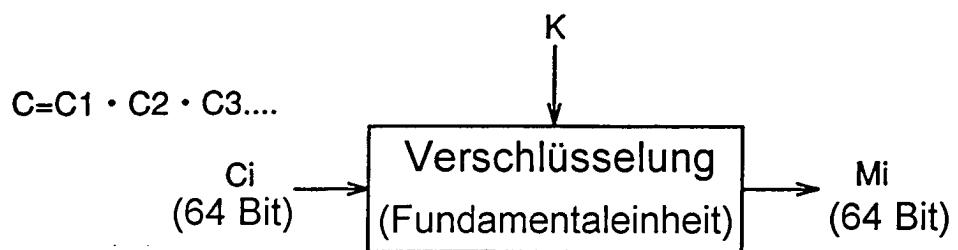

[0032] **Fig. 13** ist eine konzeptuelle Zeichnung, die Entschlüsselung darstellt, die entsprechend zu **Fig. 10** durchgeführt wird;

[0033] **Fig. 14** ist eine konzeptuelle Zeichnung, die Entschlüsselung darstellt, die entsprechend zu **Fig. 11** durchgeführt wird;

[0034] **Fig. 15** ist eine konzeptuelle Zeichnung, die Entschlüsselung darstellt, die entsprechend zu **Fig. 12** durchgeführt wird;

[0035] **Fig. 16** ist eine konzeptuelle Zeichnung zum Beschreiben einer Verschlüsselung in einem EBC-Modus;

[0036] **Fig. 17** ist eine konzeptuelle Zeichnung zum Darstellen von Entschlüsselung in dem EBC-Modus;

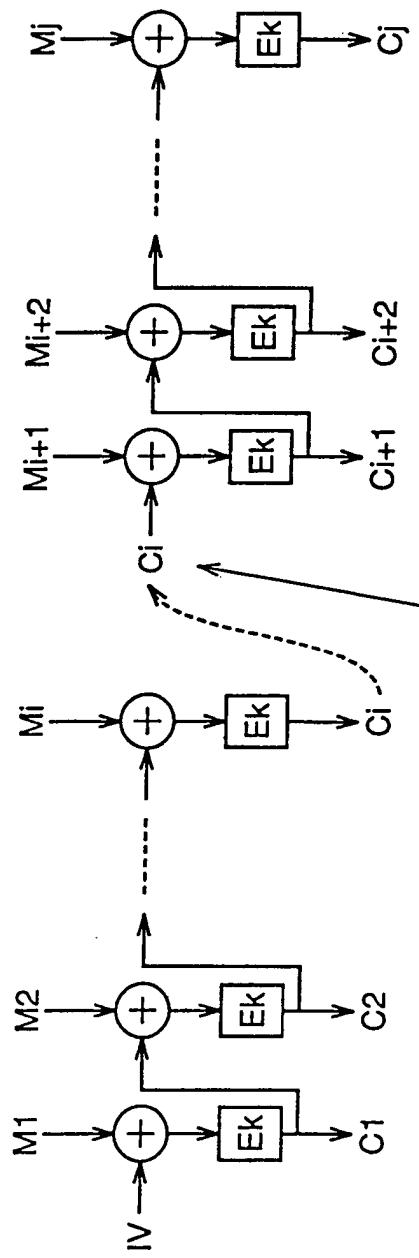

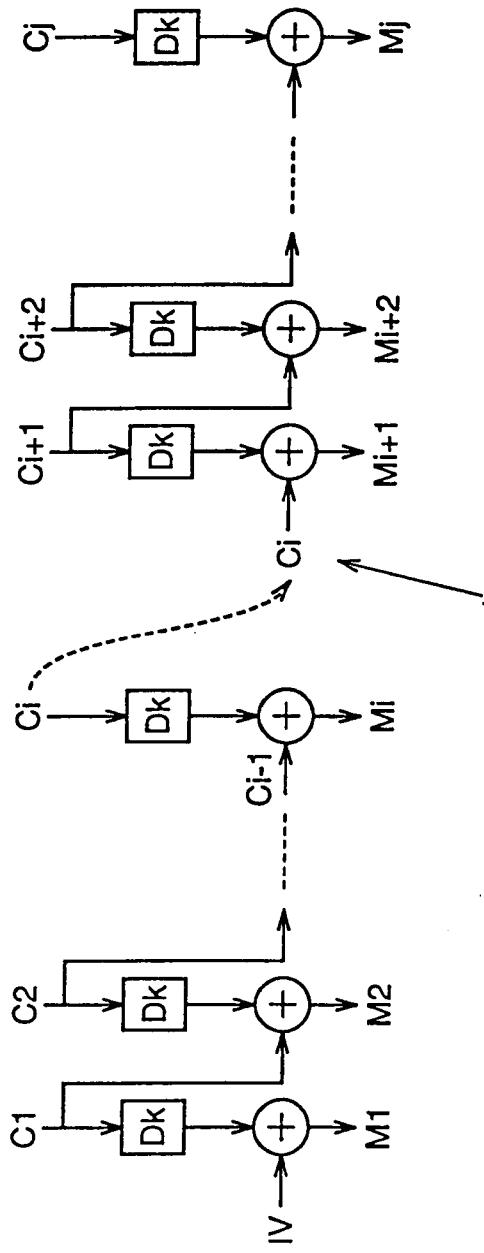

[0037] **Fig. 18** ist eine konzeptuelle Zeichnung zum Beschreiben von Verschlüsselung in einem CBC-Modus;

[0038] **Fig. 19** ist eine konzeptuelle Zeichnung, die Verarbeitung zum Dechiffrieren eines Chiffriertextes darstellt, der auf die in **Fig. 18** gezeigte Weise chiffriert ist;

[0039] **Fig. 20** ist ein Zeitablaufdiagramm zum Be-

schreiben der Verarbeitung, die in **Fig. 8** beschrieben ist, wenn verschiedene Arten von Verschlüsselungsmodi vorhanden sind;

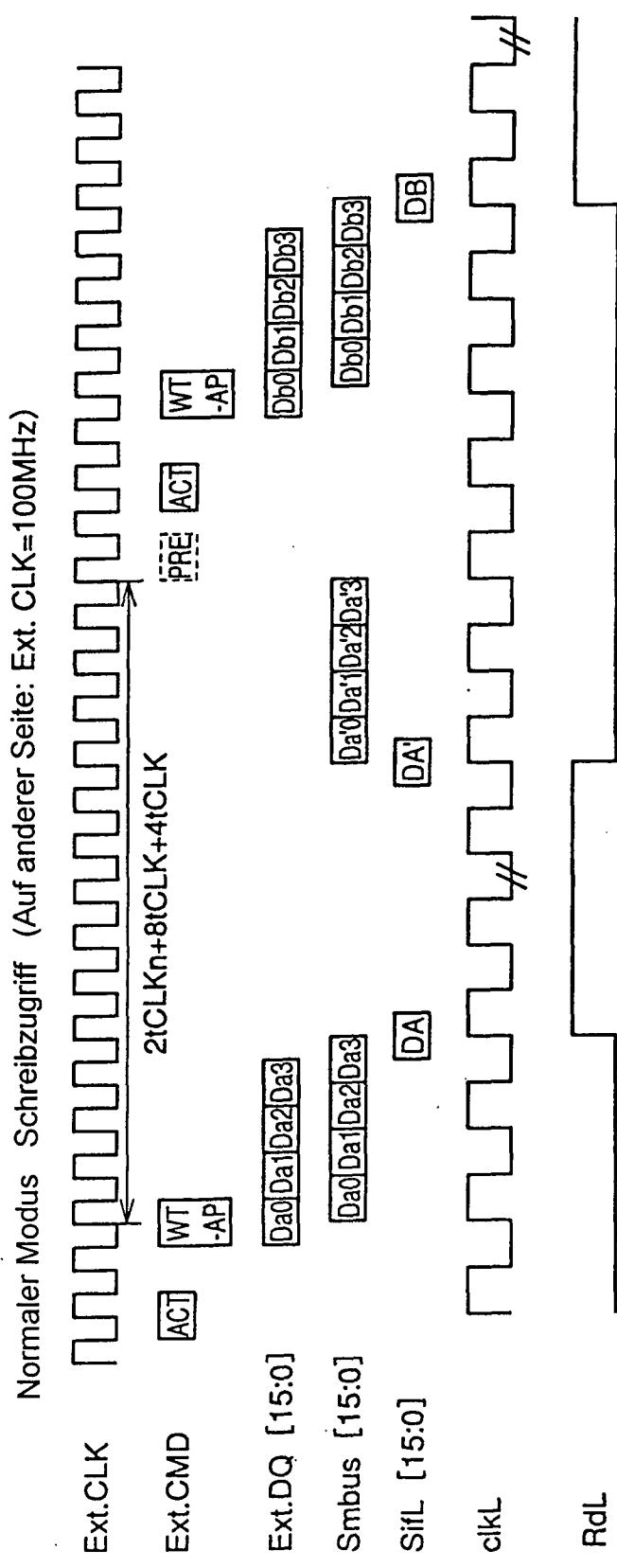

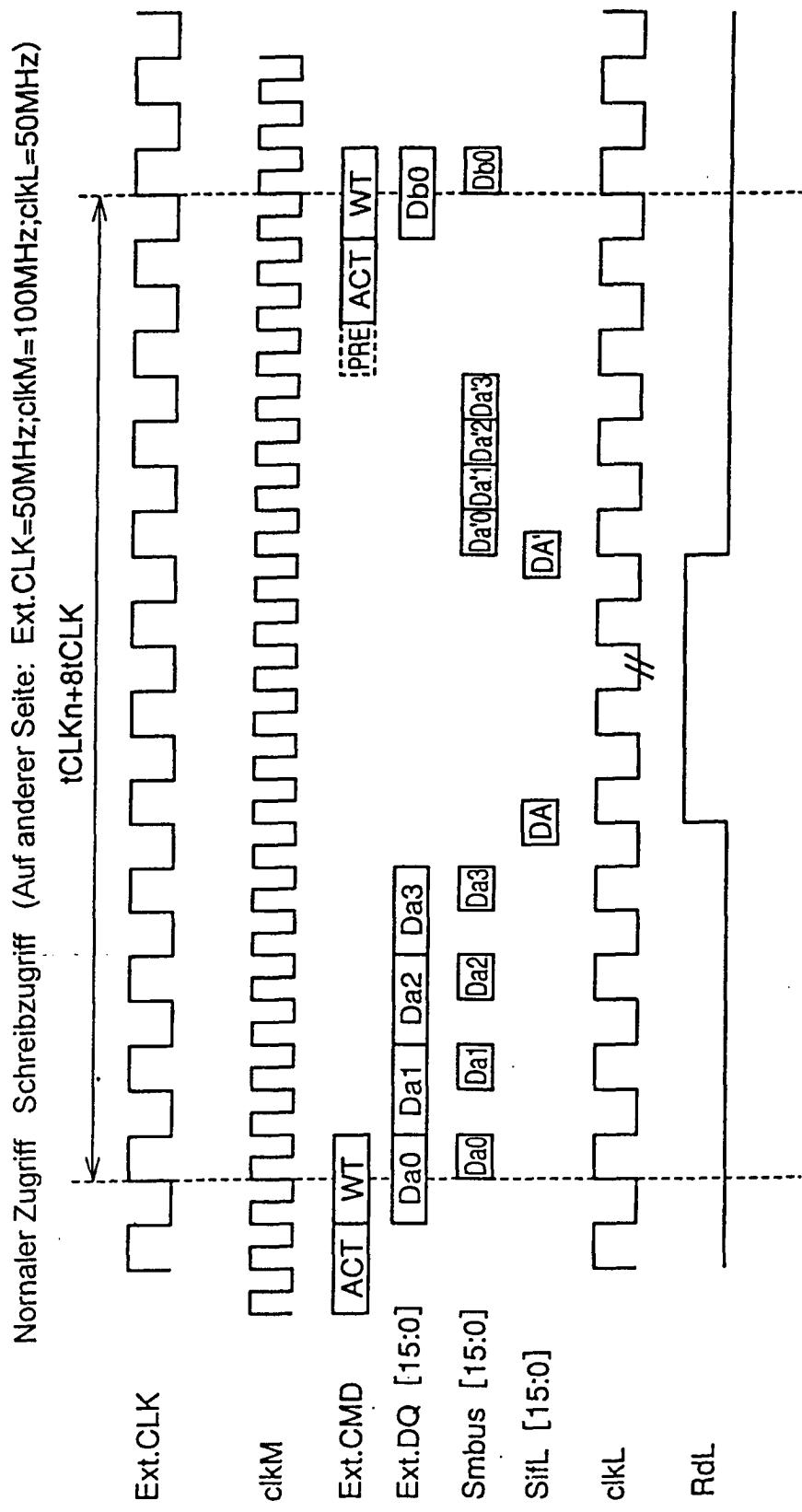

[0040] **Fig. 21** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Daten auf die gleiche Seite bei Schreibzugriff des normalen Modus geschrieben werden;

[0041] **Fig. 22** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Daten von 64 Bit auf eine andere Seite in dem normalen Modus geschrieben werden;

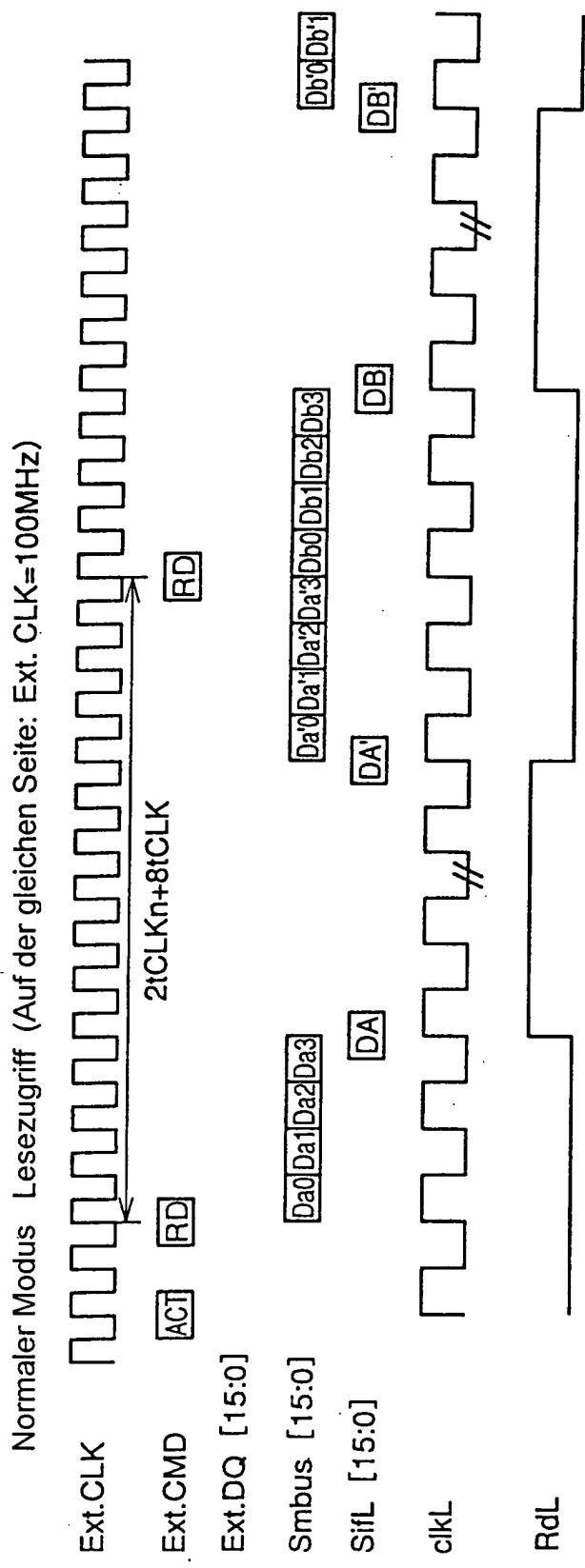

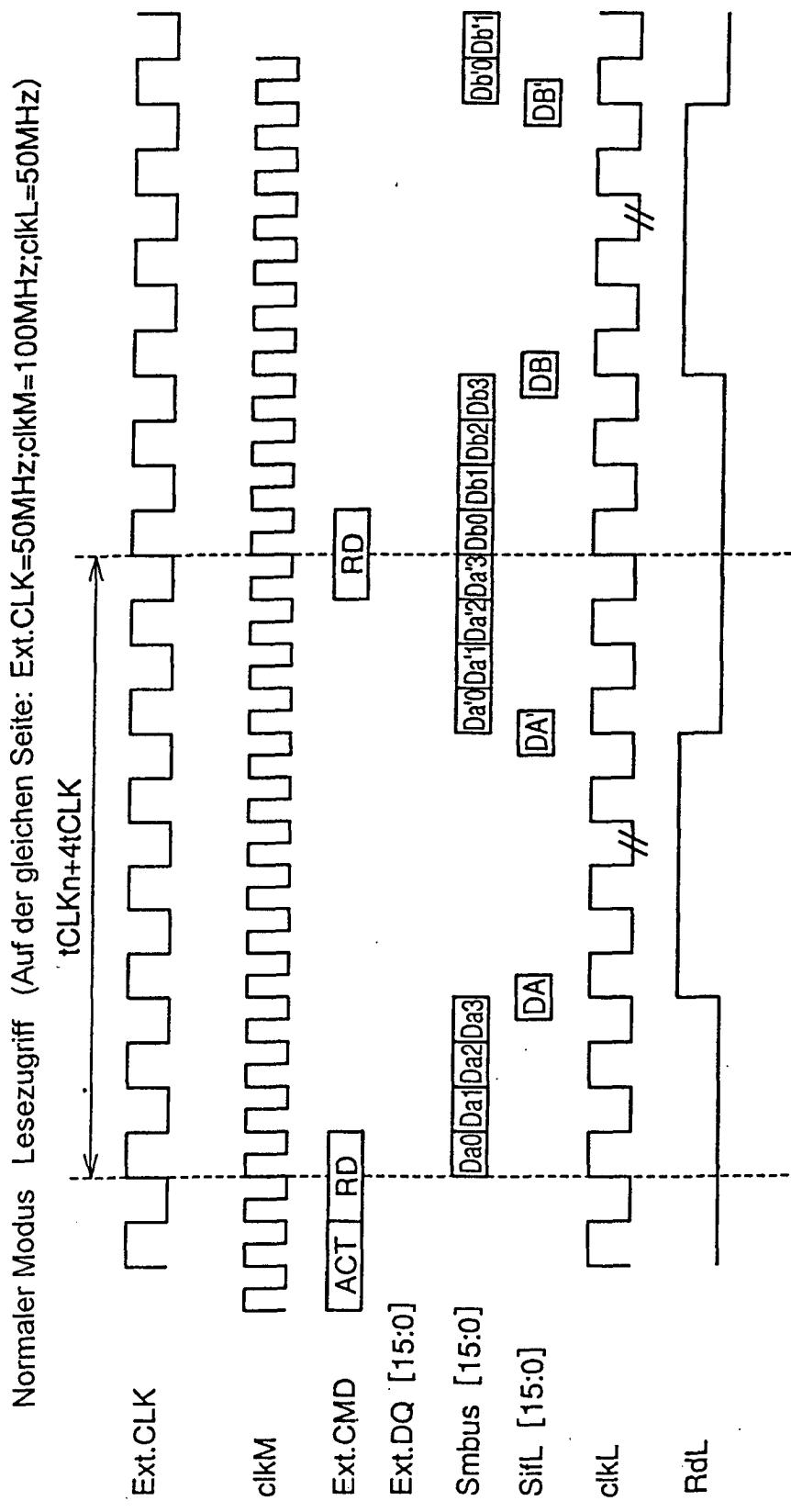

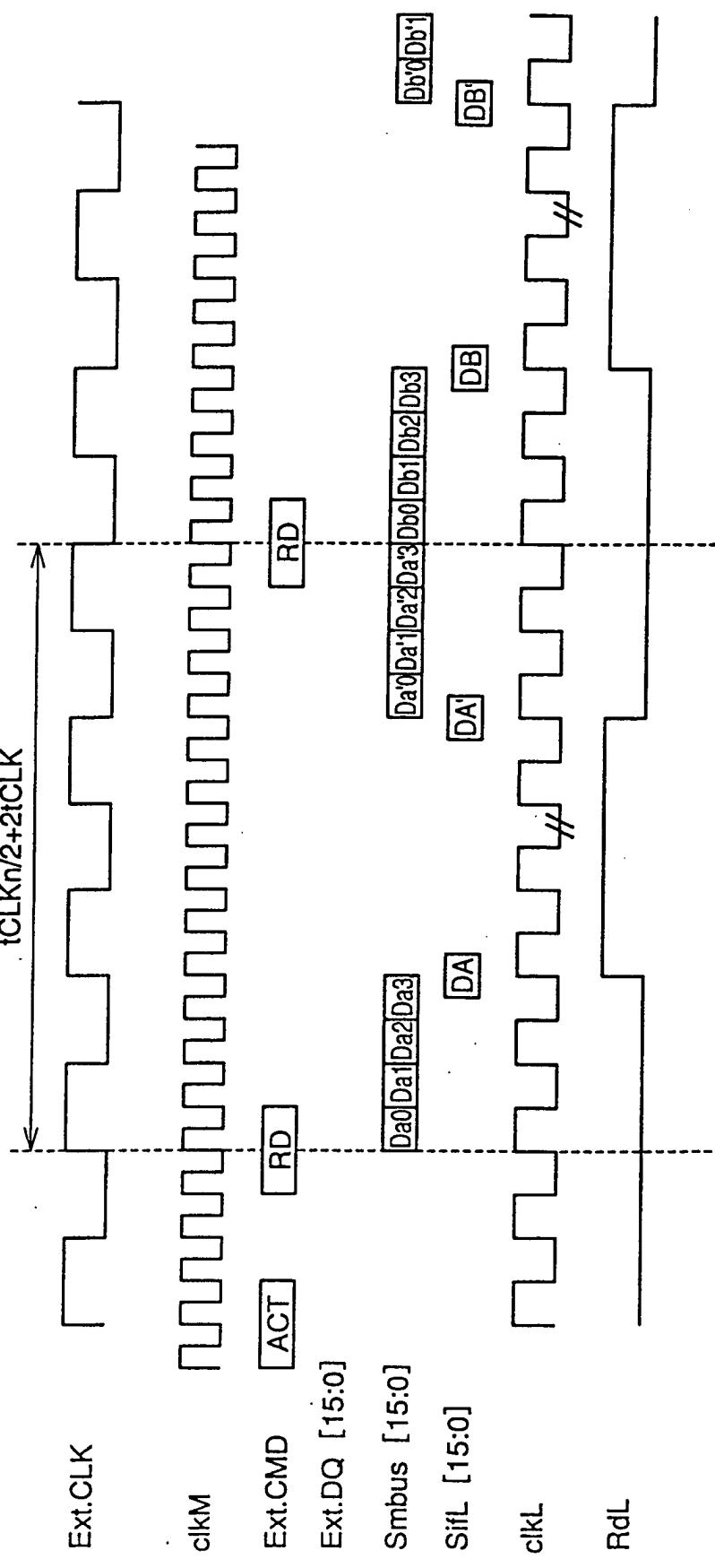

[0042] **Fig. 23** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus durchgeführt wird;

[0043] **Fig. 24** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf eine andere Seite durchgeführt wird;

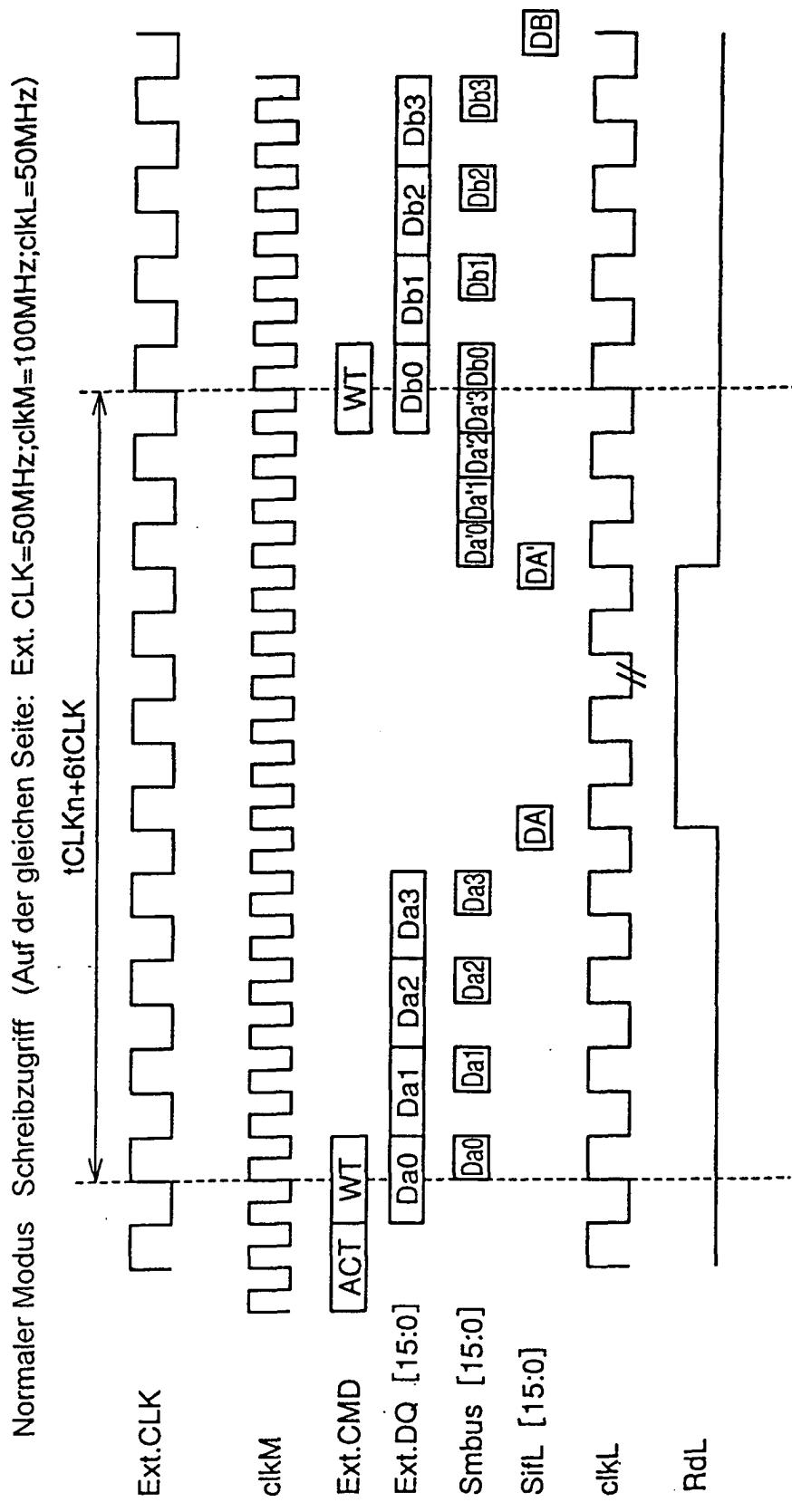

[0044] **Fig. 25** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes der integrierten Halbleiterschaltungsvorrichtung **1**, wenn ein externes Taktignal Ext.CLK gleich 50 MHz ist;

[0045] **Fig. 26** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Schreibzugriff auf eine andere Seite in dem normalen Modus durchgeführt wird;

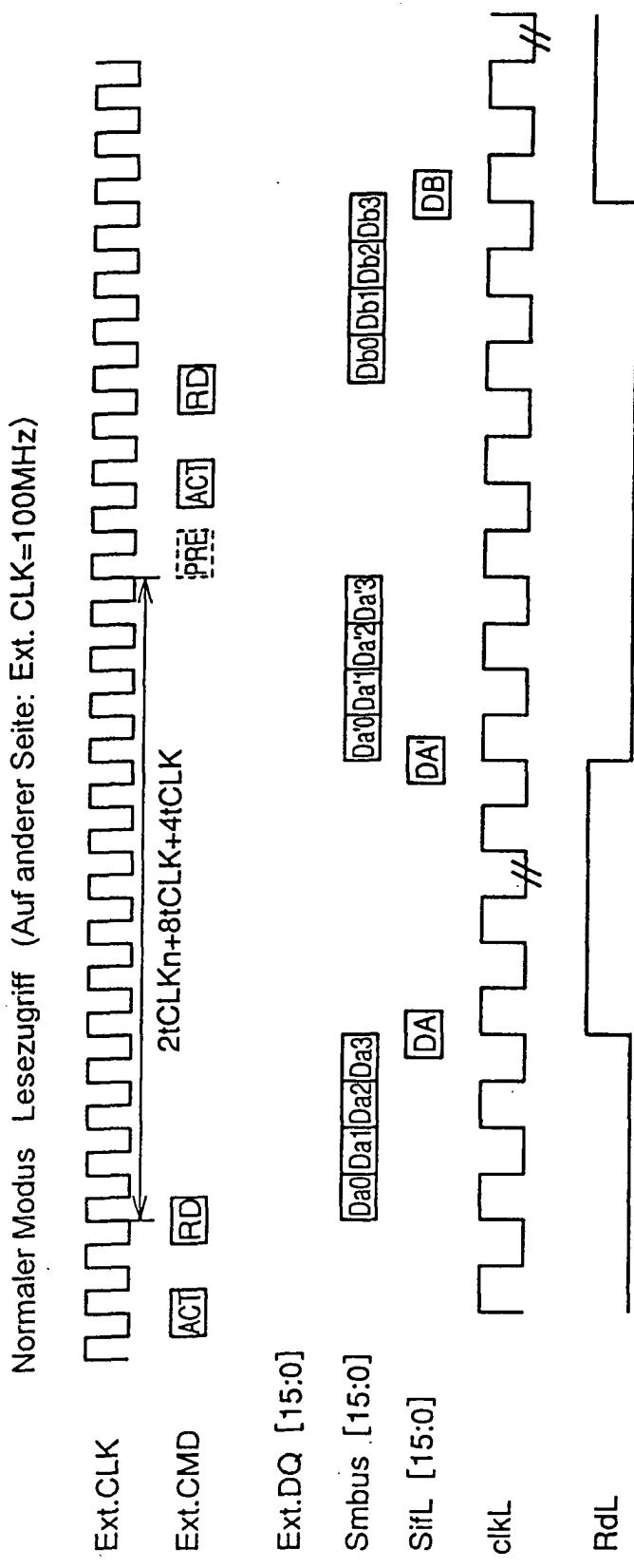

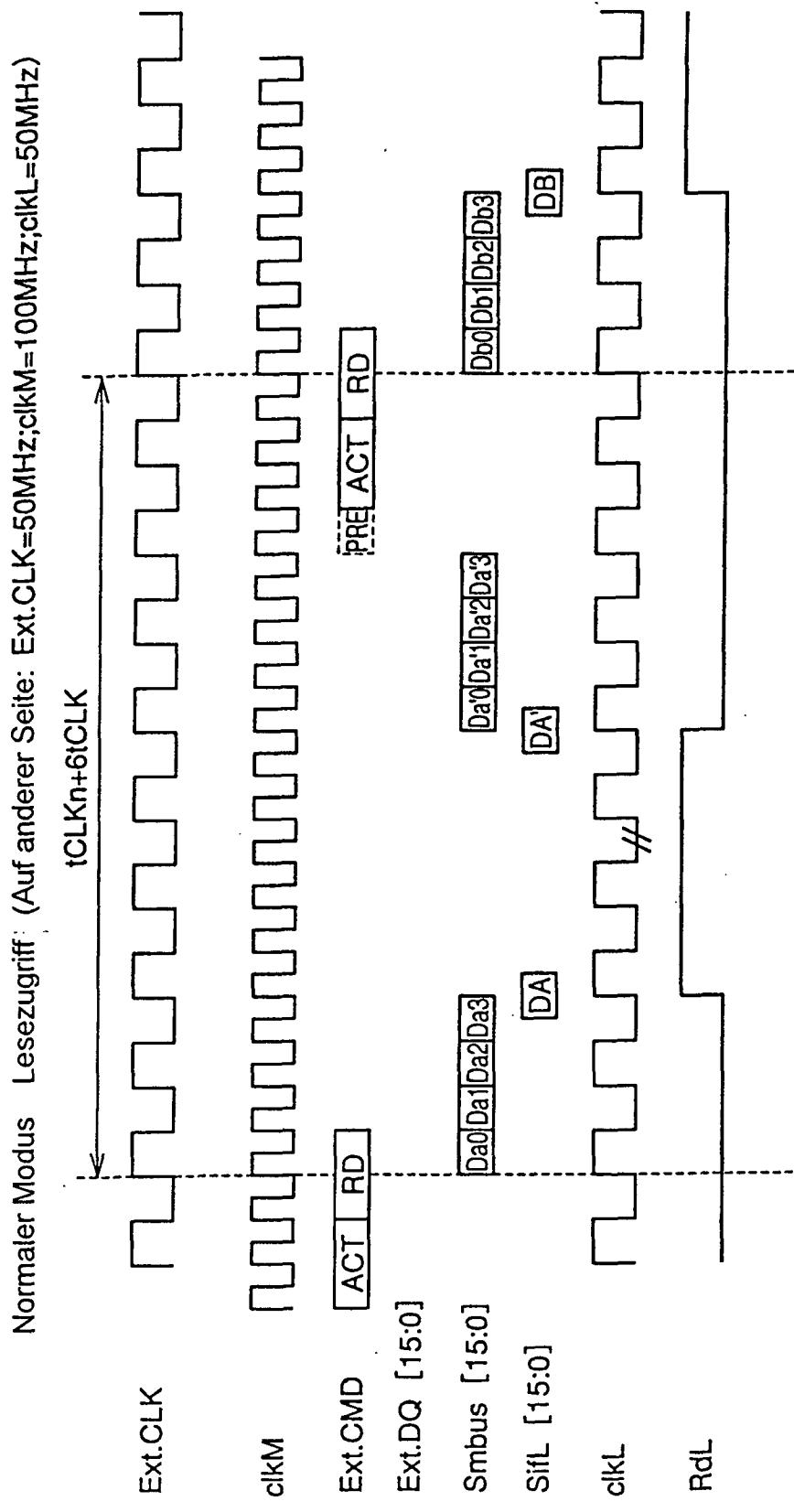

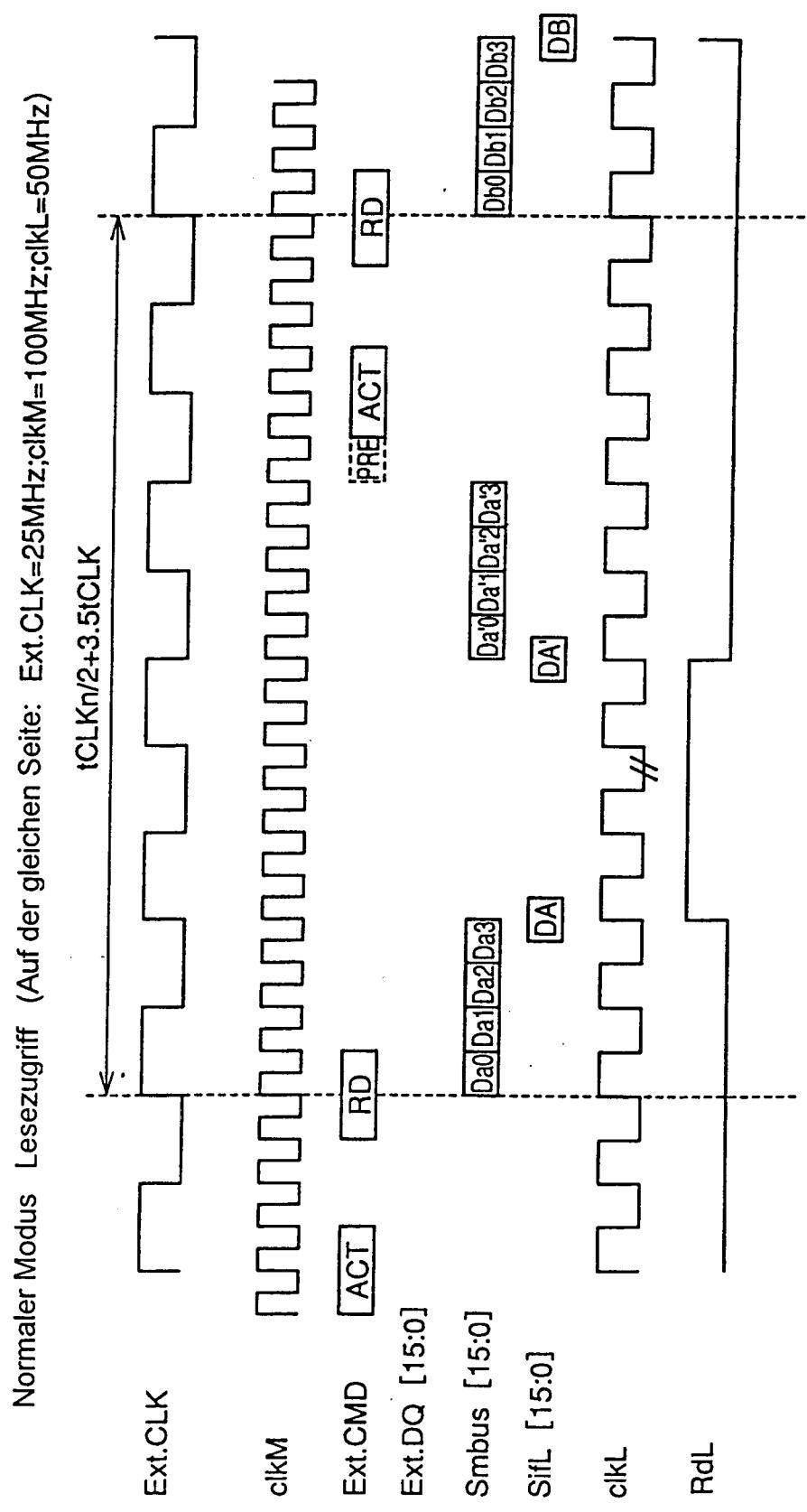

[0046] **Fig. 27** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus durchgeführt wird;

[0047] **Fig. 28** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf eine andere Seite in dem normalen Modus durchgeführt wird;

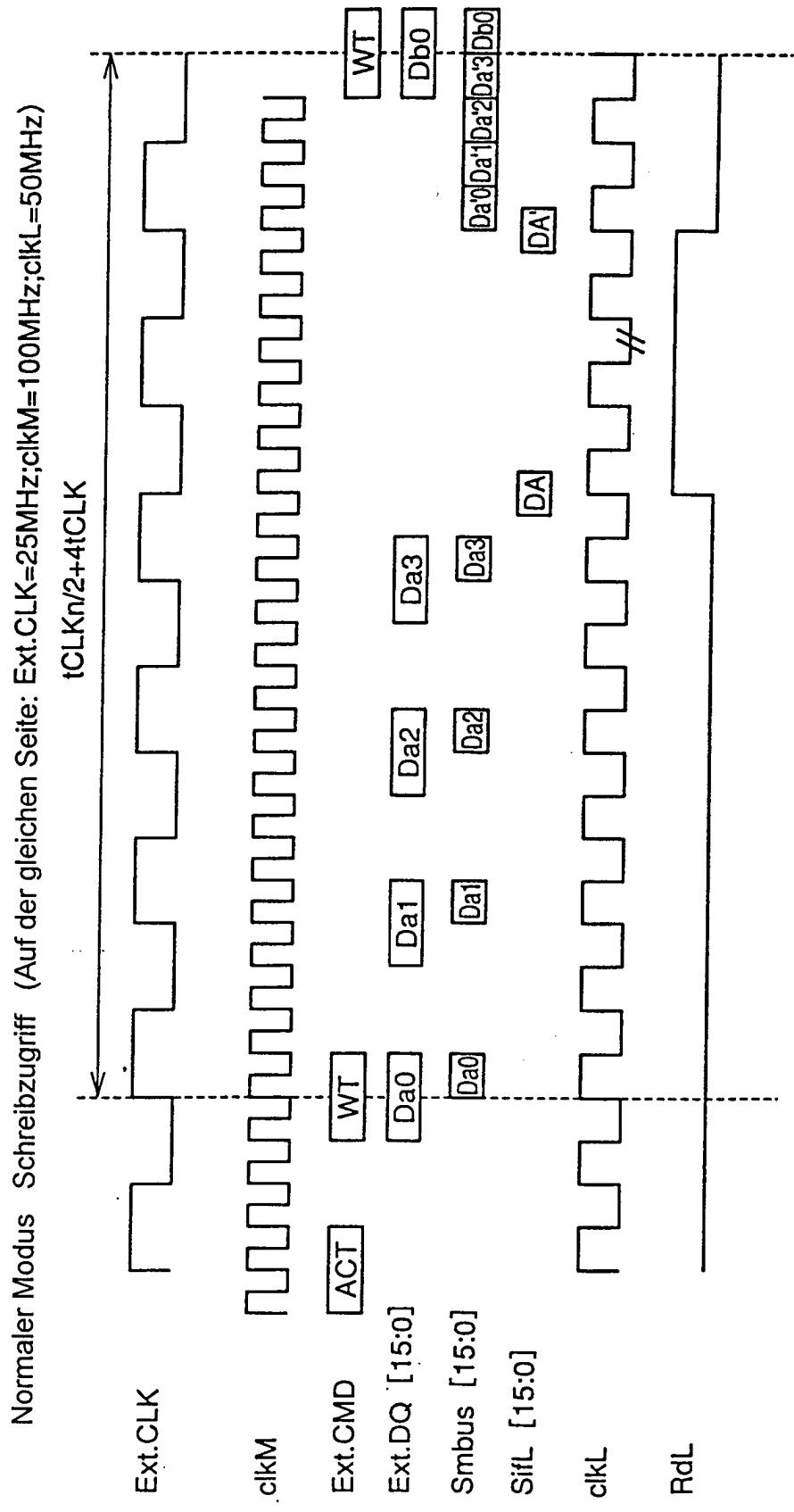

[0048] **Fig. 29** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn ein internes Taktignal clkL, das an die Logikschaltung **8** gegeben wird, zu 50 MHz umgewandelt wird;

[0049] **Fig. 30** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus durchgeführt wird;

[0050] **Fig. 31** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf eine andere Seite in dem normalen Modus durchgeführt wird;

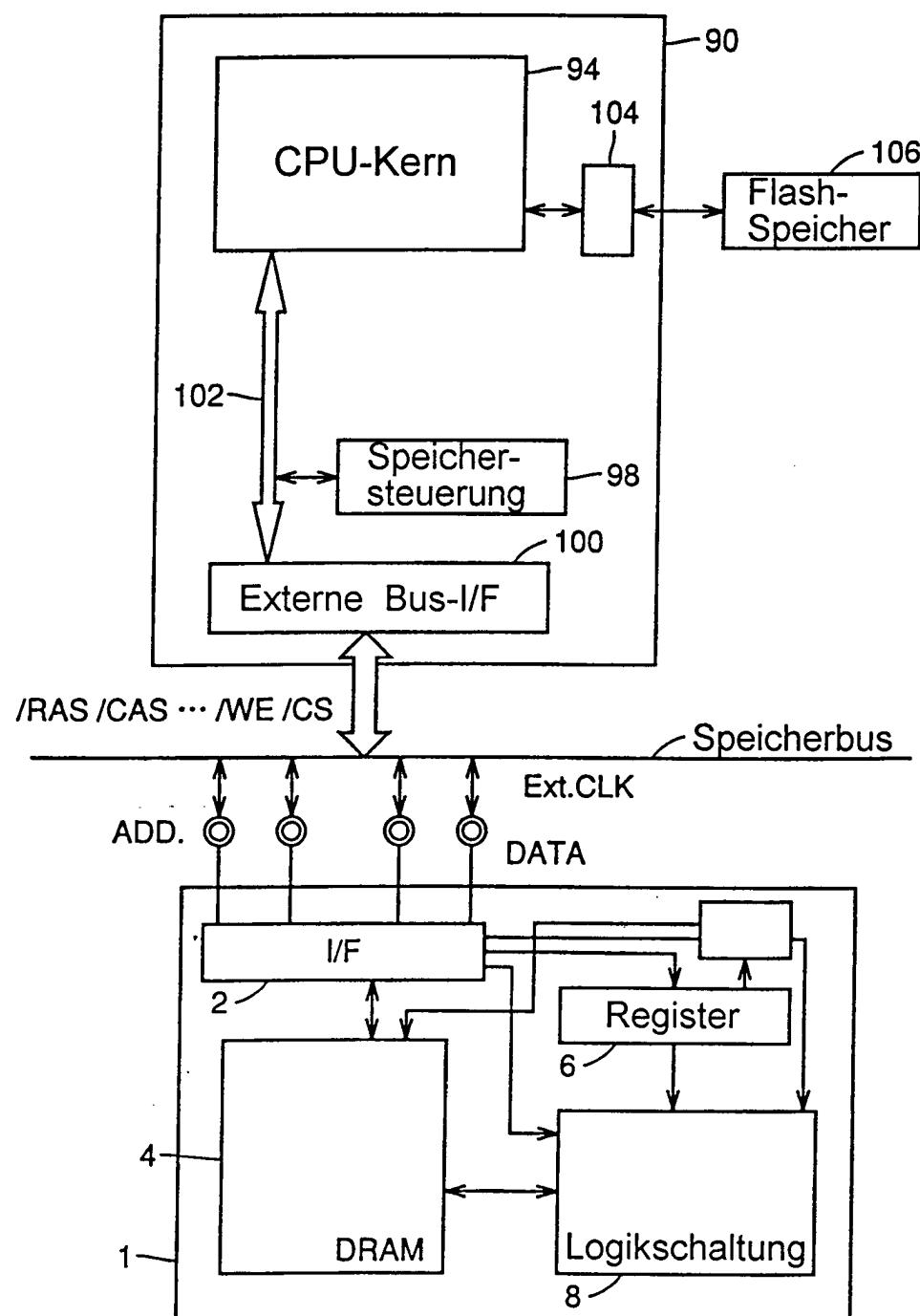

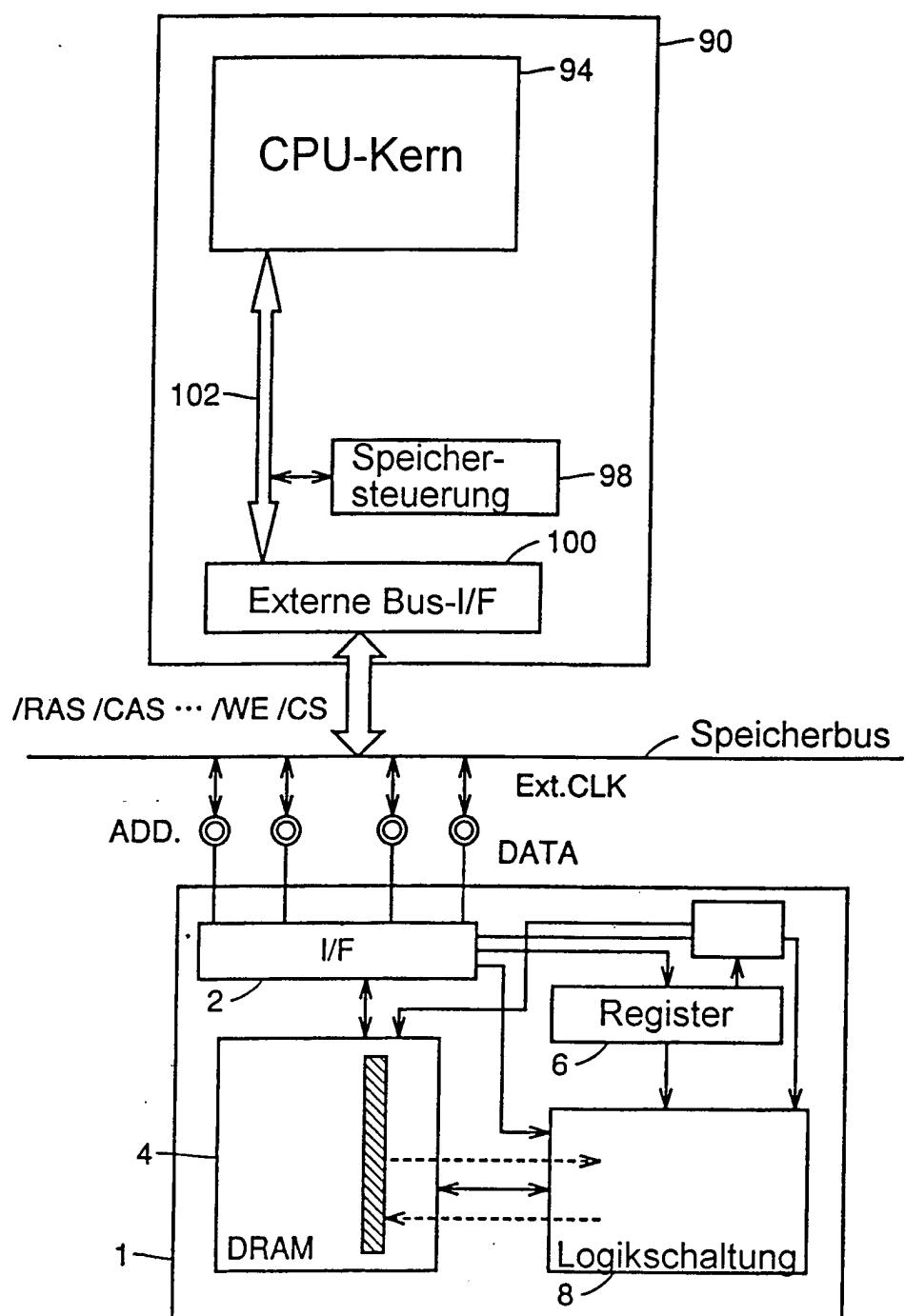

[0051] **Fig. 32** ist ein konzeptuelles Blockschaltbild, das einen Weg darstellt, wie eine integrierte Halbleiterschaltungsvorrichtung **1** der vorliegenden Erfindung und ein Mikroprozessor **90** verbunden werden;

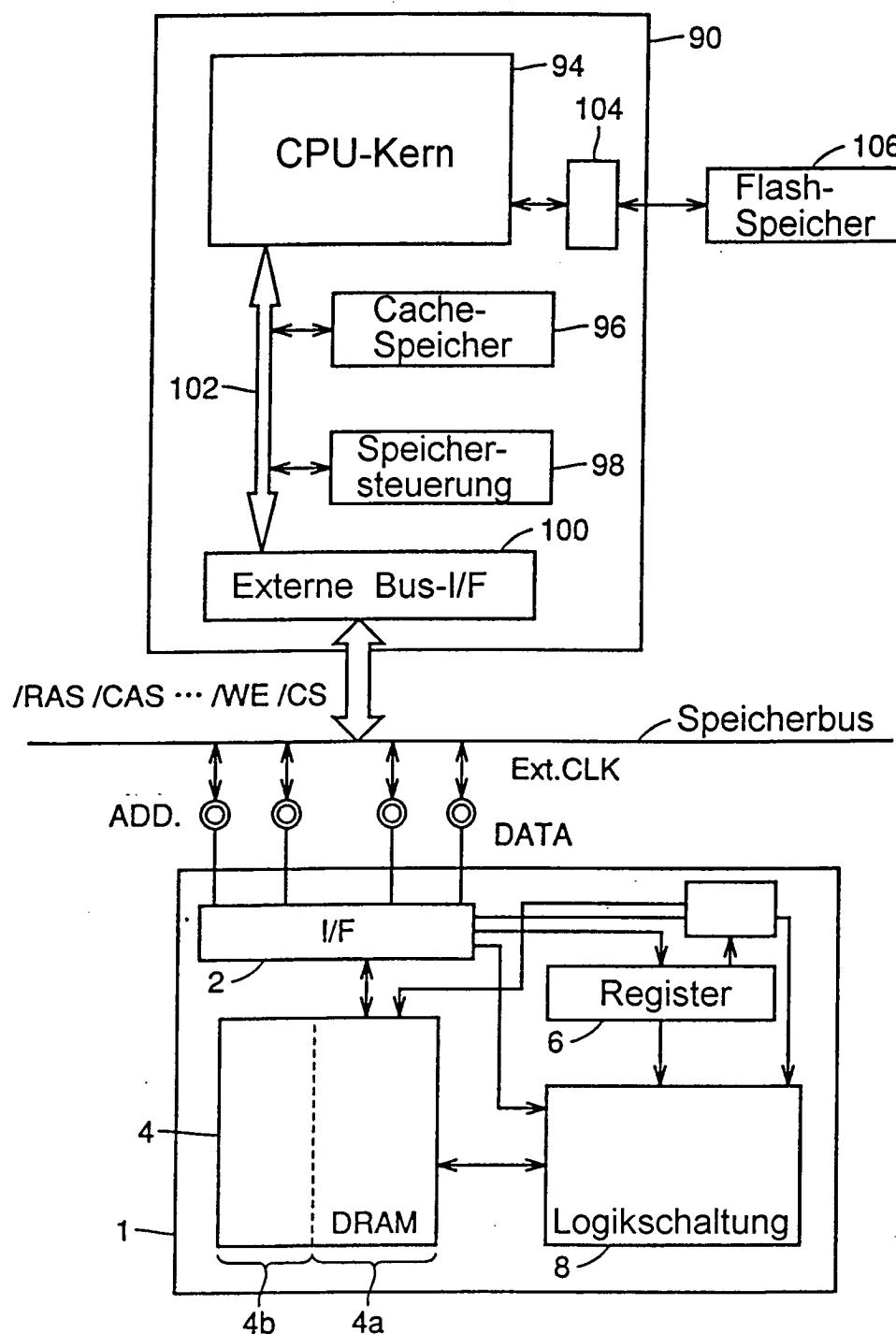

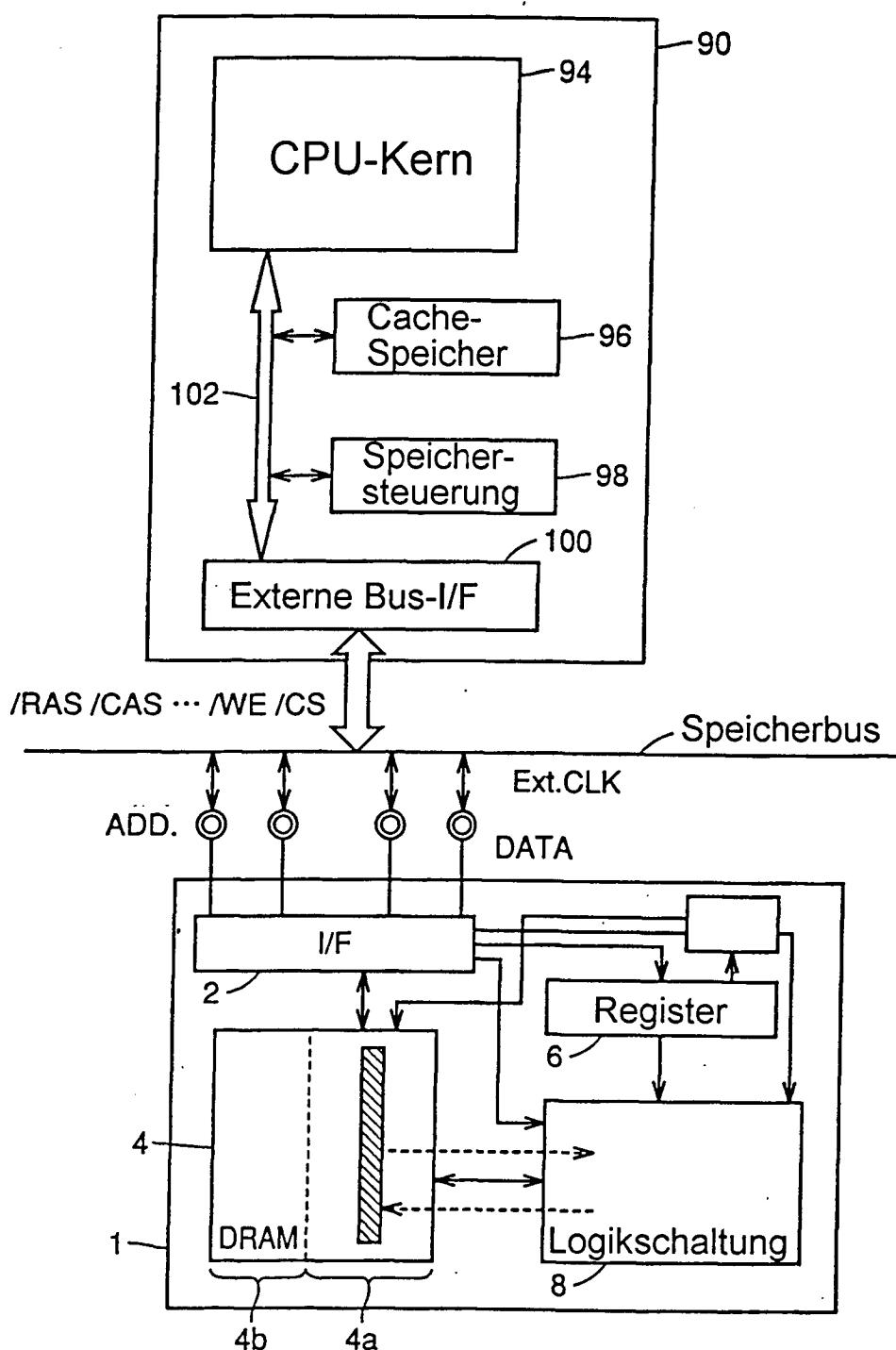

[0052] **Fig. 33** ist ein konzeptuelles Blockschaltbild, das einen anderen Weg darstellt, wie die integrierte Halbleiterschaltungsvorrichtung **1** der vorliegenden Erfindung und ein Mikroprozessor **90** verbunden werden;

[0053] **Fig. 34** ist ein Flußdiagramm zum Beschreiben der Steuerung der integrierten Halbleiterschaltungsvorrichtung **1**;

[0054] **Fig. 35** ist ein konzeptuelles Blockschaltbild, das ein Beispiel eines Systems darstellt, das für die

Anwendung eines Blockmodus der integrierten Halbleiterschaltungsvorrichtung **1** geeignet ist;

[0055] **Fig. 36** ist ein konzeptuelles Blockschaltbild, das eine Konfiguration darstellt, wenn eine in dem Blockmodus tätige integrierte Halbleiterschaltungsvorrichtung **1** auf ein System angewendet wird, in dem ein Cache-Speicher **96** vorhanden ist;

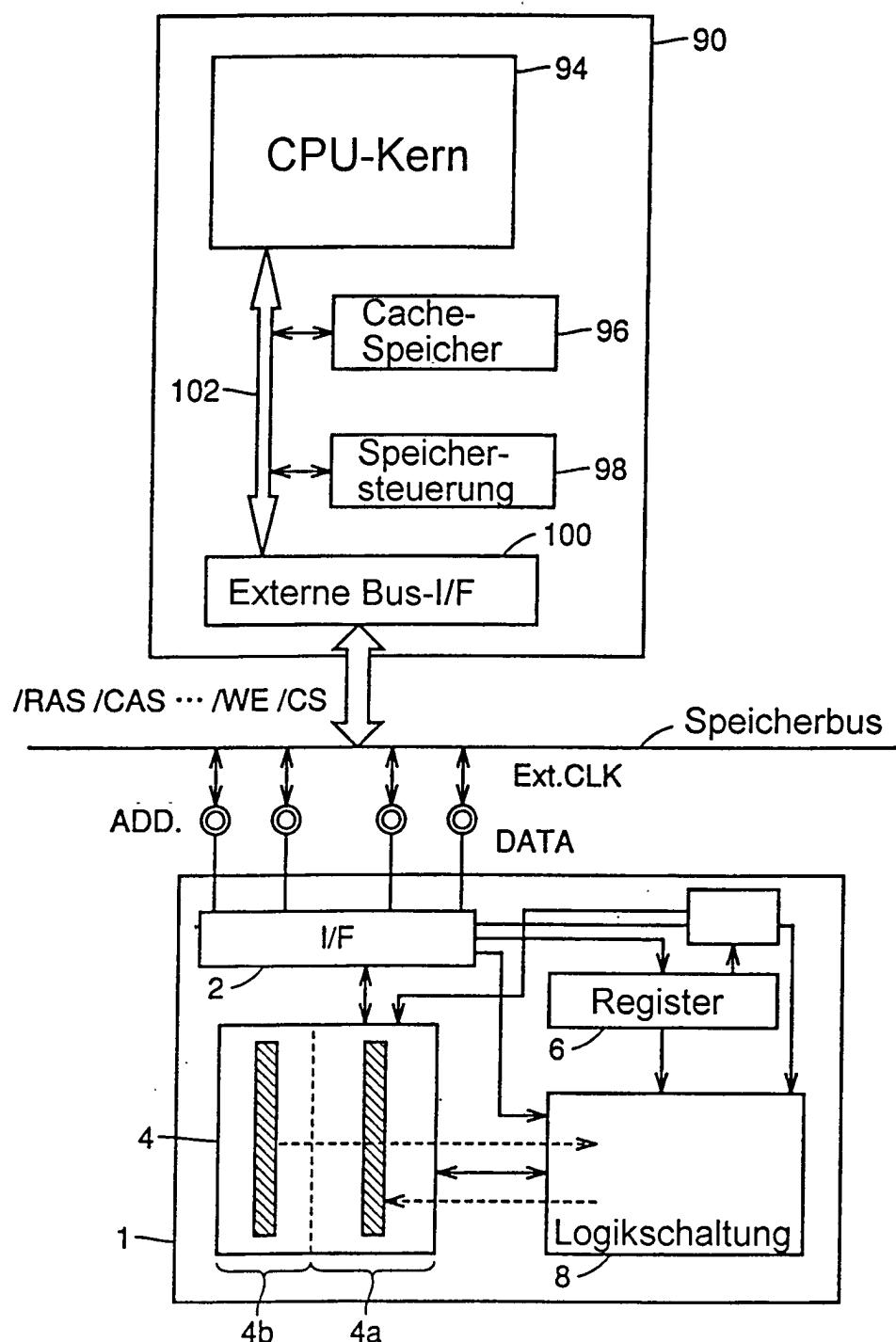

[0056] **Fig. 37** ist ein schematisches Blockschaltbild, das eine Konfiguration eines Systems zeigt, das geeignet ist, wenn ein Puffermodus der integrierten Halbleiterschaltungsvorrichtung **1** angenommen wird;

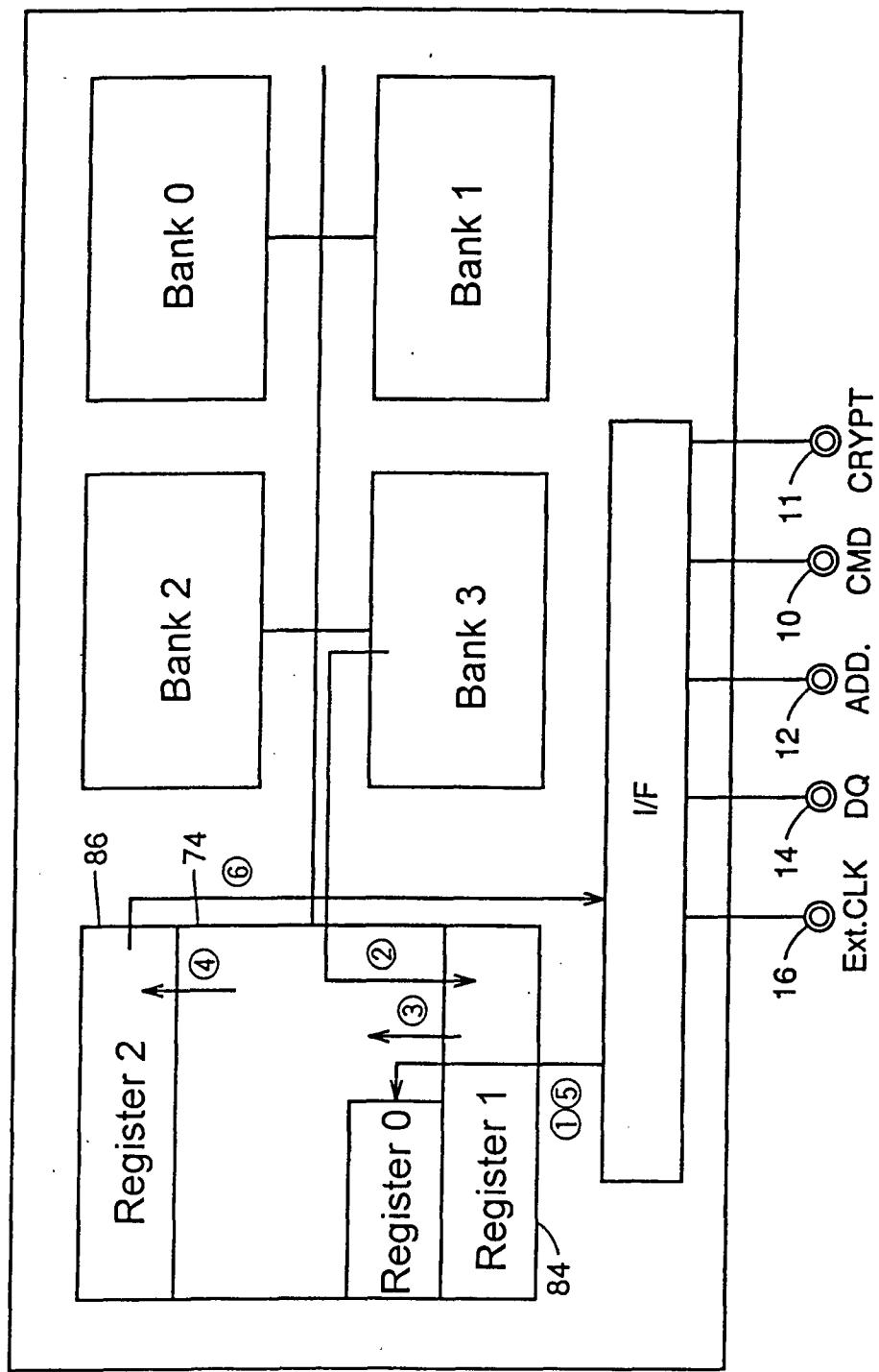

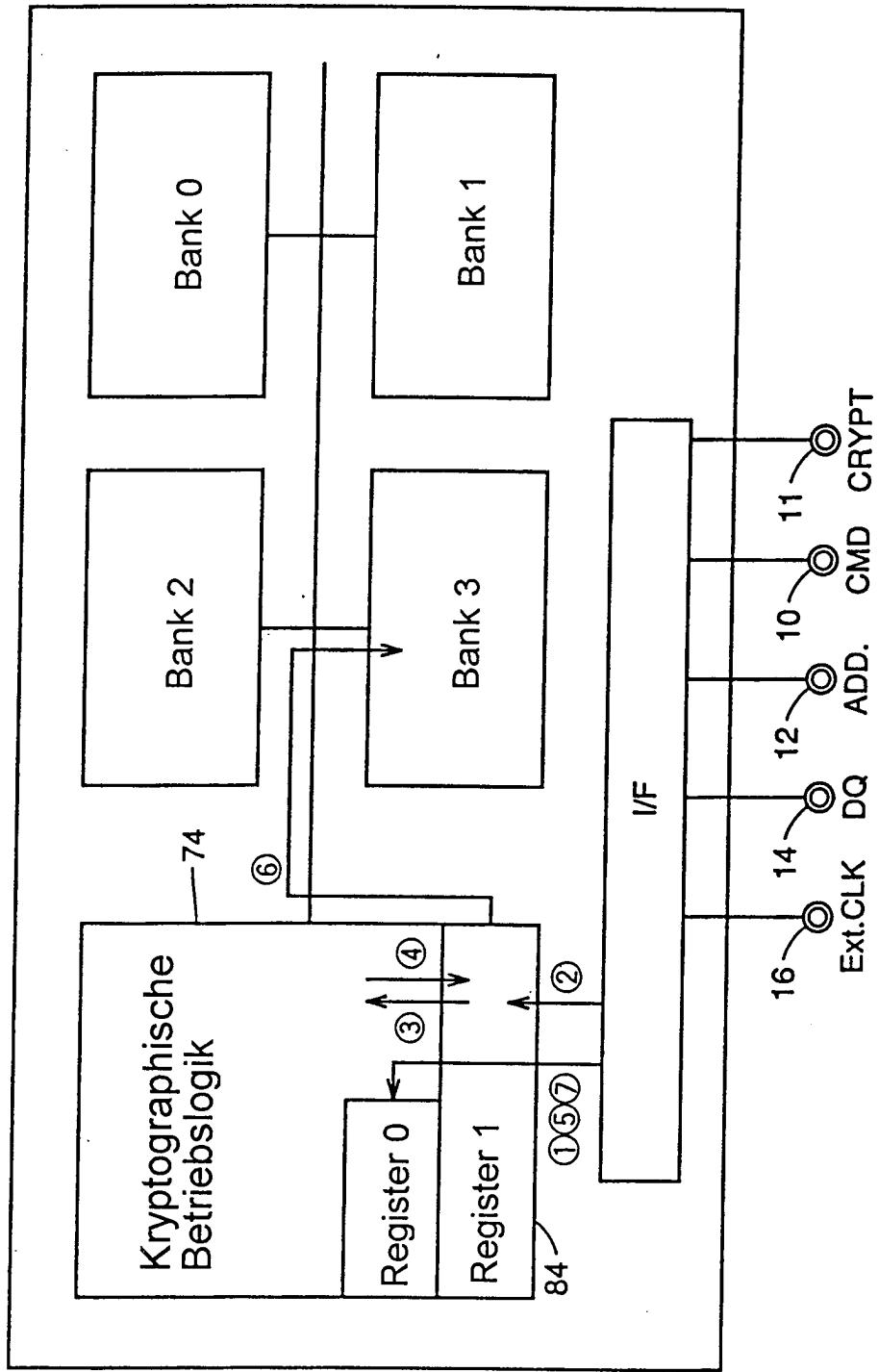

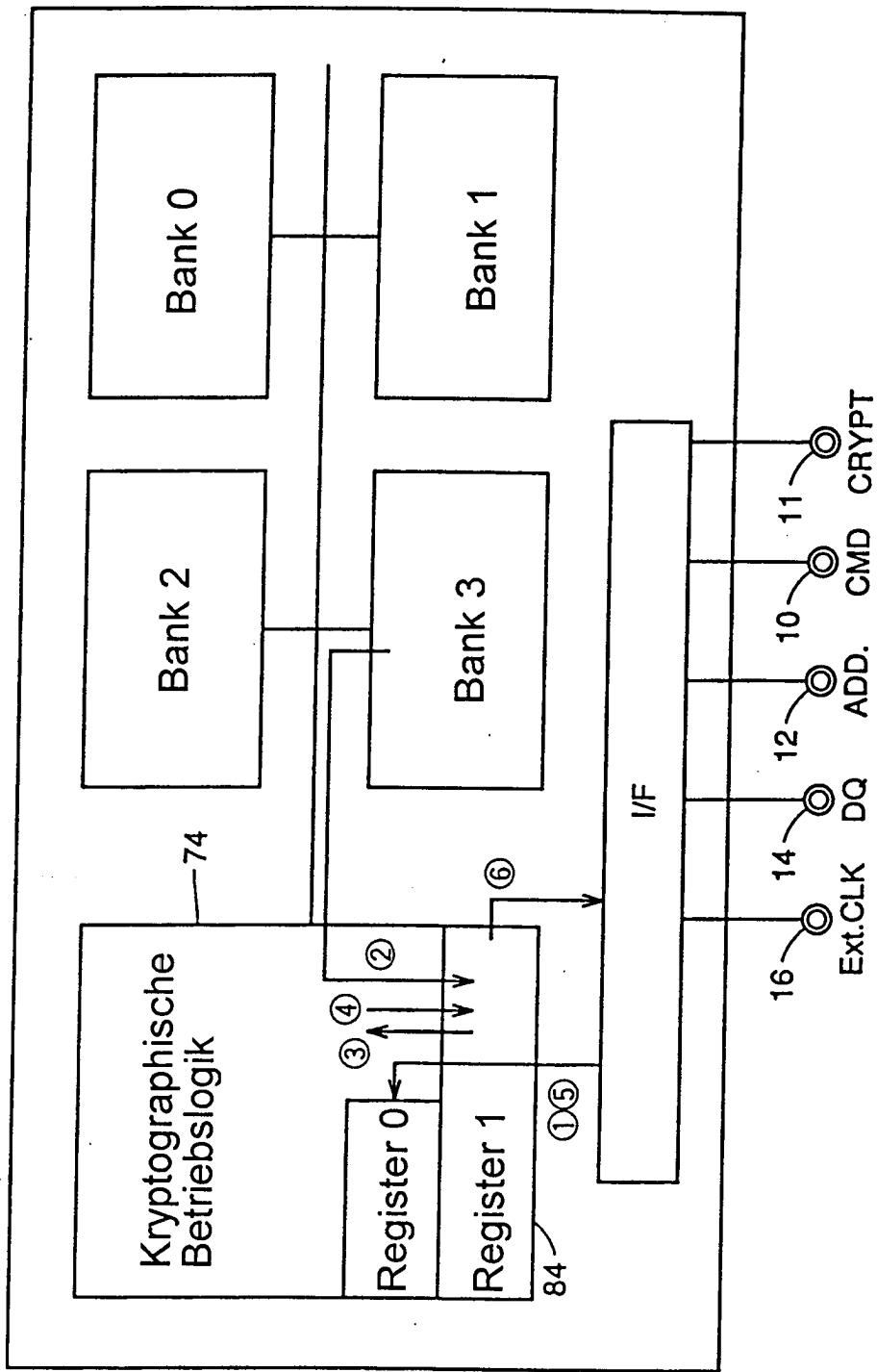

[0057] **Fig. 38** ist ein Blockschaltbild, das eine Konfiguration eines integrierten Logik-DRAM **30** eines dritten Beispiele darstellt, das durch Modifizieren der Konfiguration der integrierten Halbleiterschaltungsvorrichtung **1** des ersten Beispiele erhalten ist;

[0058] **Fig. 39** ist eine Zeichnung, die ein Speicherabbild eines Systems darstellt, das auf den integrierten Logik-DRAM **30** des dritten Beispiele angewendet ist;

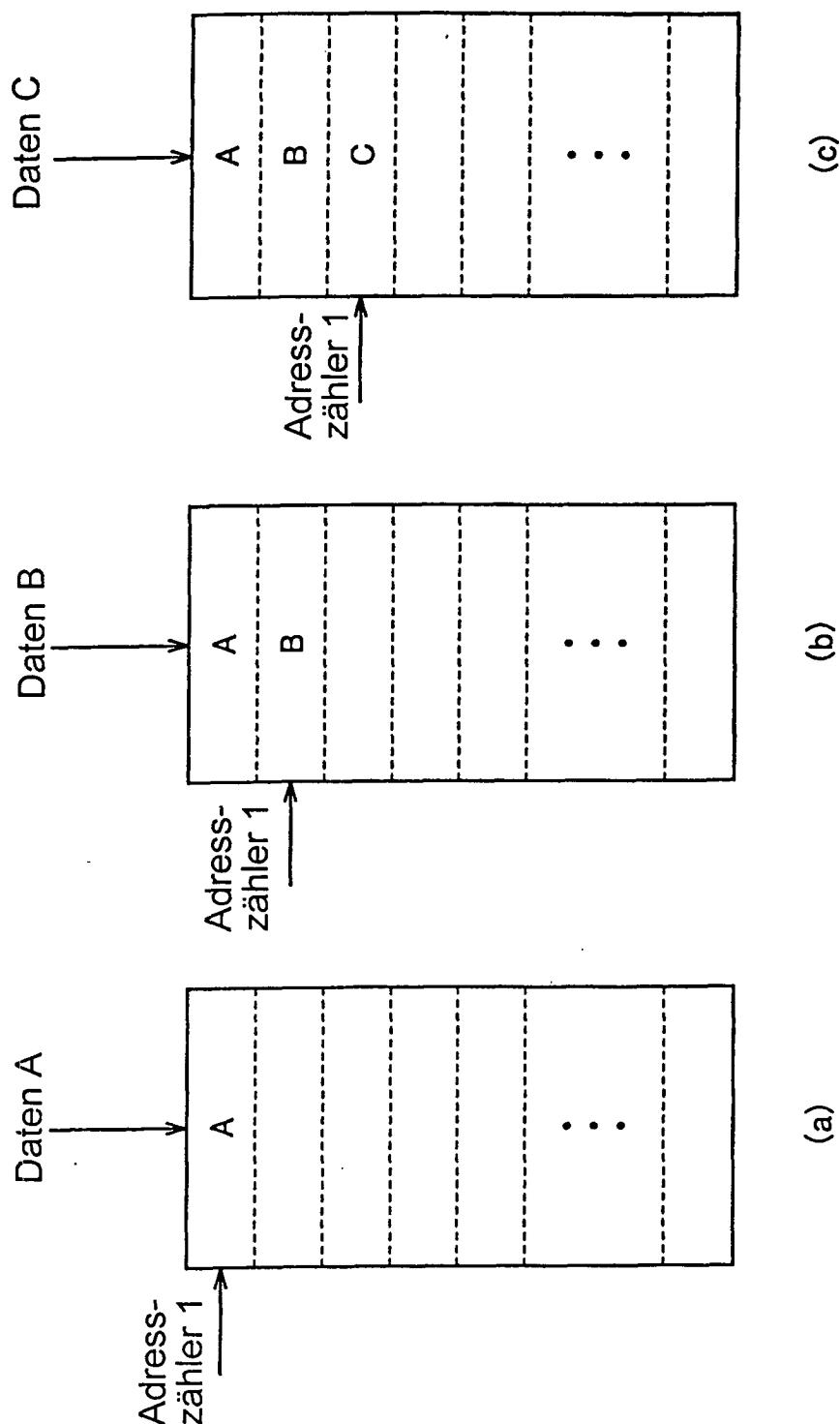

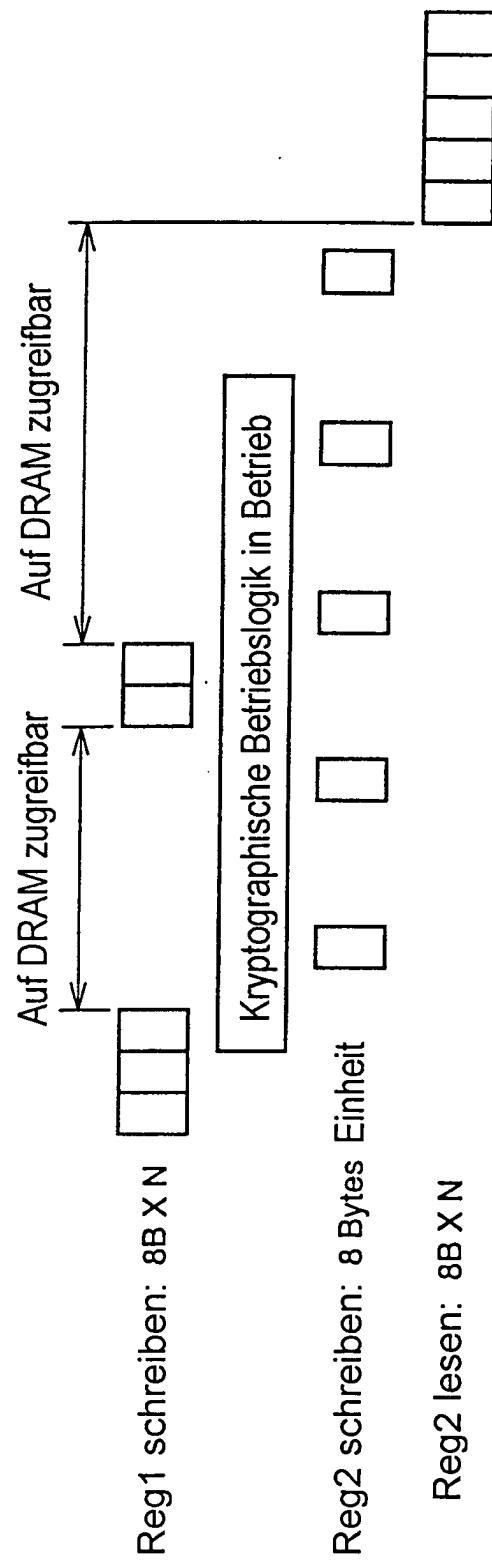

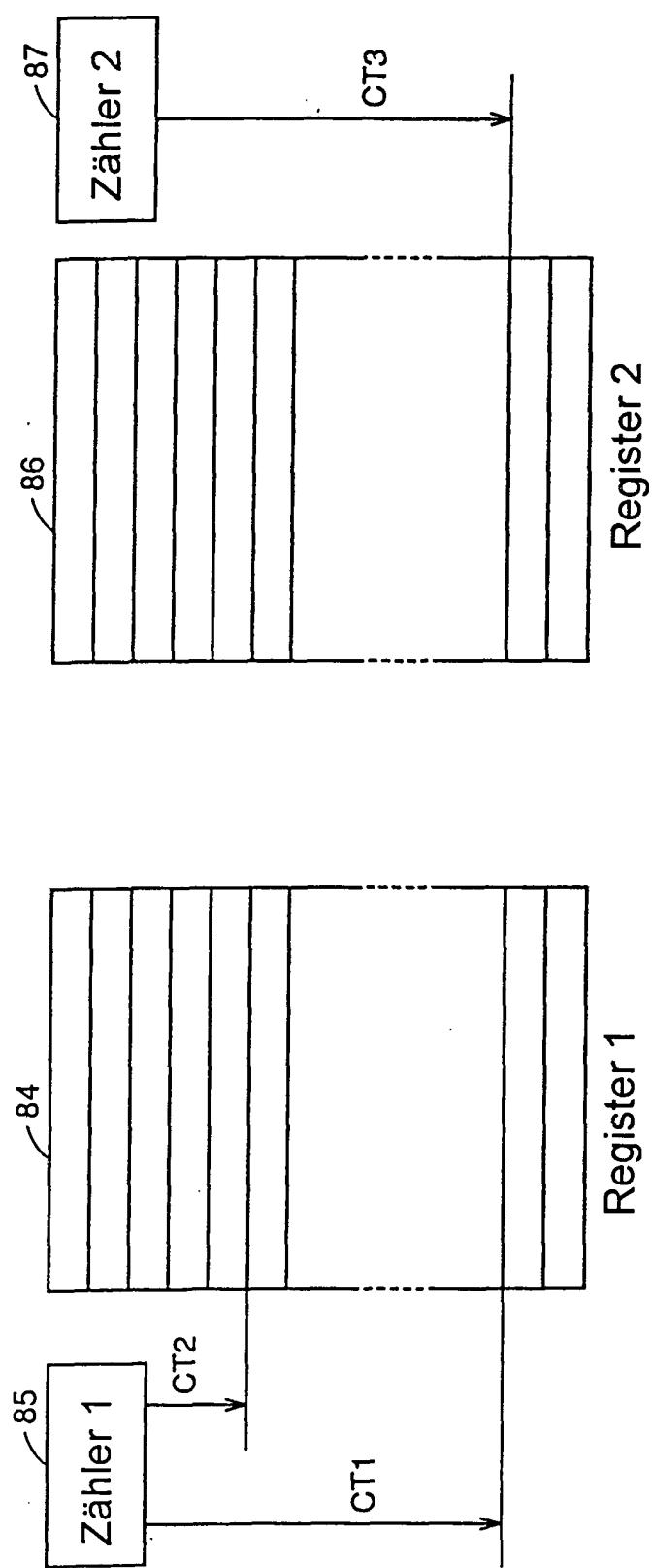

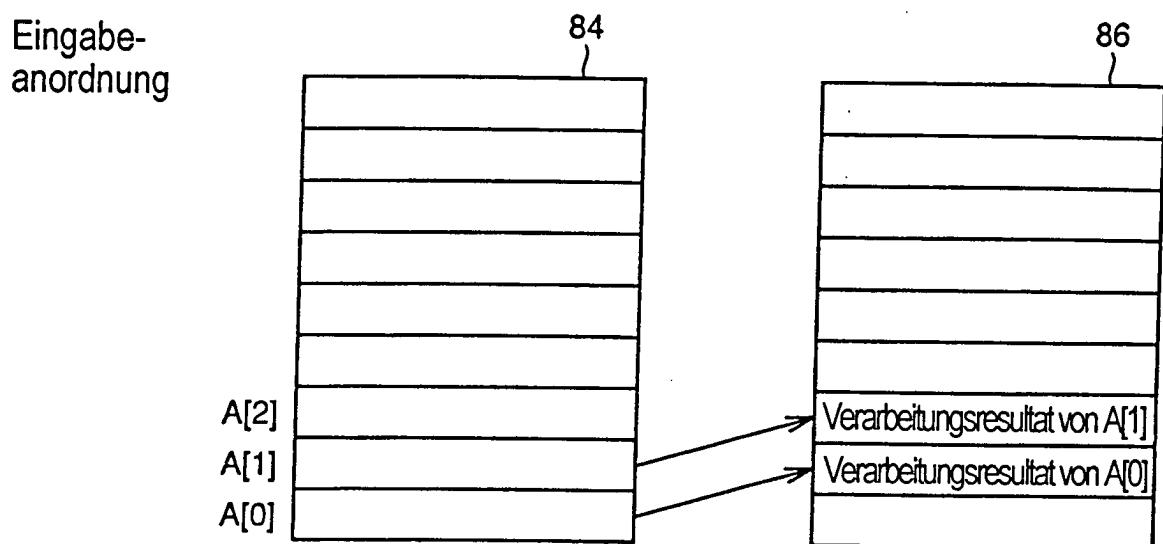

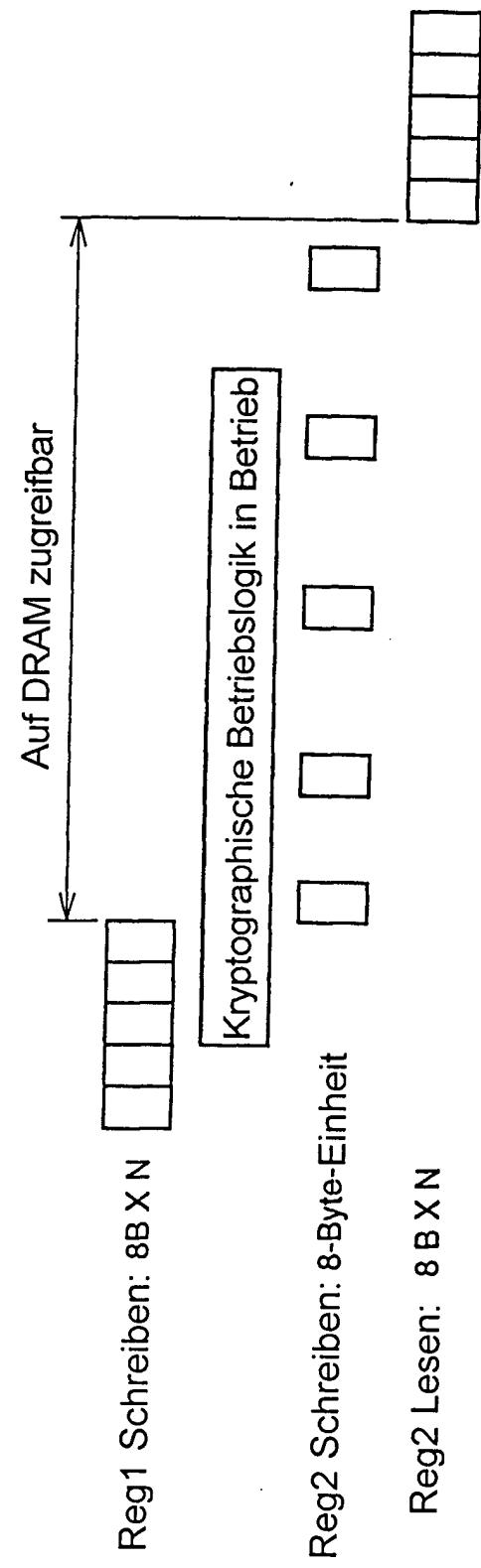

[0059] **Fig. 40** ist Zeichnungen, die Datenschreiben in ein erstes Datenregister **84** darstellen;

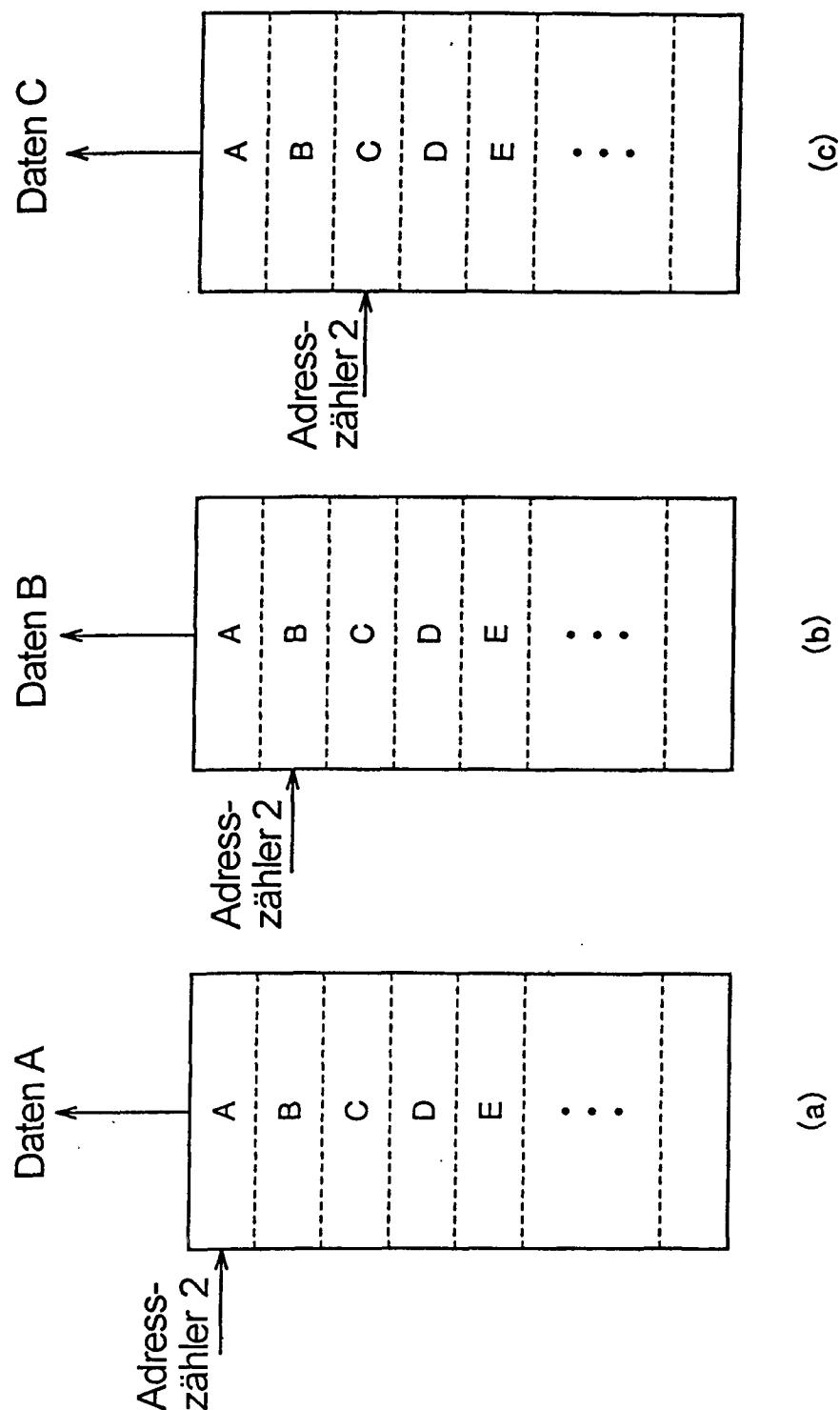

[0060] **Fig. 41** ist Zeichnungen, die Datenlesen von dem ersten Datenregister **84** darstellen;

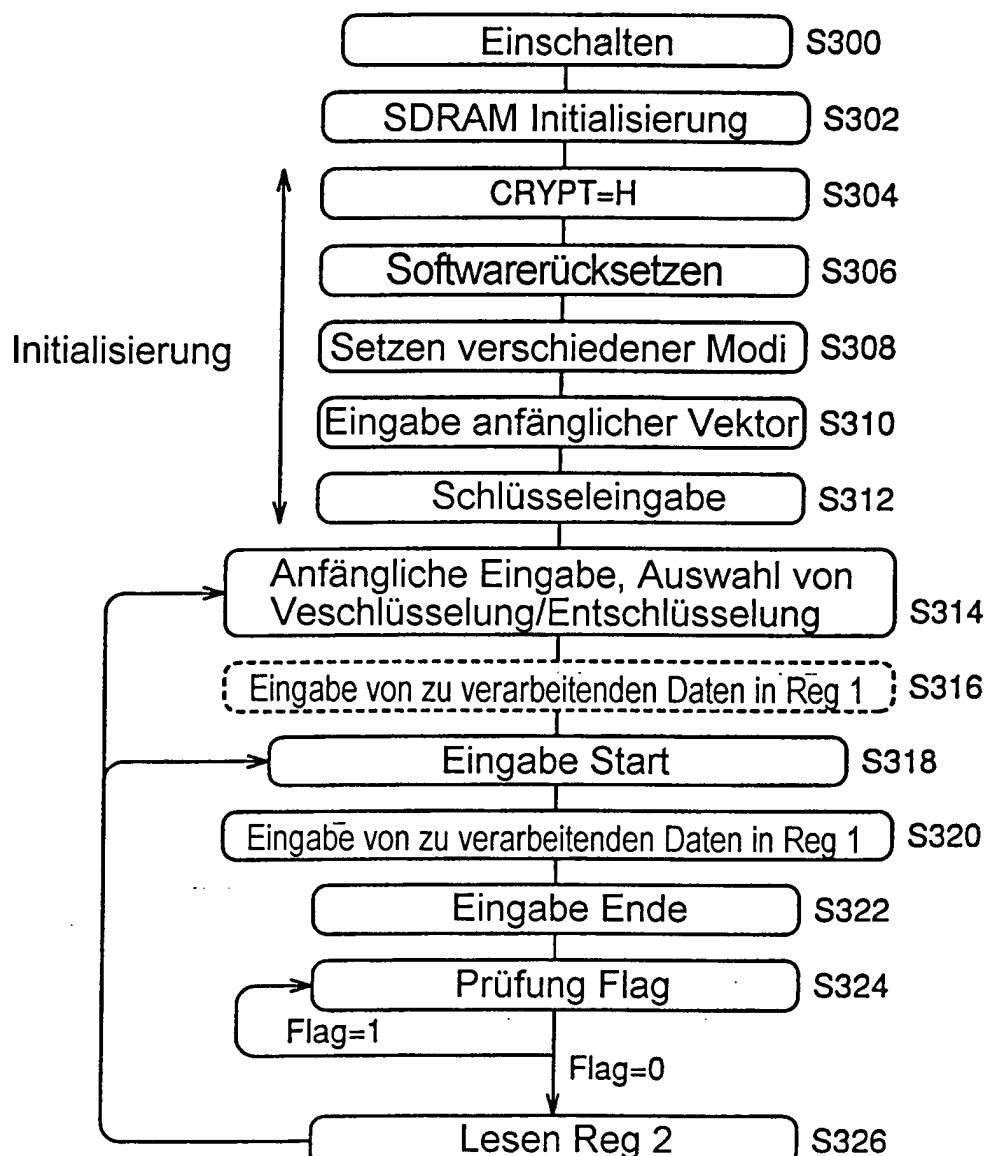

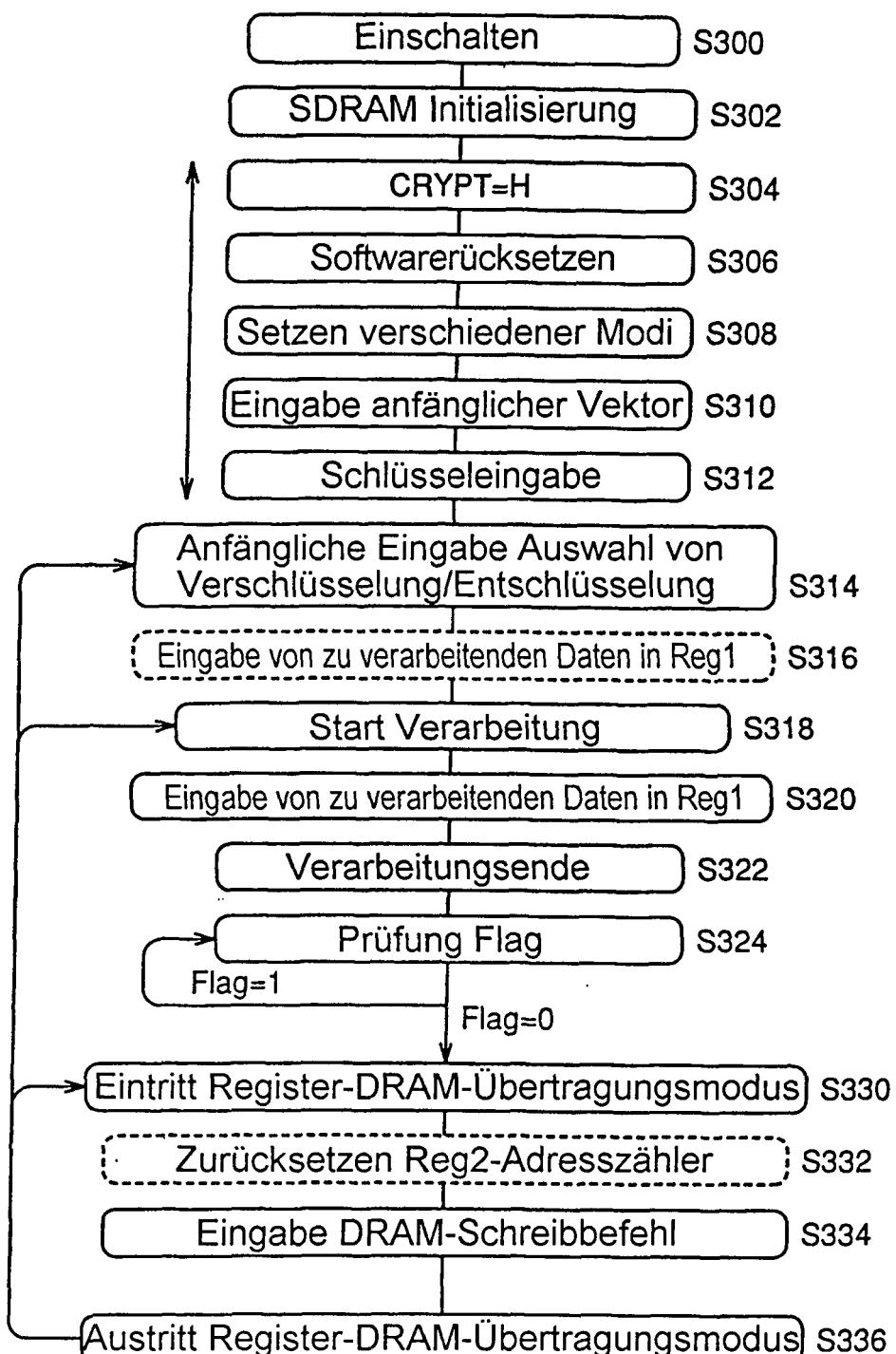

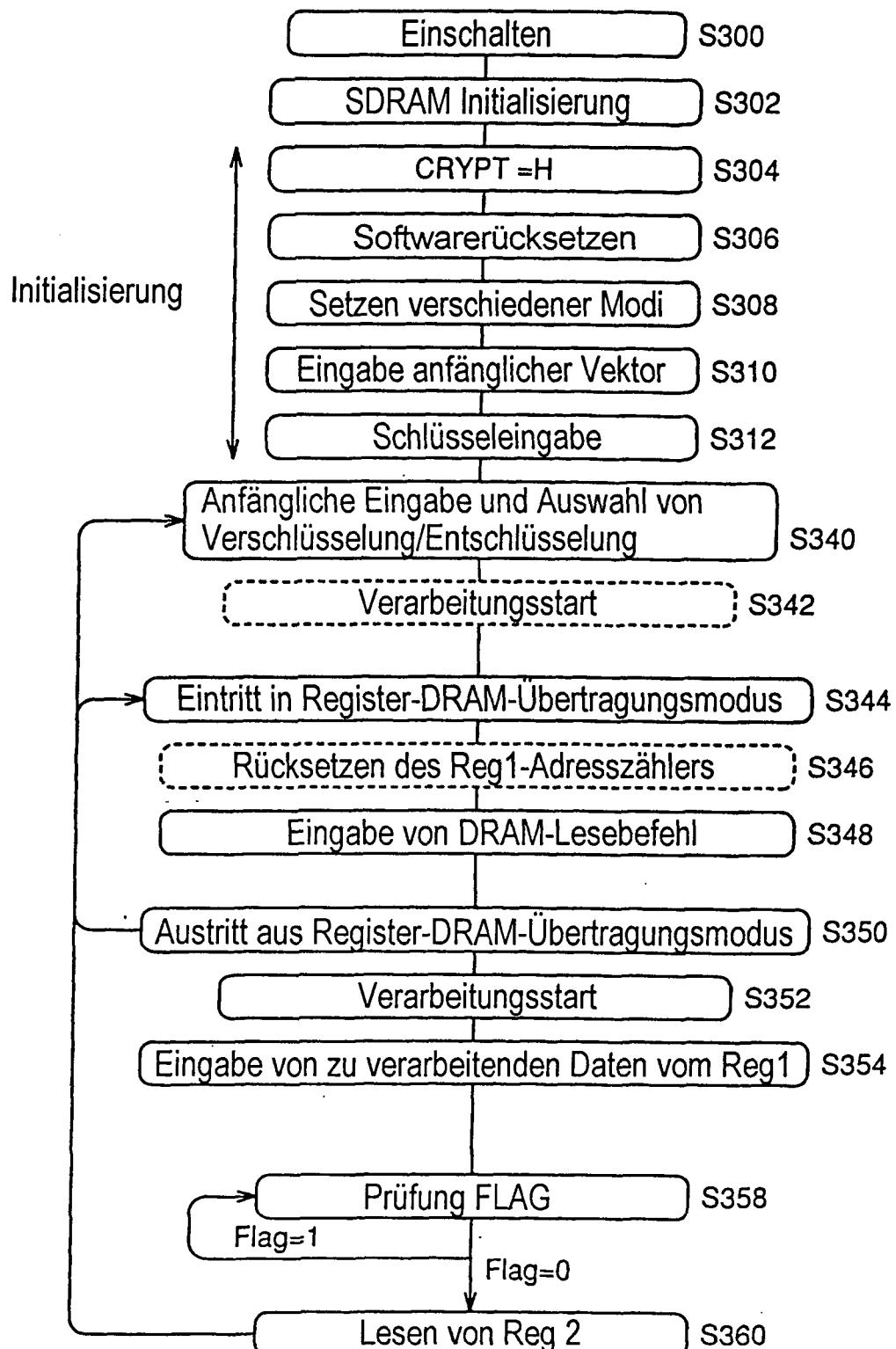

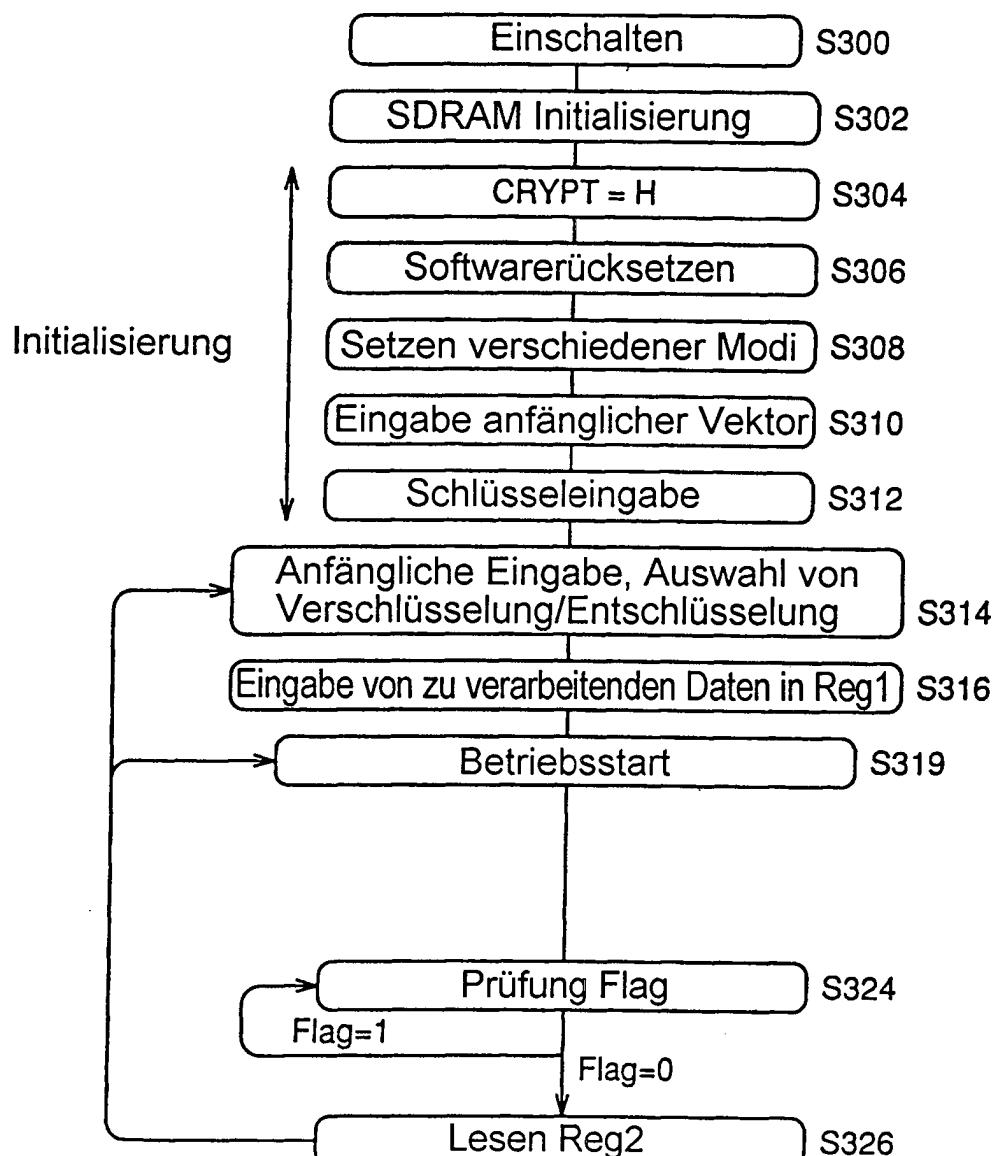

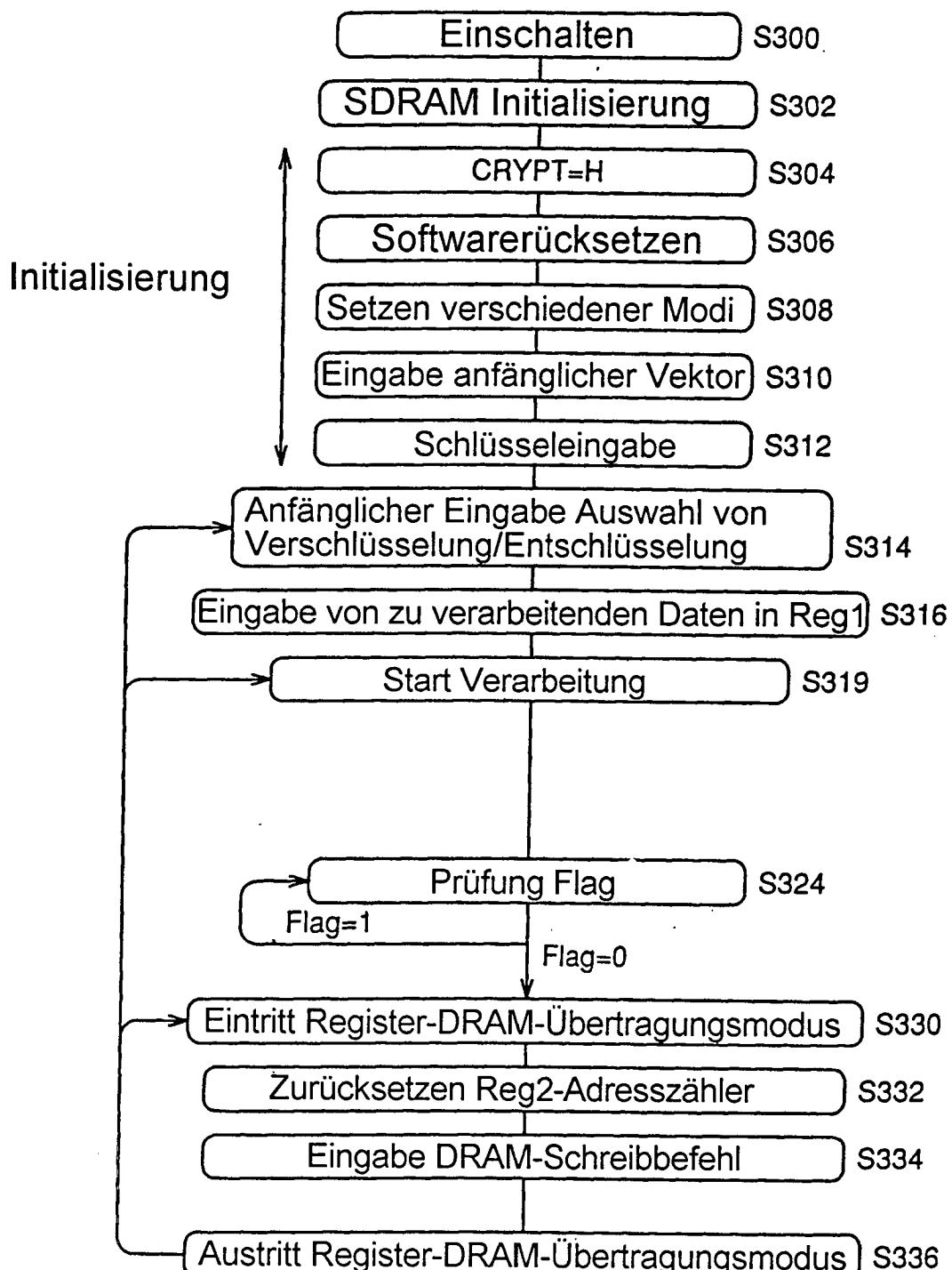

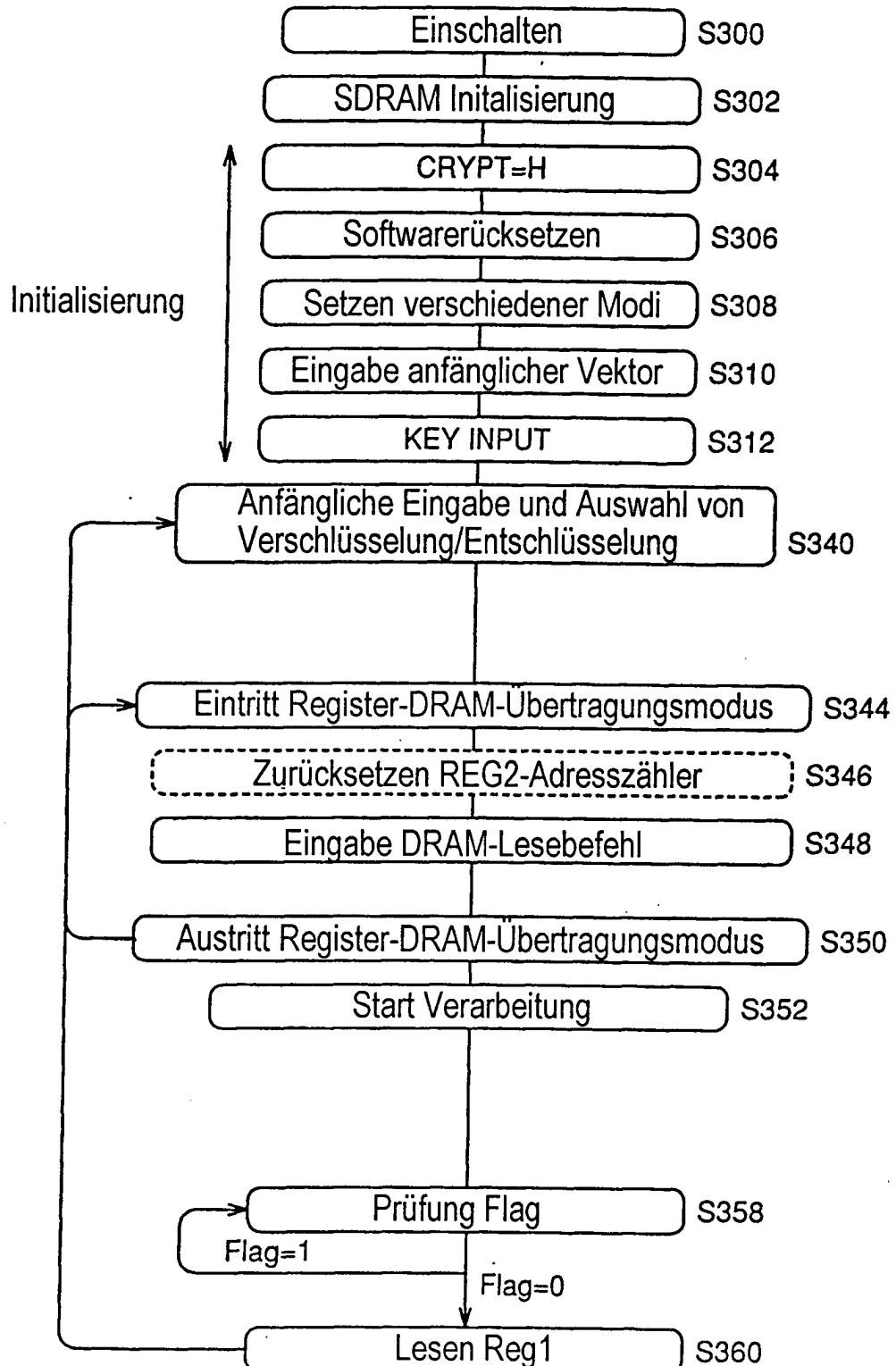

[0061] **Fig. 42** ist ein erstes Flußdiagramm zum Beschreiben eines Betriebes des in **Fig. 38** gezeigten integrierten Logik-DRAM **30**;

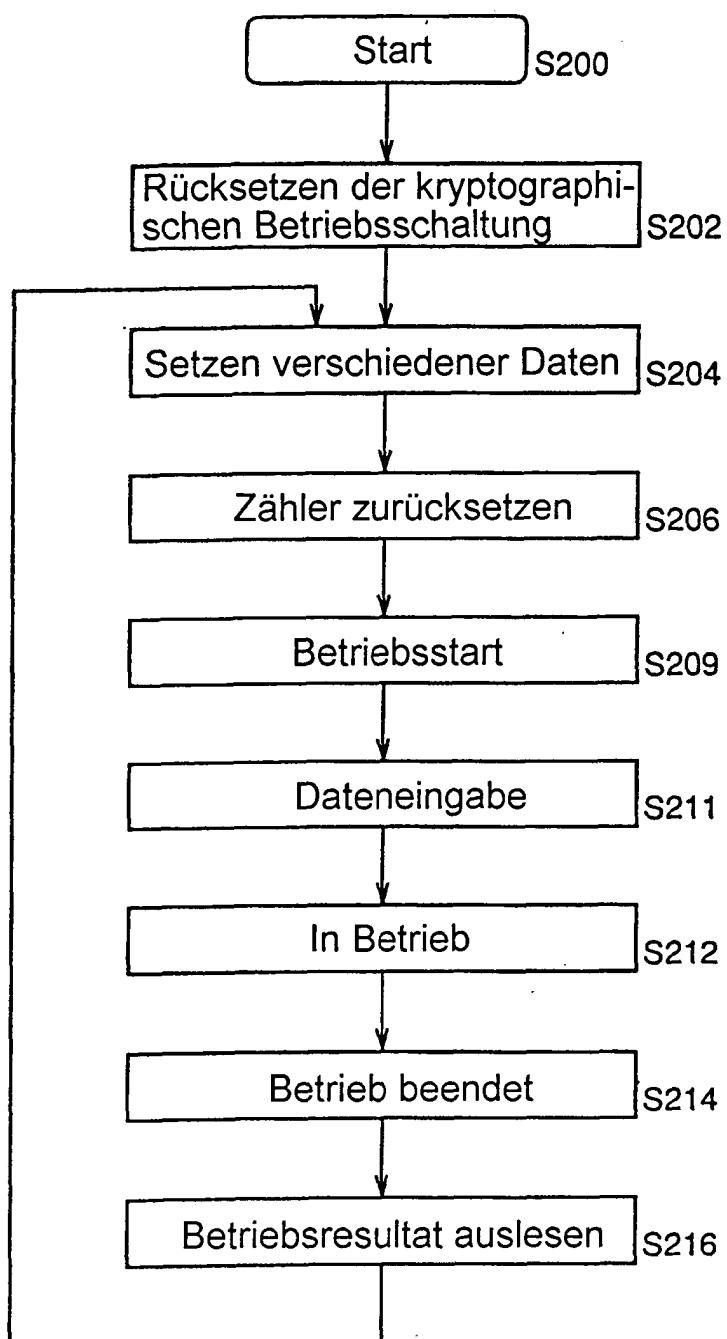

[0062] **Fig. 43** ist ein Flußdiagramm zum Schreiben eines anderen Betriebes des in **Fig. 38** gezeigten integrierten Logik-DRAM **30**;

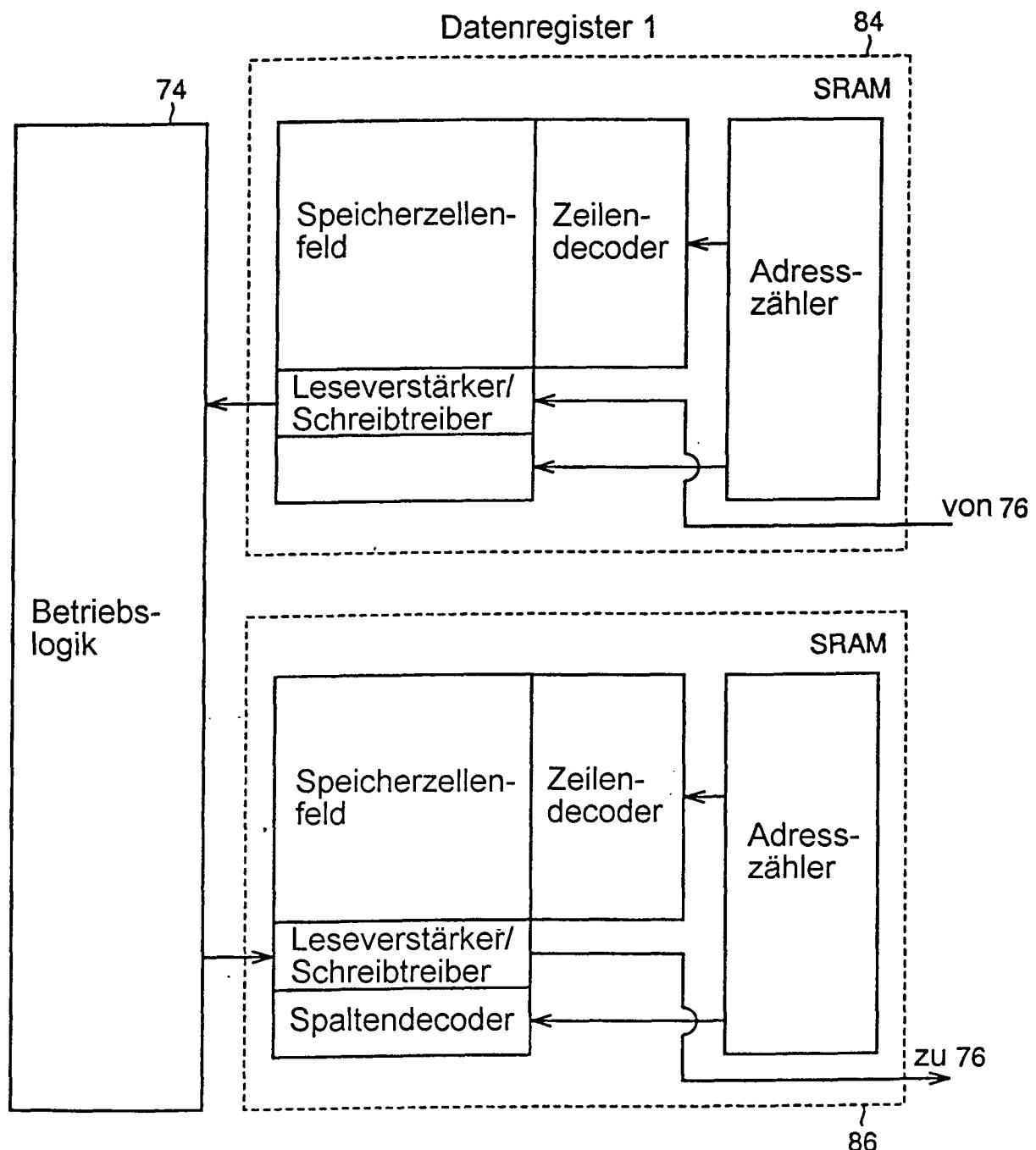

[0063] **Fig. 44** ist ein Blockschaltbild, das eine Konfiguration darstellt, wenn das erste und das zweite Register aus SRAMs dargestellt sind;

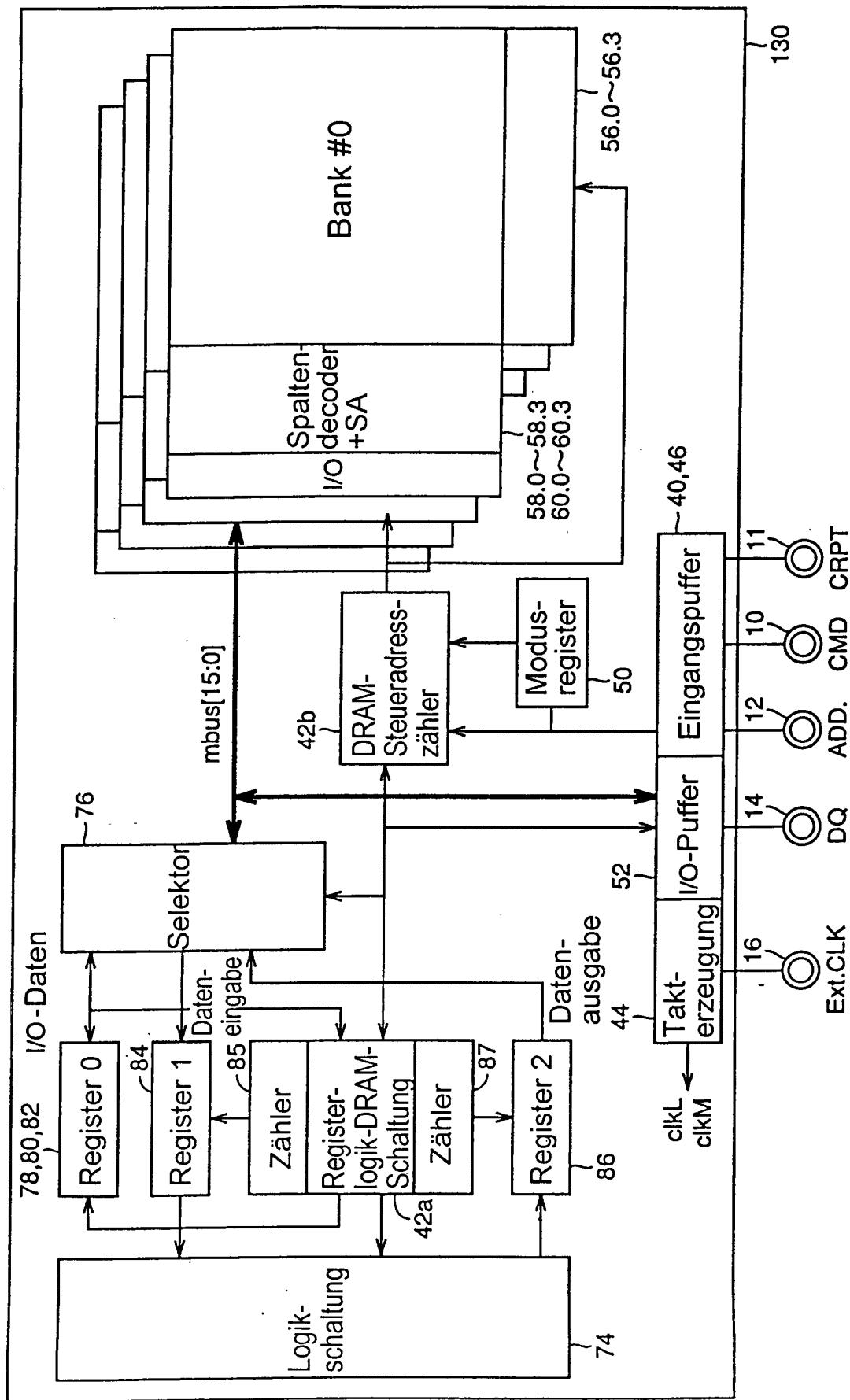

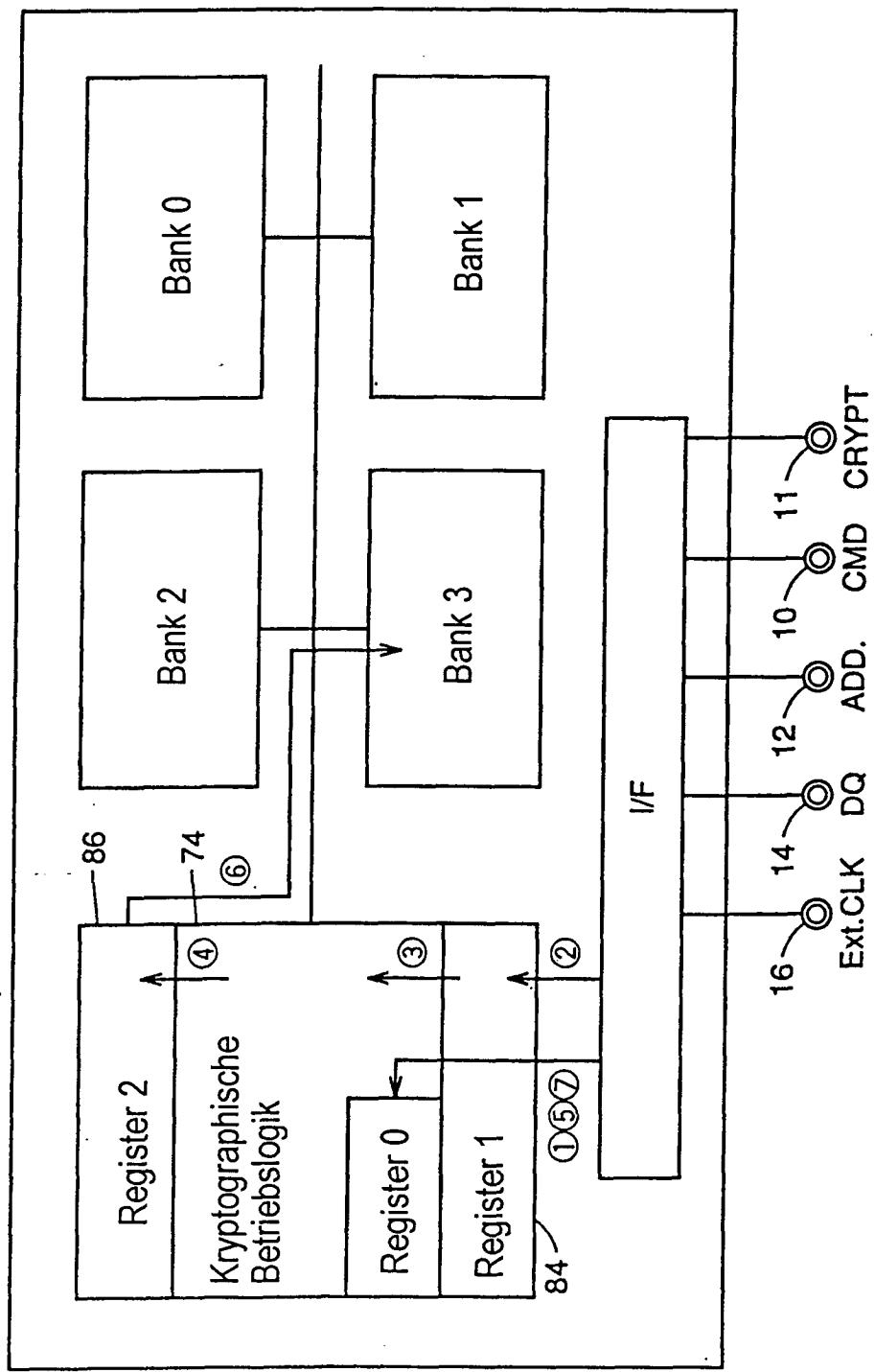

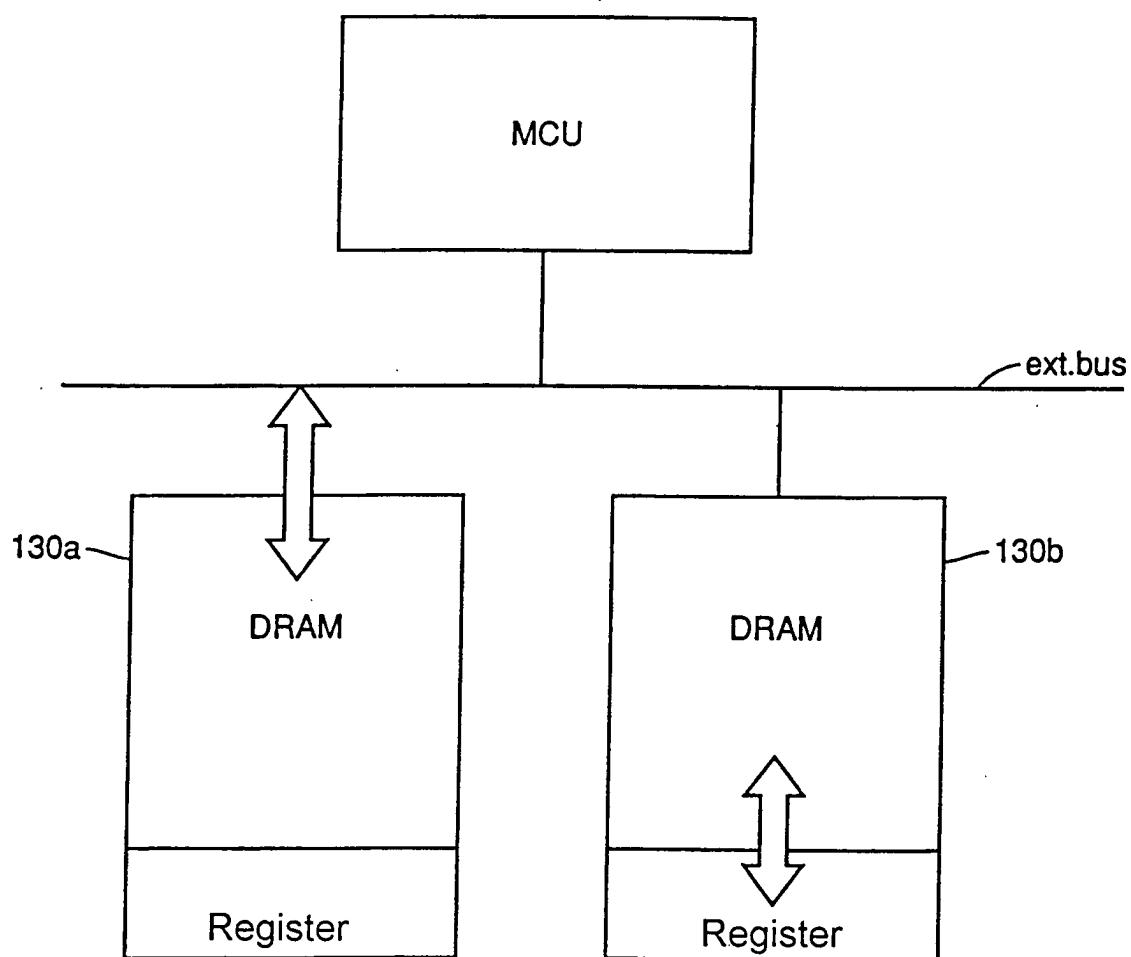

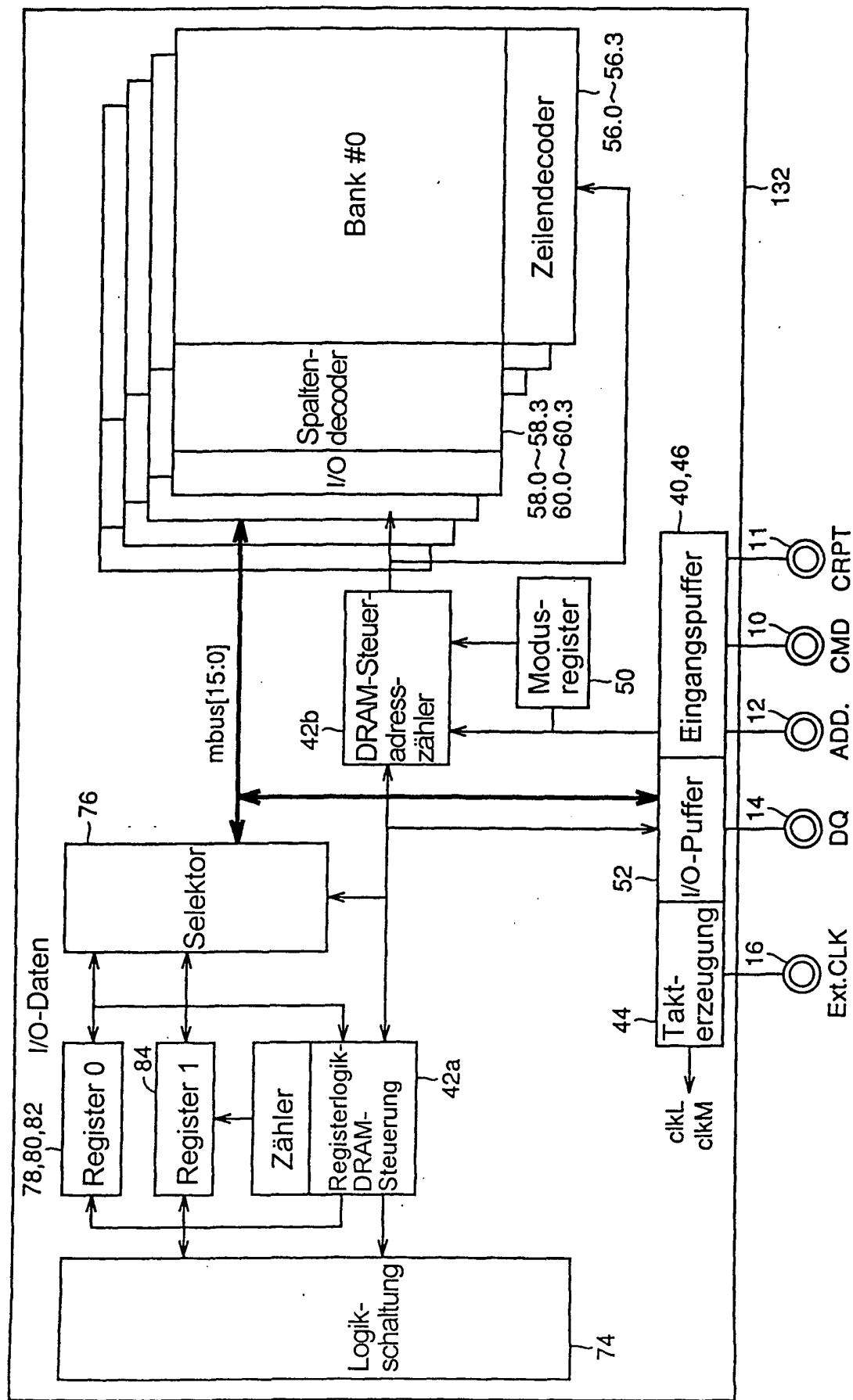

[0064] **Fig. 45** ist ein schematisches Bild zum Beschreiben einer Konfiguration eines integrierten Logik-DRAM **130** eines vierten Beispiele der vorliegenden Erfindung;

[0065] **Fig. 46** ist ein konzeptuelles Blockschaltbild zum Beschreiben einer Register-Registertätigkeit;

[0066] **Fig. 47** ist ein Flußdiagramm zum Beschreiben eines Betriebes des integrierten Logik-DRAM **130** auf eine detailliertere Weise;

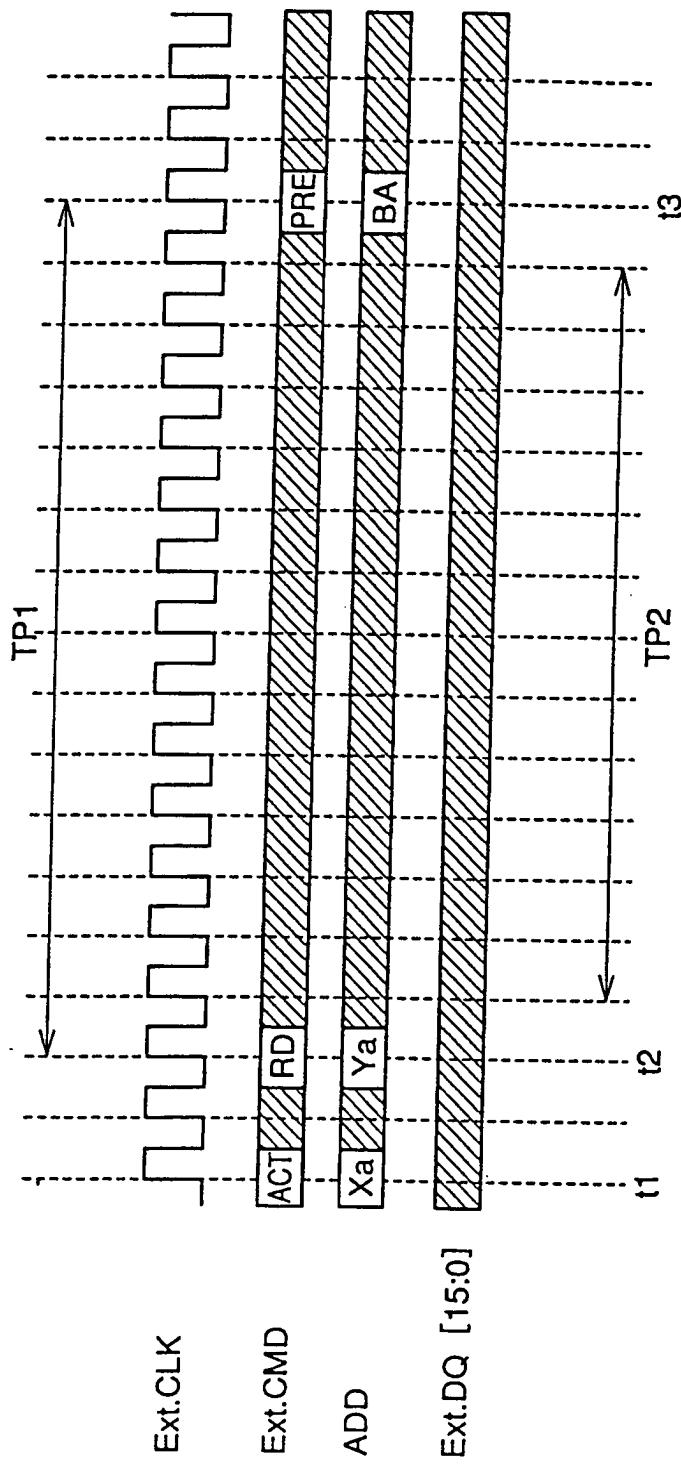

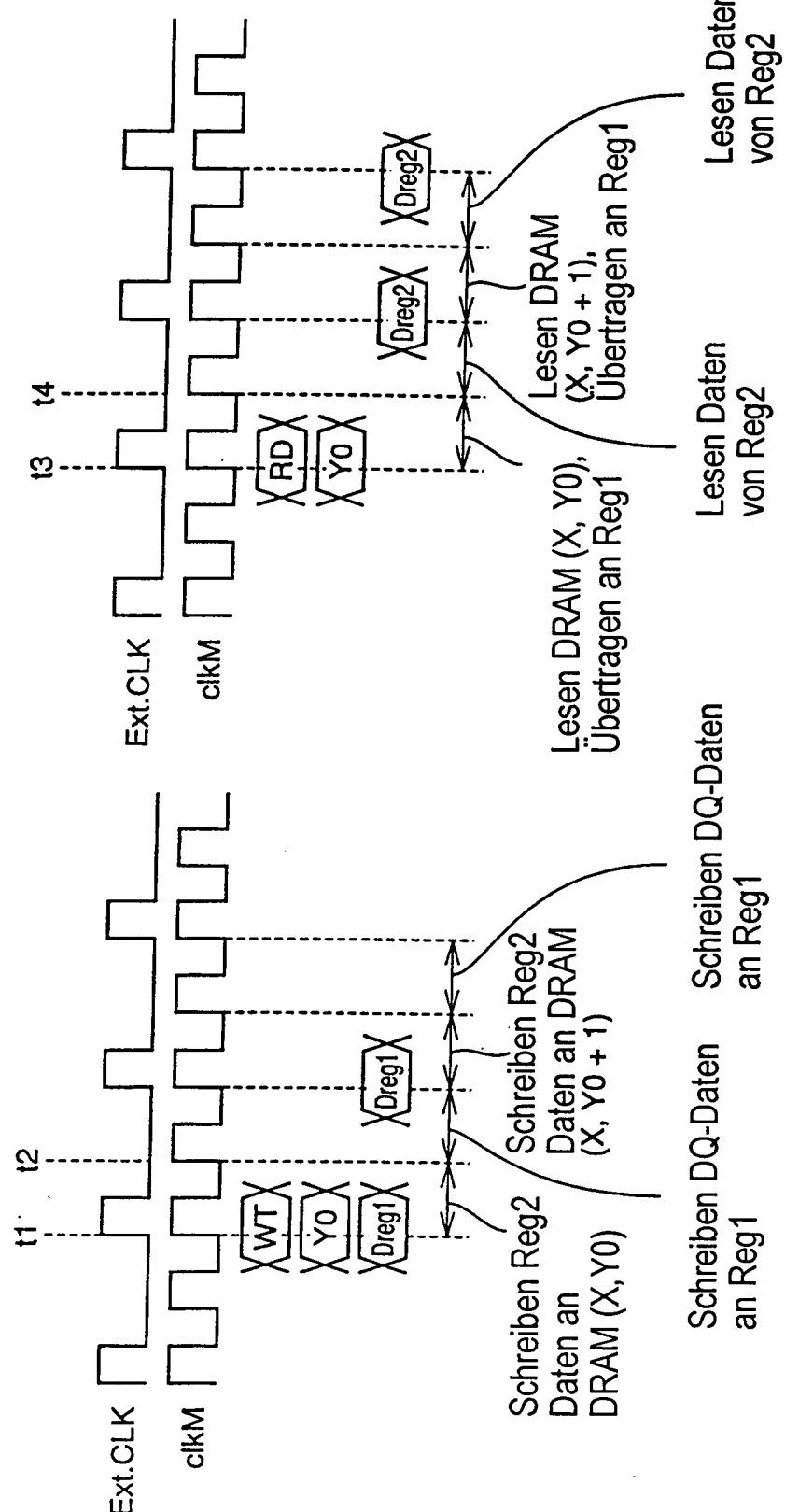

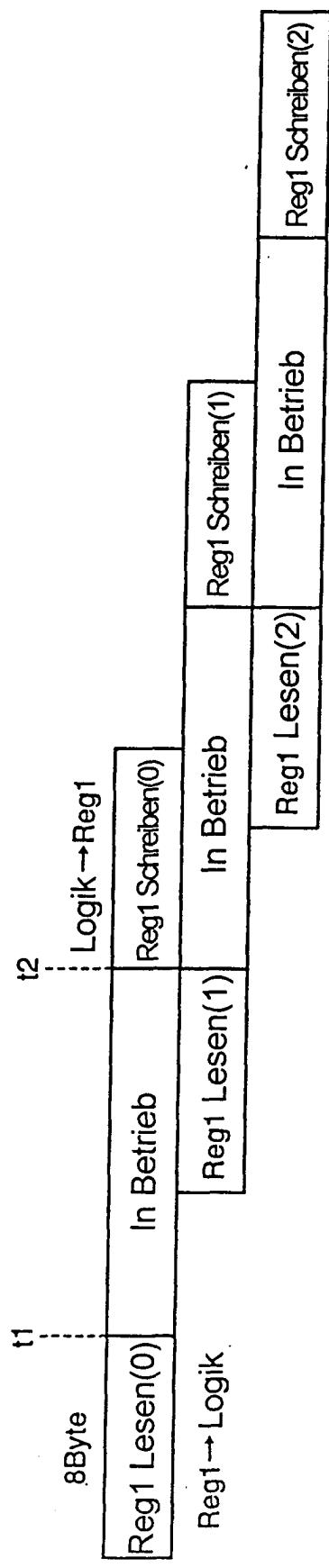

[0067] **Fig. 48** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes des integrierten Logik-DRAM **130** in dem Prozeßfluß, wie in **Fig. 47** gezeigt ist;

[0068] **Fig. 49** ist ein konzeptuelles Blockschaltbild zum Beschreiben eines anderen Betriebes des in **Fig. 45** gezeigten integrierten Logik-DRAM **130**;

[0069] **Fig. 50** ist eine konzeptuelle Zeichnung zum Beschreiben eines Konzeptes von Betrieben des ersten und des zweiten Registers **84** und **86** und Zählern **85** und **87**;

[0070] **Fig. 51** ist ein Flußdiagramm zum Beschreiben von mehr Einzelheiten des unter Bezugnahme auf **Fig. 49** beschriebenen Betriebes;

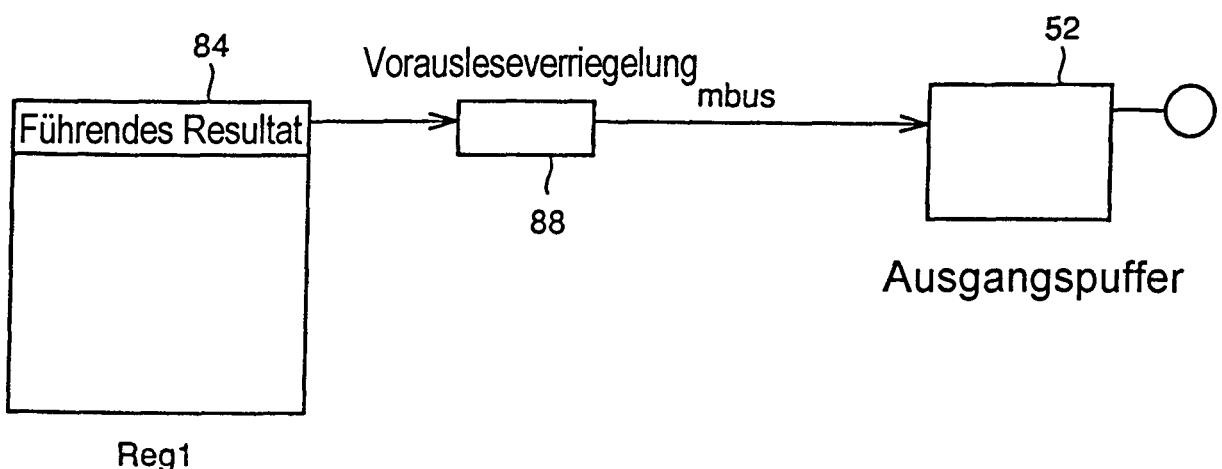

[0071] **Fig. 52** ist ein Blockschaltbild, das einen Zustand eines externen Busses darstellt;

[0072] **Fig. 53** ist ein Zeitablaufdiagramm, das ei-

nen Betrieb eines Vollseitenmodus in einem Register-DRAM-Übertragungsmodus darstellt;

[0073] **Fig. 54** ist eine Zeichnung, die eine Zuordnung von Adressen zu einem Register 0, einem ersten Datenregister **84** und einem zweiten Datenregister **86** darstellt;

[0074] **Fig. 55** ist eine Zeichnung, die ein Beispiel von den in den Registern gehaltenen Daten darstellt;

[0075] **Fig. 56** ist ein schematisches Blockschaltbild zum Beschreiben eines DRAM-Registerbetriebsmodus;

[0076] **Fig. 57** ist ein Flußdiagramm zum Beschreiben von mehr Einzelheiten des in **Fig. 56** beschriebenen Betriebes;

[0077] **Fig. 58** ist eine Zeichnung, die ein Konzept eines Datenübertragungszeitpunktes zum Verbessern einer Übertragungseffektivität darstellt, wenn ein Betrieb in dem Register-DRAM-Übertragungsmodus durchgeführt wird;

[0078] **Fig. 59** ist ein Zeitablaufdiagramm, das einen Betrieb zum Verbessern einer Effektivität von Datenübertragung beschreibt;

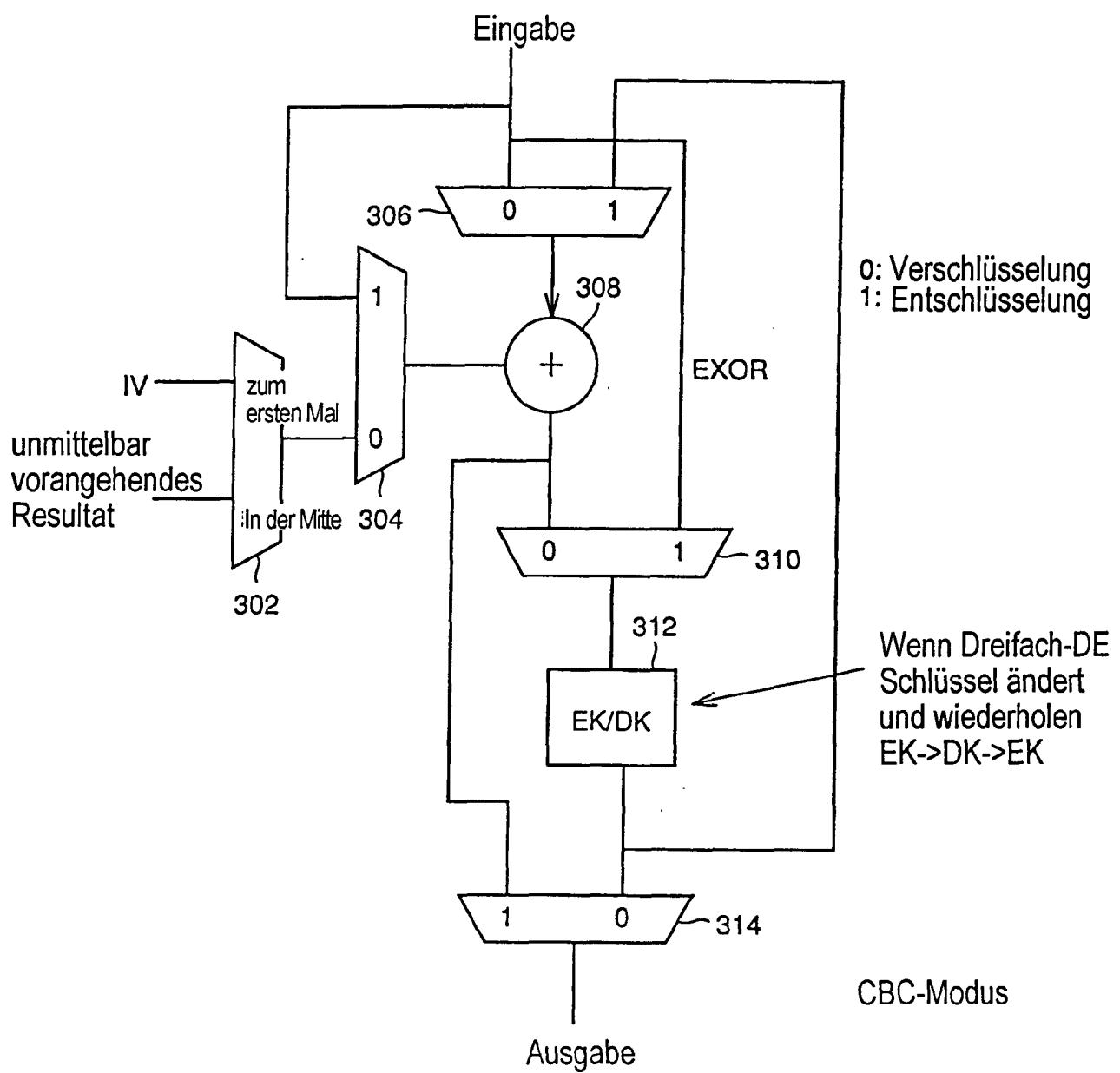

[0079] **Fig. 60** ist ein Blockschaltbild, das ein Beispiel einer Schaltungskonfiguration zum Durchführen von Verschlüsselung oder Entschlüsselung im CBC-Modus darstellt;

[0080] **Fig. 61** ist ein schematisches Blockschaltbild zum Beschreiben einer Konfiguration eines integrierten Logik-DRAM **132** eines fünften Beispieles der vorliegenden Erfindung;

[0081] **Fig. 62** ist ein konzeptuelles Blockschaltbild zum Beschreiben einer Register-Registertätigkeit des integrierten Logik-DRAM **132** des vierten Beispiels;

[0082] **Fig. 63** ist ein Flußdiagramm zum Beschreiben eines Betriebes des integrierten Logik-DRAM **132** auf eine detailliertere Weise;

[0083] **Fig. 64** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes des integrierten Logik-DRAM **132** in dem Prozeßfluß, wie in **Fig. 61** gezeigt ist;

[0084] **Fig. 65** ist ein konzeptuelles Blockschaltbild zum Beschreiben des Register-DRAM-Betriebes des in **Fig. 61** gezeigten integrierten Logik-DRAM **132**;

[0085] **Fig. 66** ist ein Flußdiagramm zum Beschreiben von mehr Einzelheiten des in **Fig. 65** beschriebenen Betriebes;

[0086] **Fig. 67** ist eine konzeptuelle Zeichnung zum Beschreiben von Datenübertragungsverarbeitung zwischen dem Register **84** und einer Logikschaltung **74** in einer ersten Modifikation des fünften Beispiels;

[0087] **Fig. 68** ist ein konzeptuelles Blockschaltbild zum Beschreiben einer Route von dem Register **84** zu einem Datenausgang in einer zweiten Modifikation des fünften Beispiels;

[0088] **Fig. 69** ist ein konzeptuelles Blockschaltbild zum Beschreiben des DRAM-Registerbetriebsmodus;

[0089] **Fig. 70** ist ein Flußdiagramm zum Beschreiben von mehr Einzelheiten des in **Fig. 69** beschriebe-

nen Betriebes;

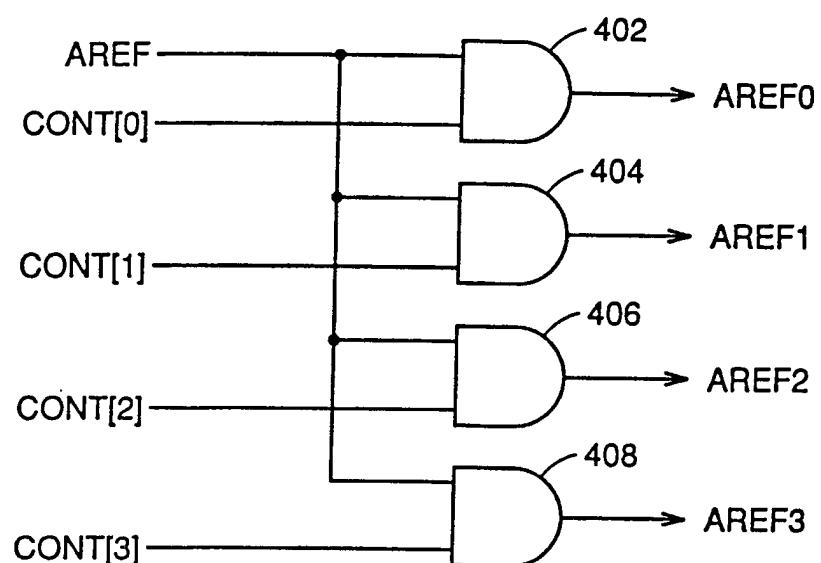

[0090] **Fig. 71** ist ein Blockschaltbild, das eine Schaltungskonfiguration darstellt, die einen internen Befehl zum Selbstauffrischen erzeugt;

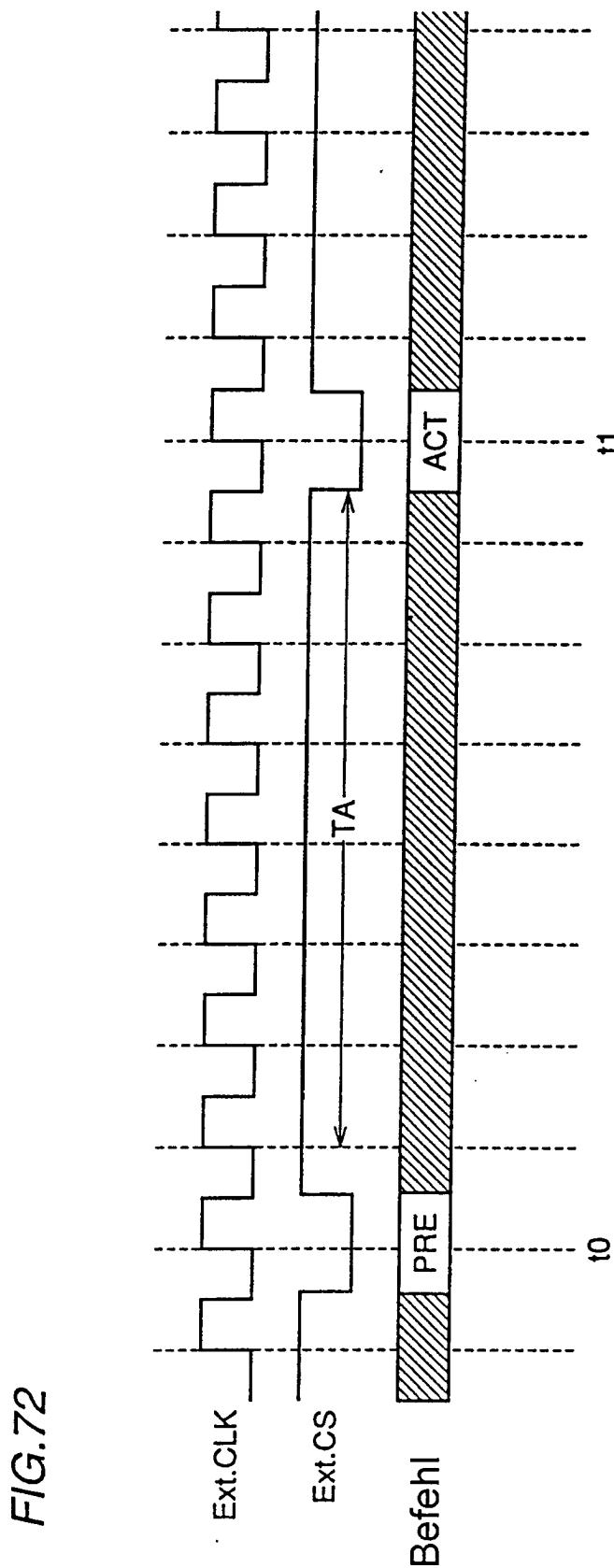

[0091] **Fig. 72** ist ein Zeitablaufdiagramm, das ein Verfahren zum Eintritt in einen Niedrigleistungsmodus darstellt;

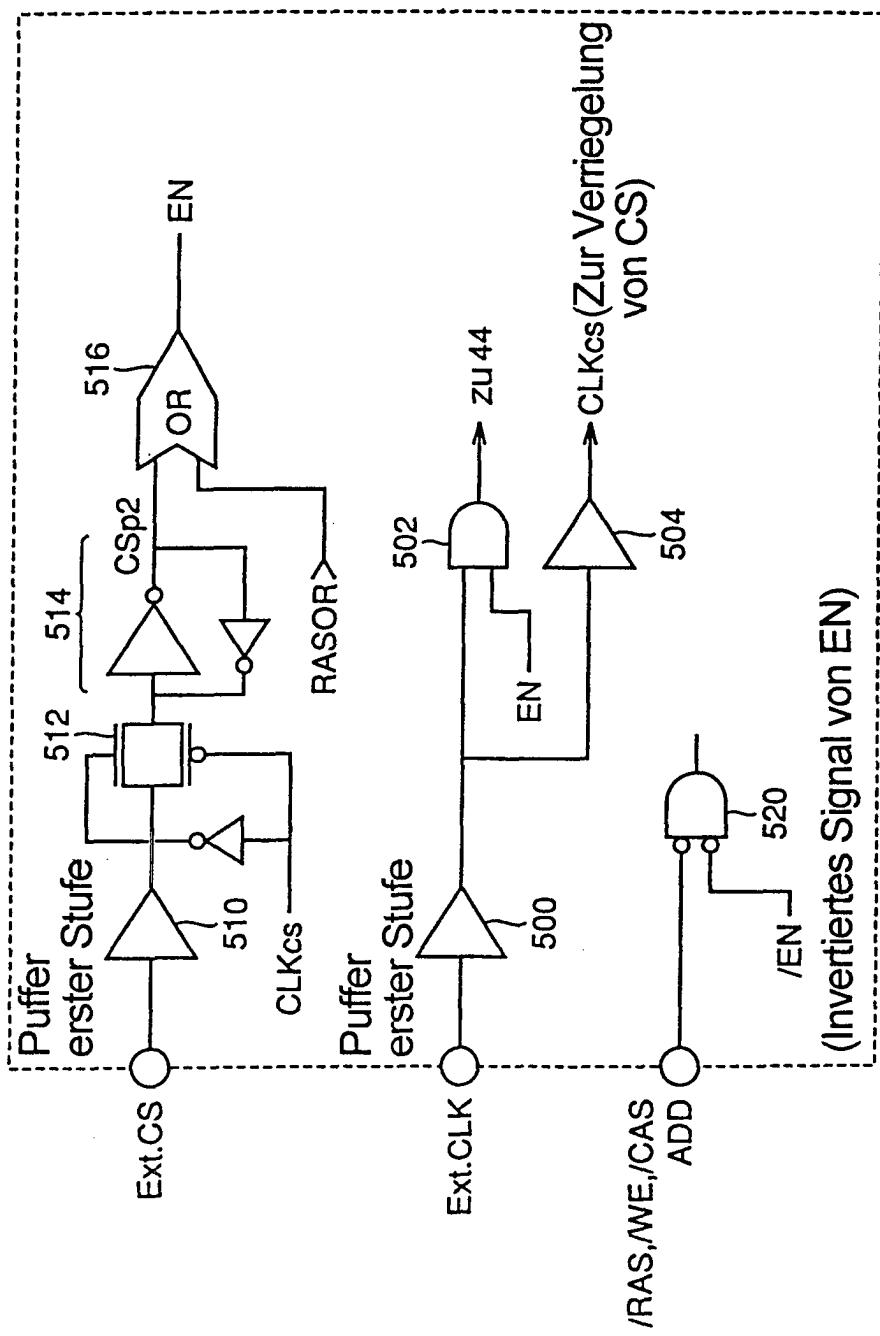

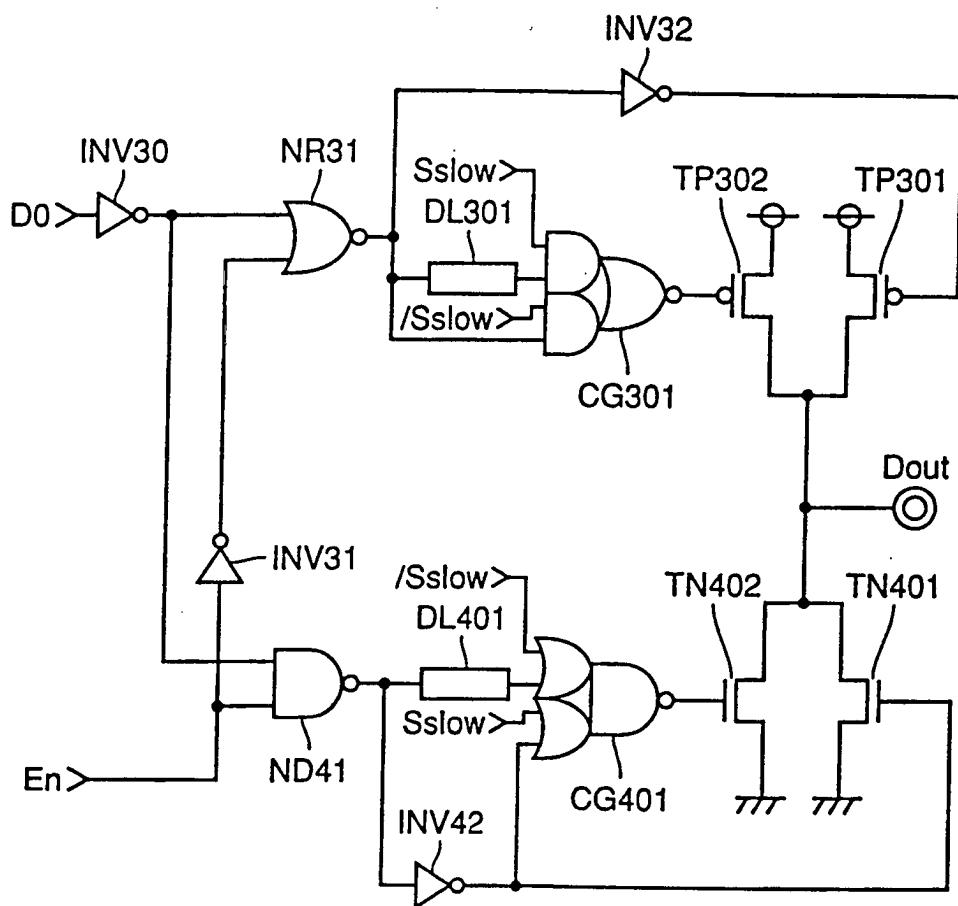

[0092] **Fig. 73** ist ein Bild, das eine Schaltungskonfiguration darstellt, die Steuerung von Eingangspuffern **40** oder **42** in dem Niedrigleistungsmodus durchführt;

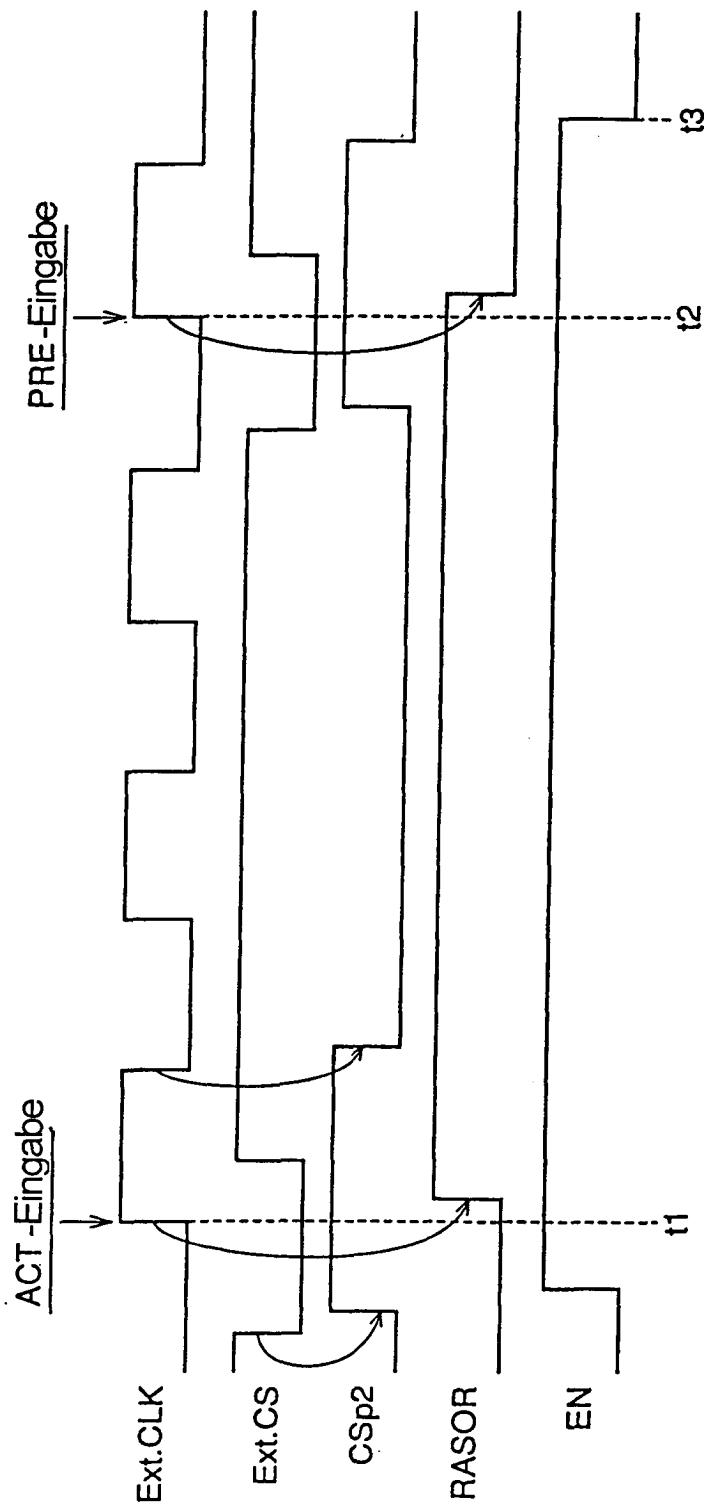

[0093] **Fig. 74** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes der in **Fig. 73** gezeigten Schaltung;

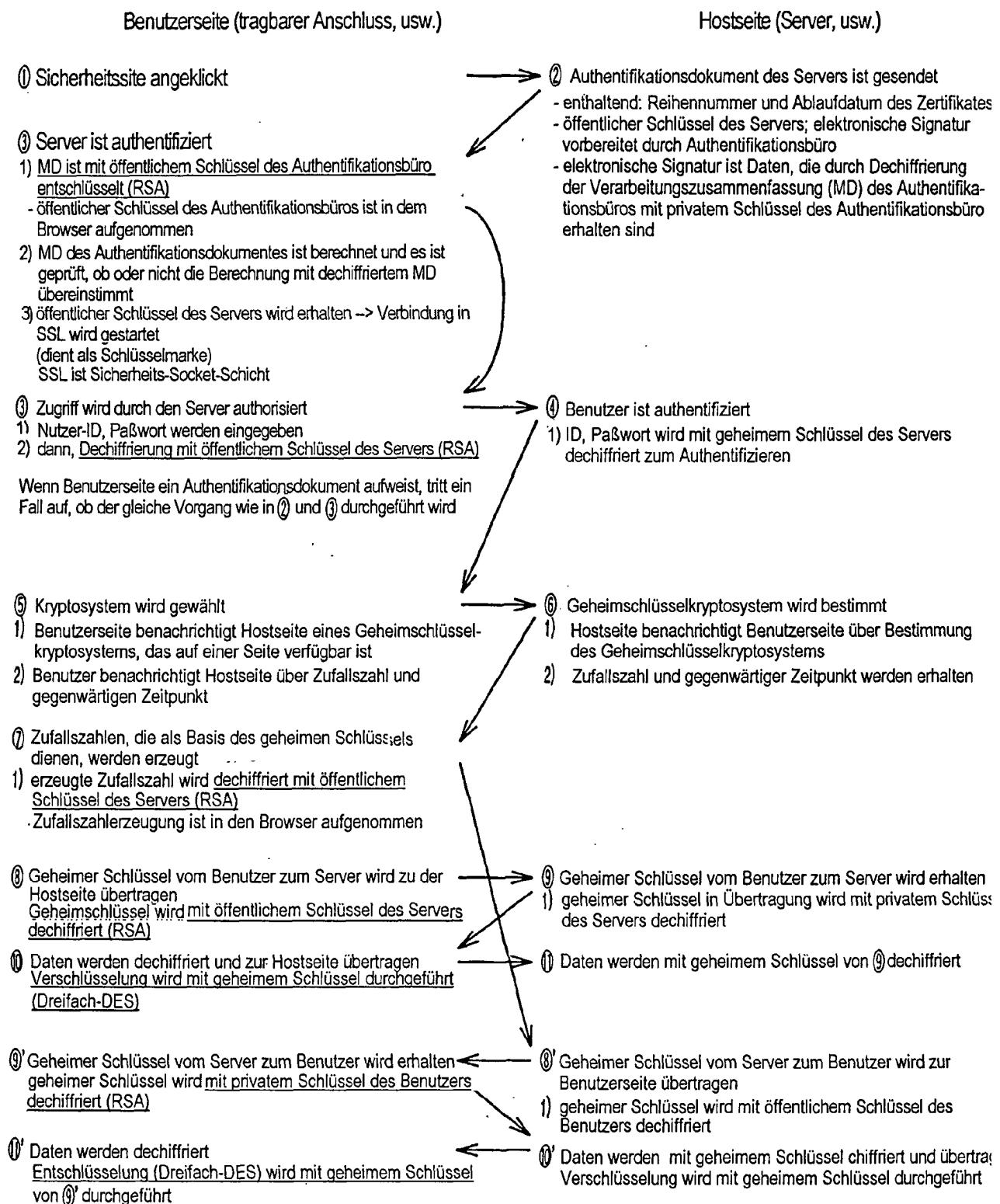

[0094] **Fig. 75** ist eine Darstellung zum einfachen Beschreiben einer Verarbeitung von Sicherheitsdatenkommunikation in dem Internet;

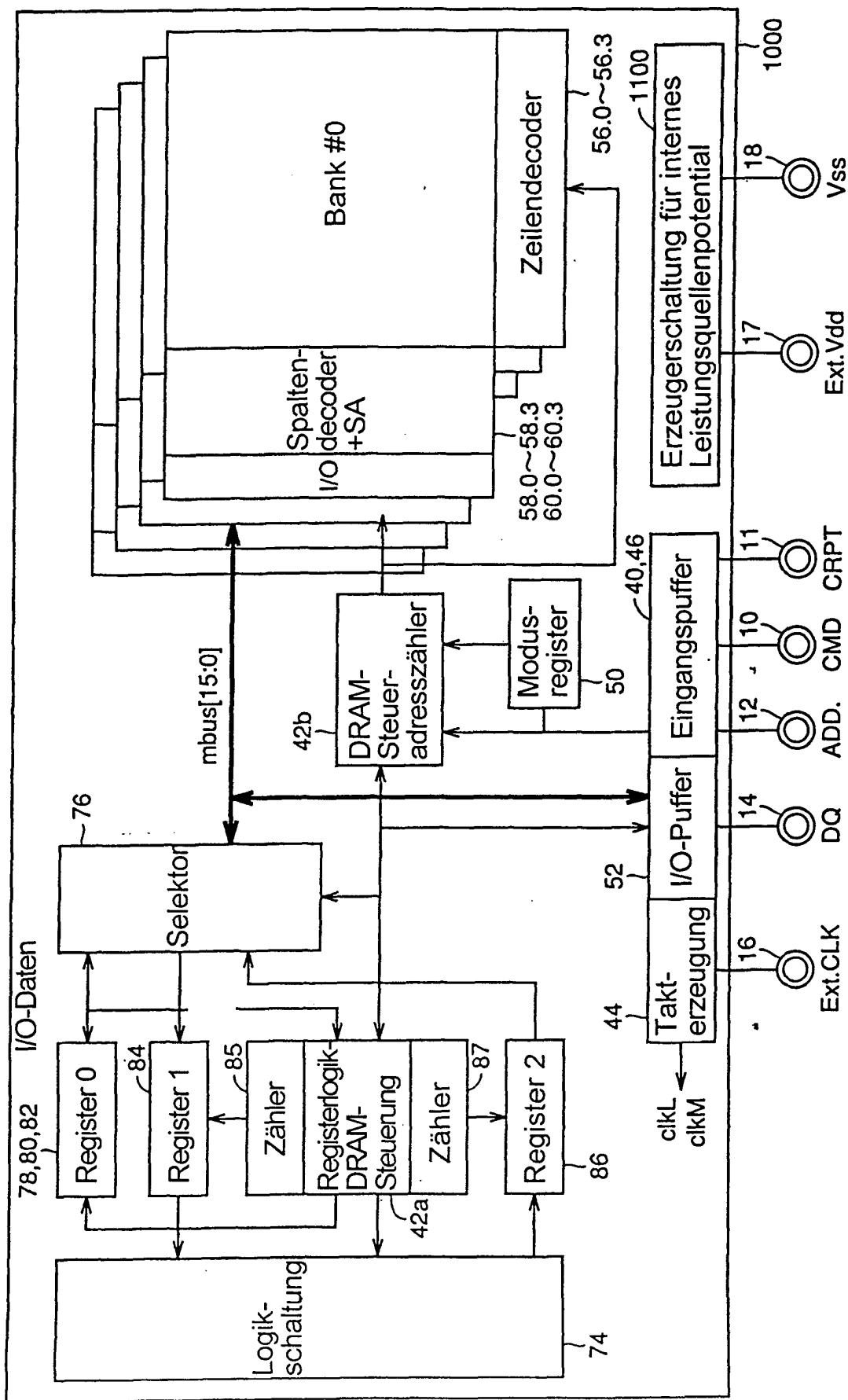

[0095] **Fig. 76** ist ein schematisches Blockschaltbild zum Beschreiben eines integrierten Logik-DRAM, der sich auf ein neuntes Beispiel der vorliegenden Erfindung bezieht;

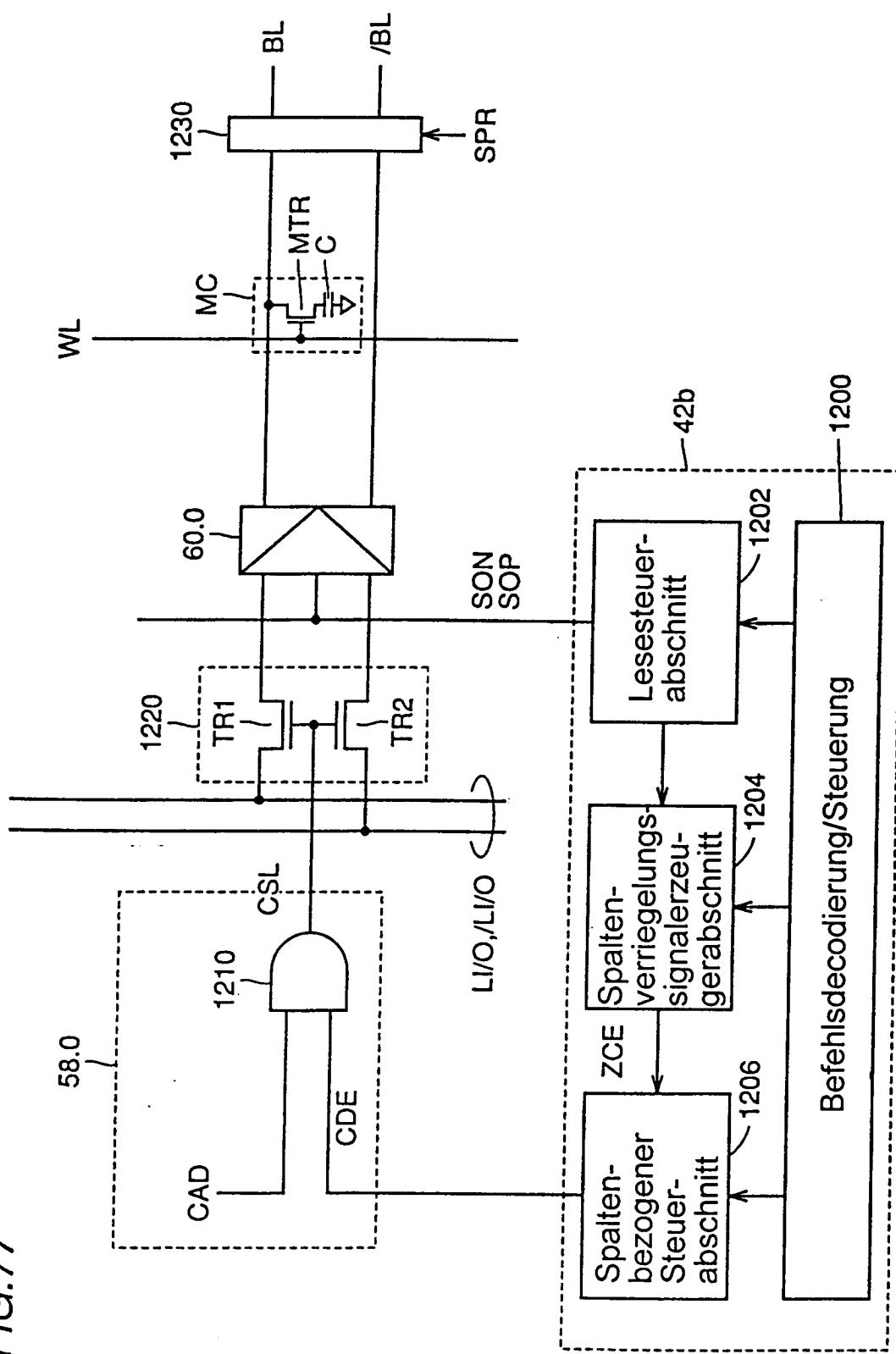

[0096] **Fig. 77** ist ein schematisches Blockschaltbild, das eine Konfiguration eines DRAM-Steuerabschnittes **42b** und eines Spaltendecoders **58.0** eines Leseverstärkers **60.0** und eines I/O-Abschnittes, der für eine Bank #0 vorgesehen ist, die extrahiert werden, darstellt;

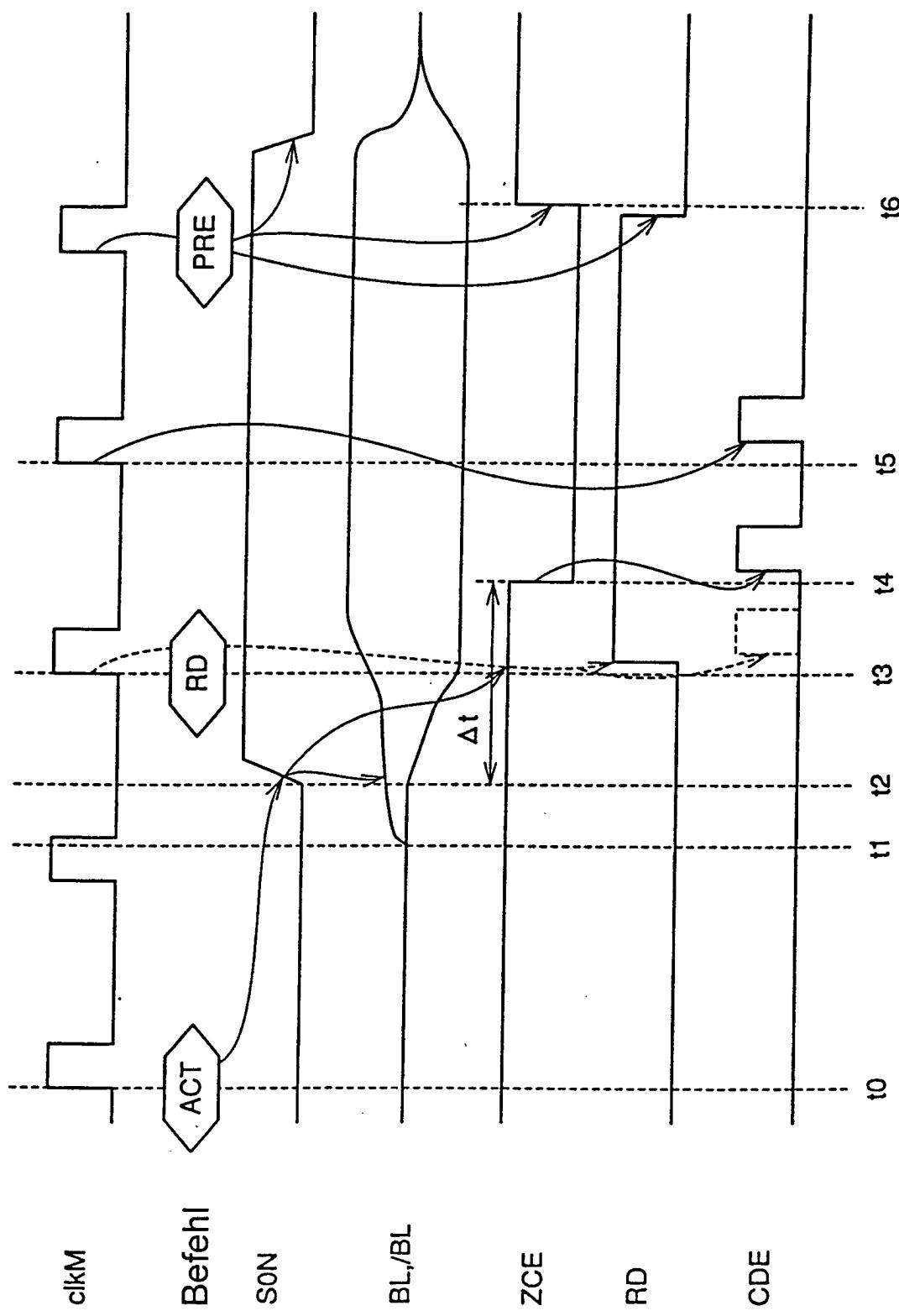

[0097] **Fig. 78** ist ein Zeitablaufdiagramm zum Beschreiben von Betrieben, bei denen Daten auf ein Bitleitungs paar und weiter auf ein I/O-Leitungs paar LI/O und /LI/O ausgelesen werden;

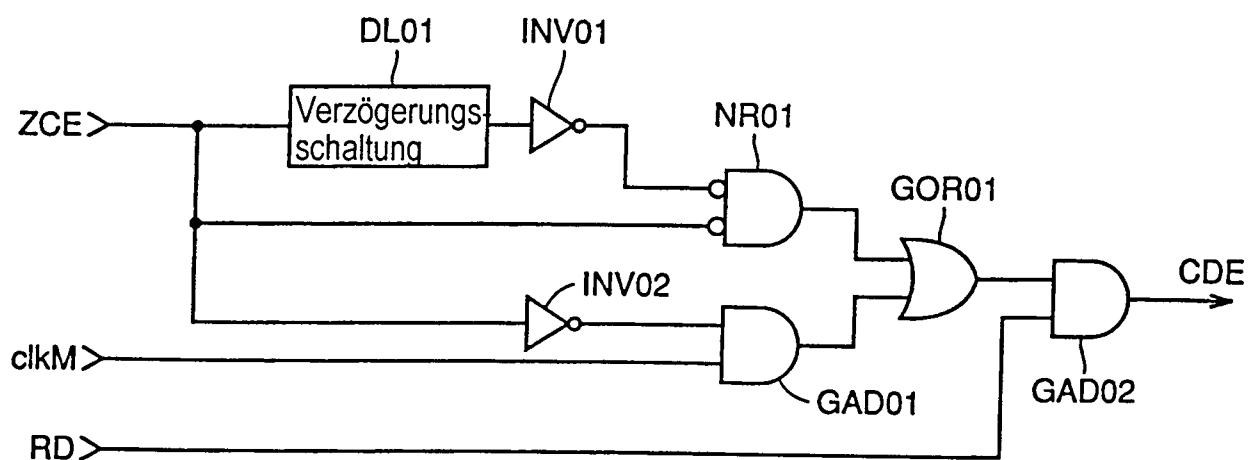

[0098] **Fig. 79** ist ein Bild, das eine Konfiguration eines spaltenbezogenen Steuerabschnittes **1206** darstellt;

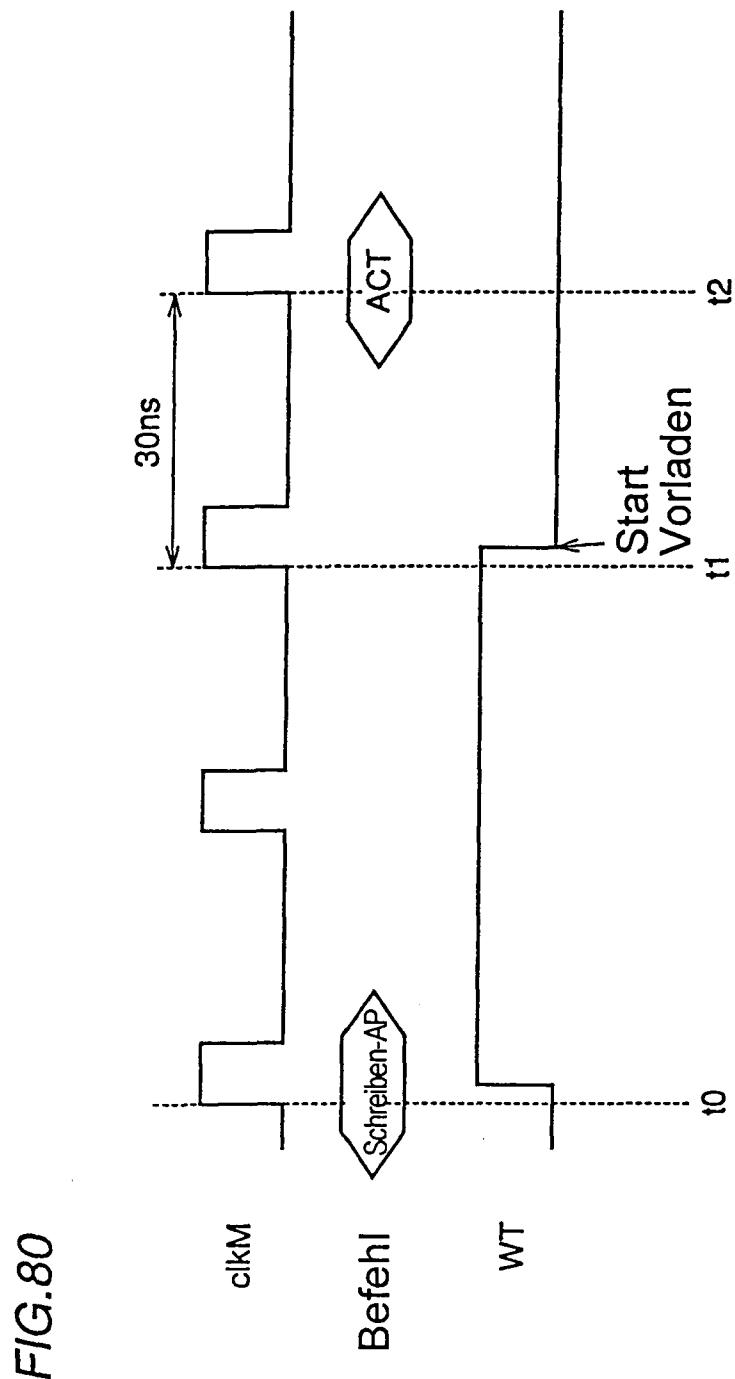

[0099] **Fig. 80** ist ein Zeitablaufdiagramm, das Zeitpunkte darstellt, zu denen ein Betrieb des Schreibens ohne Selbstvorladen des Standes der Technik durchgeführt wird;

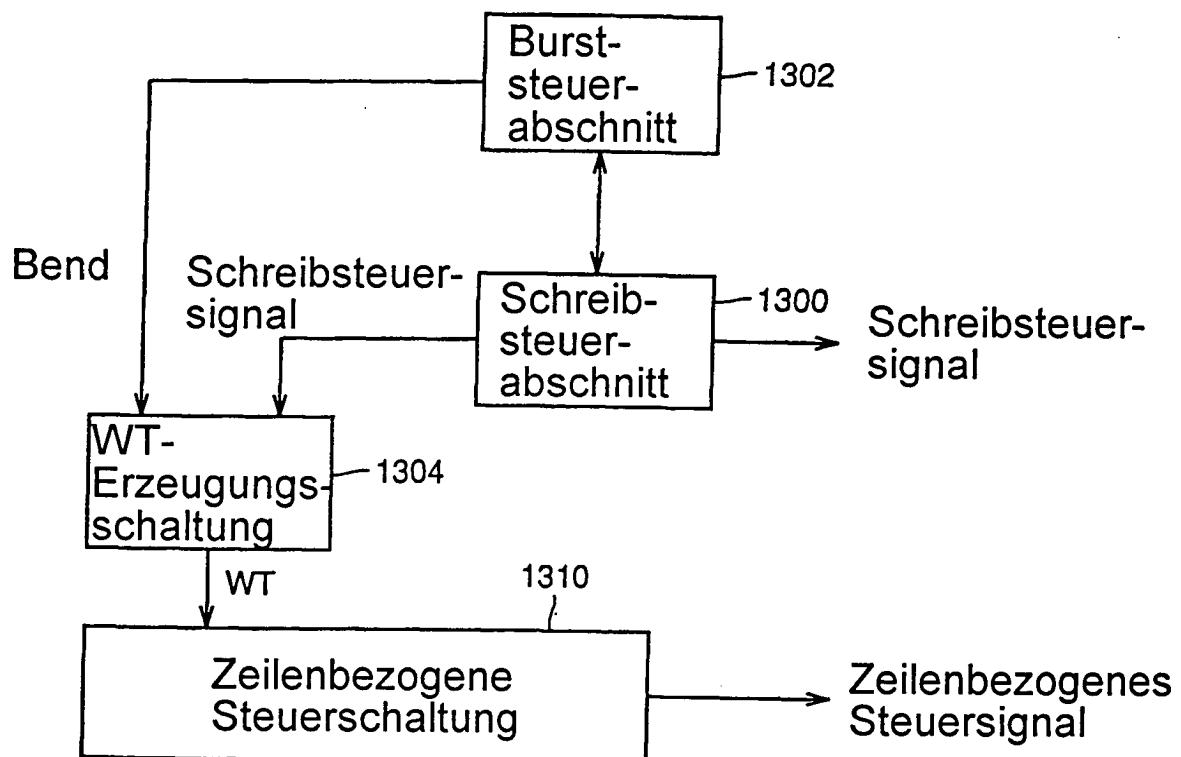

[0100] **Fig. 81** ist ein schematisches Blockschaltbild, das eine Konfiguration zum Steuern einer Schreibtätigkeit darstellt, die extrahiert ist;

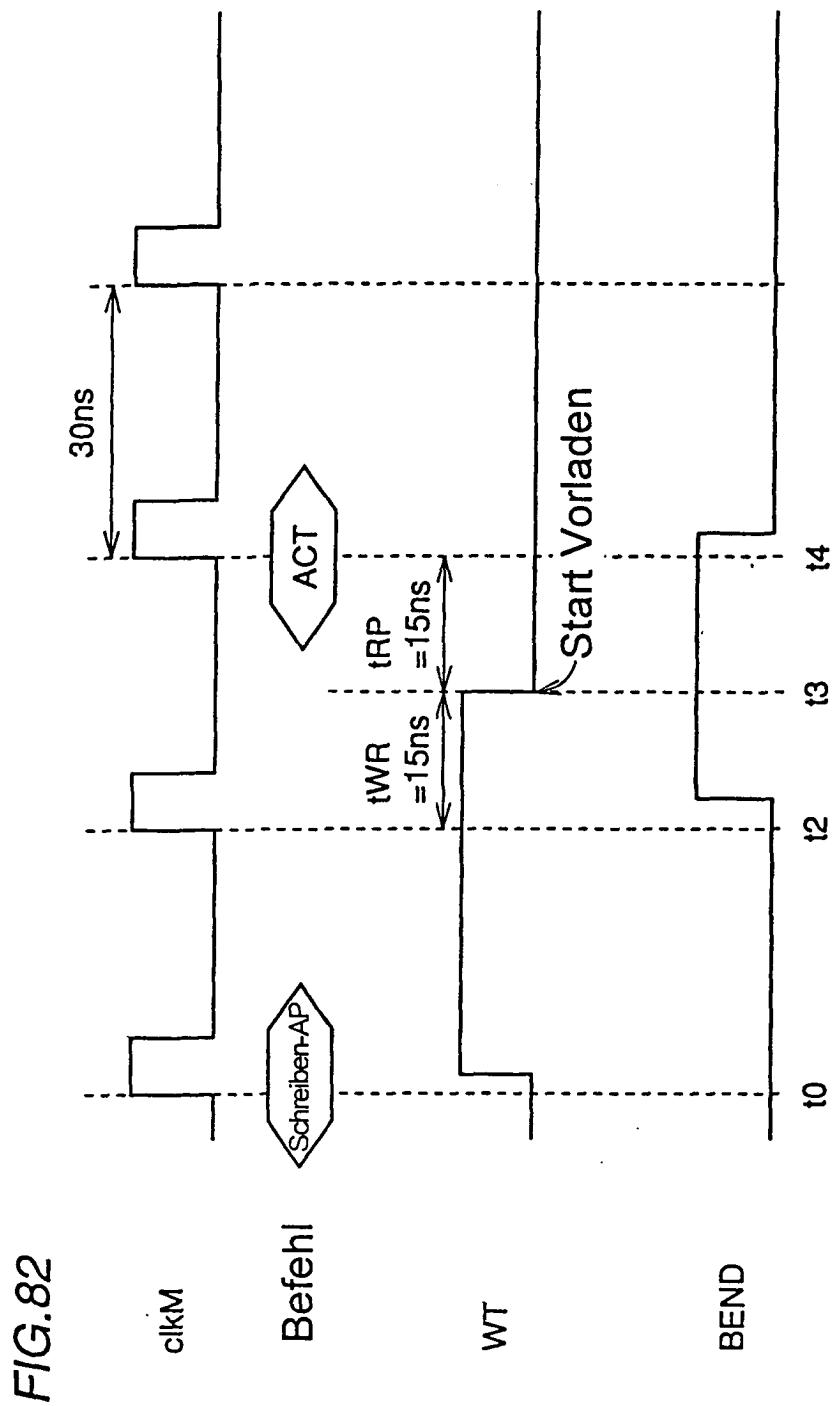

[0101] **Fig. 82** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes einer in **Fig. 81** gezeigten schreibbezogenen Steuerschaltung;

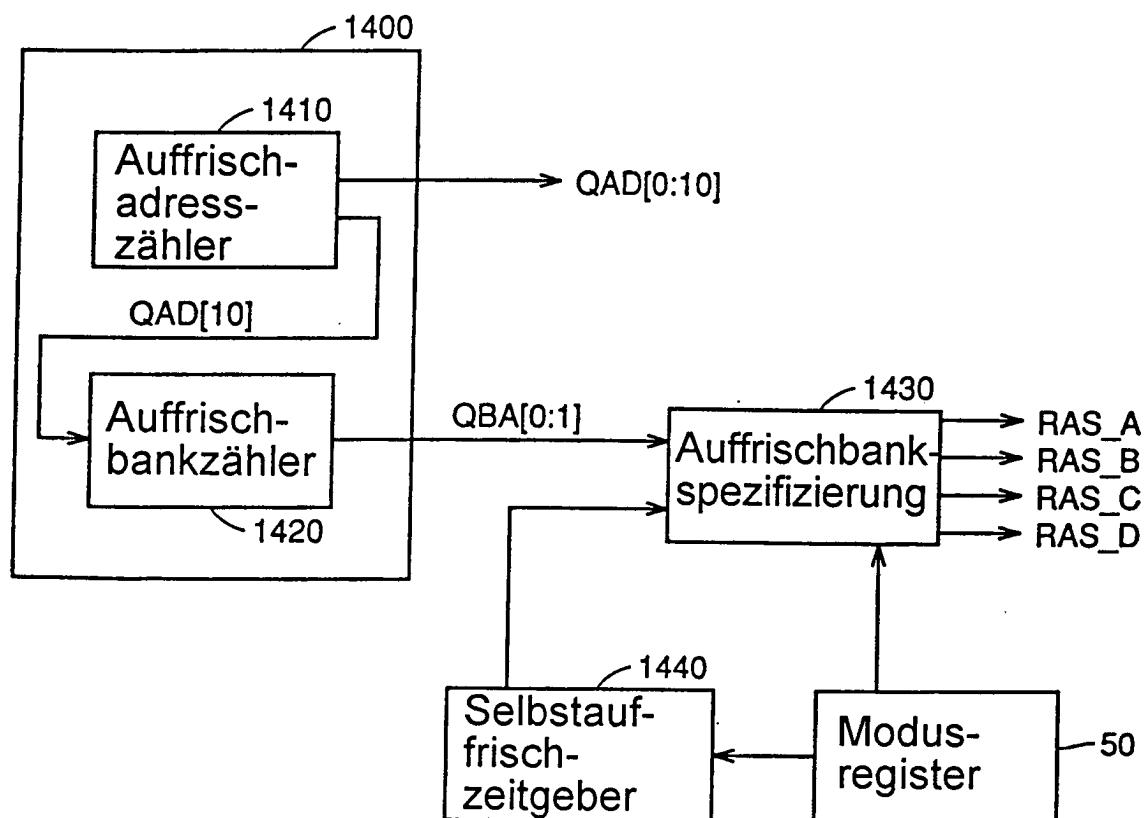

[0102] **Fig. 83** ist ein schematisches Blockschaltbild zum Beschreiben einer Konfiguration, die einen Selbstauffrischbetrieb steuert zum Verhindern einer Fehlfunktion bei einem Auffrischbetrieb;

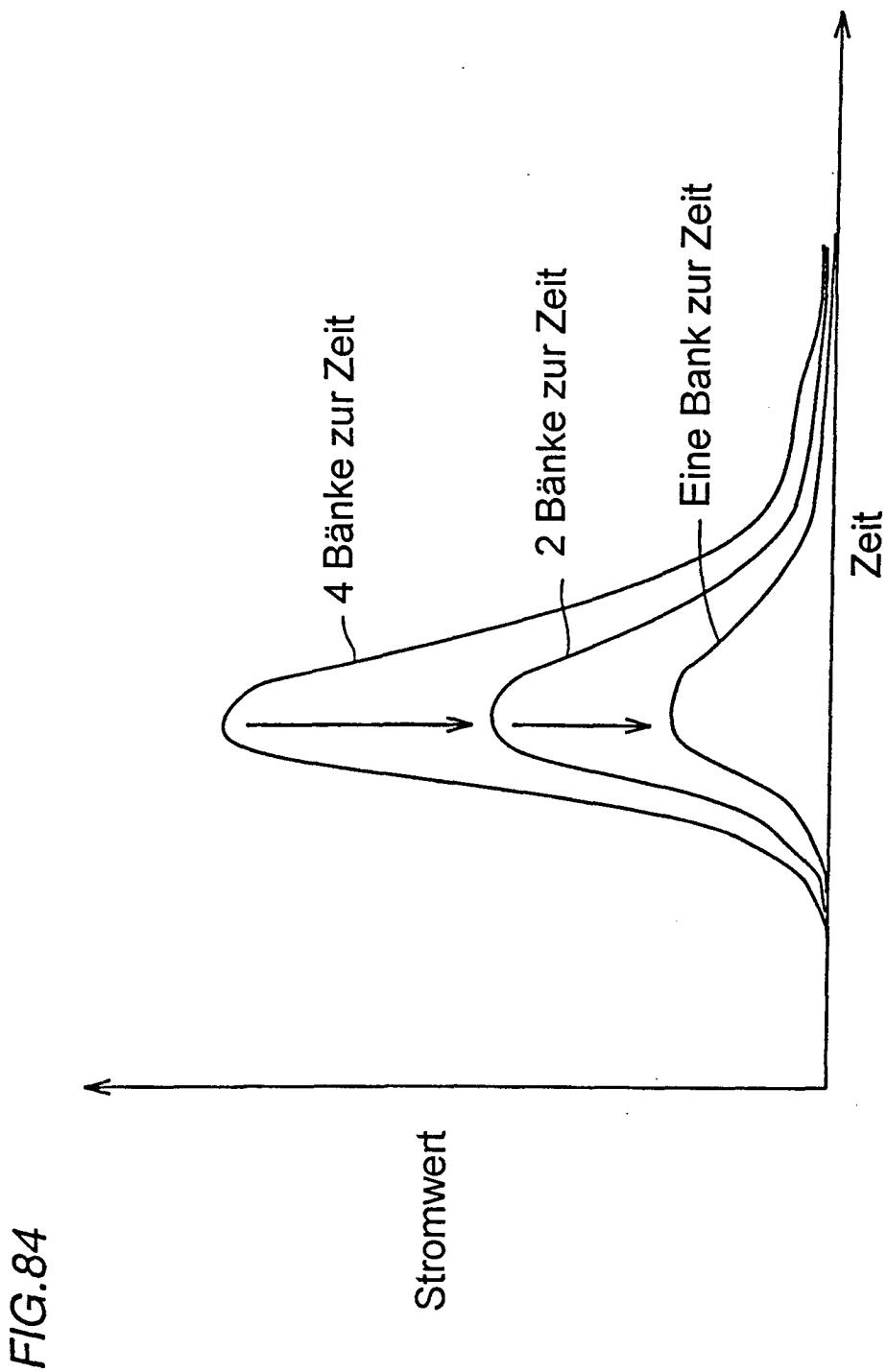

[0103] **Fig. 84** ist ein Diagramm zum Beschreiben eines Effektes des Verringerns einer Stromspitze bei dem in **Fig. 83** beschriebenen Selbstauffrischbetrieb;

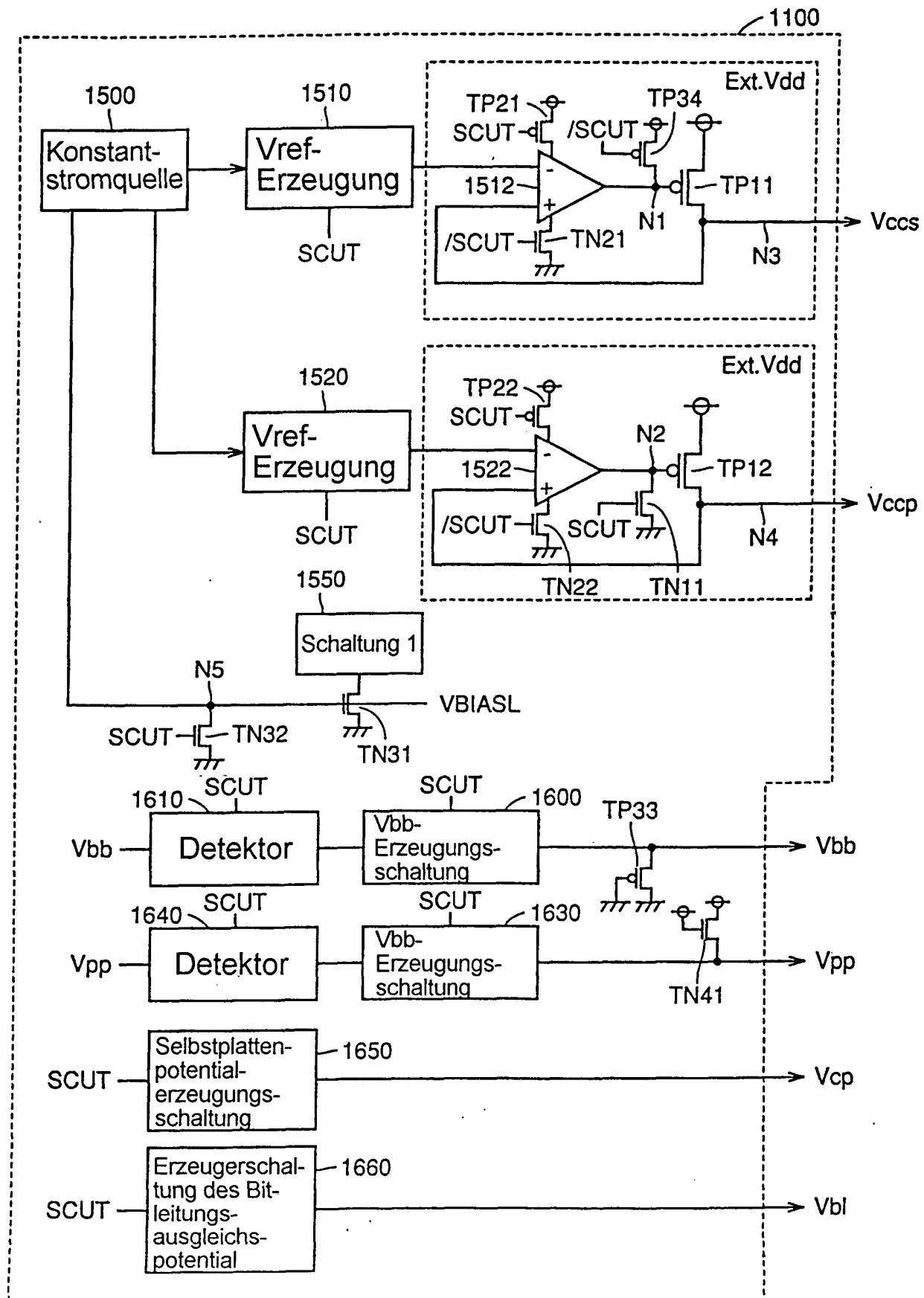

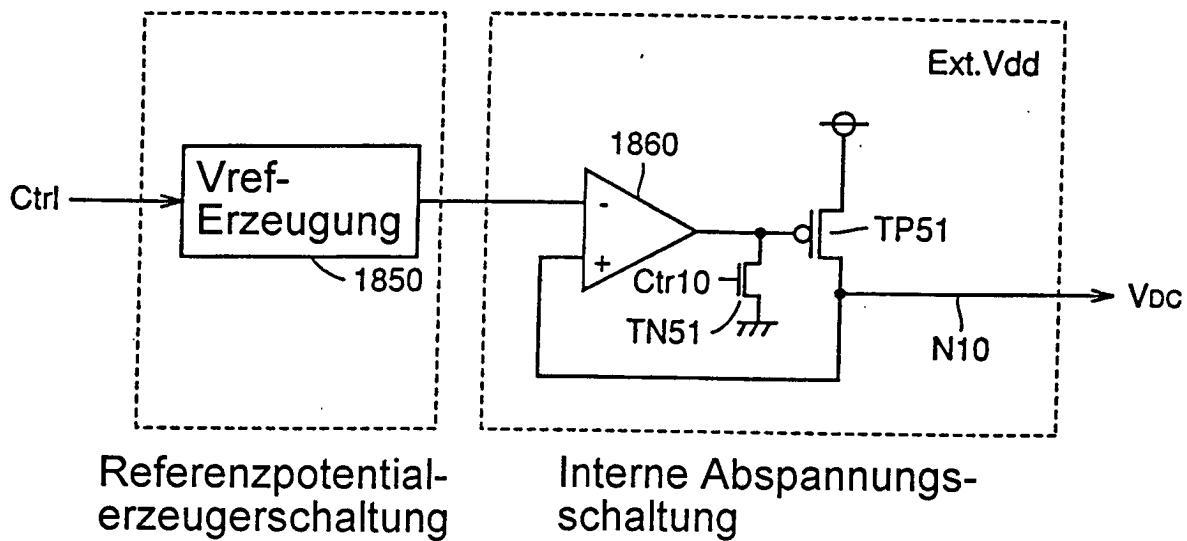

[0104] **Fig. 85** ist ein schematisches Blockschaltbild, das eine Konfiguration darstellt, die mit einer internen Leistungsquellenpotentialerzeugerschaltung **1100** verknüpft ist;

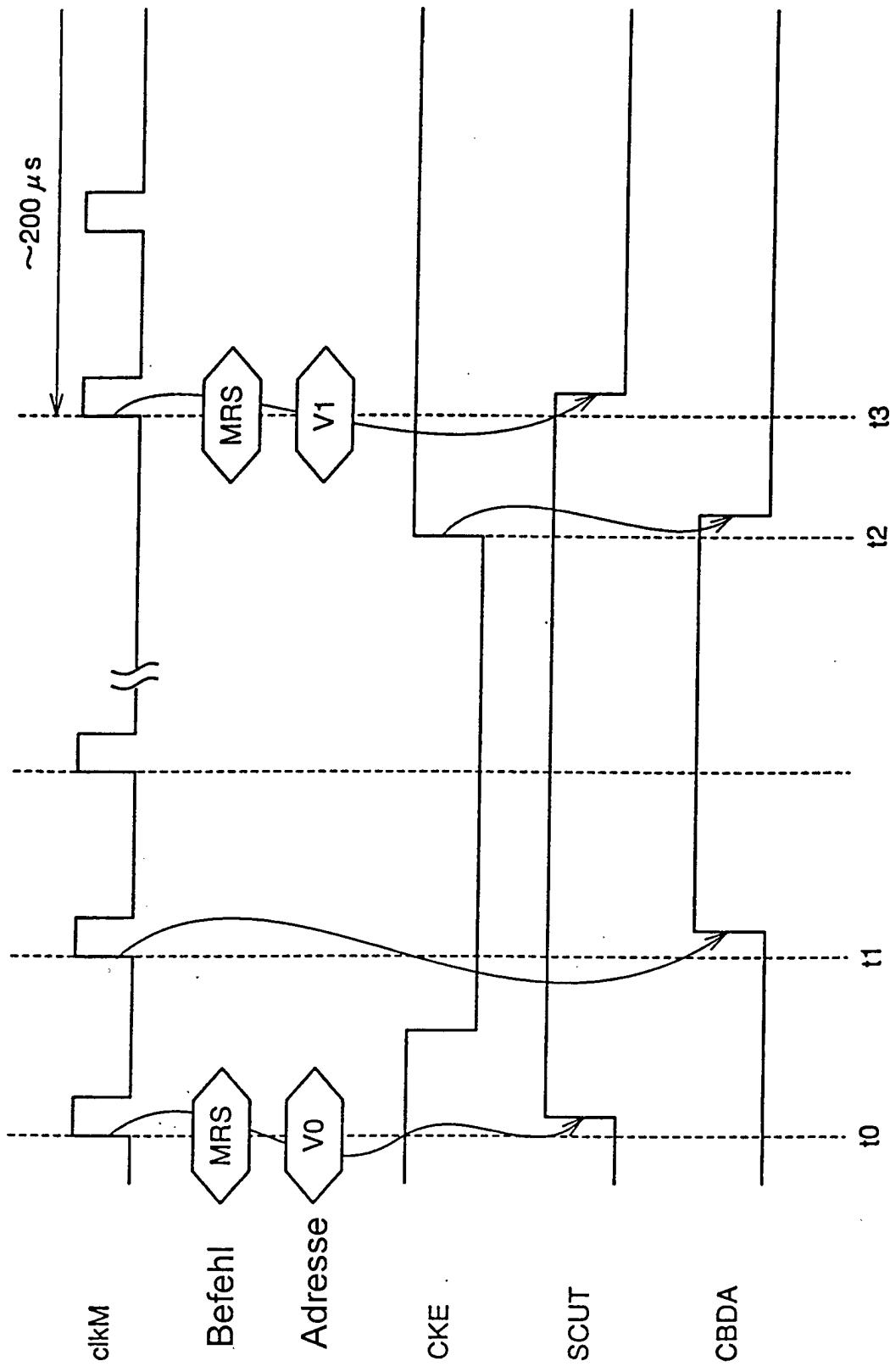

[0105] **Fig. 86** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes (Eintritt), bei dem ein Leistungsquellenabschnittmodus betreten wird, und eines Betriebes (Ausgang), bei dem der Leistungsquellenabschnittmodus verlassen wird;

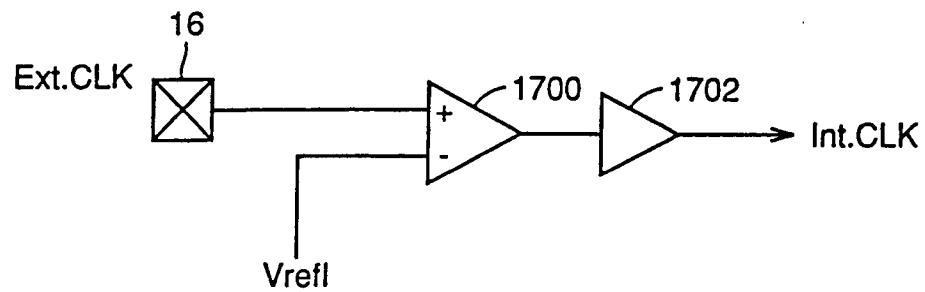

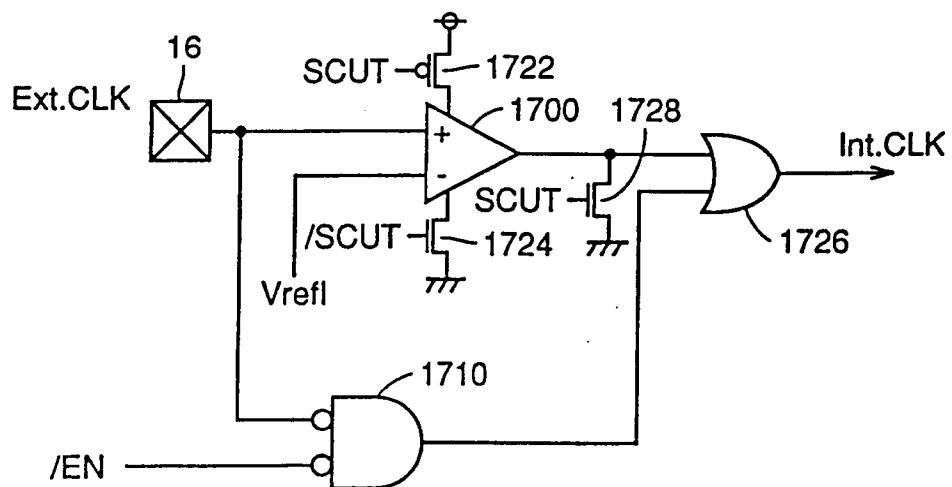

- [0106] **Fig.** 87 ist ein Schaltbild, das eine Beispielkonfiguration eines Taktpuffers **44** darstellt;

- [0107] **Fig.** 88 ist ein Schaltbild, das eine andere Schaltungskonfiguration des Taktpuffers **44** darstellt;

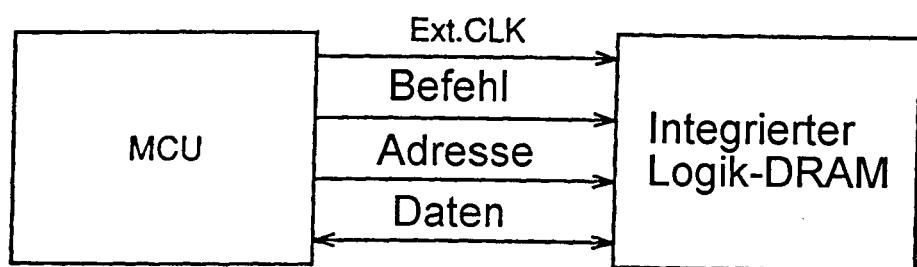

- [0108] **Fig.** 89 ist ein konzeptuelles Blockschaltbild, das eine Konfiguration eines Systems darstellt, in dem ein integrierter Logik-DRAM **1000** verwendet ist;

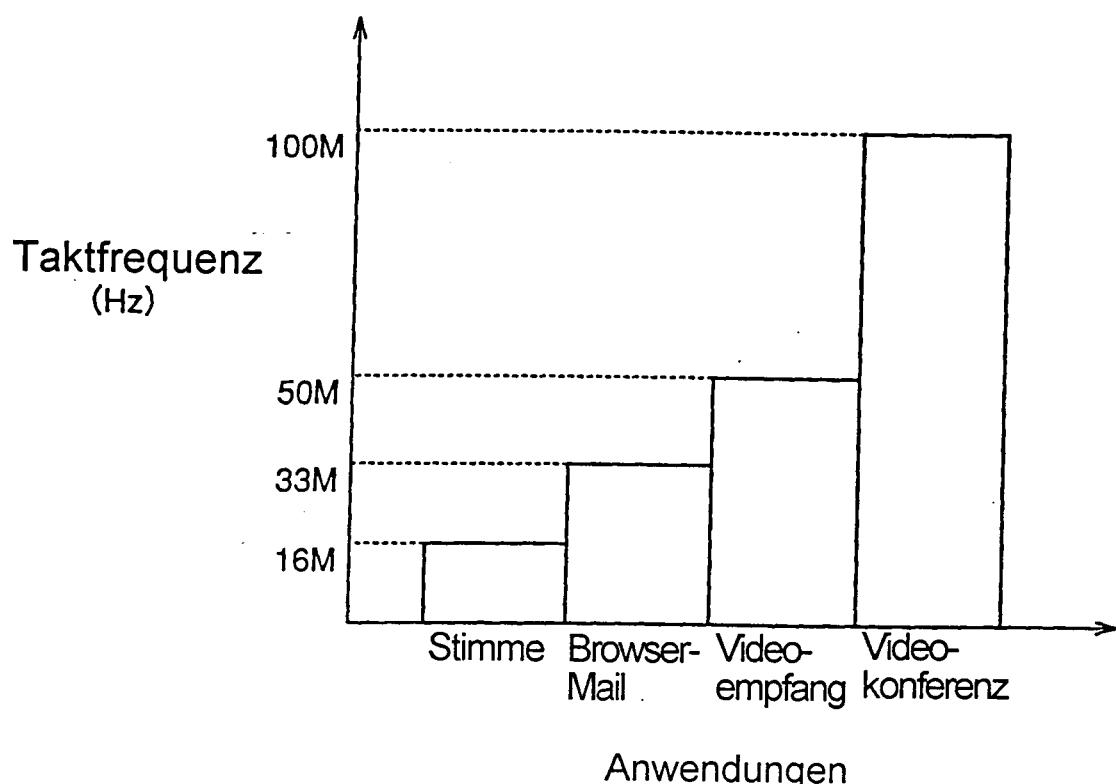

- [0109] **Fig.** 90 ist ein Diagramm, das Betriebsfrequenz eines Speichers darstellt, die gemäß Anwendungen benötigt werden;

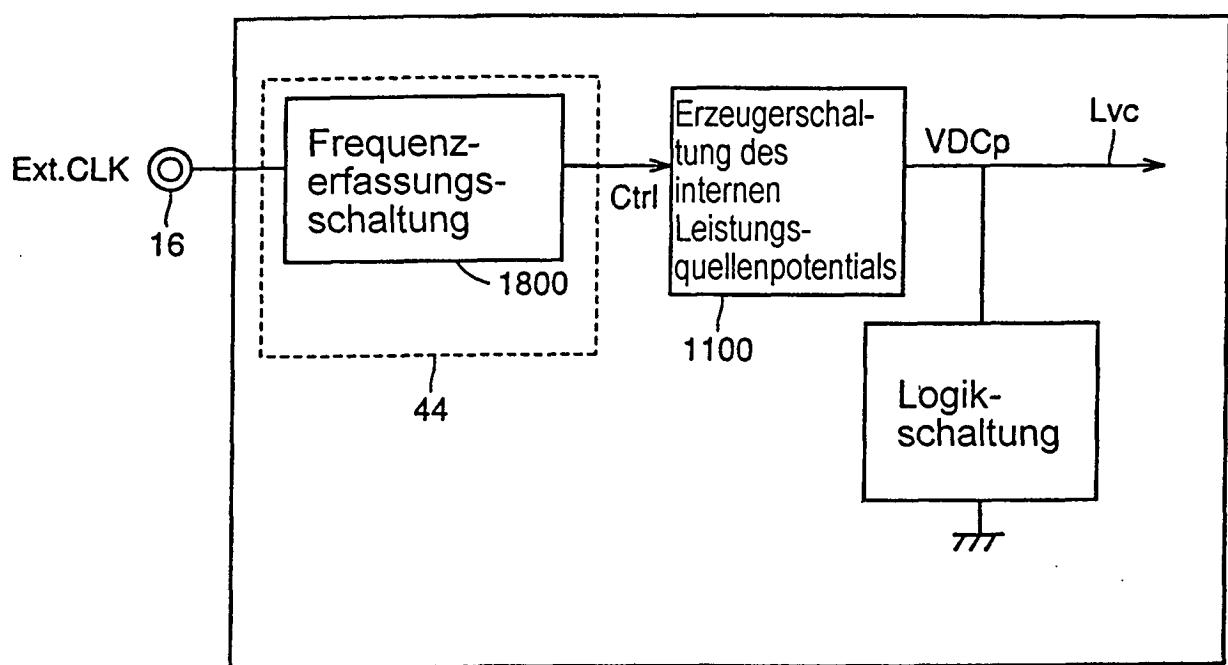

- [0110] **Fig.** 91 ist ein konzeptuelles Blockschaltbild zum Beschreiben einer Konfiguration, die eine Betriebsgeschwindigkeit eines D-Abschnittes gemäß einer Taktfrequenz ändern kann;

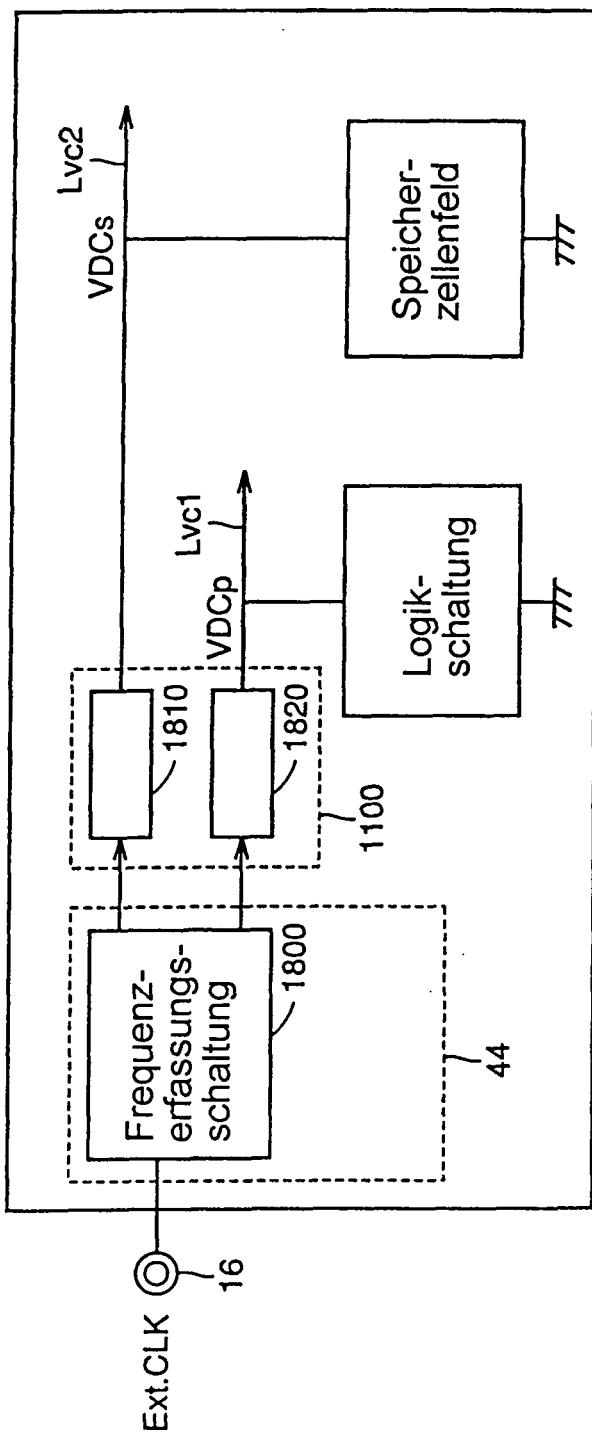

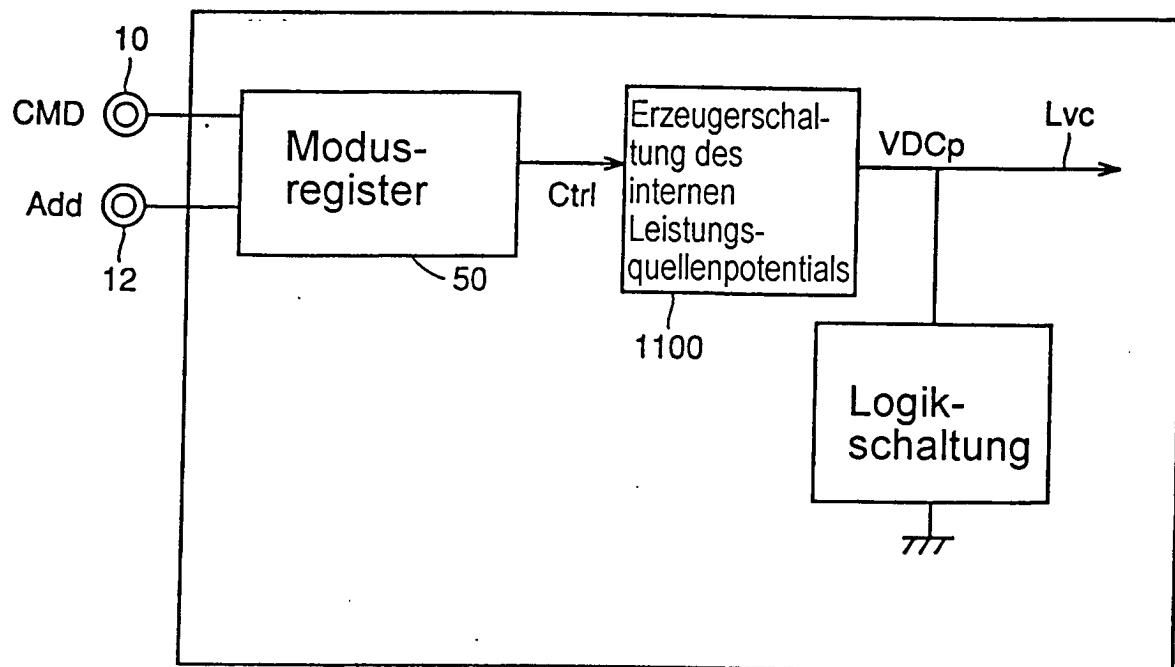

- [0111] **Fig.** 92 ist ein schematisches Blockschaltbild, das eine andere Konfiguration darstellt, die ein internes Leistungsquellenpotential gemäß einem externen Taktsignal Ext.CLK steuert;

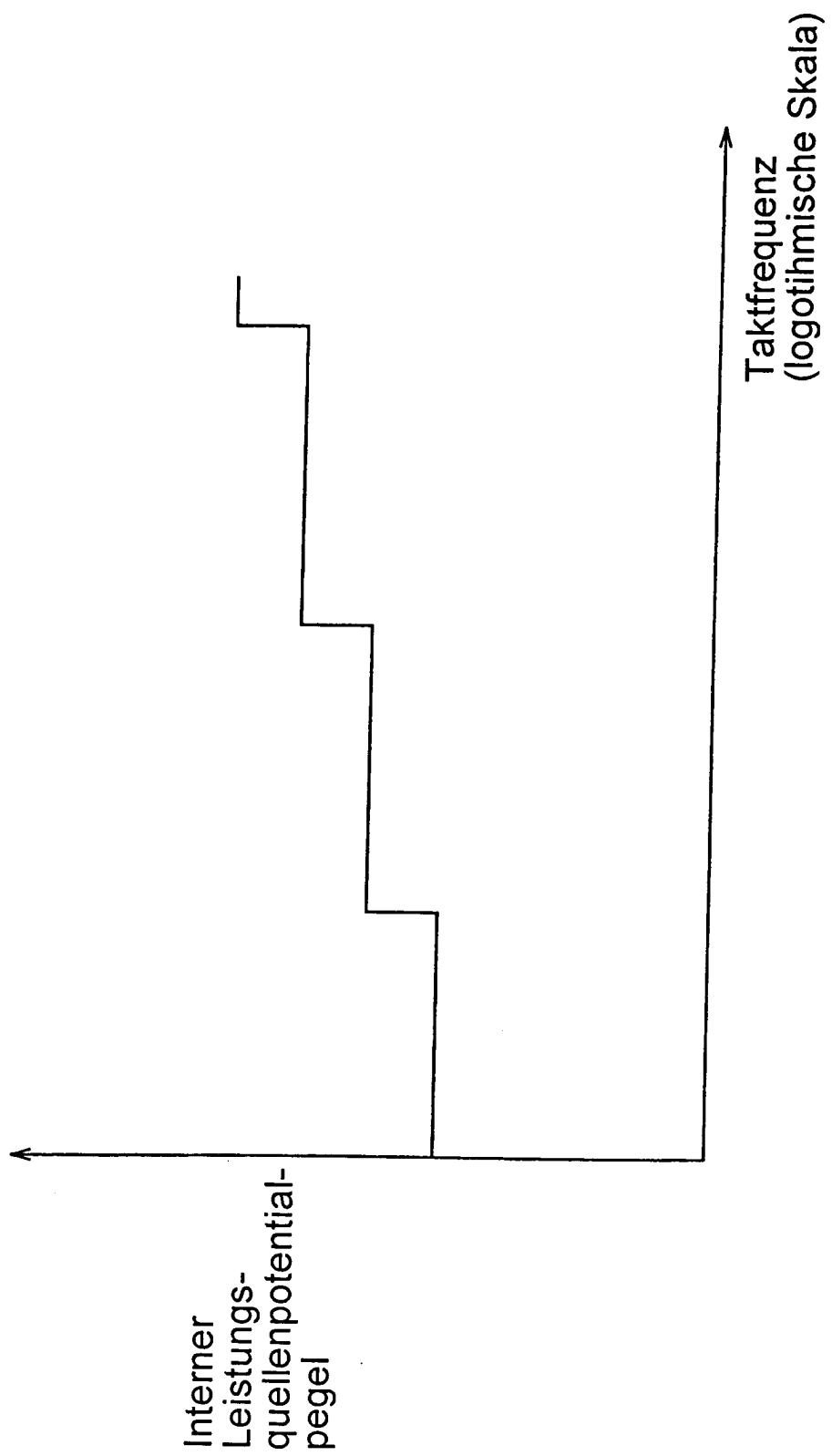

- [0112] **Fig.** 93 ist ein Diagramm zum Beschreiben eines Steuerbetriebes für ein internes Leistungsquellenpotential;

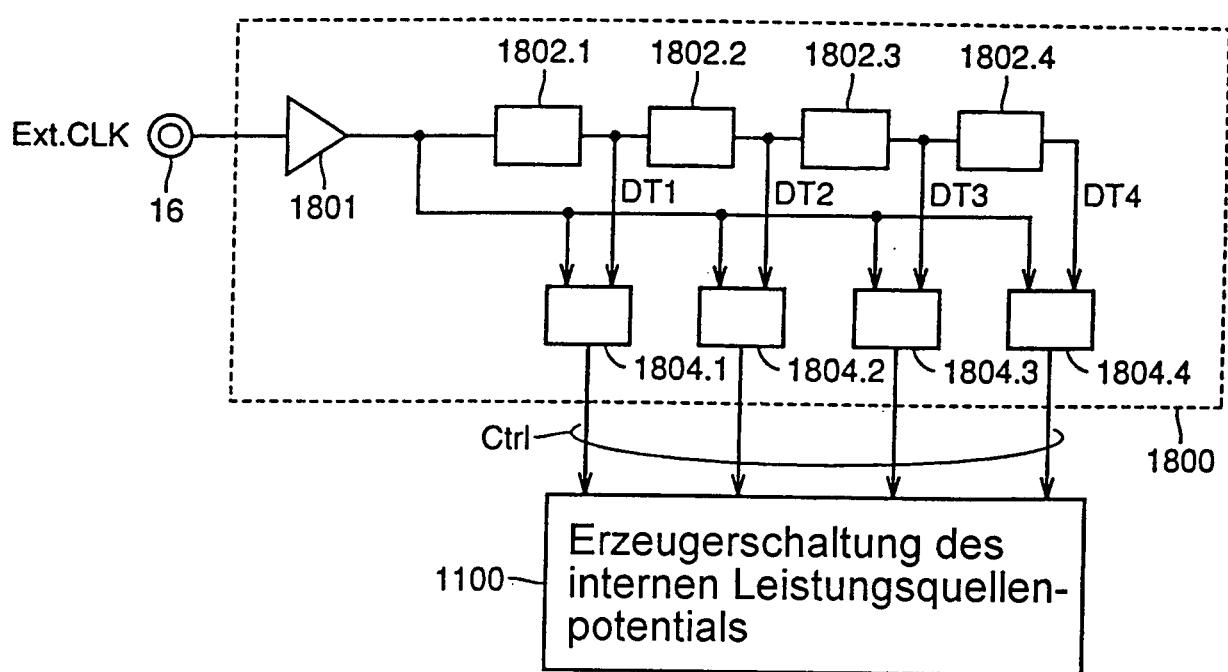

- [0113] **Fig.** 94 ist ein schematisches Blockschaltbild zum Beschreiben einer Konfiguration einer Frequenzerfassungsschaltung **1800**;

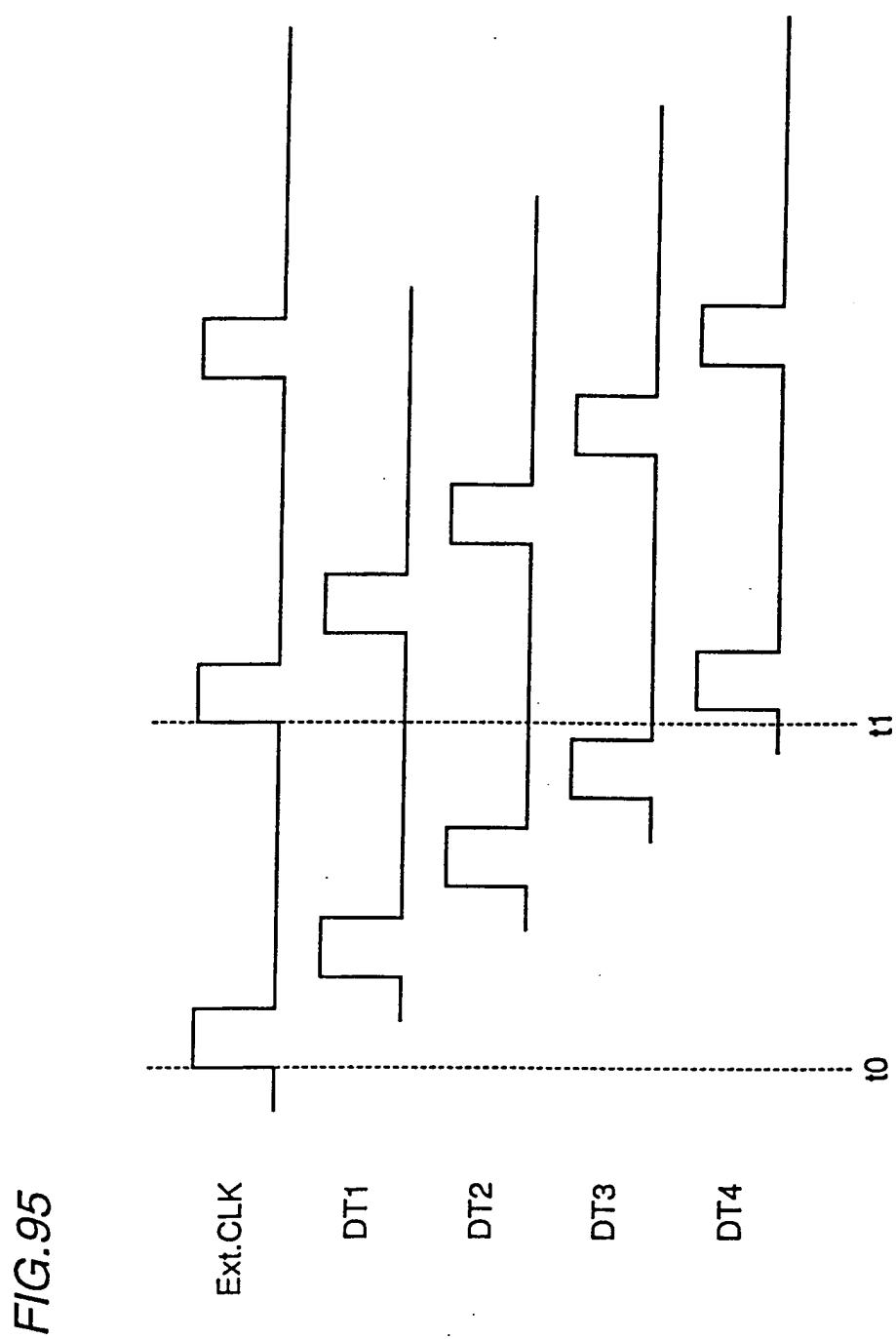

- [0114] **Fig.** 95 ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes der in **Fig.** 94 gezeigten Frequenzerfassungsschaltung;

- [0115] **Fig.** 96 ist ein schematisches Blockschaltbild zum Beschreiben einer Konfiguration einer internen Leistungsquellenorschaltung in der internen Leistungsquellenpotentialerzeugerschaltung **1100**;

- [0116] **Fig.** 97 ist ein schematisches Blockschaltbild, das eine andere Konfiguration zum Steuern eines internen Leistungsquellenpotentials darstellt;

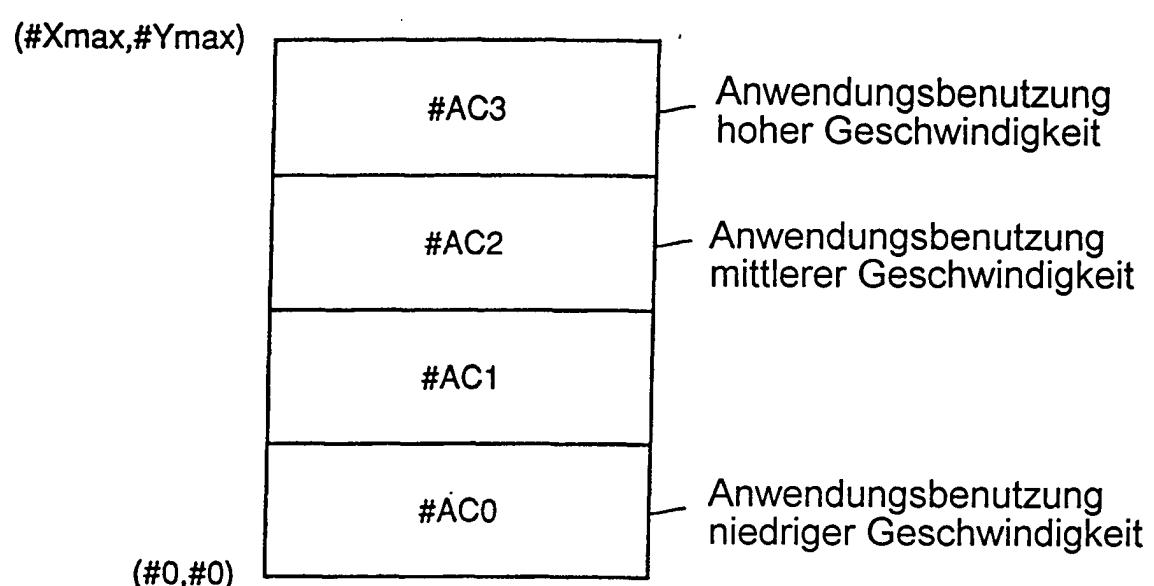

- [0117] **Fig.** 98 ist ein Speicherabbild zum Beschreiben eines Beispies einer Zuordnung in einem Speicherraum, wenn mehrere Arten von Betriebsgeschwindigkeitsmodi vorhanden sind;

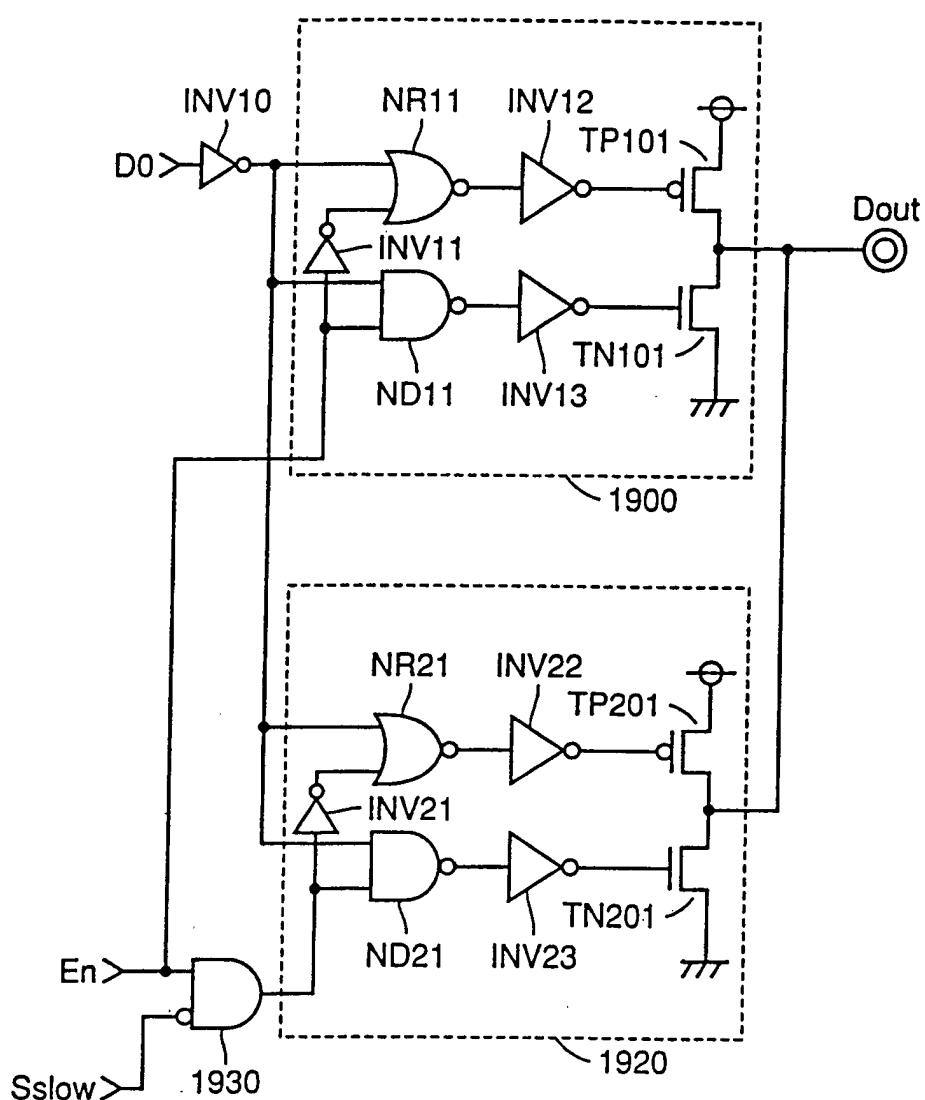

- [0118] **Fig.** 99 ist ein schematisches Blockschaltbild zum Beschreiben einer Konfiguration einer Treiberschaltung in einem I/O-Puffer **52**;

- [0119] **Fig.** 100 ist ein schematisches Blockschaltbild zum Beschreiben einer anderen Konfiguration einer Treiberschaltung in dem in **Fig.** 76 gezeigten I/O-Puffer **52**;

- [0120] **Fig.** 101 ist eine Draufsicht einer Stiftkonfiguration eines synchronen dynamischen Direktzugriffsspeicher (SDRAM) des Standes der Technik;

- [0121] **Fig.** 102 ist eine Tabelle, die Anschlußnamen des SDRAM und ihre Funktionen darstellt; und

- [0122] **Fig.** 103 ist ein Blockschaltbild, das eine Konfiguration eines integrierten Logik-DRAM des Standes der Technik darstellt.

## BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSFORMEN

- [0123] Eine detaillierte Beschreibung wird von Ausführungsformen der vorliegenden Erfindung unter Bezugnahme auf die begleitenden Zeichnungen ge-

geben, in denen die gleichen Symbole in den Zeichnungen die gleichen oder ähnliche Bestandteile bezeichnen.

### Erstes Beispiel

- [0124] **Fig.** 1 ist ein Blockschaltbild, das eine Konfiguration einer integrierten Halbleiterschaltungsvorrichtung **1** eines ersten Beispiele der vorliegenden Erfindung darstellt.

- [0125] Bezug nehmend auf **Fig.** 1 enthält eine integrierte Halbleiterschaltungsvorrichtung **1**: einen Anschluß **10**, der ein Steuersignal wie ein Steuersignal /RAS, /CAS, ..., /CS oder /WE empfängt; einen Anschluß **12**, der ein Adresssignal ADD empfängt; einen Anschluß **14**, der ein Datensignal DATA empfängt; einen Anschluß **16**, der ein externes Taktsignal Ext.CLK empfängt; einen Schnittstellenabschnitt **2**, der Steuersignale an das Innere gemäß den Steuersignalen /RAS, /CAS, ..., /CS oder /WE, dem Adresssignal ADD und dem Datensignal DATA ausgibt; einen Speicherabschnitt (DRAM) **4**, der eine Ausgabe des Schnittstellenabschnittes **2** zum Tätigwerden empfängt; ein Register **6**, das Daten und einen Befehl, die von dem Schnittstellenabschnitt **2** gegeben werden, oder ein Logikoperationsresultat hält; eine Logikschaltung **8**, die einen Betrieb wie Signalverarbeitung gemäß den Ausgaben von dem Register **6** und dem Schnittstellenabschnitt **2** durchführt; eine interne Takerzeugerschaltung **7** zum Erzeugen eines internen Taktsignals clkM für den Speicherabschnitt (DRAM) **4** und eines internen Taktsignal clkL für die Logikschaltung **8** gemäß dem externen Taktsignal Ext.CLK; und einen Schnittstellenabschnitt **9** zum Freigeben als Zwischenstufe der Datenlieferungs/Empfangs zwischen dem Register **6** und sowohl dem Speicherabschnitt **4** als auch dem Schnittstellenabschnitt **2**. Das Datenliefern/Empfangen zwischen dem Schnittstellenabschnitt **6**, dem Speicherabschnitt **4** und dem Schnittstellenabschnitt **9** wird durch einen internen Bus mbus durchgeführt.

- [0126] Anschlüsse eines Chips **1** sind die gleichen wie Anschlüsse, die in einem Allzweck-DRAM benutzt werden. Folglich kann das gleiche Gehäuse wie das, in dem ein Allzweck-DRAM-Chip aufgenommen ist, verwendet werden. Zum Beispiel ist ein Gehäuse, in dem die integrierte Halbleiterspeichervorrichtung **1** aufgenommen ist, eines mit einer Stiftkonfiguration, wie sie in **101** gezeigt ist.

- [0127] Aus diesem Grund wird, wenn eine integrierte Halbleiterschaltungsvorrichtung **1** der vorliegenden Erfindung in einer vorhandenen Anwendung angenommen wird, ein vorhandener Allzweck-DRAM einfach durch die integrierte Halbleitervorrichtungsschaltung **1** ersetzt, so daß keine Notwendigkeit auftritt, eine Baugruppe neu zu entwerfen oder einen zugeschnittenen Steuer-LSI zu entwickeln. Das heißt, da die integrierte Halbleiterschaltungsvorrichtung **1** stiftkompatibel mit dem Allzweck-DRAM ist, kann eine neue Funktion nur durch Ändern einer Software

hinzugefügt werden. Als neue Funktionen sind zum Beispiel Hinzufügen einer Schaltung zur Benutzung in einer Hochgeschwindigkeitsbildverarbeitung und eine Logikschaltung, die Verarbeitungen durchführt, die eine lange Zeit auf einem Mikrocomputer dauert, wie Verschlüsselungsverarbeitung denkbar. Weiterhin ist es erlaubt, daß Steuersignale unter Benutzung mehrerer nichtbenutzter Anschlüsse eingegeben werden können, z. B. ein NC (Nicht-verbindungs-)Stift wie der sechsunddreißigste Stift und der vierzigste Stift in **Fig. 101** in einem Verpackungsgehäuse eines Allzweck-DRAM.

[0128] Als nächstes wird die Beschreibung eines konkreten Steuerverfahrens gegeben. Ein sogenanntes speicherabgebildetes I/O-Verfahren wird auf eine Steuerung einer integrierten Logikschaltung **8** angewendet.

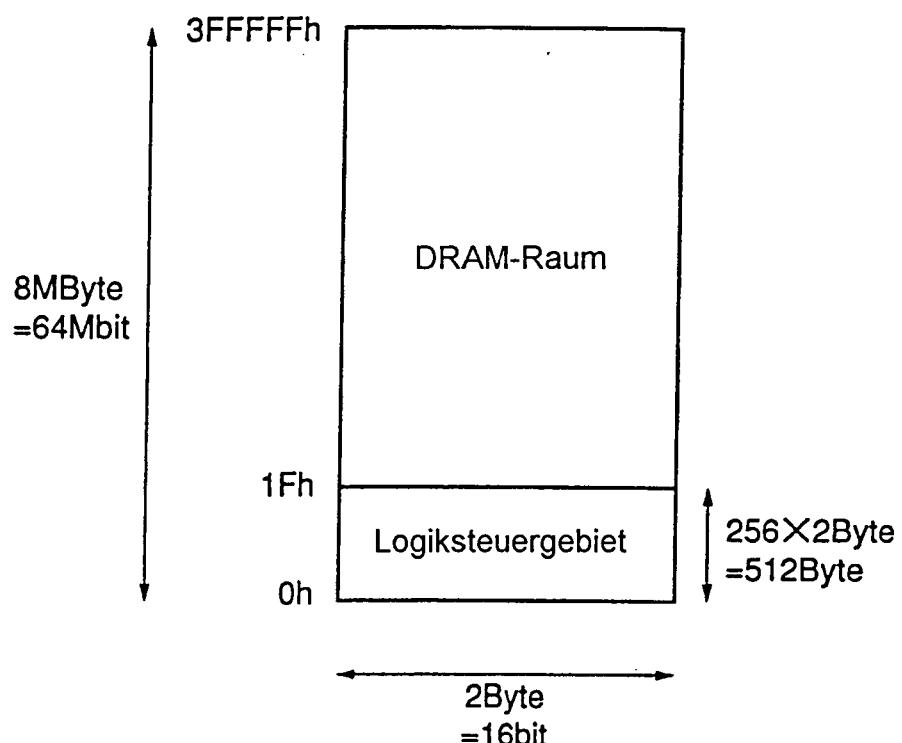

[0129] **Fig. 2** stellt ein Speicherabbild einer integrierten Logikhalleiterspeichereinrichtung des ersten Beispieles dar.

[0130] Bezug nehmend auf **Fig. 2** wird angenommen, daß eine Kapazität eines auf einem Chip hergestellten DRAM gleich 64 Mbit ist und eine Wortkonfiguration von 16 Bit ist. Adressen des DRAM enthalten eine X-Adresse, die von X0 bis X13 reicht, und eine Y-Adresse, die von Y0 bis Y7 reicht. Daher sind die Speicheradressen, die 8 Mbyte steuern, von 0h bis 3FFFFh.

[0131] In dem Allzweck-DRAM können Daten in dem gesamten Adressraum geschrieben und ausgelesen werden. Solch ein Raum, in den Daten geschrieben und ausgelesen sein können, wird ein DRAM-Raum als Definition genannt. Bei der vorliegenden Erfindung ist ein spezielles Gebiet in dem Adressraum einem Logiksteuerbereich für die integrierte Logikschaltung zugeordnet. Zum Beispiel von 0h bis 1Fh in der Adresse dem Logiksteuerbereich zugeordnet. Eine Kapazität des Logiksteuerbereiches beträgt z. B.  $256 \times 2$  Byte = 512 Byte. Ein Befehl und ein Modus, die die Logikschaltung steuern, können gemäß den in den Adressraum geschriebenen Daten ausgewählt werden.

[0132] Während in **Fig. 2** ein Gebiet in der Seite der niedrigsten Adresse gesichert ist, kann das Logiksteuerbereich der höchsten Seite (3 FFFFh bis 3FFE0h) zugeordnet sein. Es ist auch erlaubt, daß, wenn der SDRAM als DRAM gedacht wird, der auf einem Chip integriert ist, ein Gebiet, in dem eine Adresse zugeordnet ist, nach dem Setzen eines Modusregisters ausgewählt werden kann. Weiterhin kann, solange das Logiksteuerbereich einer Einstellung eines Modusregisters zugeordnet ist, der SDRAM auch als ein normaler SDRAM von 64 Mbit benutzt werden.

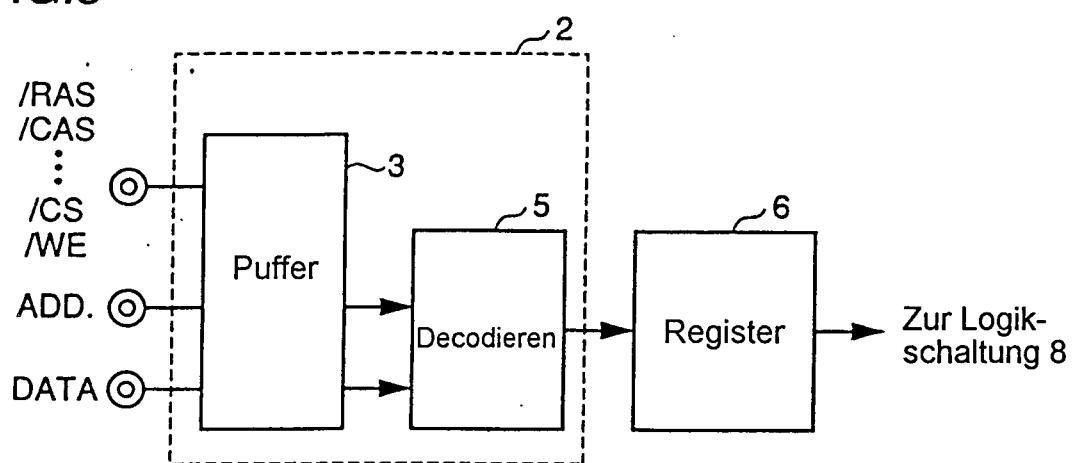

[0133] **Fig. 3** ist ein Blockschaltbild zum Beschreiben eines Weges, wie ein extern eingegebenes Signal zu einer Logikschaltung übertragen wird.

[0134] Bezug nehmend auf **Fig. 3** enthält ein Schnittstellenabschnitt **2**: einen Puffer **3**, der die Steuersignale /RAS, /CAS, ..., /CS und /WE, die Adresse ADD und das Datensignal DATA empfängt;

und eine Decodierschaltung **5**, die eine Ausgabe des Puffers **3** empfängt zum Decodieren der Ausgabe, worin das Register **6** Information wie einen Modus und einen Befehl als Reaktion auf eine Ausgabe der Decodierschaltung **5** hält, und die Logikschaltung **8** wird gemäß der in dem Register **6** gehaltenen Information gesteuert.

[0135] Während die Decodierschaltung **5** das Adresssignal ADD und das Datensignal DATA decodiert, tritt ein Fall auf, in dem Daten, die in das Logiksteuerbereich geschrieben werden, das durch ein Adresssignal spezifiziert ist, gehalten werden, wie sie ursprünglich in dem Register **6** sind.

[0136] Wenn das Register **6** aus einem SRAM (Statischer Direktzugriffsspeicher) oder ähnlichem aufgebaut ist, tritt ein Fall auf, in dem Daten in einem Gebiet des SRAM gehalten werden, das gemäß dem Adresssignal ADD spezifiziert ist. Weiter ist es auch erlaubt, daß ein Gebiet, ein Teil des DRAM, als eine Halteschaltung anstelle des Registers **6** benutzt wird, und Daten zur Steuerung der Logikschaltung werden in dem Gebiet gehalten.

[0137] Das heißt, eine Konfiguration kann angenommen werden, bei der ein Adressgebiet selbst, in dem der oben beschriebene Logiksteuerbereich zugeordnet ist, in dem Speicherabschnitt **4** zugeordnet ist. Alternativ kann eine Konfiguration auch angenommen werden, bei der die höchsten Bit virtuell zu einem Adressraum des Speicherabschnittes **4** addiert werden, und ein Adressgebiet, in dem ein Logiksteuerbereich zugeordnet ist, ein Gebiet wird, ein Teil des virtuellen Adressraumes, der nicht ein Adressraum eines Speicherzellenfeldes ist.

[0138] In der folgenden Beschreibung wird jedoch zur Vereinfachung der Beschreibung, obwohl es speziell nicht begrenzt ist, angenommen, daß eine solch einem Logiksteuerbereich zugeordnete Adresse dem Register **6** von **Fig. 1** zuzuordnen ist.

[0139] Weiterhin ist in der folgenden Beschreibung zur Vereinfachung der Beschreibung eine Logikoperation in der Logikschaltung **8** eine Verschlüsselung, obwohl nicht speziell darauf begrenzt.

[0140] Es sei angenommen, daß die in **Fig. 1** gezeigte integrierte Halbleiterschaltungsvorrichtung **1** drei Arten von Betriebsmodi aufweist, wie unten beschrieben wird, und eine der drei Arten von Betriebsmodi wird gemäß einer Kombination von Steuersignalen ausgewählt, die extern gegeben werden.

[0141] Wie in der unten gegebenen Beschreibung klar ist, wird in der Halbleiterspeichereinrichtung **1** mit den Betriebsmodi, wie sie unten beschrieben werden, indem ein richtiger Verarbeitungsmodus in Übereinstimmung mit einem eingebetteten System ausgewählt wird, das keinen Daten-Cache enthält, ein System, in dem ein Daten-Cache enthalten ist, oder ein System, in dem eine MMU (Memory Management Unit) unterstützt wird und das in einem virtuellen Adressraum programmiert wird, eine Verarbeitungseffektivität der Verschlüsselung verbessert.

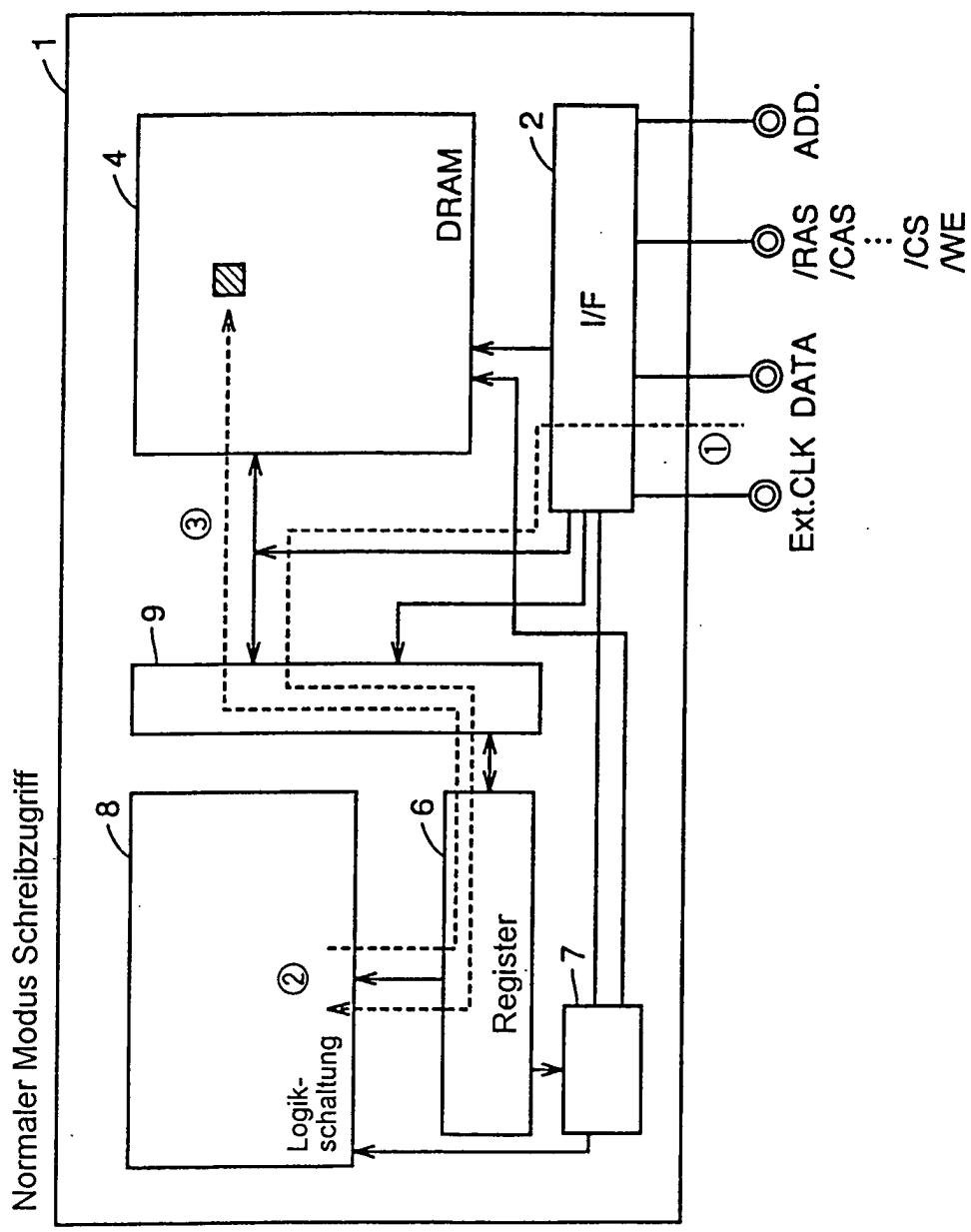

[0142] **Fig. 4** ist ein Blockschaltbild zum Beschrei-

ben eines Betriebes in einem normalen Modus, einer der Betriebsmodi der integrierten Halbleiterschaltungsvorrichtung 1.

[0143] In **Fig. 4** wird eine Beschreibung eines Betriebes von Schreibzugriff in dem normalen Modus gegeben.

[0144] Wenn Schreibzugriff auf die integrierte Halbleiterschaltungsvorrichtung 1 während des Eintritts in einen Verschlüsselungsmodus gemäß einer Kombination von Steuersignalen durchgeführt wird, werden Schreibdaten verschlüsselt, und ein Resultat davon wird automatisch an einer im Schreiben spezifizierten Adresse gehalten. Das heißt, wenn Daten, von denen gewünscht wird, daß sie verschlüsselt werden, eingegeben werden ([1]), wird Verschlüsselung in der Logikschaltung 8 ([2]) durchgeführt, und ein Verschlüsselungsresultat wird zu einer Adresse in dem Schreibzugriff ([3]) übertragen.

[0145] **Fig. 5** ist ein Blockschaltbild zum Beschreiben eines Betriebes von Lesezugriff in dem normalen Modus.

[0146] Wenn Lesezugriff auf die integrierte Halbleiterschaltungsvorrichtung 1 während des Eintritts in einen Verschlüsselungsmodus gemäß einer Kombination von Steuersignalen durchgeführt wird, werden Daten an einer Adresse, auf die zugegriffen wird, zu der Logikschaltung 8 von dem Speicherabschnitt 4 übertragen ([1]), Verschlüsselung wird in der Logikschaltung 8 durchgeführt ([2]), und ein Verschlüsselungsresultat wird zu der gleichen Adresse wie eine Adresse in dem Lesezugriff übertragen ([3]).

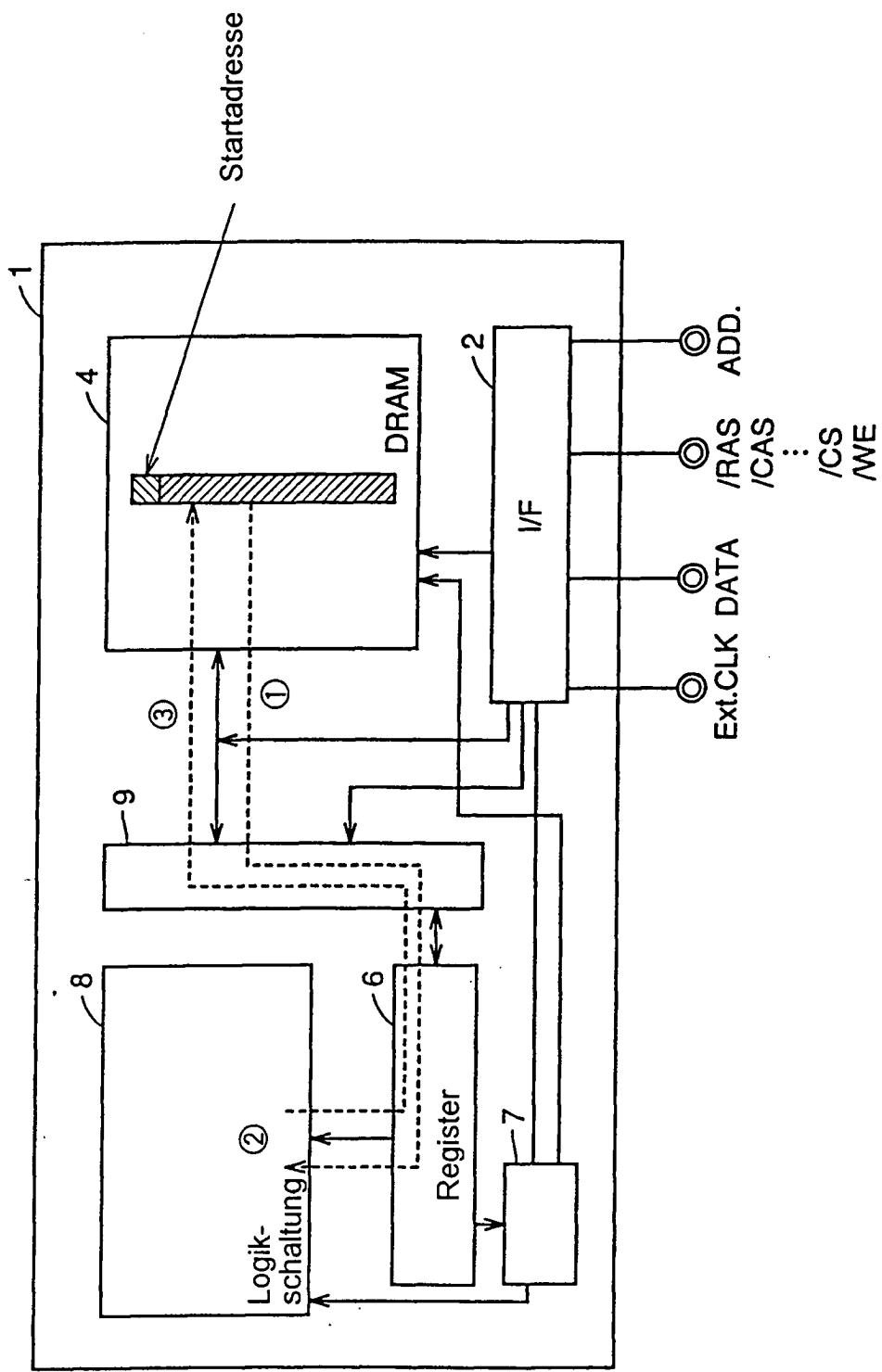

[0147] **Fig. 6** ist ein Blockschaltbild zum Beschreiben eines Betriebes in einem Blockmodus, einem anderen der Betriebsmodi der integrierten Halbleiterschaltungsvorrichtung 1.

[0148] In dem Blockmodus wird eine Blocklänge (Verarbeitungseinheit der Verschlüsselung) von Daten gemäß einer Kombination eines Steuersignals, eines Adresssignals und anderer während des Setzens eines Verschlüsselungsmodus gesetzt.

[0149] Danach wird das Setzen einer Startadresse für die Verarbeitung durch Bewirken eines Blindsightschreibens (oder Blindlesens) an eine Adresse durchgeführt. Daten der gesetzten Blocklänge werden automatisch zu der Logikschaltung 8 von dem Speicherabschnitt 4 übertragen ([1]), wobei die Startadresse als ein Startpunkt dient, Verschlüsselung wird durchgeführt ([2]), und danach werden die Daten eines verarbeiteten Resultats wieder automatisch zu den Adressen über eine Blocklänge von der Startadresse als ein Startpunkt geschrieben ([3]). Eine Adresszählerschaltung (nicht gezeigt) ist für die Datenübertragung der Daten wie eine Blocklänge vorgesehen. Die Adresszählerschaltung kann funktional durch einen Adresszähler ersetzt werden, der benutzt wird, wenn eine Selbstauffrischätigkeit in dem DRAM durchgeführt wird.

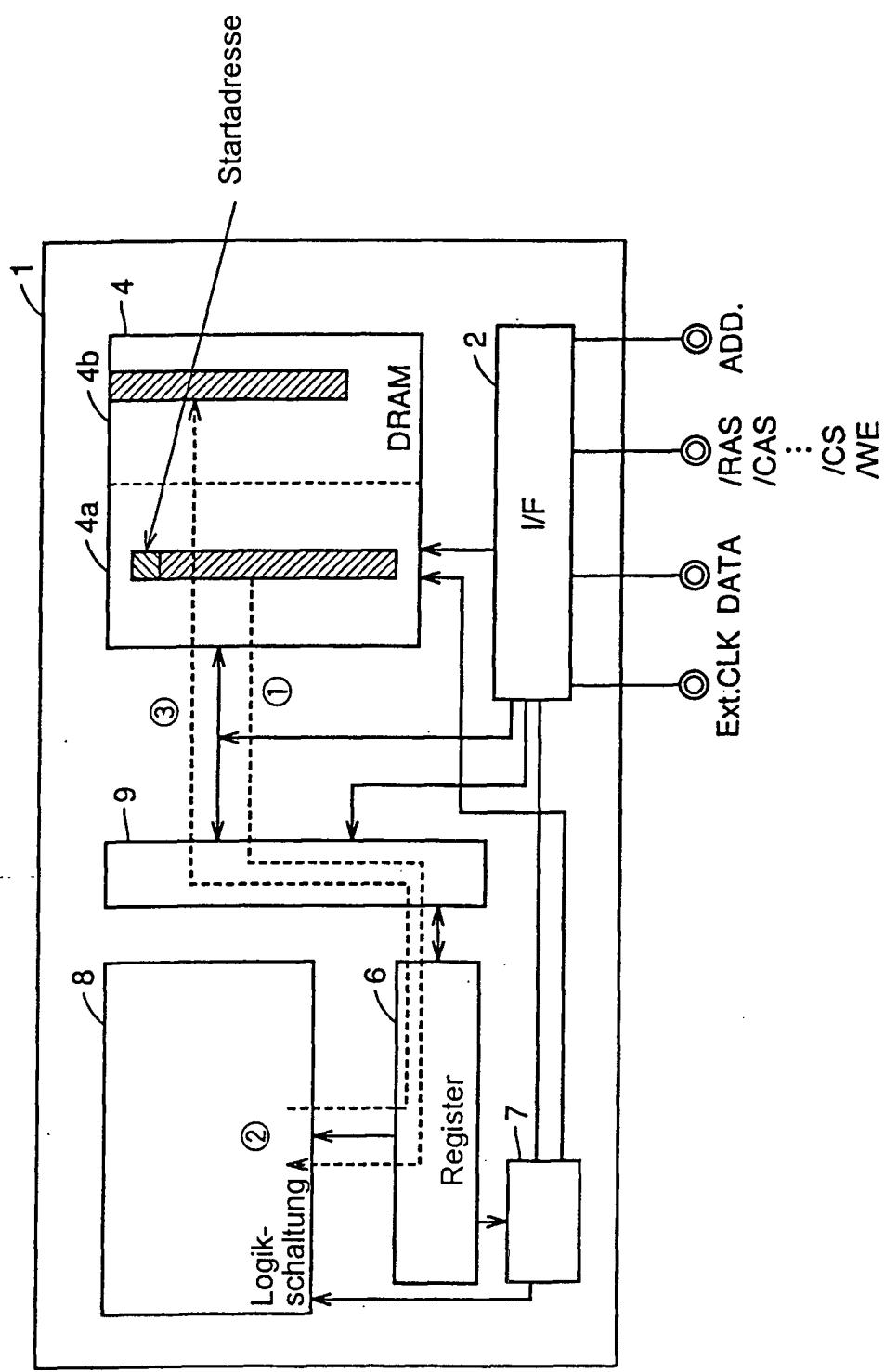

[0150] **Fig. 7** ist ein Blockschaltbild zum Beschreiben eines Betriebes in einem Puffermodus, ein noch anderer der Betriebsmodi der integrierten Halbleiter-

schaltungsvorrichtung 1.

[0151] In dem Puffermodus wird eine Blocklänge von zu chiffrierenden Daten während des Einstellens des Verschlüsselungsmodus gesetzt. In dem Puffermodus wird ein vorgeschrriebenes Adressgebiet des Speicherabschnitts 4 als ein Pufferadresgebiet 4b gesichert. In dem Pufferadresgebiet 4b wird eine Mehrzahl von Puffergebieten gesetzt und Puffer-IDs werden den entsprechenden Puffergebieten zur Unterscheidung zugeordnet. Folglich wird in dem Puffermodus das Einstellen eines Puffer-ID einer Übertragungsbezeichnung eines Chiffrierungsresultats nach Setzen einer Blocklänge von zu chiffrierenden Daten durchgeführt.

[0152] Danach wird das Setzen einer Startadresse zum Verarbeiten durch Bewirken eines Blindsightschreibens (oder Blindlesens) einer Adresse in einem Verarbeitungsadresgebiet 4a durchgeführt.

[0153] Die Daten der gesetzten Blocklänge werden automatisch zu der Logikschaltung 8 von dem Speicherabschnitt 4 mit der Startadresse als ein Startpunkt übertragen ([1]), Verschlüsselung wird durchgeführt ([2]), und danach werden Daten eines Verarbeitungsresultats automatisch zu einem Puffergebiet einer spezifizierten Puffer-ID übertragen ([3]).

[0154] Es sei angemerkt, daß in einem Fall, in dem der Speicherabschnitt 4 aus einer Mehrzahl von Bänken aufgebaut ist, kein Konflikt zwischen Lesen und Schreiben auf einer Bank auftritt, wodurch eine effiziente Verarbeitung ermöglicht wird, wenn Puffergebiete gleichmäßig den Bänken zugeordnet werden, und eine Bank, zu der das Verarbeitungsadresgebiet 4a gehört, und eine Bank, zu der ein Puffergebiet einer Übertragungsbezeichnung gehört, unterscheiden sich voneinander.

[0155] **Fig. 8** ist ein Flußdiagramm zum Beschreiben von Tätigkeiten in den drei Modi, wie oben beschrieben wurde.

[0156] Bezug nehmend auf **Fig. 8**, wenn die Verarbeitung gestartet wird (Schritt S100), wird die Logikschaltung 8 durch Softwarerücksetzen zurückgesetzt, wenn eine Verschlüsselungsfunktion zum ersten Mal nach dem Einschalten benutzt wird (Schritt S102).

[0157] Aufeinander folgend wird, wie später im einzelnen ausgeführt wird, das Einstellen verschiedener Arten von Modi für die Verschlüsselung durchgeführt (Schritt S104): zum Beispiel Auswahl eines Verschlüsselungssystems mit Geheimschlüssel, Auswahl einer der drei Arten von Verschlüsselungsmodi, die oben beschrieben wurden, Bezeichnung einer Zahl von Puffern, wenn in dem Puffermodus.

[0158] Weiterhin wird ein Geheimschlüssel eingegeben (Schritt S106). Hierin wird, wenn ein Drei-fach-DES-(Datenverschlüsselungsstandard)System ausgewählt ist, die Eingabe von zwei Arten von Schlüsseln benötigt.

[0159] Wenn eine Blockschiffierung in einer Kette benutzt wird, wird ein anfänglicher Vektor eingegeben (Schritt S108).

[0160] In Aufeinanderfolge in einem Zustand, in dem der normale Modus ausgewählt ist, wenn die Dateneingabe durch ein Dateneingabebefehl gestartet wird (Schritt S110), wird Datenlesen über eine Verschlüsselungsblocklänge und ihre Verschlüsselung bei normalem Lesezugriff durchgeführt (Schritt S112), während andererseits Datenverschlüsselung über die Verschlüsselungsblocklänge und Schreiben eines Verarbeitungsresultats davon in normalem Schreibzugriff durchgeführt wird (Schritt S114). Das heißt, in einer Periode während ein Dateneingabebefehl eingegeben wird und Dateneingabe in dem normalen Lesen und normalen Schreiben durchgeführt wird, wird eine Mehrzahl von Speicherzugriffen der Verschlüsselungsblocklänge angenommen, und Verschlüsselung davon wird sequentiell in der Logikschaltung **8** durchgeführt.

[0161] Wenn ein Befehl eines Dateneingabestopps gegeben wird, hört die Dateneingabe auf (Schritt S116), und darauf folgend wird eine Flagprüfung in dem Register **6** extern durchgeführt (Schritt S138). Solange das Flag FL = "1", was "in Verschlüsselung" bezeichnet, kann kein Zugriff zu dem DRAM durchgeführt werden und der Zugriff zu dem DRAM wird zuerst freigegeben, nachdem FL = "0" hergestellt ist (Schritt S140).

[0162] Wenn andererseits der Blockmodus oder der Puffermodus spezifiziert ist, wird die Eingabe einer Blocklänge folgend dem Schritt S108 (Schritt S120) durchgeführt.

[0163] Darauf folgend wird in dem Fall des Blockmodus, wenn ein Dateneingabebefehl gegeben wird (Schritt S122), das Blindlesen oder Blindschreiben zum Spezifizieren einer Startadresse durchgeführt (Schritt S124), und eine Verarbeitung in dem Blockmodus wird durchgeführt. Wenn ein Dateneingabestoppbefehl eingegeben wird (Schritt S126), dann bewegt sich die Verarbeitung zu Schritt S138.

[0164] In dem Puffermodus wird zuerst eine Puffer-ID eingegeben (Schritt S130). Wenn ein Dateneingabebefehl gegeben wird (Schritt S132), dann wird Blindlesen oder Blindschreiben zum Spezifizieren einer Startadresse bewirkt (Schritt S134), und die Verarbeitung in dem Puffermodus folgt. Wenn ein Dateneingabestoppbefehl eingegeben wird (Schritt S136), dann bewegt sich die Verarbeitung zu Schritt S138.

[0165] Durch Durchführen der oben beschriebenen Verarbeitung ist es möglich, drei Arten von Betriebsmodi zu steuern.

[0166] Bei der obigen Verarbeitung ist ein spezieller Modus vorhanden während einer Periode von einer Zeit, wenn ein Dateneingabestartbefehl eingegeben wird, bis zu einer Zeit, wenn ein Dateneingabestoppbefehl eingegeben wird. Wenn folglich der Zugriff extern auf einen Speicherraum eines DRAM durchgeführt wird, wird eine der drei Arten von Verarbeitungen, wie oben beschrieben wurde, auf zu verarbeitenden Daten durchgeführt.

[0167] Selbst wenn der Dateneingabestoppbefehl

eingegeben wird, wird Information über einen Modus selbst in dem Register **6** gehalten; wenn daher der Dateneingabestartbefehl eingegeben wird, ist es möglich, die Verarbeitung in dem gleichen Verarbeitungsmodus durchzuführen.

[0168] In einem Fall, in dem eine Unterbrechung, die eine Auffrischtätigkeit anweist, von einer Speichersteuerung eines Systems während der Verschlüsselung in der Logikschaltung **8** gegeben wird, kann eine Verarbeitung wie unten beschrieben angenommen werden.

[0169] Zählen der Zahl von Auffrischbefehlen, die während der Verarbeitung in der Logikschaltung **8** eingegeben werden, wird durchgeführt, und die Information wird zum Beispiel in dem Register **6** gehalten. Wenn Verschlüsselung in der Logikschaltung **8** beendet ist, werden Auffrischverarbeitungen auf dem Speicherabschnitt **4** so häufig wie die Zahl der Zählungen durchgeführt. Das Flag FL bleibt in einem Zustand von "1" während der Auffrischperiode ähnlich zu einer Verarbeitungsperiode der Logikschaltung **8** in Hinblick auf die Auffrischperiode als eine von Kein-DRAM-Zugriff. Nachdem die Auffrischtätigkeit beendet ist, geht das Flag FL zu einem Zustand von "0" über.

[0170] Weiterhin nimmt in **Fig. 8** nach Eingabe eines Dateneingabestartbefehls die integrierte Halbleiterschaltung **1** nur entweder einen Stoppbefehl oder einen Softwarerücksetzbefehl an.

[0171] Es wird angenommen, daß in dem Speicherabschnitt **4** ein Modusregister zum Spezifizieren eines Betriebsmodus davon zum Beispiel einer Burstlänge oder Dauer vorgesehen ist. Es wird weiter angenommen, daß eine Konfiguration angenommen ist, in der die Verarbeitung aus einem Steuermodus der Logikschaltung **8** derart herauskommen kann, daß die integrierte Halbleiterschaltung **1** einen normalen Betrieb fortsetzen kann unabhängig davon, in welchem Zustand die integrierte Halbleiterschaltung **1** bei dem Einschalten ist: nicht nur, wenn ein Softwarerücksetzbefehl gegeben ist, sondern auch wenn ein Modusregistereinstellbefehl an den Speicherabschnitt **4** gegeben ist.

#### [Inhalte von Verschlüsselung]

[0172] Eine einfache Beschreibung der in der Logikschaltung **8** durchgeföhrten Verschlüsselung wird im folgenden gegeben.

[0173] **Fig. 9** ist eine Tabelle, die Beispiele von Kryptosystemen darstellt, die eine Logikschaltung **8** durchführen kann.

[0174] Bezugnehmend auf **Fig. 9** unterstützt die Logikschaltung **8** RSA-(Rivest-Shamir-Adelman)Verschlüsselung als ein Kryptosystem mit öffentlichem Schlüssel und ein DES-System und ein Dreifach-DES-System als ein Kryptosystem mit geheitem Schlüssel.

[0175] Weiterhin werden in dem Kryptosystem mit geheitem Schlüssel Modi unterstützt wie ECB (Elek-

trisches Codebuch), CBC (Chiffrierungsblockketten), OFB (Ausgaberückkopplung), CFB (Chiffierungs-rückkopplung), die die hauptsächlichen Blockverschlüsselungsmodi sind. Der Logikschaltung 8 ist eine kritische Verarbeitung in der Verschlüsselung zum Verstärken der Geeignetheit der Anwendung zugeordnet, und andere Verarbeitungen werden der Softwarezentrierungstätigkeiten auf der Seite des Mikrocomputers des Systems unterworfen, das die integrierte Halbleiterschaltungsvorrichtung 1 steuert. Das größte Merkmal davon ist, daß Verschlüsselungssteuerung auf eine Weise kompatibel zu einem Allzweck-SDRAM realisiert werden kann.

[0176] Zum Beispiel wird in einem elektronischen Handelsmarkt die Aufstellung solch eine Kryptosystems, wie es oben beschrieben wurde, wichtig. Selbst bei einem drahtlosen Anwendungsprotokoll (WAP), dessen Anwendung auf ein tragbares Telefon erwartet wird, werden die oben beschriebenen Kryptosysteme unterstützt.

[0177] Zum Beispiel werden in Sicherheitsverarbeitung in solch einem Netzwerk Verarbeitungen wie Hash, Datencodierung und -füllen auf der Seite des Mikrocomputers des Systems verarbeitet. Im Gegensatz dazu kann die integrierte Halbleiterschaltungsvorrichtung Verarbeitungen durchführen, von denen gesagt werden kann, daß sie einen Hauptteil von Softwarezentrierungsverarbeitung in einer Praxis des Standes der Technik ist, wie Leistungsrestbetrieb, der bei elektronischer Authentifizierung gemäß RSA durchgeführt wird, Montgomery-Multiplikationsrestbetrieb und andere Restbetriebe. Wenn folglich eine integrierte Halbleiterschaltungsvorrichtung 1 nur kritische Verarbeitungen in dein System durchführt, kann Hochgeschwindigkeitsverarbeitung realisiert werden, während ein Freiheitsgrad auf der Anwendungsseite vergrößert wird.

#### [Kryptosystem mit geheimem Schlüssel]

[0178] In dem oben beschriebenen elektronischen Handel oder ähnlichem wird elektronische Authentifizierung in einem Kryptosystem mit öffentlichem Schlüssel durchgeführt, während Verschlüsselung von Datenübertragung/Empfang nach der Authentifizierung allgemein unter Benutzung eines Kryptosystems mit geheimem Schlüssel durchgeführt wird: Benutzung eines sogenannten Hybridsystems.

[0179] **Fig. 10** ist eine konzeptuelle Zeichnung, die eine fundamentale Einheit für DES-Verschlüsselung darstellt, die als ein Kryptosystem mit geheimem Schlüssel benutzt wird.

[0180] Eine Schlüssellänge des DES ist 56 Bit, und 14 Bit eines einfachen Textes wird als 14 Bit eines Chiffretextes ausgegeben.

[0181] Andererseits sind **Fig. 11** und **12** konzeptuelle Zeichnungen, die ein sogenanntes Dreifach-DES-Verarbeitungssystem darstellen.

[0182] Das Dreifach-DES enthält ein Kryptosystem von 112 Bit in Schlüssellänge, wie in **Fig. 11** gezeigt

ist, und ein Kryptosystem von 168 Bit in Schlüssellänge, wie in **Fig. 12** gezeigt ist.

[0183] Bei dem in **Fig. 11** gezeigten Dreifach-DES-112 wird ein einfacher Text von 64 Bit mit einem ersten 56 Bit-Schlüssel chiffriert, danach mit einem zweiten 56 Bit-Schlüssel dechiffriert, dann weiter mit dem ersten 56 Bit-Schlüssel chiffriert, und ein chiffriertes Resultat wird als Chiffretext von 64 Bit ausgegeben.

[0184] Bei dem Dreifach-DES-168, das in **Fig. 12** gezeigt ist, wird ein einfacher Text von 64 Bit mit einem ersten 56 Bit-Schlüssel chiffriert, darauf folgend wird dieses mit einem zweiten 56 Bit-Schlüssel dechiffriert, dann weiter mit einem dritten 56 Bit-Schlüssel chiffriert, und ein chiffriertes Resultat wird als Chiffretext von 64 Bit ausgegeben.

[0185] **Fig. 13** bis **15** sind konzeptuelle Zeichnungen, die die Entschlüsselung darstellen, die entsprechend zu den **Fig. 10** bis **12** durchgeführt wird.

[0186] Wie in **Fig. 13** bis **15** gezeigt ist, kann die Entschlüsselung eines Chiffretextes in einen einfachen Text in DES durchgeführt werden, indem absolut der gleiche Algorithmus wie die Chiffrierung von einem einfachen Text in ein Chiffretext benutzt wird.

#### [EBC-Modus]

[0187] **Fig. 16** ist eine konzeptuelle Zeichnung zum Beschreiben einer Verschlüsselung in dem EBC-Modus. **Fig. 17** ist eine konzeptuelle Zeichnung zum Darstellen von Verschlüsselung in dem EBC-Modus.

[0188] Bei der Verschlüsselung wird ein gewöhnlicher Text (einfacher Text) in 64 Bitblöcke  $M_i$  ( $M = M_1, M_2, M_3, \dots$ ) unterteilt, und die Verschlüsselung wird auf jedem Block mit einem geheimen Datenschlüssel  $K$  durchgeführt, der gemeinsam einem Sender und einem Empfänger eigen ist. Indem das getan wird, werden Chiffretexte  $C_i$  ( $C = C_1, C_2, C_3, \dots$ ) von jeweils 64 Bit erzeugt.

[0189] Wie in **Fig. 17** gezeigt ist, wird bei der Entschlüsselung ein Chiffretext  $C_i$  mit dem gleichen Schlüssel entschlüsselt, wie bei der Verschlüsselung benutzt wurde, wodurch einfache Texte  $M_i$  ( $M = M_1, M_2, M_3, \dots$ ) erzeugt werden.

#### [CBC-Modus]

[0190] Eine einfache Beschreibung wird von dem CBC-Modus als ein Blockmodus in Kette unten gegeben.

[0191] In dem CBC-Modus wird ein Block  $M_i$ , der durch Unterteilen eines einfachen Textes in 64 Bit-Blöcke erhalten wird, zum Erhalten eines Chiffretextblockes  $C_i$  ähnlich zu dem oben beschriebenen EBC-Modus chiffriert, und weiter wird eine Exklusiv-lagiksumme zwischen dem Chiffretextblock  $C_i$  und dem nächsten Einfachtextblock  $M_{i+1}$  als Eingabe bei der nächsten Verschlüsselung benutzt. Solch ein Vorgang wird wiederholt, und eine Kette wird erstreckt, indem eins nach dem andern addiert wird,

wodurch eine Chiffre erzielt werden kann, die schwer zu knacken ist.

[0192] Andererseits wird Entschlüsselung derart durchgeführt, daß ein Chiffretextblock  $C_i$  ähnlich dem EBC-Modus entschlüsselt wird, so daß ein Resultat  $M_i$  erhalten wird, eine Exklusivlogiksumme zwischen  $C_i$  und einem entschlüsselten Resultat des nächsten Chiffretextblockes  $C_{i+1}$  wird als ein Ausgangsein-fachtextblock  $M_{i+1}$  erzeugt, und solch ein Vorgang wird wiederholt, und eine Kette wird erstreckt, indem eins nach dem andern addiert wird, wodurch eine Entschlüsselung durchgeführt werden kann.

[0193] Wenn ein Einfachtextblock durch  $M_i$  bezeichnet ist, wird ein Chiffretextblock durch  $C_i$  ( $i = 1, 2, \dots$ ) bezeichnet, Verschlüsselung unter Benutzung eines kryptografischen Schlüssels  $K$  wird durch  $E_K$  bezeichnet, und Entschlüsselung wird durch  $D_K$  bezeichnet, durch Definition kann der CBC-Modus durch die unten gezeigten Logikausdrücke durchgeführt werden:

$$C_1 = E_K(M_1 + IV)$$

$$C_i = E_K(M_i + C_{i-1}) \quad (i: 2, 3, \dots)$$

$$M_i = D_K(C_i) + M_{i-1}$$

$$M_i = D_K(C_i) + C_{i-1} - 1 \quad (i: 2, 3, \dots)$$

worin  $IV$  ein Anfangswert ist und in einem ersten Schritt sowohl bei der Verschlüsselung als auch bei der Entschlüsselung benutzt wird; ein Symbol  $+$  bedeutet eine Exklusivlogiksummenoperation; und eine Funktion  $E_K(\dots)$  bezeichnet eine Verschlüsselung, und eine Funktion  $D_K(\dots)$  bezeichnet eine Entschlüsselung.

[0194] Der Anfangswert (anfängliche Vektor)  $IV$  ist der gleiche Wert auf der Seite der Verschlüsselung als auch auf der Seite der Entschlüsselung. Da ein Wert des Anfangswertes  $IV$  einer dritten Partei bekannt sein kann, ist es nicht notwendig, daß der Anfangswert  $IV$  zwischen einem Sender und einem Empfänger geheim gesendet wird. Zu dieser Zeit wird, wenn ein Wert des Anfangswertes  $IV$  geändert wird, ein anderer Chiffretext aus der gleichen Nachricht erzeugt.

[0195] **Fig. 18** ist eine konzeptuelle Zeichnung zum Beschreiben von Verschlüsselung in dem CBC-Modus.

[0196] Durch Durchführen der Verschlüsselung einer Exklusivlogiksumme zwischen dem Anfangswert  $IV$  und einem Einfachtextblock  $M_1$  wird ein entschlüsselter Block  $C_1$  erzeugt, und solch ein Vorgang wird sequentiell in Kette danach wiederholt.

[0197] Eine Einfachtextblocklänge, die zu einer Zeit an die integrierte Halbleiterschaltungsvorrichtung 1 eingegeben werden kann, wird jedoch durch eine Größe des Registers 6 bestimmt.

[0198] Wenn daher ein einfacher Text mit einer Länge länger als die Größe des Registers 6, wird ein

nächster Einfachtextblock mit dem unmittelbar vorangehenden Chiffretextblock ( $C_i$  in **Fig. 18**) als ein Anfangswert chiffriert.

[0199] **Fig. 19** ist eine konzeptuelle Zeichnung, die Verarbeitung zum Dechiffrieren eines Chiffretextes darstellt, der auf die in **Fig. 18** gezeigte Weise chiffriert ist.

[0200] Eine Verarbeitung wird in diesem Fall grundsätzlich umgekehrt zu der Verarbeitung von **Fig. 18** durchgeführt. Weiter wird in einem Fall, in dem ein Chiffretext  $C$  länger als eine Größe des Registers 6 ist, eine Verarbeitung gekettet mit einem unmittelbar vorangehenden Chiffretextblock  $C_i$  als ein Anfangswert zu einem Zeitpunkt, zu dem der Chiffretext  $C$  die Größe des Registers 6 überschreitet.

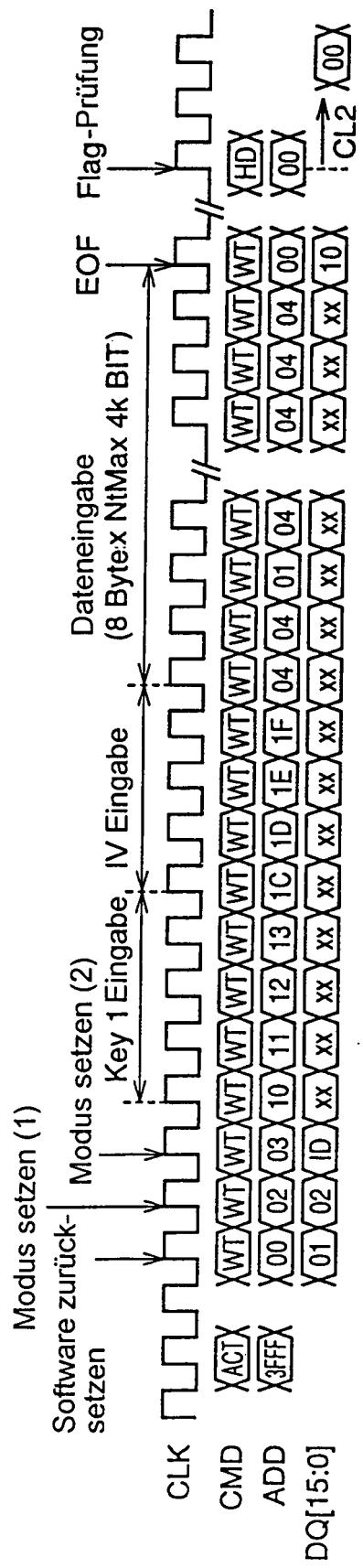

[0201] **Fig. 20** ist ein Zeitablaufdiagramm zum Beschreiben der in **Fig. 8** beschriebenen Verarbeitung, wenn verschiedene Arten von Verschlüsselungsmodi vorhanden sind.

[0202] Ein charakteristischer Punkt in **Fig. 20**, der sich von einem gewöhnlichen DRAM im Zugriff auf das Register 6 unterscheidet, ist der, daß eine Verarbeitung durchgeführt wird, vorausgesetzt, daß eine Buslänge 1 ist, ohne Rücksicht auf das Setzen in dem Modusregister, das in den Speicherabschnitt 4 gesetzt ist.

[0203] In Hinblick auf die anderen Punkte kann ein Zugriff auf ein Register zu dem gleichen Zeitpunkt und in der gleichen Sequenz wie in einem DRAM durchgeführt werden.

[0204] Bei dem in **Fig. 20** gezeigten Beispiel ist ein Fall gezeigt, in dem ein Adressraum zum Zugriff auf das Steuerregister 6 gleich  $X = h3FFF$  ist.

[0205] Auf solche Weise wird, nachdem eine Adresse, auf die zuzugreifen ist, spezifiziert ist, ein Softwarerücksetzen zuerst durchgeführt. Darauf folgend wird das Setzen durchgeführt, ob DES-56 oder CBC-Modus zum Beispiel ausgewählt ist, als ein Kryptosystem mit geheimem Schlüssel in einer ersten Moduseinstellung.

[0206] Infolge wird eine Tätigkeit als eine zweite Moduseinstellung durchgeführt, wie eine Einstellung eines Verschlüsselungsmodus, Rücksetzen eines Adresszählers eines Registers oder Bezeichnung, ob oder nicht ein Laden eines Anfangswertes durchgeführt wird, oder andere.

[0207] Weiter in Reihenfolge wird ein kryptografischer Schlüssel Keyl eingegeben, und ein Anfangswert  $IV$  wird ausgegeben.

[0208] Noch weiter in Reihenfolge wird ein einfacher Text mit 8 Byte als eine Einheit eingegeben, und wenn die Dateneingabe beendet ist, wird ein Dateiendsignal EOF eingegeben. Danach wird das Flag geprüft zum Bestätigen, ob oder nicht die Logikschaltung 8 während Verarbeitung ist.

[Details des normalen Betriebes]

[0209] **Fig. 21** ist ein Zeitablaufdiagramm zum Beschreiben des Betriebes, wenn Daten auf die gleiche

Seite im Schreibzugriff des normalen Modus geschrieben werden.

[0210] Es sei angenommen, daß in **Fig. 21** ein externes Taktsignal Ext.CLK zum Beispiel 100 MHz hat.

[0211] Weiterhin ist ein interner Takt ClkM zur Benutzung bei dem Betrieb des Speicherabschnittes **4** von 100 MHz synchron zu dem externen Taktsignal Ext.CLK.

[0212] Andererseits wird ein an die Logikschaltung **8** geliefertes Taktsignal clkL durch Frequenzteilen des externen Taktsignals Ext.CLK um zwei in der internen Takterzeugerschaltung **7** erzeugt.

[0213] Daher wird angenommen, daß eine Frequenz des internen Taktsignals clkL zum Beispiel 50 MHz beträgt.

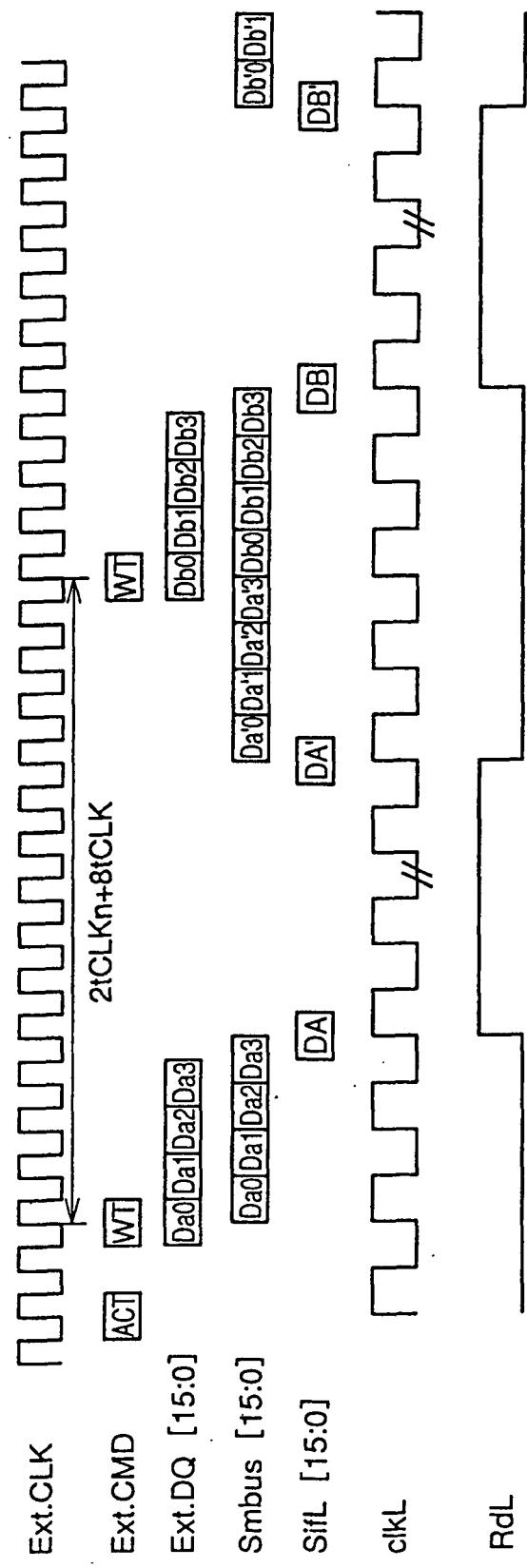

[0214] **Fig. 21** stellt einen Fall dar, in dem kontinuierlich gegebene Schreibbefehle WT an Adressen auf der gleichen Seite in dem normalen Schreiben ausgegeben werden.

[0215] In **Fig. 21** ist ein Signal Ext.DQ [15:0] Daten von einer 16 Bit-Wortkonfiguration und werden an einen Daten-I/O-Anschluß **14** des Speicherabschnitts **4** gegeben.

[0216] Ein Signal Smbus [15:0] ist Daten auf einem internen Speicherdatenbus, der den Speicherabschnitt **4** und die Logikschaltung **8** dazwischen verbindet, wie in **Fig. 1** gezeigt ist.

[0217] Ein Signal SifL [15:0] bezeichnet Daten in der internen Schnittstelle **9** und dem Register **6** zum Durchführen von Eingeben/Ausgeben von Daten auf einem internen Bus mbus oder der Logikschaltung **8**.

[0218] Das heißt, 16 Bit von Daten, die von dem Daten-I/O-Anschluß **14** durch das Register **6** und die interne Schnittstelle **9** gegeben sind, werden an die Logikschaltung **8** nach einer Seriell-Parallelumwandlung in 64 Bit-Daten gegeben, während Daten nach Verschlüsselung, die von der Logikschaltung **8** ausgegeben werden, parallel-seriell umwandelt werden in Daten jeweils von 16 Bit und danach an den DRAM **4** gegeben.

[0219] Ein Signal RdL ist ein Signal, das anzeigt, daß die Logikschaltung **8** die Verarbeitung gestartet hat und sich in einer Verarbeitungsperiode befindet, worin es in einer Periode, in der das Signal auf dem H-Pegel ist, anzeigt, daß die Logikschaltung **8** in Betrieb ist.

[0220] Bezug nehmend auf **Fig. 21** müssen Daten, die extern durch den Daten-I/O-Anschluß **14** gegeben sind, gerade viermal geschrieben werden, da die Verschlüsselung mit 64 Bit als eine Einheit durchgeführt wird. Mit einer gegebenen Burstlänge von 4, wenn ein Schreibbefehl WT an die integrierte Halbleiterschaltungsvorrichtung **1** gegeben wird, werden dann Daten Da0 bis Da3 jeweils mit 16 Bit kontinuierlich von dem Daten-I/O-Anschluß **14** gegeben. Die Daten werden an die interne Schnittstelle **9** und das Register **6** durch den internen Bus Mbus gegeben, Daten von 64 Bit in der Länge werden in dem Register **6** gespeichert und danach werden die Daten an die Logikschaltung **8** als Daten DA zur Verschlüsse-

lung gegeben. Zur gleichen Zeit wie dieses geht das Signal RdL auf den H-Pegel zum Starten des Betriebes der Logikschaltung **8**.

[0221] Wenn Daten Da' als ein Resultat der Verschlüsselung in der Logikschaltung **8** an das Register **6** ausgegeben werden, geht das Signal RdL auf den L-Pegel zum Beenden des Betriebes der Logikschaltung **8**.

[0222] Die an das Register **6** ausgegebenen Daten Da' sind parallelseriell umgewandelt und auf den internen Bus mbus von der internen Schnittstelle **9** als Daten Da'0 bis Da'3 jeweils von 16 Bit ausgegeben, die in den Speicherabschnitt **4** zu schreiben sind.

[0223] Ein Schreibbefehl WT, der danach gegeben wird, ist nötig zum Eingeben mit einem Intervall von  $2t\text{CLK} \times m + 8t\text{CLK}$  oder länger nach dem ersten Schreibbefehl, worin n die Zahl der Zyklen des internen Taktsignals clkL bedeutet, die für die Verschlüsselung von Daten von 64 Bit notwendig sind.

[0224] **Fig. 22** ist ein Zeitallaufdiagramm zum Beschreiben des Betriebes, wenn 64 Bit-Daten auf eine unterschiedliche Seite in dem normalen Modus geschrieben werden.

[0225] In diesem Fall wird ein Schreiben-mit-Autovorladenbefehl als ein Schreibbefehl gegeben, worin eine Vorladetätigkeit automatisch durchgeführt wird, nachdem verschlüsselte Daten in den Speicherabschnitt **4** (DRAM) geschrieben sind.

[0226] Nachdem die Vorladetätigkeit beendet ist, wird ein Akt-Befehl ACT wiedergegeben, und danach wird eine ähnliche Verarbeitung wiederholt.

[0227] Wenn hierin ein einfacher Vorladebefehl an die integrierte Halbleiterschaltungsvorrichtung **1** anstelle des Schreiben-mit-Autovorladenbefehl gegeben wird, wird Verarbeitung wie unten beschrieben durchgeführt.

[0228] Das heißt, wenn ein Vorladebefehl PRE eingegeben wird, bevor verschlüsselte Daten in den Speicherabschnitt **4** geschrieben werden, wird das Vorladen automatisch nach Beendigung einer Schreibtätigkeit gestartet.

[0229] Wenn andererseits das Schreiben beendet ist, wird die Vorladetätigkeit bald zu irgendeiner Zeit gestartet.

[0230] **Fig. 23** ist ein Zeitallaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus durchgeführt wird.

[0231] In **Fig. 23** wird ebenfalls angenommen, daß das externe Taktsignal Ext.CLK zum Beispiel 100 MHz ist.

[0232] Daher wird angenommen, daß das an den Speicherabschnitt **4** gegebene interne Taktsignal ClkM ebenfalls 100 MHz ist, und daß das an die Logikschaltung **8** gegebene Taktsignal clkL gleich 50 MHz ist.

[0233] Bezug nehmend auf **Fig. 23**, wenn ein Lesebefehl RD gegeben wird, werden Lesedaten von dem Speicherabschnitt **4** auf den internen Datenbus mbus als Daten Da0 bis Da3 jeweils in 16 Bit in Reihenfolge

ausgegeben.

[0234] Daten DA von 64 Bit sind seriell-parallel umgewandelt durch die interne Schnittstelle **9** und das Register **6**. Die Daten DA werden in der Logikschaltung **8** chiffriert. Daten DA' nach der Verschlüsselung werden auf den internen Datenbus mbus durch das Register **6** und die interne Schnittstelle **9** als Daten Da'0 bis Da'3 jeweils von 16 Bit nach parallel-serieller Umwandlung ausgegeben. Die Daten Da'0 bis Da'3 nach der Seriell-Parallelwandler werden in den Speicherabschnitt **4** geschrieben.

[0235] Eine Periode von der Zeit, zu der ein erster Lesebefehl RD gegeben wird, bis zu dem nächsten Lesebefehl  $RD = 2tCLK \times n + 8tCLK$  oder länger ähnlich der Schreibtätigkeit; der nächste Lesebefehl muß an solch einem Intervall oder länger eingegeben werden.

[0236] **Fig. 24** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Lesezugriff auf eine andere Seite unter der gleichen Bedingung wie in **Fig. 22** durchgeführt wird.

[0237] In diesem Fall ist die Verarbeitung ähnlich zu dem Fall der in **Fig. 22** gezeigten Schreibtätigkeit, und Daten, die mit der Verschlüsselung fertig sind, werden in den Speicherabschnitt **4** geschrieben, was von einem automatischen Vorladen gefolgt wird.

[0238] **Fig. 25** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes der integrierten Halbleiterorschaltungsvorrichtung **1**, wenn ein externes Taktsignal Ext.CLK gleich 50 MHz ist.

[0239] In **Fig. 25** ist ein Fall gezeigt, in dem Schreibzugriff auf Adressen auf der gleichen Seite in dem normalen Modus durchgeführt wird.

[0240] In diesem Fall ist das interne Taktsignal clkM zur Benutzung in dem Speicherabschnitt **4**, das von der internen Takterzeugerschaltung **7** erzeugt ist, von einer Frequenz von 100 MHz, die durch Multiplizieren des externen Taktsignals Ext.CLK zur Umwandlung erhalten wird.

[0241] Andererseits ist das interne Taktsignal clkK, das an die Logikschaltung **8** gegeben wird, von 50 MHz synchron zu dem externen Taktsignal.

[0242] Bei dem Betrieb von **Fig. 25** werden ein Schreibbefehl WT und andere von außen mit einer Frequenz von 50 MHz synchron zu einer externen Taktfrequenz eingegeben, während ein Lesebetrieb von dem Speicherabschnitt **4** und ein Schreibbetrieb in den Speicherabschnitt **4** eines Verschlüsselungsresultats mit 100 MHz synchron zu dem internen Taktsignal clkM verarbeitet werden.

[0243] In diesem Fall wird eine Periode von  $tCLK \times n + tCLK$  benötigt zum Sicherstellen einer Periode vom Ausgeben des ersten Schreibbefehls WT bis zu der Zeit des Ausgebens des nächsten Schreibbefehls WT.

[0244] **Fig. 26** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebes, wenn Schreibzugriff auf eine andere Seite in dem normalen Modus in einem Fall durchgeführt wird, in dem das externe Taktsignal ext.CLK von 50 MHz ist.

[0245] In diesem Fall wird ebenfalls ein Schreiben-mit-Autovorladenbefehl als Schreibbefehl gegeben.

[0246] Daher wird eine Vorladetätigkeit durchgeführt, nachdem Daten DA', die in der Logikschaltung **8** verschlüsselt worden sind, parallel-seriell gewandelt sind und in den Speicherabschnitt **4** als Daten Da'0 bis Da'3 jeweils von 16 Bit geschrieben sind.

[0247] Eine Periode von der Zeit, zu der ein erster Zeitschreibbefehl WT gegeben wird, bis zu dem nächsten Schreibbefehl WT gegeben wird, wird gleich oder länger als eine Periode von  $tCLK \times n + 8tCLK$  benötigt.

[0248] **Fig. 27** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebs, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus unter den gleichen Bedingungen in dem externen Taktsignal ext.CLK und den internen Taktsignalen clkM und clkL wie in **Fig. 25** und 26 durchgeführt wird.

[0249] Weiterhin ist **Fig. 28** ein Zeitablaufdiagramm zum Beschreiben eines Betriebs, wenn Lesezugriff auf eine unterschiedliche Seite in dem normalen Modus unter den gleichen Bedingungen wie für **Fig. 27** durchgeführt wird.

[0250] In **Fig. 27** und 28 werden ebenfalls mit Ausnahme, daß Befehle und andere synchron zu dem externen Taktsignal Ext.CLK gegeben werden, Tätigkeiten grundsätzlich ähnlich zu jenen in **Fig. 23** und 24 durchgeführt.

[0251] In **Fig. 27** muß jedoch eine Periode von der Zeit, wenn ein erster Zeitlesebefehl RD gegeben wird, bis zu der nächsten Zeit, zu der der Lesebefehl RD gegeben wird, gleich oder länger als  $tCLK \times n + 4tCLK$  sein, und in **Fig. 28** muß die Periode gleich oder länger als  $tCLK \times n + 6tCLK$  sein.

[0252] **Fig. 29** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebs, wenn das externe Taktsignal Ext.CLK von 25 MHz ist und eine Frequenzmultiplikationstätigkeit in der internen Takterzeugerschaltung **7** mit dem Resultat durchgeführt wird, daß das an den Speicherabschnitt **4** gegebene interne Taktsignal clkM zu 100 MHz umgewandelt ist und das an die Logikschaltung **8** gegebene interne Taktsignal clkL zu 50 MHz umgewandelt ist.

[0253] Externe Befehle werden synchron zu dem externen Taktsignal Ext.CLK ausgegeben, und interne Tätigkeiten werden ebenfalls synchron zu dem externen Taktsignal ext.CLK durchgeführt.

[0254] In **Fig. 29** ist ein Betrieb in einem Fall gezeigt, in dem Schreibzugriff auf der gleichen Seite in dem normalen Modus durchgeführt wird.

[0255] In diesem Fall muß eine Periode von der Zeit, zu der ein erster Zeitschreibbefehl WT gegeben wird, bis dann, wenn der nächste Schreibbefehl gegeben wird, gleich oder länger als  $tCLK \times n/2 + 4tCLK$  sein.

[0256] **Fig. 30** ist ein Zeitablaufdiagramm zum Beschreiben eines Betriebs, wenn Lesezugriff auf die gleiche Seite in dem normalen Modus unter Bedingungen durchgeführt wird, daß das gleiche Taktsig-

nal wie in **Fig. 29** benutzt wird.

[0257] Andererseits ist **Fig. 31** ein Zeitablaufdiagramm zum Beschreiben eines Betriebs, wenn Lesezugriff auf eine andere Seite in dem normalen Modus unter Bedingungen durchgeführt wird, daß das gleiche Taktsignal wie in **Fig. 30** benutzt wird.

[0258] Während in dem Fall von **Fig. 30** eine Periode vom Ausgeben des ersten Zeitlesebefehls RD bis zu der Ausgabe des nächsten Lesebefehls RD gleich oder länger als  $t_{CLK} \times n/2 + 2t_{CLK}$  sein muß, muß in dem Fall von **Fig. 31** die Periode gleich oder länger als  $t_{CLK} \times n/2 + 3,5t_{CLK}$  sein.

[0259] In dem oben beschriebenen normalen Modusbetrieb in dem Fall des Zugriffs zu der gleichen Seite, wenn Verschlüsselung beendet ist (einschließlich einer Schreibtätigkeit eines Verschlüsselungsresultats in den Speicherabschnitt 4) sowohl bei der Lese- als auch Schreibtätigkeit, ist es notwendig, daß ein Stoppbefehl nach Eingeben eines Vorladebefehls eingegeben wird. Wenn ein Stoppbefehl nach Bestätigung eingegeben wird, daß die Verschlüsselung fertig ist, und zusätzlich keine Unterbrechung der Auffrischung während der Verschlüsselung auftritt, dann wird keine Bestätigung eines Flags FL in der in **Fig. 8** beschriebenen Verarbeitung benötigt.

[0260] Wenn ein Stoppbefehl in einem Zustand einer offenen Seite eingegeben wird, wird Vorladen automatisch nach Beendigung der Verschlüsselung durchgeführt (einschließlich einer Schreibtätigkeit eines Verschlüsselungsresultates in den Speicherabschnitt 4), worin eine Bestätigung eines Flags benötigt wird.

[0261] In jedem Fall wird die Beendigung der Verschlüsselung zu der Außenseite benachrichtigt durch Setzen von "0" des Flags, wenn die Verschlüsselung fertig ist.

[0262] Wenn eine Unterbrechung befohlen wird und ein Auffrischbefehl während der Verschlüsselung oder während des Schreibens eines Verschlüsselungsresultats in den Speicherabschnitt 4 gegeben wird, werden die Befehle angenommen, und die Zahl der angenommenen Auffrischbefehle wird gezählt. Das heißt, ein getrennter Zähler ist vorgesehen. Dann werden, nachdem eine Tätigkeit der Verschlüsselung beendet ist oder nachdem eine Schreibtätigkeit des Verschlüsselungsresultats in den Speicherabschnitt 4 beendet ist, Auffrischbefehle an den Speicherabschnitt 4 mit der gleichen Anzahl der gezählten Anzahl in Intervallen einer richtigen Zyklusperiode gegeben.

[0263] In diesem Fall müssen die Auffrischtätigkeiten nur durchgeführt werden, bis der Auffrischzähler in dem Speicherabschnitt 4 zum Anzeigen von 0 in dem Zählerwert kommt, während der Zähler heruntergezählt wird.

[0264] Im allgemeinen wird ein Auffrischen eines CBR-Befehls durchgeführt, wenn ein Autoauffrischbefehl gegeben wird oder wenn der Speicherabschnitt 4 ein DRAM in dem EDU-Modus ist. Daher ist eine Adresse, an der Auffrischen durchgeführt wird,

eine Adresse, die von dem getrennten Auffrischzähler erzeugt wird. Nachdem die Auffrischtätigkeiten beendet sind, wird das in **Fig. 8** beschriebene Flag FL von "1" auf "0" geändert, wobei die Beendigung der Auffrischtätigkeiten als Beendigung der Verschlüsselung betrachtet werden.

[0265] Es sei angemerkt, daß nicht nur in dem Blockmodus sondern auch in dem Puffermodus Tätigkeiten grundsätzlich ähnlich zu den in dem Fall des normalen Modus sind, wie oben beschrieben wurde.

[0266] Was sich unterscheidet ist das, daß kontinuierliche Dateneingaben automatisch in der integrierten Halbleitervorrichtung 1 mit einer Startadresse als Referenz erzeugt werden.

[0267] Weiterhin wird in dem Puffermodus eines Falles, in dem der Speicherabschnitt 4 eine Mehrzahl von Bänken enthält, ein Puffer-ID, das einer Bank unterschiedlich von einer Bank zugeordnet ist, auf der das Lesen durchgeführt wird, ausgewählt und ein Verschlüsselungsresultat wird in das Puffergebiet geschrieben, das durch das ID zugeordnet ist.

[0268] Die Eingabe einer Startadresse bedeutet zum Beispiel das Spezifizieren einer Zeilenadresse, wenn ein ACT-Befehl eingegeben wird, als ein Zugriff auf einen gewöhnlichen SDRAM, und dann Spezifizieren einer Spaltenadresse durch Eingeben derselben, wenn Blindlesen oder Blindschreiben durchgeführt wird.

[0269] Selbst wenn eine Burstlänge 1 oder länger ist, ist die Eingabe einer Startadresse für eine Adresse, zu der eingegeben wird, zuerst in einem Blindspaltenzugriff durchgeführt.

[0270] In dem Blockmodus und dem Puffermodus wird, nachdem ein Verschlüsselungsresultat vollständig in dem Speicherabschnitt 4 gespeichert ist und somit die Verschlüsselung vollständig ist, eine Bank, die aktiviert worden ist, automatisch vorgeladen.

[0271] In dem Fall werden ein Vorladebefehl und ein Autovorladebefehl, die während der Verschlüsselung eingegeben sind, ignoriert.

[0272] Weiterhin wird in dem Blockmodus und dem Puffermodus, sobald eine Startadresse gegeben ist, eine Spaltenzugriffstätigkeit ignoriert, selbst wenn der Befehl danach extern gegeben wird.

[0273] Weiterhin wird in dem Blockmodus und dem Puffermodus die Verschlüsselung automatisch über eine Blocklänge von der Startadresse durchgeführt. Zu dieser Zeit können die Tätigkeiten von nicht nur der Erhöhung einer Blocklänge sondern auch einer Verringerung einer Blocklänge möglich sein durch Datensetzen in das Register 6.

[0274] Nebenbei, in dem Blockmodus und dem Puffermodus kann Datenschreiben als solches nicht nur in einem sequentiellen Modus sondern auch in einem verschachtelten Modus wie in einem SDRAM möglich sein.

#### [Beispiel 2]

[0275] **Fig. 32** ist ein konzeptuelles Blockschaltbild,

das einen Weg darstellt, wie die integrierte Halbleiterschaltungsvorrichtung 1 der vorliegenden Erfindung und ein Mikroprozessor 90 verbunden sind.

[0276] Der Mikrocomputer 90 enthält: einen CPU-Kern 94, eine Speichersteuerung 98 und eine externe Busschnittstellenschaltung 100, worin die Bestandteile miteinander durch einen internen Bus 102 verbunden sind. Der CPU-Kern 94 ist mit einem Flash-Speicher 106 verbunden, in dem Daten, die zu chiffrieren oder zu dechiffrieren sind, durch eine serielle Schnittstelle 104 gespeichert werden.

[0277] Die externe Schnittstellenschaltung 100 gibt ein Steuersignal, ein Adresssignal und Daten an die integrierte Halbleiterschaltungsvorrichtung 1 gemäß den Befehlen von dem CPU-Kern 94 aus.

[0278] **Fig.** 32 zeigt ein System, das für einen Betrieb im normalen Modus geeignet ist.

[0279] Das heißt, solch eine Konfiguration ist geeignet für ein System, in dem in dem normalen Modus die zu chiffrierenden oder zu dechiffrierenden Daten an den Mikrocomputer 90 von einer externen Einrichtung gegeben werden, die nicht der Speicherabschnitt 4 der integrierten Halbleiterspeichervorrichtung 1 ist, zum Beispiel der Flash-Speicher 106.

[0280] Wenn Daten zeitweilig in dem Speicherabschnitt 4 gespeichert sind, die durch den Mikrocomputer 90 übertragen werden, werden die Daten in dem Speicherabschnitt 4 gehalten, nachdem sie automatisch zu einem kryptografischen Verarbeitungsresultat umgewandelt sind. Folglich kann die Zahl der Zugriffe auf den Speicherabschnitt 4, die für die kryptografische Verarbeitung notwendig ist, verringert werden.

[0281] **Fig.** 33 ist ein konzeptuelles Blockschaltbild, das einen anderen Weg darstellt, wie die integrierte Halbleiterschaltungsvorrichtung 1 der vorliegenden Erfindung und der Mikroprozessor 90 verbunden sind.

[0282] Der Mikrocomputer 90 enthält: einen CPU-Kern 94; einen Cache-Speicher 96; eine Speichersteuerung 98; und eine externe Busschnittstellenschaltung 100, worin die Bestandteile miteinander durch einen internen Bus 102 verbunden sind. Die externe Busschnittstellenschaltung 100 gibt ein Steuersignal, ein Adresssignal und Daten an die integrierte Halbleiterschaltungsvorrichtung 1 gemäß einem Befehl von dem CPU-Kern 94 aus. Daher sind die externe Busschnittstellenschaltung 100 und ein integrierter Logik-DRAM 92 miteinander durch einen Steuersignalbus verbunden, der Steuersignale wie Signale /RAS, /CAS, ..., /CS überträgt, durch einen Adressbus, der eine Adresse ADD überträgt, und durch einen Datenbus, der Daten DATA überträgt.

[0283] Zum Steuern der integrierten Halbleiterschaltungsvorrichtung 1 in solch einem System muß manchmal über Software nachgedacht werden, die auf dem Mikrocomputer 90 läuft.

[0284] **Fig.** 34 ist ein Flußdiagramm zum Beschreiben der Steuerung der integrierten Halbleiterschaltungsvorrichtung 1.

[0285] Bezug nehmend auf **Fig.** 34 wird zuerst in einem Schritt S1 eine Adresse eines Logiksteuergebietes in einem reservierten Gebiet spezifiziert. Das heißt, dadurch wird ein Programm nicht einem Adressraum für Befehlssteuerung einer Logikschaltung zugeordnet. Als ein Verfahren zum Verhindern, daß das Gebiet zugeordnet wird, ist eines beispielhaft, bei dem ein Logiksteuergebiet als ein reserviertes Gebiet geschützt wird, indem eine Funktion eines OS (Betriebssystem) benutzt wird.

[0286] Eine besondere Aufmerksamkeit muß selbst auf einen Einschaltzeitpunkt des OS gerichtet werden, so daß Kernroutinen selbst, die ein Herz eines OS sind, die grundlegende Steuerung des Systems wie Speicherverwaltung, Unterbrechungsverwaltung und Zwischenprozeßkommunikation durchführen, nicht dem Logiksteuergebiet zugeordnet werden. Folglich wird ein reserviertes Gebiet auf der Seite des OS mit spezieller Aufmerksamkeit spezifiziert, daß die Kernroutinen selbst nicht einem Logiksteuergebiet zugeordnet werden.

[0287] Dann werden in Schritt S2 mindestens ein Logiksteuergebiet und ein Gebiet, in dem zu chiffrierende oder zu dechiffrierende Daten gespeichert werden, als ein Gebiet ungeeignet für Cache 4a in einem System mit einem Daten-Cache spezifiziert, wie in **Fig.** 33 gezeigt ist.