(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7479850号

(P7479850)

(45)発行日 令和6年5月9日(2024.5.9)

(24)登録日 令和6年4月26日(2024.4.26)

(51)国際特許分類

|        |                  |     |        |        |   |

|--------|------------------|-----|--------|--------|---|

| H 01 L | 27/146 (2006.01) | F I | H 01 L | 27/146 | D |

| H 04 N | 25/70 (2023.01)  |     | H 04 N | 25/70  |   |

| H 04 N | 25/76 (2023.01)  |     | H 04 N | 25/76  |   |

請求項の数 11 (全21頁)

|                   |                                  |          |                                                                                      |

|-------------------|----------------------------------|----------|--------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2020-1233(P2020-1233)          | (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路12<br>9 |

| (22)出願日           | 令和2年1月8日(2020.1.8)               |          |                                                                                      |

| (65)公開番号          | 特開2020-113762(P2020-113762<br>A) |          |                                                                                      |

| (43)公開日           | 令和2年7月27日(2020.7.27)             |          |                                                                                      |

| 審査請求日             | 令和4年12月21日(2022.12.21)           |          |                                                                                      |

| (31)優先権主張番号       | 10-2019-0003842                  |          |                                                                                      |

| (32)優先日           | 平成31年1月11日(2019.1.11)            |          |                                                                                      |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                           | (74)代理人  | 110000051<br>弁理士法人共生国際特許事務所                                                          |

|                   |                                  | (72)発明者  | 李允基<br>大韓民国, 16677, ギョンギ-ド,<br>スウォン-シ, ヨントン-グ, サムスン<br>最終頁に続く                        |

(54)【発明の名称】 イメージセンサー

## (57)【特許請求の範囲】

## 【請求項1】

第1領域及び第2領域を含み、互いに対向する第1面及び第2面を有する半導体層と、前記半導体層の前記第1領域及び前記第2領域内に配置されて、前記第1領域及び前記第2領域内に提供された複数のピクセルを定義する素子分離膜と、

前記半導体層の前記第1領域の前記第1面上に、前記素子分離膜と重畳するように配置された第1グリッドパターンと、

前記半導体層の前記第2領域の前記第1面上に配置された遮光パターンと、を含み、

前記第1グリッドパターンの上面は第1レベルに位置し、前記遮光パターンの上面は第2レベルに位置し、前記第1レベルは前記第2レベルよりも低く、前記第1レベル及び前記第2レベルは前記半導体層の前記第1面に対して定義され、

前記第1グリッドパターンの厚さは、前記遮光パターンの厚さよりも薄く、

前記第1グリッドパターン上の第2グリッドパターンをさらに含み、

前記第1グリッドパターンは、金属及び金属窒化膜の中の少なくとも1つを含み、

前記第2グリッドパターンは、低屈折物質を含み、

前記遮光パターンは、金属物質を含む単一層からなり、

前記半導体層は、第3領域をさらに含み、

前記半導体層の前記第3領域上のパッドをさらに含み、

前記第1グリッドパターンは、前記遮光パターンを通じて前記パッドに連結されることを特徴とするイメージセンサー。

**【請求項 2】**

前記第1グリッドパターンは、前記第2領域上に延長されて前記遮光パターンの側面を覆い、前記遮光パターンの上面を露出させることを特徴とする請求項1に記載のイメージセンサー。

**【請求項 3】**

前記第1グリッドパターンは、前記第2領域上に延長されて前記遮光パターンの側面及び上面を覆うことを特徴とする請求項1に記載のイメージセンサー。

**【請求項 4】**

前記第1グリッドパターンの側面と前記第2グリッドパターンの側面とが整列されたことを特徴とする請求項1に記載のイメージセンサー。

**【請求項 5】**

前記複数のピクセルは、前記半導体層の前記第1領域内に提供された第1ピクセル及び前記半導体層の前記第2領域内に提供された第2ピクセルを含み、

前記イメージセンサーは、

前記第1ピクセル内の第1光電変換素子と、

前記第2ピクセル内の第2光電変換素子と、をさらに含み、

前記第1グリッドパターンは、前記第1光電変換素子を露出させ、

前記遮光パターンは、前記第2光電変換素子を覆うことを特徴とする請求項1に記載のイメージセンサー。

**【請求項 6】**

前記複数のピクセルは、前記半導体層の前記第1領域内に提供された第1ピクセル及び前記半導体層の前記第2領域内に提供された第2ピクセルを含み、

前記イメージセンサーは、

前記第1ピクセル内の一対の第1光電変換素子と、

前記第2ピクセル内の一対の第2光電変換素子と、

前記半導体層の前記第1面上に配置され、前記一対の第1光電変換素子を覆うマイクロレンズと、をさらに含むことを特徴とする請求項1に記載のイメージセンサー。

**【請求項 7】**

前記素子分離膜は、前記半導体層を貫通して前記半導体層の前記第1面及び前記第2面に接触することを特徴とする請求項1に記載のイメージセンサー。

**【請求項 8】**

前記素子分離膜は、前記半導体層の前記第1面に接触し、前記半導体層の前記第2面から離隔されたことを特徴とする請求項1に記載のイメージセンサー。

**【請求項 9】**

前記第1グリッドパターンの物質は、前記遮光パターンの物質とは異なることを特徴とする請求項1に記載のイメージセンサー。

**【請求項 10】**

前記複数のピクセルは、前記半導体層の前記第1領域内の第1ピクセル及び前記半導体層の前記第2領域内の第2ピクセルを含み、

前記イメージセンサーは、

前記第1ピクセル上のカラーフィルターと、

前記第2領域上のカラーフィルター膜と、

前記カラーフィルター上のマイクロレンズと、を含み、

前記マイクロレンズは、前記カラーフィルター膜を露出させることを特徴とする請求項1に記載のイメージセンサー。

**【請求項 11】**

第1領域及び第2領域を含む半導体層と、

前記半導体層の前記第1領域及び前記第2領域内に配置されて、前記第1領域及び前記第2領域内に提供された複数のピクセルを定義する素子分離膜と、

前記半導体層の前記第1領域上に、前記素子分離膜と重畳するように配置されたグリッ

10

20

30

40

50

ドパターンと、

前記半導体層の前記第2領域上の遮光構造体と、を含み、

前記グリッドパターンは、

前記半導体層上に配置されて前記遮光構造体の側面を覆う第1グリッドパターンと、

前記第1グリッドパターンを覆う第2グリッドパターンと、を含み、

前記第1グリッドパターンは、前記遮光構造体の側面と前記第2グリッドパターンとの間に挟まれ、

前記第1グリッドパターンの厚さは、前記遮光構造体の厚さよりも薄く、

前記遮光構造体は、前記半導体層の前記第2領域上に積層された遮光パターン、導電パターン、及び有機パターンを含み、

前記第1グリッドパターンは、前記導電パターンに連結され、

前記第2グリッドパターンは、前記有機パターンに連結され、

前記半導体層は、第3領域をさらに含み、

前記半導体層の前記第3領域上のパッドをさらに含み、

前記第1グリッドパターンは、前記遮光パターンを通じて前記パッドに連結されることを特徴とするイメージセンサー。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、イメージセンサーに関し、より詳しくはイメージ特性がより改善されたイメージセンサーに関する。

【背景技術】

【0002】

イメージセンサーは、光学イメージ(optical image)を電気信号に変換する半導体素子である。イメージセンサーは、CCD(charge coupled device)型及びCMOS(complementary metal oxide semiconductor)型に分類される。CMOS型イメージセンサーはCIS(CMOS image sensor)と略称される。CISは2次元的に配列された複数のピクセルを具備する。ピクセルの各々はフォトダイオード(photo diode、PD)を含む。フォトダイオードは入射された光を電気信号に変換する役割を果たす。

【先行技術文献】

【特許文献】

【0003】

【文献】米国特許第9947714号明細書

【文献】米国特許第10074680号明細書

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明は、上記従来技術に鑑みてなされたものであって、本発明の目的は、イメージ特性がより改善されたイメージセンサーを提供することにある。

【課題を解決するための手段】

【0005】

上記目的を達成するためになされた本発明の一態様によるイメージセンサーは、第1領域及び第2領域を含み、互いに対向する第1面及び第2面を有する半導体層と、前記半導体層内に配置されて、ピクセルを定義する素子分離膜と、前記半導体層の前記第1領域の前記第1面上に配置された第1グリッドパターンと、前記半導体層の前記第2領域の前記第1面上に配置された遮光パターンと、を含み、前記半導体層の前記第1面から前記第1グリッドパターンの上面は、前記半導体層の前記第1面から前記遮光パターンの上面よりも低いレベルに位置することを特徴とする。

【0006】

10

20

30

40

50

上記目的を達成するためになされた本発明の他の態様によるイメージセンサーは、第1領域及び前記第1領域周辺の第2領域を含む半導体層と、前記半導体層内に配置されて、ピクセルを定義する素子分離膜と、前記半導体層の前記第1領域上で前記素子分離膜に沿って延長され、第1パターンを含むグリッドパターンと、前記半導体層の前記第2領域上の遮光パターンと、を含み、前記第1パターンの厚さは前記遮光パターンの厚さよりも小さく、前記第1パターンは、前記遮光パターンの側面を覆うことを特徴とする。

【0007】

上記目的を達成するためになされた本発明のさらに他の態様によるイメージセンサーは、第1領域及び第2領域を含む半導体層と、前記半導体層内に配置されて、ピクセルを定義する素子分離膜と、前記半導体層の前記第1領域上のグリッドパターンと、前記半導体層の前記第2領域の上の遮光構造体と、を含み、前記グリッドパターンの厚さは、前記遮光構造体の厚さよりも薄いことを特徴とする。

10

【発明の効果】

【0008】

本発明によれば、グリッドパターンが遮光パターンの積層構造とは異なる積層構造を有するように形成される。グリッドパターンの第1パターンは金属物質を含むが、遮光パターンよりも薄く形成されることによって、静電気を外部へ放出させる通路の役割を果たしながら、光の吸収を最小化させることができる。グリッドパターンの第2パターンは、低屈折物質で形成され、カラーフィルターの縁に隣接して、入射される光を屈折させて該当ピクセルに入射させることができる。したがって、クロストーク (cross talk) が減少され、光効率が増大されたイメージセンサーを提供することができる。

20

【図面の簡単な説明】

【0009】

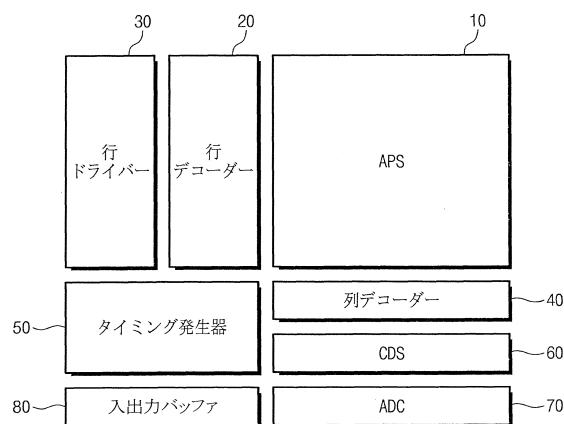

【図1】本発明の一実施形態によるイメージセンサーのブロック図である。

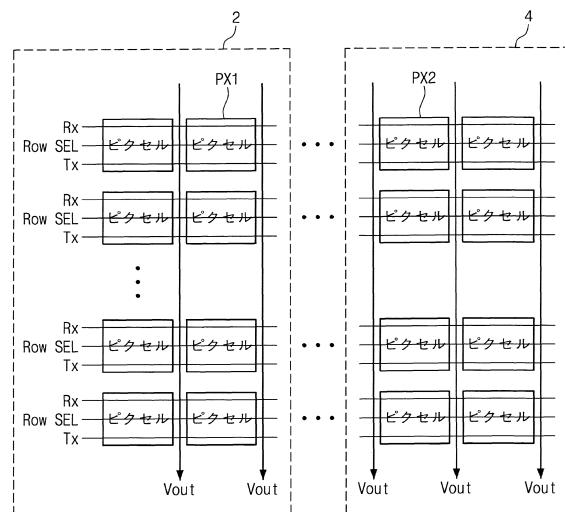

【図2】本発明の一実施形態によるイメージセンサーのセンサーリーの簡略な回路図である。

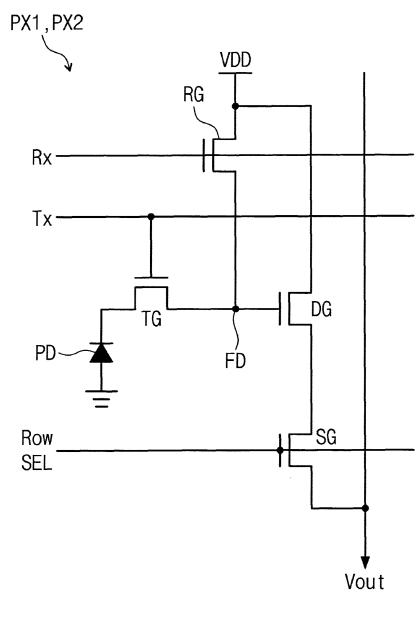

【図3】本発明の一実施形態によるイメージセンサーのピクセルを示す回路図である。

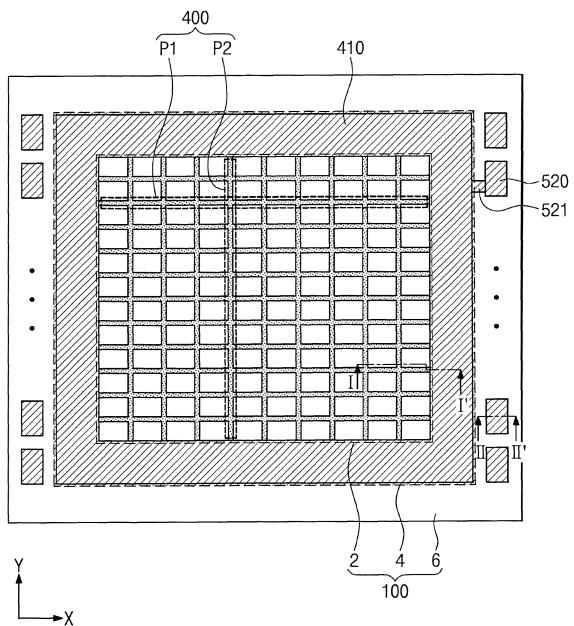

【図4】本発明の一実施形態によるイメージセンサーを示す平面図である。

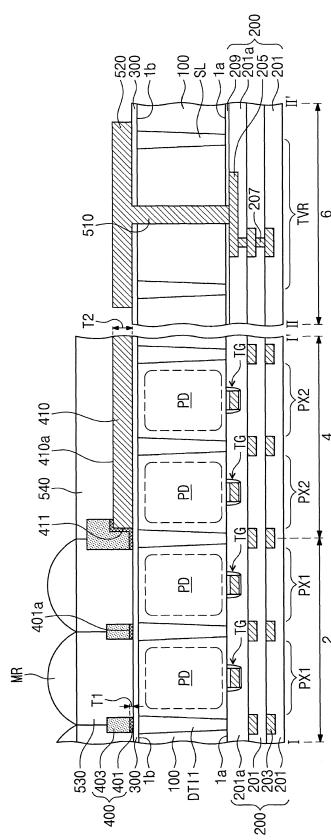

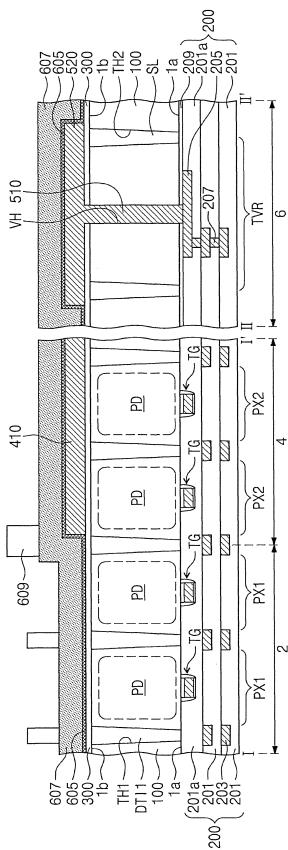

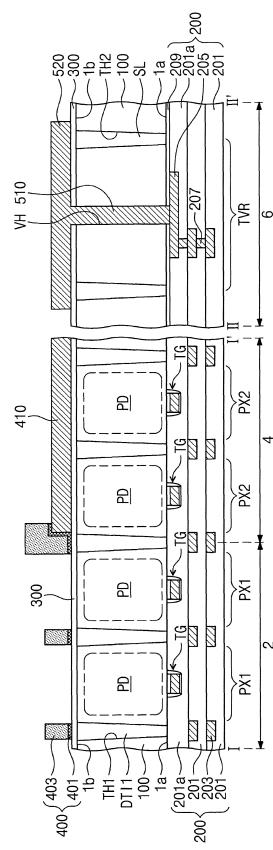

【図5】本発明の一実施形態によるイメージセンサーの一例を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

30

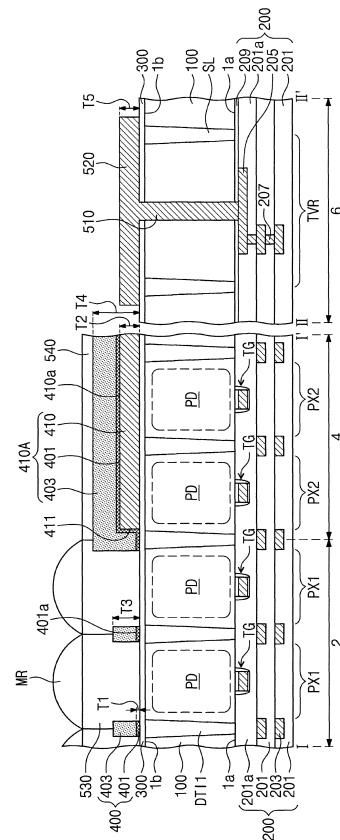

【図6】本発明の一実施形態によるイメージセンサーの他の例を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

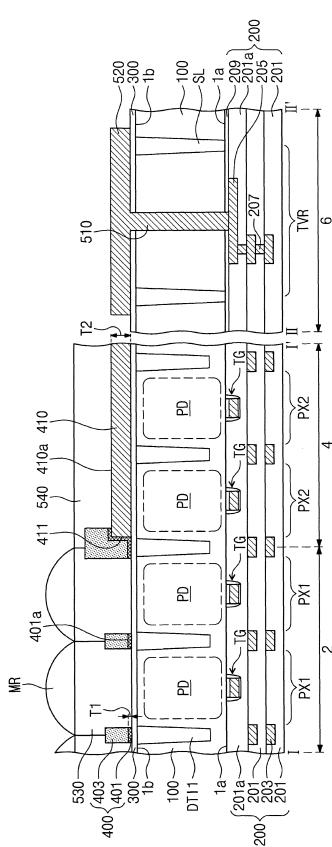

【図7】本発明の一実施形態によるイメージセンサーのさらに他の例を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

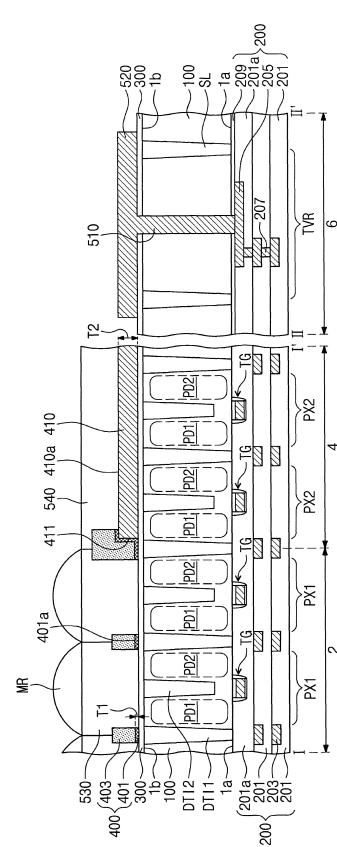

【図8】本発明の一実施形態によるイメージセンサーのその他の例を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

【図9】本発明の他の実施形態によるイメージセンサーを示す断面図である。

【図10】本発明の他の実施形態によるイメージセンサーを示す平面図である。

【図11A】本発明の一実施形態によるイメージセンサーの製造方法を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

40

【図11B】本発明の一実施形態によるイメージセンサーの製造方法を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

【図11C】本発明の一実施形態によるイメージセンサーの製造方法を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

【図11D】本発明の一実施形態によるイメージセンサーの製造方法を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

【発明を実施するための形態】

【0010】

図1は、本発明の一実施形態によるイメージセンサーのブロック図である。

【0011】

50

図2は、本発明の一実施形態によるイメージセンサーのセンサーリレイの簡略な回路図である。

【0012】

図1を参照すると、本発明の一実施形態によるイメージセンサーは、アクティブピクセルセンサーリレイ(Active Pixel Sensor(APS) Array)10、行デコーダー(row decoder)20、行ドライバー(row driver)30、列デコーダー(column decoder)40、タイミング発生器(timing generator)50、相関二重サンプラー(CDS:Correlated Double Sampler)60、アナログデジタルコンバーター(ADC:Analog to Digital Converter)70、及び入出力バッファ(I/O buffer)80を含む。

10

【0013】

APSアレイ10は、図2に示すように、光が入射される第1領域2及び光が入射されない第2領域4を含み、ピクセル(PX1、PX2)が2次元的に配列される。第1領域2及び第2領域4の各々は、第1ピクセルPX1及び第2ピクセルPX2を含む。第1領域2内に提供された第1ピクセルPX1は、入射光を電気的信号に変換する。第2領域4内に提供された第2ピクセルPX2は、光が入射されないピクセルで発生される電気的信号を出力する。また、第1領域2及び第2領域4内での第1ピクセルPX1及び第2ピクセルPX2は、行ドライバー30から提供された行選択信号(Row SEL)、リセット信号Rx、及び電荷伝送信号Txのような複数の駆動信号によって駆動される。また、APSアレイ10で生成された電気的信号は相関二重サンプラー60に提供される。

20

【0014】

行ドライバー30は、行デコーダー20でデコーディングされた結果に応じて複数のピクセルを駆動するための複数の駆動信号をAPSアレイ10に提供する。ピクセルが行列形状に配列された場合には、駆動信号が各行別に単位ピクセルに提供される。

【0015】

タイミング発生器50は、行デコーダー20及び列デコーダー40にタイミング(timing)信号及び制御信号を提供する。

【0016】

相関二重サンプラー60は、APSアレイ10で生成された電気的信号を受信して維持(hold)及びサンプリングする。相関二重サンプラー60は、特定の雑音レベル(noise level)と電気的信号による信号レベルを二重にサンプリングして、雑音レベルと信号レベルの差に該当する差レベルを出力する。

30

【0017】

アナログデジタルコンバーター70は、相関二重サンプラー60から出力された差レベルに該当するアナログ信号をデジタル信号に変換して出力する。

【0018】

入出力バッファ80は、デジタル信号をラッチ(latch)し、ラッチされた信号は列デコーダー40でのデコーディング結果に応じて順次的に映像信号処理部(未図示)にデジタル信号を出力する。

40

【0019】

図3は、本発明の一実施形態によるイメージセンサーのピクセルを示す回路図である。

【0020】

図3を参照すると、第1ピクセルPX1及び第2ピクセルPX2は、入射光を電気的信号に変換する光電変換素子PD及び光電変換素子PDで生成された電気的信号を読み出す読み出し素子を各々含む。読み出し素子(トランジスタ)は、トランジスターゲートTG、リセット(reset)素子RG、ドライブ(drive)素子DG、又は選択(select)素子SG等を含む。また、トランジスターゲートTGの駆動信号Tx、リセット素子RGの駆動信号Rx、及び選択素子SGの行選択信号Row SELは、同一の行に含まれたピクセルに共通に連結される。以下、単一の光電変換素子PDに対して説明する。

50

## 【0021】

より詳細に説明すると、光電変換素子PDは、入射光に対応する電荷を生成及び蓄積する。例えば、光電変換素子PDは、フォトダイオード(photo diode)、フォト素子(photo transistor)、フォトゲート(photo gate)、ピンドフォトダイオード(PPD: Pinned Photo Diode)、及びこれらの組み合わせを含む。光電変換素子PDは、蓄積された電荷を浮遊拡散領域(FD:Floating Diffusion region)に伝達するトランスマルチゲートTGに連結される。

## 【0022】

浮遊拡散領域FDは、光電変換素子PDから、蓄積された電荷を受信する。浮遊拡散領域FDは寄生キャパシタンスを有するので、電荷が累積的に格納される。また、浮遊拡散領域FDはドライブ素子DGと電気的に連結されているので、ドライブ素子DGを制御する。

10

## 【0023】

トランスマルチゲートTGは、光電変換素子PDから浮遊拡散領域FDに電荷を伝送する。トランスマルチゲートTGは一般的に1つの素子からなり、電荷伝送信号Txによって制御される。

## 【0024】

リセット素子RGは、浮遊拡散領域FDを定期的にリセットさせ、リセット信号Rxによって制御される。そして、リセット素子RGのソースは浮遊拡散領域FDに連結され、ドレーンは電源電圧VDDに連結される。したがって、リセット信号Rxによってリセット素子RGがターンオンされると、リセット素子RGのドレーンに連結された電源電圧VDDが浮遊拡散領域FDに伝達される。

20

## 【0025】

ドライブ素子DGは、定電流源(図示せず)と組み合わされてソースフォロワバッファ增幅器(source follower buffer amplifier)の役割を果たし、光電変換素子PDに蓄積された光電荷を受信した浮遊拡散領域FDの電気的ポテンシャルの変化を增幅し、これを出力ラインVoutに出力する。

## 【0026】

選択素子SGは、行単位に読み出すピクセルを選択する役割を果たす。選択素子SGは行選択信号(Row SEL)によって駆動され、選択素子SGがターンオンされると、選択素子SGのドレーンに連結された電源電圧VDDがドライブ素子DGのドレーンに伝達される。

30

## 【0027】

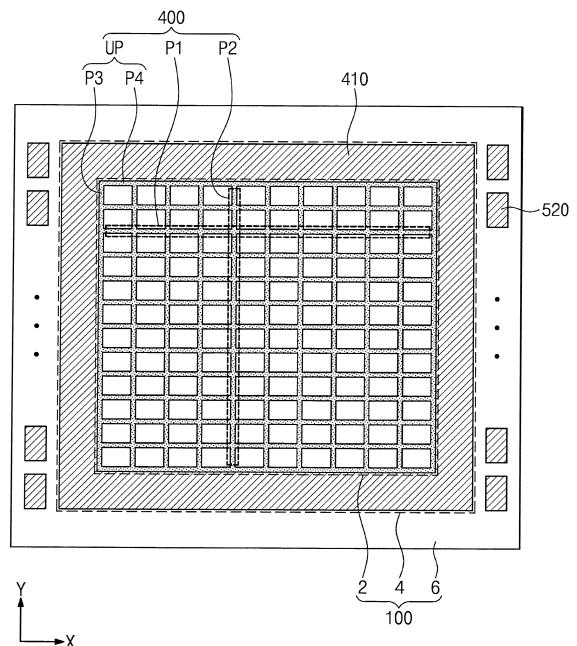

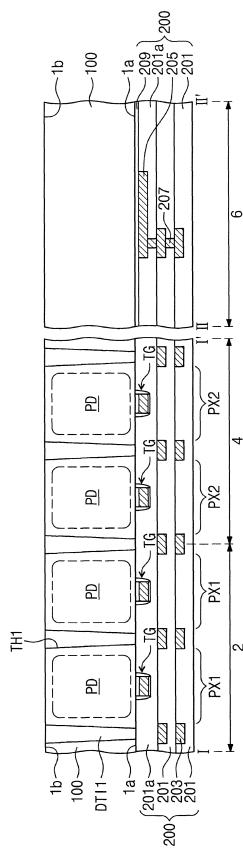

図4は、本発明の一実施形態によるイメージセンサーを示す平面図である。図5は、本発明の一実施形態によるイメージセンサーを示す図であって、図4のI-I'及びII-II'線に沿って切断された断面図である。

## 【0028】

図4及び図5を参照すると、半導体層100は、第1領域2、第2領域4、及び第3領域6を含む。第2領域4は半導体層100の第1領域2の周囲に位置し、第3領域6は半導体層100の第2領域4の周囲に位置する。第1領域2は、例えば、受光領域であり、第2領域4は遮光領域であり、第3領域6は入出力領域である。半導体層100は、例えば、シリコン半導体層、ゲルマニウム半導体層、シリコン-ゲルマニウム半導体層、II-VI族化合物半導体層、II-IV族化合物半導体層、又はSOI(Silicon on insulator)半導体層である。半導体層100は、第1面1a及び第2面1bを含む。第1面1a及び第2面1bは互いに対向する。

40

## 【0029】

第1素子分離膜DTI1が、半導体層100の第1領域2及び第2領域4内に配置される。第1素子分離膜DTI1は半導体層100を貫通する。例えば、第1素子分離膜DTI1の第1面は、半導体層100の第1面1aと共に面を有し、第1素子分離膜DTI1の

50

第1面に対向する第2面は、半導体層100の第2面1bと共に面を有する。第1素子分離膜DTI1は、後述する配線構造体200の層間絶縁膜(201、201a)の中で、最下層の層間絶縁膜201aに接触する。第1素子分離膜DTI1は、半導体層100の第1ピクセルPX1及び第2ピクセルPX2を定義する。第1ピクセルPX1は半導体層100の第1領域2内に提供され、第2ピクセルPX2は半導体層100の第2領域4内に提供される。第1素子分離膜DTI1は、例えば、シリコン酸化膜、シリコン窒化膜、誘電膜(例えば、AlO<sub>2</sub>、HfO<sub>2</sub>)、半導体物質(例えば、ポリシリコン)、及び金属物質(例えば、タンゲステン、銅、アルミニウム)の中の少なくとも1つを含む。

### 【0030】

保護分離膜SLが、半導体層100の第3領域6内に配置される。保護分離膜SLは半導体層100を貫通する。例えば、保護分離膜SLの第1面は、半導体層100の第1面1aと共に面を有し、保護分離膜SLの第1面に対向する第2面は、半導体層100の第2面1bと共に面を有する。保護分離膜SLは、後述する配線絶縁膜209に接触する。保護分離膜SLは、半導体層100の第3領域6内で貫通ビア領域TVRを定義する。一例として、保護分離膜SLは多角形又は円形のリング形状を有する。他の実施形態として、保護分離膜SLは多角形又は円形を含むグリッド構造を有する。保護分離膜SLは、シリコン窒化膜、タンタル酸化膜、及びハフニウム酸化膜の中の少なくとも1つを含み得る。

10

### 【0031】

光電変換素子PDが、半導体層100の第1ピクセルPX1及び第2ピクセルPX2内に配置される。光電変換素子PDは、第1方向X及び第1方向Xと交差する第2方向Yに離隔配置される。半導体層100の第1領域2内に配置された光電変換素子PDは、半導体層100の第2面1bから入射された光を独立的に収集する。光電変換素子PDは、例えば、n型不純物を含み得る。

20

### 【0032】

配線構造体200が、半導体層100の第1面1a上に配置される。配線構造体200は、層間絶縁膜(201、201a)、第1配線203、第2配線205、ビア207、トランスマルチゲートTG、及び配線絶縁膜209を含む。層間絶縁膜(201、201a)は、半導体層100の第1面1a上に順に積層される。層間絶縁膜(201、201a)は、例えば、シリコン酸化膜又はシリコン窒化膜を含む。第1配線203及び第2配線205は、層間絶縁膜(201、201a)内に配置される。例えば、第1配線203は、半導体層100の第1領域2及び第2領域4上に配置される。第2配線205は、半導体層100の第3領域6上に配置される。第2配線205の中で半導体層100に最も隣接する配線205は、配線絶縁膜209上に配置される。第1配線203及び第2配線205は、例えば金属物質(例えば、銅、タンゲステン)を含む。ビア207は、半導体層100の第3領域6上に配置される。ビア207は、層間絶縁膜(201、201a)内に配置される。ビア207は、第2配線205との間を連結する。図5には図示しないが、ビア207は、半導体層100の第1領域2及び第2領域4上にも配置され得る。ビア207は、例えば金属物質(例えば、銅、タンゲステン)を含む。

30

### 【0033】

トランスマルチゲートTGが、半導体層100の第1面1a上に配置される。トランスマルチゲートTGは、半導体層100の第1領域2及び第2領域4上に配置される。トランスマルチゲートTGは、第1ピクセルPX1及び第2ピクセルPX2の光電変換素子PDに対応するように配置される。トランスマルチゲートTGは、半導体層100の第1面1aに最も隣接する最下層の層間絶縁膜201aによって覆われる。配線絶縁膜209は、半導体層100の第3領域6の第1面1aと最下層の層間絶縁膜201aとの間に介在される。配線絶縁膜209は、半導体層100の第3領域6の第1面1aを覆う。配線絶縁膜209は、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸化窒化膜、又は熱酸化膜を含む。他の実施形態において、配線絶縁膜209は省略され得る。この場合、半導体層100の第1面1aに隣接する第2配線205と半導体層100の第1面1aとの間に層間絶縁膜201が提供される。

40

50

## 【0034】

反射防止膜300が、半導体層100の第2面1b上に配置される。反射防止膜300は、半導体層100の第1領域～第3領域(2、4、6)上に配置される。半導体層100の第3領域6上に配置された反射防止膜300は、後述するパッド520と半導体層100との間を電気的に絶縁する。反射防止膜300は、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸化窒化膜、又は高誘電膜(例えば、ハフニウム酸化膜、アルミニウム酸化膜)を含む。

## 【0035】

グリッドパターン400が、反射防止膜300上に配置される。例えば、グリッドパターン400は、半導体層100の第1領域2の第2面1b上に配置される。グリッドパターン400は、第1素子分離膜DTI1と重畳するように配置され、第1素子分離膜DTI1に沿って延長される。例えば、グリッドパターン400は、第1部分P1及び第2部分P2を含む。第1部分P1は第1方向Xに延長され、第2方向Yに離隔配置される。第2部分P2は第2方向Yに延長され、第1方向Xに離隔配置される。第1部分P1及び第2部分P2は、後述する遮光パターン410に連結される。グリッドパターン400は多角形を含むグリッド構造を有し得る。

10

## 【0036】

グリッドパターン400は、半導体層100の第1ピクセルPX1内に配置された光電変換素子PDを露出させる。グリッドパターン400は複数の膜からなる。グリッドパターン400は、反射防止膜300上に順に積層された第1グリッドパターン401(以下では第1パターン401として参照される)及び第2グリッドパターン403(以下では第2パターン403として参照される)を含む。第1パターン401は導電物質を含み得る。例えば、第1パターン401は、金属物質及び金属窒化膜の中の少なくとも1つを含む。第1パターン401は、チタニウム(Ti)、チタニウム窒化物(TiN)、タンゲステン(W)、アルミニウム(Al)、及び銅(Cu)の中の少なくとも1つを含み得る。第1パターン401は、約100～約1500の第1厚さT1を有する。第2パターン403は、第1パターン401上に配置される。第2パターン403は、有機物質を含み得る。第2パターン403は、後述するカラーフィルター530の屈折率よりも低い屈折率を有する物質を含む。第2パターン403は、約1.4以下の屈折率を有する低屈折物質を含む。第2パターン403の厚さは、第1パターン401の第1厚さT1よりも大きい。

20

## 【0037】

遮光パターン410が、反射防止膜300上に配置される。例えば、遮光パターン410は、半導体層100の第2領域4の第2面1b上に配置される。遮光パターン410は、半導体層100の第2領域4を完全に覆う。例えば、遮光パターン410は、半導体層100の第2ピクセルPX2内に配置された光電変換素子PDを覆う。グリッドパターン400は、遮光パターン410の側面411を覆う。より具体的に、グリッドパターン400の第1パターン401は、遮光パターン410の側面411を覆い、遮光パターン410に接触する。グリッドパターン400は、遮光パターン410の側面411の一部分及び遮光パターン410の側面411に隣接する上面410aの一部分を覆う。即ち、グリッドパターン400は、半導体層100の第1領域2から第2領域4上に延長される。他の実施形態において、グリッドパターン400は、遮光パターン410の側面411の一部分を覆い、遮光パターン410の上面410aを露出させる。

30

## 【0038】

遮光パターン410は単一膜からなる。遮光パターン410は、約1500～約5000の第2厚さT2を有する。遮光パターン410の第2厚さT2は、第1パターン401の第1厚さT1よりも厚い( $T2 > T1$ )。半導体層100の第2面1bから遮光パターン410の上面410aは、半導体層100の第2面1bから第1パターン401の上面401aよりも高いレベルに位置する。レベルは半導体層100の第2面1bに対して定義される。例えば、第1パターン401の上面と半導体層100の第2面1bとの間

40

50

の距離は、半導体層 100 の第 2 面 1b と遮光パターン 401 の上面 410a との間の距離よりも小さい。遮光パターン 401 は金属物質（例えば、タングステン（W））を含み得る。

#### 【0039】

貫通ビア 510 が、半導体層 100 の第 3 領域 6 上に配置される。一例として、貫通ビア 510 の各々は、半導体層 100 の貫通ビア領域 TVR 内に配置される。他の実施形態として、複数の貫通ビア 510 は、半導体層 100 の貫通ビア領域 TVR 内に配置される。貫通ビア 510 は、半導体層 100 、反射防止膜 300 、及び配線絶縁膜 209 を貫通して配線構造体 200 の第 2 配線 205 に連結される。パッド 520 が、半導体層 100 の第 3 領域 6 上に配置される。例えば、パッド 520 は、半導体層 100 の第 3 領域 6 の第 2 面 1b 上に配置された反射防止膜 300 上に配置される。パッド 520 は互いに電気的に絶縁される。パッド 520 は貫通ビア 510 上で貫通ビア 510 に連結される。各貫通ビア 510 と、各貫通ビア 510 上の各パッド 520 とは一体形である。

#### 【0040】

一実施形態において、パッド 520 の中の少なくとも 1 つは、遮光パターン 410 に連結され得る。図 4 を参照すると、パッド 520 の中の少なくとも 1 つは、遮光パターン 410 に電気的及び / 又は物理的に連結されるように連結パターン 521 に第 1 方向 X に沿って連結される。したがって、パッド 520 の中の少なくとも 1 つは、遮光パターン 410 を通じてグリッドパターン 400 と物理的 / 電気的に連結される。パッド 520 の中の少なくとも 1 つに連結されたグリッドパターン 400 は、貫通ビア 510 を通じて第 2 配線 205 に連結される。他の実施形態において、パッド 520 は遮光パターン 410 及びグリッドパターン 400 から物理的 / 電気的に離隔される。この場合、パッド 520 は遮光パターン 410 と物理的 / 電気的に連結されない。グリッドパターン 400 に連結された遮光パターン 410 は、半導体層 100 の第 2 領域 4 内に配置された貫通ビア（図示せず）を通じて配線構造体 200 の第 2 配線 205 及び / 又は半導体層 100 の第 2 領域 4 内に配置された配線構造体 200 の第 1 配線 203 に電気的に連結され得る。

#### 【0041】

グリッドパターン 400 は、外部から流れ込んだ静電気を外部へ放出する通路の役割を果たす。一実施形態において、静電気は、グリッドパターン 400 、遮光パターン 410 、パッド 520 の中の少なくとも 1 つ、及びパッド 520 の中の少なくとも 1 つに連結された貫通ビア 510 を通じて第 2 配線 205 に放出される。他の実施形態において、静電気は、グリッドパターン 400 、遮光パターン 410 、及び貫通ビア（図示せず）を通じて第 1 配線 203 及び / 又は第 2 配線 205 に放出される。この場合、第 1 配線 203 及び / 又は第 2 配線 205 には接地電圧又は負の電圧が印加される。

#### 【0042】

本発明の一実施形態によると、グリッドパターン 400 は、遮光パターン 410 の積層構造とは異なる積層構造を有するように形成される。グリッドパターン 400 の第 1 パターン 401 は金属物質を含むが、遮光パターン 410 よりも薄く形成されることによって、静電気を外部へ放出させる通路の役割を果たしながら、光の吸収を最小化させる。グリッドパターン 400 の第 2 パターン 403 は低屈折物質で形成され、カラーフィルター 530 の縁に隣接して入射される光を屈折させて該当ピクセルに入射させる。したがって、クロストーク（cross talk）が減少され、光効率が増大されたイメージセンサーを提供することができる。

#### 【0043】

カラーフィルター 530 が、半導体層 100 の第 1 領域 2 上に配置される。例えば、カラーフィルター 530 は、半導体層 100 の第 2 面 1b 上に配置され、第 1 ピクセル PX 1 内に配置された光電変換素子 PD に対応するように配置される。カラーフィルター 530 は、グリッドパターン 400 及び反射防止膜 300 を覆う。例えば、カラーフィルター 530 は、約 1.5 以上の高屈折率を有する物質を含む。

#### 【0044】

10

20

30

40

50

カラーフィルター膜 540 が、半導体層 100 の第 2 領域 4 上に配置される。例えば、カラーフィルター膜 540 は、半導体層 100 の第 2 面 1b 上に配置され、第 2 ピクセル PX2 内に配置された光電変換素子 PD を覆う。カラーフィルター膜 540 は反射防止膜 300 を覆う。パッド 520 は、カラーフィルター 530 及びカラーフィルター膜 540 によって露出される。マイクロレンズ MR が、カラーフィルター 530 上に配置される。マイクロレンズ MR は、第 1 ピクセル PX1 内に配置された光電変換素子 PD に対応するように配置される。カラーフィルター膜 540 及びパッド 520 は、マイクロレンズ MR によって露出される。

【0045】

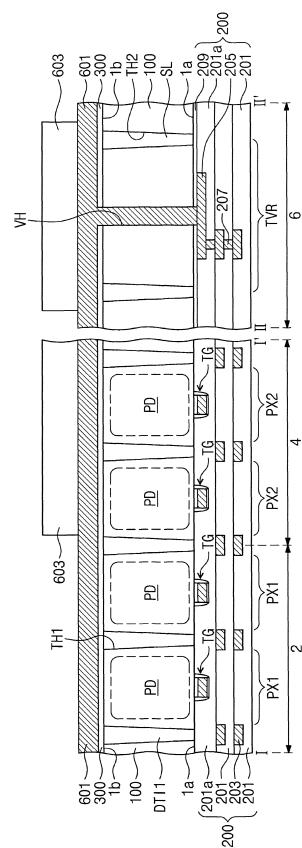

図 6 は、本発明の一実施形態によるイメージセンサーの他の例を示す図であって、図 4 の I - I' 及び II - II' 線に沿って切断した断面図である。 10

【0046】

図 6 を参照すると、遮光構造体 410A が、半導体層 100 の第 2 領域 4 上に配置される。例えば、遮光構造体 410A は、半導体層 100 の第 2 領域 4 の第 2 面 1b 上に提供された反射防止膜 300 上に配置される。遮光構造体 410A は、第 2 ピクセル PX2 内に配置された光電変換素子 PD を覆う。遮光構造体 410A は、反射防止膜 300 上に順に積層された遮光パターン 410、第 1 パターン 401、及び第 2 パターン 403 を含む。半導体層 100 の第 1 領域 2 上に配置された第 1 パターン 401 は、第 2 領域 4 上に延長される。第 1 パターン 401 は、遮光パターン 410 の側面 411 及び上面 410a を覆う。第 1 パターン 401 は、遮光パターン 410 に接触及び連結される。半導体層 100 の第 2 領域 4 上で、第 1 パターン 401 上に配置された第 2 パターン 403 は、第 1 パターン 401 に沿って半導体層 100 の第 2 領域 4 上に延長される。第 2 パターン 403 は、半導体層 100 の第 2 領域 4 上に配置された第 1 パターン 401 の側面及び上面を覆う。一実施形態において、グリッドパターン 400 の第 3 厚さ T3 は、遮光構造体 410A の第 4 厚さ T4 よりも小さい ( $T3 < T4$ )。半導体層 100 の第 2 面 1b からグリッドパターン 400 の上面は、半導体層 100 の第 2 面 1b から遮光構造体 410A の上面よりも低いレベルに位置する。パッド 520 は、遮光構造体 410A、カラーフィルター膜 540、及びマイクロレンズ MR によって露出される。パッド 520 の各々の第 5 厚さ T5 は、グリッドパターン 400 の第 3 厚さ T3 及び遮光構造体 410A の第 4 厚さ T4 よりも小さい ( $T5 < T3, T4$ )。パッド 520 の第 5 厚さ T5 は、遮光パターン 410 の第 2 厚さ T2 と実質的に同一である。 20 30

【0047】

図 7 は、本発明の一実施形態によるイメージセンサーのさらに他の例を示す図であって、図 4 の I - I' 及び II - II' 線に沿って切断した断面図である。 30

【0048】

図 7 を参照すると、第 1 素子分離膜 DTI1 が、半導体層 100 内で半導体層 100 の第 2 面 1b から第 1 面 1a に向かって延長される。第 1 素子分離膜 DTI1 は、配線構造体 200 の最下層の層間絶縁膜 201a から離隔される。例えば、第 1 素子分離膜 DTI1 の第 2 面は、半導体層 100 の第 2 面 1b と共に面を有し、第 1 素子分離膜 DTI1 の第 1 面は半導体層 100 の第 1 面 1a と共に面を有しない。例えば、第 1 素子分離膜 DTI1 の第 1 面は、半導体層 100 の第 1 面 1a と第 2 面 1b との間のレベルに位置する。 40

【0049】

図 8 は、本発明の一実施形態によるイメージセンサーのその他の例を示す図であって、図 4 の I - I' 及び II - II' 線に沿って切断した断面図である。

【0050】

図 8 を参照すると、第 1 光電変換素子 PD1 及び第 2 光電変換素子 PD2 が、第 1 ピクセル PX1 及び第 2 ピクセル PX2 の各々内に配置される。即ち、1 つのピクセル内に一対の第 1 光電変換素子 PD1 及び第 2 光電変換素子 PD2 が配置される。第 2 素子分離膜 DTI2 が、第 1 ピクセル PX1 及び第 2 ピクセル PX2 の各々内に配置される。各第 2 素子分離膜 DTI2 は、1 つのピクセル内に配置された一対の第 1 光電変換素子 PD1 と

第2光電変換素子P D 2との間に配置されて、これらの間を物理的に分離する。一実施形態において、第2素子分離膜D T I 2は、第1素子分離膜D T I 1に連結される。他の実施形態において、第2素子分離膜D T I 2は、第1素子分離膜D T I 1から離隔される。第2素子分離膜D T I 2は、半導体層100の第2面1bから第1面1aに向かって延長される。第2素子分離膜D T I 2は、半導体層100の第2面1bに接触し、第1面1aから離隔される。例えば、第2素子分離膜D T I 2の第1面(図8に図示された下面)のレベルは、半導体層100の第1面1aと第2面1bとの間のレベルに位置する。第2素子分離膜D T I 2の第2面(図8に図示された上面)は、半導体層100の第2面1bと共に面を有する。第2素子分離膜D T I 2は、例えば、シリコン酸化膜、シリコン窒化膜、及び誘電膜(A1O2、HfO2)の中の少なくとも1つを含む。

10

#### 【0051】

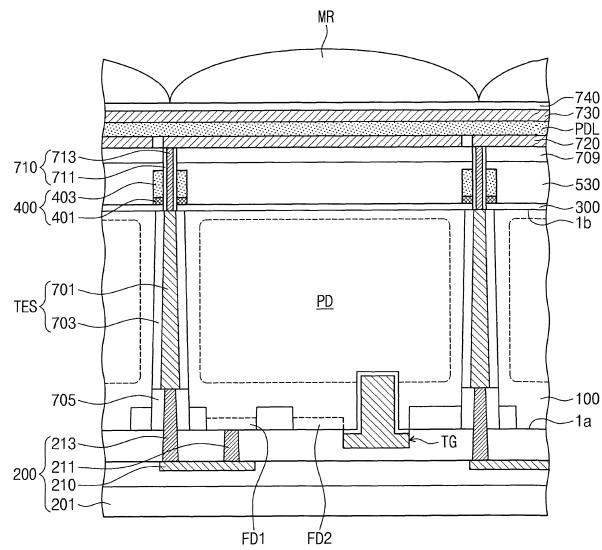

図9は、本発明の他の実施形態によるイメージセンサーを示す断面図である。

#### 【0052】

図9を参照すると、一対の第1浮遊拡散領域F D 1及び第2浮遊拡散領域F D 2が、半導体層100内に配置される。一実施形態において、一対の第1浮遊拡散領域F D 1及び第2浮遊拡散領域F D 2は、半導体層100の第1ピクセルP X 1(図5参照)及び第2ピクセルP X 2(図5参照)の各々内に配置される。第1浮遊拡散領域F D 1及び第2浮遊拡散領域F D 2は、半導体層100の第1面1aに隣接するように配置される。第2浮遊拡散領域F D 2は、トランスマルチゲートT Gの一側の半導体層100内に配置される。一実施形態において、図9に示すトランスマルチゲートT Gの一部は、図5に示すトランスマルチゲートT Gとは異なり、半導体層100内に埋め込まれる。貫通電極構造体T E Sが、第1素子分離膜D T I 1を貫通する。貫通電極構造体T E Sは、半導体層100内に配置される。貫通電極構造体T E Sの各々は、第1ピクセルP X 1及び第2ピクセルP X 2の各々に対応するように提供される。貫通電極構造体T E Sの各々は、貫通電極701及び貫通絶縁パターン703を含む。貫通絶縁パターン703は、貫通電極701の側壁を囲む。貫通絶縁パターン703は、例えば、シリコン酸化物、シリコン窒化物、及び/又はシリコン酸窒化物を含む。貫通電極701は、例えば、n型又はp型不純物でドーピングされたポリシリコンを含む。

20

#### 【0053】

埋め込み絶縁パターン705が、貫通電極構造体T E Sの各々と半導体層100の第1面1aとの間に配置される。埋め込み絶縁パターン705の一面は、半導体層100の第1面1a(図9に図示された下面)と共に面を有する。埋め込み絶縁パターン705は、例えば、シリコン酸化膜、シリコン窒化膜、シリコン酸化窒化膜の中の少なくとも1つを含む。

30

#### 【0054】

配線構造体200が、半導体層100の第1面1a上に配置される。配線構造体200は、複数の層間絶縁膜201、連結配線210、第1連結ビア211、及び第2連結ビア213を含む。第1連結ビア211は、層間絶縁膜201の中の少なくとも1つを貫通して第1浮遊拡散領域F D 1に連結される。第2連結ビア213は、層間絶縁膜201の中の少なくとも1つ及び埋め込み絶縁パターン705を貫通して貫通電極構造体T E Sの貫通電極701に連結される。連結配線210は、層間絶縁膜201の中の少なくとも1つ内に配置され、第1連結ビア211と第2連結ビア213との間を連結する。連結配線210、第1連結ビア211、及び第2連結ビア213は、金属物質(例えば、タンゲステン、銅、アルミニウム)及び金属窒化膜(例えば、タンタル窒化物、チタニウム窒化物、タンゲステン窒化物)の中の少なくとも1つを含み得る。

40

#### 【0055】

グリッドパターン400が、半導体層100の第2面1b上に配置される。グリッドパターン400は、第1素子分離膜D T I 1及び貫通電極構造体T E S上に配置される。グリッドパターン400は、遮光パターン(図5の410参照)に連結される。絶縁膜709が、カラーフィルター530上に配置される。絶縁膜709は、カラーフィルター53

50

0の上面を覆う。絶縁膜709は、例えば、シリコン酸化膜、シリコン窒化膜、又はシリコン酸化窒化膜を含む。

【0056】

コンタクトプラグ構造体710が、貫通電極構造体TES上に配置される。コンタクトプラグ構造体710は、反射防止膜300、グリッドパターン400、カラーフィルター530、及び絶縁膜709を貫通する。コンタクトプラグ構造体710は、貫通電極構造体TESに連結される。コンタクトプラグ構造体710の各々は、コンタクトプラグ713及びスペーサー711を含む。コンタクトプラグ713は、反射防止膜300、グリッドパターン400、カラーフィルター530、及び絶縁膜709を貫通する。スペーサー711は、コンタクトプラグ713の側壁を囲む。コンタクトプラグ713は、金属物質(例えば、タンクステン)を含む。スペーサー711は、絶縁物質(例えば、シリコン酸化膜、シリコン窒化膜)を含む。

10

【0057】

下部電極720が、絶縁膜709上に配置される。下部電極720は、光電変換素子PDと対応するように配置される。下部電極720は、互いに離隔して配置される。コンタクトプラグ構造体710の各々は、下部電極720の各々に対応するように配置され、互いに電気的に連結される。下部電極720は、透明導電性物質を含む。例えば、下部電極720は、ITO(Indium Tin Oxide)、IZO(Indium Zinc Oxide)、ZnO(Zinc Oxide)、及び/又は有機透明導電物質を含む。

20

【0058】

光電変換層PDLが、下部電極720上に配置される。一実施形態において、光電変換層PDLは、有機光電変換層を含む。有機光電変換層は、p型有機半導体物質及びn型有機半導体物質を含み、p型有機半導体物質とn型有機半導体物質とはpn接合を形成する。一例において、光電変換層PDLは、量子ドット(quantum dot)又はカルコゲナイト(chalcogenide)を含む。

30

【0059】

上部電極730が、光電変換層PDL上に配置される。上部電極730は、透明導電性物質を含む。例えば、上部電極730は、ITO(Indium Tin Oxide)、IZO(Indium Zinc Oxide)、ZnO(Zinc Oxide)、及び/又は有機透明導電物質を含む。

30

【0060】

キャッピング層740が、上部電極730上に配置される。キャッピング層740は、絶縁物質を含む。例えば、キャッピング層740は、アルミニウム酸化物、シリコン酸化物、シリコン窒化物、及び/又はシリコン酸窒化物を含む。

【0061】

マイクロレンズMRが、キャッピング層740上に配置される。

【0062】

図10は、本発明の他の実施形態によるイメージセンサーを示す平面図である。

【0063】

図10を参照すると、グリッドパターン400は、外側セグメントUP、第1部分P1、及び第2部分P2を含む。外側セグメントUPは、一対の第3部分P3及び一対の第4部分P4を含む。一対の第3部分P3は第2方向Yに延長され、第1方向Xに離隔配置される。一対の第4部分P4は第1方向Xに延長され、第2方向Yに離隔配置される。一対の第3部分P3の端部と一対の第4部分P4の端部とは互いに連結される。したがって、外側セグメントUPは、四角形のリング形状を有する。第1部分P1及び第2部分P2は、外側セグメントUP内に配置される。第1部分P1は、第1方向Xに延長され、第2方向Yに離隔配置される。第2部分P2は、第2方向Yに延長され、第1方向Xに離隔配置される。第1部分P1及び第2部分P2は、外側セグメントUPに連結される。遮光パターン410は、グリッドパターン400の外側セグメントUPの外側壁を囲む。

40

【0064】

50

図11A～図11Dは、本発明の一実施形態によるイメージセンサーの製造方法を示す図であって、図4のI-I'及びII-II'線に沿って切断した断面図である。

【0065】

図11Aを参照すると、半導体層100が提供される。半導体層100は、互いに対向する第1面1a及び第2面1bを含む。半導体層100は、第1領域2、第2領域4、及び第3領域6を含む。光電変換素子PDが、半導体層100の第1領域2及び第2領域4内に形成される。光電変換素子PDは、半導体層100の第1面1aを通じてイオン注入工程を行って形成される。光電変換素子PDは、例えば、n型不純物をドーピングして形成される。

【0066】

配線構造体200が、半導体層100の第1面1a上に形成される。配線構造体200は、トランスマルチゲートTG、層間絶縁膜(201、201a)、第1配線203、第2配線205、ビア207、及び配線絶縁膜209を含む。トランスマルチゲートTGは、半導体層100の第1領域2及び第2領域4の第1面1a上に形成される。配線絶縁膜209は、半導体層100の第3領域6の第1面1a上に形成される。層間絶縁膜(201、201a)は、半導体層100の第1面1a上に順に形成される。層間絶縁膜(201、201a)の中で最下層の層間絶縁膜201aは、トランスマルチゲートTG及び配線絶縁膜209を覆う。第1配線203及び第2配線205が、層間絶縁膜(201、201a)内に配置される。第1配線203は、半導体層100の第1領域2及び第2領域4上に配置される。第2配線205は、半導体層100の第3領域6上に配置される。第1配線203及び第2配線205は、層間絶縁膜(201、201a)によって覆われる。ビア207が、層間絶縁膜(201、201a)内に形成される。ビア207は、半導体層100の第3領域6上に配置される。ビア207は、第2配線205の間を連結する。

【0067】

第1素子分離膜DTI1が、半導体層100の第1領域2及び第2領域4内に形成される。第1素子分離膜DTI1は、半導体層100を蝕刻して第1トレンチTH1を形成し、第1トレンチTH1内に絶縁物質及び/又は導電物質を満たして形成される。一実施形態において、図11Aに示すように、第1トレンチTH1は、半導体層100の第2面1bから蝕刻されて形成される。他の実施形態において、第1トレンチTH1は、配線構造体200を形成する前に、半導体層100の第1面1aから蝕刻されて形成される。第1素子分離膜DTI1は、半導体層100の第1領域2及び第2領域4内で半導体層100の第1ピクセルPX1及び第2ピクセルPX2を定義する。第1ピクセルPX1は、半導体層100の第1領域2内に提供され、第2ピクセルPX2は、半導体層100の第2領域4内に提供される。光電変換素子PDが第1ピクセルPX1及び第2ピクセルPX2内に配置される。

【0068】

図11Bを参照すると、保護分離膜SLが、半導体層100の第3領域6内に形成される。保護分離膜SLは、半導体層100の第3領域6内に第2トレンチTH2を形成し、第2トレンチTH2内に絶縁物質を満たして形成される。一実施形態において、第2トレンチTH2は、半導体層100の第3領域6を貫通して形成される。保護分離膜SLは、半導体層100の第3領域6内で貫通ビア領域TVRを定義する。

【0069】

反射防止膜300が、半導体層100の第2面1b上に形成される。反射防止膜300は、半導体層100の第2面1b及び半導体層100の第2面1bに露出された第1素子分離膜DTI1の第2面(図11Bに図示された上面)及び保護分離膜SLの第2面(図11Bに図示された上面)を覆う。図11Bに図示しないが、反射防止膜300は、第2トレンチTH2内を満たす。ビアホールVHが、半導体層100の第3領域6内に形成される。例えば、ビアホールVHは、半導体層100の貫通ビア領域TVR内に形成される。ビアホールVHは、反射防止膜300、半導体層100、及び配線絶縁膜209を貫通して第2配線205の中のいずれか1つを露出させる。

10

20

30

30

40

50

## 【0070】

遮光膜601が、半導体層100の第2面1b上に形成される。遮光膜601は、半導体層100の第1領域～第3領域(2、4、6)上に形成される。遮光膜601は、反射防止膜300の上面を覆い、ビアホールVH内を満たす。遮光膜601は、約1500～約5000の厚さを有するように形成される。遮光膜601は、金属物質(例えば、タンゲステン(W))を含み得る。第1マスクパターン603が、遮光膜601上に形成される。第1マスクパターン603は、半導体層100の第2領域4及び第3領域6上に形成される。一例として、第1マスクパターン603は、半導体層100の第1領域2上に形成された遮光膜601及び半導体層100の第3領域6上に形成された遮光膜601の一部分を露出させる。第1マスクパターン603は、例えば、フォトレジスト物質を含む。

10

## 【0071】

図11Cを参照すると、第1マスクパターン603を蝕刻マスクに使用して遮光膜601を蝕刻する。したがって、遮光パターン410が半導体層100の第2領域4上に形成され、パッド520及び貫通ビア510が、半導体層100の第3領域6上に形成される。遮光パターン410は、半導体層100の第1領域2上に形成された反射防止膜300の上面を露出させる。遮光パターン410は、半導体層100の第2領域4上に形成された反射防止膜300の上面を覆う。貫通ビア510はビアホールVH内に形成され、パッド520は貫通ビア510上に形成される。一実施形態において、パッド520は互いに離隔配置されて形成され、パッド520の中の少なくとも1つと遮光パターン410とは互いに連結される。他の実施形態において、パッド520は互いに離隔配置されて形成され、パッド520と遮光パターン410とは互いに連結されない。蝕刻工程は乾式蝕刻工程が遂行される。蝕刻工程の後に残った第1マスクパターン603は除去される。第1マスクパターン603はアッシング工程又はストリップ工程を遂行して除去される。

20

## 【0072】

フィルム膜605が、半導体層100の第2面1b上に形成される。フィルム膜605は、半導体層100の第1領域2上に形成された反射防止膜300の上面、半導体層100の第2領域4上に形成された遮光パターン410の上面及び側面、及び半導体層100の第3領域6上に形成されたパッド520の上面及び側面を覆う。フィルム膜605は、遮光パターン410の厚さよりも薄い厚さを有するように形成される。フィルム膜605は、例えば、約100～約1500の厚さを有するように形成される。フィルム膜605は、例えば、チタニウム(Ti)、チタニウム窒化物(TiN)、タンゲステン(W)、アルミニウム(Al)、及び銅(Cu)の中の少なくとも1つを含む。低屈折膜607が、フィルム膜605上に形成される。低屈折膜607はフィルム膜605の上面及び側面を覆う。低屈折膜607は、例えば、約1.4以下の屈折率を有する低屈折物質を含む。

30

## 【0073】

第2マスクパターン609が、低屈折膜607上に形成される。第2マスクパターン609は、半導体層100の第1領域2及び第2領域4上に形成される。第2マスクパターン609は、半導体層100の第1領域2内に形成された第1素子分離膜DTI1に重畳するように形成される。第2マスクパターン609は、半導体層100の第1領域2内に形成された第1素子分離膜DTI1に沿って形成される。一実施形態において、第2マスクパターン609によって半導体層100の第1領域2上に形成された低屈折膜607の一部分、半導体層100の第2領域4上に形成された低屈折膜607の一部分、及び半導体層100の第3領域6上に形成された低屈折膜607の全体が露出される。他の実施形態において、第2マスクパターン609によって半導体層100の第1領域2上に形成された低屈折膜607の一部分及び半導体層100の第3領域6上に形成された低屈折膜607の全体が露出される。即ち、第2マスクパターン609は、半導体層100の第2領域4上に形成された低屈折膜607の上面全体を覆う。第2マスクパターン609は、例えば、フォトレジスト物質を含む。

40

50

## 【0074】

図11Dを参照すると、第2マスクパターン609を蝕刻マスクに使用して低屈折膜607及びフィルム膜605を蝕刻する。したがって、グリッドパターン400が半導体層100の第1領域2上に形成される。グリッドパターン400は、半導体層100の第1領域2上に形成された第1素子分離膜DTI1に重畳するように形成される。グリッドパターン400は、第1ピクセルPX1内に形成された光電変換素子PDを露出させる。グリッドパターン400は、半導体層100の第1領域2に隣接する遮光パターン410の側面及び上面の一部分を覆う。グリッドパターン400は、第1パターン401及び第2パターン403を含む。第1パターン401はフィルム膜605がパターニングされて形成されたものであり、第2パターン403は低屈折膜607がパターニングされて形成されたものである。第1パターン401は、遮光パターン410の側面及び上面の一部分を覆う。パッド520の上面はグリッドパターン400によって露出される。蝕刻工程は乾式蝕刻工程が遂行される。蝕刻工程の後に残った第2マスクパターン609は除去される。第2マスクパターン609は、アッシング工程又はストリップ工程を遂行して除去される。

10

## 【0075】

再び図5を参照すると、カラーフィルター530が、半導体層100の第2面1b上に形成される。カラーフィルター530は、第1ピクセルPX1内に形成された光電変換素子PDに対応するように形成される。カラーフィルター膜540が、半導体層100の第2面1b上に形成される。カラーフィルター膜540は、半導体層100の第2領域4上に形成されて遮光パターン410を覆う。カラーフィルター530及びカラーフィルター膜540は、半導体層100の第3領域6上に形成されたパッド520を露出させる。マイクロレンズMRがカラーフィルター530上に形成される。

20

## 【0076】

以上、図面を参照しながら本発明の実施形態を説明したが、本発明が属する技術分野で通常の知識を有する者は、本発明の技術的思想や必須の特徴を変形せずに、他の具体的な形態で実施可能である。したがって、以上に記載した実施形態はすべての面で例示的なものであり、限定的なものではない。

## 【符号の説明】

## 【0077】

30

- 10 アクティブピクセルセンサー(APS)アレイ

- 20 行デコーダー

- 30 行ドライバー

- 40 列デコーダー

- 50 タイミング発生器

- 60 相関二重サンプラー(CDS)

- 70 アナログデジタルコンバーター(ADC)

- 80 入出力バッファ

- 100 半導体層

- 200 配線構造体

- 201、201a 層間絶縁膜

- 203 第1配線

- 205 第2配線

- 207 ピア

- 209 配線絶縁膜

- 210 連結配線

- 211 第1連結ピア

- 213 第2連結ピア

- 300 反射防止膜

- 400 グリッドパターン

40

50

|                 |                           |    |

|-----------------|---------------------------|----|

| 4 0 1           | 第 1 ( グリッド ) パターン         |    |

| 4 0 3           | 第 2 ( グリッド ) パターン         |    |

| 4 1 0           | 遮光パタン                     |    |

| 4 1 0 a         | 上面                        |    |

| 4 1 0 A         | 遮光構造体                     |    |

| 4 1 1           | 側面                        |    |

| 5 1 0           | 貫通ビア                      |    |

| 5 2 0           | パッド                       |    |

| 5 2 1           | 連結パタン                     |    |

| 5 3 0           | カラーフィルター                  | 10 |

| 5 4 0           | カラーフィルター膜                 |    |

| 6 0 1           | 遮光膜                       |    |

| 6 0 3           | 第 1 マスクパタン                |    |

| 6 0 5           | フィルム膜                     |    |

| 6 0 7           | 低屈折膜                      |    |

| 6 0 9           | 第 2 マスクパタン                |    |

| 7 0 1           | 貫通電極                      |    |

| 7 0 3           | 貫通絶縁パタン                   |    |

| 7 0 5           | 埋め込み絶縁パタン                 |    |

| 7 0 9           | 絶縁膜                       | 20 |

| 7 1 0           | コンタクトプラグ構造体               |    |

| 7 1 1           | スペーサー                     |    |

| 7 1 3           | コンタクトプラグ                  |    |

| 7 2 0           | 下部電極                      |    |

| 7 3 0           | 上部電極                      |    |

| 7 4 0           | キャッピング層                   |    |

| D T I 1、D T I 2 | 第 1 素子分離膜                 |    |

| F D 1、F D 2     | ( 第 1 、第 2 ) 浮遊拡散領域       |    |

| M R             | マイクロレンズ                   |    |

| P 1、P 2、P 3、P 4 | ( 第 1 、第 2 、第 3 、第 4 ) 部分 | 30 |

| P D             | 光電変換素子                    |    |

| P D 1、P D 2     | ( 第 1 、第 2 ) 光電変換素子       |    |

| S L             | 保護分離膜                     |    |

| T E S           | 貫通電極構造体                   |    |

| T G             | トランスマルチゲート                |    |

| T H 1、T H 2     | ( 第 1 、第 2 ) トレンチ         |    |

| T V R           | 貫通ビア領域                    |    |

| U P             | 外側セグメント                   |    |

| V H             | ビアホール                     |    |

## 【図面】

## 【図 1】

## 【図 2】

## 【図 3】

## 【図 4】

10

20

30

40

50

【図5】

【図6】

10

20

【図7】

【図8】

30

40

50

【図9】

【図10】

10

20

【図11A】

【図11B】

30

40

50

【図11C】

### 【図11D】

10

20

30

40

50

---

フロントページの続き

- 口, 129

(72)発明者 金 正 生

大韓民国, 16677, ギヨンギ-ド, スウォン-シ, ヨントン-グ, サムスン-口, 129

(72)発明者 俞 錦 根

大韓民国, 16677, ギヨンギ-ド, スウォン-シ, ヨントン-グ, サムスン-口, 129

審査官 柴山 将隆

(56)参考文献 米国特許出願公開第2015/0264233 (US, A1)

特開2010-109295 (JP, A)

国際公開第2016/103936 (WO, A1)

特開2016-096323 (JP, A)

特開2013-175494 (JP, A)

特開2018-019139 (JP, A)

特開2012-084693 (JP, A)

特開2017-034499 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H04N 25/70

H04N 25/76