UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA NUMERO     | 101990900136141 |  |

|--------------------|-----------------|--|

| Data Deposito      | 14/08/1990      |  |

| Data Pubblicazione | 14/02/1992      |  |

| Priorità               | 07/394.497 |

|------------------------|------------|

| Nazione Priorità       | US         |

| Data Deposito Priorità |            |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| Н       | 04     | В           |        |             |

# Titolo

APPARECCHIO DI ABBONATO PER UN SISTEMA DI COMUNICAZIONI DI TIPO DIGITALE VIA RADIO AD ABBONATI

SIB 88755

07/394.497

DESCRIZIONE dell'invenzione industriale dal titolo:

"APPARECCHIO DI ABBONATO PER UN SISTEMA DI

COMUNICAZIONI DI TIPO DIGITALE VIA RADIO AD

ABBONATI"

della ditta statunitense INTERNATIONAL MOBILE MACHINES CORPORATION

con sede in KING OF PRUSSIA, PENNSYLVANIA, U.S.A.

# **DESCRIZIONE**

#### BASE TECNICA E SOMMARIO DELL'INVENZIONE

La presente invenzione si riferisce genericamente a sistemi di comunicazione di abbonato e si riferisce in particolare ad una unità di abbonato perfezionata per comunicazioni via radio con una stazione di base in un sistema di comunicazione di tipo digitale via radio ad abbonati.

Un tipico apparecchio di abbonato è descritto nella domanda di brevetto degli stati Uniti n.06/893.916 depositata il 7 Agosto 1986 da David N. Critchlow ed altri. Una stazione di base impiegata con un apparecchio di abbonato di questo genere in un sistema di comunicazione di tipo

digitale via radio per abbonati è descritta nell'attestato di brevetto degli stati Uniti n.4.777.636 a nome Thomas E. Fletcher, Wendeline R. Avis, Gregory T. Saffee e Karle J. Johnson. apparecchiatura di abbonato descritta nella domanda n. 06/893.916 comprende mezzi per transcodificare un segnale di ingresso in fonia digitale per fornire simboli di ingresso digitali; mezzi per il filtraggio FIR dei simboli di ingresso digitali; mezzi per ricavare un segnale di ingresso a frequenza intermedia analogica dai simboli di ingresso filtrati; mezzi per combinare il segnale di ingresso a frequenza intermedia con una portante RF per la trasmissione via radio verso la stazione di base; mezzi per demodulare un segnale di uscita ricevuto dalla stazione base per fornire simboli digitali di uscita; e mezzi per sintetizzare un segnale di uscita in fonia digitale dai simboli digitali di uscita. L'apparecchio di abbonato comprende un chip di elaborazione in banda base ed un chip elaboratore modem. Ambedue sono elaboratori segnale digitali tipo TMS32020. elaboratore in banda base effettua la transcodifica del segnale di ingresso in fonia digitale, la sintesi dei simboli di uscita digitali e varie

funzioni di controllo in banda base; ed il chip elaboratore modem effettua il filtraggio FIR dei simboli di ingresso digitali, e la demodulazione del segnale di uscita ricevuto dalla stazione di base. Il chip elaboratore modem in genere agisce come unità di controllo centrale per il sistema.

### SOMMARIO DELL'INVENZIONE

La presente invenzione fornisce บทล apparecchiatura di abbonato meno costosa. apparecchiatura di abbonato della presente invenzione comprende mezzi per transcodificare un segnale di ingresso in fonia digitale per fornire simboli di ingresso digitali; mezzi per filtraggio FIR dei simboli di ingresso digitali; mezzi per modulare un segnale a frequenza intermedia digitale con i simboli di ingresso filtrato per fornire un segnale di ingresso a frequenza intermedia modulata; mezzi per elaborare il segnale di ingresso modulato per la trasmissione verso la stazione di base; mezzi per demodulare un segnale di uscita ricevuto dalla stazione di base per fornire simboli digitali di uscita; e mezzi per sintetizzare un segnale di uscita in fonia digitale simboli di uscita digitali; in l'apparecchio di abbonato comprende un chip FIR per

effettuare detto filtraggio FIR dei simboli digitali di ingresso; un chip DIF per sintetizzare digitalmente detto segnale a frequenza intermedia digitale e per effettuare detta modulazione di detto segnale a frequenza intermedia digitale; ed un chip a unico elaboratore per effettuare detta transcodifica di detti segnali in fonia digitale in ingresso, per effettuare detta demodulazione di detto segnale di uscita ricevuto dalla stazione di base e per effettuare detta sintesi dei simboli di uscita digitale.

Il chip FIR effettua la funzione di filtraggio FIR che era realizzata in software nell'elaboratore di modem dell'apparecchio di abbonato secondo la tecnica precedente sopra illustrato. Spostando la funzione di filtraggio FIR di trasmissione che richiede tempo fuori dell'elaboratore modem ed effettuando la funzione di demodulazione con lo stesso elaboratore che effettua la funzione di elaborazione in banda base, è necessario soltanto un chip elaboratore.

I mezzi per sintetizzare per via digitale il segnale a frequenza intermedia digitale consistono in un sintetizzatore digitale diretto (DDS) che comprende mezzi accoppiati dal chip elaboratore per

accumulare dati di fase forniti dal chip elaboratore per indicare una frequenza intermedia prestabilita, e mezzi per elaborare i dati di fase accumulati per generare detto segnale a frequenza intermedia digitale alla frequenza intermedia prestabilita. La presente invenzione aggiunge caratteristiche di funzionalità all'apparecchio di abbonato che non esistevano nell'apparecchio di abbonato della tecnica precedente sopra descritto, per il fatto che la sintesi digitale diretta consente una sintonizzazione estremamente flessibile dell'apparecchio di abbonato. Nell'apparecchio di abbonato secondo la tecnica precedente sopra descritto, la sintonizzazione era limitata ad un insieme finito di canali distanziati di incrementi di 25 KHz. Inoltre, la differenza di frequenza tra trasmissione e ricezione era fissata a 5 MHz. La funzione DDS del chip DIF rimuove queste limitazioni, consentendo altri tipi di spaziatura di canale o sfalsamento TX/RX che possano essere sostenuti con minime e nulle modifiche alla circuiteria dell'apparecchio di abbonato.

Consequentemente, il chip DIF fornisce un segnale IF digitale interamente modulato che può

essere sintetizzato digitalmente su una qualsiasi di una molteplicità di diverse frequenze presetabilite; ed si può fornire una regolazione di frequenza a risoluzione fine nel chip DIF per consentire l'inseguimento in sequenza del segnale di uscita ricevuto dalla stazione di base. Queste due caratteristice consentono che la radio dell'apparecchio di abbonato contenga soltanto un riferimento LO a frequenza fissa ed elimina necessità di un sintetizzatore F. Oueste due caratteristiche consentono anche che sia fisso il riferimento di frequenza primario nell'apparecchio abbonato con tutte le regolazioni sintonizzazione che sono effettuate dal chip DIF.

Un sintetizzatore diretto di tipo digitale è stabile e di facile produzione. Si possono soddisfare le specifiche di rumore di fase senza la necessità di sintetizzatori RF costosi e complessi del tipo PLL. La caratteristica DDS fornisce agilità in frequenza entro la banda IF e fornisce più facili modifiche di frequenza per il funzionamento su altre bande.

Un'altra caratteristica della presente invenzione consiste nel fatto che il chip FIR comprende mezzi per generare segnali di

temporizzazione per temporizzare la temporizzazione di transcodifica e l'operazione di sintesi del segnale di uscita in fonia digitale per mezzo del chip elaboratore.

Tuttavia, il chip elaboratore effettua la demodulazione del segnale di uscita ricevuto dalla stazione di base indipendentemente dai segnali di temporizzazione generati dal chip FIR. Il chip elaboratore riceve detto segnale di uscita secondo i segnali di temporizzazione prodotti dal chip FIR, ed effettua una memorizzazione temporanea del segnale di uscita ricevuto per la demodulazione, consentendo quindi che il chip elaboratore effettui detta demodulazione quando non effettua dette operazioni di transcodifica e di sintesi.

La presente invenzione riduce inoltre i costi di fabbricazione includendo una combinazione di una memoria lenta accoppiata al chip elaboratore per immagazzinare i codici di elaborazione impiegati dal chip elaboratore quando detti codici non debbono operare con zero tempi di attesa; ed una memoria veloce accoppiata al chip elaboratore per memorizzare temporaneamente codici di elaborazione utilizzati dal chip elaboratore quando detti codici sono fatti lavorare con zero tempi di attesa. RAM

veloci (con zero tempi di attesa), e EPROMS veloci con la medesima densità su chip sono molto costose. Al fine di ridurre i costi, i codici di elaboratore possono essere memorizzati in una EPROM lenta (con uno o più stati di attesa), e quando debbono essere fatte marciare procedure con zero tempi di attesa, il codice può essere caricato dalla memoria lenta alla memoria velocità e fatto marciare da questa.

Caratteristiche aggiuntive della presente invenzione sono descritte in riferimento alla descrizione della forma di realizzazione preferita.

#### BREVE DESCRIZIONE DEI DISEGNI

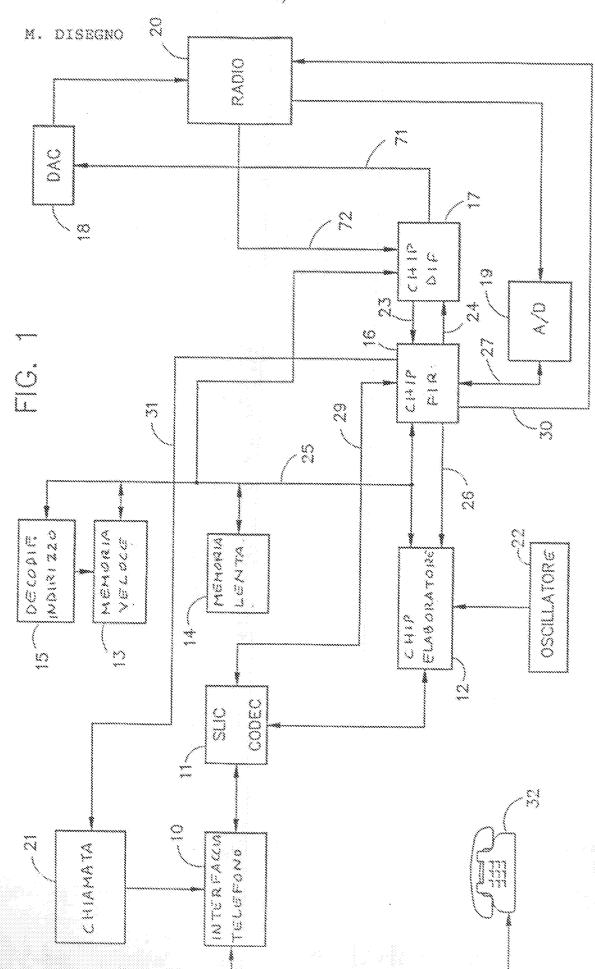

La figura 1 è uno schema a blocchi di una forma di realizzazione preferita dell'apparecchio di abbonato della presente invenzione;

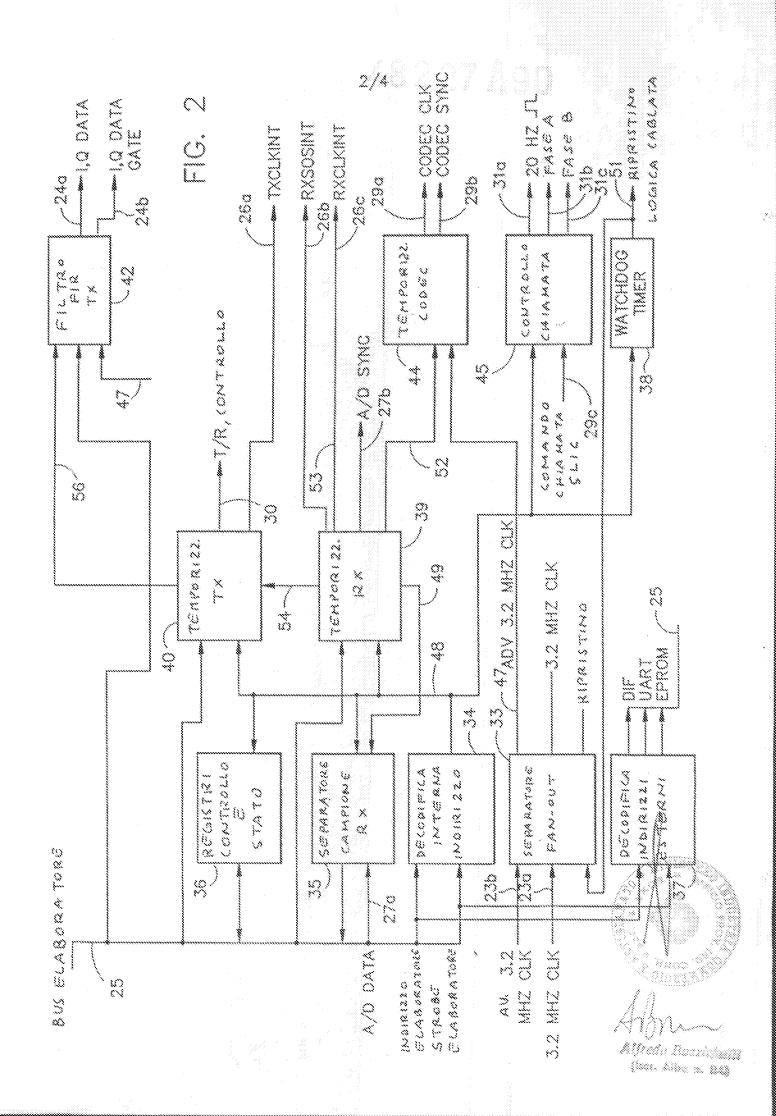

la figura 2 è uno schema a blocchi del chip FIR incluso nella forma di realizzazione mostrata in figura 1;

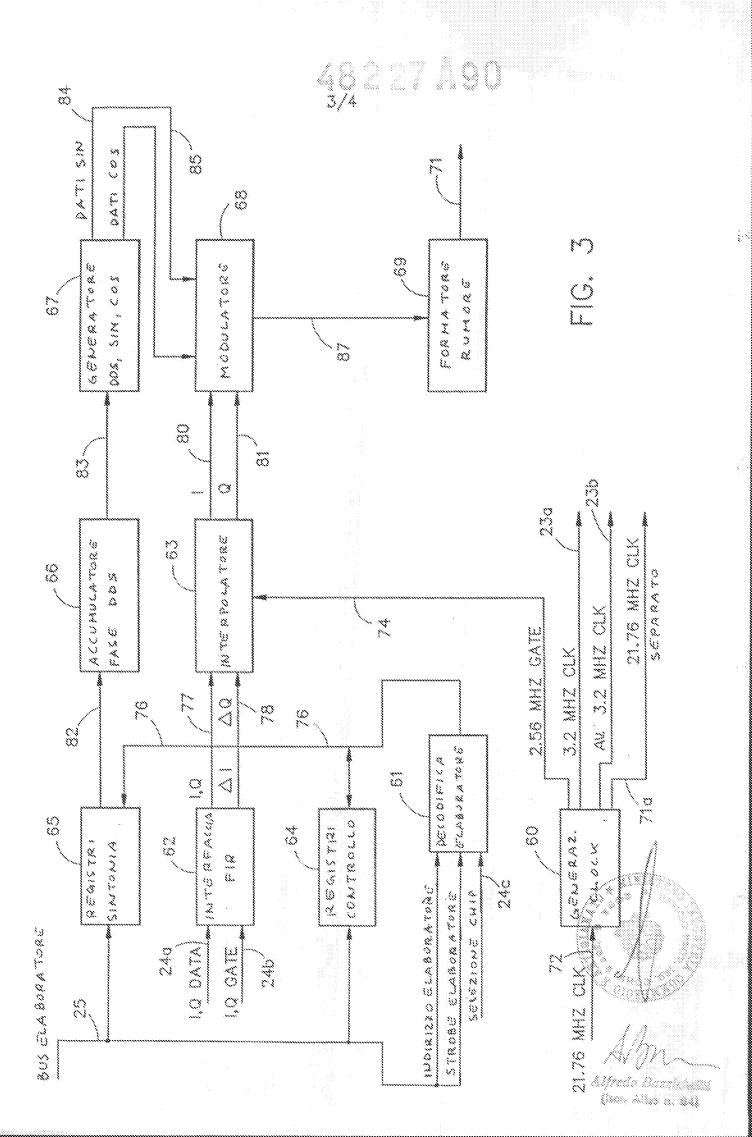

la figura 3 è uno schema a blocchi del chip DIF incluso nella forma di realizzazione mostrata in figura 1;

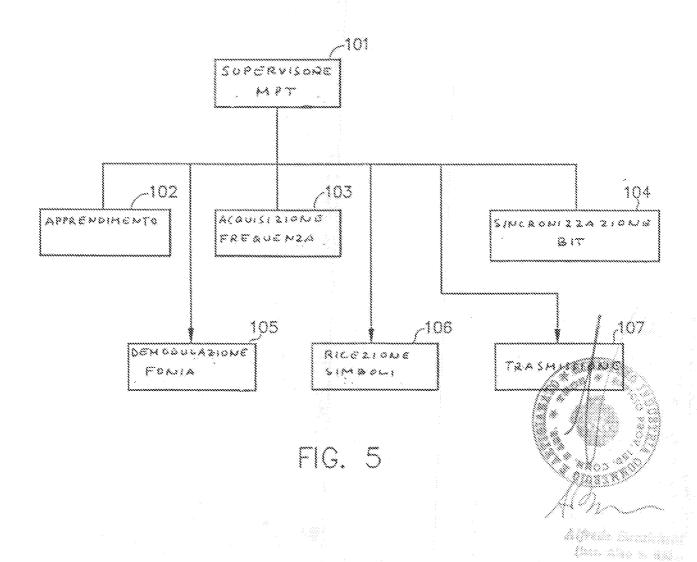

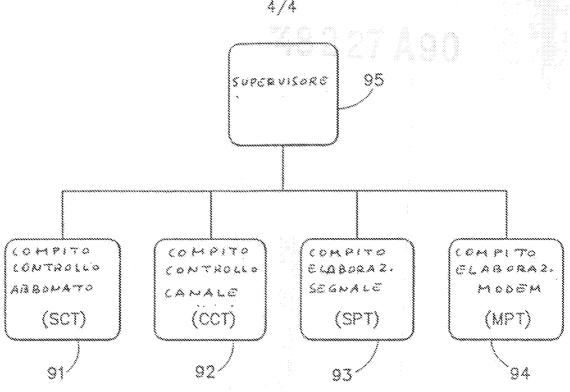

la figura 4 illustra i compiti di elaborazione effettuati dal chip elaboratore mostrato nella forma di realizzazione di figura 1.

La figura 5 illustra le routines di

elaborazione incluse nel compito di elaborazione di modem mostrato in figura 4.

# DEFIZIONE DI ABBREVIAZIONE ED ACRONIMI

Quanto segue è una definizione delle abbreviazioni ed acronimi qui utilizzati:

| A/D   | Analog to Digital                       |

|-------|-----------------------------------------|

| AGC   | Automatic Gain Control                  |

| ASIC  | Application Specific Integrated Circuit |

| BPSK  | Binary Phase Shift Keying               |

| CCT   | Channel Control Task                    |

| ccu   | Channel Control Unit                    |

| CRC   | Cyclic Redundancy Check                 |

| DAC   | Digital to Analog Converter             |

| DDS   | Direct Digital Synthesizer              |

| DIF   | Digital Intermediate Frequency          |

| DIP   | Dual In-line Package                    |

| DOR   | Data Output Ready                       |

| DPSK  | Differential Phase Shift Keying         |

| DSP   | Digital Signal Processing               |

| EPROM | Erasable Read Only Memory               |

| FIR   | Finite Impulse Response                 |

| 1/0   | Input/Output                            |

| LSB   | Least Significant Bit                   |

| MPT   | Modem Processing Task                   |

| MSB   | Most Significant Bit                    |

| MUX   | Multiplexer                             |

| PCM   | Pulse Code Modulation                   |

| PLL   | Phase Locked Loop                       |

| PWM   | Pulse Width Modulation                  |

| QPSK  | Quadrature Phase Shift Keying           |

| RAM   | Random Access Memory                    |

| RCC   | Radio Control Channel                   |

|       |                                         |

Residual Excited Linear Predictive

RELP

RF Radio Frequency

ROM Read Only Memory

RX Receive

RXCLK Receive Clock

RXSOS Receive Start of Slot

SCT Subscriber Control Task

SLIC Subscriber Line Interface Circuit

SPC Signal Processing Control

SPT Signal Processing Task

SPTCTL Signal Processing Task Controller

SSB Switch-hook Sample Buffer

TDM Time Division Multiplexing

TX Transmit

TXCLK Transmit Clock

UART Universal Asynchronous Receiver Transmitter

VLSI Very Large Scale Integration

XOR Exclusive Or

### DESCRIZIONE DELLA FORMA DI REALIZZAZIONE PREFERITA

Facendo riferimento alla figura 1, una forma di realizzazione preferita dell'apparecchio di abbonato della presente invenzione comprende un circuito 10 di interfaccia telefonica, un SLIC e un circuito 11 codec, un chip elaboratore 12, una memoria veloce 13, una memoria lenta 14, un decodificatore 15 di indirizzo, un chip FIR, un chip 17 DIF, un DAC 18, un convertitore 19 A/D, una radio 20, un circuito di chiamata 21 ed un

oscillatore 22.

Il chip 16 FIR che è un chip ASIC, viene interfacciato con il chip 17 DIF con le linee 23 e 24, verso il chip 12 elaboratore con il bus di elaboratore e la linea 26 verso il convertitore 19 A/D con la linea 27, verso il circuito SLIC e codec con la linea 29, verso la radio 20 con la linea 30 e verso il circuito 21 di chiamata con la linea 31,

Il circuito 10 di interfaccia telefonica viene interfacciato con un telefono 32 che converte onde sonore in un segnale di fonia di ingresso, e converte un segnale di fonia di uscita in onde sonore.

Lo SLIC ed il circuito 11 codec sono accoppiati al circuito 10 di interfaccia telefonica per convertire il segnale di ingresso in fonia in un segnale di ingresso digitale in banda base, che viene applicato al chip elaboratore 12.

In una forma di realizzazione alternativa (non mostrata) il chip elaboratore viene anche interfacciato direttamente con un UART per ricevere alternativamente segnali di ingresso digitali direttamente da ed inviare segnali di uscita digitali direttamente ad un dispositivo digitale di I/O. Il chip 12 elaboratore comprende un

elaboratore di segnale digitale modello TMS320C25 che transcodifica il segnale digitale di ingresso in banda base secondo un algoritmo RELP per fornire simboli di ingresso di dati digitali TX sul bus 25 di elaboratore. L'impiego di un elaboratore di segnale digitale per effettuare l'algoritmo RELP è descritto nella domanda di brevetto internazionale n. PCT/US85/02168, International Publication No. WO 86/02726, pubblicata il 9 Maggio 1986.

Il chip 16 FIR filtra a FIR i simboli digitali di ingresso e fornisce dati I, Q al chip 17 DIF sulle linee 24. Il chip 17 DIF interpola i simboli di ingresso digitali filtrati, e modula un segnale a frequenza intermedia con i simboli di ingresso interpolati per fornire un segnale di ingresso digitale modulato.

Il DAC 18 converte il segnale di ingresso digitale modulato in un segnale analogico di ingresso modulato.

La radio 20 trasmesse il segnale di ingresso analogico modulato alla stazione di base; e riceve e demodula il segnale di uscita analogico modulato dalla stazione di base.

L'oscillatore 22 è un oscillatore ad oscillazione libera, che fornisce segnali di clock

al chip 12 elaboratore.

Una descrizione della relazione tra l'apparecchio di abbonato e la stazione di base è contenuta nell'attestato di brevetto degli Stati Uniti n. 4.777.633.

Il convertitore A/D 19 converte il segnale di uscita analogico ricevuto demodulato in un segnale di uscita digitale contenente i simboli di uscita digitale.

Il chip 12 elaboratore sintetizza un segnale di uscita digitale in banda base dai simboli digitali di uscita. La sintesi dei simboli trancodificati RELP mediante un elaboratore di segnale è anche descritta nella pubblicazione internazionale wO 86/02726. Il chip 12 elaboratore inoltre effettua la cancellazione dell'eco come descritto nell'attestato di brevetto degli stati Uniti n. 4.697.261 a nome David T. K. Wang e Philip J. Wilson.

Lo SLIC ed il circuito codec 11 convertono il segnale di uscita digitale in banda base in un segnale di uscita in fonia che è fornito dal circuito di interfaccia telefonica verso il telefono 32.

Il chip 16 FIR consolida la funzionalità del

circuito in un dispositivo vLSI a fine di ridurre i costi di produzione dell'apparecchio di abbonato eliminando numerose parti separate ad integrazione a media scala.

Facendo riferimento alla figura 2, il chip 16 FIR, include un separatore 33 di fanout, un modulo 34 di decodifica interna, un separatore 35 di campione RX, registri 36 di controllo e di stato, ed un modulo 37 di decodifica di indirizzo esterno, un modulo 38 di temporizzatore di watchdog, un modulo 39 di temporizzazione RX, un modulo 40 di temporizzazione TX, un filtro 42 TX FIR, un modulo 44 di temporizzazione codec, ed un modulo 45 di controllo di chiamata.

Il chip 16 FIR fornisce la generazione di marcatore di frame da 45 millisecondi, generazione di marker di slot da 11,25 millisecondi, generazione di clock di simbolo a 16 KHz, circuiti di regolazione di temporizzazione, separazione del campione RX, separazione del campio TX, generazione di temporizzazione del codec a 8 KHz, decodifica di interfaccia di elaboratore, un generatore di temporizzazione di chiamata, decodifica esterna di indirizzo е generazione di ripristino temporizzatore di watchdog. Il chip 16 FIR separa

due simboli TX a 5 bit alla cadenza di 8 Khz. Il chip FIR 16 converte e filtra i simboli TX simboli di dati I e Q, con ciascuno di tali simboli che è da 10 bit ad una cadenza di 160 KHz. I dati I e Q sono interfogliati e forniti in uscita sul chip 17 DIF ad una cadenza di 320 KHz. Il chip 16 FIR separa i campioni di dati rX alla cadenza di 64 KHz e vengono eletti quattro campioni di dati RX dal chip 12 elaboratore alla cadenza di 16 KHz. Vengono generati dal chip FIR 16 segnali e clock di temporizzazione da un segnale di clock principale a 3,2 MHz. Il chip 12 elaboratore viene sincronizzato per queste cadenze di dati dagli interrupts di slot e di simbolo generati dal chip 16 FIR. Il clock di codec e di strobe di temporizzazione ha 8 KHz per il codec e l'elaboratore sono generati dal chip 16 FIR e sincronizzano nel tempo di campioni RX in arrivo. Il chip 16 FIR genera inoltre segnali di controllo e temporizzazione per controllare la forma e la temporizzazione della tensione di chiamata fornita dal circuito 21 di chiamata. Il modulo 38 di temporizzatore di watchdog fornisce un segnale di ripristino nel caso in cui il chip 12 elaboratore non esegua correttamente le istruzioni.

Il separatore 33 di fanout separa il segnale

di clock principale a 3,2 MHz ricevuto sulla linea 23a dal chip 17 DIF, un segnale di clock avanzato a 3,2 MHz ricevuto sulla linea 23b dal chip DIF 17, ed un segnale di ripristino ricevuto sulla linea 51 dal temporizzatore 38 di watchdog. A meno che non sia indicato altrimenti, ogni temporizzazione entro il chip FIR viene ricavata dal segnale di clock a 3,2 MHz sulla linea 23a. Il segnale di clock anticipato a 3,2 MHz sulla linea 23 si trova in anticipo rispetto al segnale di clock a 3,2 MHz sulla linea 23a di un ciclo di un segnale di riferimento a 21,76 MHz che è presente entro il chip DIF 17. Il segnale di clock a 3,2 MHz è ricavato dal riferimento a 21,76 MHz nel chip DIF 17 la minima larghezza di impulso è conseguentemente di 276 nanosecondi. Il segnale di clock a 3,2 MHz anticipato proveniente dalla linea 23b è fornito sale separatore 33 attraverso la linea interna 47 verso il filtro TX FIR 42 ed il modulo 44 di temporizzazione del codec. Il filtro TX FIR 42 viene realizzato in parte con una ROM che è di tipo pseudostatico e richiede che il suo ingresso di abilitazione venga disattivato dal segnale di clock anticipato a 3,2 MHz sulla linea 47 tra accessi successivi.

Il segnale di ripristino HW sulla linea 51 ripristina tutti i circuiti interni del chip 16 FIR e fornisce un reset di elettronica cablata sui moduli di figura 1.

I clock interni sono versioni disaccoppiate del segnale di clock principale a 3,2 MHz ricevuti sulla linea 23 o divisioni di questo clock.

Il modulo 34 di decoficazione di indirizzo interno consente al chip 12 di elaboratore di accedere alle funzioni interne del chip 16 FIR allo scopo di controllare tali funzioni e determinare il loro stato. Il modulo 34 di decodifica di indirizzo interno riceve indirizzi di elaboratore e strobe di elaboratore sul bus 25.Il modulo 34 di decodifica di indirizzo interno fornisce segnali di uscita sul bus interno 48.

I segnali di uscita del bus 48 dal modulo 34 di decodifica di indirizzo interno includono un segnale di abilitazione a lettura per il separatore 35 di campione RX, un segnale di controllo di scrittura ed segnali di lettura di stato verso i registri 36 di controllo e di stato, un segnale di scrittura verso il filtro TX FIR 42, segnali di slot e di scrittura di clock verso il modulo 39 di temporizzazione RX, un segnale di scrittura verso

il modulo 40 di temporizzazione TX e segnali di controllo sul modulo 42 di filtro TX FIR ed il separatore 35 di campione RX ed un segnale di strobe AM, che fa in modo che il modulo 39 di temporizzazione RX ripristini la temporizzazione di slot. soltanto uno dei rispettivi segnali di lettura o scrittura sul bus 48 proveniente dal modulo 34 di decodifica di indirizzo interno è attivo in un qualsiasi dato momento.

Il separatore 35 di campione RX riceve quattro campioni per ciascun tempo di simbolo RX dal convertitore 19 A/D attraverso la linea 27a ad una cadenza di 64 KHz separa due simboli di dati, con un totale di 8 campioni, e quindi invia tali campioni di dati al chip 12 elaboratore attraverso il bus 25 dell'elaboratore. Il separatore 35 di campione RX è realizzato come una RAM a doppia pagina. Il separatore 35 di campione RX riceve un segnale di abilitazione a lettura su un bus 48 interno da un modulo 34 di decodifica di indirizzo ed un segnale di strobe di scrittura su una linea interna 49 dal modulo 39 di temporizzazione RX.

I registri 36 di controllo e di stato consentono al chip 12 elaboratore di controllare le funzioni interne del chip FIR 16, e consentono al

chip 12 elaboratore di leggere lo stato del filtro 42 TX FIR e il separatore 35 di campione RX, ed altri segnali interni. I segnali di controllo sono forniti dal chip 12 elaboratore attraverso il bus 25 di elaboratore e le indicazioni di stato sono ricavate da vari moduli interne del chip FIR. Le indicazioni di stato sono forniti al chip 12 elaboratore attraverso il bus 25 dell'elaboratore. Le indicazioni di stato sono RX Underrun, RX Overrun, TX Underrun, TX Overrun, Start of Frame, RX Start di slot, Clock di simbolo TX, Clock di simbolo RX, e Overflow di filtro TX FIR.

I segnali di controllo che sono forniti dai registri 36 di controllo ai circuiti interni attraverso i bus 48 interno comprendono i seguenti: TX Enable, Modulation Level, Ringer Enable, Software Reset, Tristate e Watchdog Strobe.

Il segnale TX Enable indica l'inizio di uno slot TX basato sul ritardo TX stabilito dal modulo 40 di temporizzazione TX.

Il segnale Modulation Level è fornito dal modulo 39 di temporizzazione RX e determina se una lunghezza di slot sia di 180 o 360 simboli.

Il segnale Software Reset consente al chip 12 elaboratore di ripristinare le funzioni interne

entro il chip FIR 16.

Il segnale Tristate consente al chip 12 di elaboratore di disabilitare le uscite del chip FIR 16.

Il segnale Ringer Enable consente al chip 12 elaboratore di attivare e disattivare il circuito 21 di chiamata. Questo segnale fornisce una cadenza di due secondi e quattro secondi per il segnale di chiamata.

Il Watchdog Strobe consente al chip 12 elaboratore di ripristinare il modulo del temporizzatore di watchdog in modo da impedire un ripristino di elettronica cablata.

Il chi 12 elaboratore riceve un interrupt di clock RX (RXCLKINT) come segnale dal modulo 39 di temporizzazione RX attraverso la linea 26c quando sono stati scritti dati entro le prime quattro collocazioni della RAM a doppia pagina del separatore 35 di campione RX. Il chip elaboratore 12 legge quindi i campioni RX dalle prima quattro collocazioni della RAM a doppia pagina attraverso il bus 25 dell'elaboratore. A questo momento, vengono scritti campioni nelle successive quattro collocazioni della RAM a doppia pagina alla cadenza di 64 KHz. L'evento a 16 KHz è una derivata

dell'evento a 64 KHz che mantiene sincronizzati gli eventi di lettura e scrittura. Ciò assicura che le operazioni di lettura e scrittura non si verifichino allo stesso tempo su una qualsiasi collocazione di memoria ed inoltre assicura un adeguato tempo di risposta dal chip 12 elaboratore.

Un separatore di simbolo TX nel filtro 42 TX FIR riceve simboli TX dal chip 12 elaboratore attraverso il bus 25 di elaboratore e separa a memorizzazione temporanea fino a due simboli TX. Il chip 12 di elaboratore viene sottoposto ad interruzione ogni altro tempo di simbolo TX per scrivere altri due simboli nel separatore di simbolo TX.

Il separatore di simbolo TX nel filtro 42 TX FIR riceve un segnale di scrittura attraverso il bus 48 interno dal modulo 34 di decodifica di indirizzo interno.

Dopo ciascun segnale di interruzione di clock TX (TXCLKINT) a 8KHz sulla linea 26a il chip 12 elaboratore scrive in uscita due simboli TX a 5 bit. I dati sono un formato a codice gray del tipo DPSK. Il separatore di simbolo TX fornisce in uscita un simbolo ogni KHz per la elaborazione da parte del filtro 42 TX FIR. Questi dati sono

separati due volte per effetto di una assenza di sincronismo tra il chip FIR 16 ed il chip 12 elaboratore. L'ultimo valore di dati viene ripetuto fin quando sono scritti i nuovi dati. Dati di zero o nullo possono essere ripetuti in questo modo. Il separatore di simbolo TX viene azzerato durante un ripristino.

Durante l'apprendimento, viene inviata una sequenza fissa di simboli al chip FIR 16 per mezzo del chip 12 elaboratore. Il chip 16 FIR effettua un filtraggio del tipo FIR su questi simboli e fornisce in uscita coppie I, Q al chip DIF 17.

La radio 20 pone in anello i dati indietro verso il convertitore A/D 19. I campioni sono letti dal chip 12 elaboratore in un modo in linea e vengono regolati i coefficienti del filtro RX dell'elaboratore realizzati dal chip 12 elaboratore. La sola temporizzazione critica per l'apprendimento è generata dai moduli di temporizzazione 39, 40 di RX e TX.

Il modulo 39 di temporizzazione di RX genera tutti i clock e strobe di riferimento per la elaborazione dei simboli RX. La temporizzazione viene regolata dal chip 12 elaboratore in modo che la elaborazione possa essere sincronizzata sui

campioni RX ricevuti attraverso la linea 27a dalla stazione di base. Il modulo 39 di temporizzazione RX comprende un circuito di temporizzazione frazionata di clock RX ed un circuito temporizzazione di slot RX. Lo scopo di questi due circuiti è quello di sincronizzare la temporizzazione di ricezione del modem con il chip 12 elaboratore sui campioni RX ricevuti sulla linea 27a dalla stazione di base ed attraverso convertitore 19 A/D ed inoltre aggiusta il modulo 40 di temporizzazione TX ed il modulo 44 di temporizzazione del codec.

Il modulo 39 di temporizzazione RX è munito di un clock alla cadenza di 3,2 MHz e riceve i seguenti ingressi di segnale di controllo dal chip 12 elaboratore attraverso il bus 25 dell'elaboratore: un segnale di strobe AM, un segnale di RX Slot Clock write e un segnale di RX Bit Tracking.

**S**ono generate varie uscite dal modulo 39 di temporizzazione RX. Uno strobe di scrittura a 64 KHz viene fornito sulla linea 49 per controllare la scrittura del separatore 35 di campione RX. Viene fornito un segnale di strobe a 64 KHz A/DSYNC sulla linea 27b verso il convertitore A/D 19 per

sincronizzare il suo funzionamento. Viene anche fornito un segnale di strobe a 8 KHz verso il modulo 44 di temporizzazione codec attraverso la linea 52. Un segnale di interruzione del clock rX a 16 KHz (RXCLKINT) sulla linea 26c ed un segnale di interrupt di inizione di slot RX (RXSOSINT) sulla linea 26b sono forniti in uscita dal chip 12 elaboratore. Viene fornito su una linea 54 uno strobe di temporizzazione di slot pre-RX per controllare il modulo 40 di temporizzazione TX.

Il circuito di temporizzazione frazionaria nel modulo 39 di temporizzazione RX viene posizionato dal chip 12 elaboratore per generare il segnale di interruzione di inizione di slot RX sulla linea Il chip 12 elaboratore determina la collocazione di una lacuna AM (segnale di strobe) trasmessa dalla stazione di base durante acquisizione. Quando il chip 12 di elaboratore rivela il segnale di strobe AM, il circuito di temporizzazione di slot nel modulo 39 di temporizzazione RX viene ripristinato da un segnale di ripristino proveniente dal chip 12 elaboratore. Ciò allinea i marcatori di frame e di slot sul segnale di strobe AM. Il marcatore di frame è un impulso pari a 62,5 microsecondi che si presenta

ogni 45 millisecondi. Il marcatore di slot è un impulso da 62,5 microsecondi che si ripete ogni 11,5 millisecondi oppure ogni 22,5 millisecondi quando si trova nel modo QPSK.

I simboli RX in attivo sono demodulati dal chip 12 elaboratore e viene ulteriormente regolata, se necessario, la temporizzazione. Per regolare il clock di simbolo RX a 16 KHz, il chip elaboratore forza il circuito di temporizzazione frazionaria (inseguimento di bit) per accorciare o allungare lo strobe da 64 KHz fino a 50 cicli di 3,2 MHz.

Il chip 12 elaboratore sorveglia la relazione fra i simboli RX nella temporizzazione di frame ed effettua regolazioni conseguenti nel clock RX a 16 KHz. Quando il clock RX viene regolato vengono anche cambiati i marcatori di slot e di frame dato che questi sono una derivata del clock RX.

Per mantenere sincronizzati nella temporizzazione di frame il numero di campioni Pulse Code Modulated (PCM) forniti a e dal circuito 11 di SLIC e codec, il modulo 39 di temporizzazione RX controlla il modulo 44 di temporizzazione del codec.

Il modulo 40 di temporizzazione tX comprende un circuito di ritardo TX, ed un circuito di

temporizzazione di controllo TX. Questi circuiti generano un segnale di interruzione di clock TX (TXCLKINT) che viene fornito al chip 12 elaboratore attraverso la linea Il modulo 26a. temporizzazione TX è sincronizzato con il modulo 39 di temporizzazione RXdallo strato di temporizzazione di slot pre-RX, che è fornito al modulo di temporizzazione TX dal modulo 39 di temporizzazione RX sulla linea 54 ed impiegato per ripristinare il circuito di ritardo TX che a sua volta genera il marcatore di slot temporizzazione del clock TX è basata sul clock interno a 3,2 MHz.

Il chip 12 elaboratore controlla anche i circuiti di ritardo TX e di temporizzazione TX fornendo segnali di controllo di scrittura di dati TX sul bus 25 dell'elaboratore.

Il modulo 40 di temporizzazione TX fornisce un segnale di controllo T/R sulla linea 30 verso la radio 20. Questo segnale determina se la radio stia trasmettendo o ricevendo dati.

Il modulo 40 di temporizzazione TX controlla anche lo spostamento del simbolo TX l'indirizzo della RHM, la temporizzazione di accumulazione, e la memorizzazione del prodotto I, Q per l'uscita

verso il chip 17 DIF.

Il modulo 40 di temporizzazione TX fornisce segnali di controllo sulla linea 56 per mantenere sincronizzato il filtro 42 TX FIR sulla temporizzazione di simbolo e di slot TX. Una tale sincronizzazione viene effettuata secondo il marcatore di temporizzazione di slot tX. Dopo un ripristino, il modulo 40 di temporizzazione TX genera in modo attivo segnale di controllo sulla linea 56 una volta che inizia uno slot TX.

Il filtro 42 TX FIR comprende una ROM che realizza un filtro FIR fornendo prodotti di dati I e Q in risposta alla ROM che è indirizzata per la consultazione da una combinazione di simboli TX ricevuti dal chip 12 elaboratore attraverso il bus 25 di elaborazione ed i conteggi di coefficiente SINE e COSINE forniti da un contatore entro il modulo 42 del filtro TX FIR. Il filtro 42 TX FIR accumula sei prodotti sequenziali I e Q e memorizza i risultati per la uscita verso il chip 17 DIF attraverso la linea 24a.

La frequenza minima richiesta per il funzionamento del filtro 42 TX FIR è determinato dalla cedenza di simbolo (16 KHz) moltiplicata per il numero di campioni (2) I e Q moltiplicata per il

nuero di coefficienti (10) moltiplicata il numero di prese (6) = 1,92 MHz. Il clock principale a 3,2 MHz soddisfa questo requisito minimo di frequenza. Sono aggiunti periodi di attesa per compensare tempi di esecuzione più veloci.

Il modulo 40 di temporizzazione TX opera su un clock ad una frequenza di clock di 3,2 MHz che definisce un periodo di uno stato. Dato che questa cadenza di clock è superiore al minimo richiesto di 1,92 MHz il filtro TX FIR genera segnale per i primi sei tra i dieci periodi di stato.

Ciascun nuovo simboli TX deve essere caricato in una memoria temporanea circolare nel filtro 42 TX FIR alla cadenza di 16 KHz. Il nuovo simbolo TX e i procedimenti cinque simboli TX sono memorizzati nella memoria temporanea circolare. Il più vecchio simboli TX viene lasciato cadere quando viene introdotto un nuovo simbolo TX. La cadenza di uscita dal filtro 42 TX FIR è di 320 KHz. Da ciascun simbolo TX vengono generati dieci valori di dati I e dieci valori di dati q. La tabella 1 seguente mostra come si può ricavare da ciascun valore a 5 bit informazione di I, Q e di nullo.

BIT 1 BIT 2 BIT 3 BIT 4 BIT 5 I & Q LSB I & Q I MSB Q MSB NULL

TABELLA 1

I dati nella memoria tampone circolare sono ruotati ogni 6 di 10 stati. Un nuovo simbolo TX e cinque precedenti simboli TX risiedono nella memoria temporanea circolare per venti di questi dieci periodi di stato. La parte di coefficiente dell'indirizzo ROM viene anche aumentata ogni sei tra dieci periodi di stato, un accumulatore nel filtro 42 TX FIR raggiunge i risultati di ciascun prodotto di dati I forniti dalla ROM per ciascuno dei sei periodi di stato. Conseguentemente, il registro accumulatore viene azzerato per la prima somma, e ciascun risultato successivo di somma viene inserito a clock in un registro di retroazione dell'accumulatore 10 in modo che esso essere sommato al prodotto di consultazione. Una volta che si sono verificate sei addizioni, il risultato viene inserito a clock in un registro di scorrimento di uscita. Lo stesso procedimento si verifica per gli stessi coefficienti e i prodotti dei dati q forniti dalla ROM per esempio ciascun simbolo TX.

Le linea di indirizzo di ROM consentono sessanta consultazioni di coefficienti COS e sessanta coefficienti SIN, per quattro possibili indici di dati I, Q. Ciò richiede sette linee di

indirizzo per i coefficienti e due linee di indirizzo per i dati I, Q. La uscita del filtro FIR richiede dieci bit. Sono richiesti due bit extra per mantenere la precisione della parte frazionaria del valore di consulatazione. Ciò rende la grandezza della ROM pari a 512 X 12. Il MSB dell'indice di dati I, Q viene fatto passare attorno alla ROM in un circuito di complemento ad 1, che forza la uscita della ROM ad essere invertita oppure non invertita.

Se l'indirizzamento di simbolo della ROM è un simbolo nullo, il bit di nullo controlla quattro delle sette linee di indirizzo di coefficiente. Dato che sono impiegate sette linee di indirizzo per la consultazione di coefficiente, ciò fornisce 128 collocazioni. Sono necessari soltanto 120 coefficienti. Ciò lascia otto collocazioni non utilizzate. Sono memorizzate in questa collocazione valori di zero in modo che l'informazione di nullo possa essere facilmente posta in uscita dalla ROM.

Una funzione di complemento a 2 viene realizzata mediante un complemento ad 1 e con un riporto ad 1 logico nel sommatore successivo. La uscita del sommatore è ricondotta attorno all'ingresso del sommatore per successive addizioni

o uscite attraverso un MUX verso un registro di scorrimento di uscita. La uscita viene arrotondata con l'impiego dei soli dieci bit superiori.

Le uscite della memoria temporanea circolare del filtro TX FIR sono posizionate a zero dopo un ripristino. Ciò consente che venga elaborata la informazione di nullo fin quando vengono caricati nuovi valori di simbolo TX. I dati I sono elaborati per primi e seguiti dai dati q. Il segnale di interrupt di clock TX si presenta soltanto durante uno slot TX. L'elaboratore non è a conoscenza del momento in cui uno slot TX inizia o finisce ad eccezione che rispondendo a questa interruzione. Il segnale ha una durata di attivo basso di un ciclo del clock a 3,2 MHz per garantire che l'interrupt non sia attivo una volta che è stato servito. Lo interrupt di TX Clock si presenta ogni coltra tempo di simbolo (16 KHz/2).

Lo interrupt di RX Clock si presenta per un frame intero. Il chip elaboratore maschera questo interrupt impiegando come maschera il marcatore di RX slot. L'interrupt di RX clock ha una durata attiva bassa di un ciclo del clock a 3,2 MHz.

Lo interrupt di RX Start of Slot si presenta ogni 11,25 millisecondi ed ha una durata attiva

bassa di un ciclo di clock a 3,2 MHz.

Ciascun segnale di interrupt viene forzato ad uno stato inattivo alto a seguito di un ripristino.

Il modulo 44 di temporizzazione del codec genera strobe di temporizzazione ed invia il necessario segnale di clock attraverso le linee 29 verso il circuito 11 di \$LIC e codec per fare in modo che vengano trasferiti 8 bit di dati tra il codec e l'elaboratore alla cadenza di 8 KHz. Il codec 11 riceve e trasmette 8 bit di dati ogni 8 kHz. Il modulo 44 di temporizzazione di codec invia un segnale di clock di codec sulla linea 29a ed un segnale di sincronismo di codec sulla linea 29b. Il segnale di clock di codec sulla linea 29a è generato ad una cadenza di 1,6 MHz ottenuta dividendo per due il clock avanzato a 3,2 MHz. Viene ricevuto un impulso a 8 KHz di un periodo a 3,2 MHz dal circuito 39 di temporizzazione di RX e viene di nuovo ripassato con il clock per verificarsi in un periodo a 1,6 MHz, e conseguentemente si garantisce che si presenti con i fronti di salita del clock a 1,6 MHz. Con questi due segnali, viene effettuato il trasferimento dei dai PCM tra il codec 11 ed il chip 12 elaboratore. Ciò consente che i dati PCM di abbonato vengono

sincronizzati con i dati PCM della stazione base.

Il modulo 45 di controllo di chiamata risponde ad un segnale di controllo di abilitazione di chiamata che si origina nel chip 12 di elaboratore ed è fornito dal registro 36 di controllo e di stato sul bus 48 interno generando un segnale ad onda quadra a 20 Hz sulla linea 31a e due segnali di controllo di fase a 80 KHz, PHASEA sulla linea 31b e PHASEB ed inviando questi segnali al circuito 21 di chiamata. Il segnale ad onda quadra a 20 Hz sulla linea 31a controlla la polarità della tensione di chiamata fornita dal circuito 21 di chiamata al circuito 10 di interfaccia telefonica. I segnali di fase a 80 KHz sulle linee 31b e 31c controllano la sorgente di alimentazione modulata ad ampiezza di impulso nel circuito 21 di chiamata.

Un segnale di comando di chiamata \$LIC o di ripristino sulla linea 29c dalla parte SLIC del circuito 11 di SLIC e di codec disinserisce e prende azione su questi segnali sulle linee 31a, 31b e 31c dopo che il segnale di abilitazione alla chiamata che si presenta nel chip 12 di elaboratore li ha attivati. Ciò assicura che il dispositivo di chiamata sia disinserito se si presenta un ripristino o se il microtelefono viene sollevato.

Dato che il circuito 21 di chiamata genera una tensione elevata e dissipa molta potenza, questa tensione non viene generata ad eccezione di quando ciò sia richiesto dal chip 12 di elaboratore.

esterno genere selezioni di chip sul bus 25 dell'elaboratore che sono impiegate dal chip 12 dell'elaboratore per accedere al chip 17 DIF, l'elettronica cablata UART, e le EPROM di memoria lenta 14 in segmenti di indirizzo distinti e separati. Il chip 12 di elaboratore fornisce otto linee di indirizzo MSB, segnali di spazio di dati, e di spazio di programma. Questi sono decodificati per generare le appropriate selezioni di chip.

Il modulo 38 di temporizzatore di watchdog genera un impulso di reset di elettronica cablata da 50 millisecondi sulla linea 51, che ripristina tutti i moduli dei chip 16 FIR e tutti i moduli di unità di abbonato di figura 1. Il modulo 38 di temporizzatore di watchdog genera un impulso se questo non viene resettato entro un periodo di 512 millisecondi da segnale di strobe di Watchdog fornito sul bus 48 dai registri 36 di controllo e di stato.

Il chip 17 DIF viene interfacciato sul chip 12

di elaboratore dal bus 25 di elaboratore, verso il chip 26 FIR con le linee 23 e 24, verso il DAC 18 con la linea 721 e verso un oscillatore nella radio 20 come la linea 72.

L'oscillatore nella radio 20 fornisce un segnale di clock principale a 21,76 MHz sulla linea 71 verso il chip 17 DIF.

Facendo riferimento alla figura 3, il chip 17 DIF comprende un generatore 40 di clock, un modulo 61 di decodifica di elaboratore, un modulo 62 di interfaccia di chip FIR, un interpolatore 63, un registro 64 di controllo, registri sintonizzazione, un accumulatore 66 di fase DDS, un modulo 67 di generatore DDS SIN e COS, modulatore 68 e un formatore di rumore 69. combinazione l'accumulatore 66 di fase DDS ed il generatore 67 DDS SIN COS costituiscono sintetizzatore digitale diretto (DDS) sintetizzare digitalmente un segnale a frequenza intermedia digitale.

Il chip 17 DIF è anche esseo un chip ASIC, che viene mappato come memoria di dati per l'elaboratore.

Il chip 17 DIF funziona in uno di due modi operativi, un modo a generazione di portante

modulata, ed un modo a portante pura. Nel modo di generazione a portante modulata, dati in banda base sono portati in ingresso nel dominio I,Q e questi dati sono impiegati per modulare la portante pura generata dalla funzione DDS del chip 17 DIF. Nel modo Pure Carrier Generation, gli ingressi di dati in banda base sono ignorati e viene fornita al DAC 18 una portante non modulata dal DDS.

Il generatore 60 di clock genera tutti i clock e temporizzazioni entro il chip 17 DIF ed anche genera il segnale di clock a 3,2 MHz ed il segnale di clock avanzato a 3,2 MHz che sono applicati al chip 16 FIR sulle linee 23a e 23b. I due segnali primari di temporizzazione impiegati entro il chip 17 DIF sono un clock a 21,76 MHz ed un segnale di abilitazione di interpolazione a 2,56 MHz. Il clock a 3,2 MHz viene impiegato internamente per spostare i dati I e Q sulla linea 24a dal chip 16 FIR entro il modulo 62 di interfaccia FIR.

Il generatore 60 di clock separa il clock a 21,76 MHz ricevuto sulla linea 72 dall'oscillatore nella radio 20 e fornisce un segnale di clock separato a 21,76 MHZ sulla linea 71a. Tale separazione viene effettuata per fornire una sufficiente capacità di pilotaggio per funzioni

interne e per minimizzare le sfasature di clock. Il clock a 21,76 MHz separato fornisce anche un clock per il DAC 18 ed altre circuiterie esterne.

Il generatore 60 di clock fornisce il segnale di clock a 3,2 Mhz dividendo il clock a 21.76 MHz per 6 e per 8 nella sequenza seguente: 6-8-6-8-6 il che dà origine ad un divisore medio di 6,8 (21,76 ÷ 6,8 = 3,29). L'effetto di questa variazione per ciclo è un periodo minima di 276 ns ed un periodo massimo di 368 ns. Una versione avanzata del segnale di clock a 3,2 MHz viene anche essa generata come il segnale di clock avanzato a 3,2 MHz sulla linea 23b. Ambedue i clock sono identici con la eccezione che il segnale deselezionato della ROM sulla linea 23b si trova in anticipo rispetto al segnale di clock a 3,2 MHz sulla linea 23a di un ciclo di clock a 21,76 MHz.

Il generatore 60 di clock fornisce il segnale di abilitazione a 2,56 MHz sulla linea interna 74 dividendo il clock a 21,76 MHz per 8 e per 9 in una sequenza pari (8-9-8-9-...), la qual cosa dà origine ad un divisore medio di 8,5 (21,76 ÷ 8,5 = 2,56 MHz). Questo segnale viene impiegato dall'interpolatore 63 e dal modulatore 68.

Il modulo 61 di decodifica dell'elaboratore

consente all'elaboratore di controllare tutte le funzioni interne del chip 17 DIF. Il modulo 61 di decodifica dell'elaboratore decodifica indirizzi dell'elaboratore e ali strobe dell'elaboratore ricevuti dallo spazio dati sul bus 25 dell'elaboratore per fornire strobe interni di scrittura che sono disposti sul bus 76 interno verso il registro 64 di controllo ed i registri 66 di sintonia per consentire al chip di elaboratore di scrivere dati di controllo e di configurazione. In ogni dato momento è attiva soltanto una uscita dal modulo 61 di decodifica dell'elaboratore. Gli indirizzi di elaboratore determinano quale uscita venga generata. Se viene scelta una funzione entro lo spazio di indirizzo del chip 17 DIF, diviene attivo un segnale di selezione id chip sulla linea 24c dal chip 16 FIR.

Il modulo 62 di interfaccia FIR riceve i campioni IR e Q dal chip 16 FIR sulla linea 24a in un formato serie e li converte in un formato parallelo a 10 bit nella quale forma questi sono applicati al modulo interpolatore sulla linea 77. I segnali di abilitazione I,Q sulla linea 24b dal chip 16 FIR sono impiegati per distinguere i dati I dai dati q. Il modulo 62 di interfaccia FIR sottrae

anche i precedenti campioni I e Q dai campioni correnti per formare campioni I e Q che sono quindi spostati a destra di quattro posizioni (÷ 16) per formare il corretto incremento per il modulo interpolatore sulla linea 78. Dato che il modulo 62 di interfaccia FIR fornisce dati all'interpolatore 63, viene inviato un segnale di sincronismo dal modulo 62 di interfaccia FIR verso il generatore 60 di clock per sintonizzare l'impulso di abilitazione a 2,56 MHz fornito sulla linea 74.

L'interpolatore 63 accumula i termini I, Q alla cadenza di 160 KHz x 16 = 2,56 MHz e fornisce campioni interpolati I e Q verso il modulatore 68 sulle linee 80 ed 81, rispettivamente. L'interpolatore 63 effettua una interpolazione lineare x16 al fine di ridurre le spurie di campionamento a 160 KHz presenti nei dati in banda base ricevuti dal chip FIR 16.

L'interpolatore 63 successivamente accumula i campioni I e Q per generare una uscita alla cadenza di 2,56 MHz. Al termine di un ciclo di accumulazione (16 iterazioni), l'uscita dell'interpolatore deve essere uguale ai campioni correnti I e Q. Ciò è critico dato che il prossimo

ciclo di accumulazione inizia il suo ciclo con i dati correnti. Per assicurare che i dati siano corretti, durante l'ultimo ciclo di accumulazione i dati correnti I e Q sono portati in ingresso direttamente sul registro di uscita dell'interpolatore in luogo della uscita del sommatore (che dovrebbe avere gli stessi dati).

I registri 64 di controllo sono impiegati per controllare e configurare il chip 17 DIF e per selezionare i modi operativi. Tutti i registri 64 di controllo sono caricati dal chip 12 elaboratore attraverso il bus 25 dell'elaboratore.

Vi sono tre registri 64 di controllo. Il primo registro di controllo registra un segnale CW MODE, un segnale AUTO TUNE H-L, un segnale AUTO TUNE L-H. Il secondo registro di controllo registra un segnale SIGN SELECT, un segnale OUTPUT CLOCK PHASE SELECT, un segnale INTERPOLATOR ENABLE, un segnale SERIAL PORT CLOCK SELECT, un segnale SERIAL/PARALLEL SELECT, ed un segnale MODE funzioni di controllo QUADRATURE ENABLE. Le associate con questi segnali sono descritte in seguito alla conclusione della descrizione degli altri moduli del chip 17 DIF.

Il terzo registro di controllo abilita e

specifica i coefficienti per il formatore di rumore 69.

Vi sono tre registri 65 di sintonia ad 8 bit per memorizzare 24 bit di dati di incremento di fase per specificare la frequenza del DDS. Ciò fornisce una parola di sintonia a 24 bit che consente una risoluzione di frequenze di (cadenza di campione)/ $2^{24} = 21,76 \text{ MHx}/2^{24} \approx 1,297 \text{ Hz}$ . La frequenza di uscita del DDS è eguale alla risoluzione moltiplicata per la parola di sintonia a 24 bit.

I registri 65 di sintonia sono caricati dal chip 12 elaboratore attraverso il bus 25 dell'elaboratore. La parola di sintonia viene separata due volte dai registri 12 di sintonia in modo che il chip 12 elaboratore possa scrivere dati in questi registri liberamente senza alterare il funzionamento corrente del DDS.

La parola di sintonia viene caricata dai registri tampone di sintonia nei registri di sintonia di uscita ogni volta che viene emesso un comando TUNE. Il comando TUNE è sincronizzato sul clock a 21,76 MHz per fornire una transizione sincrona.

L'accumulatore 66 di fase DDS esegue una

accumulazione modulo 2<sup>24</sup> dell'incremento di fase fornito sulla linea 82 dai registri 65 di sintonia. La uscita dell'accumulatore 66 di fase rappresenta un valore di fase digitalizzato che è fornito sulla linea 83 al generatore 67 DDS SIN e COS. Il generatore 67 DDS SIN e COS genera una funzione sinusoidale. Un DDS funziona sul principio che si può generare una forma d'onda digitalizzata accumulando variazioni di fase ad una cadenza più elevata.

La parola di sintonia, che sarà diversa per divresi apparecchi di abbonato, rappresenta una variazione di fase nell'accumulatore di fase 66. La uscita dell'accumulatore 66 può variare da O fino a 1. Questo intervallo rappresenta variazione di fase di 360°. Anche se l'accumulatore 66 lavora in binario standard, questa rappresentazione di fase digitalizzata può essere portata all'ingresso di un generatore di forma d'onda per produrre una qualsiasi forma d'onda arbitraria. Nel chip 17 DIF, i generatori 67 DDS SIN COS producono funzioni SIN cos rispettivamente sulle linee 84 e 85.

Il periodo della funzione di forma d'onda è basato sul tempo richiesto per effettuare una

sommatoria sul limite superiore dell'accumulatore (2<sup>24</sup>-1). Ciò significa che se viene fornito un grosso incremento di fase, allora questo limite verrà raggiunto al più presto. Al contrario, se è dato un piccolo incremento di fase, allora è necessario un tempo più lungo. L'accumulatore di fase 66 effettua una semplice somma degli incrementi di fase in ingresso e può essere rappresentato dalla seguente equazione:

$$\Phi_{\mathbf{T}} = \Sigma_{i=n}^{n} \Phi_{inc} \{Eq.1\}$$

٠.,

3

ą

Dove n è il numero delle iterazioni e  $\Phi_{\text{inc}}$  sono semplicemente i dati forniti sulla linea 82 dai registri 65 di sintonia.

Nella forma di realizzazione qui descritta del chip 17 DIF, il valore di  $\Phi_{\rm T}$  è vincolato alla lunghezza dell'accumulatore per avere un massimo di  $2^{24}$ . Conseguentemente, la fase corrente può essere descritta come:

$$\Phi_{t} = (\Phi_{t-1} + \Phi_{inc}) \text{modulo } 2^{24} \{\text{Eq.2}\}$$

Dato che il clock di accumulazione è fissato al clock di ingresso principale a 21,76 MHz, ciò dà origine al fatto che un ciclo completo impiega  $2^{24}/\Phi_{\rm inc}$  iterazioni su a per un periodo di iterazione di 1/21,76 MHz. Conseguentemente, l'intero ciclo impiega il seguente tempo:

224

21,76MHz • Φinc

Dato che questo periodo rappresenta un ciclo di 360 gradi, il reciproco di questa espressione rappresenta una frequenza. La frequenza DDS è conseguentemente

$$f_{DDS} = \frac{21,76MHz \cdot \Phi_{inc}}{224}$$

{Eq.3}

Nel modulo 67 di generazione DDS SIN, COS, vengono generate le forme d'onda SIN e COS in modo che si possa effettuare una miscelazione completa da parte del modulatore. Ciascuna viene generata da tabelle consultazione (lookup) rappresentano una stima grossolana e fine della forma d'onda. I due valori sono sommati per formare segnali di uscita di dati SIN e COS compositi a 12 bit con segno e complemento a 2 sulle linee 84 e 85. Le tabella di consultazione sono implementate in ROM che sono indirizzate dai 14 bit più significativi per segnare sulla linea 83 dall'accumulatore 66 di fase DDS.

Si desidera avere tanta risoluzione in fase ed ampiezza per quanto sia pratico. Nella

progettazione del chip 17 DIF, sono disposti 14 bit di ingresso di fase e 12 bit di uscita di dati di ampiezza nella parte di generazione di forma d'onda. Se venisse intrapreso un approccio a "forza bruta" per generare questi dati sarebbero necessarie tabelle estremamente grandi per produrre tutti i possibili valori di fase e di ampiezza (ad esempio 16K parole x 12 bit ciascuna). minimizzare la grandezza della tabella, il chip 17 DIF fa uso di simmetria di quadrante e decomposizione trigonometrica dei dati di uscita. Dato che le forme d'onda sIN e COS hanno una simmetria di quadrante, i due bit più significativi dei dati di fase sono impiegati per ribaltare specualmente i dati un singolo quadrante sugli assi X ed Y. Per la funzione SIN, la ampiezza dell'onda negli intervalli tra  $\pi$  e  $2\pi$  è esattamente il negato della ampiezza nell'intervallo tra 0 e  $\pi$ . Per la funzione COS, la ampiezza dell'onda nell'intervallo tra  $\pi$  fino a  $3\pi/2$  è esattamente il negato della ampiezza nell'intervallo  $3\pi/2$  fino a  $\pi/2$ . I due MSB dell'accumulatore di fase specificano il quadrante (00->1, 01->2, 10->3, 11->4). Per la funzione SIN, lo MSB dei dati di fase viene impiegato per negare i dati positivi generati per i primi due quadranti.

Per la funzione COS, viene impiegato un XOR dei MSB di dati di fase per negare i dati positivi generati per i quadranti 1 e 4.

La tecnica di cui sopra riduce i requisiti di memoria per un fattore di 4. Ciò dà origine ad un requisito di memoria di 4K parole x 12 bit. Per ridurre ulteriormente la grandezza della tabella, viene effettuata sugli angoli una decomposizione trigonometrica. Viene impiegata la seguente identità trigonometrica:

$\sin\theta = \sin(\Phi_1 + \Phi_2) = \sin\Phi_1\cos\Phi_2 + \sin\Phi_2\cos\Phi_1$  {Eq.4} Ponendo  $\Phi_2 << \Phi_1$  conduce alla approssimazione completa come segue:

$\sin\theta \approx \sin\Phi_1 + \sin\Phi_2\cos\Phi_1 \{Eq.5\}$

Non è necessario impiegare tutti i bit di  $\Phi_1$  quando si calcola il secondo termine dell'equazione per cui  $\widehat{\Phi}_1$  è un sottoinsieme di  $\Phi_1$ .

Per generare la funzione COS, si può usare la medesima approssimazione dato che

$cos\theta = sin(\theta+\pi/2) \{Eq.6\}$

Ciò dà origine ad una modifica delle variabili  $\Phi_1$  &  $\Phi_1$  quando si calcola la funzione COS. I dati memorizzati nella ROM COS incorporeranno questa modifica di angolo per cui non sono richieste variazioni sui dati di fase.

I1 modulatore 68 miscela i campioni interpolati I e Q sulle linee 80 ed 81 con il frequenza sequale а intermedia digitale rappresentata dai dati di funzione complessa SIN e COS sulle linee 84 ed 85 per produrre un segnale digitale modulato a frequenza intermedia sulla linea 87.

I campioni I, Q interpolati e la uscita DDS sono miscelati digitalmente da due moltiplicatori 10X12. Le uscite del processo di miscelazione sono quindi sommate su un sommatore a 12 bit per formare una portante modulata. E' possibile modificare il funzionamento del modulatore 68 forzando l'ingresso I a tutti zeri e l'ingresso Q a tutti uno. L'effetto di ciò è che un moltiplicatore fornirà in uscita tutti zeri e l'altro fornirà in uscita il segnale dal solo generatore 67 DDS SIN, COS. La somma di questi due segnali fornirà un segnale a frequenza intermedia digitale non modulato.

Il modulatore 68 crea un segnale a frequenza intermedia digitale modulato sulla linea 87 secondo la seguente equazione:

## $f(t) = I \cdot COS(\Phi(t)) + Q \cdot SIN(\Phi(t)) \{Eq.7\}$

La uscita a 12 bit dal generatore 67 DDS SIN e COS moltiplicata per i campioni a dieci bit

interpolati I e Q dall'interpolatore 63 per generare due prodotti a 12 bit. I due prodotti sono poi sommati (combinati) per generare una uscita modulata a 12 bit sulla linea 87.

Dato che ambedue i moltiplicatori I e Q generano prodotti a 12 bit, è possibile che si verifichi un trabocco quando vengono combinate le loro uscite. Conseguentemente è necessario assicurare che la ampiezza del vettore generato da I e Q non superi mai 1 supponendo che I valore assoluto e Q valore assoluto siano numeri frazionari ≤1). Se ciò non viene assicurato allora è possibile un trabocco sul sommatore modulatore:

Il formatore 69 di rumore fornisce un segnale a frequenza intermedia digitale modulato o non modulato filtrato sulla linea 71 verso il DAC 18. Il formatore 69 di rumore è progettato per far decrescere la quantità di potenza di rumore sullo spettro di uscita provocata da errori di quantizzazione di ampiezza.

Il filtro 69 di rumore lavora sul fatto che il rumore di quantizzazione è un normale processo casuale e che la densità spettrale di potenza del processo è piatta sulla banda di frequenza. Il desiderato segnale di uscita viene sovrapposto

sulla cima di questo pianerottolo di rumore di quantizzazione. Il dispositivo formatore di rumore è semplicemente un filtro semplice a più prese a risposta impulsiva finita (FIR). Il filtro crea uno zero che fa decrescere la potenza di rumore di quantizzazione in una certa parte della banda di frequenze. Quando il segnale desiderato viene sovrapposto sullo spettro di rumore filtrato, il SQNR effettivo aumenta.

La funzione di trasferimento del filtro FIR è data da

$$H(z) = 1 + bz^{-1} - z^{-2} \{Eq.8\}$$

Uno stadio sommatore di due crea un secondo valore di presa di b nell'intervallo di +1,75 fino a -1,75 (in pesi binari di 0, 0,25, 0,50, 1,0) che sposteranno allo zero del filtro la banda di frequenza e di uscita, in modo che questo possa essere collocato quanto possibile in prossimità alla frequenza di uscita desiderata per una massima prestazione SONM.

La frequenza di zero può essere calcolata risolvendo le radici della equazione di cui sopra nel piano z. Le radici sono una coppia complessa coniugata che risiede sul circolo unitario. La frequenza di zero è data dalla relazione:

Α

$$f_{\text{null}} = \frac{}{} \cdot f_{\text{sampling }} \{\text{Eq.9}\}$$

Dove 0 è l'angolo della radice nel semipiano superiore. La radice coniugata fornirà uno zero riflesso attorno alla frequenza di Nyquist.

La tabella 2 elenca le frequenze di zero generate dalla seconda presa a pesatura binaria. Siano b3, b2 e b1 corrispondenti ai pesi 1,0 0,5 0,25, un simbolo "+" significa che la presa è eguale al suo peso, un simbolo "-" significa che la presa è eguale al negativo del suo peso, e "0" significa che la presa non ha peso. Alcune delle frequenze di nullo sono eguale a quelle di altri combinazioni semplicemente per il fatto che talvolta le combinazioni possibili si sovrappongono (ad esempio 1,0 + 0,5 - 0,25 = 1,0 + 0,0 + 0,25). f<sub>sample</sub> è 1,00.

| ъ3         | b2         | <b>b1</b> | f(null) | f(alias) |

|------------|------------|-----------|---------|----------|

|            |            |           |         |          |

| 0          | 0          | 0         | 0,250   | 0,750    |

| 0          | 0          | -         | 0,269   | 0,731    |

| 0          | 0          | +         | 0,230   | 0,770    |

| 0          | +          | 0         | 0,210   | 0,790    |

| 0          | +          | +         | 0,188   | 0,812    |

| 0          | +          | -         | 0,230   | 0,770    |

| 0          | -          | 0         | 0,290   | 0,710    |

| 0          | _          | +         | 0,269   | 0,731    |

| 0          | -          | -         | 0,312   | 0,688    |

| +          | 0          | 0         | 0,167   | 0,833    |

| +          | 0          | -         | 0,188   | 0,812    |

| +          | 0          | +         | 0,143   | 0,857    |

| +          | +          | 0         | 0,115   | 0,885    |

| +          | +          | +         | 0,080   | 0,420    |

| +          | +          | -         | 0,143   | 0,857    |

| +          | -          | 0         | 0,210   | 0,790    |

| +          | -          | +         | 0,188   | 0,812    |

| +          | _          | -         | 0,230   | 0,770    |

| -          | Ö          | 0         | 0,333   | 0,667    |

| -          | 0          | -         | 0,357   | 0,643    |

| -          | 0          | +         | 0,312   | 0,688    |

| · <b>-</b> | +          | 0         | 0,290   | 0,710    |

| -          | +          | +         | 0,269   | 0,731    |

| . <b>–</b> | ` <b>+</b> | -         | 0,312   | 0,688    |

| -          | -          | 0         | 0,385   | 0,615    |

| -          | -          | +         | 0,357   | 0,643    |

| -          |            | -         | 0,420   | 0,580    |

## TABELLA 2

Tutta la temporizzazione è derivata dal segnale di clock a 21,76 MHz sulla linea 71a.

Verranno ora descritte le funzioni associate con i segnali nei registri 64 di controllo.

Quando viene impostato il segnale CW MODE l'ingresso I sul rispettivo moltiplicatore nel modulatore 68 è forzato a tutti zeri, ed il

corrispondente ingresso quadro viene forzato a tutti uno. L'effetto netto è che verrà generata una portante non modulata. Questa funzione è separata due volte ed i caricati non diverranno attivi fin quando non viene emesso un comando TUNE.

Il segnale INTERPOLATOR ENABLE abilita l'interpolatore x16 sui campioni I,Q. Se il segnale INTERPOLATOR ENABLE non è posizionato, allora i dati I, Q sono introdotti direttamente nel moltiplicatore. La memoria esterna necessaria per il funzionamento del chip 12 elaboratore è fornita da una memoria veloce 13 e da una memoria lenta 14. L'accesso alla memoria veloce 13 è effettuato con un decodificatore 15 di indirizzo. La memoria veloce 13 è una memoria "cache" realizzata in una RAM avente zero stati di attesa. La memoria 14 lenta è una memoria di massa che è realizzata con una EPROM avente due stati di attesa. La memoria 14 lenta è accoppiata al chip 12 elaboratore per memorizzare codici di elaborazione utilizzati dal chip 12 elaboratore quando detti codici non devono essere fatti funzionare con zero stati di attesa e la memoria veloce è accoppiata al chip elaboratore per memorizzare temporaneamente codici di elaborazione impiegati dal chip 12 elaboratore quando detti codici sono attuati con zero stati di attesa. Quando le procedure debbono essere svolte con zero stati di attesa, il codice può essere caricato dalla memoria 14 lenta alla memoria 15 veloce e operato da questa. Tali procedure includono le routine si servizio di interruzione, demodulazione di simbolo, acquisizione RCC, demodulazione BPK, ed elaborazione di fonia e dati.

Il chip 12 elaboratore comprende elaboratore unico di segnale digitale modello TM320C25, che svolge quattro compiti principali, un compito di controllo di abbonato 91 (sCT), compito di controllo di canale (CCT) 92, compito di elaborazione di segnale (SPT) 93 ed un compito di elaborazione di modem (MPT) 94, così come mostrato in figura 4. Questi quattro compiti sono controllati da un modulo supervisore 95. Lo SCT tratta la interfaccia telefonica l'elaborazione di chiamata ad alto livello. Il CCT controllo il modem ed il funzionamento RELP e la temporizzazione, ed effettua le regolazioni di temporizzazione TX e di livello di potenza secondo le richieste della stazione base. Lo SPT svolge lo RELP la cancellazione di eco e le funzioni di qenerazione di nota. Il supervisore chiama

sequenzialmente questi quattro compiti e comunica con essi attraverso parole di controllo. Lo SCT 91 fornisce la funzione di controllo ad alto livello entro l'apparecchio di abbonato ed ha tre modi fondamentali di funzionamento: attesa, voce, e chiusura anticipata.

entra nel Idle Mode Lo SCT dopo la applicazione di energia elettrica e rimane in questo stato fino a quando non venga effettuata una effettiva connessione in fonia. Quando si trova nel lo SCT sorveglia la interfaccia Idle Mode, telefonica di abbonato nei riguardi della sua attività e risponde alle richieste da parte della stazione di base ricevute sul canale di controllo radio (RCC). La funzione primaria dello SCT è di la Subscriber Unit quidare attraverso la il configurazione iniziale e di distacco collegamento in fonia su un canale radio. Prima che la unità possa costituire un qualsiasi tipo di chiamata, tuttavia, questa deve trovare la corretta stazione base. Lo SCT determina quale frequenza RCC debba essere usata ed invia la informazione di descrizione frequenza allo CCT. Una della inizializzazione di un canale di comunicazione tra l'apparecchio di abbonato e la stazione di base è

. |

contenuta nella domanda di brevetto degli stati Uniti n.07/070.970 depositata l'8 Luglio 1987.

Una volta che la unità di abbonato ha ottenuto il sincronismo RCC, questa può costituire una chiamata scambiando messaggi sul RCC con la stazione di base e sorvegliando e impostando segnali di elettronica cablata sulla interfaccia telefonica. La seguente descrizione sommaria illustra in breve gli eventi che avvengono durante la costituzione di una chiamata.

La normale impostazione di chiamata per origine di una chiamata inizia con il fatto che l'abbonato solleva l'impugnatura per iniziare una richiesta di servizio. Lo SCT invia un messaggio CALL REQUEST alla stazione base. Lo SCT riceve un messaggio CALL CONNECT. Lo SCT segnale a CCT di cercare di sincronizzarsi sul canale in fonia assegnato attraverso il mesaggio CALL CONNECT. Il CCT raggiunge il sincronismo sul canale di fonia. L'abbonato riceve un segnale di centrale dall'ufficio centrale. è in tal modo completata la impostazione di una chiamata. L'ufficio centrale fornisce il resto del supporto per la terminazione di una chiamata.

La impostazione normale di chiamata per la

terminazione di chiamata avviene come segue: lo SCT riceve un messaggio PAGE dalla stazione di base. Lo SCT risponde con un CALL ACCEPT. Lo SCT riceve un messaggio CALL CONNECT. Il CCT raggiunge il sincronismo sul canale in fonia. Lo SCT avvia il Ring Generator per applicare la chiamata sul circuito locale. L'abbonato solleva il microtelefono. Lo squillo viene arrestato. La connessione in fonia è completa.

Lo SCT realizza la impostazione della chiamata e le operazioni di distacco come una macchina a stati finiti.

Se arriva con successo a completamento la cattura di un canale, lo SCT commuta sul modo in fonia ed effettua un limitatissimo insieme di funzioni di supporto. Il caricamento dell'elaboratore SCT viene mantenuto ad un minimo a questo momento per fornire la compressione di fonia RELP, la cancellazione di eco e gli algoritmi di elaborazione per il modem alla massima capacità dell'elaboratore.

Lo SCT entra nel modo a distacco prematuro come risultato di un tentativo senza successo di originare una chiamata o una sequenza non prevista di distacco anticipato di una chiamata. Durante il

modo a terminazione prematura, viene inviato al microtelefono un nuovo ordine. Lo SCT sorveglia la interfaccia telefonica di abbonato per una disconnessione (riaggancio esteso) al quale momento la apparecchiatura di abbonato entra nel modo a riposo. Le richieste da parte della stazione di base ricevute sopra il canale di controllo radio (RCC) sono rifiutate fino a quando è stata rilevata la disconnessione.

Il CCT 92 opera come unità di controllo di canale a livello di collegamento nel software di banda base. Il CCT ha tre stadi fondamentali: funzionamento RCC, aggiustamenti fini e funzionamento in fonia.

Al momento dell'inserimento dell'alimentazione, il CCT entra nello stato di azionamento RCC

per ricercare e quindi supportare il canale RCC. Il

funzionamento RCC comprende le seguenti funzioni:

controllo di lacuna AM; sorveglia di sincronismo e

di stato del compito del modem; regolazioni di

temporizzazione sul canale radio; filtraggio di

messaggio RX RCC; formattazione del messaggio TX

RCC; sorveglianza del separatore I/O PCM; ed

elaborazione di informazione di collegamento.

Dopo che è stato stabilito un collegamento

in fonia, il CCT entro nello stato ad aggiustamento fine per accordare in modo fine la temporizzazione frazionaria del modem. Gli aggiustamenti fini comprendono le seguenti funzioni: interpretazione e risposta alle segnalazioni di aggiustamento fine, creazione e formattazione delle informazioni di aggiustamento fine TX; invio di messaggi se del caso a sCT; sorveglianza dello stato del modem; e sorveglianza del separatore I/O PCM.

Dopo l'aggiustamento fine, il CCT inizia il funzionamento in fonia che comprende le seguenti funzioni: supporto alla segnalazione di parola di codice; recupero di cadute, sorveglianza di sincronismo e di stato del modem e sorveglianza del separatore I/O PCM.

Il CCT 92 ha tre stadi fondamentali di funzionamento: attesa, aggiustamento fine e fonia. Quando segue è un esame sommario delle transizioni di stato coinvolte nel funzionamento CCT.

Dopo un ripristino il CCT entra in uno stato di attesa e rimane inattivo fin quando pervengono istruzioni di assegnazione di canale da SCT. Lo SCT fornisce al CCT una frequenza sulla quale ricercare il canale di controllo radio (RCC). Il CCT fornisce quindi istruzioni a MPT di sincronizzare il

ricevitore sulla data frequenza e di ricercare una lacuna AM. Il fallimento a rivelare una lacuna AM entro un periodo di tempo prestabilito fa in modo che il CCT richieda un'altra frequenza sulla quale effettuare la ricerca da parte di SCT. Ciò continua indefinitamente fin quando non avviene con successo la rivelazione di una lacuna AM.

A seguito di una rivelazione con successo di una lacuna AM il CCT inizia a verificare i dati ricevuti per la parola unica. Viene esplorata una piccola finestra attorno alla posizione della parola nominale unica dato che il processo di rivelazione di lacuna AM può essere fuori attività per alcuni tempi di simbolo. Una volta che è stata localizzata la parola unica ed è stata verificata la correttezza della parola di rivelazione di errore CRC. può essere determinata la temporizzazione esatta del simbolo di ricezione. I marker di frame di TDM sono quindi regolati per il corretto allineamento ed inizia il supporto normale RCC. Se la parola unica non può essre localizzata, la rivelazione della lacuna AM è considerata falsa ed il CCT richiede una nuova assegnazione di frequenza da SCT.

Durante il funzionamento RCC, il CCT filtra i

messaggi RCC ricevuti. La maggior parte dei messaggi RCC della stazione di base sono configurazioni di zero e queste sono eliminate dopo che è stata letta la informazione di collegamento dal byte di collegamento. I messaggi RCC che contengono informazione effettiva sono inviati allo SCT per la elaborazione. Se viene a mancate la sincronizzazione RCC, il CCT di nuovo richiede una nuova frequenza da SCT. Lo SCT risponderà alla frequenza corretta secondo l'algoritmo di ricerca di frequenza RCC.

Quando lo SCT inizia una chiamata in fonia, a CCT viene assegnato un canale in fonia ed un slot di Ιl CCT porta in tempo. attività la apparechiatura di abbonato secondo assegnazione ed inizia il processo di regolazione fine. Durante la regolazione fine, le unità di base di abbonato trasmettono un segnale progettato specificamente per assistere il modem nella acquisizione di tempo su bit frazionario. La stazione di base CCU rinvia lo sfalsamento di temporizzazione di bit indietro alla di abbonato come valore apparecchiatura diregolazione a complemento a due. Il CCT mantiene una media nel tempo di questi sfalsamenti in

retroazione. Una volta che il CCT determina che il valore di temporizzazione frazionaria si trova entro una tolleranza richiesta, questo regola di conseguenza la temporizzazione di trasmissione della unità. La lunghezza della media nel tempo è determinata dinamicamente, a seconda della varianza dei campioni di tempo frazionari. Dopo una regolazione di temporizzazione, la media nel tempo viene ripristinata e viene ripetuta la procedura.

Una volta che la stazione di base rivela che l'apparecchiatura di abbonato si trova entro una tolleranza di temporizzazione accettabile, questa fa terminare il processo di aggiustamento fine ed inizia il funzionamento in fonia. La lunghezza del processo di aggiustamento fine viene determinata dinamicamente. а seconda del successo delle regolazioni di temporizzazione sulla apparecchiatura di abbonato. Le temporizzazioni di potenza e di simbolo intero sono anche esse sorvegliate e regolate così come necessario durante il processo di aggiustamento fine. Se l'abbonato non riesce trovare а le segnalazioni aggiustamento fine della stazione di base dopo un certo periodo di tempo, o se il processo di aggiustamento fine non può fornire una

temporizzazione accettabile il collegamento viene interrotto ed il CCT ritorna al funzione RCC.

A seguito di un aggiustamento fine che ha avuto successo, il CCT entra nel funzionamento in fonia al livello di modulazione assegnato. I compiti di funzionamento in fonia comprendono il controllare le operazioni RELP e MPT, stabilendo la sincronizzazione di fonia е sorvegliando continuativamente le parole di codice di fonia inviate dalla stazione di base. Variazioni sul controllo del circuito locale segnalate attraverso parole in codice, sono riportate allo SCT così come queste si presentano. Sono anche determinate dalle parole di codice potenza e variazioni incrementali di temporizzazione frazionaria. Le parole di codice di fonia trasmessa sono formulate da CCT sulla base del controllo di circuito locale fornito da SCT e la qualità del collegamento sul canale riportata dal modem. Il CCT ritorna allo RCC quando SCT esegue una sequenza di distacco di chiamata.

Se viene ad essere persa la sincronizzazione in fonia, il CCT inizia una operazione di recupero da attenuazione. Dopo 10 secondi di incapacità a ristabilire una buona connessione in fonia il CCT informa lo SCT della condizione, iniziando un

distacco di chiamata. Ciò riporta il CCT nella condizione di attesa.

Durante una operazione di prova su canale, una segnalazione in fonia viene sostituita da dati di prova del canale. Quando è stata appena ricevuta una informazione, questa viene analizzata per errori sui bit. Il conteggio di errore sui bit viene passato alla stazione di base attraverso le informazioni di canale inverso.

Lo SPT 93 effettua tutti i compiti di elaborazione digitale di segnale (DSP) entro la apparecchiatura di abbonato. Le varie funzioni DSP sono richiamate così come richiesto sotto il controllo del modulo supervisore 95.

Lo SPT include un modulo RELP che viene eseguito da una RAM ad alta velocità. Il modulo RELP effettua una compressione ed espansione di RELP Speech con cancellazione di eco. Il modulo RELP trasforma blocchi di 180 byte di dati di fonia PCM a 64 Kbps verso e da 42 byte di dati di fonia compressi impiegando l'algoritmo RELP.

Lo SPT include anche un modulo (sPC) di controllo di elaborazione di segnale che determina se la generazione di nota di RELP deve essere chiamata. In presenza di RELP, SPC determina se chiamare le routine di sintesi o di analisi. La routine di sintesi riferisce un conteggio di errore di parità, che è trattato dalla routine sPTCTL. Se la generazione di nota è richiesta, questa determina se fornire in uscita un silenzio oppure un nuovo ordine.

Lo SPT viene controllato attraverso comandi da SCT e CCT. Questi comandi chiamano e controllano il funzionamento delle varie funzioni entro lo SPT come queste sono richieste dalla unità di abbonato. RELP ed il software di cancellazione di eco, ad esempio, sono eseguite soltanto quando apparecchiatura di abbonato è attiva su una chiamata in fonia. Note di progresso di chiamata vengono generate in un qualsiasi momento quando il ricevitore della apparecchiatura di abbonato è sganciato e RELP non è attivo. Le note includono silenzio e nuovo ordine. Ad eccezione del modo IDLE, la routine di servizio di interruzione che tratta il codec PCM funziona continuativamente come procedimento di "foreground", riempimento della memoria tampone circolare PCM.

Le funzioni di controllo e di modem sono svolte tra le elaborazioni di analisi e di sintesi.

La procedura di demodulazione MPT 94 è divisa

in due procedure: DEMODA & DEMODB consentendo quindi che venga effettuata la sintesi RELP sui dati RX nel separatore A immediatamente dopo che sia stata completata la procedura DEMODA. Dopo DEMODA le variabili della RAM interna debbono essere memorizzate in una RAM esterna, quindi ricaricate nella RAM interna prima di effettuare DEMODB. Ciò è dovuto al fatto che la RELP impiega la RAM interna.

Quando l'interruzione RXCLK sulla linea 26e viene ricevuta dal chip elaboratore 12, lo MPT fa in modo che vengano letti quattro campioni di dati RX ricevuti e quindi collocati in una memoria temporanea circolare, per la elaborazione da parte della procedura di demodulazione. Ciò consente che vengano effettuati altri compiti mentre si ricevono i campioni RX.

Lo MPT riceve il segnale di interruzione RXCLK sulla linea 26e dal chip FIR ogni 62,5 µsec durante lo slot di ricezione. Il segnale di interruzione RXCLK viene mascherato dal firmware del chip elaboratore durante la attesa o gli slot di trasmissione.

Lo PT riceve il segnale di introduzione TXCLK sulla linea 26f dal chip 16 FIR soltanto durante lo

slot di trasmissione. Il segnale di interruzione TXCLK dice al chip 12 elaboratore quando inviare un nuovo simbolo TX al chip FIR.

Lo MPT legge quattro campioni dal separatore 35 di campione RX nel chip 16 FIR durante ciascuna interruzione RXCLK sulla linea 26e. Lo MPT azzera i contatori di indirizzo di ingresso e di uscita nel separatore all'inizio dello slot di ricezione.

Il MPT invia simboli TX al separatore 36 di simbolo TX nel chip 16 FIR.

Il MPT fornisce i dati al circuito di temporizzazione frazionata nel modulo 39 di temporizzazione RX nel chip 16 FIR che viene impiegato per allineare i segnali di interruzione RXCLK sulla linea 26e con la trasmissione della stazione di base.

Lo MPT sincronizza anche la frequenza DDS sulla frequenza di trasmissione della stazione di base.

Facendo riferimento alla figura 5 lo MPT include i seguenti moduli: un modulo 101 supervisore, un modulo 102 di apprendimento, un modulo 103 di acquisizione di frequenza, un modulo 104 di sincronizzazione di bit, un modulo 105 di demodulazione di fonia, un modulo 106 di ricezione

di simbolo, ed un modulo 107 di trasmissione.

Il modulo 101 supervisore è un supervisore del compito MPT. Questo legge la parola di controllo di MPT (CTRLO) dalla RAM, e chiama altre routine secondo la parola di controllo.

Il modulo 102 di apprendimento calcola un vettore i 28 coefficienti complessi del filtro FIR. Questo viene attivato durante il modo ad attesa dopo l'attacco dell'alimentazione ed ogni circa tre ore. Un trasmettitore di apprendimento realizzato con il MPT viene attivato in un modo a circuito a ritorno per inviare una certa sequenza di simboli. Questa sequenza viene rinviata indietro ad un ricevitore di apprendimento realizzato da MPT in un modo normale in modi a temporizzazione avanzata o ritardata, ed in canali adiacenti superiore ed inferiore.