(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6096109号

(P6096109)

(45) 発行日 平成29年3月15日(2017.3.15)

(24) 登録日 平成29年2月24日(2017.2.24)

(51) Int.Cl.

F 1

|             |           |      |       |      |

|-------------|-----------|------|-------|------|

| H01L 21/338 | (2006.01) | H01L | 29/80 | F    |

| H01L 29/812 | (2006.01) | H01L | 29/80 | H    |

| H01L 29/778 | (2006.01) | H01L | 21/28 | 301B |

| H01L 21/28  | (2006.01) | H01L | 29/44 | P    |

| H01L 29/41  | (2006.01) | H01L | 21/88 | T    |

請求項の数 14 (全 18 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-504077 (P2013-504077)  |

| (86) (22) 出願日 | 平成23年4月13日(2011.4.13)         |

| (65) 公表番号     | 特表2013-528930 (P2013-528930A) |

| (43) 公表日      | 平成25年7月11日(2013.7.11)         |

| (86) 国際出願番号   | PCT/CA2011/000396             |

| (87) 国際公開番号   | W02011/127568                 |

| (87) 国際公開日    | 平成23年10月20日(2011.10.20)       |

| 審査請求日         | 平成26年4月11日(2014.4.11)         |

| (31) 優先権主張番号  | 61/323,470                    |

| (32) 優先日      | 平成22年4月13日(2010.4.13)         |

| (33) 優先権主張国   | 米国(US)                        |

前置審査

|           |                                                                                                |

|-----------|------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 512091246<br>ジーエーエヌ システムズ インコーポレ<br>イテッド<br>カナダ ケイ2ケイ 3ジー8 オンタリ<br>オ州 オタワ イノベーション ドライブ<br>1145 |

| (74) 代理人  | 100102978<br>弁理士 清水 初志                                                                         |

| (74) 代理人  | 100102118<br>弁理士 春名 雅夫                                                                         |

| (74) 代理人  | 100160923<br>弁理士 山口 裕孝                                                                         |

| (74) 代理人  | 100119507<br>弁理士 刑部 俊                                                                          |

最終頁に続く

(54) 【発明の名称】アイランドトポロジを用いる高密度窒化ガリウム装置

## (57) 【特許請求の範囲】

## 【請求項 1】

窒化物半導体デバイスであって、

- (a) 前面と背面とを有する基板であって、該前面が該基板の正面を含む、該基板と、

- (b) 該基板の該正面に形成された窒化物半導体層であって、該正面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

- (c) 該窒化物半導体層上に形成され、該窒化物半導体層において多くの二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極であって、

- i) マルチアイランドトランジスタのソース電極およびドレイン電極、または

- ii) マルチアイランドダイオードの陽極電極および陰極電極

である、第一および第二のアイランド電極と、

- (d) 第一および第二のアイランド電極への接続のための複数の開口部を有する、該窒化物半導体層上に形成された絶縁層と、

- (e) 複数の第一および第二の共通の電極接続エリアであって、

該第一の共通の電極接続エリア(34/84)のそれぞれが、複数の第一のアイランド電極(17/67)のクラスタ(31/81)と接続され、

該第二の共通の電極接続エリア(35/85)のそれぞれが、複数の第二のアイランド電極(18/68)のクラスタ(32/82)と接続され、

該第一の共通の電極接続エリアのそれぞれがバンプ接続部を含むとともに、

10

20

該第二の共通の電極接続エリアのそれぞれが基板貫通ビア接続部を含み、かつ基板貫通ビア接続部のそれぞれが該基板を通して該基板の該背面上の大きな単一の電極共通パッドに接続し、かつ

該複数の第一の共通の電極接続エリアの該バンプ接続部が、該デバイスの前面上の該デバイス全体に、分配された集電ポイントを提供する、

複数の第一および第二の共通の電極接続エリアと、

を備える、窒化物半導体デバイス。

#### 【請求項2】

第一のアイランド電極および第二のアイランド電極が、四角形形状を有する、請求項1記載の窒化物半導体デバイス。 10

#### 【請求項3】

第一のアイランド電極および第二のアイランド電極が、三角形形状を有する、請求項1記載の窒化物半導体デバイス。

#### 【請求項4】

第一のアイランド電極および第二のアイランド電極が、活性面積利用率を最適化するための様々な異なる多角形形状の組み合わせである、請求項1記載の窒化物半導体デバイス。

#### 【請求項5】

窒化物半導体デバイスであって、

(a) 前面と背面とを有する基板であって、該前面が該基板の主面を含む、該基板と、 20

(b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

(c) 該窒化物半導体層上に形成され、該窒化物半導体層において多くの二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極であって、

- i) マルチアイランドトランジスタのソース電極およびドレイン電極、若しくは

- ii) マルチアイランドダイオードの陽極電極および陰極電極

である、第一および第二のアイランド電極と、

(d) 第一および第二のアイランド電極への接続のための複数の開口部を有する、該窒化物半導体層上に形成された絶縁層と、 30

(e) 複数の第一および第二の共通の電極接続エリアであって、

各第一の共通の電極接続エリア(34/84)が単一のまたは複数の第一の金属層によつて複数の第一のアイランド電極(17/67)のクラスタ(31/81)に接続され、かつ各第一の共通の電極接続エリアがバンプ接続部を含み、

各第二の共通の電極接続エリア(35/85)が単一または複数の第二の金属層によつて複数の第二のアイランド電極(18/68)のクラスタ(32/82)に接続され、かつ各第二の共通の電極接続エリアがバンプ接続部を含み、かつ

該複数の第一および第二の共通の電極接続エリアの該バンプ接続部が、該デバイスの前面上の該デバイス全体に、分配された集電ポイントを提供する、

複数の第一および第二の共通の電極接続エリアと

を備える、窒化物半導体デバイス。 40

#### 【請求項6】

第一および第二の金属層が、第一および第二の電極ならびにそれらの接続部の間ににおける高電圧応力の分離を提供する、請求項5記載の窒化物半導体デバイス。

#### 【請求項7】

第一および第二の金属層が、リフトオフレジストマスクプロセスによって製作される、請求項5記載の窒化物半導体デバイス。

#### 【請求項8】

基板が導電性で、かつ前記基板貫通ビア接続部のそれぞれが、該導電性基板を通して該基板の前記背面上の前記单一の電極共通パッドに接続する、請求項1記載の窒化物半導体 50

デバイス。

**【請求項 9】**

ケイ化物 / ポリシリコンの相互接続および接触系、または金属の相互接続および接触系を含む、請求項1記載の窒化物半導体デバイス。

**【請求項 10】**

第一および第二のアイランド電極が、仕事関数の異なる2つの金属層から作製されている、請求項1記載の窒化物半導体デバイス。

**【請求項 11】**

窒化物半導体デバイスであって、

- (a) 前面と背面とを有する基板であって、該前面が該基板の主面を含む、該基板と、10

- (b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

(c) 該窒化物半導体層上に形成され、該窒化物半導体層において多くの二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極であって、マルチアイランドダイオードの陽極電極および陰極電極であり、かつ該複数の第一のアイランド電極と該複数の第二のアイランド電極が、それぞれ、少なくとも一つの側部から突出している複数の城郭状の半島状部を有し、第一のアイランド電極の該城郭状の半島状部が隣接する第二のアイランド電極の城郭状の半島状部に挿設されている (interleaved) 、第一および第二のアイランド電極と、

(d) 第一および第二のアイランド電極への接続のための複数の開口部を有する、該窒化物半導体層上に形成された絶縁層と、20

(e) 複数の第一および第二の共通の電極接続エリアであって、

該第一の共通の電極接続エリア(84)のそれぞれが複数の第一のアイランド電極(67)のクラスタ(81)に接続され、

該第二の共通の電極接続エリア(85)のそれぞれが单一のまたは複数の第二の金属層によって複数の第二のアイランド電極(68)のクラスタ(82)に接続され、

前記複数の第一および第二の共通の電極接続エリアのそれぞれがバンプ接続部を含み、かつ

該複数の第一および第二の共通の電極接続エリアの該バンプ接続部が、該デバイスの前面に於ける該デバイス全体に、分配された集電ポイントを提供する、30

複数の第一および第二の共通の電極接続エリアと

を備える、窒化物半導体デバイス。

**【請求項 12】**

窒化物半導体デバイスであって、

- (a) 前面と背面とを有する基板であって、該前面が該基板の主面を含む、該基板、

- (b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

(c) i) 窒化物半導体層上に形成され、該窒化物半導体層において二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極のアレイであって、該第一および第二のアイランド電極が少なくとも一つの側部から突出している複数の城郭状の半島状部を有し、該第一のアイランド電極の該城郭状の半島状部が隣接する第二のアイランド電極の城郭状の半島状部に挿設されている (interleaved) とともに、該第一および第二のアイランド電極がマルチアイランドトランジスタのソース電極およびドレイン電極である、複数の第一のアイランド電極および複数の第二のアイランド電極のアレイと、40

ii) 該窒化物半導体層上の各第一のアイランド電極および各第二のアイランド電極の間の領域に形成され、かつ該マルチアイランド電界効果トランジスタのゲート電極として機能する、複数の第三のストライプ電極と、

(d) 第一の電極、第二の電極、第三の電極への接続のための複数の開口部を有する、該窒化物半導体層上に形成された絶縁層と、50

(e) 複数の第一および第二の共通の電極接続エリアであって、

各第一の共通の電極接続エリア(34)が複数の第一のアイランド電極(17)のクラスタ(31)に接続され、

各第二の共通の電極接続エリア(35)が複数の第二のアイランド電極(18)のクラスタ(32)に接続され、

該複数の第一および第二の共通の電極接続エリアのそれぞれがバンプ接続部を含み、かつ

該複数の第一および第二の共通の電極接続エリアの該バンプ接続部が、該デバイスの前面上の該デバイス全体に、分配された集電ポイントを提供する、

複数の第一および第二の共通の電極接続エリアと

を備える、窒化物半導体デバイス。

#### 【請求項 13】

エンハンスマントデバイスを作製するために、p型窒化ガリウム(GaN)材料の層またはp型窒化アルミニウムガリウム(AIGaN)材料の層がゲート電極の下に設けられている、請求項12記載の窒化物半導体デバイス。

#### 【請求項 14】

窒化物半導体層が、アンドープ窒化ガリウム(GaN)層およびその上を覆うアンドープ窒化アルミニウムガリウム(AIGaN)層からなるヘテロ層を含む、請求項12記載の窒化物半導体デバイス。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

##### 技術分野

本開示は、窒化ガリウム半導体（トランジスタおよびダイオード）に関する。より詳しくは、本開示は、高電流能力を提供するために必要なパワーデバイスに関する。

##### 【背景技術】

##### 【0002】

##### 背景

窒化ガリウムベースのパワー半導体デバイスが、パワー用途にとって望ましい特性を有することは周知である。提案されている構造のほとんどは、デバイスの上面に沿って配置されたパワー電極および制御電極を有する水平方向導電デバイスである。電極のすぐ下の窒化アルミニウムガリウム(AIGaN)および窒化ガリウム(GaN)のヘテロ構造において、自発分極および圧電分極によりヘテロ界面で電荷が発生し、それにより、わざわざ不純物を添加しなくても $1 \times 10^{13} \text{ cm}^{-2}$ 以上のシートキャリア濃度が得られる。その結果として、ヘテロ界面で発生した二次元電子ガス(2DEG)を利用することによって、高電流密度のヘテロ接合電界効果トランジスタ(HFET)を実現することができる。

##### 【0003】

したがって、窒化物半導体ベースのパワートランジスタは、今まで広く研究開発されており、Siベースの金属酸化物半導体の電界効果トランジスタ(MOSFET)の1/10以下および絶縁ゲートバイポーラトランジスタ(IGBT)の1/3以下の低いオン抵抗が、200V以上の破壊電圧を必要とする分野において実現されている（例えば、W. Saitoら，“IEEE Transactions on Electron Devices,” 2003, Vol. 50, No. 12, p. 2528（非特許文献1）を参照されたい）。窒化物半導体デバイスでは、Siベースの半導体デバイスよりも活性領域のサイズを小さくすることが可能である。したがって、半導体デバイスのサイズの縮小も期待されている。

##### 【0004】

従来の窒化物半導体デバイスでは、活性領域のサイズを、Siベースの半導体デバイスの活性領域のサイズの約1/3～約1/10まで減らすことが可能である。しかしながら、配線を接続するための電極パッドが大きな面積を占めるため、水平方向窒化物半導体デバイスの、電流が流れる相互接続トラックのサイズは、エレクトロマイグレーションの問題から

10

20

30

40

50

、十分には縮小することができない。

#### 【0005】

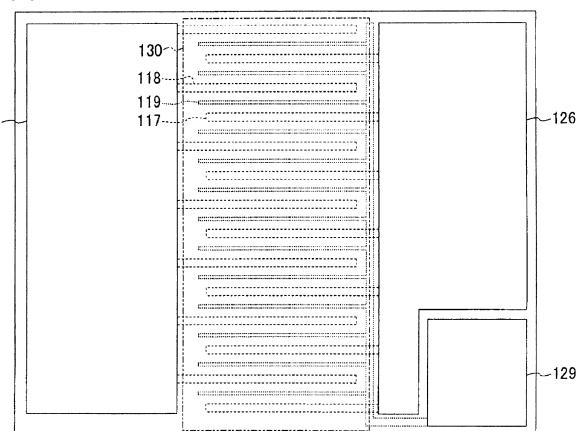

例えば、図11に示されている窒化物半導体デバイスは、ドレイン電極118に接続されたドレイン電極パッド125、ソース電極117に接続されたソース電極パッド126、およびゲート電極119に接続されたゲート電極パッド129を有する。この場合、当該窒化物半導体デバイスに必要な面積は、活性領域130の面積の約3倍の大きさとなる。電極パッドのサイズを小さくすることも可能ではあるが、そのような電極パッドのサイズ縮小は、歩留まりの関係から限界がある。

#### 【0006】

電極パッドを活性領域の上に形成することも可能である。しかしながら、窒化物半導体デバイスでは、電子が走行するチャネルが基板の主面に対して平行な方向に広がっている。したがって、ゲート電極だけでなく、ソース電極およびドレイン電極も、活性領域の上に形成される。パワーデバイスでは、例えば、数百ボルトの電圧がドレイン電極パッドとソース電極の間にかかる。したがって、通常の層間絶縁フィルムではドレイン電極パッドとソース電極との間の絶縁性を確保することが困難である。

10

#### 【0007】

さらに、図11に示されるようなマルチフィンガー型の窒化物半導体デバイスにおいて電極パッドが活性領域の上に形成されている場合、電極パッドおよび当該電極パッドの直下に形成された電極を、特別なプラグまたはビアによって互いに接続する必要がある。したがって、当該パッドを接続し、さらに電極パッドの平坦性も確保するのは、困難である。

20

#### 【先行技術文献】

#### 【非特許文献】

#### 【0008】

【非特許文献1】W. Saitoら,"IEEE Transactions on Electron Devices," 2003, Vol. 50, No. 12, p. 2528

#### 【発明の概要】

#### 【0009】

#### 概要

したがって、エレクトロマイグレーション、電極パッドの面積の問題、電気的相互接続エリアの問題、および制限された活性エリアの不足を解決することが望ましい。先行技術におけるこれらの問題および他の欠点を克服するために、本開示は、GaN半導体デバイスにおける新規の構成およびトポロジを提供する。

30

#### 【0010】

より具体的には、一般的なマルチフィンガー構造またはインターデジタル構造に代わって、アイランド、すなわち三角形または四角形のいずれかのアイランド構造を使用することを提案する。これら新規のアイランドトポロジは容易に、いわゆる固有トランジスタ抵抗を、面積が同等のマルチフィンガーレイアウトによって達成されるものの半分未満とすることができる。それ以上に意味があるのは、表面の相互接続およびパッドの必要性が減じられることにより、有効面積比または活性面積比が、3~5倍優れていることである。

#### 【0011】

40

本開示は、所定の活性エリア内において、より大きなゲート幅（通常、 $W_g$ として知られる）を有するデバイスを提供する。ある特定の例示的態様において、活性エリア内だけではなくデバイス全体の単位面積あたりの電流処理能力を大幅に増加させる、ダイオードおよびトランジスタのためのトポロジを提供する。加えて、優れた能力のGaNトランジスタおよびダイオードを製作するための簡素なプロセスを提供する。

#### 【0012】

#### [本発明1001]

(a) 基板と、

(b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

50

(c) 該窒化物半導体層において多くの二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極と、

(d) 第一および第二のアイランド電極ならびに任意の共通の電極接続エリアを露出させる複数の開口部を有する、該窒化物半導体層上に形成された絶縁フィルムと、

(e) それぞれ第一および第二のアイランド電極を露出させる該複数の開口部上に形成された複数のボール接続部またはバンプ接続部と

を備える、窒化物半導体デバイス。

[本発明1002]

第一もしくは第二のアイランド電極または共通の電極接続エリアのいずれかがボール接続部またはバンプ接続部を用いて接続されていない場合に、複数の基板貫通ビア接続部が形成されている、本発明1001の窒化物半導体デバイス。 10

[本発明1003]

大きな単一の電極共通パッドを、複数の基板貫通ビアの底部に形成することができるか、さもなければ、第一もしくは第二のアイランド電極または共通の電極の上部に接続することができ、それにより、基板の正面の反対側に単一の電極が提供される、本発明1002の窒化物半導体デバイス。

[本発明1004]

第一のアイランド電極および第二のアイランド電極が、四角形形状を有する、本発明10

01の窒化物半導体デバイス。 20

[本発明1005]

第一のアイランド電極および第二のアイランド電極が、三角形形状を有する、本発明10

01の窒化物半導体デバイス。

[本発明1006]

アイランドが、活性面積利用率を最適化するための様々な異なる多角形形状の組み合わせである、本発明1001の窒化物半導体デバイス。

[本発明1007]

(a) 単一または複数の金属層が、複数の第一のアイランド電極と、共通の第一の電極金バンプ接続部との電気接続を可能にし、かつ

(b) 単一または複数の金属層が、複数の第二のアイランド電極と、共通の第二の電極金バンプ接続部との電気接続を可能にする、

本発明1001の窒化物半導体デバイス。 30

[本発明1008]

2つの金属層を使用することにより、第一および第二の電極ならびにそれらの接続部の間ににおける応力の高電圧分離を提供することができる、本発明1007の窒化物半導体デバイス。

[本発明1009]

金属層が、リフトオフによって除去される、本発明1007の窒化物半導体デバイス。

[本発明1010]

ウェハの背面または底部へと接続するように、第一の電極の上部または第二の電極の上部または共通接続部のうちの1つの上部のいずれかからの導電性のビア接続部が基板に作製された、本発明1001の窒化物半導体デバイス。 40

[本発明1011]

金属の相互接続および接触系の代わりに、ケイ化物／ポリシリコンの相互接続および接触系を用いた、本発明1001の窒化物半導体デバイス。

[本発明1012]

陽極電極が、仕事関数の異なる2つの金属層から作製されている、本発明1001の窒化物半導体デバイス。

[本発明1013]

複数の第一のアイランド電極が、その側部のそれぞれから突出している複数の城郭状の

半島状部を有し、該半島状部が、複数の第二のアイランド電極の側部のそれぞれから突出している複数の城郭状の半島状部に組み合わされている（interlaced）、本発明1001の窒化物半導体デバイス。

[本発明1014]

(a) 基板と、

(b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

(c) 該窒化物半導体層において二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極と、

(d) 該窒化物半導体層上の各第一のアイランド電極および各第二のアイランド電極との間に形成され、かつマルチアイランド電界効果トランジスタのゲート電極として機能する複数の第三のストライプ電極であって、該アイランド電極のそれぞれが、電界効果トランジスタのドレイン電極またはソース電極のいずれかである、複数の第三のストライプ電極と、

(e) 第一の電極、第二の電極、第三の電極を露出させる複数の開口部、ならびに第一の電極および第二の電極および第三の電極を電気的に接続することによって形成されている任意の共通の電極接続エリアを露出させる複数の開口部を有する、該窒化物半導体層上に形成された絶縁フィルムと、

(f) 第一の電極および第二の電極および第三の電極のそれぞれ、ならびに任意の共通の電極接続エリアを露出させる複数の開口部上に形成されている、複数のホール接続部またはバンプ接続部と

を備える、窒化物半導体デバイス。

[本発明1015]

エンハンスマントデバイスを作製するために、p型AlGaN材料の層がゲート電極の下に被着されている、本発明1014の窒化物半導体デバイス。

[本発明1016]

エンハンスマントデバイスを作製するために、p型GaN材料の層がゲート電極の下に被着されている、本発明1014の窒化物半導体デバイス。

[本発明1017]

(a) 複数の第一のアイランド電極が、その側部のそれぞれから突出している複数の城郭状の半島状部を有し、該半島状部が、複数の第二のアイランド電極の側部のそれぞれから突出している複数の城郭状の半島状部に嵌合しており、

(b) 複数の第三のストライプ電極が、前記窒化物半導体層上の各第一のアイランド電極の城郭状半島状部と各第二のアイランド電極の城郭状半島状部との間に形成され、マルチアイランド電界効果トランジスタのゲート電極として機能し、

該アイランド電極のそれぞれが電界効果トランジスタのドレイン電極またはソース電極のいずれかである、本発明1014の窒化物半導体デバイス。

[本発明1018]

(a) 基板と、

(b) 該基板の主面上に形成された窒化物半導体層であって、該主面に対して平行な方向に電子が走行するチャネル領域を有する窒化物半導体層と、

(c) 該窒化物半導体層において二次元活性領域を生じるように、互いに離間されて交互に配置されている、複数の第一のアイランド電極および複数の第二のアイランド電極と、

(d) 該窒化物半導体層上の各第一のアイランド電極および各第二のアイランド電極との間に形成され、かつマルチアイランド電界効果トランジスタのゲート電極として機能する複数の第三のストライプ電極であって、該アイランド電極のそれぞれが、電界効果トランジスタのドレイン電極またはソース電極のいずれかである、複数の第三のストライプ電極と、

10

20

30

40

50

(e) 第一の電極、第二の電極、第三の電極を露出させる複数の開口部、または第一の電極もしくは第二の電極もしくは第三の電極を電気的に接続することによって形成されている任意の共通の電極接続エリアを露出させる複数の開口部を有する、該窒化物半導体層上に形成された絶縁フィルムと、

(f) 第一の電極もしくは第二の電極もしくは第三の電極のそれぞれ、または任意の共通の電極接続エリアを露出させる複数の開口部上に形成されている、複数のボール接続部またはバンプ接続部と

を備える、窒化物半導体デバイス。

以上は、原則的特徴およびいくつかの任意の局面についてまとめたものである。以下の実施例の説明により、さらなる理解を得ることができる。

10

#### 【図面の簡単な説明】

##### 【0013】

【図1】例示的一態様による窒化物半導体デバイスの平面図。

【図2】図1の窒化物半導体デバイスの断面図。

【図3】図1の窒化物半導体デバイスのソースクラスタおよびドレインクラスタを示す詳細な平面図。

【図4】図1の窒化物半導体デバイスのゲートクラスタを示す詳細な平面図。ゲートクラスタをより明確に示すために、ドレインおよびソースの相互接続はこの図には示されていない。

20

【図4A】図1の窒化物半導体デバイスのゲートクラスタを示す詳細な平面図。ゲートクラスタをより明確に示すために、ドレインおよびソースの相互接続はこの図には示されていない。

【図5】クラスタ配置において使用した金バンプの断面図。

【図6】別の例示的態様による窒化物半導体デバイスの平面図。

【図7】図6の窒化物半導体デバイスの断面図。

【図8】図6の窒化物半導体デバイスにおいて三角形形状の電極を使用した変更例の平面図。

【図9】さらに別の態様による窒化物半導体デバイスのアイランドの各側部から突出している城郭状の半島状部を使用する変更例の平面図。

【図10】図9による窒化物半導体デバイスのアイランドの各側部から突出している城郭状の半島状部を使用するさらなる変更例の平面図。

30

【図11】従来の窒化物半導体デバイスの平面図。

#### 【発明を実施するための形態】

##### 【0014】

#### 詳細な説明

本開示内において、電極、アイランド、およびアイランド電極なる言葉の使用は、ソース、ドレイン、陽極、または陰極について言及する場合、互換性を持って使用され、同じ意味および関心対象を表し得る。

##### 【0015】

ここで、ある特定の例示的態様について説明することにより、本明細書において開示されるデバイスおよび方法の構造、機能、製造、および使用の原則についての全体的な理解を提供する。これらの態様の1つ以上の例を添付の図面に示す。当業者であれば、本明細書において具体的に説明され、添付の図面に示されたデバイスおよび方法は、非限定的な例示的態様であることを理解するであろう。例示的一態様に関連して示された、または説明された特徴は、他の態様の特徴と組み合わせができる。そのような変更例または変形例は、本開示の範囲内に含まれることが意図される。

40

##### 【0016】

本明細書内において値の範囲について言及された場合、特にそうでないことが明記されない限り、その中の部分範囲も含まれることが意図される。ある特徴がいずれかの変形例に起因する場合、そうでないことが特に明記されない限り、そのような特徴は、そのよう

50

な特徴が適切であるような、または適合性を有するような他のすべての変形例に適用されることが意図される。

**【実施例 1】**

**【0017】**

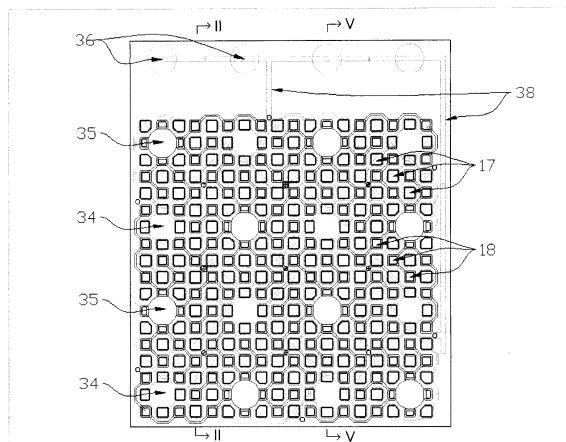

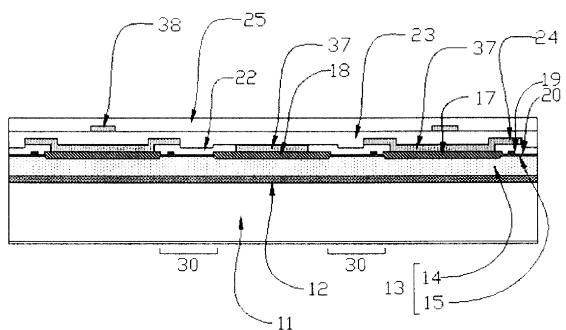

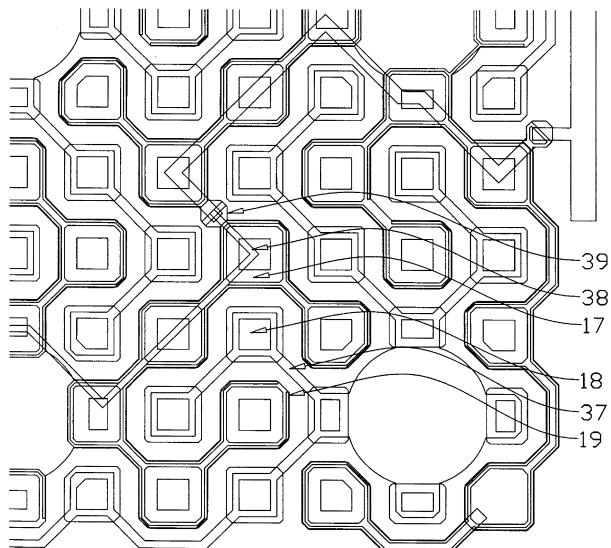

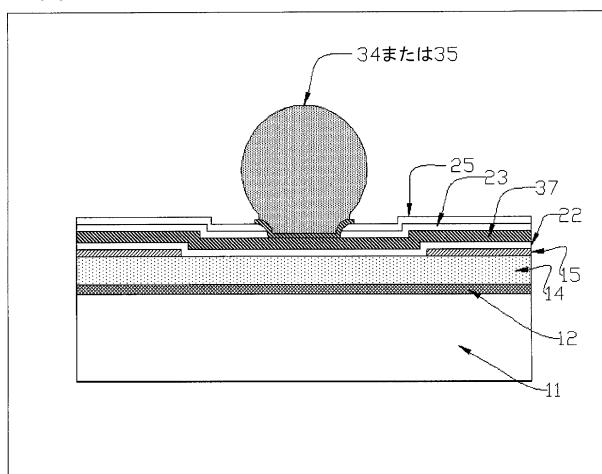

図1は、例示的態様の窒化物半導体デバイスの平面構造を示している。図2は、図1の線I-I'に沿った断面構造の一部を示している。

**【0018】**

図2に示されているように、当該窒化物半導体デバイスは、間にバッファ層12を介在させて非導電性構造体11上に形成された窒化物半導体層13を有する。窒化物半導体層13は、厚さ1μmのアンドープ窒化ガリウム(GaN)層14と、厚さ25nmのアンドープ窒化アルミニウムガリウム(AIGaN)層15とから形成されている。アンドープGaN層14およびアンドープAIGaN層15は、バッファ層12の上にこの順序で連続して形成されている。アンドープGaN層14におけるアンドープAIGaN層15との界面領域では、二次元電子ガス(2DEG)が発生し、チャネル領域が形成される。

**【0019】**

図1および2は、窒化物半導体層13上において互いに間隔をおいて形成されたソース電極アイランド17およびドレイン電極アイランド18を示している。接触抵抗を減じるために、ソース電極17およびドレイン電極18の領域においてアンドープAIGaN層15とアンドープGaN層の一部とが除去され、それにより、ソース電極17およびドレイン電極18は、アンドープAIGaN層15とアンドープGaN層14との間の界面より深いレベルに達する。ソース電極17およびドレイン電極18は、チタン(Ti)およびアルミニウム(Al)から形成される。

**【0020】**

図2を参照すると、ソース電極17およびドレイン電極18の間ににおいて、厚さ200nmのp型AI<sub>x</sub>GaN層20がストライプ形状で形成されている。p型AIGaN層20上には、ゲート電極19が形成されている。ゲート電極19は、パラジウム(Pd)から形成される。

**【0021】**

窒化物半導体層13のチャネル領域における、互いに隣接して形成されたソース電極17およびドレイン電極18と、その間に設けられたゲート電極とを含む領域は、活性界面エリア30と呼ばれる。

**【0022】**

図1および2に示された窒化物半導体は、マルチアイランド型電界効果トランジスタ(FET)である。より具体的には、それぞれの四角形ソース電極アイランド17および四角形ドレイン電極アイランド18が、複数の活性界面エリア30を有する。

**【0023】**

ゲート電極19および活性界面エリア30の上面に第一絶縁層22が被着され、ゲートの上方において一段高いソースフィールドプレート24が提供される。フィールドプレート24は、次に行われる金相互接続メタライゼーションプロセスにおいて形成される。加えて、第一絶縁層22は、ソース電極の金相互接続部とゲート電極19との間にも電気的絶縁性をもたらす。

**【0024】**

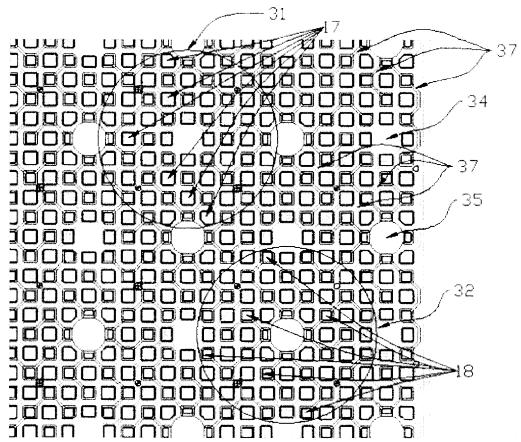

図3に示されているように、複数のソースアイランド電極17が、1~50個のアイランドのクラスタにおいて互いに電気的に接続されており、ソース金パンプ34によって形成された共通の電気的相互接続ポイントを有するソースクラスタ31を形成する。

**【0025】**

図3に示されているように、複数のドレインアイランド電極18が、1~50個のアイランドによるクラスタにおいて互いに電気的に接続されており、ドレイン金パンプ35によって形成された共通の電気的相互接続ポイントを有するドレインクラスタ32を形成する。

**【0026】**

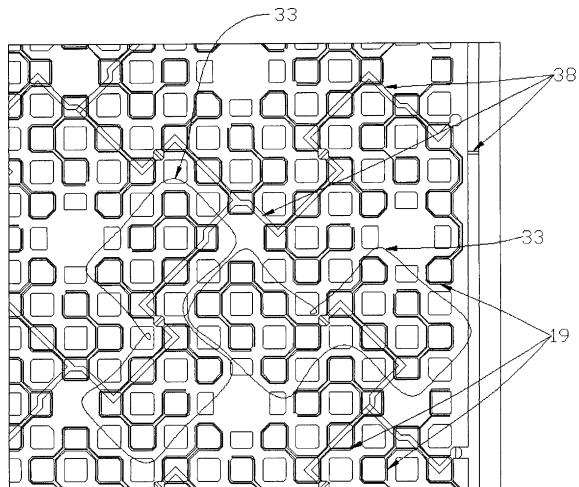

図4に示されているように、複数のゲート電極19が、1~50個によるクラスタにおいて互いに電気的に接続され、その結果、ゲートクラスタ33を形成しており、さらに、これらの

10

20

30

40

50

ゲートクラスタ33は、ゲート金バンプ36で終端する金でメタライズされたトラック37によってデバイス全体にわたって電気的に接続されている。金でメタライズされたゲートトラック38は、同様の電圧電位にあるソース金属トラックの垂直上方を通るように配置され、したがって、ゲートトラックとドレイントラックの間の潜在的な破壊電圧の問題を減じる。

#### 【 0 0 2 7 】

複数のソースクラスタ31、ドレインクラスタ32、およびゲートクラスタ33は、ゲート電極19を介在させて、それぞれのドレイン電極18およびソース電極17が交互に逆転するよう配置される。

#### 【 0 0 2 8 】

アイランド電極間の電気接続部は、1つまたは複数の金メタライゼーション層を用いて、各層に対してリフトオフレジストマスクを使用して、ピアと厚さ $1\mu\text{m}$ で幅 $3\sim4\mu\text{m}$ の金でメタライズされたトラックとによって作製される。複数のメタライゼーション層を使用することにより、デバイス製作の歩留まりが向上し、製作プロセス中の金属リフトオフの問題が軽減される。

#### 【 0 0 2 9 】

ソース金バンプ34、ドレイン金バンプ35、およびゲート金バンプ36による電気的相互接続ポイントは、ドレイン電極、ソース電極、およびゲート電極に対して、デバイス全体に分配された集電ポイントを提供し、その結果、他のパワー電子半導体デバイスに見られる電圧降下の変動およびエレクトロマイグレーションの問題を実質的に排除し、かつ金の標準的な厚さおよび従来のトラック幅の使用を可能にするものであり、したがって、ダイ面積を消費する複数の典型的な幅広い集電トラックとボンディングパッドの必要性をなくし、その一方で、単一のデバイス表面上にすべての相互接続ポイントを提供する。

#### 【 0 0 3 0 】

第二絶縁層23は、ソースおよびドレインの金メタライゼーショントラック37が作製された後に被着され、ソース金トラックとゲート金トラックの間に絶縁性を提供する。図4aに示されているように、ゲート電極集中ポイント39からゲート金メタライゼーショントラック38への電気接続を可能するために、ピアがエッチングされる。

#### 【 0 0 3 1 】

第三絶縁層25は、酸化からダイを保護するために、ゲート金メタライゼーショントラックが作製された後に被着される。ソース、ドレイン、およびゲートのすべての金バンプにおいてエッチングによりピアを作ることにより、金でメタライズされたトラックから、ソース、ドレイン、およびゲートの複数の金バンプ34、35、36への電気接続が可能となる。

#### 【 0 0 3 2 】

図5は、図1の線V-Vに沿った断面構造の一部を示している。図5には、金バンプ34、35の例が示されている。金バンプの現状技術水準は容易に利用可能であるが、バンプ中心間に間隔制限があり、このことにより、デバイス上において金バンプを互いにどこまで近くに位置できるかが制限される。本開示は、この金バンプの間隔制限無しに、各アイランド上における金バンプを可能にするものであり、したがって、金でメタライズされたトラック37によって提供されるアイランド間の電気接続の必要性が排除され、その結果、面積あたりのゲート幅が最大化される。しかしながら、利用可能な金バンプ技術に基づくと、実現可能なデバイスは、典型的には、金バンプあたり $24\sim48$ 個のアイランド電極のクラスタを有し得る。さらに大きな金バンプ間隔が必要な場合には、より大きなクラスタを形成することもできる。

#### 【 0 0 3 3 】

このマルチアイランド構造は、窒化物半導体デバイスにおいて非常に幅広いゲート幅( $W_g$ )を可能にし、それにより、高電流操作が可能な高パワーデバイスを実現することができる。第一、第二、および第三絶縁層22、23、および25は、典型的には、窒化シリコン(SiN)から形成され、 $1\mu\text{m}$ の厚さを有する。

#### 【 0 0 3 4 】

10

20

30

40

50

上記の例は、相互接続に金属を使用することに限定されるものではなく、コスト、電流ホギング、集中応力、およびエレクトロマイグレーション因子の低減を考慮に入れて、金属による相互接続および接触系の代わりにケイ化物／ポリシリコンなどの材料を使用してもよい。

#### 【 0 0 3 5 】

シリコンカーボン(SiC)基板は、最小の格子不整合度でバッファ層12に整合する配向を用いることにより、基板11として使用することができる。しかしながら、基板としては、SiCのみに限定されるわけではなく、基板が電気的に絶縁性であり、かつ窒化物半導体層がその基板上に成長可能である限り、任意の基板を使用することができる。

#### 【 0 0 3 6 】

上記の例は、エンハンスマントモードFETを説明しており、この態様の変形例は、製作プロセスにおいてp型AlGaN層20を含ませないことによってデプレッションモードFETに適用することができる。

#### 【 0 0 3 7 】

金パンプを用いての外部相互接続のみに限定されるわけではない。FETにおけるソースまたはドレンの電気接続のいずれかのために、あるいはダイオードのための陰極または陽極の電気接続のために、金パンプの代わりに基板貫通ピアを使用することもできる。電導性基板11は、基板貫通ピアを使用するデバイスに使用することができる。

#### 【 0 0 3 8 】

以下の例示的な寸法は、範囲を限定するために含まれているのではなく、さらなる説明を提供するためのものである。第一および第二のアイランド電極は、主に、隣接する電極間の水平方向間隔が8μmである、一辺18μmの四角形の形状であり得る。ソース電極およびドレン電極の両方について金パンプ接続部あたり24個のアイランド電極のクラスタを、50個の活性セグメントのゲートクラスタと共に使用することができる。

#### 【 実施例 2 】

#### 【 0 0 3 9 】

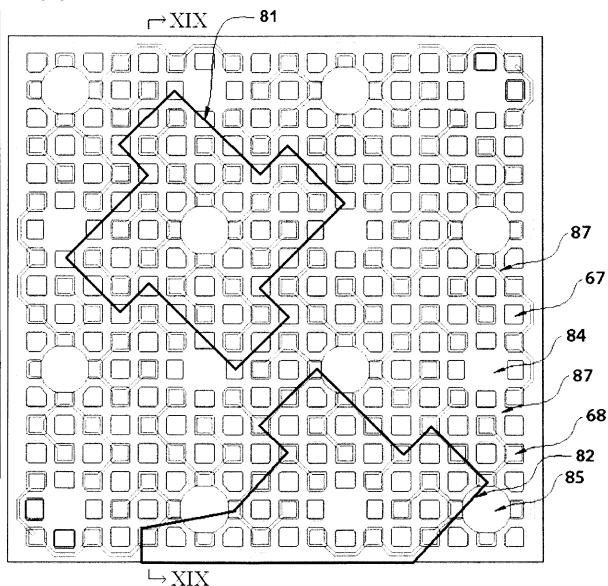

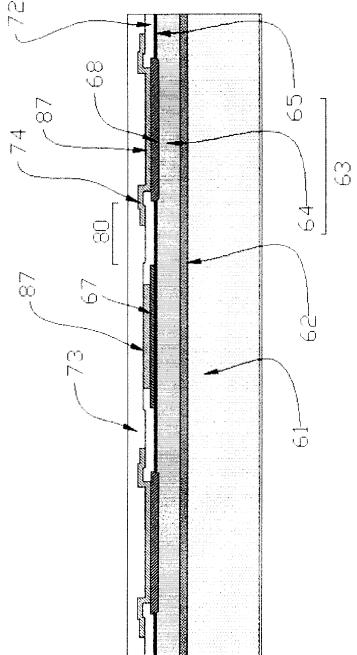

以下において、別の例示的態様について添付の図面を参照しながら説明する。図6は、別の例示的態様による窒化物半導体デバイスの平面構造を示している。図7は、図6の線VI - VIIに沿った断面構造の一部を示している。

#### 【 0 0 4 0 】

図6および7に示されているように、第二態様の窒化物半導体デバイスは、電気的に絶縁性のシリコン(SiC)基板61上に形成された窒化物半導体層63と、その間に介挿されたバッファ層62とを有する。窒化物半導体層63は、厚さ1μmのアンドープ窒化ガリウム(GaN)層64と厚さ25nmのアンドープ窒化アルミニウムガリウム(AlGaN)層65とから形成されている。アンドープGaN層64およびアンドープAlGaN層65は、バッファ層62の上に、この順序で連続して形成されている。アンドープGaN層64におけるアンドープAlGaN層65との界面領域において、二次元電子ガス(2DEG)が発生する。

#### 【 0 0 4 1 】

陰極電極アイランド67および陽極電極アイランド68は、窒化物半導体層63上に、互いに間隔をおいて形成される。陰極電極アイランド67は、チタン(Ti)およびアルミニウム(Al)から形成され得、アンドープAlGaN層65とアンドープGaN層64との間の界面より深いレベルに達している。陽極電極アイランド68は、パラジウム(Pd)から形成され、アンドープAlGaN層65の上面に接している。

#### 【 0 0 4 2 】

本態様において、窒化物半導体層63において陰極電極アイランド67および陽極電極アイランド68が互いに隣接して形成される領域は、活性界面エリア30と呼ばれる。

#### 【 0 0 4 3 】

この態様の窒化物半導体デバイスは、マルチアイランド型ダイオードである。より具体的には、それぞれの四角形陰極電極アイランド67および四角形陽極電極アイランド68は、複数の活性界面エリア30を有する。

10

20

30

40

50

**【 0 0 4 4 】**

活性界面エリア30の上面に第一絶縁層72が被着され、一段高い陽極フィールドプレート74が提供される。フィールドプレート74は、次に行われる金相互接続メタライゼーションプロセスにおいて形成される。

**【 0 0 4 5 】**

複数の陰極電極アイランド67は、1~50個のアイランドによるクラスタにおいて、金でメタライズされたトラック87によって互いに電気的に接続されており、陰極金バンプ84で形成された共通の電気的相互接続ポイントを有する陰極クラスタ81を形成する。

**【 0 0 4 6 】**

複数の陽極電極アイランド68は、1~50個のアイランドによるクラスタにおいて、金でメタライズされたトラック87によって互いに電気的に接続されており、陽極金バンプ85で形成された共通の電気的相互接続ポイントを有する陽極クラスタ82を形成する。

**【 0 0 4 7 】**

複数の陰極クラスタ81および陽極クラスタ82は、陰極電極67および陽極電極68のそれぞれが交互に逆転するように配置されており、それによって、最大数の活性界面エリア30を作り出している。

**【 0 0 4 8 】**

この実施例において使用されるアイランド電極間の電気接続、金バンプ技術、基板貫通ビア、および基板は、第一の実施例において使用されているものと同じであり、そこで説明したのと同じ拡張もここに適用される。

10

20

**【 0 0 4 9 】**

この構造は、陰極電極および陽極電極の間にこの実施例の窒化物半導体デバイスが非常に大きな集合的活性界面を有することを可能にし、それにより、高電流動作が可能な高パワーデバイスが実現可能である。

**【 0 0 5 0 】**

第二絶縁層73は、陰極金バンプ84および陽極バンプ85が配置されるエリアを除いて、デバイス上に形成される。第二絶縁層73は、デバイスの表面を安定化させるために提供され、窒化シリコン(SiN)から形成され、1μmの厚さを有する。

**【 0 0 5 1 】**

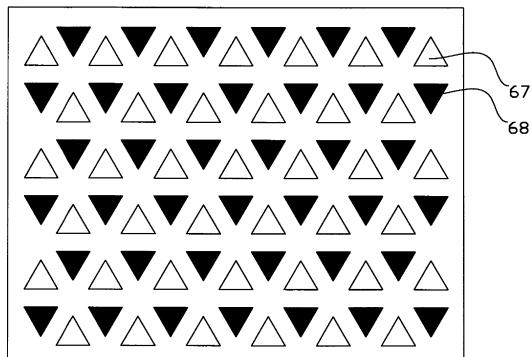

第一実施例および第二実施例において説明された四角形アイランド電極構造に対する代替例として、窒化物半導体ダイオードの一部が図示されている図8の平面図に示されているように、三角形電極アイランド形状(67、68)を使用してもよい。ソース電極アイランドとドレイン電極アイランドとの間にゲート電極を有する類似の構造も、本開示の範囲内である。

30

**【 実施例 3 】****【 0 0 5 2 】**

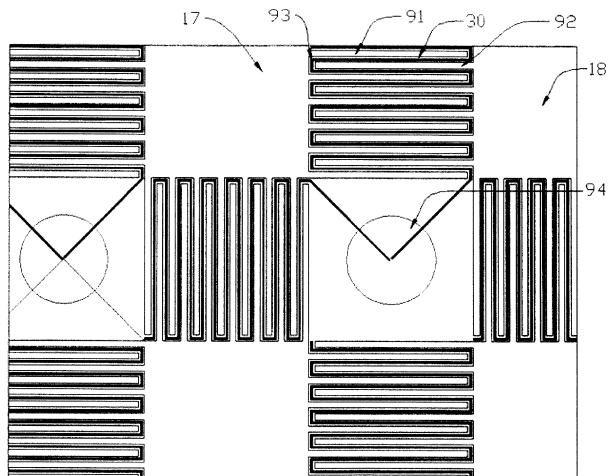

以下において、さらに別の例示的態様について、添付の図面を参照しながら説明する。この態様を形成するために使用されるプロセス工程は、最初の2つの実施例において採用された工程に類似する。図9は、第三態様による窒化物半導体デバイスの平面構造の一部の平面図を示しており、ここで、複数の簡単な四角形アイランド電極の形状は城郭状(鋸歯状)である。第一の電極アイランドから突出している城郭状の半島状部91は、第二の電極アイランドから突出している城郭状の半島状部92と交互に配置されており、それにより、各タイプの電極間の活性界面エリア30が増加する。窒化物トランジスタのゲート電極を形成するために、第一の電極と第二の電極の間のこれらの活性界面エリア内において、ストライプ形状の第三の電極93が被着されている。電極アイランドの城郭状の半島状部の間にゲート電極が無い類似のダイオードも、本開示の範囲内である。

40

**【 0 0 5 3 】**

あるいは、図9において四角形の形状で示されている城郭状の半島状部91および92は、任意の高電流用途に関するエレクトロマイグレーションの問題を改善するために、テーパー状の台形形状にすることもできる。当該城郭状の半島状部は、金または他の金属をそ

50

れらの中心に配置することにより、それらの電流処理能力を増加させることができる。図9に示された構造を使用して作製されたトランジスタは、より小さい電極間隔を使用することにより、実用的な低電圧半導体を実現するための単純なアイランド構造に比べて、2~3倍低いオン抵抗を提供することができる。

#### 【0054】

図9に示されている構造は、前に説明した、金バンプを使用したフリップチップ電極電気接続に非常に適している。規則的な間隔での、ゲート電極への、金または他の導電性金属による複数の電気接続部94は、これらの窒化物トランジスタのスイッチング速度およびスイッチング遅延時間を実質的に改善する。

#### 【0055】

第三態様において説明した四角形アイランド電極構造の代替例の、城郭状の半島状部を有する三角形電極アイランド形状は、ゲート電極を用いてまたは用いずに、トランジスタまたはダイオードのいずれかを作製するために使用することができる。

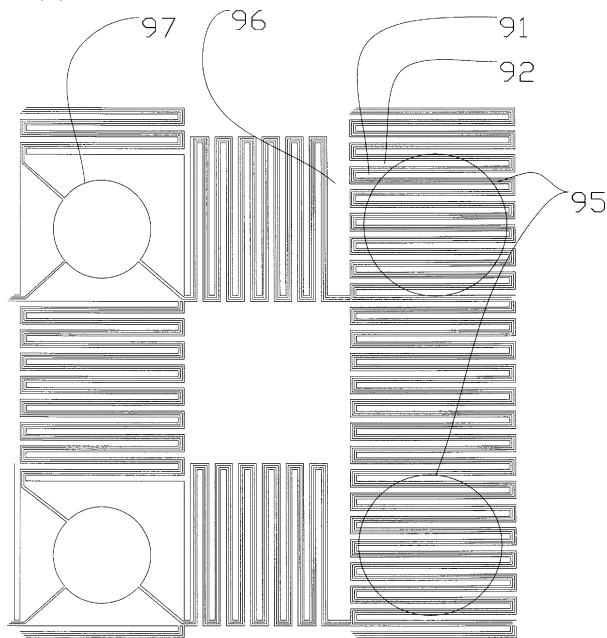

#### 【0056】

第三態様において説明した城郭状の半島状部に対する追加の変更例として、図10に示されているように、隣接するアイランド電極から、城郭状の半島状部を、これらのエリア95内へと延在させることによって、複数のさらなる活性界面エリア30を作り出すことができる。これにより、さらに25%までゲート長および電流処理能力が増加する。典型的には、当該増加はより少なくともよく、挿設されたさらなる半島状部91、92からの電流を処理するためのより広い半島状部96を作り出すことが可能となる。結果として得られる半導体デバイスは、ゲート電極を用いてまたは用いずに形成することにより、トランジスタまたはダイオードのいずれかを作製することができる。ダイオード用途において、またはトランジスタのゲート速度が重要でない場合には、他の非活性エリア97がゲート接続に必要がなければ、それらも追加の半島状部のために使用することができるので、電流処理能力はおよそ50%まで増加し得る。

20

#### 【0057】

上記において説明したように、全体面積が小さい一方で、当該全体面積の範囲内に全ての電極接続部と実際のデバイスを取り付ける全ての手段とを提供し、同時に有用な活性面積も最大化する、一連のデバイスの実施形態を本明細書において開示している。この方法で作製されたダイオードおよびトランジスタは、製造コスト低減に有用であるとともに、パワーシステムのサイズを縮小する。

30

#### 【0058】

本開示は、本明細書において説明した特定の態様に限定されるものではなく、当業者には明らかとなるであろう統合、様々な変更、再編、および置き換えが可能であることは理解されるであろう。

#### 【0059】

##### 結論

添付の特許請求の範囲およびそこで使用される表現は、説明された変形例の観点から理解されるべきである。それらは、そのような変形例に制限されるものではなく、本明細書によって提供された開示において默示的に含まれている全ての範囲を網羅するものとして解釈されるべきである。

40

【図1】

【図3】

【図2】

【図4】

【図4A】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

先行技術

## フロントページの続き

| (51)Int.Cl.              | F I                |

|--------------------------|--------------------|

| H 01 L 21/3205 (2006.01) | H 01 L 21/88 Z     |

| H 01 L 21/768 (2006.01)  | H 01 L 29/06 301 F |

| H 01 L 23/522 (2006.01)  | H 01 L 29/91 F     |

| H 01 L 29/06 (2006.01)   | H 01 L 29/91 D     |

| H 01 L 29/861 (2006.01)  | H 01 L 29/91 K     |

| H 01 L 29/868 (2006.01)  |                    |

(74)代理人 100142929

弁理士 井上 隆一

(74)代理人 100148699

弁理士 佐藤 利光

(74)代理人 100128048

弁理士 新見 浩一

(74)代理人 100129506

弁理士 小林 智彦

(74)代理人 100114340

弁理士 大関 雅人

(74)代理人 100114889

弁理士 五十嵐 義弘

(74)代理人 100121072

弁理士 川本 和弥

(72)発明者 ロバーツ ジョン

カナダ オンタリオ州 オタワ ノース リバー ロード 411 アパートメント ピーエイチ

10

(72)発明者 ミザン アフマド

カナダ オンタリオ州 オタワ プリンス オブ ウェールズ ドライブ 1435 アパートメ

ント 708

(72)発明者 パタスン ガーバン

カナダ オンタリオ州 オタワ ウィンドミア アベニュー 545

(72)発明者 クロワク グレッグ

カナダ オンタリオ州 オタワ シャーク クレセント 51

審査官 儀同 孝信

(56)参考文献 特開2008-198731 (JP, A)

特開2009-032927 (JP, A)

特開2006-173595 (JP, A)

特公平05-056864 (JP, B2)

特開2008-124373 (JP, A)

特開2009-194250 (JP, A)

特開2008-108794 (JP, A)

特開2008-159681 (JP, A)

特開平11-214408 (JP, A)

特開平08-181307 (JP, A)

特開昭57-106174 (JP, A)

特開昭55-113378 (JP, A)

特開2006-229218 (JP, A)

特開2001-028425(JP,A)

特表2013-520000(JP,A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 338

H 01 L 21 / 28

H 01 L 21 / 3205

H 01 L 21 / 768

H 01 L 23 / 522

H 01 L 29 / 06

H 01 L 29 / 41

H 01 L 29 / 778

H 01 L 29 / 812

H 01 L 29 / 861

H 01 L 29 / 868