# (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2007-122627 (P2007-122627A)

(43) 公開日 平成19年5月17日(2007.5.17)

(51) Int.C1. F I テーマコード (参考)

**GO 6 F** 1/24 (2006.01) GO 6 F 1/00 35 OA 5BO 54 **GO 6 F** 12/06 (2006.01) GO 6 F 12/06 51 OB 5BO 6O

#### 審査請求 有 請求項の数 5 〇L (全 12 頁)

|           |                              |          | 明小日 明小人の数 5 〇七 (主 12 頁) |

|-----------|------------------------------|----------|-------------------------|

| (21) 出願番号 | 特願2005-317178 (P2005-317178) | (71) 出願人 | 000003078               |

| (22) 出願日  | 平成17年10月31日 (2005.10.31)     |          | 株式会社東芝                  |

|           |                              |          | 東京都港区芝浦一丁目1番1号          |

|           |                              | (74) 代理人 | 100058479               |

|           |                              |          | 弁理士 鈴江 武彦               |

|           |                              | (74) 代理人 | 100091351               |

|           |                              | ` '      | 弁理士 河野 哲                |

|           |                              | (74)代理人  | 100088683               |

|           |                              |          | 弁理士 中村 誠                |

|           |                              | (74) 代理人 | 100108855               |

|           |                              |          | 弁理士 蔵田 昌俊               |

|           |                              | (74)代理人  | 100075672               |

|           |                              | ((1))    | 弁理士 峰 隆司                |

|           |                              | (74)代理人  | 100109830               |

|           |                              |          | 弁理士 福原 淑弘               |

|           |                              |          | 最終頁に続く                  |

(54) 【発明の名称】情報処理装置及びメモリ初期化方法

# (57)【要約】

【課題】メモリ初期化処理を高速に処理することを可能 とする。

【解決手段】メモリモジュール13には、主メモリを構成するのに用いられるRAM及び第1のSPDデータを格納するSPD130が搭載されている。フラッシュROM19は、CPU11が直接アクセス可能なメモリ空間に割り当てられる。SPDデータ保存処理モジュール191cは、SPD130に格納されている第1のSPDデータを第2のSPDデータとしてフラッシュROM19のSPD保存領域192に保存する。メモリコントローラ設定処理モジュール191dは、パーソナルコンピュータの電源オン時に、SPD保存領域192に保存されている第2のSPDデータに基づいて、RAMを主メモリの構成要素として機能させるための初期設定処理を行う。

【選択図】 図1

### 【特許請求の範囲】

### 【請求項1】

各種プログラムを実行するCPUを有する情報処理装置において、

主メモリを構成するのに用いられるRAM及び第1のSPDデータを格納する第1の不揮発性メモリが搭載されたメモリモジュールであって、前記第1のSPDデータが当該メモリモジュールの仕様を表すメモリモジュールと、

前記CPUが直接アクセス可能なメモリ空間に割り当てられる第2の不揮発性メモリと

前記メモリモジュールの前記第1の不揮発性メモリに格納されている前記第1のSPDデータを第2のSPDデータとして前記第2の不揮発性メモリの所定領域に保存する保存処理モジュールと、

前記情報処理装置の電源オン時に前記第2の不揮発性メモリの前記所定領域に保存されている前記第2のSPDデータに基づいて、前記メモリモジュールに搭載された前記RAMを前記主メモリの構成要素として機能させるための初期設定処理を行う設定処理モジュールと

を具備することを特徴とする情報処理装置。

### 【請求項2】

前記メモリモジュールの前記第1の不揮発性メモリに格納されている前記第1のSPDデータが、前記第2のSPDデータとして前記第2の不揮発性メモリに保存されているかを前記情報処理装置の電源オン時に判定する判定処理モジュールを更に具備し、

前記設定処理モジュールは、前記第1の不揮発性メモリに格納されている前記第1のSPDデータが、前記第2のSPDデータとして前記第2の不揮発性メモリに保存されている第1の状態の場合、当該第2のSPDデータに基づいて前記初期設定処理を行い、前記第1の不揮発性メモリに格納されている前記第1のSPDデータが、前記第2のSPDデータとして前記第2の不揮発性メモリに保存されていない第2の状態の場合、当該第1のSPDデータに基づいて前記初期設定処理を行い、

前記保存処理モジュールは、前記第2の状態の場合、前記第1の不揮発性メモリに格納されている前記第1のSPDデータを前記第2のSPDデータとして前記第2の不揮発性メモリの前記所定領域に保存する

ことを特徴とする請求項1記載の情報処理装置。

### 【請求項3】

前記保存処理モジュールは、前記メモリモジュールの前記第1の不揮発性メモリに格納されている前記第1のSPDデータを前記第2のSPDデータとして前記第2の不揮発性メモリの前記所定領域に保存する場合に、当該メモリモジュール及び前記情報処理装置に固有のフラグ情報を第1及び第2のフラグ情報として、それぞれ前記第1及び第2の不揮発性メモリの所定領域に保存し、

前記判定処理モジュールは前記情報処理装置の電源オン時に、前記第1及び第2の不揮発性メモリにそれぞれ保存されている前記第1及び第2のフラグ情報を比較し、前記第1及び第2のフラグ情報が一致し、且つ前記第2のSPDデータが前記第2の不揮発性メモリに保存されている場合に前記第1の状態を判定し、そうでない場合に前記第2の状態を判定する

ことを特徴とする請求項2記載の情報処理装置。

### 【請求項4】

前記第2の不揮発性メモリは前記CPUによって実行可能なBIOSを格納しており、 当該BIOSは前記保存処理モジュール、前記設定処理モジュール及び前記判定処理モジュールを含むことを特徴とする請求項2記載の情報処理装置。

#### 【請求項5】

各種プログラムを実行するCPUと、主メモリを構成するのに用いられるRAM及び第1のSPDデータを格納する第1の不揮発性メモリが搭載されたメモリモジュールであって、前記第1のSPDデータが当該メモリモジュールの仕様を表すメモリモジュールと、

20

10

30

50

40

前記 C P U が直接アクセス可能なメモリ空間に割り当てられる第 2 の不揮発性メモリとを 有する情報処理装置に適用されるメモリ初期化方法であって、

前記メモリモジュールの前記第1の不揮発性メモリに格納されている前記第1のSPDデータを第2のSPDデータとして前記第2の不揮発性メモリの所定領域に保存するステップと、

前記情報処理装置の電源オン時に前記第2の不揮発性メモリの前記所定領域に保存されている前記第2のSPDデータに基づいて、前記メモリモジュールに搭載された前記RAMを前記主メモリの構成要素として機能させるための初期設定処理を行うステップとを具備することを特徴とするメモリ初期化方法。

【発明の詳細な説明】

10

20

30

### 【技術分野】

[00001]

本発明は、メモリ初期化処理を高速で実行するのに好適な情報処理装置及びメモリ初期化方法に関する。

#### 【背景技術】

[00002]

パーソナルコンピュータの電源をオンすると、システム B I O S (Basic Input Output System)の P O S T (Power On Self Test) 処理が実行されるのが一般的である。

#### $\mathbf{r}$

従来のPOST処理では、当該POST処理の初めで、メモリ初期化処理が実行される。このメモリ初期化処理内で、まずメモリ認識処理が行われる。システムBIOSは、このメモリ認識処理で、メモリモジュールに含まれているSPD(Serial Presence Detect)に格納されているSPDデータを読み込む。SPDは、SPDデータを格納した不揮発性メモリ、例えばEEPROMである。メモリモジュールは、主メモリを構成するのに用いられるRAMを含む。システムBIOSは、SPDから読み込んだSPDデータをもとに、メモリモジュールに搭載されたRAMを主メモリの構成要素として機能させるための初期設定処理を行う。

#### [0004]

一方、例えば特許文献1には、SPDデータを利用した次のような技術(以下、先行技術と称する)が開示されている。この先行技術においては、パーソナルコンピュータの電源がオンされると、DIMM(Dual In-line Memory Module)のようなメモリモジュールに格納されているSPDデータは、メモリモジュールに接続されたフラッシュROMにコピーされる。そして、メモリモジュールに格納されているSPDデータは消去される。つまり、メモリモジュールに格納されているSPDデータは、コンピュータ本体のフラッシュROMに移動される。これにより、このメモリモジュールが無断で持ち出されて、別のコンピュータで使用される場合、当該別のコンピュータは異常動作状態になる。つまり、このメモリモジュールは、別のコンピュータにおいては使用することが不可能である。よって、結果的にメモリモジュールが盗難されることを防ぐことが可能となる。

【特許文献1】特開2000-148600号公報

#### 【発明の開示】

40

【発明が解決しようとする課題】

#### [0005]

上記したように、先行技術によれば、メモリモジュールに格納されているSPDデータは、パーソナルコンピュータの電源のオン時に、当該メモリモジュールからフラッシュROMに移動される。また、この先行技術において、メモリ初期化処理は、フラッシュROMに移動されたSPDデータに基づいて実行される。

### [0006]

しかしながら、先行技術では、メモリ初期化処理の高速化については考慮されていない

[0007]

本発明は上記事情を考慮してなされたものであり、その目的は、メモリ初期化処理を高速に実行することが可能な情報処理装置及びメモリ初期化方法を提供することにある。

### 【課題を解決するための手段】

### [0008]

本発明の1つの態様によれば、各種プログラムを実行するCPUを有する情報処理装置が提供される。この情報処理装置は、主メモリを構成するのに用いられるRAM及び第1のSPDデータを格納する第1の不揮発性メモリが搭載されたメモリモジュールであって、前記第1のSPDデータが当該メモリモジュールの仕様を表すメモリモジュールと、前記メモリモジュールの前記第1のSPDデータとして前記第2の不揮発性メモリの所定領域に保存する保存処理モジュールと、前記情報処理装置の電源オン時に前記第2の不揮発性メモリの前記所定領域に保存されている前記第2の構成情報に基づいて、前記メモリモジュールに搭載された前記RAMを前記主メモリの構成要素として機能させるための初期設定処理を行う設定処理モジュールとを具備する。

#### 【発明の効果】

### [0009]

本発明によれば、メモリモジュールの第1の不揮発性メモリに格納されたSPDデータではなくて、CPUが直接アクセス可能なメモリ空間に割り当てられる第2の不揮発性メモリに保存されたSPDデータに基づいてメモリ初期化処理を実行することによって、当該メモリ初期化処理を高速に実行することが可能となる。

### 【発明を実施するための最良の形態】

### [0010]

以下、図面を参照して本発明の実施形態を説明する。

まず、図 1 を参照して、本発明の一実施形態に係る情報処理装置の構成について説明する。この情報処理装置は、例えば、ノートブック型パーソナルコンピュータとして実現されている。図 1 は、ノートブック型パーソナルコンピュータの構成を示すブロック図である。このパーソナルコンピュータは、CPU11、ノースブリッジ12、メモリモジュール13、グラフィクスコントローラ14、サウスブリッジ16、ハードディスクドライブ(HDD)17、光ディスクドライブ(ODD)18、フラッシュROM19及びエンベデッドコントローラ / キーボードコントローラIC(EC / KBC)21等を備えている

#### [0011]

CPU11は、コンピュータの動作を制御するために設けられたプロセッサである。 CPU11は、コンピュータのハードウェア資源及びソフトウェア資源の割り当て等を統合的に管理するオペレーティングシステム(OS)、及び動画再生アプリケーションプログラムのような各種アプリケーションプログラムを実行する。 OS及び各種アプリケーションプログラムは、ハードディスクドライブ(HDD)17から後述する主メモリ(図示せず)にロードされる。また、CPU11は、フラッシュROM19に格納されたシステムBIOS191(Basic Input Output System)も実行する。

# [ 0 0 1 2 ]

ノースブリッジ12は、CPU11のローカルバスとサウスブリッジ16との間を接続するブリッジデバイスである。ノースブリッジ12は、メモリモジュール13へのアクセスを制御するメモリコントローラ12aを内蔵する。ノースブリッジ12は、AGP(Accelerated Graphics Port)バスなどを介してグラフィクスコントローラ14との通信を実行する機能を有する。

### [0013]

メモリモジュール 13 は、主メモリを構成するのに用いられる、 DRAM (Dynamic RAM )のような RAMを有する。メモリモジュール 13 はまた、 SPD (Serial Presence Detect) 130を有する。 SPD130 は、不揮発性メモリ(第1の不揮発性メモリ)、例

20

30

40

50

20

30

40

50

えばEEPROMである。SPD130は、第1のSPDデータが格納されるSPDデータ領域131を有する。SPDデータは、メモリモジュール13の容量、アクセス速度、アクセス方法、メモリ構成情報等、当該メモリモジュール13の仕様を表すデータである。また、SPD130は、後述する第1のSPDデータ保存フラグ(フラグ情報)が書き込まれるフラグ保存領域132を有する。

[0014]

グラフィクスコントローラ 1 4 は、コンピュータのディスプレイモニタとして使用される L C D 1 5 を制御する表示コントローラである。このグラフィクスコントローラ 1 4 は、ビデオメモリ( V R A M )に書き込まれた映像データを L C D 1 5 に表示する。

[0015]

サウスブリッジ16は、LPC (Low Pin Count)バス20上の各デバイス、及びPCI(Peripheral Component Interconnect)バス(図示せず)上の各デバイスを制御する。また、サウスブリッジ16は、HDD17、ODD18を制御するためのIDE (Integrated Drive Electronics)コントローラを内蔵する。更に、サウスブリッジ16は、フラッシュROM19(第2の不揮発性メモリ)へのアクセスを制御するための機能を有する。

[0016]

H D D 1 7 は、各種ソフトウェア及びデータを格納する記憶装置である。 O D D 1 8 は、ビデオコンテンツ等が格納された D V D メディア、 C D メディアなどの記憶メディアを駆動するためのドライブユニットである。

[0017]

EC/KBC21は、電力管理のためのエンベデッドコントローラ(EC)と、キーボード(KB)22及びタッチパッド23を制御するためのキーボードコントローラとが集積された単一チップのマイクロコンピュータである。このEC/KBC21は、ユーザによるパワ・ボタンの操作に応じてコンピュータを電源オン/電源オフする機能を有している。

[0018]

フラッシュ R O M 1 9 は、書き換え可能な不揮発性メモリである。フラッシュ R O M 1 9 は、C P U 1 1 が直接アクセス可能なメモリ空間に割り当てられている。このメモリ空間には主メモリも割り当てられている。フラッシュ R O M 1 9 は、システム B I O S 1 9 1 を格納する。また、フラッシュ R O M 1 9 は S P D 保存領域 1 9 2 を有する。 S P D 保存領域 1 9 2 は、 S P D 1 3 0 の S P D データ領域 1 3 1 に格納されている S P D データを保存する S P D データ保存領域 1 9 2 a を含む。また、 S P D 保存領域 1 9 2 は、 第 2 の S P D データ保存フラグを保存するフラグ保存領域 1 9 2 b を含む。

[0019]

ここで、SPDデータ保存フラグについて説明する。このフラグは、メモリモジュール及びパーソナルコンピュータに固有の情報である。このフラグは、メモリモジュール13のSPD130に含まれるSPDデータ領域131に格納されている第1のSPDデータがフラッシュROM19に第2のSPDデータとして保存されているかを判定するために用いられる。つまりフラグは、メモリモジュール13が別のメモリモジュールに差し替えられたか否かを判定するために用いられる。このフラグは、システムBIOS191によって、第1のSPDデータ保存フラグとしてSPD130のフラグ保存領域132に書き込まれる。また、このフラグは、システムBIOS191によって、第2のSPDデータ保存フラグとしてフラッシュROM19のフラグ保存領域192bに書き込まれる。

[0020]

システム B I O S 1 9 1 は、ハードウェア制御のためのプログラムである。このシステム B I O S 1 9 1 を C P U 1 1 が実行することによりハードウェア制御が実現される。しかし、以下の説明では、煩雑さを避けるために、システム B I O S 1 9 1 がハードウェア制御を行うものとする。

[0021]

システムBIOS191は、メモリ認識実行判断処理モジュール191a、メモリ認識

(6)

処理 モジュール 1 9 1 b 、 S P D データ保存処理 モジュール 1 9 1 c 、 メモリコントローラ設定処理 モジュール 1 9 1 e を有する。

[ 0 0 2 2 ]

メモリ認識実行判断処理モジュール191aは、パーソナルコンピュータの電源オン時に、フラグ保存領域132及び192bにそれぞれ書き込まれた第1及び第2のSPDデータ保存フラグを読み込む。また、メモリ認識実行判断処理モジュール191aは、読み込んだフラグが一致するか否かを判定する。メモリ認識実行判断処理モジュール191aは、フラグが一致するか否かに基づいて、メモリモジュール13が差し替えられたか否かを判定する。また、メモリ認識実行判断処理モジュール191aは、第2のSPDデータがSPDデータ保存領域192aに格納されているかを判定する機能を有する。

[0023]

メモリ認識処理モジュール 1 9 1 b は、 S P D 1 3 0 の S P D データ領域 1 3 1 に格納されている第 1 の S P D データを読み込む。またメモリ認識処理モジュール 1 9 1 b は、読み込んだ第 1 の S P D データから、メモリ構成情報等を取得する。

[0024]

S P D データ保存処理モジュール 1 9 1 c は、 S P D 1 3 0 の S P D データ領域 1 3 1 に格納されている第 1 の S P D データを第 2 の S P D データとしてフラッシュ R O M 1 9 の S P D データ保存領域 1 9 2 a に書き込む。このとき S P D データ保存処理モジュール 1 9 1 c は、 S P D データ保存フラグをフラグ保存領域 1 3 2 及び 1 9 2 b にそれぞれ第 1 及び第 2 の S P D データ保存フラグとして書き込む。

[0025]

メモリコントローラ設定処理モジュール 1 9 1 d は、第 1 または第 2 の S P D データをもとに、メモリモジュール 1 3 に搭載された R A M を主メモリの構成要素として機能させるための初期設定処理をメモリコントローラ 1 2 a に対して行う。

[0026]

S P D データ取得モジュール 1 9 1 e は S P D データ保存領域 1 9 2 a に書き込まれた第 2 の S P D データを読み込む。 S P D データ取得モジュール 1 9 1 e は、読み込んだ S P D データから、メモリ構成情報等を取得する。

[0027]

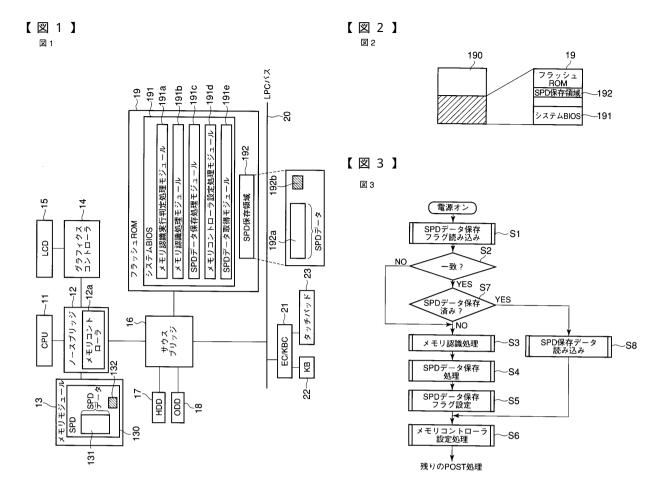

図2は、CPU11が直接アクセス可能なメモリ空間190に対するメモリマッピングの一例を示す。このメモリ空間190にはフラッシュROM19が割り当てられている。つまり、メモリ空間190にはシステムBIOS191及びSPD保存領域192が割り当てられている。これにより、SPD保存領域192に含まれるSPDデータ保存領域192に保存されている第2のSPDデータを高速で読み出すことが可能となる。

[0028]

次に、図3のフローチャートを参照して、メモリ初期化処理の手順について説明する。

[0029]

図 1 に示すパーソナルコンピュータの電源がオンされると、システムBIOS191によりPOST(Power On Self Test)処理が実行される。メモリ初期化処理は、このPOST処理の初めで実行される。

[ 0 0 3 0 ]

メモリ初期化処理において、メモリ認識実行判断処理モジュール191aはまず、フラグ保存領域132及び192bからそれぞれ第1及び第2のSPDデータ保存フラグを読み込む(ステップS1)。メモリ認識実行判断処理モジュール191aは、読み込んだ両方のフラグが一致するか否かを判定する(ステップS2)。ここでは、例えば図1のパーソナルコンピュータが初めて起動された場合のように、フラグ保存領域132及び192bに有効な第1及び第2のSPDデータ保存フラグが格納されていない場合には不一致が判定される。また、後述するようにメモリモジュール13が差し替えられた場合にも、不一致が判定される。

[0031]

40

30

10

20

50

30

40

50

今、ステップS2において不一致が判定されたものとする。この場合、メモリ認識処理モジュール191bは、以下に述べるメモリ認識処理を実行する(ステップS3)。まずメモリ認識処理モジュール191bは、SPD130のSPDデータ領域131に格納されている第1のSPDデータを読み込む。この第1のSPDデータの読み込みは、SPD130を入出力デバイスの1つとして所定のプロトコルにより実行される。このため第1のSPDデータの読み込みを高速に実行することは困難である。メモリ認識処理モジュール191bは、読み込んだ第1のSPDデータから、メモリ構成情報等を取得してメモリモジュール13の構成等を認識する。

[0032]

メモリ認識処理モジュール191bによってステップS3が実行されると、SPDデータ保存処理モジュール191cが起動される。SPDデータ保存処理モジュール191cは、メモリ認識処理モジュール191bによってSPD130のSPDデータ領域131から読み込まれた第1のSPDデータを第2のSPDデータとして、フラッシュROM19のSPD保存領域192 a に書き込む(ステップS4)。このSPD 1 3 0 のSPDデータ領域131に格納されている第1のSPDデータが第2のSPDデータとしてフラッシュROM19のSPDデータ保存領域192 a に保存されている状態を第1の状態と呼び、それ以外の状態を第2の状態と呼ぶ。

[0033]

次にSPDデータ保存処理モジュール191cは、SPDデータ保存フラグを生成して、SPD130のフラグ保存領域132及びフラッシュROM19のフラグ保存領域192 b に、それぞれ第1及び第2のSPDデータ保存フラグとして書き込む(ステップS5)。ここで、SPDデータ保存フラグは、SPDデータ保存処理モジュール191cを含むシステムBIOS191が動作するパーソナルコンピュータ、及び当該パーソナルコンピュータに実装されているメモリモジュール13の組み合わせで一意に生成されるに固有の情報である。

[0034]

SPDデータ保存処理モジュール191cによってステップS4及びS5が実行されると、メモリコントローラ設定処理モジュール191dが起動される。メモリコントローラ設定処理モジュール191bによって読み込まれたSPDデータ(ここでは第1のSPDデータ)をもとにメモリコントローラ12aを初期化するための初期設定処理を実行する(ステップS6)。この初期設定処理により、メモリモジュール13に搭載されたRAMを主メモリとして機能させるための最適な動作条件がメモリコントローラ12aに設定される。

[0035]

ステップS6の初期設定処理が実行されると、メモリ初期化処理が終了し、POST処理の残りの処理が実行される。POST処理が完了すると、フラッシュROM19に格納されているシステムBIOSは主メモリの所定領域にロードされる。CPU11は、主メモリにロードされたシステムBIOSを実行する。

[0036]

次に、このような状態で、図1のパーソナルコンピュータの電源がオフされ、しかる後に、当該電源が再度オンされたものとする。この場合、まずメモリ初期化処理が開始される。するとメモリ認識実行判断処理モジュール191aは、フラグ保存領域132及び192bからそれぞれ第1及び第2のSPDデータ保存フラグを読み込む(ステップS1)。メモリ認識実行判断処理モジュール191aは、読み込んだ両方のフラグが一致するか否かを判定する(ステップS2)。

[0037]

さて図1のパーソナルコンピュータでは、上述したように、前回の電源オン時のメモリ初期化処理で上記ステップS1-S6が実行されている。この初期化処理(ステップS5)では、第2のSPDデータ保存フラグがフラグ保存領域192bに書き込まれる。したがって、現在この第2のSPDデータ保存フラグがフラグ保存領域192bに格納されて

20

30

40

50

いる。

### [0038]

ここで、前回の電源オン時から今回の電源オン時までの間にメモリモジュール13が差し替えられていないものとする。この状態では、フラグ保存領域132には、前回の電源オン時のメモリ初期化処理(ステップS5)で当該フラグ保存領域132に書き込まれた第1のSPDデータ保存フラグが格納されている。したがって今回の初期化処理のステップS2では、メモリ認識実行判断処理モジュール191aによって一致が判定される。この場合、メモリ認識実行判断処理モジュール191aは、メモリモジュール13が前回の電源オン時から今回の電源オン時までの間に差し替えられていないことを判定する。

#### [0039]

このとき、メモリモジュール13のSPD130に格納されている第1のSPDデータは、例えばフラッシュROM19の異常等が発生しないならば、第2のSPDデータとして当該フラッシュROM19のSPDデータ保存領域192aに保存されているはずである。そこでメモリ認識実行判断処理モジュール191aは、SPDデータ保存領域192aに第2のSPDデータが保存されているか否かを判定する(ステップS7)。

#### [0040]

このように、ステップS2において上記両方のSPDデータ保存フラグが一致していることが判定され、ステップS7において第2のSPDデータがSPDデータ保存領域192aに保存されていると判定されると、即ち前記第1の状態が判定されると、SPDデータ取得モジュール191eは、以下に述べるメモリ認識処理を実行する(ステップS8)。まずSPDデータ取得モジュール191eは、SPDデータ保存領域192aから第2のSPDデータを読み込む。ここで、SPDデータ保存領域192aを含むフラッシュROM19は、CPU11が直接アクセス可能なメモリ空間に割り当てられている。このため、SPDデータ取得モジュール191eは、SPDデータ保存領域192aからの第2のSPDデータの読み込みを高速に実行することが可能である。SPDデータ取得モジュール191eは、読み込んだ第2のSPDデータから、メモリ構成情報等を取得してメモリモジュール13の構成等を認識する。

#### [0041]

SPDデータ取得モジュール191eによって、ステップS8が実行されると、メモリコントローラ設定処理モジュール191dが起動される。メモリコントローラ設定処理モジュール191dは、先に述べたステップS6とは異なり、ステップS8においてSPDデータ取得モジュール191eによって読み込まれたSPDデータ(ここでは第2のSPDデータ)をもとにステップS6(初期設定処理)を実行する。

### [0042]

さて、フラグ保存領域132及び192bに第1及び第2のSPDデータ保存フラグが保存されていて、当該両フラグの一致が判定された場合でも、SPDデータ保存領域192aに保存されていた第2のSPDデータが何らかの原因によって消失することがあり得る。もし、SPDデータ保存領域192aに保存されていた第2のSPDデータが消失した場合、上記ステップS7の判定はNOとなり、前記第2の状態(非第1の状態)が判定される。この場合、上記両フラグの不一致が判定された場合と同様に、ステップS3乃至S6の処理が実行される。

#### [ 0 0 4 3 ]

次に、パーソナルコンピュータの電源がオフされた後にメモリモジュール 1 3 が別のメモリモジュールに差し替えられ、しかる後に当該コンピュータの電源が再びオンされた場合のメモリ初期化処理について説明する。ここで、差し替え前のメモリモジュール 1 3 を旧メモリモジュール 1 3 と呼び、差し替え後のメモリモジュールを新メモリモジュール 1 3 と呼ぶ。

### [0044]

まずメモリ認識実行判断処理モジュール 1 9 1 a は、フラグ保存領域 1 3 2 及び 1 9 2 b からそれぞれ第 1 及び第 2 の S P D データ保存フラグを読み込む(ステップ S 1)。次

20

30

40

50

にメモリ認識実行判断処理モジュール191aは、読み込んだ両方のフラグが一致するか 否かを判定する(ステップS2)。

#### [0045]

今、フラグ保存領域192bには、前回電源がオンされたときに実行されるメモリ初期化処理によって、旧メモリモジュール13及び図1のパーソナルコンピュータに固有の第2のSPDデータ保存フラグが格納されている。また、SPDデータ保存領域192aには、旧メモリモジュール13のSPD130に含まれるSPDデータ領域131に格納されている第1のSPDデータが、第2のSPDデータとして格納されている。旧メモリモジュール13が差し替えられる場合、新メモリモジュール13は旧メモリモジュール13とはタイプが異なるのが一般的である。

#### [0046]

ここで、旧メモリモジュール13が新メモリモジュール13に差し替えられているにも拘わらずに、上述の初期化処理でステップS8が実行される場合を想定する。この場合、新メモリモジュール13のSPD130に格納されているSPDデータとは異なるSPDデータ、つまり旧メモリモジュール13のSPD130に格納されているSPDデータが読み込まれる。すると、適正なメモリ初期化処理が行われないことになる。そこで本実施形態では、メモリモジュールが差し替えられたかが次のようにして判定される。

#### [0047]

まず、旧メモリモジュール13に差し替えられる新メモリモジュール13が、図1のパーソナルコンピュータとは別のパーソナルコンピュータに備えられているものとする。また、この新メモリモジュール13のフラグ保存領域132に第1のSPDデータ保存フラグが格納されているとする。この第1のSPDデータ保存フラグは、旧メモリモジュール13のフラグ保存領域132に格納されている第1のSPDデータ保存フラグとは異なる。よって、今回の初期化処理のステップS2では、メモリ認識実行判断処理モジュール191aによって不一致が判定される。この場合、メモリ認識実行判断処理モジュール191aは、旧メモリモジュール13が新メモリモジュール13に差し替えられたことを判定できる。

#### [0048]

次に、新メモリモジュール 1 3 が例えば未使用のために、新メモリモジュール 1 3 のフラグ保存領域 1 3 2 に有効な第 1 の S P D データ保存フラグが格納されていないものとする。この場合でも、上記ステップ S 2 において不一致が判定されることから、メモリ認識実行判断処理モジュール 1 9 1 a は、旧メモリモジュール 1 3 が新メモリモジュール 1 3 に差し替えられたことを判定できる。

### [0049]

ステップS2において不一致が判定された場合、つまり旧メモリモジュール13が新メモリモジュール13に差し替えられたことが判定された場合、前記第2の状態が判定される。この場合、前述のステップS3乃至S6の処理が実行される。

### [0050]

上述したように本実施形態においては、メモリモジュール13のSPD130に格納された第1のSPDデータではなくて、CPU11が直接アクセス可能なメモリ空間に割り当てられるフラッシュROM19のSPD保存領域192に保存された第2のSPDデータに基づいてメモリ初期化処理を実行することによって、当該メモリ初期化処理を高速に実行することが可能となる。

# [0051]

また、旧メモリモジュール 1 3 が新メモリモジュール 1 3 に差し替えられたにも拘わらずに、旧メモリモジュール 1 3 の S P D データ保存領域 1 9 2 a から読み出されてフラッシュ R O M 1 9 の S P D 保存領域 1 9 2 に保存された S P D データを用いると適正なメモリ初期化処理が行われない。しかしながら、本実施形態においては、メモリモジュール 1 3 のフラグ保存領域 1 3 2 及びフラッシュ R O M 1 9 のフラグ保存領域 1 9 2 b にそれぞれ書き込まれる S P D データ保存フラグを参照することによって、メモリモジュール 1 3

20

の差し替えを判定することができる。したがって、旧メモリモジュール 1 3 が新メモリモジュール 1 3 に差し替えられた場合には、当該新メモリモジュール 1 3 の S P D データ領域 1 3 1 に格納されている S P D データに基づいてメモリ初期化処理が実行される。

[0052]

よって、本実施形態によれば、旧メモリモジュール13が新メモリモジュール13に差し替えられたにも拘わらず、旧メモリモジュール13のSPDデータに基づいてメモリ初期化処理が実行されることを防ぐことが可能となる。

[0053]

なお、本発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせにより種々の発明を形成できる。例えば、実施形態に示される全構成要素からいくつかの構成要素を削除してもよい。

【図面の簡単な説明】

[0054]

【 図 1 】 本 発 明 の 一 実 施 形 態 に 係 る パ ー ソ ナ ル コ ン ピ ュ ー タ の シ ス テ ム 構 成 を 示 す ブ ロ ッ ク 図 。

【 図 2 】 C P U 1 1 が直接アクセス可能なメモリ空間 1 9 0 に対するメモリマッピングの一例を示す図。

【図3】上記実施形態で適用されるメモリ初期化処理手順を示すフローチャート。

【符号の説明】

[0055]

1 1 … C P U、 1 2 … ノースブリッジ、 1 2 a … メモリコントローラ、 1 3 … メモリモジュール、 1 6 … サウスブリッジ、 1 9 … フラッシュ R O M、 1 3 0 … S P D、 1 3 1 … S P D データ領域、 1 3 2 … フラグ保存領域、 1 9 0 … メモリ空間、 1 9 1 … システム B I O S、 1 9 1 a … メモリ認識実行判断処理モジュール、 1 9 1 b … メモリ認識処理モジュール、 1 9 1 c … S P D データ保存処理モジュール、 1 9 1 d … メモリコントローラ設定処理モジュール、 1 9 1 e … S P D データ取得モジュール、 1 9 2 … S P D 保存領域、 1 9 2 a … S P D データ保存領域、

# フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 井上 雅之

東京都青梅市新町3丁目3番地の5 東芝デジタルメディアエンジニアリング株式会社内

(72)発明者 真田 俊孝

東京都青梅市新町3丁目3番地の5 東芝デジタルメディアエンジニアリング株式会社内

F ターム(参考) 5B054 AA01 BB01 CC02

5B060 MM06