Filed July 19, 1954

38 Sheets-Sheet 1

INVENTOR CHARLES R. BORDERS

Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 3

F1G. 1C

INVENTOR CHARLES R. BORDERS

Buight D. Mooney ATTORNEY

COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 5

Filed July 19, 1954

38 Sheets-Sheet 6

FIG.6C

INVENTOR CHARLES R. BORDERS

hwight D. mooney

Filed July 19, 1954

38 Sheets-Sheet 10

|        | •         | CIRC     | UIT | POIN | TS (F | IGS. 7 | 7A.8A | , 8B) | UNIT | 'S OF  | RDER |

|--------|-----------|----------|-----|------|-------|--------|-------|-------|------|--------|------|

| TIME   | OPERATION | 17(INPUT |     |      |       | 15-1   |       | D2    | D1   | D8     | D 10 |

| 0.00   |           | 0        | 0   | 0    | 0     | 0      | 0     | 0     | 0    | 0      | 0    |

| 0.10   |           | 1        | 0   | 0    | 0     | 1      | 0     | 0     | 0    | 0      | 0    |

| 0.20   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 0    | 0      | 0    |

| 0.30   |           | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 0    | 0      | 0    |

| 0.40   |           | 0        | 0   | 0    | 0     | 0      | 0     | 0     | 1    | 0      | 0    |

| 0.50   |           | 0        | 1   | 0    | 0     | 1      | 0     | 0     | 0    | 1      | 0    |

| 0.60   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 0    | 0.     | 0    |

| 0.70   |           | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 0    | 0      | 0    |

| 1.00   | READOUT 1 | 0        | 0   | 0    | 0     | 0      | 0     | 0     | 1    | 0      | 0    |

| 1. 1 0 |           | 1        | 1   | 0    | 1     | 0      | 0     | 0     | 0    | 1      | 0    |

| 1.20   |           | 0        | 0   | 1    | 0     | 1      | 0     | 0     | 0    | 0      | 0    |

| 1.30   |           | 0        | 0   | 0    | 9 0   | 0      | 1     | 0     | 0    | 0      | 0    |

| 1.40   |           | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 0    | 0      | 0    |

| 1.50   |           | 0        | 0   | 0    | 0     | 0      | 0     | 0     | 1    | 0      | 0    |

| 1.60   |           | 0        | 1   | 0    | 0     | 1      | 0     | 0     | 0    | 1      | 0    |

| 1.70   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 0    | 0      | 0    |

| 2.00   | READOUT 2 | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 0    | 0      | 0    |

| 2.10   |           | 1        | 0   | 0    | 0     | 1      | 0     | 0     | 1    | 0      | 0    |

| 2.20   |           | 0        | 1   | 0    | 0     | 1      | 1     | 0     | 0    | 1      | 0    |

| 2.30   |           | 0        | 0   | 0    | 0     | 0      | 1     | 1     | 0    | 0      | 0    |

| 2.40   |           | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 1    | 0      | 0    |

| 2.50   |           | 0        | 1   | 0    | 0     | 1      | 0     | 0     | 1    | 1      | 0    |

| 2.60   |           | 0        | 1   | 0    | 0     | 1      | 1     | 0     | 0    | 1      | 0    |

| 2.70   |           | 0        | 0   | 0    | 0     | 0      | 1     | 1     | 0    | 0      | 0    |

| 3.00   | READOUT 3 | 0        | . 0 | 0    | 0     | 0      | 0     | 1     | 1    | 0      | 0    |

| 3.10   |           | 1        | 1   | 0    | 1     | 0      | 0     | 0     | 1    | 1      | 0    |

| 3.20   |           | 0        | 1   | 1    | 1     | 0      | 0     | 0     | 0    | 1      | 0    |

| 3.30   |           | 0        | 0   | 1    | 0     | 1      | 0     | 0     | 0    | 0      | 0    |

| 3.40   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 0    | 0      | 0    |

| 3.50   |           | 0        | 0   | 0    | 0     | 0      | 0     | 1     | 0    | 0      | 0    |

| 3.60   |           | 0        | . 0 | 0    | 0     | 0      | 0     | 0     | 1    | 0      | 0    |

| 3.70   |           | 0        | 1   | 0    | 0     | 1      | 0     | 0     | 0    | 1      | 0    |

| 4.00   | READOUT 4 | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 0    | 0      | 0    |

| 4.10   |           | 1        | 0   | 0    | 0     | 1      | 0     | 1     | 0    | 0      | 0    |

| 4.20   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 1    | 0      | 0    |

| 4.30   |           | 0        | 1   | 0    | 0     | 1      | 0     | 1     | 0    | 1      | 0    |

| 4.40   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 1    | 0      | 0    |

| 4.50   |           | 0        | 1   | 0    | 0     | 1      | 0     | 1     | 0    | 1      | 0    |

| 4.60   |           | 0        | 0   | 0    | 0     | 0      | 1     | 0     | 1    | 0      | 0    |

| 4.70   |           | 0        | 1   | 0    | 0     | 1      | 0     | 1     | 0    | 1      | 0    |

|        |           |          |     |      |       |        |       |       |      | INFENT | OR.  |

FIG.7C

CHARLES R. BORDERS

BY Duight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 11

| T        |                 |          |                    |    |     | <del></del> |    |     |     |   |   |   |   |       |   |      |

|----------|-----------------|----------|--------------------|----|-----|-------------|----|-----|-----|---|---|---|---|-------|---|------|

|          |                 |          |                    |    |     | ,           | ,  |     |     |   |   |   |   |       |   |      |

| TIME     | OPERATION       | 17(INPUT | +                  | 14 | 13  | 16-1        | 15 | - 1 | D 4 | D | 2 | D | 1 | D     | 8 | D 10 |

| 5.00     | READOUT 5       | 0        |                    | 0  | 0   | 0           |    | 0   | 1   |   | 0 | 1 |   |       | 0 | 0    |

| 5.10     | _               | 1        | 1                  |    | 0   | 1           |    | 0   | 0   | 1 |   |   | 0 | 1     |   | 0    |

| 5.20     | _               | 0        | <u> </u>           | 0  | 1   | 0           | 1  |     | 0   |   | 0 | 1 |   |       | 0 | 0    |

| 5.30     | _               | 0        | 1                  |    | 0   | 0           | 1  |     | 1   |   | 0 |   | 0 | 1     |   | 0    |

| 5.40     | _               | 0        | $oldsymbol{\perp}$ | 0  | 0   | . 0         |    | 0   | 1   | 1 |   |   | 0 |       | 0 | 0    |

| 5.50     | _               | 0        |                    | 0  | 0   | 0           |    | 0   | 0   | 1 |   | 1 |   |       | 0 | 0    |

| 5.60     |                 | 0        | 1                  |    | . 0 | 0           | 1  |     | 0   |   | 0 | 1 |   | 1.    |   | 0    |

| 5.70     |                 | 0        | 1                  |    | 0   | 0           | 1  |     | 1   |   | 0 |   | 0 | 1     |   | 0    |

| 6.00     | READOUT 6       | 0        |                    | 0  | 0   | 0           |    | 0   | 1   | 1 |   |   | 0 |       | 0 | 0    |

| 6.10     |                 | 1        |                    | 0  | 0   | 0           | 1. |     | 0   | 1 |   | 1 |   |       | 0 | 0    |

| 6.20     |                 | 0        | 1                  |    | 0   | 0           | 1  |     | 1   |   | 0 | 1 |   | 1     |   | 0    |

| 6.30     |                 | 0        | 1                  |    | 0   | 0           | 1  |     | 1   | 1 |   |   | 0 | 1 -   |   | 0    |

| 6.40     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 1   | 1 | : | 1 |   |       | 0 | 0    |

| 6.50     |                 | 0        | 1                  |    | . 0 | 0           | 1  |     | 0   | 1 |   | 1 |   | 1     |   | 0    |

| 6.60     |                 | 0        | 1                  |    | 0   | 0           | 1  |     | 1   |   | 0 | 1 |   | 1     |   | 0    |

| 6.70     | 1               | 0        | 1                  |    | 0   | 0           | 1  |     | 1   | 1 |   |   | 0 | 1     |   | 0    |

| 7.00     | READOUT 7       | 0        | L                  | 0  | 0   | 0           |    | 0   | 1   | 1 |   | 1 |   |       | 0 | . 0  |

| 7.10     |                 | 1        | - 1                |    | 0   | 1           |    | 0   | 0   | 1 |   | 1 |   | 1     |   | 0    |

| 7.20     | 1               | 0        | 1                  |    | 1   | 1           |    | 0   | 0   |   | 0 | 1 |   | 1     |   | 0    |

| 7.30     | 1               | 0        | 1                  |    | 1   | 1           |    | 0   | 0   |   | 0 |   | 0 | 1     |   | 0    |

| 7.40     | <u> </u>        | 0        |                    | 0  | 1   | 0           | 1  |     | 0   |   | 0 |   | 0 |       | 0 | 0    |

| 7.50     |                 | ٥        |                    | 0  | 0   | 0           |    | 0   | 1   |   | 0 |   | 0 |       | 0 | 0    |

| 7.60     | <u>.</u> :      | 0        | <u> </u>           | 0  | 0   | 0           |    | 0   | 0   | 1 |   |   | 0 |       | 0 | 0    |

| 7.70     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 0   |   | 0 | 1 |   |       | 0 | 0    |

| 8.00     | READOUT 8       | 0        | 1                  |    | 0   | 0           | 1  |     | 0   |   | 0 |   | 0 | 1     |   | 0    |

| 8.10     |                 | 1        |                    | 0  | 0   | 0           | 1  |     | 1   |   | 0 |   | 0 |       | 0 | 0    |

| 8.20     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 1   | 1 |   |   | 0 |       | 0 | 0    |

| 8.30     | į               | 0        |                    | 0  | 0   | 0           |    | 0   | 0   | 1 |   | 1 |   |       | 0 | 0    |

| 8.40     |                 | . 0      | 1                  |    | 0   | 0           | 1  |     | 0   |   | 0 | 1 |   | 1     |   | 0    |

| 8.50     |                 | 0        | 1                  |    | 0   | 0           | 1  |     | 1   |   | 0 |   | 0 | 1     |   | 0    |

| 8.60     | .               | 0        |                    | 0  | 0   | . 0         |    | 0   | 1   | 1 |   |   | 0 |       | 0 | 0    |

| 8.70     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 0   | 1 |   | 1 |   |       | 0 | 0    |

| 9.00     | READOUT 9       | 0        | 1                  |    | 0   | 0           | 1  |     | 0   |   | 0 | 1 |   | 1     |   | 0    |

| 9.10     |                 | 1        | 1                  |    | 0   | 1           |    | 0   | 1   |   | 0 |   | 0 | 1     |   | 0    |

| 9.20     | CARRY AND CLEAR | 0        |                    | 0  | 1   | . 0         | 1  |     | 0   | 1 |   |   | 0 |       | 0 | 1    |

| 9.30     | .               | 0        |                    | 0  | 0   | 0           |    | 0   | 0   |   | 0 |   | 0 |       | 0 | 0    |

| 9.40     | ļ               | 0        |                    | 0  | 0   | 0           |    | 0   | 0   |   | 0 |   | 0 |       | 0 | 0    |

| 9.50     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 0   | 1 | 0 |   | 0 |       | 0 | 0    |

| 9.60     |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 0   |   | 0 |   | 0 |       | 0 | 0    |

| 9.70     |                 | 0        |                    | Ö  | 0   | Ŏ           |    | 0   | 0   |   | 0 |   | 0 |       | 0 | 0    |

| <u> </u> |                 | 0        |                    | 0  | 0   | 0           |    | 0   | 0   | L | 0 | - | 0 | 101/1 | 0 | 0    |

FIG.7D

FIG. 7E FIG. 7D

INVENTOR CHARLES R. BORDERS

BY Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 12

INVENTOR CHARLES R. BORDERS

Dwight & moongy

INVENTOR CHARLES R. BORDERS

Dwight D. Mooney

INVENTOR CHARLES R. BORDERS

Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 16

|          | [           | CIRC      | UIT F | POINT | S (FI | GS. 7A      | , 8A, | 3B) · | TENS | ORDE | R I  |

|----------|-------------|-----------|-------|-------|-------|-------------|-------|-------|------|------|------|

| TIME     | OPERATION   | 17(IHPUT) |       | 13    | 16-10 | 15-10       | D20   | D10   | D80  | D40  | D100 |

| 9.20     |             | 1         | 0     | 0     | 0     | 1           | 0     | 0     | 0    | 0    | 0    |

| 9.30     |             | 0         | 0     | 0     | 0     | 0           | 1     | 0     | 0    | 0    | 0    |

| 9.40     | ļ           | 0         | 0     | 0     | 0     | 0           | 0     | 1     | 0    | 0    | 0    |

| 9.50     |             | 0         | 0     | 0     | 0     | - 0         | 0     | 0     | 1    | 0    | 0    |

| 9.60     |             | .0        | 1     | 0     | 0     | 1           | 0     | 0     | 0    | 1 0  | 0    |

| 9.70     |             | 0         | 0     | 0     | 0     | 0           | 1     | 0     | 0    | 0    | 0    |

| 10.00    | READOUT 10  | 0         | 0     | 0     | 0     | 0           | 0     | 1     | 0    | 0    | 0    |

| 10.10    |             | 0         | 0     | 0     | 0     | 0           | 0     | . 0   | 1    | 0    | 0    |

| 10.20    |             | 0         | 1     | 0     | 0     | 1           | 0     | 0     | . 0  | 1    | 0    |

| 10.30    |             | 0         | 0     | 0     | 0     | 0           | 1 0   | 0     | 0    | 0    | 0    |

| 10.40    |             | 0         | 0     | 0     | 0     | 0           | 0     | 1     | 0    | 0    |      |

| 10.50    |             | 0         | 0     | 0     | 0     | 0           | 0     | 0     | ,    |      | 0    |

| 10.60    | 4.5         | 0         | 1     | 0     | 0     | 4           | 0     | 0     | 1    | , 0  |      |

| 10.70    |             | 0         | 0     | 0     | 0     | , 0         |       |       | 0    | 1    | 0    |

| 11.00    | READOUT 11  | 0         | 0     | 0     | 0     |             | 1     | 0     | 0    | 0    | 0    |

| <u> </u> | (10 IN TENS |           |       |       | 0     | <u> _ 이</u> | 0     | 1     | 0    | 0    | 0    |

IN UNITS)

98.00 READOUT 98 (90 IN TENS, 98.10 8 IN UNITS) 98.20 0 1 98.30 98.40 98.50 98.60 98.70 99.00 READOUT 99 Ō (90 IN TENS, 9 IN UNITS) 99.10  $\overline{\circ}$ 99.20 99.30 CARRY AND CLEAR

FIG. 9A

INVENTOR.

CHARLES R. BORDERS

BY Duight D. Mooney

ATTORNEY

Dec. 26, 1961

#### C. R. BORDERS

3,014,662

#### COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 17

|        |             | CIRCL     | JIT F | POINT | S (FI  | SS. 8C | ,8D) | HUND | REDS | ORE  | ER    |

|--------|-------------|-----------|-------|-------|--------|--------|------|------|------|------|-------|

| TIME   | OPERATION   | 17(INPUT) | 14    | 13    | 16-100 | 15-100 | D100 | D800 | D400 | D200 | D1000 |

| 99.30  |             | 1         | 0     | 0     | 0      | 1      | 0    | 0    | 0    | 0    | 0     |

| 99.40  | ·           | 0         | 0     | 0     | 0      | 0      | 1    | 0    | 0    | . 0  | 0     |

| 99.50  |             | . 0       | 0     | 0     | 0      | 0      | 0    | 1    | 0    | 0    | . 0   |

| 99.60  |             | 0         | 0     | 0     | 0      | 0      | 0    | 0    | 1    | 0    | 0     |

| 99.70  |             | 0         | 1     | 0     | 0      | 1      | 0    | 0    | 0    | 1    | 0     |

| 100.00 | READOUT 100 | 0         | 0     | 0     | 0      | 0      | 1    | 0    | 0    | 0    | 0     |

(100 IN HUNDREDS ORDER)

|          | EADOUT 998               | 0   | 0   | 0 | 0   | 0 | 1 | 1 | 0  | 0 | 0 |

|----------|--------------------------|-----|-----|---|-----|---|---|---|----|---|---|

| 1330.10  | OO IN HUNDREDS           | 0   | 0   | 0 | 0   | 0 | 0 | 1 | 1  | 0 | 0 |

| 998.20   | 90 IN TENS<br>8 IN UNITS | 0   | 1   | 0 | 0   | 1 | 0 | 0 | 1  | 1 | 0 |

| 998.30   |                          | 0   | 1   | 0 | . 0 | 1 | 1 | 0 | 0  | 1 | 0 |

| 998.40   |                          | 0   | . 0 | 0 | 0   | 0 | 1 | 1 | 0  | 0 | 0 |

| 998.50   | İ                        | 0   | 0   | 0 | 0   | 0 | 0 | 1 | 1. | 0 | 0 |

| 998.60   |                          | 0   | 1   | 0 | 0   | 1 | 0 | 0 | 1  | 1 | 0 |

| 998.70   |                          | 0   | 1   | 0 | 0   | 1 | 1 | 0 | 0  | 1 | 0 |

| 1000.00  | EADOUT 999               | 0   | 0   | 0 | 0   | 0 | 1 | 1 | 0  | 0 | 0 |

| 1333.10  | 00 IN HUNDREDS           | 0   | 0   | 0 | 0   | 0 | 0 | 1 | 1  | 0 | 0 |

| 999.20   | 9 IN UNITS               | . 0 | 1   | 0 | 0   | 1 | 0 | 0 | 1  | 1 | 0 |

| 999.30   |                          | 1   | 1   | 0 | 1   | 0 | f | 0 | 0  | 1 | 0 |

| 999.40 C | ARRY AND                 | 0   | 0   | 1 | . 0 | 1 | 0 | 1 | 0  | Q | 1 |

|          | CLEAR                    |     |     |   |     |   |   |   |    |   |   |

FIG. 9B

INVENTOR. CHARLES R. BORDERS

BY Duight D. Mooney

Dec. 26, 1961

### C. R. BORDERS

3,014,662

COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 18

|         |              | CIRC      | CUIT | POIN | TS (F   | IGS. 8  | C, 8D) | THO   | USANI | S OR  | DER     |

|---------|--------------|-----------|------|------|---------|---------|--------|-------|-------|-------|---------|

| TIME    | OPERATION    | 17(INPUT) | 14   | 13   | 16-1000 | 15-1000 | D8000  | D4000 | D2000 | D1000 | D10,000 |

| 999.40  | 7,1          | 1         | 0    | 0    | 0       | 1       | 0      | 0     | 0     | 0     | 0       |

| 999.50  |              | 0         | 0    | 0    | 0       | 0       | 1      | 0     | 0     | 0     | 0       |

| 999.60  |              | 0         | 0    | 0    | 0       | 0       | 0      | 1     | 0     | 0     | 0       |

| 999.70  |              | 0         | 0    | 0    | 0       | 0       | 0      | 0     | 1     | 0     | 0       |

| 1000.00 | READOUT 1000 | 0         | 1    | 0    | 0       | 1       | 0      | 0     | 0     | 1     | 0       |

(1000 IN THOUSANDS)

| 9998.00 |                      | _ | 1 |   | 0 | 0   | 1 |   | 1 | (   | )        | 0   | 1  |   | 0 |

|---------|----------------------|---|---|---|---|-----|---|---|---|-----|----------|-----|----|---|---|

| 9998.10 | BOOO IN THOUS        | 0 |   | 0 | 0 | . 0 |   | 0 | 1 | 1   |          | 0   |    | 0 | 0 |

| 9998.20 | ANDS.<br>900 IN HUN- | 0 |   | 0 | 0 | 0   |   | 0 | 0 | . 1 |          | 1   |    | 0 | 0 |

| 999830  | DREDS.               | 0 | 1 |   | 0 | 0   | 1 |   | 0 | (   | 5        | 1   | 1  |   | 0 |

| 9998.40 | 90 IN TENS.          | 0 | 1 |   | 0 | 0   | 1 |   | 1 | (   | )        | . 0 | -1 |   | 0 |

| 999850  | 8 IN UNITS.          | 0 |   | 0 | 0 | 0   |   | 0 | 1 | 1   |          | 0   |    | 0 | 0 |

| 999860  | ,                    | 0 |   | 0 | 0 | 0   |   | 0 |   | 1   |          | 1   |    | 0 | 0 |

| 9999.70 |                      | 0 | 1 |   | 0 | 0   | - |   |   | •   | <b>o</b> | 1   | 1  |   | 0 |

| 9999.00 |                      | 0 | 1 |   | 0 | 0   | 1 |   | 1 |     | o        | 0   | 1  |   | 0 |

| 9999.10 | (9000 IN THOUS       | 0 |   | 0 | 0 | 0   |   | 0 | 1 | 1   |          | 0   |    | 0 | 0 |

| 9999.20 | ANDS.                | 0 |   | 0 | 0 | 0   |   | 0 |   | 1   |          | 1   |    | 0 | 0 |

| 9999.30 | DREDS                | 0 | 1 |   | 0 | 0   | 1 |   |   | •   | )        | 1   | 1  |   | 0 |

| 9999.40 | 90 IN TENS.          | 1 | 1 |   | 0 | 1   |   | 0 | 1 | (   | <b>o</b> | 0   | 1  |   | 0 |

| 999950  | CARRY AND CLEAR      | 0 |   | 0 | 1 | 0   | 1 |   |   | 1   |          | 0   |    | 0 | 1 |

| 9999.60 | CARRI AND CLEAR      | 0 |   | 0 | 0 | 0   |   | 0 |   | (   | 2        | 0   |    | 0 | 0 |

| 9999.70 |                      | 0 |   | 0 | 0 | 0   |   | 0 |   | (   | )        | 0   |    | 0 | 0 |

| 0000.00 |                      | 0 |   | 0 | 0 | 0   |   | 0 |   | (   | )        | 0   |    | 0 | 0 |

FIG.9C

**FIG.10**

| 7C         |

|------------|

| FIG.<br>7D |

| FIG.<br>9A |

| FIG.<br>9B |

| FIG.<br>9C |

INVENTOR.

CHARLES R. BORDERS

BY Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 19

Filed July 19, 1954

38 Sheets-Sheet 20

Filed July 19, 1954

38 Sheets-Sheet 21

CHARLES R. BORDERS

BY Duight D. Mooner

Filed July 19, 1954

38 Sheets-Sheet 22

FIG. 14

INVENTOR.

CHARLES R. BORDERS

BY Dwight D. Mooney

ATTORNEY

Filed July 19, 1954

38 Sheets-Sheet 23

#### CRT A

| 2 O 22 O O O 0 0 0 0 0 0 0 0 0 0 0 0 0 0      | 4 6 8 10<br>O O O O<br>24 26 28 30<br>O O O O<br>O O O O<br>84 86 88 90<br>O O O | 12 14 16 18<br>O O O O<br>32 34 36 38<br>O O O O<br>O O<br>O O O<br>92 94 96 98<br>O O O | 100 102 104 106 108 110 112 114 116 118<br>O O O O O O O O O O O O<br>120 122 124 126 128 130 132 134 136 138<br>O O O O O O O O O O O<br>140<br>O O O O O O O O O O O<br>160<br>O O O O O O O O O O O<br>180 182 184 186 188 190 192 194 196 198<br>O O O O O O O |

|-----------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O O 220 O 240 O O 260                         | 204 208<br>0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0 0 0 0                   | 212 218<br>O O O O<br>O O O O<br>O O O O<br>O O O O<br>O O O O<br>294 296<br>O O O O     | 300 304 308 312 316 318 O O O O O O O O O O O O O O O O O O O                                                                                                                                                                                                      |

| 420<br>O O<br>440<br>O O<br>460<br>O O<br>480 |                                                                                  | O O O O O O O O O O O O O O O O O O O                                                    | 500 O O O O O O O O O O O O O O O O O O                                                                                                                                                                                                                            |

| 620<br>O O<br>640<br>O O<br>660<br>O O<br>680 |                                                                                  | O O O O O O O O O O O O O O O O O O O                                                    | 700 O O O O O O O O O O O O O O O O O O                                                                                                                                                                                                                            |

| 820<br>O O<br>840<br>O O<br>860<br>O O<br>880 |                                                                                  | O O O O O O O O O O O O O O O O O O O                                                    | 900 918 918 938 938 938 958 960 960 978 978 978 978 978 978 978 978 978 978                                                                                                                                                                                        |

**FIG. 15A**

CHARLES R. BORDERS

Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 24

|                                                     |                   |                            |              |               |              |                                         |                                    |                                    |                                                          | CRT     | В                                                   |                    |                           |           |                                |         |                                |                  |                                |                                                     |

|-----------------------------------------------------|-------------------|----------------------------|--------------|---------------|--------------|-----------------------------------------|------------------------------------|------------------------------------|----------------------------------------------------------|---------|-----------------------------------------------------|--------------------|---------------------------|-----------|--------------------------------|---------|--------------------------------|------------------|--------------------------------|-----------------------------------------------------|

| 10 210 410 610 810                                  | 3 O 23 O O O 83 O | 5<br>O 25<br>O O O 85<br>O | 70270 0 0870 | 90 20 0 0 890 | 10 30 0 0 30 | 13<br>0<br>33<br>0<br>0<br>0<br>93<br>0 | 15<br>O<br>35<br>O<br>O<br>95<br>O | 17<br>0<br>37<br>0<br>0<br>97<br>0 | 39<br>O<br>59<br>O<br>79<br>O                            | CRI     | B<br>101<br>0 121<br>0 141<br>0 161<br>0 181        | 103<br>O<br>O<br>O | 105<br>O<br>O<br>185<br>O | 0700000   | 109<br>O<br>O<br>O<br>189<br>O | 1100000 | 113<br>O<br>O<br>O<br>193<br>O | 0 0 0            | 117<br>O<br>O<br>O<br>197<br>O | O<br>139<br>O<br>159<br>O<br>179<br>O               |

| 201<br>O<br>221<br>O<br>241<br>O<br>261<br>O<br>281 | 0 0 0 0           | 0 0 0 0 0                  | 0 0 0 0      | 0 0 0 0 0     | 0 0 0 0 0    | 0 0 0 0 0                               | 0 0 0 0 0                          | 00000                              | 219<br>O 239<br>O 259<br>O 279<br>O 299                  |         | 3 01<br>0 3 21<br>0 3 41<br>0 3 61<br>0 3 81        | 0 0 0 0            | 0 0 0 0 0                 | 0 0 0 0 0 | 0 0 0 0                        | 0 0 0 0 | 0 0 0 0 0                      | 0 0 0 0          | 0 0 0 0                        | 319<br>O<br>339<br>O<br>359<br>O<br>379<br>O<br>399 |

| 401<br>0 421<br>0 441<br>461<br>0 481               | 0 0 0 0           | 0 0 0 0 0                  | 00000        | 0 0 0 0       | 0 0 0 0      | 0 0 0 0 0                               | 00000                              | 0 0 0 0 0                          | 419<br>O<br>439<br>O<br>459<br>O<br>479<br>O<br>499<br>O |         | 501<br>521<br>541<br>561<br>580<br>581              | 0 0 0 0            | 0 0 0 0                   | 00000     | 0 0 0 0 0                      | 0 0 0 0 | 0 0 0 0 0                      | 0 0 0 0 0        | 00000                          | 519<br>O<br>539<br>O<br>559<br>O<br>579<br>O<br>599 |

| 601<br>621<br>641<br>661<br>661<br>681              | 0 0 0 0           | 00000                      | 00000        | 0 0 0 0       | 00000        | 0 0 0 0 0                               | 0 0 0 0                            | 0 0 0 0 0                          | 619<br>O<br>639<br>O<br>659<br>O<br>679<br>O<br>699      |         | 701<br>0<br>721<br>0<br>741<br>0<br>761<br>0<br>781 | 0 0 0 0            | 0 0 0 0                   | 0 0 0 0   | 0 0 0 0 0                      | 00000   | 00000                          | 0 0 0 0 0        | 00000                          | 719<br>O<br>739<br>O<br>759<br>O<br>779<br>O<br>799 |

| 801<br>O<br>821<br>O<br>841<br>O<br>861<br>O<br>881 | 00000             | 0 0 0 0                    | 0 0 0 0      | 0 0 0 0       | 0 0 0 0 0    | 0 0 0 0                                 | 0 0 0 0                            | 0                                  | 819<br>O<br>839<br>O<br>859<br>O<br>879<br>O<br>899      | · · · · | 901<br>O 921<br>O 941<br>O 961<br>O 981             | 0 0 0 0            | 00000                     | 0 0 0 0   | 0 0 0 0                        |         | 0<br>0<br>0<br>0<br>0<br>VVE   | 0<br>0<br>0<br>0 |                                | 919<br>O<br>939<br>O<br>959<br>O<br>979<br>O<br>999 |

FIG.15B

BY Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 25

#### CRT C

| 1000<br>0 0<br>1020<br>0 0<br>1040<br>0 0<br>1060<br>0 0           | 0 0 0   | 0       | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 0 | 0 0 0 0   | 0 1018<br>0 0 1038<br>0 0 1058<br>0 0 1078<br>0 1098<br>0 0             | 1100<br>0<br>1120<br>0<br>1140<br>0<br>1160<br>0    | 0 0 0 0   | 0 0 0 0 0 | 0 0 0 0          | 0 0 0 0          | 0 0 0 0 0   | 0 0 0 0 0 | 0 0 0 0                    | O 1118<br>O 0 1138<br>O 0 1158<br>O 0 1178<br>O 0 1198<br>O 0           |

|--------------------------------------------------------------------|---------|---------|---------|---------|-----------|-----------|-------------------------------------------------------------------------|-----------------------------------------------------|-----------|-----------|------------------|------------------|-------------|-----------|----------------------------|-------------------------------------------------------------------------|

| 1200<br>0 0<br>1220<br>0 0<br>1240<br>0 0<br>1260<br>0 1280<br>0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0   | 0 0 0 0 0 | 1218<br>O O<br>1238<br>O O<br>1258<br>O O<br>1278<br>O O<br>1298<br>O O | 1300<br>O<br>1320<br>O<br>1340<br>O<br>1360<br>O    | 0 0 0     | 0 0 0 0 0 | 0 0 0 0 0        | 0                | 0 0 0       | 0 0 0 0   | 0 0 0 0                    | 1318<br>O O<br>1338<br>O O<br>1358<br>O O<br>1378<br>O O<br>1398<br>O O |

| 1400<br>O O 1420<br>O O 1440<br>O O 1460<br>O O 1480<br>O O        | 0 0 0 0 | 0       | 0 0     | 0 0 0 0 | 0 0 0 0   | 0 0 0 0 0 | 1418<br>O O 1438<br>O O 1458<br>O O 1478<br>O 1498<br>O O               | 1500<br>1520<br>0<br>1540<br>0<br>1560<br>0<br>1580 |           | 0 0 0     | 0 0 0            | 0 0 0 0 0        | 0 0         | 0 0 0 0 0 | 0 0 0 0 0                  | O O 1558<br>O O 1578<br>O O 1578<br>O O 0 1598<br>O O 0                 |

| 1600<br>O O<br>1620<br>O O<br>1640<br>O O<br>1660<br>O O           | 0 0 0 0 |         | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 0 | 0 0 0 0 0 | 0 1618<br>0 0 1638<br>0 0 1658<br>0 0 1678<br>0 0 1698<br>0 0           | 1700<br>1720<br>0<br>1740<br>0<br>1760<br>0<br>1780 |           | 0 0 0 0 0 | 0 0 0 0          | 0 0 0 0          | 0 0 0 0     | 0 0 0 0   | 0 0 0 0                    | O 1718<br>O O 0<br>1738<br>O O 0<br>1758<br>O O 0<br>1778<br>O O 0      |

| 1800<br>O O<br>1820<br>O O<br>1840<br>O O<br>1860<br>O O           | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0   | 0 0 0 0 0 | 1818<br>O O<br>1838<br>O O<br>1858<br>O O<br>1878<br>O O<br>1898<br>O O | 1900<br>O<br>1920<br>O<br>1940<br>O<br>1960<br>O    | 0 0 0 0 0 | 00000     | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0 | NVE       | 0<br>0<br>0<br>0<br>0<br>0 |                                                                         |

FIG. 15C

Duight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 26

| ^ |   | ~ | _ |

|---|---|---|---|

| u | π |   | u |

| 1001<br>O O<br>1021<br>O O<br>1041<br>O O<br>1061<br>O O                | 0   | 0 0         | 0 0 0 0 | 0 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 1039                                                     | 1101<br>O<br>1121<br>O<br>1141<br>O<br>1161<br>O         | 0       | 0 0 0 0 | 0 0 | 0 0 0 0   |       | 0 0 0 0          | 0 0 0 0 0 | 0 0 0 0 | 1139<br>O<br>1159                                        |

|-------------------------------------------------------------------------|-----|-------------|---------|-----------|---------|---------|----------------------------------------------------------|----------------------------------------------------------|---------|---------|-----|-----------|-------|------------------|-----------|---------|----------------------------------------------------------|

| 1201<br>O O<br>1221<br>O O<br>1241<br>O O<br>1261<br>O O<br>1281<br>O O | 0   | 0 0 0 0 0 0 |         |           | 0 0 0 0 | 0 0 0 0 | 1219<br>O<br>1239<br>O<br>1259<br>O<br>1279<br>O<br>1299 | 130°<br>O<br>1321<br>O<br>1341<br>O<br>1361<br>O         | 0 0 0   | 0       | 0 0 | 0 0       | 0 0   | 0                | 0 0 0 0 0 | 00000   | 1319<br>O<br>1339<br>O<br>1359<br>O<br>1379<br>O<br>1399 |

| 1401<br>O O<br>1421<br>O O<br>1441<br>O O<br>1461<br>O O<br>1481<br>O O | 0 0 | 0 0         | _       | 0 0       | _       | 0 0 0 0 | 1419<br>O<br>1439<br>O<br>1459<br>O<br>1479<br>O<br>1499 | 1501<br>O<br>1521<br>O<br>1541<br>O<br>1561<br>O<br>1581 | 0       | 0 0     | 0 0 |           | 0 0   | 0 0 0 0 0        | 0 0 0 0   | 0 0 0   | 1519<br>O<br>1539<br>O<br>1559<br>O<br>1579<br>O<br>1599 |

| 1621<br>O O<br>1641<br>O O<br>1661<br>O O<br>1681                       | 0 0 | 0 0         |         | 0         |         | 0       | 1619<br>O<br>1639<br>O<br>1659<br>O<br>1679<br>O<br>1699 | 1701<br>O<br>1721<br>O<br>1741<br>O<br>1761<br>O<br>1781 | 0       | 0       | 0   |           | 0 0   |                  | 0 0 0 0   | 0 0 0   | 1719<br>O<br>1739<br>O<br>1759<br>O<br>1779<br>O<br>1799 |

| 1821                                                                    |     |             | 0 0 0 0 |           | 0 0 0 0 | 0       | 1819<br>O<br>1839<br>O<br>1859<br>O<br>1879<br>O<br>1899 | 1901<br>O<br>1921<br>O<br>1941<br>O<br>1961<br>O<br>1981 | 0 0 0 0 |         | 0   | 0 0 0 0 0 | 0 0 0 | 0<br>0<br>0<br>0 | 0 0 0     | 0 0 0 0 | 1919<br>O<br>1939<br>O<br>1959<br>O<br>1979<br>O<br>1999 |

INVENTOR.

FIG.15D

Dwight D. Mooney

Filed July 19, 1954

38 Sheets-Sheet 27

|                  | TAL & VERTIC         | AL DEFLECTION    | V CIRCUITS           | DECIMAL NO<br>CORRESPONDING |  |  |

|------------------|----------------------|------------------|----------------------|-----------------------------|--|--|

| THOUSAND'S ORDER | HUNDRED'S ORDER      | TEN'S ORDER      | UNIT'S ORDER         | TO ADDRESSE                 |  |  |

| 0000             | 0000                 | 0000             | 0000                 | 0                           |  |  |

|                  |                      | 4                | 0001                 | 1                           |  |  |

|                  |                      |                  | 0010                 | 2                           |  |  |

|                  |                      |                  | 0011                 | 3                           |  |  |

|                  |                      | TENS ORDER       | 0100                 | 4                           |  |  |

|                  |                      | INACTIVE         | 0101                 | 5                           |  |  |

|                  |                      |                  | 0110                 | 6                           |  |  |

|                  |                      | Y                | 0111                 | 7                           |  |  |

|                  |                      | Ť                | 1000                 | 8                           |  |  |

|                  |                      | 0000             | 1001                 | 9                           |  |  |

|                  |                      | 0001             |                      | 10                          |  |  |

|                  |                      | 1                |                      | 11                          |  |  |

|                  | UIMODEC'S SEC        |                  |                      | 12                          |  |  |

|                  | HUNDRED'S ORDER      | 0001 REMAINS     | INITIAL CYCLE        | 13                          |  |  |

|                  | IS INACTIVE          | FOR EACH NEW     | OF UNITS ORDER       | 14                          |  |  |

|                  |                      | ADDRESS          | REPEATED             | 15                          |  |  |

|                  |                      | /                | ,                    | 16                          |  |  |

| HOUSAND'S ORDER  |                      | ļ                |                      | 17                          |  |  |

| IS INACTIVE      |                      | 0001             |                      | 18                          |  |  |

| 13 THACTIVE      |                      | 0001             | <b>†</b>             | 19                          |  |  |

|                  |                      | 0010             | 0000                 | 20                          |  |  |

|                  |                      | 0011             |                      | 30                          |  |  |

|                  | <u> </u>             | 0100             |                      | 40                          |  |  |

|                  |                      | 0101             | INITIAL CYCLE OF     | 50                          |  |  |

|                  |                      | 0110             | UNITS ORDER RE-      | 60                          |  |  |

|                  |                      | 0111             | PEATED EACH TIME     | 70                          |  |  |

|                  | 0000                 | 1000             | TENS ORDER ADVANCES, | 80                          |  |  |

|                  |                      | 1001             |                      | 90                          |  |  |

|                  | 0001                 | 00,00            | 0000                 | 100                         |  |  |

|                  | 0010                 |                  | <b>A</b>             | 200                         |  |  |

|                  | 0011                 | INITIAL CYCLE OF | ·                    | 300                         |  |  |

|                  | 0100                 | TENS ORDER RE-   | ' INITIAL CYCLE OF ' | 400                         |  |  |

|                  | 0101                 | PEATED EACH      | UNITS ORDER RE-      | 500                         |  |  |

|                  | 0110                 | TIME HUNDRED'S   | PEATED EACH TIME     | 600                         |  |  |

|                  | 0111                 | ORDER ADVANCES   | TENS ORDER ADVANCES  | 700                         |  |  |

| 0000             | 1000                 |                  |                      | 800                         |  |  |

| 0000             | 1001                 | 0000             | <u> </u>             | 900                         |  |  |

| 3001             | 0000                 | 0000             | 0000                 | 1000                        |  |  |

|                  | 0001                 | 1                | A.                   | 1100                        |  |  |

|                  | 0010                 |                  |                      | 1200                        |  |  |

| 0001 REMAINS     | 001 <u>1</u><br>0100 | CANE             |                      | 1300                        |  |  |

| FOR EACH NEW     | 0100                 | SAME             |                      | 1400                        |  |  |

| ADDRESS          |                      |                  | SAME                 | 1500                        |  |  |

|                  | 0110                 |                  |                      | 1600                        |  |  |

| <del></del>      | 0111                 |                  |                      | 1700                        |  |  |

|                  | 1000                 | <u> </u>         |                      | 1800                        |  |  |

| 0001             | 1001                 | 0000             |                      | 1900                        |  |  |

| 0010             | 1001<br>0000         | 1001             | 0000                 | 1999<br>2000 (0             |  |  |

FIG. 16

CHARLES R. BORDERS

Filed July 19, 1954

38 Sheets-Sheet 28

INVENTOR.

CHARLES R. BORDERS

**FIG.17**

Dwight D Mooney

Filed July 19, 1954

38 Sheets-Sheet 29

FIG. 18

INVENTOR.

CHARLES R BORDERS

Duight D. Mooney

Filed July 19, 1954 38 Sheets-Sheet 30 SW10-- 369 - 367 SW100-354 g INVENTOR. FIG.19A FIG.19B CHARLES R. BORDERS

Filed July 19, 1954

38 Sheets-Sheet 31

CHARLES R. BORDERS

BY Durght D. Mooney

COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 33

TU9TUO <sup>/</sup>

Filed July 19, 1954

38 Sheets-Sheet 35

# FIG. 23

INVENTOR.

CHARLES R. BORDERS

BY Dwight D Mooney

Filed July 19, 1954

38 Sheets-Sheet 36

| T     |                                       | CIRC     | 111 | T P | OIN      | TC | / EIG   | -     | 00.0 | <u></u>  | TU  |          | C A A | 100      | _   |          |        |

|-------|---------------------------------------|----------|-----|-----|----------|----|---------|-------|------|----------|-----|----------|-------|----------|-----|----------|--------|

| TIME  | OPERATION                             |          |     | 14  |          |    | (FIG    | J.,   | 00,0 | U)       | 10  | 00       | SAI   | ND:      | 5 0 | שא       | EK     |

| 9.30  | OPERATION                             | 17(INPUT | 1   |     | 1        | 3  | 16-1000 | )   5 |      |          | 000 | D2       |       |          | 000 | D8       | 000    |

| 9.40  |                                       | 0        | ╁.  | 0   | —        | 0  | .0      | 1     | 0    | 1        |     | <u> </u> | 0     | 1        |     | <u> </u> | 0      |

| 9.50  |                                       | 0        | 1   |     | _        | 0  | 0       | 1     |      | _        | 0   | 1        |       | L        | 0   | 1        |        |

| 9.60  |                                       | 0        | +   | _0  | -        | 0  | 0       | _     | 0    | 1        |     | <u> </u> | 0     | 1        |     | L        | 0      |

| 9.70  |                                       | 0        | 1   |     | -        | 0  | 0       | 1     |      | ļ.,      | 0   | 1        |       | <u> </u> | 0   | 1        |        |

| 10.00 | READOUT 10                            | 0        | +.  | _0  | -        | 0  | 0       | 1     | 0    | 1        |     | <u> </u> | 0     | 1        |     | _        | 0      |

| 10.10 | READOUT 10                            | 0        | 1   |     | <u> </u> | 0  | 0       | 1     |      | <u> </u> | 0   | 1        |       | L        | 0   | 1        |        |

| 10.10 |                                       | 1        | 1   | 0   | Ļ        | 0  | 0       | 1     |      | 1.       |     |          | 0     | 1        |     | <u> </u> | 0      |

| 10.20 |                                       | 0        | 1   |     | _        | 0  | 0       | 1     |      | 1        |     | 1        |       |          | 0   | 1        |        |

| 10.40 |                                       | 0        | 1   | 0   | <u> </u> | 0  | 0       | _     | 0    | 1        |     | 1        |       | 1        |     |          | 0      |

|       |                                       | 0        | 1   |     | <u> </u> | 0  | 0       | 1     |      | <u> </u> | 0   | 1        |       | 4        |     | 1        |        |

| 10.50 |                                       | 0        | 1   |     |          | 0  | 0       | 1     |      | 1        |     |          | 0     | 1        |     | 1        |        |

| 10.60 |                                       | 0        | 1   |     | <u> </u> | 0  | 0       | 1     |      | 1        |     | 1        |       |          | 0   | 1        |        |

| 10.70 |                                       | 0        |     | 0   |          | 0  | 0       | L     | _0   | 1        |     | 1        |       | 1        |     |          | 0      |

| 11.00 | READOUT 11                            | 0        | .1  |     |          | 0  | 0       | 1     |      |          | 0   | 1        |       | 1        |     | 1        |        |

| 11.10 |                                       | 1        | 1   |     |          | 0  | 1       | L     | 0    | 1        |     |          | 0     | +        |     | 1        |        |

| 11.20 |                                       | 0        | 1   |     | 1        |    | 1       | L     | 0    |          | 0   | 1        |       |          | 0   | 1        |        |

| 11.30 |                                       | 0        | L   | 0   | 1        |    | 0       | 1     |      |          | 0   |          | 0     | 1        |     |          | 0      |

| 11.40 |                                       | 0        | 1   |     |          | 0  | 0       | 1     |      | 1        |     |          | 0     |          | 0   | 1        |        |

| 11.50 |                                       | 0        |     | 0   |          | 0  | 0       |       | 0    | 4        |     | 1        |       |          | 0   |          | 0      |

| 11.60 |                                       | 0        |     | 0   |          | 0  | 0       | L     | 0    |          | 0   | 1        |       | 1        |     |          | 0      |

| 11.70 |                                       | 0        | 1   |     | <u> </u> | 0  | 0       | 1     |      |          | 0   |          | 0     | 1        |     | 1        | $\Box$ |

| 12.00 | READOUT 12                            | 0        | 1   |     |          | 0  | 0       | 1     |      | 1        |     |          | 0     |          | 0   | 1        | $\neg$ |

| 12.10 |                                       | 1        |     | 0   |          | 0  | . 0     | 1     |      | 1        |     | 1        |       |          | 0   |          | 0      |

| 12.20 |                                       | 0        |     | 0   |          | 0  | 0       |       | 0    | 1        |     | 1        |       | 1        |     |          | 0      |

| 12.30 |                                       | 0        | 1   |     |          | 0  | 0       | 1     |      |          | 0   | 1        |       | 1        |     | 1        |        |

| 12.40 |                                       | 0        | 1   |     |          | 0  | 0       | 4     |      | 1        |     |          | 0     | 1        |     | 4        | $\neg$ |

| 12.50 |                                       | 0        | 1   |     |          | 0  | . 0     | 1     |      | 1        |     | 1        |       |          | 0   | 1        | $\neg$ |

| 12.60 |                                       | 0        |     | 0   |          | 0  | 0       |       | 0    | 1        |     | 1        |       | 1        |     |          | 0      |

| 12.70 | · · · · · · · · · · · · · · · · · · · | 0        | 1   |     |          | 0  | 0       | 1     |      |          | 0   | 1        |       | 1        |     | 1        | ヿ      |

FIG. 24A

INVENTOR.

BY

Dwight D. Mooney

COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 37

|       |            | CIRCL              | IJТ | PC | TNIC     | ·s | (FI      | 3S. | 8C,      | 8D  | ) T      | НО             | US       | AN  | os  | OF | RDE      | R   |

|-------|------------|--------------------|-----|----|----------|----|----------|-----|----------|-----|----------|----------------|----------|-----|-----|----|----------|-----|

| TIME  | OPERATION  | 1 <b>7</b> (INPUT) | 14  | }  | 13       | ,  | 16-10    | 00  | 15-10    | 000 | D4       | 000            | D20      | 000 | DIO | 00 | D80      | 100 |

| 13.00 | READOUT 13 | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 4        |                |          | 0   | 4   |    | 1        |     |

| 13.10 | ·          | 4                  | 1   |    |          | 0  | 1        |     |          | 0   | 1        |                | 4        |     |     | 0  | 1        |     |

| 13.20 | •          | 0                  |     | 0  | 1        |    |          | 0   | 1        |     |          | 0              | 1        |     | 1   |    |          | 0   |

| 13.30 | *          | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                |          | 0   | 4   |    | 1        |     |

| 13.40 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                | 1        |     |     | 0  | 1        |     |

| 13.50 |            | 0                  |     | Ó  |          | 0  |          | 0   |          | 0   | 1        |                | 1        |     | 4   |    |          | 0   |

| 13.60 |            | 0                  | 1   |    |          | 0  |          | Q   | 1        |     |          | 0              | 1        |     | 1   |    | 1        |     |

| 13.70 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                |          | 0   | 1   |    | 1        |     |

| 14.00 | READOUT 14 | 0                  | 1   | -  |          | 0  |          | 0   | 1        |     | 4        |                | 1        |     |     | 0  | 1        |     |

| 14.10 |            | 1                  |     | 0  |          | 0  | ·        | 0   | 1        | -   | 1        |                | 4        |     | 4   |    |          | 0   |

| 14.20 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                | 1        |     | 1   |    | 1        |     |

| 14.30 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                | 1        |     | 1   |    | 1        |     |

| 14.40 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                | 1        |     | 1   |    | 1        |     |

| 14.50 |            | 0                  | 1   |    |          | 0  | <u> </u> | 0   | 1        |     | 1        | •              | 1        |     | 1   |    | 1        |     |

| 14.60 |            | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        | · <del>,</del> | 1        |     | 1   |    | 1        | _   |

| 14.70 |            | 0                  | 1   |    | <u> </u> | 0  |          | 0   | 1        |     | 1        |                | 1        |     | 1   |    | 1        |     |

| 15.00 | READOUT 15 | 0                  | 1   |    |          | 0  |          | 0   | 1        |     | 1        |                | 1        |     | 1   |    | 1        |     |

| 15.10 |            | 1                  | 1   |    |          | 0  | 1        |     |          | 0   | 1        |                | 1        |     | 1   |    | 1        | _   |

| 15.20 |            | 0                  | 1   |    | 1        |    | 1        |     | <u> </u> | 0   |          | 0              | 1        |     | 1   |    | 1        |     |

| 15.30 |            | 0                  | 1   |    | 1        |    | 1        |     |          | 0   |          | 0              |          | 0   | 1   |    | 1        |     |

| 15.40 |            | 0                  | 1_  |    | 1        |    | 1        |     |          | 0   |          | 0              |          | 0   |     | 0  | 4        |     |

| 15.50 | -          | 0                  |     | 0  | 1        |    |          | 0   | 1        |     |          | 0              | L        | 0   |     | 0  |          | 0   |

| 15.60 |            | 0                  |     | 0  |          | 0  |          | 0   |          | 0   | 1        | 0              | <u> </u> | 0   |     | 0  | <u> </u> | 0   |

| 15.70 |            | 0                  |     | 0  | L        | 0  | <u> </u> | 0   |          | 0   | <u> </u> | 0              | 1        |     |     | 0  |          | 0   |

| 0.00  |            | 0                  |     | 0  |          | 0  | L        | 0   | <u> </u> | 0   |          | 0              | Ŀ        | 0   | 1   |    |          | 0   |

FIG. 24B

FIG. 24C

FIG. 7D FIG. 24A FIG. 24B

FIG. 7C

INVENTOR.

CHARLES R. BORDERS

Duight D. Mooney

Dec. 26, 1961

# C. R. BORDERS

3,014,662

COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Filed July 19, 1954

38 Sheets-Sheet 38

# FIG. 25

| TIME  | COUNTING           | DESIGNATED TERMINALS CONNECTED TO TERMINALS LISTED IN SAME COLUMN |     |     |       |     |      |     |

|-------|--------------------|-------------------------------------------------------------------|-----|-----|-------|-----|------|-----|

|       | ( CARRY AND CLEAR) | 282<br>n.2PULSE                                                   | D4  | D2  | D4    | D8  | 13   | 450 |

| 0.20  | CCI                | 202                                                               | 200 |     |       |     |      |     |

| 1.20  | C C2               | 202                                                               |     |     |       |     | 200  |     |

| 2.20  | CC3                |                                                                   | 200 |     | "", I | 202 |      |     |

| 3.20  | CC4                |                                                                   |     |     | 1     | 202 | 200  |     |

| 4.20  | CC5                |                                                                   | 200 |     | 202   |     |      |     |

| 5. 20 | CC6                |                                                                   |     |     | 202   |     | 200  |     |

| 6.20  | CC7                |                                                                   | 455 |     | 453   | 454 |      |     |

| 7.20  | CC8                |                                                                   |     |     | 453   | 454 | 4.55 |     |

| 8.20  | CC9                | 455                                                               | 453 | 454 |       |     |      |     |

| 9.20  | C C 10             |                                                                   |     | 202 |       |     | 200  |     |

| 10.20 | CCH                | 456                                                               | 457 | 458 |       | 459 |      |     |

| 11.20 | C C12              | 456                                                               |     | 457 |       | 458 |      | 459 |

| 12.20 | C C13              | 456                                                               | 457 | 458 | 459   |     |      |     |

| 13.20 | C C14              | 456                                                               |     | 457 | 458   |     |      | 459 |

| 14.20 | C C15              |                                                                   | 456 | 457 | 458   | 459 |      |     |

| 15.20 | C C16              | 456                                                               |     | 457 | 458   | 459 |      |     |

INVENTOR.

CHARLES R BORDERS

FIG. 26

Durght D. Mooney

3,014,662 COUNTERS WITH SERIALLY CONNECTED DELAY UNITS

Charles R. Borders, Alpine, N.J., assignor to International Business Machines Corporation, New York, N.Y., a corporation of New York

Filed July 19, 1954, Ser. No. 444,251 30 Claims. (Cl. 235-176)

This invention relates to electronic circuits and more 10 particularly to a novel regeneration type counter.

In the binary notation only two digits are employed; i.e., 0 and 1. The binary digit 0 is represented by decimal digit 0 and the binary digit 1 is represented by decimal digit 1. These binary digits are referred to as bits. 15 The digital positions or orders in a binary number, reading from right to left, correspond in value to 20, 21, 22, 23, 24, etc. or decimal digits 1, 2, 4, 8, 16, etc. respectively. For example, binary number 1001 represents decimal digit 9 which is determined by the addition of 20 decimal digits 1 and 8 indicated by a binary 1 in the extreme right and left binary positions respectively. Hence, by using binary bits or pulses in groups of four wherein a pulse represents a binary 1 and the absence of a pulse represents a binary 0 any decimal digit from 0-9 inclusive may be written in the pure binary-notation.

This system of representing decimal numbers, digit for digit, in the pure binary notation is referred to herein as the binary-decimal system. The four consecutive binary orders, reading from right to left, represent the 30 decimal digits 1, 2, 4 and 8 for the units decimal order and are accordingly referred to as the 1 bit, 2 bit, 4 bit and 8 bit respectively. It follows that the four binary orders of the tens decimal order represent the decimal digits 10, 20, 40 and 80, respectively. Likewise, in sub- 35 sequent decimal orders, for example, the four respective binary orders of the hundreds decimal order represent the decimal digits 100, 200, 400 and 800 respectively.

As an example, 459 will be represented in the binarydecimal system by 0100,0101,1001. The four binary bits at the right represent the decimal digit 9 of the units order, the next four bits to the left represent the decimal digit 5 of the tens order, and the four bits at the extreme left represent the decimal digit 4 of the hundreds order.

Any decimal number from 0-15 inclusive can be represented by a group of four binary bits. If the decimal number is 16, than a binary carry occurs to the next group of binary bits to be added or to the next decimal order. However, in the binary-decimal system, only the 50 decimal digits 0-9 inclusive are represented by each group of four binary bits.

The addition of two decimal digits or a decimal column of the decimal numbers to be added may provide at most a sum of 18 plus a carry. The range of decimal sums is, therefore, 0-19 inclusive. As stated, if this addition is performed in the pure binary notation, and the sum is 16 or more, a carry is provided and in any case if the sum is over 9 (1001), it is not expressed in the binary-decimal system by mere binary addition. It follows that the sum, in the binary-decimal system of two decimal numbers written in the binary-decimal system, may be obtained by adding the two numbers in the pure binary notation and providing circuit means response to a sum greater than 9 (1001), which circuit means will reduce such sums to the appropriate digit (less than ten) and a decimal carry.

A principal object of the invention is to provide a novel regeneration counter which produces a cyclic output representative of the value stored therein.

Another object is to provide a novel regeneration counter wherein binary bits are read in serially and the

binary sum of the bits read in is read out either serially or in parallel.

A further object is to provide a regeneration counter having a predetermined maximum storage capacity for any preselected value from 1 to 16, inclusive.

A still further object is to provide a regeneration counter which automatically effects clear and carry in response to any predetermined number of input pulses.

Another object is to provide a regeneration counter including a binary adder and a plurality of delay circuits for effecting storage of binary bits received in sequence and providing an output, representing the sum stored, in either parallel form or serial form.

Still another object of the invention is to provide a novel octal counter for producing similar pulses during each of eight uniform time intervals collectively comprising a predetermined cycle.

A further object is to provide a novel circuit means for cyclically producing uniformly spaced pulses in time wherein the initiation of the production of a certain preselected pulse of each cycle causes the initiation of a new cycle of operation.

Another object is to provide a novel regeneration counter having a plurality of serially connected orders wherein the amount stored in each order is in circulation and is read out periodically in response to a single read out pulse.

A further object is to provide a plural order counter wherein pulses representing the amount stored therein are in continuous circulation to provide a cyclically repetitious read out in the absence of successive read in.

A still further object is to provide a novel octal commutator operable as a master to produce eight uniformly spaced pulses during each cycle of operation and to control slave commutators for producing similar pulses synchronized therewith.

Other objects of the invention will be pointed out in the following description and claims and illustrated in the accompanying drawings, which disclose, by way of example, the principle of the invention and the best mode, which has been contemplated, of applying that principle.

In the drawings:

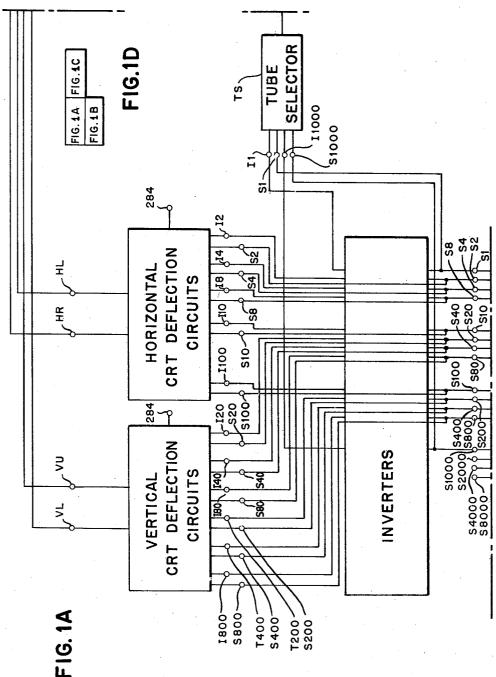

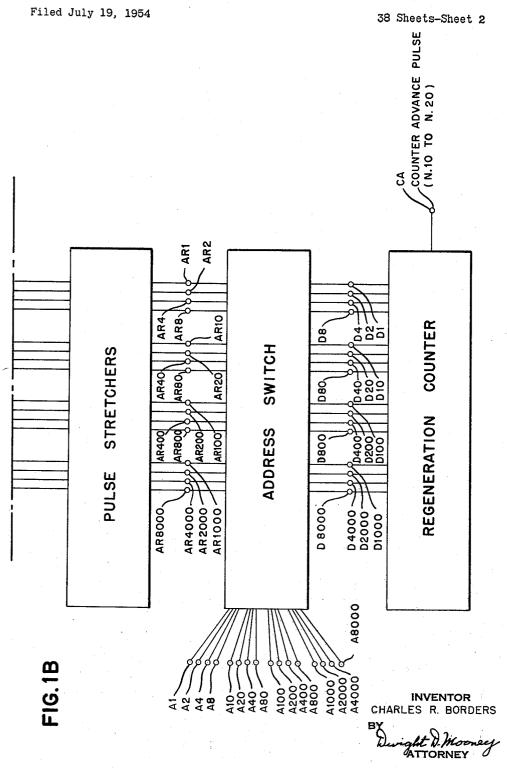

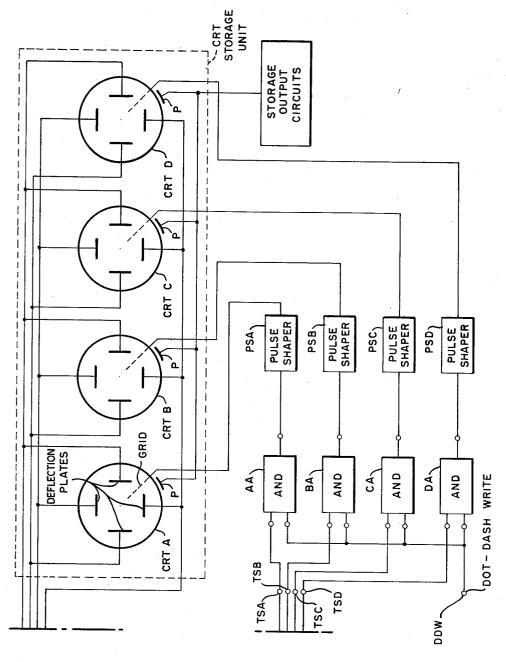

FIGS. 1A, 1B and 1C are block diagrams of a cathode ray storage system,

FIG. 1D shows the arrangement of FIGS. 1A, 1B and 1C to form a complete block diagram of the storage system.

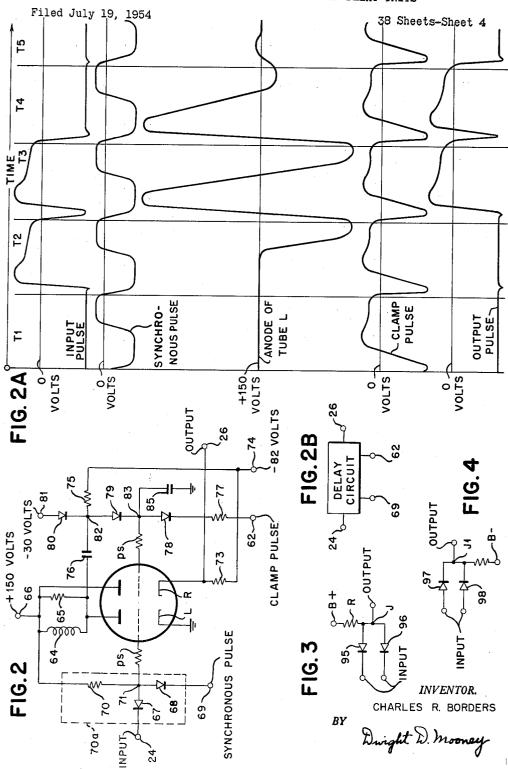

FIGS. 2 and 2B are circuit and block diagrams respectively of a delay circuit employed in practicing the invention, FIG. 2A shows waveforms explanatory of the opera-

tion of the circuit of FIG. 2.

FIG. 3 is a circuit diagram of a typical AND circuit employed by the invention,

FIG. 4 is a circuit diagram of a typical OR circuit employed by the invention,

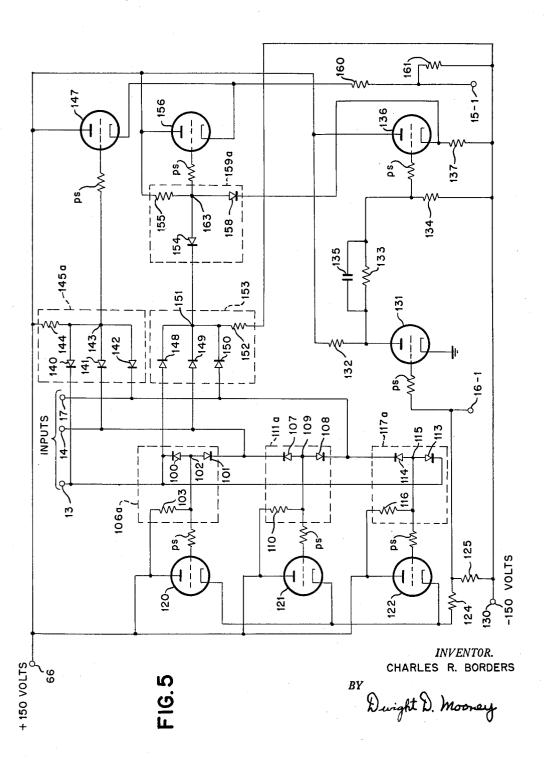

FIG. 5 is a circuit diagram of a binary adder employed by the invention.

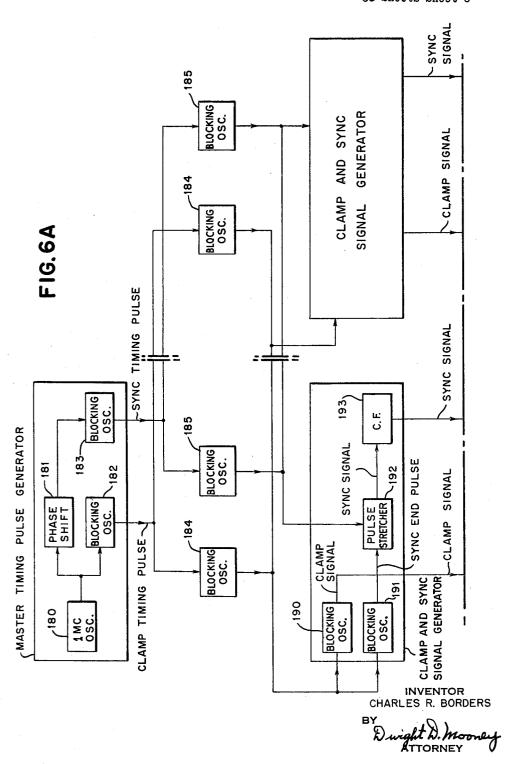

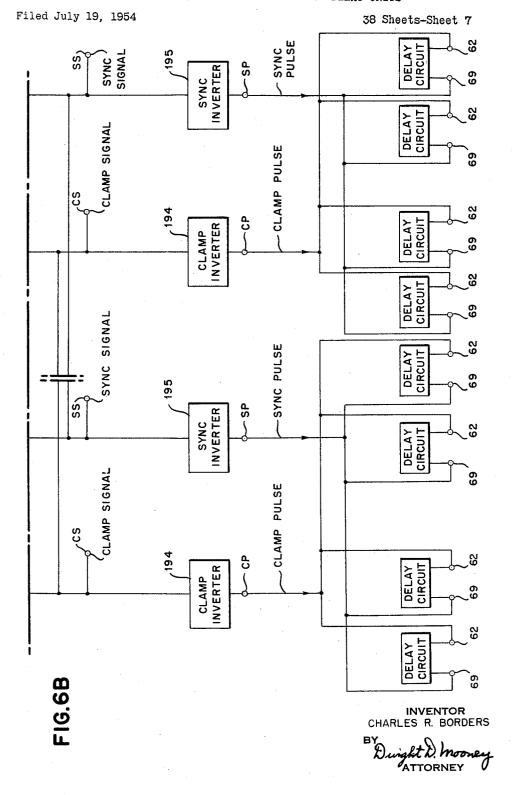

FIGS. 6A and 6B show in block diagram form a clamp and sync signal, and clamp and sync pulse source suitable for use with the delay circuits employed in practicing the invention.

FIG. 6C shows idealized waveforms explanatory of the operation of FIGS. 6A and 6B,

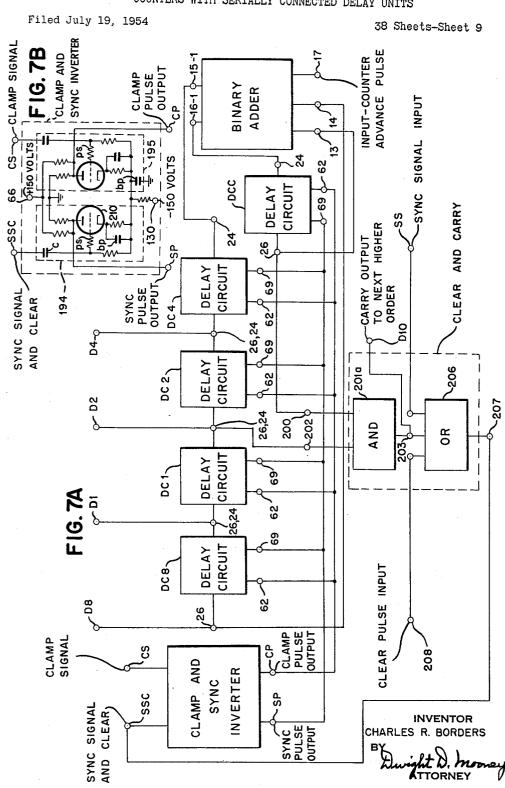

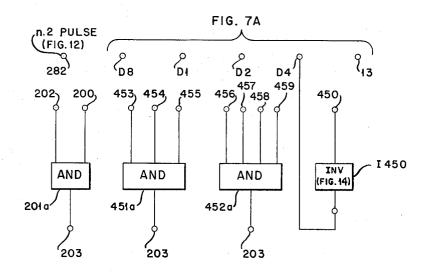

FIG. 7A shows in block diagram form one order of the regeneration counter of the invention,

FIG. 7B is a circuit diagram of a clamp and sync inverter suitable for use in FIG. 7A.

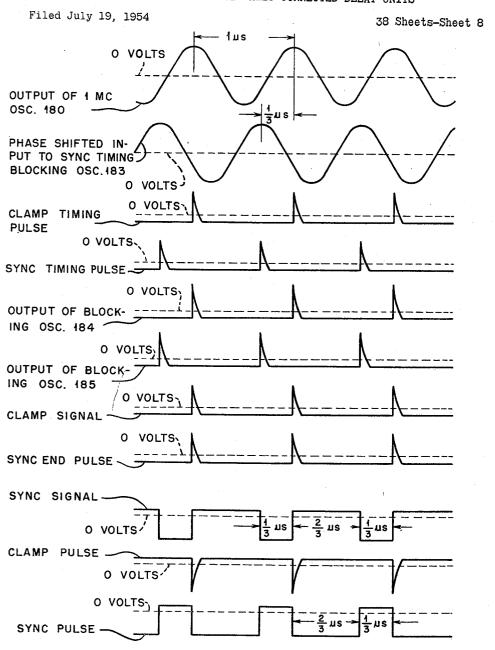

FIGS. 7C and 7D comprise a chart indicating a cycle of operation for the counter order shown in Fig. 7A,

FIG. 7E shows the arrangement of FIGS. 7C and 7D to form a single chart,

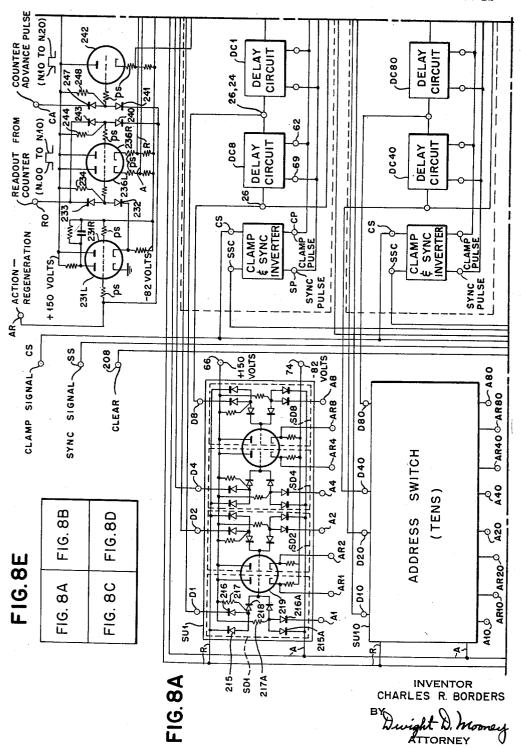

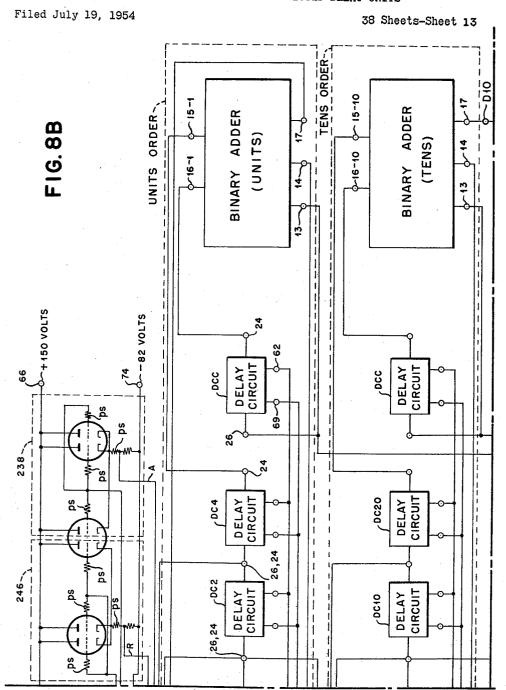

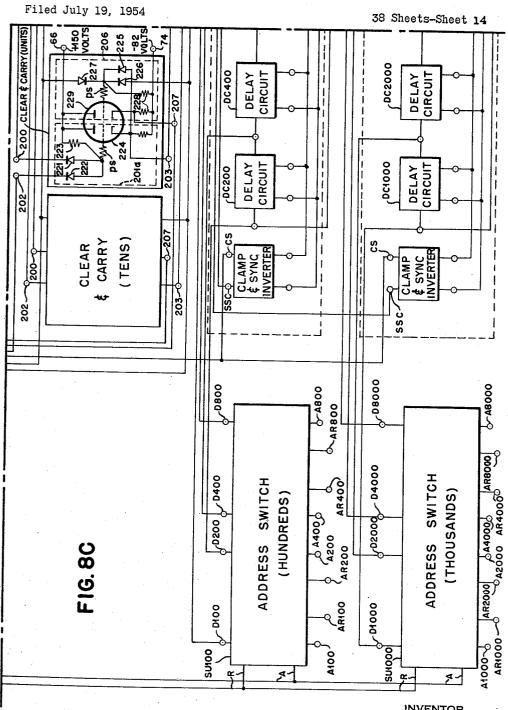

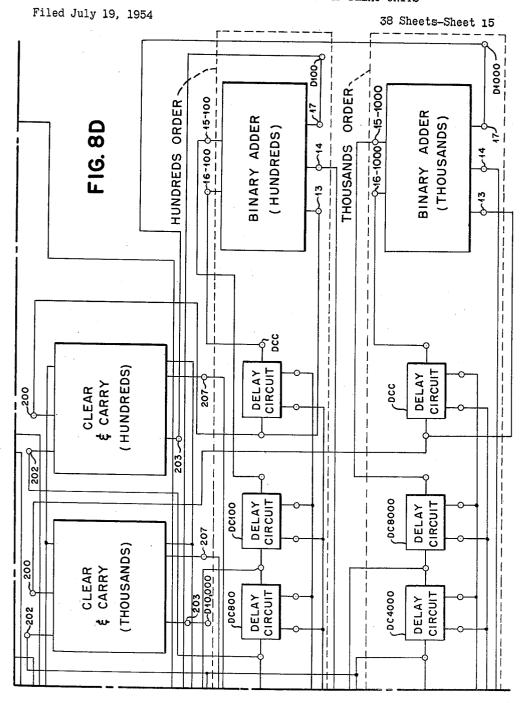

FIGS. 8A, 8B, 8C and 8D comprise a diagram of the regeneration counter of the invention and the address switch employed,

FIG. 8E shows the arrangement of FIGS. 8A, 8B, 8C

and 8D to form a single diagram,

FIGS. 9A, 9B and 9C are charts explanatory of the operation of the counter of FIGS. 8A, 8B, 8C and 8D,

FIG. 10 shows the arrangement of FIGS. 7C, 7D, 9A, 9B and 9C to form a single chart explanatory of the operation of the entire counter of FIGS. 8A, 8B, 8C and 10 8D.

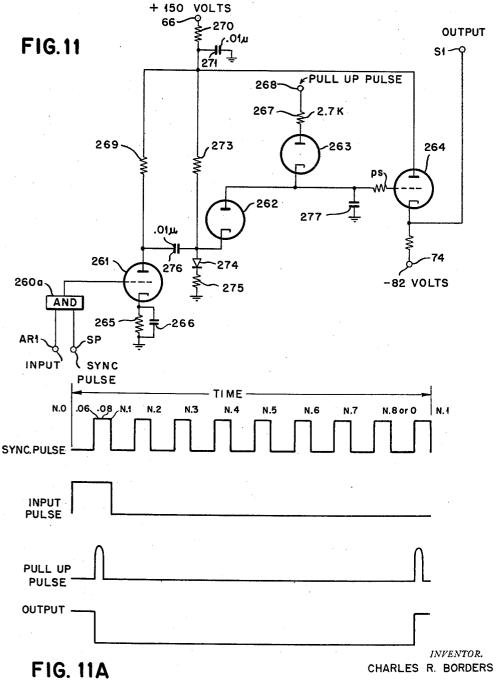

FIG. 11 is a circuit diagram of a pulse stretcher employed by the invention.

FIG. 11A is a timing chart explanatory of the operation of the pulse stretcher of FIG. 11,

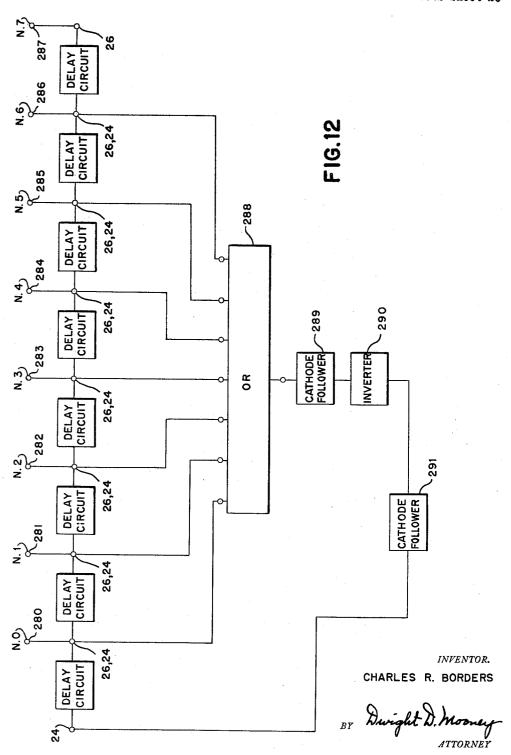

FIG. 12 is a diagram of a free running octal commutator of the invention,

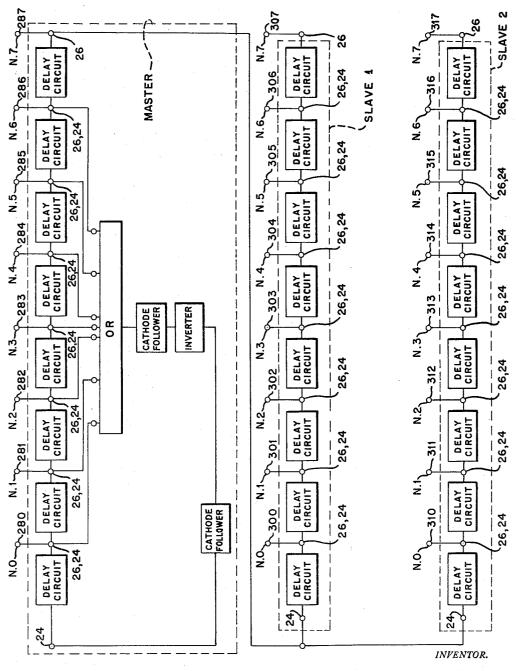

FIG. 12A is a diagram of a free running octal commutator of the invention employing master and slave commutators.

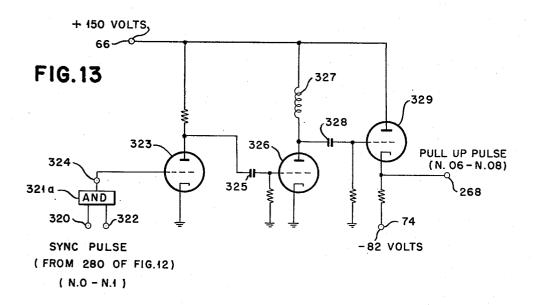

FIG. 13 shows a suitable circuit for providing the pull up pulse required for the operation of the circuit diagram of FIG. 11,

FIG. 14 is a circuit diagram of an inverter,

FIGS. 15A, 15B, 15C and 15D, respectively, show the physical arrangement of stored information upon the face of the CRTs A, B, C and D shown in FIG. 1C,

FIG. 16 is a chart showing the operation of the regeneration counter or voltages applied to the deflection circuits and to the tube selector to obtain a deflection of the electron beams to corresponding addresses,

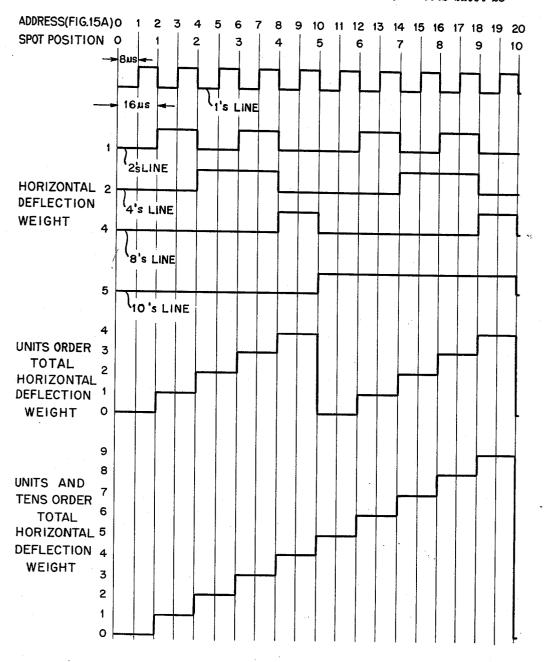

FIG. 17 is a horizontal deflection weight voltage chart representing the voltage values employed to produce horizontal beam deflection to the indicated addresses and spot positions,

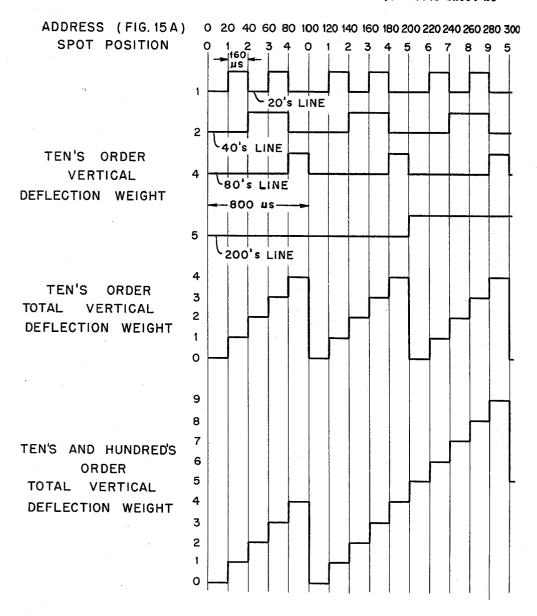

FIG. 18 is a vertical deflection weight voltage chart representing the voltage values employed to produce vertical beam deflection to the indicated addresses and spot positions,

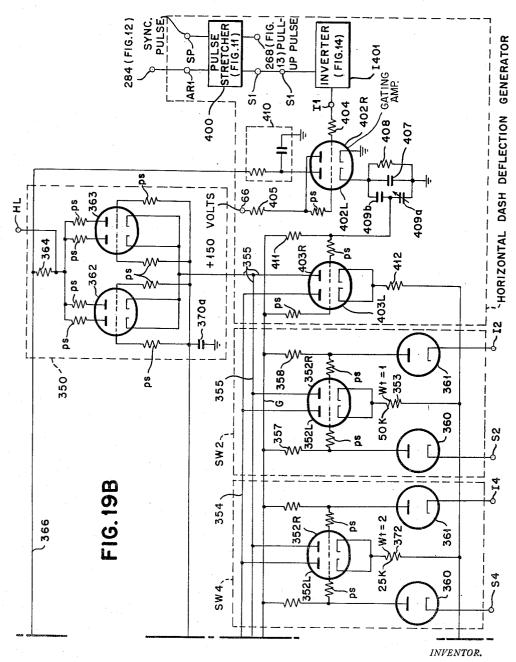

FIGS. 19A and 19B show horizontal deflection circuits 40 suitable for producing the storage pattern shown in FIGS. 15A, 15B, 15C and 15D.

FIG. 19C shows the placement of FIGS. 19A and 19B to form the complete horizontal deflection circuits,

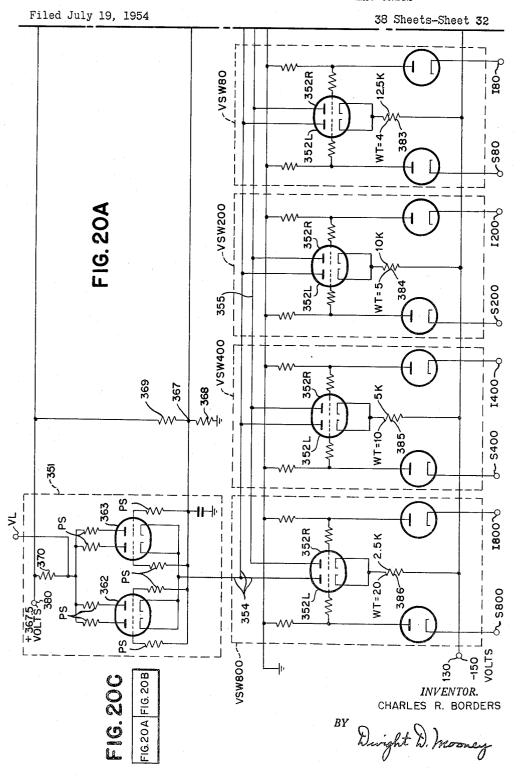

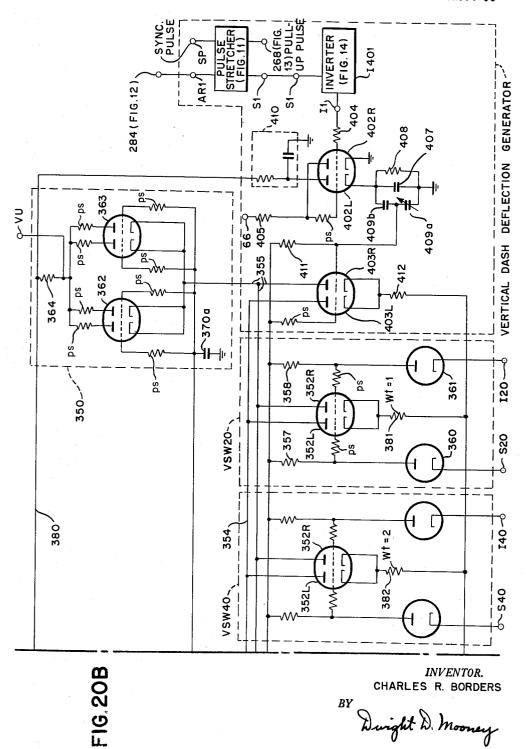

FIGS. 20A and 20B comprise a circuit diagram of a vertical deflection circuit suitable for use with the in- 45 vention,

FIG. 20C shows the arrangement of FIGS. 20A and 20B to realize a complete vertical deflection circuit dia-

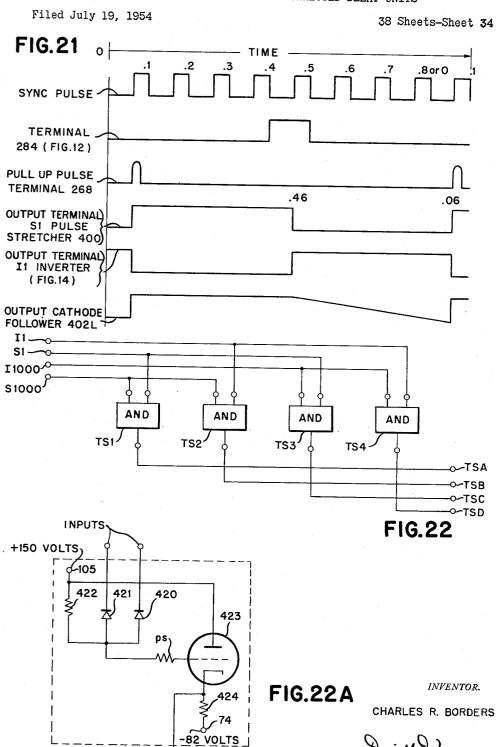

FIG. 21 shows waveforms realized from operation of 50 the dash deflection generator shown in FIGS. 19B and 20B.

FIG. 22 is a block diagram of the tube selector,

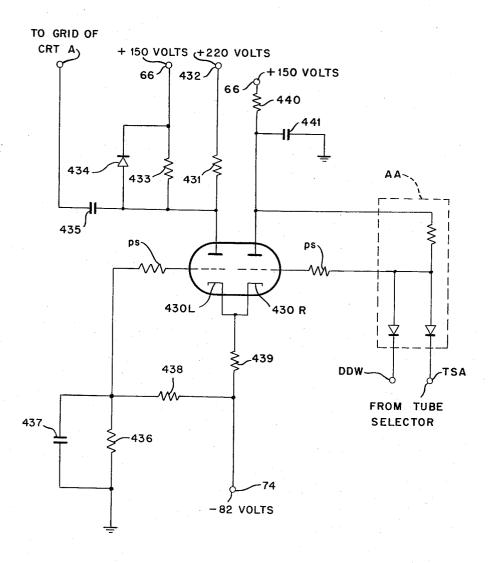

FIG. 22a is a circuit diagram of a circuit suitable for use in the tube selector of FIG. 22,

FIG. 23 is a circuit diagram of a suitable AND circuit and pulse shaper circuit,

FIGS. 24A and 24B comprise a chart showing the operation of the regeneration counter when decimal numbers 9 to 15 are read out,

FIG. 24C shows the placement of FIGS. 7C, 7D, 24A and 24B to form a single chart showing operation of the regeneration counter for read out of all numbers from 0 to 15.

FIG. 25 is a diagrammatic showing which provides for 65 connections to cause the regeneration counter of FIG. 7A to read out when it reaches any predetermined number from 0 to 15, and

FIG. 26 is a chart showing the particular connections made in FIG. 25 to obtain read out of each number 70 from 1 to 16,

Various circuits used herein or particular points within the circuits are frequently referred to as Up or Down. Up means that the voltage present at the particular point 4

respect to ground. Down means that the voltage present at the particular point or at the output of the circuit designated is negative with respect to ground. If the control grid of a vacuum tube is referred to as Down, it means that the voltage at that control grid is below the cutoff value for the vacuum tube if the cathode thereof is grounded, otherwise it means that the voltage is at the lower of two values each of which is present during the operation of the tube.

Numerous coincidence circuits are employed herein. An AND circuit refers to a circuit which is operable to produce a positive voltage at its output terminal only when all of the input terminals thereof have a positive voltage applied thereto simultaneously. An OR circuit 15 refers to a circuit operable to produce a positive voltage at its output terminal when only one or a plurality of the input terminals thereof have a positive voltage applied thereto.

When information is stored on a cathode ray tube it 20 must be refreshed or is lost. The time during which this refreshing is effected is referred to herein as a regenera-

Information is read in or read out of cathode ray tube storage during a preselected operational cycle. cycle is referred to herein as an action cycle.

As described herein each regeneration cycle and each action cycle have a duration of 8 microseconds or eight time intervals.

As used herein a word is represented by 16 decimal 30 digits to be stored. The term CRT unit refers to four cathode ray tubes operated in parallel to accommodate the storage of a single binary bit of each of the words to be stored.

The system of timing designation used herein com-35 prises a combination of octal and decimal representations. For example, in designation 1.15 the 1 to the left of the decimal point represents the number of cycles already performed, the 1 to the right of the decimal point represents the particular microsecond interval of the cycle, and the second number 5 to the right of the decimal point represents that the time referred to is 1/40 of a microsecond in addition to the one microsecond represented by the 1 to the right of the decimal point. Hence, the time indicated is 15/10 microseconds after the beginning of the second cycle.

As a further example, the time designation 4.30 represents the beginning of the third microsecond interval of the fifth cycle, four cycles having already elapsed. Each cycle has a duration of eight microseconds.

As a still further example a pulse may be said to be present from N.10 to N.20. This means that a pulse having a duration of one microsecond occurs between the first and second microsecond intervals of each cycle.

#### General description

The regeneration counter of the invention is illustrated as employed in an electrostatic cathode ray storage system. All operations of the storage system are effected during either an action cycle or a regeneration cycle.

Referring more particularly to FIGS. 1A, 1B and 1C, the input to the regeneration counter is a positive counter advance pulse applied to terminal CA from time N.10 to N.20 of each action and regeneration cycle. Circuit means are described hereinafter for rendering the counter advance pulse ineffective during an action cycle. Hence, the counter advance pulse is effective to advance the storage effected by the regeneration counter only during regeneration cycles. The output at the regeneration counter is available during one time interval of each regeneration cycle or during one-eighth of the time of that cycle. Each output of the regeneration counter consists of a preselected number of binary outputs or representations of binary bits in parallel and is used to or at the output of the circuit designated is positive with 75 position the electron beams of the cathode ray tubes to

a preselected position or address. Each subsequent counter advance pulse is added to the output of the counter, which output is used to cause the electron beams to assume the next preselected position or address during a regeneration cycle; during an action cycle the 5 counter is effectively stationary. The regeneration counter therefore provides the address control required to obtain a refreshing or regeneration, during all regeneration cycles of the information electrostatically stored on the face of the cathode ray tubes. The output 10 of the regeneration counter is present in the binarydecimal notation at the terminals D1-D8000 (FIG. 1B). The output of the regeneration counter serves as one input to the address switch (FIG. 1B). The address switch includes another group of input terminals desig- 15 nated A1-A8000. These terminals receive an input in the binary-decimal notation similar to the output of the regeneration counter and in each instance designate the one of the addresses or beam positions to be selected during that action cycle. The actual generation of the 20 pulses applied to terminals A1-A8000 is not shown It is understood that any suitable source may be employed.

The address switch includes a plurality of two-poletwo-position switches. The inputs of these separate 25 switches are connected to corresponding terminals A1-A8000 and D1-D8000. For example, one switch has one of its input terminals connected to terminal D1 and its other input terminal connected to terminal A1. As a further example, the terminals A1000 and D1000 are 30 connected to the respective inputs of another switch. During an action cycle, a voltage is applied to each address switch such that the switch is energized if an input is provided by the A terminal connected thereto. During a regeneration cycle, a voltage is applied to each switch 35 such that the switch is energized if an input is provided by the D terminal connected thereto. During each cycle, action or regeneration, an output is present from time N.00 to N.10 at the output terminals AR1-AR8000 of the address switch. The output at these terminals is 40 applied to the pulse stretchers (FIG. 1B) which provide outputs at the corresponding output terminals S1-S8009 during substantially the entire portion of that cycle. These output terminals S1-S1000 are connected to supply inputs to the inverters (FIG. 1A) to provide an output at the terminals II-I1000.

The cathode ray tube (CRT) storage unit (FIG. 1C) comprises four cathode ray tubes CRT A, CRT B, CRT C and CRT D having their deflection plates connected in parallel so that the electron beam of each tube is always at the same position or address as that of the 50 The tube selector (FIG. 1A) having its inputs supplied from terminals I1, S1, I1000 and S1000 determines which of the cathode ray tubes CRT A, CRT B, CRT C or CRT D is selected for read in, read out or regeneration during the particular action or regeneration 55 cycle being performed. At any given time only one of the cathode ray tubes is operable. Hence, CRTs A, B, C and D function as a single tube and effect the storage of a single binary bit. Four cathode ray tubes are used instead of one in order to decrease the spot or density of storage areas and thereby decrease the effect of interaction between the storage areas. Since any decimal digit to be stored includes four binary bits, four such units or 16 cathode ray tubes will be required to store one decimal digit. Hence, if a word to be stored includes 65 16 decimal digits a total of 16×16 or 256 cathode ray tubes will be required.

The terminals S2-S10, S100, I2-10, and I100 are connected to supply inputs to the horizontal deflection circuits and terminals S2-S80, S200-S800, I20-I80 and 70 I200-I800 are connected to supply inputs to the vertical deflection circuits. The output terminals HR and HL of the horizontal deflection circuits are connected respectively to the right and left horizontal deflection plates of the CRTs A, B, C and D. The output terminals VU 75

6

and VL of the vertical deflection circuits are connected respectively to the upper and lower plates of the CRTs A, B, C and D. The voltage present at these outputs is such that the deflection of the electron beam in each CRT A, B, C and D follows a predetermined pattern in response to inputs to the terminals A1-A8000 and terminals D1-D8000.

Circuits under the control of the tube selector and an external voltage representative of a dot and a dash supply an increased voltage to the grid of the cathode ray tube selected to effect the read in of a dot or dash, as the case may be, during an action cycle. During a regeneration cycle these circuits effect the refreshing or regeneration of the information previously stored.

A pickup plate P is placed in proximity to the face of each CRT and connected in parallel to storage output circuits to effect a read out of the information stored.

#### Delay circuit

Referring more particularly to FIGS. 2 and 2A, the delay circuit shown is used repeatedly herein. This circuit is claimed in the application of Byron L. Havens, Serial No. 239,370, filed July 30, 1951, now Patent 2,624,839 on January 6, 1953 and reissued as Re. 23,699 on August 18, 1953. The curves of FIG. 2A demonstrate the operation of the circuit shown in FIG. 2. In order to facilitate the description, the time axis (abscissa) is divided into equal time intervals designated T1, T2, T3, T4 and T5, respectively. The length of each of these time intervals is dependent upon the particular circuit design and as used herein is equal to one microsecond or the time elapsing between the initiation of the addition of one decimal column and the initiation of the addition of the next decimal column to be added.

Briefly, an input pulse (FIG. 2A) is applied to the input terminal 24 of the circuit shown in FIG. 2 during one preselected time interval and produces an output pulse (FIG. 2A) at the output terminal 26 during the next subsequent time interval. An input pulse may be applied to the input terminal 24 during the same time interval, T3 for example, that an output pulse is produced at the output terminal 26. The flyback produced by an input pulse is used to set up the output pulse and the circuitry is such that there is complete isolation between the output and input pulse during any given time interval.

A clamp pulse (FIG. 2A) is applied to the terminal 62 to wipe out or remove the information stored in the delay circuit after that information has been utilized.

The anode of tube L is connected through inductance 64 and an anode load resistor 65, in parallel, to a +150 volt terminal 66. The inductance 64 is provided to increase the voltage swing in the positive direction at the anode of the tube L (FIG. 2A during T3 and T4) for a preselected time immediately after that tube is rendered non-conductive.

The diode rectifiers 67 and 68 connected respectively to input terminal 24 and terminal 69, and the resistor 70 connected between the juncture 71 of the diodes 67 and 68 and the +150 volt terminal 66 comprise an AND circuit generally designated as 70a. This juncture 71 is connected through a parasitic suppressor resistor ps to the control grid of the tube L.

The tube R is operated as a cathode follower and is always conductive during operation of the delay circuit. The cathode load resistor 73 is connected to a -82 volt terminal 74 which is also connected through a resistor 75 and a condenser 76 to the anode of the tube L. The terminal 62 is connected through a resistor 77 and diode rectifiers 78, 79 and 80, in series, to a -30 volt terminal 81. The juncture 82 is connected between the rectifiers 79 and 80 and between the resistor 75 and condenser 76. The juncture 83 joining rectifiers 78 and 79 is connected through a parasitic suppressor resistor ps to the control grid of the tube R and through a condenser 85 to ground.

During the time interval T1, an input pulse is not ap-