(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4148717号

(P4148717)

(45) 発行日 平成20年9月10日(2008.9.10)

(24) 登録日 平成20年7月4日(2008.7.4)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 29/78  | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/423 | (2006.01) |

| HO 1 L 29/49  | (2006.01) |

| HO 1 L        | 29/78     |

|               | 301G      |

|               | 301P      |

|               | G         |

|               | 301L      |

請求項の数 17 (全 15 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-227883 (P2002-227883)  |

| (22) 出願日     | 平成14年8月5日(2002.8.5)           |

| (65) 公開番号    | 特開2003-110104 (P2003-110104A) |

| (43) 公開日     | 平成15年4月11日(2003.4.11)         |

| 審査請求日        | 平成15年6月19日(2003.6.19)         |

| (31) 優先権主張番号 | 2001-047148                   |

| (32) 優先日     | 平成13年8月4日(2001.8.4)           |

| (33) 優先権主張国  | 韓国(KR)                        |

|           |                                                                                                                                                              |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>SAMSUNG ELECTRONICS<br>CO., LTD.<br>大韓民国京畿道水原市靈通区梅灘洞416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do 442-742<br>(KR) |

| (74) 代理人  | 100086368<br>弁理士 萩原 誠                                                                                                                                        |

| (72) 発明者  | 柳 赫 株<br>大韓民国京畿道九里市橋門2洞808番地<br>徳▲ヒュン▼アパート105棟2003<br>号                                                                                                      |

最終頁に続く

(54) 【発明の名称】半導体素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上にゲート酸化膜及び第1ゲート電極を形成する第1工程と、

前記第1工程後、前記半導体基板に不純物をイオン注入して、前記第1ゲート電極両側の前記半導体基板内にソース／ドレイン延長領域を形成する第2工程と、

前記第2工程後、前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が約30°～80°である高角ハロイオン注入法を利用して、前記ソース／ドレイン延長領域のチャネル領域側の側部に隣接するように、前記半導体基板部分にハロイオン注入領域を形成する第3工程と、

前記第3工程後、前記半導体基板上の全面に、表面の段差に沿ってシリコン窒化膜を形成し、さらにその上に平坦化用の酸化膜を形成する第4工程と、

前記第4工程後、前記半導体基板上の全面を化学機械的研磨することにより、前記第1ゲート電極の上面が露出される状態にして、全面を平坦化する第5工程と、

前記第5工程後、幅が前記第1ゲート電極の幅より大きい第2ゲート電極を前記第1ゲート電極上部に形成する第6工程と、

前記第6工程後、前記第2ゲート電極をエッティングマスクとして使用して前記平坦化用の酸化膜をエッティングすることにより、前記第1ゲート電極の側面部分に相当する前記第2ゲート電極の側端部下のみに前記平坦化用の酸化膜を残す第7工程と、

前記第7工程後、残存した前記平坦化用の酸化膜の側面と前記第2ゲート電極の側面に絶縁膜の第1スペーサを形成する第8工程と、

10

20

前記第8工程後、前記第2ゲート電極および前記第1スペーサをマスクとして前記半導体基板に不純物をイオン注入することにより、前記第1スペーサ側方の前記半導体基板部分に深いソース／ドレイン領域を形成する第9工程と、

を具備することを特徴とする半導体素子の製造方法。

【請求項2】

前記第9工程後、前記第1スペーサの側壁に絶縁膜の第2スペーサを形成する第10工程と、

前記第10工程後、前記第1スペーサ、前記第2スペーサおよび前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第2スペーサ側方の前記半導体基板部分に第2の深いソース／ドレイン領域を形成する第11工程と、

が追加されることを特徴とする請求項1に記載の半導体素子の製造方法。

10

【請求項3】

半導体基板上にゲート酸化膜及び第1ゲート電極を形成する第1工程と、

前記第1工程後、前記半導体基板に不純物をイオン注入して、前記第1ゲート電極両側の前記半導体基板内にソース／ドレイン延長領域を形成する第2工程と、

前記第2工程後、前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が約30°～80°である高角ハロイオン注入法を利用して、前記ソース／ドレイン延長領域のチャネル領域側の側部に隣接するように、前記半導体基板部分にハロイオン注入領域を形成する第3工程と、

前記第3工程後、前記半導体基板上の全面に、表面の段差に沿ってシリコン窒化膜を形成し、さらにその上に平坦化用の酸化膜を形成する第4工程と、

20

前記第4工程後、前記半導体基板上の全面を化学機械的研磨することにより、前記第1ゲート電極の上面が露出される状態にして、全面を平坦化する第5工程と、

前記第5工程後、幅が前記第1ゲート電極の幅より大きい第2ゲート電極を前記第1ゲート電極上部に形成する第6工程と、

前記第6工程後、前記第2ゲート電極をエッティングマスクとして使用して前記平坦化用の酸化膜をエッティングすることにより、前記第1ゲート電極の側面部分に相当する前記第2ゲート電極の側端部下のみに前記平坦化用の酸化膜を残す第7工程と、

前記第7工程後、前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第2ゲート電極側方の前記半導体基板部分に深いソース／ドレイン領域を形成する第8工程と、

30

前記第8工程後、前記第2ゲート電極の側面と、該第2ゲート電極の側端部下に残存した前記平坦化用の酸化膜の側面とに絶縁膜の第1スペーサを形成する第9工程と、

を具備することを特徴とする半導体素子の製造方法。

【請求項4】

前記第9工程後、前記第1スペーサおよび前記第2ゲート電極をマスクとして前記半導体基板に不純物をイオン注入することにより、前記第1スペーサ側方の前記半導体基板部分に第2の深いソース／ドレイン領域を形成する第10工程と、

前記第10工程後に、前記第1スペーサの側壁に絶縁膜の第2スペーサを形成する第11工程と、

40

が追加されることを特徴とする請求項3に記載の半導体素子の製造方法。

【請求項5】

前記ゲート酸化膜及び前記第1ゲート電極を形成する工程の前に、

前記半導体基板に素子分離領域を形成する工程と、

前記半導体基板にスレッショルド電圧調節のために不純物をイオン注入する工程とが実施されることを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項6】

前記第1ゲート電極は約500～1500の高さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項7】

50

前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項8】

前記ハロイオン注入領域形成のための不純物は前記ソース／ドレイン延長領域形成のための不純物とは反対タイプの不純物であることを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項9】

前記深いソース／ドレイン領域形成のための不純物のイオン注入ドーズ量は前記ソース／ドレイン延長領域形成のための不純物のイオン注入ドーズ量より高いことを特徴とする請求項1または3に記載の半導体素子の製造方法。

10

【請求項10】

前記ソース／ドレイン延長領域形成のためのイオン注入は約 $1\text{E}14\sim2\text{E}15\text{cm}^{-2}$ のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項11】

前記ハロイオン注入領域形成のためのイオン注入は約 $1\text{E}13\sim5\text{E}14\text{cm}^{-2}$ のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項12】

前記深いソース／ドレイン領域形成のためのイオン注入は約 $3\text{E}15\sim7\text{E}15\text{cm}^{-2}$ のドーズ量で実施することを特徴とする請求項1または3に記載の半導体素子の製造方法。

20

【請求項13】

前記第2ゲート電極は約 $300\sim1500$ の高さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項14】

前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項15】

前記シリコン窒化膜は約 $30\sim200$ の厚さに形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

30

【請求項16】

前記平坦化用の酸化膜は前記シリコン窒化膜とのエッチング選択比が大きい高温酸化膜、中温酸化膜または低温酸化膜で形成することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【請求項17】

前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極はT字状構造を有することを特徴とする請求項1または3に記載の半導体素子の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

40

本発明は半導体素子及びその製造方法に係り、より詳細には低いゲート抵抗と小さな寄生キャパシタンスを有する第1ゲート電極と第2ゲート電極よりなるT字状構造のゲート電極と、短チャンネル効果を効果的に抑制できるハロ(halo)イオン注入領域を含む半導体素子の構造と、ゲート電極間の間隔を広げなくても高角ハロイオン注入が可能な半導体素子の製造方法に関する。

【0002】

【従来の技術】

MOSトランジスタを採用した半導体素子において、ゲート電極の臨界寸法(critical dimension、CD)はMOSトランジスタの特性に多くの影響を及ぼす。半導体素子の集積度が高まるにつれてゲート電極の臨界寸法は小さくなりつつあり、こ

50

れにより短チャンネル効果が深刻な問題となっている。このようなトランジスタのスケールダウンによる短チャンネル効果を改善するために狭幅接合を形成させる方法が用いられているが、この方法はソース／ドレイン延長領域の抵抗を増加させる限界を有している。これに対する解決方法としてハロイオン注入法が提案された。しかし、ゲートの臨界寸法の縮小による短チャンネル効果を抑制するためにハロイオン注入の濃度を高め続けており、これは接合キャパシタンス及び接合漏れ電流の増加、オン電流の減少などの問題を引き起こした。この問題を解決する方法として提示されたものが高角ハロイオン注入法である。

#### 【0003】

前記高角ハロイオン注入法は、イオン注入時に高角を使用してソース／ドレイン延長領域の側部に選択的に不純物を注入してハロイオン注入領域を形成させる方法であって、低濃度の不純物を使用しても短チャンネル効果を効果的に抑制できる。そして、このようにハロイオン注入領域の不純物濃度を低めれば、胴体効果（body effect、基板効果ともいう）を減らしてオン電流は増加させ、オフ電流は減少させる効果がある。また、前記高角ハロイオン注入法を使用すれば、接合キャパシタンスの減少、ゲート大きさ変化の減少効果がある。

#### 【0004】

##### 【発明が解決しようとする課題】

しかし、半導体素子の集積度の上昇によるゲート電極間間隔の限界のために一定角度以上のハロイオン注入が不可能で高角ハロイオン注入法の長所を利用できない。すなわち、前述したように高性能トランジスタを作るためには高角ハロイオン注入法の適用が必須であるが、隣接したゲート電極によりイオン注入遮断効果が発生して高角のハロイオン注入を実施できない。これを解決するためにはゲート電極間の間隔を広げるか、あるいはゲート電極の高さを十分に低める必要がある。しかし、ゲート電極間の間隔を広げるほどチップサイズが大きくなつて高集積化に逆行する結果をもたらす。また、ゲート電極の高さを低めることによって抵抗減少のために必須なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的工程に対する十分なゲート電極の高さを確保できなくなる。

#### 【0005】

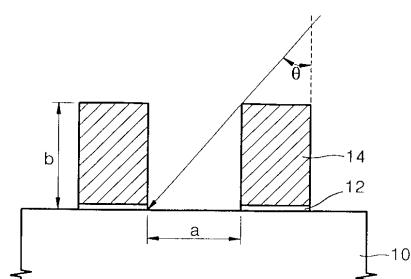

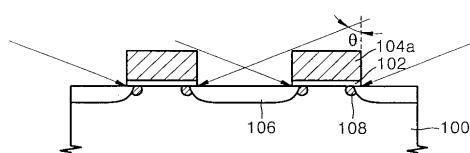

図1は、ゲート電極の高さとゲート電極の間隔がハロイオン注入角度に及ぼす影響を説明するために示した断面図である。

図1を参照すれば、ゲート電極14間の間隔をa、ゲート電極14の高さをb、半導体基板10に垂直の方向と不純物イオンの入射方向とがなす角をθとする時、θが大きい高角ハロイオン注入法を適用するためには十分なa/b比を有する必要がある。このためにはゲート電極14間の間隔aを十分に広げるか、あるいはゲート電極14の高さbを十分に低める必要がある。しかし、ゲート電極14の高さbを十分に低めれば、抵抗減少のために必須なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜12や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的研磨工程に対する十分なゲート電極の高さを確保できなくなる。一方、ゲート電極14間の間隔aを十分に大きくする場合は、デザインルール上の損失をもたらしてチップサイズが大きくなる。これは半導体工程において高集積化という目標に逆行する結果となる。

#### 【0006】

本発明は、低いゲート抵抗と、小さい寄生キャパシタンスを有するT字状構造のゲート電極と、短チャンネル効果を効果的に抑制できるハロイオン注入領域を含む半導体素子の構造を提供することを目的とする。

本発明は、ゲート電極間の間隔を広げなくても高角ハロイオン注入が可能な半導体素子の製造方法を提供することを他の目的とする。

#### 【0007】

10

20

30

40

50

## 【課題を解決するための手段】

本発明は、半導体基板内に形成された第1イオン注入領域と、この第1イオン注入領域の両側に形成された第2イオン注入領域と、この第2イオン注入領域に接して前記第1イオン注入領域と反対側に形成されたハロイオン注入領域と、前記半導体基板上に形成されたゲート酸化膜と、このゲート酸化膜上に形成された第1ゲート電極と、前記半導体基板の表面、前記ゲート酸化膜の側縁及び前記第1ゲート電極の側壁に沿って形成されたシリコン窒化膜と、このシリコン窒化膜に接して前記第1ゲート電極と反対側に形成された酸化膜と、前記第1ゲート電極、前記シリコン窒化膜及び前記酸化膜上に形成された第2ゲート電極と、この第2ゲート電極及び前記酸化膜の側壁に形成されたスペーサとを含むことを特徴とする半導体素子とする。

10

## 【0008】

前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極は前記第2ゲート電極の幅が前記第1ゲート電極の幅より大きいT字状構造を有する。

前記第1ゲート電極の両側部分に形成された前記シリコン窒化膜はL字状または逆L字状である。

前記ゲート酸化膜は前記第2イオン注入領域間の前記半導体基板の表面に形成されている。

前記第2イオン注入領域は前記スペーサ間の間隔より広い領域にわたって前記半導体基板内に形成されている。

前記ハロイオン注入領域の不純物は前記第1及び前記第2イオン注入領域の不純物とは反対タイプの不純物である。

20

前記第1イオン注入領域の不純物濃度は前記第2イオン注入領域の不純物濃度より高い。

前記第1イオン注入領域の不純物濃度は約 $3\text{E}15\sim7\text{E}15\text{cm}^{-2}$ であり、前記第2イオン注入領域の不純物濃度は約 $1\text{E}14\sim2\text{E}15\text{cm}^{-2}$ であることが望ましい。

前記ハロイオン注入領域の不純物濃度は約 $1\text{E}13\sim5\text{E}14\text{cm}^{-2}$ であることが望ましい。

前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成されることが望ましい。

前記第1ゲート電極の高さは約 $500\sim1000$ であることが望ましい。

前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成されることが望ましい。

30

前記第2ゲート電極の高さは約 $300\sim1500$ であることが望ましい。

前記シリコン窒化膜は約 $30\sim200$ の厚さを有することが望ましい。

前記スペーサ間の前記半導体基板内に形成された第3イオン注入領域と、前記スペーサの側部に形成された第2スペーサとをさらに含む。

## 【0009】

本発明は、以下のような半導体素子の製造方法とする。まず、半導体基板上にゲート酸化膜及び第1ゲート電極を形成する。次に、前記半導体基板に不純物をイオン注入してソース／ドレイン延長領域を形成する。次に、高角ハロイオン注入法を利用して前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角が所定角度をなすように不純物をイオン注入して前記ソース／ドレイン延長領域の両側部にハロイオン注入領域を形成する。

40

次に、前記ハロイオン注入領域が形成されている前記半導体基板上にシリコン窒化膜を形成する。次に、前記シリコン窒化膜が形成されている前記半導体基板上に酸化膜を形成する。次に、前記酸化膜が形成されている前記半導体基板を化学機械的研磨して前記第1ゲート電極が露出されるように平坦化する。次に、前記第1ゲート電極上部に選択的にエピタキシャル成長法を利用して第2ゲート電極を形成する。次に、前記第2ゲート電極をエッチングマスクとして使用して前記シリコン窒化膜が露出されるように前記酸化膜をエッチバックする。次に、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングしてスペーサを形成する。次に、前記半導体基板に不純物をイオン注入して深いソース／ドレイン領域を形成する。

50

## 【0010】

前記スペーサを形成する段階は前記酸化膜をエッチバックする段階後、前記深いソース／ドレイン領域を形成する段階前に行う。さらに、前記深いソース／ドレイン領域を形成する段階後に、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングして第2スペーサを形成する段階と、前記半導体基板に不純物をイオン注入して第2の深いソース／ドレイン領域を形成する段階とをさらに含む。前記スペーサを形成する段階と前記不純物をイオン注入する段階とを2回以上反復実施する。

## 【0011】

また、前記深いソース／ドレイン領域を形成する段階は前記酸化膜をエッチバックする段階後、前記スペーサを形成する段階前に行う。さらに、前記スペーサを形成する段階後に、前記半導体基板に不純物をイオン注入して第2の深いソース／ドレイン領域を形成する段階と、前記半導体基板上にスペーサ形成用絶縁膜を蒸着し、異方性乾式エッチングして第2スペーサを形成する段階とをさらに含む。前記不純物をイオン注入する段階と前記スペーサをイオン注入する段階とを2回以上反復実施する。

10

## 【0012】

前記ゲート酸化膜及び前記第1ゲート電極を形成する段階前に、前記半導体基板に素子分離領域を形成する段階と、前記半導体基板にスレッショルド電圧調節のために不純物をイオン注入する段階とをさらに含む。

## 【0013】

前記半導体基板に垂直な方向と不純物イオンの入射方向とがなす角は約30°～80°であることが望ましい。

20

前記半導体基板に垂直な方向と前記不純物イオンの入射方向とがなす最大角が約30°～80°になるように前記第1ゲート電極の高さを調節する。

前記第1ゲート電極は約500～1500の高さに形成することが望ましい。

前記第1ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することが望ましい。

前記ハロイオン注入領域形成のための不純物は前記ソース／ドレイン延長領域形成のための不純物とは反対タイプの不純物である。

前記深いソース／ドレイン領域形成のための不純物のイオン注入濃度は前記ソース／ドレイン延長領域形成のための不純物のイオン注入濃度より高い。

30

前記ソース／ドレイン延長領域形成のためのイオン注入は約1E14～2E15cm⁻²の濃度で実施することが望ましい。

前記ハロイオン注入領域形成のためのイオン注入は約1E13～5E14cm⁻²の濃度で実施することが望ましい。

前記深いソース／ドレイン領域形成のためのイオン注入は約3E15～7E15cm⁻²の濃度で実施することが望ましい。

前記第2ゲート電極は約300～1500の高さに形成することが望ましい。

前記第2ゲート電極は多結晶シリコン膜またはシリコンゲルマニウム膜で形成することが望ましい。

前記シリコン窒化膜は約30～200の厚さに形成することが望ましい。

40

前記酸化膜は前記シリコン窒化膜とのエッチング選択比が大きい高温酸化膜(High Temperature Oxide; HTO)、中温酸化膜(Middle Temperature Oxide; MTO)または低温酸化膜(Low Temperature Oxide; LTO)で形成することが望ましい。

前記第2ゲート電極の幅を前記第1ゲート電極の幅より大きく形成して前記第1ゲート電極及び前記第2ゲート電極よりなるゲート電極はT字状構造を有する。

## 【0014】

## 【発明の実施の形態】

以下、添付した図面を参照して本発明による望ましい実施形態を詳細に説明する。しかし、以下の実施形態は当業者が本発明を十分に理解できるように提供されるものであって、

50

色々な他の形態に変形でき、本発明の範囲が以下の実施形態に限定されるものではない。以下の説明である層が他の層上に存在すると記述される時、これは他の層の真上に存在することもあり、その間に第3の層が介在されることもある。また図面で各層の厚さや大きさは説明の便宜及び明確性のために誇張された。図面上で同一符号は同じ要素を示す。

【0015】

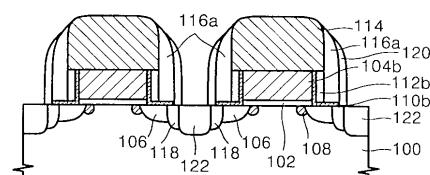

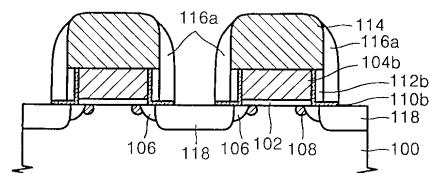

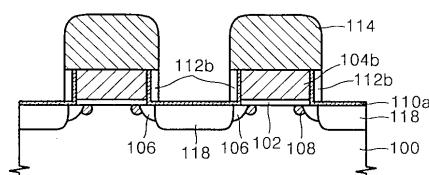

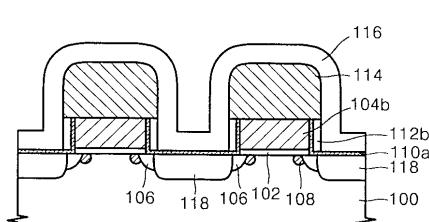

図12及び図16は、本発明の望ましい実施形態による半導体素子の構造を示した断面図である。

図12及び図16を参照すれば、半導体基板100内に第1イオン注入領域118、すなわち、深いソース／ドレイン領域118が形成されている。この第1イオン注入領域118は後述するスペーサ116a間の間隔より広い領域にわたって半導体基板100内に形成されている。第1イオン注入領域118の両側部には第2イオン注入領域106、すなわち、ソース／ドレイン延長領域106が形成されている。この第2イオン注入領域106の不純物濃度は第1イオン注入領域118の不純物濃度よりは低いことが望ましい。望ましくは、第1イオン注入領域118の不純物濃度は約 $3 \times 10^{-15} \sim 7 \times 10^{-15} \text{ cm}^{-2}$ であり、第2イオン注入領域106の不純物濃度は約 $1 \times 10^{-14} \sim 2 \times 10^{-15} \text{ cm}^{-2}$ であることが望ましい。また、ハロイオン注入領域108が第2イオン注入領域106に接して第1イオン注入領域118と反対側に形成されている。このハロイオン注入領域108に注入された不純物は第1及び第2イオン注入領域118, 106に注入された不純物とは反対タイプである。例えば、第1及び第2イオン注入領域118, 106に注入された不純物がホウ素及び／またはインジウムのようなP型不純物である場合、ハロイオン注入領域108に注入された不純物は砒素及び／または燐のようなN型不純物である。反対に、第1及び第2イオン注入領域118, 106に注入された不純物が砒素及び／または燐のようなN型不純物である場合、ハロイオン注入領域108に注入された不純物はホウ素及び／またはインジウムのようなP型不純物である。ハロイオン注入領域108は低濃度の不純物を有することが望ましい。望ましくは、ハロイオン注入領域108の不純物濃度は約 $1 \times 10^{-13} \sim 5 \times 10^{-14} \text{ cm}^{-2}$ であることが望ましい。このようにハロイオン注入領域108をソース／ドレイン延長領域106の側部に形成させれば、低い不純物濃度でも短チャンネル効果を効果的に抑制でき、また胴体効果(body effect)を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。

【0016】

一方、半導体基板100上にはゲート酸化膜102が形成されている。すなわち、ソース／ドレイン延長領域106間の半導体基板100の表面にゲート酸化膜102が形成されている。このゲート酸化膜102上には第1ゲート電極104bが形成されている。この第1ゲート電極104bは多結晶シリコン膜またはシリコングルマニウム膜よりなることが望ましい。また、第1ゲート電極104bは約500～1000の厚さを有することが望ましい。半導体基板100の表面、ゲート酸化膜102の側縁及び第1ゲート電極104bの側壁に沿ってシリコン窒化膜110bが形成されている。第1ゲート電極104bの両側部分に形成されたシリコン窒化膜110bはL字状または逆L字状である。このシリコン窒化膜110bは30～200程度の厚さを有することが望ましい。また、このシリコン窒化膜110bに接して第1ゲート電極104bと反対側に酸化膜112bが形成されている。この酸化膜112bはHTO、MTOまたはLTOで形成できる。第1ゲート電極104b、シリコン窒化膜110b及び酸化膜112b上には第2ゲート電極114が形成されている。この第2ゲート電極114は多結晶シリコン膜またはシリコングルマニウム膜よりなることが望ましい。また、第2ゲート電極114は300～1500程度の厚さを有することが望ましい。このような第2ゲート電極114及び酸化膜112bの側壁にはスペーサ116aが形成されている。すなわち、スペーサ116aは第2ゲート電極114及び酸化膜112bと接して、半導体基板表面に沿って位置するシリコン窒化膜110bの上に位置する。スペーサ116aはシリコン窒化膜、HTO、MTOまたはLTOで形成できる。

【0017】

10

20

30

40

50

本実施形態による半導体素子によれば、ゲート電極 114, 104b は第1ゲート電極 104b 及び第2ゲート電極 114 によりなる T 字状構造を有する。このような T 字状ゲート構造の場合、ゲート下部（第1ゲート電極 104b）の幅は小さくしてもゲート上部（第2ゲート電極 114）の幅は大きくしてシリサイドを広く形成することによって抵抗を低められる。また、ゲートキャパシタンスを小さくすることができ、ゲートとソース／ドレイン延長領域間のオーバラップキャパシタンスも減らしうる。

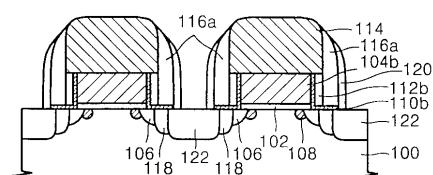

#### 【0018】

図 13 及び図 17 は、図 12 及び図 16 に示した半導体素子の構造に第3イオン注入領域 122 及び第2スペーサ 120 をさらに形成した構造を示した断面図である。

図 13 及び図 17 を参照すれば、半導体基板 100 内に第3イオン注入領域 122、すなわち、第2の深いソース／ドレイン領域 122 が形成されている。この第3イオン注入領域 122 は後述する第2スペーサ 120 間の間隔より広い領域にわたって半導体基板 100 内に形成される。この第3イオン注入領域 122 の両側部には第1イオン注入領域 118 が形成されている。この第1イオン注入領域 118 の不純物濃度は第3イオン注入領域 122 の不純物濃度より低いことが望ましい。また、第2イオン注入領域 106 が第1イオン注入領域 118 に接して第3イオン注入領域 122 と反対側に形成されている。この第2イオン注入領域 106 の不純物濃度は第1イオン注入領域 118 の不純物濃度より低いことが望ましい。また、ハロイオン注入領域 108 が第2イオン注入領域 106 に接して第1イオン注入領域 118 と反対側に形成されている。このハロイオン注入領域 108 に注入された不純物は第1、第2及び第3イオン注入領域 118, 106, 122 に注入された不純物とは反対タイプである。例えば、第1、第2及び第3イオン注入領域 118, 106, 122 に注入された不純物がホウ素及び／またはインジウムのような P 型不純物である場合、ハロイオン注入領域 108 に注入された不純物は砒素及び／または燐のような N 型不純物である。反対に、第1、第2及び第3イオン注入領域 118, 106, 122 に注入された不純物が砒素及び／または燐のような N 型不純物である場合、ハロイオン注入領域 108 に注入された不純物はホウ素及び／またはインジウムのような P 型不純物である。このようにハロイオン注入領域 108 をソース／ドレイン延長領域 106 の側部に形成させれば、低い不純物濃度でも短チャンネル効果を効果的に抑制でき、また胴体効果を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。一方、半導体基板 100 の上部のゲート構造はゲート側壁に第2スペーサ 120 をさらに形成したことを除いては図 13 及び図 16 に示した T 字状ゲート構造と同一である。

#### 【0019】

以下、本発明の望ましい実施形態による半導体素子の製造方法を説明する。

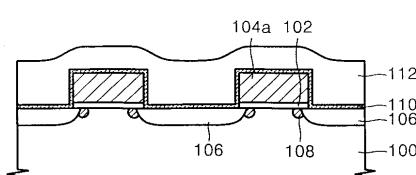

図 2 ないし図 13 は、本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

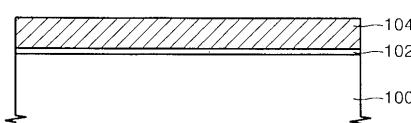

図 2 を参照すれば、半導体基板 100 に活性領域を定義し、その活性領域を電気的に分離させるフィールド酸化膜（図示せず）を形成する。このフィールド酸化膜は通常の LOCOS 工程または浅いトレンチ素子分離工程で形成できる。次いで、半導体基板 100 にスレッショルド電圧を調節するためにイオン注入を実施する。

#### 【0020】

次に、半導体基板 100 上にゲート酸化膜 102 を形成する。次いで、ゲート酸化膜 102 上に第1ゲート物質 104 を蒸着する。この第1ゲート物質 104 は多結晶シリコンまたはシリコンゲルマニウムであることが望ましい。一方、この第1ゲート物質 104 の蒸着を厚くした場合は、後続のハロイオン注入工程で高角のイオン注入を実施できない。また、第1ゲート物質 104 の蒸着を薄くした場合は、抵抗減少のために必要なシリサイド形成時にゲート高さのマージンが不十分になってゲート上部のシリサイドがゲート酸化膜 102 や活性領域にアタックを与える可能性が大きくなり、後続の化学機械的研磨工程に対する十分な厚さを確保できなくなる。したがって、第1ゲート物質 104 はこのような事項を考慮して適切にその蒸着の厚さを決定する必要がある。望ましくは、約 500 ~

10

20

30

40

50

1500 の厚さに第1ゲート物質104を蒸着する。

【0021】

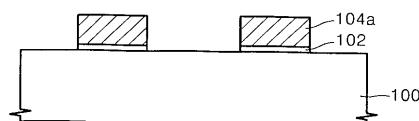

図3を参照すれば、第1ゲート物質104及びゲート酸化膜102をパターニングする。このパターニングは通常の写真工程及びエッチング工程を利用し、このパターニングにより第1ゲート電極104aが形成される。

【0022】

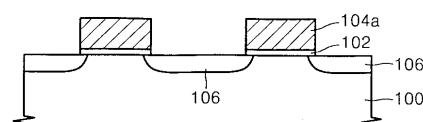

図4を参照すれば、第1ゲート電極104aが形成されている半導体基板100に不純物をイオン注入してソース／ドレイン延長領域106を形成する。このソース／ドレイン延長領域106は半導体基板100のドーピングタイプと反対タイプの不純物をイオン注入する。例えば、半導体基板100がN型不純物でドーピングされている場合、ソース／ドレイン延長領域106はホウ素、フルオロ化ホウ素( $BF_2$ )のようなP型不純物でイオン注入する。反対に、半導体基板100がP型不純物でドーピングされている場合、ソース／ドレイン延長領域106は砒素、燐のようなN型不純物でイオン注入する。ソース／ドレイン延長領域106の不純物濃度は約 $1E14 \sim 2E15 \text{ cm}^{-2}$ であることが望ましい。

10

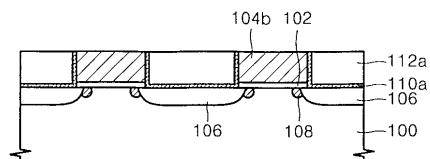

【0023】

図5を参照すれば、ソース／ドレイン延長領域106が形成されている半導体基板100に高角ハロイオン注入法を利用してハロイオン注入領域108を形成する。このハロイオン注入領域108はソース／ドレイン延長領域106の側部に形成される。このようにソース／ドレイン延長領域106の側部にハロイオン注入領域108を形成すれば、短チャンネル効果を効果的に抑制でき、胴体効果を減少させてオン電流は増加させ、オフ電流は減少させる効果を得られる。また、接合キャパシタンスの減少及びゲート長さ変化の減少効果を得られる。前記高角ハロイオン注入は半導体基板100に垂直の方向と不純物イオンの入射方向とがなす角が約 $30^\circ \sim 80^\circ$ になるように実施することが望ましい。半導体基板100に垂直の方向と不純物イオンの入射方向とがなす角が大きい高角を使用してソース／ドレイン延長領域106の側部にハロイオン注入領域108を形成すれば、低い不純物濃度を使用しても短チャンネル効果を効果的に抑制できる。一方、ハロイオン注入領域108はソース／ドレイン延長領域106のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、ソース／ドレイン延長領域106がN型不純物でドーピングされている場合、ハロイオン注入領域108はホウ素、インジウムのようなP型不純物でイオン注入する。反対に、ソース／ドレイン延長領域106がP型不純物でドーピングされている場合、ハロイオン注入領域108は砒素、燐のようなN型不純物でイオン注入する。ハロイオン注入領域108は低濃度の不純物でイオン注入されることが望ましい。ハロイオン注入領域108の不純物濃度が高すぎる場合、接合キャパシタンス及び接合漏れ電流の増加、オン電流の減少などの問題を引き起こすことがある。望ましくは、ハロイオン注入領域108の不純物濃度は約 $1E13 \sim 5E14 \text{ cm}^{-2}$ であることが望ましい。

20

【0024】

図6を参照すれば、ハロイオン注入領域108が形成されている半導体基板100上に段差に沿ってシリコン窒化膜110を形成する。このシリコン窒化膜110は約 $30 \sim 200$ の厚さに形成することが望ましい。

30

次いで、シリコン窒化膜110上にシリコン窒化膜110とエッチング選択比が大きい酸化膜112を形成する。この酸化膜112はシリコン窒化膜100とのエッチング選択比が大きいHTO、MTOまたはLTOで形成できる。この酸化膜112は約 $500 \sim 2500$ の厚さに形成することが望ましい。

40

【0025】

図7を参照すれば、酸化膜112が形成されている半導体基板100を第1ゲート電極104aの上部が露出されるように化学機械的研磨して平坦化する。この化学機械的研磨により第1ゲート電極104aを所定厚さだけリセスさせる。リセスされた後の第1ゲート電極104bの高さは約 $500 \sim 1000$ にすることが望ましい。なお、化学機械的

50

研磨後の残存酸化膜 112 は符号 112a で、残存シリコン窒化膜 110 は符号 110a でそれぞれ示す。

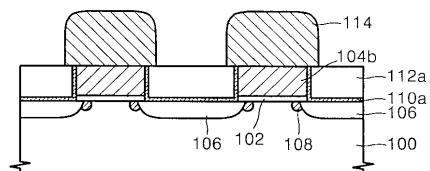

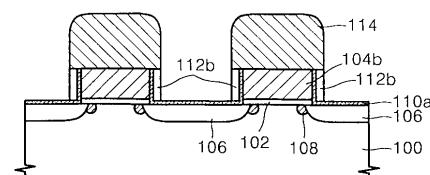

【0026】

図 8 を参照すれば、第 1 ゲート電極 104b の上部に選択的にエピタキシャル成長法を利用して第 2 ゲート物質を成長させて第 2 ゲート電極 114 を形成する。このときの前記第 2 ゲート物質は多結晶シリコンまたはシリコンゲルマニウムであることが望ましい。また、前記第 2 ゲート物質は約 300 ~ 1500 の厚さに成長させることが望ましい。このようにして第 1 ゲート電極 104b の上部に第 2 ゲート電極 114 を形成することによって本発明のゲート電極は第 2 ゲート電極 114 と第 1 ゲート電極 104b とよりなる T 字状ゲート電極構造を有する。

10

【0027】

図 9 を参照すれば、酸化膜 112a を第 2 ゲート電極 114 をエッチングマスクとして使用してエッチバックする。すなわち、第 2 ゲート電極 114 が形成された半導体基板 100 をフォトマスク層を形成せずに全面乾式エッチングする。このエッチバックにより酸化膜 112a は第 2 ゲート電極 114 の下部にのみシリコン窒化膜 110a と接しつつ酸化膜 112b として残ることになる。この時、酸化膜 112a に対してエッチング選択比を有するシリコン窒化膜 110a は前記エッチングに対するエッチング停止層の役割をする。

【0028】

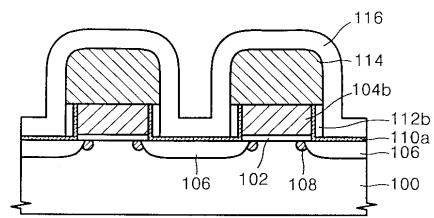

図 10 を参照すれば、半導体基板 100 上にスペーサ形成用絶縁膜 116 を形成する。このスペーサ形成用絶縁膜 116 はHTO、MTO、LTO のような酸化膜またはシリコン窒化膜で形成できる。また、このスペーサ形成用絶縁膜 116 は約 300 ~ 2500 の厚さに形成することが望ましい。

20

【0029】

図 11 を参照すれば、スペーサ形成用絶縁膜 116 を異方性乾式エッチングしてスペーサ 116a を形成する。この時、スペーサ形成用絶縁膜 116 の下部に形成されたシリコン窒化膜 110a もエッチングして所定領域の半導体基板 100 を露出させる。このエッチング後もゲート部に残ったシリコン窒化膜 110a を符号 110b で示す。

【0030】

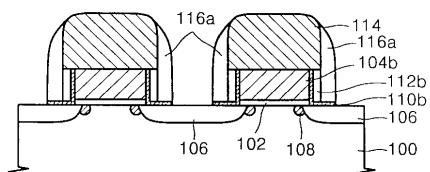

図 12 を参照すれば、スペーサ 116a が形成されている半導体基板 100 に不純物をイオン注入して深いソース / ドレイン領域 118 を形成する。この深いソース / ドレイン領域 118 は半導体基板 100 のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、半導体基板 100 が N 型不純物でドーピングされている場合、深いソース / ドレイン領域 118 はホウ素、フルオロ化ホウ素のような P 型不純物でイオン注入する。反対に、半導体基板 100 が P 型不純物でドーピングされている場合、深いソース / ドレイン領域 118 は砒素、燐のような N 型不純物でイオン注入する。深いソース / ドレイン領域 118 の不純物濃度はソース / ドレイン延長領域 106 の不純物濃度より高くすることが望ましい。望ましくは、深いソース / ドレイン領域 118 が約 3E15 ~ 7E15 cm<sup>-2</sup> の不純物濃度を有するようにする。

30

【0031】

一方、図 12 ではスペーサ 116a と深いソース / ドレイン領域 118 とを一つずつのみ形成したことを示したが、図 13 に示したように第 2 スペーサ 120 と第 2 の深いソース / ドレイン領域 122 とをさらに形成できる。すなわち、半導体基板 100 上にスペーサ形成用絶縁膜を形成した後、異方性乾式エッチングして第 2 スペーサ 120 を形成し、イオン注入を実施して第 2 の深いソース / ドレイン領域 122 を形成できる。このとき、第 2 の深いソース / ドレイン領域 122 の不純物濃度は深いソース / ドレイン領域 118 の不純物濃度より高いことが望ましい。また、前記スペーサ形成工程と深いソース / ドレイン領域形成工程を 2 回以上反復実施して、多重形態のスペーサ（図示せず）と多重の深いソース / ドレイン領域（図示せず）とを形成することもある。

40

【0032】

50

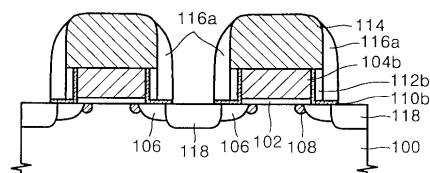

図14ないし図17は、本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

図2ないし図9に示した前記第1実施形態の各段階は本第2実施形態の各段階と同一である。したがって、前記第1実施形態で図2ないし図9を参照して詳細に説明した各工程段階は本第2実施形態では簡単に記述する。まず、半導体基板100に活性領域を定義し、その活性領域を電気的に分離させるフィールド酸化膜(図示せず)を形成する。次に、半導体基板100上にゲート酸化膜102及び第1ゲート物質104を形成した後、パターニングして第1ゲート電極104aを形成する。次いで、半導体基板100に不純物をイオン注入してソース/ドレイン延長領域106を形成する。次に、半導体基板100に高角ハロイオン注入法を利用してハロイオン注入領域108を形成する。次いで、半導体基板100上にシリコン窒化膜110及び酸化膜112を形成した後、第1ゲート電極104aの上部が露出されるように化学機械的研磨して平坦化する。次に、第1ゲート電極104bの上部に選択的にエピタキシャル成長法を利用して第2ゲート物質を成長させて第2ゲート電極114を形成する。次いで、酸化膜112aを第2ゲート電極114をエッチングマスクとして使用してエッチバックする。

#### 【0033】

図14を参照すれば、酸化膜112bがエッチバックされている半導体基板100に不純物をイオン注入して深いソース/ドレイン領域118を形成する。この深いソース/ドレイン領域118は半導体基板100のドーピングタイプと反対タイプの不純物でイオン注入する。例えば、半導体基板100がN型不純物でドーピングされている場合、深いソース/ドレイン領域118はホウ素及び/またはフルオロ化ホウ素のようなP型不純物でイオン注入する。反対に、半導体基板100がP型不純物でドーピングされている場合、深いソース/ドレイン領域118は砒素及び/または燐のようなN型不純物でイオン注入する。深いソース/ドレイン領域118の不純物濃度はソース/ドレイン延長領域106の不純物濃度よりは高くすることが望ましい。望ましくは、深いソース/ドレイン領域118が約3E15~7E15cm<sup>-2</sup>のドーピング濃度を有するようとする。

#### 【0034】

図15を参照すれば、深いソース/ドレイン領域118が形成されている半導体基板100上にスペーサ形成用絶縁膜116を形成する。このスペーサ形成用絶縁膜116はHTO、MTO、LTOのような酸化膜またはシリコン窒化膜で形成できる。また、このスペーサ形成用絶縁膜116は約300~2500の厚さに形成することが望ましい。

#### 【0035】

図16を参照すれば、スペーサ形成用絶縁膜116を異方性乾式エッチングしてスペーサ116aを形成する。この時、スペーサ形成用絶縁膜116の下部に形成されたシリコン窒化膜110aもエッチングして所定領域の半導体基板100を露出させる。このエッチング後もゲート部に残ったシリコン窒化膜110aを符号110bで示す。

#### 【0036】

図16にはスペーサ116a及び深いソース/ドレイン領域118を一つずつのみ形成したことを示したが、図17に示したように第2スペーサ120と第2の深いソース/ドレイン領域122をさらに形成できる。すなわち、半導体基板100にイオン注入を実施して第2の深いソース/ドレイン領域122を形成した後、半導体基板100上にスペーサ形成用絶縁膜を形成し、異方性乾式エッチングして第2スペーサ120を形成できる。ここで、第2の深いソース/ドレイン領域122の不純物濃度は深いソース/ドレイン領域118の不純物濃度より高いことが望ましい。また、前記深いソース/ドレイン領域形成工程と前記スペーサ形成工程を2回以上反復実施して、多重の深いソース/ドレイン領域(図示せず)と多重形態のスペーサ(図示せず)とを形成できる。

#### 【0037】

#### 【発明の効果】

以上のように、本発明による半導体素子の構造によれば、ゲート電極は第1ゲート電極及び第2ゲート電極よりなるT字状構造を有する。したがって、ゲート下部(第1ゲート電

10

20

30

40

50

極)の幅は小さくしてもゲート上部(第2ゲート電極)の幅は大きくしてシリサイドを広く形成することによって抵抗を低められる。また、ゲートキャパシタンスを小さくすることができ、ゲートとソース/ドレイン延長領域間のオーバラップキャパシタンスも減らしうる。

【0038】

一方、半導体素子の集積度が高まるにつれて、従来はゲート電極間の間隔の限界によって一定角度以上のハロイオン注入が不可能で高角イオン注入法の長所を利用できなかつたが、本発明のように従来より低い第1ゲート電極を形成した後、高角ハロイオン注入を実施して第2ゲート電極を形成することによってゲート電極間の間隔を広げずに高角ハロイオン注入を実施できる。

10

【0039】

また、本発明の半導体素子の製造方法によれば、ソース/ドレイン延長領域の側部に選択的に不純物を注入してハロイオン注入領域を形成することによって、短チャンネル効果を効果的に抑制できる。低い不純物濃度でハロイオン注入領域を形成することによって、胴体効果を減少させてオン電流は増加させ、オフ電流は減少させうる。また、接合キャパシタンスも減少させうる。

【図面の簡単な説明】

【図1】ゲート電極の高さとゲート電極の間隔がハロイオン注入角度に及ぼす影響を説明するために示した断面図である。

20

【図2】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図3】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図4】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図5】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図6】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

30

【図7】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図8】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図9】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図10】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図11】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図12】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

40

【図13】本発明の望ましい第1実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図14】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図15】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図16】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

【図17】本発明の望ましい第2実施形態による半導体素子の製造方法を説明するために示した断面図である。

50

示した断面図である。

【符号の説明】

|       |                   |    |

|-------|-------------------|----|

| 100   | 半導体基板             | 10 |

| 102   | ゲート酸化膜            |    |

| 104 b | 第1ゲート電極           |    |

| 106   | ソース / ドレイン延長領域    |    |

| 108   | ハロイオン注入領域         |    |

| 110 b | シリコン窒化膜           |    |

| 112 b | 酸化膜               |    |

| 114   | 第2ゲート電極           |    |

| 116 a | スペーサ              |    |

| 118   | 深いソース / ドレイン領域    |    |

| 120   | 第2スペーサ            |    |

| 122   | 第2の深いソース / ドレイン領域 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図16】

【図14】

【図17】

【図15】

---

フロントページの続き

(72)発明者 安 鍾 現

大韓民国京畿道水原市勸善区勸善洞1235番地 新安アパート307棟1102号

審査官 松嶋 秀忠

(56)参考文献 特開平10-275869 (JP, A)

特開平11-068088 (JP, A)

特開2003-023153 (JP, A)

特開2002-198519 (JP, A)

特開2001-044421 (JP, A)

特開2000-349281 (JP, A)

特開2000-021995 (JP, A)

特開平05-166833 (JP, A)

特開2001-024186 (JP, A)

米国特許第06239007 (US, B1)

特開平09-036358 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/78

H01L 21/336

H01L 29/423

H01L 29/49