**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

|                                              |                              |                          |

|----------------------------------------------|------------------------------|--------------------------|

| (51) Int. Cl.<br><i>H01L 21/76</i> (2006.01) | (11) 공개번호<br>10-2006-0111650 | (43) 공개일자<br>2006년10월27일 |

|----------------------------------------------|------------------------------|--------------------------|

---

|                              |                          |                                  |                               |

|------------------------------|--------------------------|----------------------------------|-------------------------------|

| (21) 출원번호<br>10-2006-7013210 | (22) 출원일자<br>2006년06월30일 | (86) 국제출원번호<br>PCT/US2004/038757 | (87) 국제공개번호<br>WO 2005/065089 |

| 번역문 제출일자<br>2006년06월30일      | 국제출원일자<br>2004년11월18일    | 국제공개일자<br>2005년07월21일            |                               |

---

|                          |             |        |

|--------------------------|-------------|--------|

| (30) 우선권주장<br>10/750,125 | 2003년12월31일 | 미국(US) |

|--------------------------|-------------|--------|

|                                                                                |

|--------------------------------------------------------------------------------|

| (71) 출원인<br>프리스캐일 세미컨덕터, 잉크.<br>미합중국 텍사스 (우편번호 78735) 오스틴 윌리암 캐논 드라이브 웨스트 6501 |

|--------------------------------------------------------------------------------|

|                                                                   |

|-------------------------------------------------------------------|

| (72) 발명자<br>키르치게스너, 제임스, 에이.<br>미국 85284 아리조나주 펠페 이스트 켄터키 레인 1929 |

|-------------------------------------------------------------------|

|                               |

|-------------------------------|

| (74) 대리인<br>주성민<br>백만기<br>이중희 |

|-------------------------------|

**심사청구 : 없음**

---

**(54) 반도체 컴포넌트 제조 방법 및 그에 의해 형성된 반도체컴포넌트**

---

**요약**

반도체 컴포넌트를 제조하는 방법은, 반도체 기판(210, 510)을 제공하는 단계와, 반도체 기판 내에 트렌치(130, 430)를 형성하여, 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 정의하는 단계와, 반도체 기판 내에서 트렌치의 부분 아래에, 트렌치와 적어도 부분적으로 인접하는 매립층을 형성하는 단계와, 매립층 형성 단계 후, 트렌치 내에 전기 절연재(133, 810)를 증착하는 단계와, 복수의 액티브 영역 중 하나의 액티브 영역 내에 컬렉터 영역(150, 950) – 컬렉터 영역은 매립층에 대한 컨택트를 형성함 – 을 형성하는 단계와, 복수의 액티브 영역 중 하나의 액티브 영역 위에 베이스 구조를 형성하는 단계와, 복수의 액티브 영역 중 하나의 액티브 영역 위에 에미터 영역을 형성하는 단계를 포함한다.

**대표도**

도 2

**색인어**

반도체, 액티브 영역, 트렌치, 매립층, 에미터, 컬렉터, 컨택트

**명세서**

## 기술분야

본 발명은 전반적으로 반도체 컴포넌트(semiconductor components)에 관한 것으로, 특히 반도체 컴포넌트 내의 매립층(buried layers)에 관한 것이다.

## 배경기술

기생 외인성 컬렉터 저항(parasitic extrinsic collector resistance:  $R_{cx}$ )는 실리콘 게르마늄 헤테로 접합 바이폴라 트랜지스터(Silicon-Germanium Heterojunction Bipolar Transistors: SiGe HBTs) 또는 다른 디바이스와 같은 고성능 바이폴라 또는 바이폴라 및 상보형 금속 산화물 반도체(Bipolar Complementary Metal Oxide Semiconductor: BiCMOS) 디바이스들의 성능을 매우 제한한다. SiGe HBT 또는 다른 디바이스에서의  $R_{cx}$ 를 제한하기 위한 시도에 있어서, 통상적으로 에피택셜 실리콘층(epitaxial silicon layer)과 접합된 고농도 도핑 N형(N+) 매립층을 사용하여, SiGe HBT 또는 다른 디바이스의 표면 아래에 매우 낮은 저항 영역을 형성함으로써,  $R_{cx}$ 의 측면 성분(lateral component)을 줄였다. 이 통상의 매립층/에피택셜층법은, 본 명세서에 참조로 통합되는 미국특허 제5,061,646호에 보다 상세히 기술되어 있다.

전형적으로, N+ 매립층의 깊이 및 두께로 인해, SiGe HBT 또는 다른 디바이스의 기생 컬렉터 기관 용량성을 허용가능한 레벨에 제한하기 위해서는 깊은 트렌치 격리 구조(deep trench isolation structures)를 SiGe HBT 또는 다른 디바이스에 부가하는 것이 요구된다. 그러므로,  $R_{cx}$ 를 제한하기 위해 사용되는 통상의 매립층법은 SiGe HBT 또는 다른 디바이스의 전체 제조 공정에 상당한 복잡성 및 비용을 부가할 수 있다. 따라서, 통상의 매립층에서 요구되는 비용 및 복잡성을 요하지 않고도, SiGe HBT 또는 다른 디바이스에서  $R_{cx}$ 를 제한하는 방법에 대한 필요성이 존재한다.

## 도면의 간단한 설명

도 1은 본 발명의 실시예에 따른 반도체 컴포넌트의 평면도이다.

도 2는 도 1의 절단선 2-2 라인을 따른 반도체 컴포넌트의 부분 단면도이다.

도 3은 본 발명의 실시예에 따른 반도체 컴포넌트를 제조하는 방법을 나타내는 플로우 차트이다.

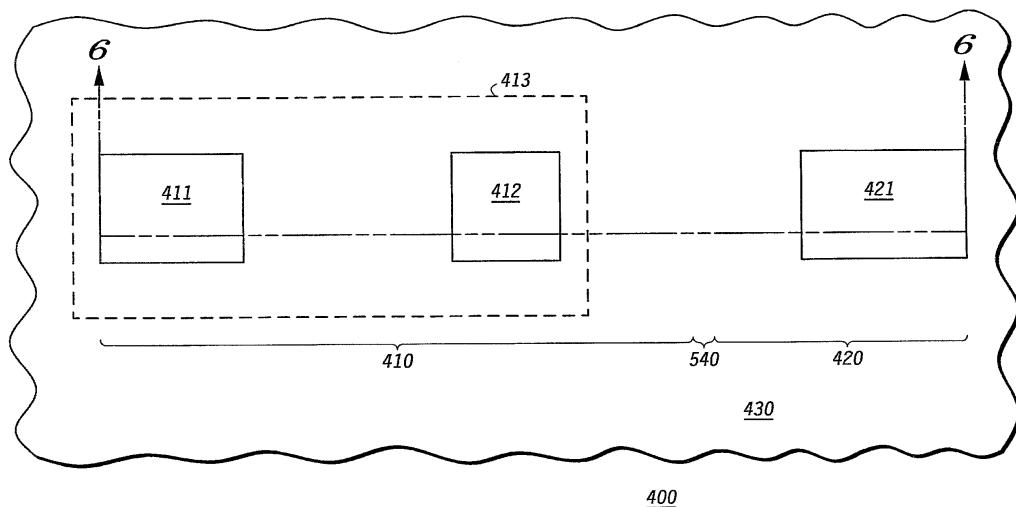

도 4는 본 발명의 실시예에 따른 다른 반도체 컴포넌트의 부분 평면도이다.

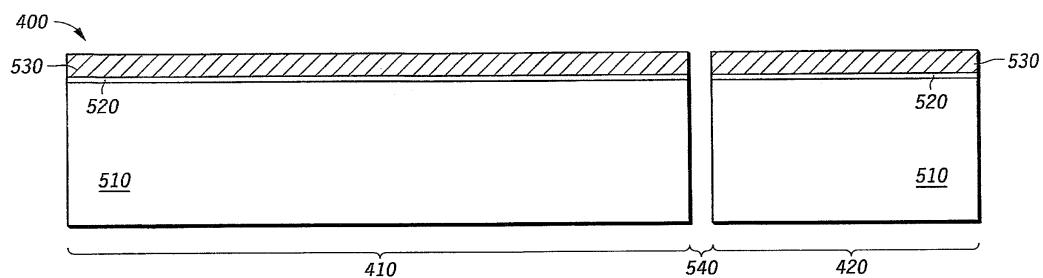

도 5는 본 발명의 실시예에 따른 제조 공정의 특정 단계에서의 도 4의 반도체 컴포넌트의 부분 단면도이다.

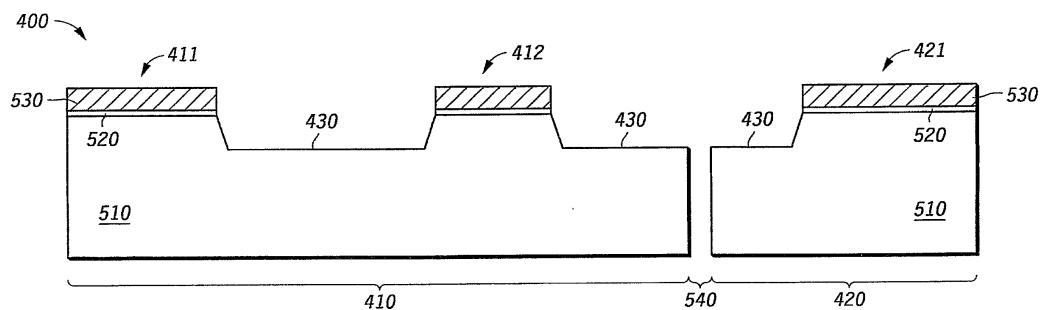

도 6은 본 발명의 실시예에 따른 제조 공정의 이후 단계에서의 도 4의 절단선 6-6에 따른 반도체 컴포넌트의 부분 단면도이다.

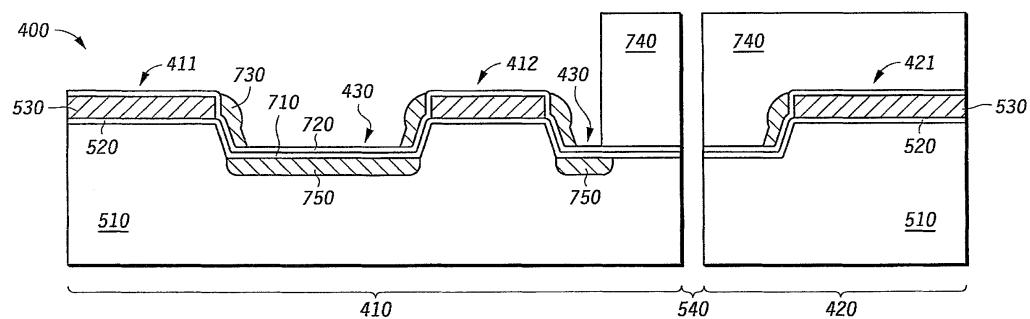

도 7은 본 발명의 실시예에 따른 제조 공정의 이후 단계에서의 도 6의 반도체 컴포넌트의 부분 단면도이다.

도 8은 본 발명의 실시예에 따른 제조 공정의 후속 단계에서 도 6의 반도체 컴포넌트의 부분 단면도이다.

도 9는 본 발명의 실시예에 따른 제조 공정의 추가 단계에서의 도 6의 반도체 컴포넌트의 부분 단면도이다.

## 발명의 상세한 설명

본 발명은 첨부된 도면과 함께 후속하는 상세한 설명을 읽으면 더 잘 이해될 것이다.

본 발명을 불필요하게 불명료하게 하는 것을 피하고, 설명의 용이성과 명료성을 위해, 도면에서 일반적 방식의 구조와, 공지된 특징 및 기술의 설명 및 세부를 생략하도록 한다. 또한, 도면의 엘리먼트는 반드시 실제 치수로 도시되어 있는 것은 아니다. 예를 들어, 도면에서 일부 엘리먼트의 치수는 본 발명의 실시예에 대한 이해를 돋기 위해 다른 엘리먼트에 비해 과장되게 나타날 수 있다. 또한, 다른 도면 내의 동일한 참조 번호는 동일한 엘리먼트를 나타낸다.

또한, 상세한 설명 및 청구범위에서 "제1", "제2", "제3", "제4" 등과 같은 용어가 만약 있다면, 이는, 유사한 엘리먼트를 구분하기 위해 사용되는 것으로서, 특정 순차 또는 연대기적 순서를 나타내는 것은 아니다. 이와 같이 사용되는 용어들은, 본 명세서 내에서 기술되는 본 발명의 실시예가 가령, 본 명세서 내에서 도시되는 것 또는 기술되는 것 이외의 순서로 동작 가능하도록, 적절한 환경 하에서 상호교환될 수 있다는 것이 이해되어야 한다. 또한, "포함한다.", "구비한다", "가진다", 및 그 유사 용어들은, 엘리먼트의 리스트를 포함하는 공정, 방법, 물품 또는 장치가 이들 엘리먼트에 한정되는 것이 아니라, 그러한 공정, 방법, 물품 또는 장치에 특별히 열거되거나 명백하지 않은 다른 엘리먼트도 포함하는 비배타적인(non-exclusive) 포함을 의미하는 것으로 사용된다.

또한, 상세한 설명 및 청구범위 내에 "좌", "우", "전", "후", "상부", "하부", "위", "아래" 등과 같은 용어들이 있다면, 이는 설명을 위해 사용되는 것이지, 영구적인 상대적 위치를 의미하는 것은 아니다. 이와 같이 사용되는 용어들은, 본 명세서 내에서 기술되는 본 발명의 실시예가 가령, 본 명세서 내에서 도시되는 것 또는 기술되는 것 이외의 순서로 동작 가능하도록, 적절한 환경 하에서 상호교환될 수 있다는 것이 이해되어야 한다. 여기서 사용되는 "결합된다"라는 용어의 의미는, 전기적 또는 비전기적 방식에 의해 직접적으로 또는 간접적으로 연결된다는 의미이다.

본 발명의 일 실시예에서, 반도체 컴포넌트의 제조 방법은, 표면 및 제1 전도형을 갖는 반도체 기판을 제공하는 단계와, 반도체 표면 내에 트렌치를 형성하여 트렌치에 의해 서로 분리되는 복수의 액티브 영역(active areas)을 정의하는 단계와, 반도체 기판 내에서 트렌치의 부분 아래에 매립층 – 매립층은 제2 전도형을 가지며 적어도 부분적으로 트렌치와 인접함 – 을 형성하는 단계와, 매립층 형성 단계 후, 트렌치 내에 전기적 절연재를 증착하는 단계와, 제2 전도형을 가지는 컬렉터 영역 – 컬렉터 영역은 매립층에 대한 컨택트를 형성함 – 을 복수의 액티브 영역 중 하나의 액티브 영역 내에 형성하는 단계와, 복수의 액티브 영역 중 하나의 액티브 영역 위에 제1 전도형을 가지는 베이스 구조를 형성하는 단계와, 복수의 액티브 영역 중 하나의 영역 위에 제2 전도형을 가지는 에미터 영역을 형성하는 단계를 포함한다.

본 발명의 다른 실시예에서, 반도체 컴포넌트 제조 방법은, 표면 및 제1 전도형을 가지는 반도체 기판 – 반도체 기판은 복수의 바이폴라 반도체 영역 및 복수의 CMOS 영역을 포함함 – 을 제공하는 단계와, 반도체 기판의 표면 내에서 복수의 바이폴라 반도체 영역 및 복수의 CMOS 영역 내에 트렌치를 형성하여, 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 정의하는 단계와, 반도체 기판 내에서 복수의 바이폴라 반도체 영역 내의 트렌치의 부분 아래에 매립층 – 매립층은 제2 전도형을 가지고 적어도 부분적으로 트렌치와 인접함 – 을 형성하는 단계와, 매립층 형성 단계 후, 전기적 절연재를 트렌치 내에 증착하는 단계와, 복수의 바이폴라 반도체 영역의 각 반도체 영역 내에 제2 전도형을 가지는 컬렉터 영역 – 컬렉터 영역은 매립층에 대한 컨택트를 형성함 – 을 형성하는 단계와, 복수의 바이폴라 반도체 영역의 각 반도체 영역 위에 제1 전도형을 가지는 베이스 구조를 형성하는 단계와, 복수의 바이폴라 반도체 영역의 각 반도체 영역 위에 소스/드레인 영역을 형성하는 단계와, 복수의 CMOS 영역의 각 CMOS 영역 위에 게이트 영역을 형성하는 단계를 포함한다.

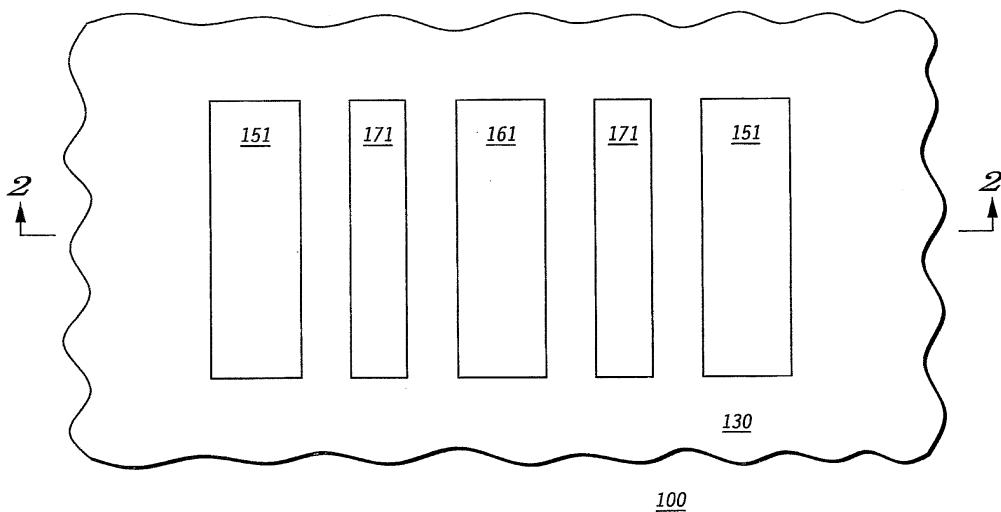

도 1은 본 발명의 일 실시예에 따른 반도체 컴포넌트(100)의 부분 평면도이다. 도 2는 도 1의 절단선 2-2에 따른 도 1의 반도체 컴포넌트(100)의 부분 단면도이다.

이제, 도 1 및 도 2를 참조하면, 반도체 컴포넌트(100)는, 표면(111)을 갖는 반도체 기판(210), 반도체 기판(210) 내의 반도체 영역(120), 반도체 기판(210)의 표면(111) 내의 트렌치(130), 트렌치(130) 아래에서 적어도 트렌치와 부분적으로 인접하는 매립층(240), 반도체 기판(210) 내의 컬렉터 영역(150), 반도체 기판(210) 위의 에미터 영역(160)을 포함한다. 반도체 영역(120), 트렌치(130), 매립층(240), 컬렉터 영역(150) 및 에미터 영역(160)은 반도체 디바이스(101)의 부분들을 형성한다. 일 실시예에서, 반도체 디바이스(101)는 바이폴라 반도체 디바이스이다. 반도체 컴포넌트(100)는, 도 1 및 도 2에 도시되지는 않았지만, CMOS 디바이스를 포함하는 부가적 반도체 디바이스, 및/또는 부가적인 바이폴라 반도체 디바이스를 더 포함할 수 있다. 일 실시예에서는, 적어도 바이폴라 반도체 디바이스 및 CMOS 반도체 디바이스가 동시에 형성될 수 있다.

컬렉터 영역(150)은 컬렉터 전극(151)을 포함하고, 에미터 영역(160)은 에미터 전극(161)을 포함한다. 반도체 기판(210)은 제1 전도형을 가지고, 반도체 영역(120), 매립층(240), 컬렉터(150) 및 에미터 영역(160)은 제2 전도형을 가진다. 예를 들어, 제1 전도형이 P형 도전성이어서, 반도체 기판(210)이 P형 전도형을 가질 수 있고, 제2 전도형이 N형 도전성이어서, 반도체 영역(120), 매립층(240), 컬렉터 영역(150) 및 에미터 영역(160)이 N형 도전성을 가질 수 있다. 다른 예로서, 매립층(240)은, 트렌치(130)의 일부 아래에서 트렌치(130)의 일부와 적어도 부분적으로 인접하는 위치 때문에 명명된, 과도평 N+ 하부 격리 매립층(heavily-dopped sub-isolation buried layer)일 수 있다. 일 실시예에서, 매립층(240)은 반도체 영

역(120) 내에 포함되며, 반도체 영역(120) 아래로 연장되지 않는다. 다른 실시예에서, 매립층(240)은 그 전체가 반도체 영역(120) 내에 포함되지 않는다. 두 실시예에서, 매립층(240) 및 반도체 영역(120)은 적어도 부분적으로 오버랩(overlap)된다.

예를 들어, 컬렉터 영역(150)은 제1 저항성을 가질 수 있고, 매립층(240)은 제2 저항성을 가질 수 있다. 매립층(240)은 과도평 매립층이기 때문에, 제2 저항성은 제1 저항성보다 적을 수 있다. 트렌치(130)의 부분 아래에서 적어도 부분적으로 트렌치(130)와 인접하는 매립층(240)의 존재는 반도체 디바이스(101) 내에서  $R_{cx}$ 의 측면 성분(lateral component)(241)을 줄인다. 소정의 실시예에서, 매립층(240)은 반도체 디바이스(101) 내의  $R_{cx}$ 의 측면 성분(241)을, 대략 50 GHz 보다 높은 피크 컷오프 주파수를 갖는 반도체 디바이스에 특히 유리한 결과인, 통상의 깊은 N+ 매립층으로 달성되는 것과 필적할 만한 레벨까지 줄인다. 예를 들어, 고주파수 반도체 디바이스는 대략 300 ohms/square의 측면 컬렉터 저항과 함께 대략 50GHz의 피크 컷오프 주파수( $f_T$ )를 가지고, 대략 30 ohms/square의 컬렉터 저항성에서 100GHz를 초과하는 피크 컷오프 주파수를 가질 수 있다. 상술한 바와 같이, 매립층(240)과 같은 하부 격리 매립층은, 통상의 깊은 N+ 매립층에 비해 제조상 덜 복잡하고 그 비용이 저렴하기 때문에 바람직하다.

소정의 제조 단계가 수행된 후, 트렌치(130)는 적어도 부분적으로 전기적 절연재(133)로 충전될 수 있다. 예를 들어, 전기적 절연재(133)는 TEOS(Tetra-Ethyl-Ortho-Silicate)를 포함할 수 있다. 본 발명의 실시예에 따른 반도체 컴포넌트(100)의 제조 방법은 이하에서 기술될 것이다. 트렌치(130)는 길이(136)를 갖는 부분(135)을 포함한다. 일 실시예에서, 매립층(240)은 적어도 길이(136)만큼 연장된다. 즉, 본 실시예에서, 매립층(240)의 길이는 적어도 트렌치(130)의 부분(135)의 길이(136) 만큼 크다. 다른 실시예에서, 매립층(240)은 길이(136)의 만큼 연장되지 않는다.

반도체 기판(210)은 부분(112) 및 부분(113)을 포함한다. 컬렉터 영역(150)은 반도체 기판(210)의 부분(112) 내에 존재하고, 에미터 영역(160)은 반도체 기판(210)의 부분(113) 위에 존재한다.

반도체 디바이스(101)는 비도평된 실리콘 에피택셜층(201), 제1 전도형을 갖는 실리콘 에피택셜층(203), 제1 전도형을 갖는 SiGe 에피택셜층(202), 실리콘 에피택셜층(201) 및 반도체 기판(210) 내에 위치하고 제2 전도형을 갖는 선택적으로 주입되는 컬렉터 영역(204), 실리콘 에피택셜층(203) 내에 위치하고 제2 전도형을 갖는 에미터 확산(205), 유전층(206), 실리콘 캡 층(207), 제2 전도형을 갖는 에미터(208), 실리사이드층(209). 스페이서 구조(211), 제1 전도형을 갖는 베이스 컨택트(212), 및 제1 전도형을 갖는 외인성 베이스 영역(213)을 더 포함한다. 또한, 반도체 디바이스(101)는 제2 전도형을 갖는 소스/드레인 영역(215), 및 저항 임플란트(216)를 더 포함한다.

예를 들어, 유전층(206)은 산화물층 또는 질화물층이 될 수 있고, 또는 몇몇 다른 유전 재료 또는 유전 재료들의 조합을 포함할 수 있다. 또 다른 예로서, 산화물층은 실질적으로 산화로(oxidation furnace) 내에서 열적 성장된 또는 화학 기상 증착 프로세서에 의해 증착된 실리콘 이산화물로 이루어질 수 있다. 다른 예들로서, 산화물층은 실질적으로 화학 기상 증착 프로세서에 의해 증착된 TEOS 또는 규산염 유리로 이루어질 수 있거나, 실질적으로 화학 기상 증착 공정에 의해 증착되는 실리콘 산화성 질화물(silicon oxy-nitride)로 이루어질 수 있다. 또한, 산화물층은, 예를 들어, 하프늄 산화물과 같은 높은 유전 상수 재료를 포함한다. 질화물층은, 예를 들어, 실질적으로 화학 기상 증착 공정에 의해 증착되는 실리콘 질화물로 이루어질 수 있다. 다른 예로서, 질화물층은 실질적으로 화학 기상 증착 공정에 의해 증착되는 산화성 질화물로 이루어질 수 있다. 또 다른 예로서, 에미터(208)는 폴리실리콘, 또는 비소 또는 인으로 도평된 폴리 실리콘을 포함할 수 있고, 실리사이드 층(209)은, 예를 들어,  $\text{CoSi}_2$  또는  $\text{TiSi}_2$ 와 같은 실리사이드를 포함할 수 있고, 저항 임플란트(216)는 인 또는 비소로 도핑될 수 있다.

또 다른 예로서, 외인성 베이스 영역(213)은 실리콘 에피택셜층(201 및 203), 실리콘 게르마늄 에피택셜층(202), 및 에미터(208)의 가장자리에 자기 정렬되는 반도체 기판 내로의 주입에 의해 형성될 수 있다. 외인성 베이스 영역(213)은 베이스 컨택트(212) 및 실리콘 게르마늄 에피택셜층(202) 사이의 저항을 줄일 수 있다. 또 다른 예로서, 실리콘 게르마늄 에피택셜층(202)은 붕소 또는 다른 도편트를 더 포함할 수 있다.

반도체 컴포넌트(100)는 에미터 영역(160)의 중심을 통해 그려지는 수직 라인(299)에 대해 대칭이다. 반도체 컴포넌트(100)는 베이스 전극(171)을 갖는 베이스 영역(170), 스페이서 구조(211), 및 베이스 컨택트(212)를 더 포함한다. 반도체 컴포넌트(100)는 웰(185) 및 트렌치(190)를 더 포함한다. 트렌치(190)는 산화물 또는 다른 유전 재료로 충전된다. 일 실시예에서, 웰(185)은 제1 전도형을 가지고, 베이스 컨택트(212)는 제2 전도형을 가진다.

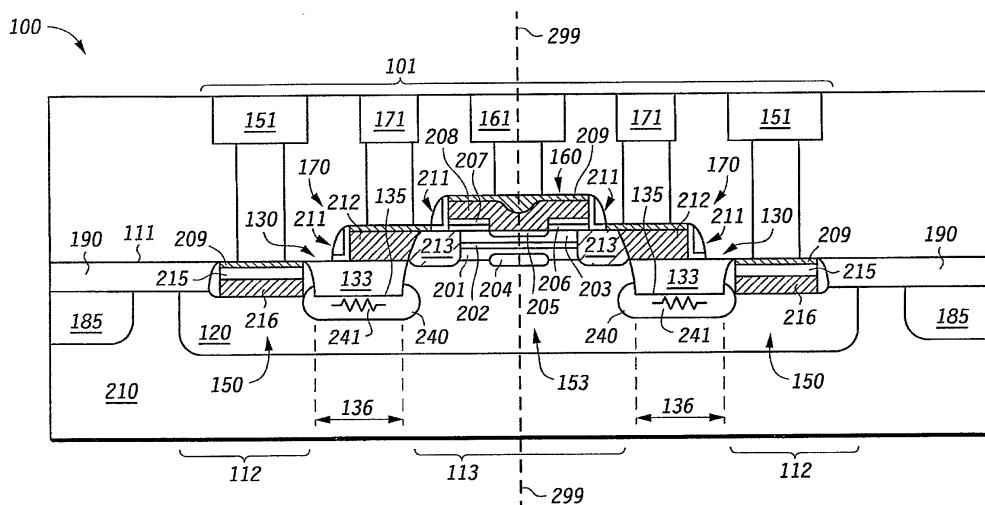

도 3은 본 발명의 실시예에 따른 반도체 캠포넌트의 제조 방법(300)을 나타내는 플로우 차트이다. 방법(300)에 있어서, 총 두께 및 도핑 농도는 공지된 파라미터 및 값에 따라 제공되므로, 여기서는 더 이상 언급하지 않기로 한다. 방법(300)의 단계 301은 표면, 제1 전도형, 제1 종의 반도체 영역, 및 제2 종의 반도체 영역을 갖는 반도체 기판을 제공한다. 예를 들어, 반도체 기판은 도 2의 반도체 기판(210)과 유사할 수 있다. 다른 예로서, 반도체 기판의 표면은 도 2의 표면(111)과 유사하다. 또 다른 예로서, 제1 종의 반도체 영역, 이하에서 도 4와 연관되어 도시되고 기술될 바이폴라 반도체 영역(410)과 유사할 수 있고, 제2 종의 반도체 영역은, 이하에서 도 4와 연관되어 도시되고 기술될 CMOS 영역(420)과 유사할 수 있다.

방법(300)의 단계 302는 반도체 기판의 표면 내에 트렌치를 형성하여, 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 정의하는 것이다. 트렌치는, 본 기술 분야에서 공지된 것과 같은, 트렌치 형성 기술에 따라 형성될 수 있다. 예를 들어, 트렌치는 도 1 및 도 2의 트렌치(130)와 유사할 수 있다. 적어도 일 실시예에서, 바이폴라 디바이스 및 CMOS 디바이스는 반도체 캠포넌트 내에 동시에 형성될 수 있다. 예를 들어, 단계 302는 반도체 캠포넌트 내에서 바이폴라 및/또는 CMOS 디바이스용 트렌치를 형성하는데에도 사용될 수도 있다.

방법(300)의 단계 303은 반도체 기판 내에서 트렌치의 부분 아래에, 제2 전도형을 갖고 적어도 부분적으로 트렌치와 인접하는 매립층을 형성하는 것이다. 예를 들어, 매립층은 도 2의 매립층(240)과 유사할 수 있다. 일 실시예에서, 단계 303은 트렌치를 통해 도편트를 주입하는 단계를 포함할 수 있다. 예를 들어, 도편트는 제2 전도형일 수 있다. 같은 또는 다른 실시예에서, 단계 303은 복수의 매립층을 형성 - 상기 복수의 매립층의 각 매립층은 단계 301과 연관되어 이미 상술된 바 있는 복수의 바이폴라 반도체 영역 중 하나의 반도체 영역 내의 트렌치의 부분 아래에 위치함 - 하는 단계를 포함할 수 있다. 단계 303은 적어도 하나의 스페이서 구조를 형성하는 단계를 더 포함할 수 있다. 예를 들어, 스페이서 구조는, 이하 도 7과 연관되어 도시되고 설명될 질화물층(730)의 부분에 의해 형성된 스페이서 구조와 유사할 수 있다. 단계 303은 CMOS 영역의 적어도 일부 위에 임플란트 마스크를 형성하는 단계, 또는 반도체 기판이 복수의 CMOS를 포함하는 경우, 하나 이상의 복수의 CMOS 영역 위에 임플란트를 형성하는 단계를 더 포함할 수 있다. 예를 들어, 임플란트 마스크는 이하 도 7의 임플란트 마스크와 유사할 수 있다. 다른 예로서, 임플란트 마스크의 위치 및 크기는, 후속 단계에서 형성되는 매립층의 파라미터를 변경하기 위해, 조정될 수 있다. 특정 예로서, 임플란트 마스크는, 단계 302에서 이미 형성된 트렌치 내의 매립층의 수평 경계를 제어하도록 배치되고 그 크기가 조정될 수 있다.

같은 또는 다른 실시예에서, 단계 303은 매립층을 트렌치에 대해 자기 정렬하는 단계를 포함할 수 있다. 여기서 사용되는 것처럼, "자기 정렬"이라는 용어는 하나 이상의 매립층의 경계를 트렌치의 가장자리에 자기 정렬시키는 것을 의미한다. 단계 303은, 도편트를 주입한 후, 트렌치를 충전하기 전에 도편트를 어닐링하는 단계를 더 포함할 수 있다. 다른 실시예에서, 도편트는 트렌치를 충전하기 전에는 어닐링되지 않고, 제조 공정 동안 수행되는 후속의 고온 처리 단계 동안 어닐링된다. 단계 303은 매립층을 형성한 후에 스페이서 구조를 제거하는 단계를 더 포함할 수 있다. 다른 실시예에서, 스페이서 구조는 제거되는 대신에 트렌치의 부분 내에 잔존할 수 있다. 같은 또는 다른 실시예에서, 스페이서 구조는 매립층이 형성된 후 트렌치 내에 형성될 수 있다.

단계 303은 본 명세서에서 매립층 모듈로서 지칭된다. 보다 구체적으로, 매립층 모듈은, 반도체 기판 내에 매립층을 형성하는 단계와, 트렌치 내에 적어도 하나의 스페이서를 선택적으로 형성하는 단계와, CMOS 영역 위에 임플란트 마스크를 형성하는 단계와, 매립층을 트렌치에 선택적으로 자기 정렬하는 단계와, 도편트 주입 후 트렌치 충전 전에 도편트를 선택적으로 어닐링하는 단계와, 매립층 형성 후에 스페이서 구조를 선택적으로 제거하는 단계를 포함할 수 있다. 매립층 모듈은 CMOS 프로세서 플로우에 적용 또는 공용될 수 있는바, 이는 매립층 모듈이, CMOS 형성 공정을 방해하거나 간섭함이 없이, CMOS 형성 공정의 일부로서 수행될 수 있다는 것을 의미한다.

방법(300)의 단계 304는 매립층을 형성한 후에 전기적 절연재를 트렌치 내에 증착하는 것이다. 예를 들어, 전기적 절연재는 도 2의 전기 절연재(133)와 유사할 수 있다. 단계 304 및 단계 302는 여기서 격리 모듈로서 참조된다. 또한, 격리 모듈은 CMOS 공정 플로우에 적용 또는 공용될 수 있는바, 이는 격리 모듈이 CMOS 형성 공정을 방해하거나 간섭함이 없이, CMOS 형성 공정의 일부로서 수행될 수 있다는 것을 의미한다.

방법(300)의 단계 305는, 제1 종의 반도체 영역 내에서 제2 전도형을 갖는 컬렉터 영역을, 매립층에 전기적으로 연결되도록 형성하는 것이다. 따라서, 컬렉터 영역은 매립층에 대한 컨택트를 형성한다. 예를 들어, 컬렉터 영역은 도 2의 컬렉터 영역(150)과 유사할 수 있다. 반도체 캠포넌트가 BiCMOS 반도체 캠포넌트를 포함하는 반도체에서, 단계 305는, 다른 바이폴라 또는 CMOS 디바이스에 대해 유사한 매립층 컨택트 영역을 적절한 곳에 동시에 형성하는데 사용될 수 있다.

방법(300)의 단계 306은 반도체 기판 위에 에피택셜 베이스 층 또는 층들을 형성하는 것이다. 예를 들어, 에피택셜층은, 반도체 커먼트가 HBT인 경우와 같이, 도 2의 실리콘 에피택셜층(201 및 203) 및 실리콘 게르마늄 에피택셜층(202)과 유사할 수 있다.

방법(300)의 단계 307은 에피택셜 베이스층 위에 유전층을 형성하는 것이다. 예를 들어, 유전층은 도 2의 유전층(206)과 유사한 구조으로 증착 및 패터닝될 수 있다.

방법(300)의 단계 308은 제1 종의 반도체 영역 위에 제2 전도형을 갖는 에미터를 형성하는 것이다. 예를 들어, 에미터는 도 2의 에미터와 유사할 수 있다. 단계 308은 폴리실리콘층을 증착 및 패터닝하는 단계를 포함한다. 반도체 커먼트가 BiCMOS 반도체 커먼트를 포함하는 곳에서, 단계 308은, 바이폴라 또는 CMOS 디바이스, 저항 등과 같은, 다른 반도체 장치 및/또는 집적 디바이스에 대해 유사 도핑된 폴리실리콘 영역을 적절한 곳에 동시에 형성하는데 사용될 수 있다. 단계 308 동안, 에미터를 형성하는데 사용된 도편트의 일부는, 단계 306에서 형성된 에피택셜층 또는 층들 및/또는 반도체 기판과 같은 반도체 커먼트의 인접 영역으로 확산할 수 있다. 도편트의 일부의 예는 도 2의 에미터 확산이다.

방법(300)의 단계 309는 제1 전도형을 갖는 베이스 구조를 제1 종의 반도체 영역 위에 형성하는 것이다. 예를 들어, 베이스 구조는 도 2의 외인성 베이스 영역(213)과 유사할 수 있다. 단계 309 또는 다른 단계는 베이스 구조를 패터닝하는 단계를 더 포함할 수 있다.

방법(300)의 단계 310은 단계 307에서 이미 형성된 유전층의 일부를 컬렉터 액티브 영역 위에서 제거하는 것이다. 유전층의 일부는 표준 에칭 기술을 사용하여 제거될 수 있다.

방법(300)의 단계 311은 에미터 영역 및 베이스 영역 주변에 스페이서 구조를 형성하는 것이다. 예를 들어, 스페이서 구조는 도 2의 스페이서 구조(211)와 유사할 수 있다. 일 실시예에서, 스스/드레인 영역(215)과 같은 소스/드레인 임플란트는, 상술한 단계들이 완료된 후, CMOS 공정 플로우의 일부로서 형성될 수 있다.

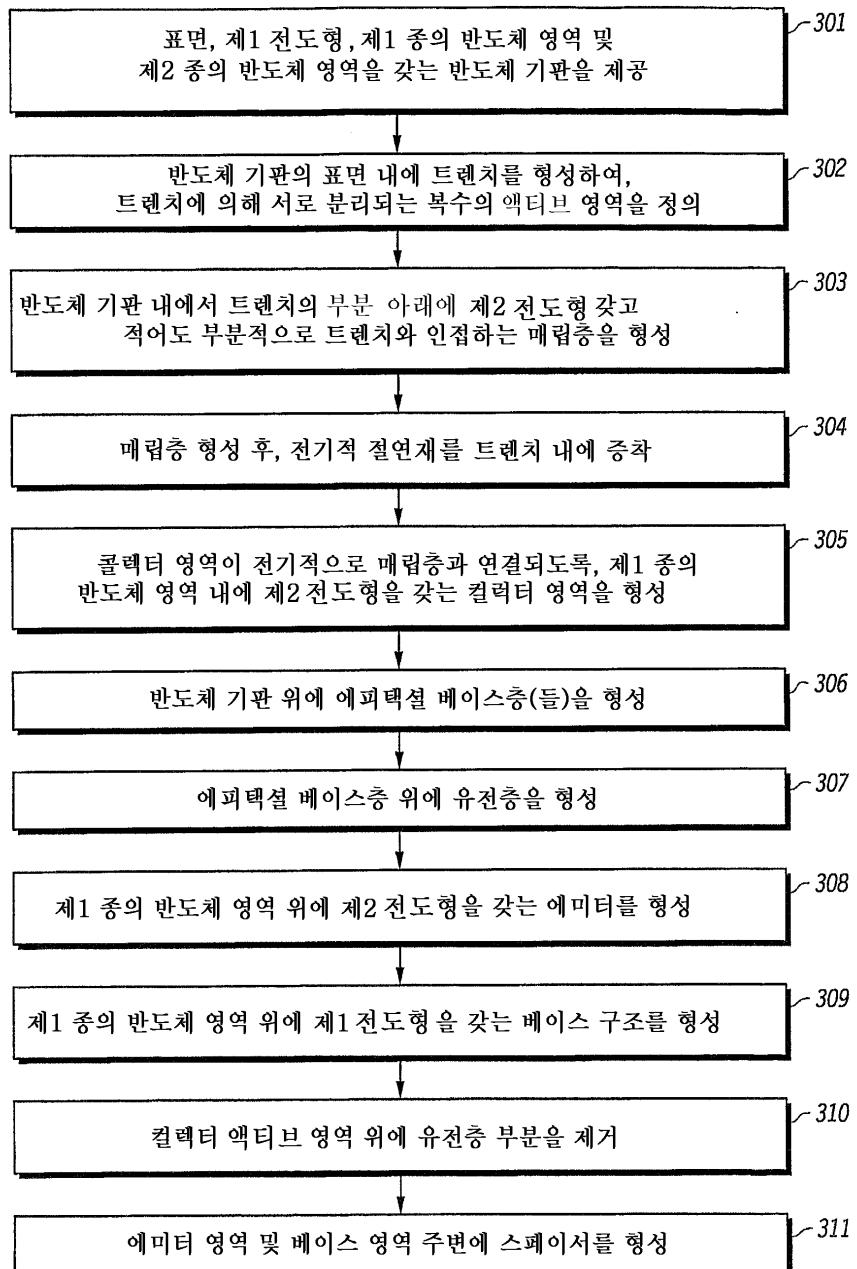

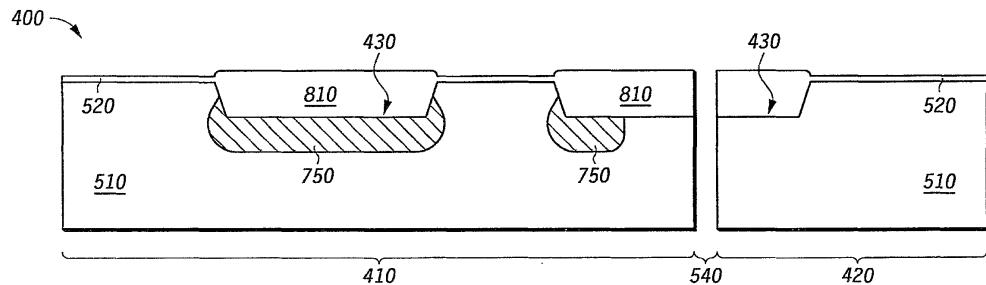

도 4는 본 발명의 실시예에 따른 반도체 커먼트(400)의 평면도이다. 반도체 커먼트(400)는 트렌치(430)에 의해 둘러싸인 바이폴라 반도체 영역(410) 및 CMOS 영역(420)을 포함한다. 도 4에서, 바이폴라 반도체 영역(410) 및 CMOS 영역(420)은 점선에 의해 둘러싸여 표시되어 있다. 일 실시예에서, 트렌치(430)는 복수의 바이폴라 반도체 영역 및 복수의 CMOS 영역을 둘러쌀 수 있다. 바이폴라 반도체 영역(410)은 액티브 영역(411) 및 액티브 영역(412)을 포함한다. CMOS 영역(420)은 액티브 영역(421)을 포함한다. 또한, 도 4에 점선에 의해 포함되도록 표시된 영역(413)은, 이하 더 상세히 기술되겠지만, 매립층이 형성되는 영역을 나타낸다.

도 5는 본 발명의 실시예에 따른 제조 공정의 특정 단계에서의 반도체 커먼트(400)의 단면도이다. 도 5에 도시된 바와 같이, 반도체 커먼트(400)는 반도체 기판(510), 산화물층(520), 및 질화물층(530)을 포함한다. 캡(540)은, 바이폴라 반도체 영역(410) 및 CMOS 영역(420)을 분리하는 캡을 나타내고, 설명을 위해 도 5 및 후속하는 도면들에 포함된다.

도 6은 본 발명의 실시예에 따른 제조 공정의 이후 단계에서 반도체 커먼트(400)의 단면도이다. 도 6은 도 4의 절단선 6-6을 따라 취해진 것이다. 도 6에 도시된 바와 같이, 트렌치(430)는 바이폴라 반도체 영역(410) 및 CMOS 영역(420) 양자 내에 위치한다. 상술한 바와 같이, 트렌치(430)는 표준 또는 공지된 트렌치 형성 기술에 따라 형성될 수 있다.

도 7은 본 발명의 실시예에 따른 제조 공정의 이후 단계에서의 반도체 커먼트(400)의 단면도이다. 도 7에 도시된 바와 같이, 반도체 커먼트(400)는 산화물층(710), TEOS층(720), 및 질화물층(730)을 더 포함한다. 또한, 도 7에 도시된 바와 같이, 임플란트 마스크(740)가 CMOS 영역(420) 내의 액티브 영역(421) 및 트렌치(430)의 일부 위에 제공되었다. 또한, 임플란트 마스크(740)는 바이폴라 반도체 영역(410) 내의 트렌치(430)의 일부 위에 제공되어 있다. 임플란트 마스크(740)를 이러한 방식으로 트렌치(430)의 일부 위에 배치하는 것은 디바이스 저항, 브레이크다운 전압, 및/또는 격리 특성이 특정 어플리케이션에 대해 우수하게 튜닝되고 맞추어지도록 한다. 도 7에 더 도시된 바와 같이, 매립층(750)은 반도체 기판(510) 내에서 바이폴라 반도체 영역(410) 내의 트렌치(430)의 일부 아래에 형성되어 있다. 예를 들어, 매립층(750)이 형성된 트렌치(430)의 일부는 도 4의 영역(413)과 유사할 수 있다. 매립층은 트렌치(430)과 적어도 부분적으로 인접한다. CMOS 영역(420)에는 어떤 매립층도 위치하지 않는다.

일 실시예에서, 질화물층(730)의 일부는 트렌치(430)의 일부 내에서 스페이서 구조로서 작용한다. 예를 들어, 스페이서 구조는, 트렌치(430)의 하부 위에서 임플란트 스크린층으로서의 역할도 하는 얇은 TEOS층 위에 실리콘 질화물층을 포함한다. 스페이서 구조는, 상당한 측벽 각을 갖는 트렌치(430)의 측벽을 마스킹하는데 사용될 수 있다. 트렌치의(430) 측벽이

이러한 방식으로 마스킹되지 않을 경우에는, 매립층(750)의 형성은 매립층 임플란트가 트렌치의 측벽을 관통하도록 야기할 것이다. 도핑된 트렌치 측벽은 컬렉터 베이스 브레이크다운 전압을 열화시키고 기생 컬렉터 베이스 용량성을 증가시켜, 전체 디바이스 성능을 열화시킬 수 있다.

도 8은 본 발명의 실시예에 따른 제조 공정의 후속 단계에서의 반도체 컴포넌트(400)의 단면도이다. 도 8에 도시된 바와 같이, TEOS와 같은 전기적 절연재는, 예를 들어, 트렌치(430) 내에 배치될 수 있고, 반도체 컴포넌트(400)는 평탄화되고 매립층(750)은 확산될 수 있다. 이러한 결과를 달성하기 위해서는 본 기술 분야에서 공지된 평탕화 및 확산 기술이 사용될 수 있다. 반도체 컴포넌트(400)의 제조는 도 8에 도시된 시점부터 표준 또는 공지된 공정에 따라 모든 바이폴라 및 CMOS 디바이스가 형성될 때까지 진행한다.

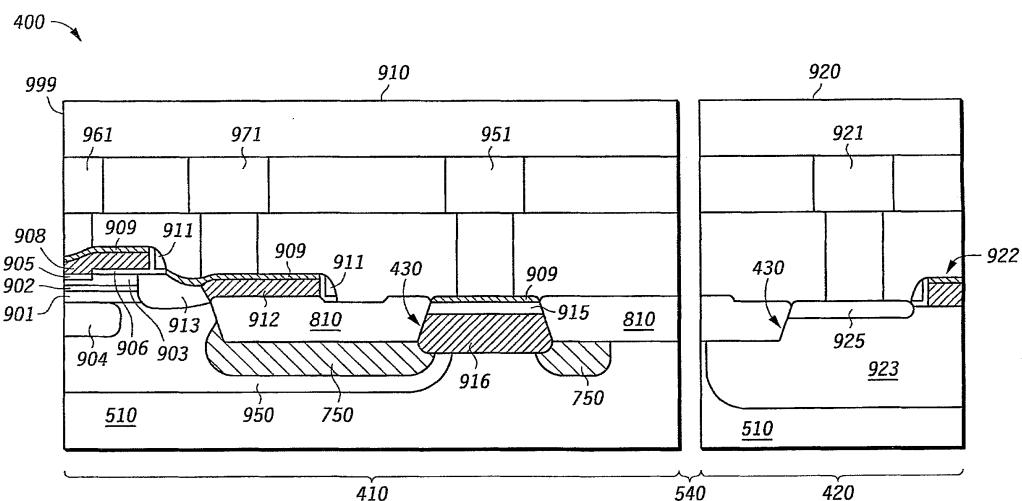

도 9는 본 발명의 실시예에 따른 제조 공정의 이후 단계에서의 반도체 컴포넌트(400)의 단면도이고, 바이폴라 반도체 영역(410) 내의 HBT 디바이스(910) 및 CMOS 영역(420) 내의 CMOS 디바이스(920)를 나타낸다. 도 9에 도시된 바와 같이, 매립층(750)은 바이폴라 반도체 영역(410) 내의 트렌치(430)의 일부 아래에는 위치하지만, CMOS 영역(420)에는 위치하지 않는다.

도 9의 바이폴라 반도체 영역(410) 내에 도시된 완성된 HBT 디바이스는 도 2에 도시된 반도체 디바이스(101)와 유사하다. 완성된 HBT 디바이스의 일부만이 도 9에 도시되어 있다. 도시된 실시예에서, HBT 디바이스(910)는 바이폴라 반도체 영역(410)의 좌측 가장자리를 나타내는 라인(999)에 대해 대칭이다. HBT 디바이스(910)는 비도핑된 실리콘 에피택셜층(910) 및 실리콘 에피택셜층(903), 실리콘 게르마늄 에피택셜층(902), 선택적 주입된 컬렉터 영역(904), 실리콘 에피택셜층(903) 내에 위치하는 에미터 확산(905), 유전층(906), 에미터(908), 실리사이드층(909), 스페이서 구조(911), 베이스 컨택트(912), 및 외인성 베이스 영역(913)을 포함한다. HBT 디바이스(910)는 소스/드레인 임플란트(915), 저항 임플란트(916), 및 컬렉터 영역(950)을 더 포함한다. 소스/드레인 임플란트(915) 및 저항 임플란트(916)는 모두 매립층(750)에 대한 컨택트를 형성한다. 또한, HBT 디바이스(910)는 컬렉터 전극(951), 에미터 전극(961), 및 베이스 전극(971)을 더 포함한다. 앞서 기술된 바와 같이, 매립층(750)은 HBT 디바이스(910) 내의  $R_{CX}$ 의 측면 컴포넌트(241)를 낮추어, HBT 디바이스(910)의 성능을 매우 향상시킨다.

도 9에 일부만 도시된 CMOS 디바이스(920)는, 표준 및 공지된 기술에 따라 제조된, 소스/드레인 영역(925), 게이트 영역(922), 웨(923), 및 소스/드레인 전극(921)을 포함한다. 반도체 컴포넌트(400)는 부가적인 바이폴라 반도체 영역(410)과 유사한 바이폴라 반도체 영역과 CMOS 영역(420)과 유사한 부가적인 CMOS 영역을 더 포함한다는 것이 이해될 것이다.

본 발명은 특정 실시예들을 참조하여 설명되었지만, 본 기술 분야에 종사하는 사람이라면, 본 발명의 사상 및 범주를 벗어남이 없이도, 다양한 변경이 이루어질 수 있음을 이해할 것이다. 그러한 변경의 다양한 예들은 전술한 설명에서 제시된 바 있다. 특정 예로서, 본 발명은 HBT와 연관하여 기술하였지만, 본 발명은 다른 종류의 디바이스와 연관되어 사용될 수도 있다. 따라서, 본 발명의 실시예의 개시는 본 발명을 한정하고자 하는 것이 아니라, 본 발명의 범주를 설명하기 위한 것이다. 본 발명의 범주는 첨부된 청구범위에 의해 요구되는 정도까지만 한정된다. 예를 들어, 본 기술 분야에 종사하는 사람에게는, 본 명세서에서 설명된 반도체 컴포넌트는 다양한 실시예로 구현될 수 있고, 이들 실시예 중 하나에 대한 이전의 논의는 모든 가능한 실시예들의 전체 기술을 나타내는 것은 아니라는 것을 쉽게 이해될 것이다.

부가적으로, 이득, 다른 이점, 및 문제에 대한 해결책이 특정 실시예에 대하여 기술되었다. 그러나, 이득, 이점, 문제점에 대한 해결책, 및 소정의 이득, 이점, 또는 해결책이 발생하고 더 언급되도록 할 수 있는 어떤 다른 요소 또는 요소들은, 어떤 또는 모든 청구범위에 대한 중대한, 필수의, 또는 본질적인 특징으로서 간주되지는 않을 것이다.

또한, 본 명세서에서 개시된 실시예들 및 한정들은, 실시예들 및/또는 한정이, (1) 청구범위에서 명백히 청구되지 않고, (2) 균등론(doctrine of equivalents) 하에서 청구범위 내에서 표현된 요소 및/또는 한정의 등가물 또는 잠재적인 등가물인 경우, 공개의 원칙하에서 공중에게 공개된 것이 아니다.

## (57) 청구의 범위

### 청구항 1.

표면 및 제1 전도형을 갖는 반도체 기판을 제공하는 단계와,

상기 반도체 기판의 표면에 트렌치를 형성하여, 상기 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 정의하는 단계와,

상기 반도체 기판 내에서 상기 트렌치부 아래에, 제2 전도형을 가지고 상기 트렌치와 적어도 부분적으로 인접하는 매립층을 형성하는 단계와,

상기 매립층 형성 단계 후, 상기 트렌치 내에 전기 절연재를 증착하는 단계와,

상기 복수의 액티브 영역 중 하나의 액티브 영역 내에 상기 제2 전도형을 갖는 컬렉터 영역을 형성하는 단계와,

상기 복수의 액티브 영역 중 하나의 액티브 영역 위에 상기 제1 전도형을 갖는 베이스 구조를 형성하는 단계와,

상기 복수의 액티브 영역 중 하나의 액티브 영역 위에 제2 전도형을 갖는 에미터 영역을 형성하는 단계를 포함하고,

상기 컬렉터 영역은 상기 매립층에 대한 컨택트를 형성하는 반도체 컴포넌트 제조 방법.

## 청구항 2.

제1항에 있어서,

상기 컬렉터 영역은 제1 저항을 가지고,

상기 매립층은 제2 저항을 가지고,

상기 제1 저항은 상기 제2 저항보다 큰 반도체 컴포넌트 제조 방법.

## 청구항 3.

제1항에 있어서,

상기 트렌치 내에 스페이서 구조를 형성하는 단계와,

상기 매립층 형성 후, 상기 스페이서 구조를 제거하는 단계

를 더 포함하는 반도체 컴포넌트 제조 방법.

## 청구항 4.

제1항에 있어서,

상기 매립층 형성 단계는 상기 트렌치를 통해 제2 전도형을 갖는 도편트를 주입하는 단계를 포함하는 반도체 컴포넌트 제조 방법.

## 청구항 5.

제4항에 있어서,

상기 매립층 형성 단계는 상기 도편트를 주입한 후, 상기 트렌치를 충전하기 전에 상기 도편트를 어닐링하는 단계를 더 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 6.

제1항에 있어서,

상기 반도체 기판은 제1 종의 반도체 영역과 제2 종의 반도체 영역을 포함하고,

상기 매립층 형성 단계 전에 상기 제2 종의 반도체 영역 위에 임플란트 마스크를 형성하는 단계를 포함하고,

상기 매립층 형성 단계는 상기 제1 종의 반도체 영역의 적어도 일부분 아래에 상기 매립층을 형성하는 단계를 더 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 7.

제6항에 있어서,

상기 제1 종의 반도체 영역은 바이폴라 반도체 영역을 포함하고,

상기 제2 종의 반도체 영역은 CMOS 영역을 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 8.

제1항에 있어서,

상기 반도체 컴포넌트의 제조는, 상기 복수의 액티브 영역 중 하나의 액티브 영역을 상기 에미터 영역의 중앙을 통해 그려지는 수직 라인에 대해 대칭이 되도록 제조하는 단계를 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 9.

표면 및 제1 전도형을 갖는 반도체 기판 - 상기 반도체 기판은 제1 종의 복수의 반도체 영역 및 제2 종의 복수의 반도체 영역을 포함함 - 을 제공하는 단계와,

상기 반도체 기판의 표면 내에 트렌치를 형성하여, 상기 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 정의하는 단계와,

상기 트렌치 내에 복수의 스페이서 구조를 형성하는 단계, 상기 제2 종의 복수의 반도체 영역 위에 임플란트 마스크를 형성하는 단계, 및 각각이 제1 종의 복수의 반도체 영역 내에서 상기 트렌치의 적어도 일부분 아래에 위치하는 복수의 매립층 - 상기 복수의 매립층은 제2 전도형을 갖고, 적어도 부분적으로 상기 트렌치와 인접하고, 상기 복수의 스페이서 구조 중 하나의 스페이서 구조는 상기 트렌치에 대해 상기 복수의 매립층 중 하나의 매립층을 자기 정렬하는데 사용됨 - 을 형성하는 단계를 포함하는 매립층 모듈 형성 단계와,

상기 복수의 매립층을 형성하는 단계 후, 상기 트렌치를 전기적 절연재를 증착하는 단계와,

상기 제1 종의 복수의 반도체 영역의 각 반도체 영역 내에 상기 제2 전도형을 갖는 컬렉터 영역을 형성하는 단계와,

상기 제1 종의 복수의 반도체 영역의 각 반도체 영역 내에 상기 제2 전도형을 갖는 에미터 영역을 형성하는 단계

를 포함하고,

상기 제1 종의 복수의 반도체 영역의 각 반도체 영역 내의 컬렉터 영역은 상기 제1 종의 복수의 반도체 영역 중 하나의 반도체 영역 내에 상기 매립층에 대한 컨택트를 형성하는 반도체 컴포넌트 제조 방법.

### 청구항 10.

제9항에 있어서,

상기 제1 종의 복수의 반도체 영역 내에서 상기 제2 전도형을 갖는 베이스 영역을 형성하는 단계를 더 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 11.

제10항에 있어서,

상기 베이스 영역을 형성하는 단계는 상기 베이스 영역 내에 컨택트를 형성하는 단계를 더 포함하고,

상기 베이스 영역 내의 컨택트는 상기 트렌치의 적어도 일부 위에 있는 반도체 컴포넌트 제조 방법.

### 청구항 12.

제9항에 있어서,

상기 컬렉터 영역은 제1 저항을 갖고,

상기 복수의 매립층은 제2 저항을 가지며,

상기 제1 저항은 상기 제2 저항보다 큰 반도체 컴포넌트 제조 방법.

### 청구항 13.

제9항에 있어서,

상기 복수의 매립층을 형성하는 단계는 상기 트렌치를 통해 상기 제2 전도형을 갖는 도편트를 주입하는 단계를 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 14.

제13항에 있어서,

상기 복수의 매립층을 형성하는 단계는, 상기 도편트를 주입한 후, 상기 트렌치를 충전하기 전에 상기 도편트를 어닐링하는 단계를 더 포함하는 반도체 컴포넌트 제조 방법.

### 청구항 15.

제9항에 있어서,

상기 반도체 캠포넌트의 제조는, 상기 제1 종의 복수의 반도체 영역을 상기 에미터 영역의 중앙을 통해 그려지는 수식 전에 대해 대칭이 되도록 제조하는 단계를 포함하는 반도체 캠포넌트 제조 방법.

### 청구항 16.

제9항에 있어서,

상기 매립층 모듈은 CMOS 공정 플로우와 공용할 수 있는 반도체 캠포넌트 제조 방법.

### 청구항 17.

표면 및 제1 전도형을 갖는 반도체 기판 – 상기 반도체 기판은 복수의 바이폴라 반도체 영역 및 복수의 CMOS 영역을 포함함 – 을 제공하는 단계와,

상기 반도체 기판의 표면 내에서 상기 복수의 바이폴라 반도체 영역 및 상기 복수의 CMOS 영역 내에 트렌치를 형성하여, 상기 트렌치에 의해 서로 분리되는 복수의 액티브 영역을 형성하는 단계와,

상기 반도체 영역 내의 상기 복수의 바이폴라 반도체 영역 내에서 상기 트렌치의 일부 아래에 매립층 – 상기 매립층은 제2 전도형을 가지고 상기 트렌치와 적어도 부분적으로 인접함 – 을 형성하는 단계와,

상기 매립층 형성 단계 후, 상기 트렌치 내에 전기 절연재를 증착하는 단계와,

상기 복수의 바이폴라 반도체 영역의 각 반도체 영역 내에 제2 전도형을 갖는 컬렉터 영역을 형성하는 단계와,

상기 복수의 바이폴라 반도체 영역의 각 반도체 영역 내에 제1 전도형을 갖는 베이스 구조를 형성하는 단계와,

상기 복수의 바이폴라 반도체 영역의 각 반도체 영역 위에 상기 제2 전도형을 갖는 에미터를 형성하는 단계와,

상기 복수의 CMOS 영역의 각 CMOS 영역 위에 소스/및 드레인 영역을 형성하는 단계와,

상기 복수의 CMOS 영역의 각 CMOS 영역 위에 게이트 영역을 형성하는 단계

를 포함하고, 상기 컬렉터 영역은 상기 매립층에 대한 컨택트를 형성하는 반도체 캠포넌트 제조 방법.

### 청구항 18.

제17항에 있어서,

상기 컬렉터 영역을 형성하는 단계는 상기 소스/드레인 영역을 형성하는 단계와 동시에 발생하는 반도체 캠포넌트 제조 방법.

### 청구항 19.

제17항에 있어서,

상기 컬렉터 영역은 제1 저항을 갖고,

상기 매립층은 제2 저항을 갖고,

상기 제1 저항은 상기 제2 저항보다 큰 반도체 컴포넌트 제조 방법.

도면

도면1

도면2

## 도면3

도면4

도면5

도면6

도면7

도면8

도면9