(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5857072号

(P5857072)

(45) 発行日 平成28年2月10日(2016.2.10)

(24) 登録日 平成27年12月18日(2015.12.18)

(51) Int.Cl.

G 0 6 F 9/45 (2006.01)

F 1

G O 6 F 9/44 3 2 2 F

請求項の数 47 (全 34 頁)

(21) 出願番号 特願2013-550671 (P2013-550671)

(86) (22) 出願日 平成24年1月24日 (2012.1.24)

(65) 公表番号 特表2014-506693 (P2014-506693A)

(43) 公表日 平成26年3月17日 (2014.3.17)

(86) 國際出願番号 PCT/US2012/022441

(87) 國際公開番号 WO2012/103148

(87) 國際公開日 平成24年8月2日 (2012.8.2)

審査請求日 平成27年1月22日 (2015.1.22)

(31) 優先権主張番号 61/436,051

(32) 優先日 平成23年1月25日 (2011.1.25)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595168543

マイクロン テクノロジー, インク.

アメリカ合衆国, アイダホ州 83716

-9632, ポイズ, サウス フェデ

ラル ウエイ 8000

(74) 代理人 100106851

弁理士 野村 泰久

(74) 代理人 100074099

弁理士 大菅 義之

(72) 発明者 シュ-, ジュンジュエン

アメリカ合衆国, カリフォルニア州 95

131, サン ノゼ, クアドロス レーン

2008

最終頁に続く

(54) 【発明の名称】オートマトンの入次数および／または出次数を制御するための量化子の展開

## (57) 【特許請求の範囲】

## 【請求項1】

量化子をオートマトンに変換することであって、変換することが、前記オートマトンの入次数を制御するように前記量化子を展開することを含む、量化子をオートマトンに変換することと、

前記オートマトンを、対象装置に対応する機械コードに変換することとを含むコンピュータ実装方法。

## 【請求項2】

式を、前記量化子を含む、言語固有でない表現に解析すること、をさらに含む、請求項1に記載のコンピュータ実装方法。 10

## 【請求項3】

式を、言語固有でない表現に解析することが、正規表現を構文木に解析することを含む、請求項2に記載のコンピュータ実装方法。

## 【請求項4】

変換することが、前記量化子に対する繰返し式が空値可能である場合、前記量化子を、ゼロ回一致し得る前記繰返し式の空値不能形式を有する量化子として展開することを含む、請求項1に記載のコンピュータ実装方法。

## 【請求項5】

前記オートマトンを機械コードに変換することが、前記オートマトンを、対象装置をプログラムするように構成されたイメージに変換することを含む、請求項1に記載のコンピ 20

ユータ実装方法。

【請求項 6】

前記イメージを公開すること、をさらに含む、請求項 5 に記載のコンピュータ実装方法。

【請求項 7】

前記オートマトンの入次数を制御するように前記量化子を展開することが、入次数制限に応じて、前記量化子を展開することを含む、請求項 1 に記載のコンピュータ実装方法。

【請求項 8】

前記入次数制限が、前記オートマトンの状態への遷移数に関する制限を含む、請求項 7 に記載のコンピュータ実装方法。 10

【請求項 9】

前記オートマトンの入次数を制御するように前記量化子を展開することが、前記対象装置の入次数制約に基づいて展開することを含む、請求項 1 に記載のコンピュータ実装方法。

【請求項 10】

前記量化子が正規表現である、請求項 1 に記載のコンピュータ実装方法。

【請求項 11】

前記オートマトンの入次数を制御するように前記量化子を展開することが、閾値に基づいて前記オートマトンの入次数を制御するように前記量化子を展開することを含む、請求項 1 に記載のコンピュータ実装方法。 20

【請求項 12】

前記閾値が、前記対象装置のハードウェア制限に基づく、請求項 11 に記載のコンピュータ実装方法。

【請求項 13】

命令を含むコンピュータ可読媒体であって、

前記命令が、前記コンピュータによって実行されるときに、前記コンピュータに：

量化子をオートマトンに変換することであって、変換することが、前記オートマトンの出次数を制御するように前記量化子を展開することを含む、量化子をオートマトンに変換することと、

前記オートマトンを、対象装置に対応する機械コードに変換することと 30

を含む動作を実行させる、

コンピュータ可読媒体。

【請求項 14】

展開することが、前記オートマトンの各状態に対する前記出次数を閾値数未満に制限することを含む、請求項 13 に記載のコンピュータ可読媒体。

【請求項 15】

展開することが、前記オートマトンの各状態に対する出遷移を最小限にすることを含む、請求項 13 に記載のコンピュータ可読媒体。

【請求項 16】

変換することが、前記量化子に対する繰返し式が空値可能である場合、前記量化子を、ゼロ回一致し得る前記繰返し式の空値不能形式を有する量化子として展開することを含む、請求項 13 に記載のコンピュータ可読媒体。 40

【請求項 17】

変換することが、

前記量化子が单一のある個数のループと一致し得る場合、前記量化子を、連続的にリンクされた前記单一のある個数に等しい、いくつかの式を表す状態を有するオートマトンを形成するように展開することを含み、前記式が、前記量化子に対する繰返し式に対応する、請求項 13 に記載のコンピュータ可読媒体。

【請求項 18】

前記量化子が複数のある個数のループと一致し得る場合、前記複数のある個数のループ 50

が、第1の数のループ、n1、および第2の数のループ、n2を含み、前記量化子を展開することが：

前記量化子を、n1-1個のループと一致し得る第1の量化子および、1~n2-n1+1個までのループと一致し得る第2の量化子に分割することを含む、

請求項13に記載のコンピュータ可読媒体。

【請求項19】

前記機械コードが、対象装置をプログラムするように構成されたイメージを含み、

前記命令が、前記コンピュータに：

前記イメージを対象装置上にロードすること

を含む動作を実行させる、請求項13に記載のコンピュータ可読媒体。 10

【請求項20】

前記機械コードが、対象装置をプログラムするように構成されたイメージを含み、

前記命令が、前記コンピュータに：

前記イメージを、コンピュータ可読媒体上に格納すること

を含む動作を実行させる、請求項13に記載のコンピュータ可読媒体。 20

【請求項21】

コンピュータであって、

ソフトウェアがその上に格納されたメモリと、

前記メモリに通信的に結合されたプロセッサであって、前記ソフトウェアが、前記プロセッサによって実行されるとき、前記プロセッサに：

量化子をオートマトンに変換することであって、変換することが、前記量化子を、前記オートマトンの入次数または出次数を制御するように展開することを含む、量化子をオートマトンに変換することと、

前記オートマトンを、対象装置に対応する機械コードに変換することと

をさせる、プロセッサと

を備えるコンピュータ。 30

【請求項22】

前記ソフトウェアが、前記プロセッサに、前記オートマトン内で入遷移を出遷移に対してトレードオフすることにより、前記入次数および出次数を制御させる、請求項21に記載のコンピュータ。 30

【請求項23】

各状態に対する前記入遷移が、展開時に閾値数未満に制限される、請求項22に記載のコンピュータ。

【請求項24】

前記入次数が、前記出次数の割合に制限される、請求項22に記載のコンピュータ。

【請求項25】

前記オートマトンの状態に対する入遷移の閾値に達するまで、前記入次数が、前記出次数の前記割合に制限される、請求項24に記載のコンピュータ。

【請求項26】

量化子をオートマトンに変換することであって、変換することが、前記オートマトンの入次数または出次数を制御するように前記量化子を展開することを含む、量化子をオートマトンに変換することと、

前記オートマトンを、対象装置に対応する機械コードに変換することと

を行うように構成されたコンピュータ 40

を備えるシステム。

【請求項27】

前記機械コードが、対象装置をプログラムするように構成されたイメージを含み、

前記コンピュータに通信的に結合され、かつ前記イメージを対象装置上にロードするよう構成された装置を

さらに含む、請求項26に記載のシステム。 50

**【請求項 2 8】**

前記オートマトンの入次数を制御するように前記量化子を展開することが、入次数制限に応じて前記量化子を展開することを含む、請求項 2 6 に記載のシステム。

**【請求項 2 9】**

前記入次数制限が、前記オートマトンの状態への遷移数に関する制限を含む、請求項 2 8 に記載のシステム。

**【請求項 3 0】**

前記オートマトンの入次数を制御するように前記量化子を展開することが、前記対象装置の入次数制約に基づいて展開することを含む、請求項 2 6 に記載のシステム。

**【請求項 3 1】**

前記オートマトンの入次数を制御するように前記量化子を展開することが、閾値に基づいて前記オートマトンの入次数を制御するように前記量化子を展開することを含む、請求項 2 6 に記載のシステム。

10

**【請求項 3 2】**

前記閾値が、前記対象装置のハードウェア制限に基づく、請求項 3 1 に記載のシステム。

**【請求項 3 3】**

量化子をオートマトンに変換することであって、変換することが、前記オートマトンの出次数を制御するように前記量化子を展開することを含む、量化子をオートマトンに変換することと、

20

前記オートマトンを、対象装置に対応する機械コードに変換することとを含むコンピュータ実装方法。

**【請求項 3 4】**

正規表現を構文木に解析すること、をさらに含む、請求項 3 3 に記載のコンピュータ実装方法。

**【請求項 3 5】**

前記オートマトンを機械コードに変換することが、前記オートマトンを、対象装置をプログラムするように構成されたイメージに変換することを含む、請求項 3 3 に記載のコンピュータ実装方法。

30

**【請求項 3 6】**

前記イメージを公開すること、をさらに含む、請求項 3 5 に記載のコンピュータ実装方法。

**【請求項 3 7】**

前記オートマトンの出次数を制御するように前記量化子を展開することが、出次数制限に応じて前記量化子を展開することを含む、請求項 3 3 に記載のコンピュータ実装方法。

**【請求項 3 8】**

前記出次数制限が、前記オートマトンの状態からの遷移数に関する制限を含む、請求項 3 7 に記載のコンピュータ実装方法。

**【請求項 3 9】**

前記オートマトンの出次数を制御するように前記量化子を展開することが、前記対象装置の出次数制約に基づいて展開することを含む、請求項 3 3 に記載のコンピュータ実装方法。

40

**【請求項 4 0】**

前記オートマトンの出次数を制御するように量化子を展開することが、閾値に基づいて前記オートマトンの出次数を制御するように前記量化子を展開することを含む、請求項 3 3 に記載のコンピュータ実装方法。

**【請求項 4 1】**

前記閾値が、前記対象装置のハードウェア制限に基づく、請求項 4 0 に記載のコンピュータ実装方法。

**【請求項 4 2】**

50

命令を含むコンピュータ可読媒体であって、

前記命令が、前記コンピュータによって実行されるときに、前記コンピュータに：

量化子をオートマトンに変換することであって、変換することが、前記オートマトンの入次数を制御するように前記量化子を展開することを含む、量化子をオートマトンに変換することと、

前記オートマトンを、対象装置に対応する機械コードに変換することと

を含む動作を実行させる、

コンピュータ可読媒体。

**【請求項 4 3】**

展開することが、前記オートマトンの各状態に対する入遷移を閾値数未満に制限することを含む、請求項 4 2に記載のコンピュータ可読媒体。 10

**【請求項 4 4】**

展開することが、前記オートマトンの各状態に対する入遷移を最小限にすることを含む、請求項 4 2に記載のコンピュータ可読媒体。

**【請求項 4 5】**

変換することが、前記量化子に対する繰返し式が空値可能である場合、前記量化子を、ゼロ回一致し得る前記繰返し式の空値不能形式を有する量化子として、展開することを含む、請求項 4 2に記載のコンピュータ可読媒体。

**【請求項 4 6】**

変換することが、

前記量化子が单一のある個数のループと一致し得る場合、連続的にリンクされた前記单一のある個数に等しい、いくつかの式を表す状態を有するオートマトンを形成するように前記量化子を展開することを含み、前記式が、前記量化子に対する繰返し式に対応する、請求項 4 2に記載のコンピュータ可読媒体。 20

**【請求項 4 7】**

前記量化子が複数のある個数のループと一致し得る場合、前記複数のある個数のループが、第 1 の数のループ、n 1、および第 2 の数のループ、n 2 を含み、前記量化子を展開することが：

前記量化子を、n 1 - 1 個のループと一致し得る第 1 の量化子および、1 ~ n 2 - n 1 + 1 個までのループと一致し得る第 2 の量化子に分割することを含む、請求項 4 2に記載のコンピュータ可読媒体。 30

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

**〔優先権主張〕**

本特許出願は、2011年1月25日に出願された、「UNROLLING QUANTIFICATIONS TO CONTROL IN-DEGREE AND/OR OUT DEGREE OF AUTOMATION」という名称の米国仮特許出願整理番号 61/436,051 に対する優先権の利益を主張し、これによって、参照によりその全体として本明細書に組み込まれる。 40

**【背景技術】**

**【0 0 0 2】**

有限状態機械（FSM）（有限状態オートマトン、オートマトン、または単に状態機械とも呼ばれる）は、状態、状態と動作との間の遷移の表現である。有限状態機械は、並列マシン用のデジタル論理、コンピュータプログラム、またはイメージを設計するために使用できる。有限状態機械は、有限数の状態、それら状態間の遷移、および出力から成る挙動のモデルである。有限状態機械は、グラフとして表すことができ、グラフのバーテックスが有限状態機械の状態に対応し、グラフのエッジが、有限状態機械に対する 1 つまたは複数の入力に起因して生じる状態間の遷移に対応する。有限状態機械は、確率的遷移、フ 50

アジー状態、または他の奇妙な事柄 ( oddity ) も持つことができる。有限状態機械は、有限の内部メモリ、入力特徴、および隨意の出力特徴を有する。出力を有する有限状態機械は、有限状態トランステューサと呼ぶことができる。

#### 【 0 0 0 3 】

有限状態機械の用途には、コンピュータによる電子設計の自動化、通信プロトコル設計、生物学および人工知能研究、ならびに自然言語の文法を説明する言語学を含む。

#### 【 図面の簡単な説明 】

#### 【 0 0 0 4 】

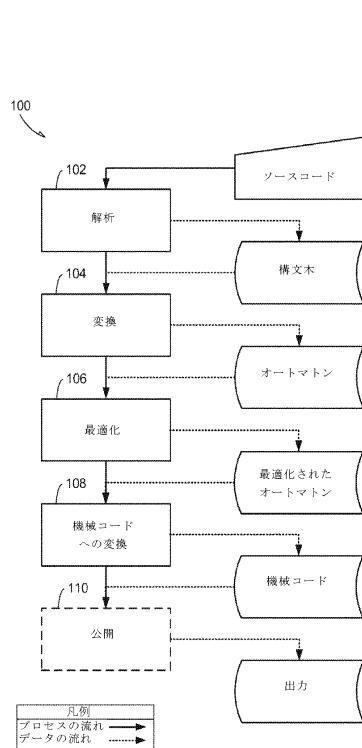

【図1】本発明の様々な実施形態に従い、オートマトンを使用して、ソースコードを機械コードに変換できるコンパイラのための流れ図の一例を示す。

10

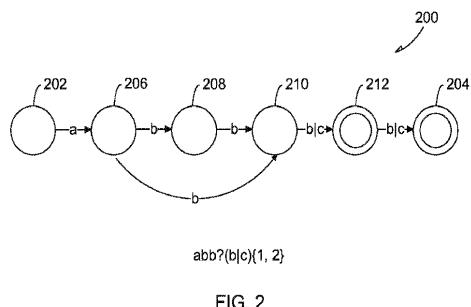

【図2】本発明の様々な実施形態に従い、コンパイラによって使用されるオートマトンの一例を示す。

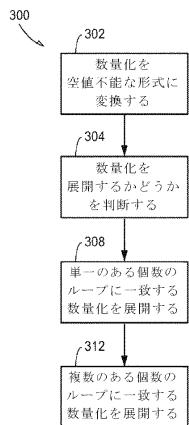

【図3】本発明の様々な実施形態に従った、量化子を展開するための方法の一例を示す。

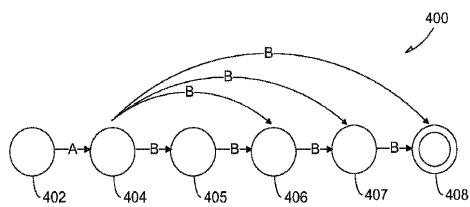

【図4 A】本発明の様々な実施形態に従って、展開された量化子のためのオートマトン例を示す。

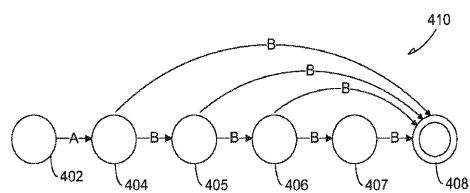

【図4 B】本発明の様々な実施形態に従って、展開された量化子のためのオートマトン例を示す。

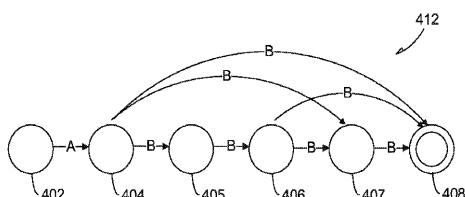

【図4 C】本発明の様々な実施形態に従って、展開された量化子のためのオートマトン例を示す。

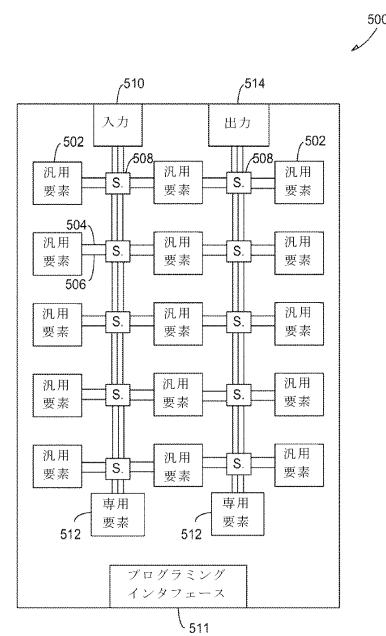

【図5】本発明の様々な実施形態に従った、並列マシンの一例を示す。

20

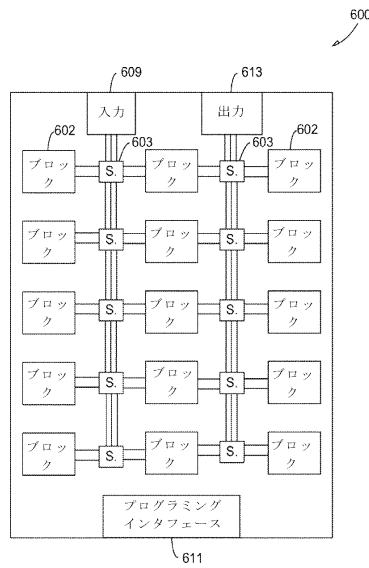

【図6】本発明の様々な実施形態に従って、有限状態機械エンジンとして実装された図5の並列マシンの一例を示す。

【図7】本発明の様々な実施形態に従って、図6の有限状態機械エンジンのブロックの一例を示す。

【図8】本発明の様々な実施形態に従って、図7のブロックの行 ( row ) の一例を示す。

【図9】本発明の様々な実施形態に従って、図8の行の2つのグループの一例を示す。

【図10】本発明の様々な実施形態に従って、コンパイラが正規表現を、図5の並列マシンをプログラムするように構成されたイメージに変換するための方法の一例を示す。

【図11 A】本発明の様々な実施形態に従った、量化子のためのオートマトンに対応するグラフ例を示す。

30

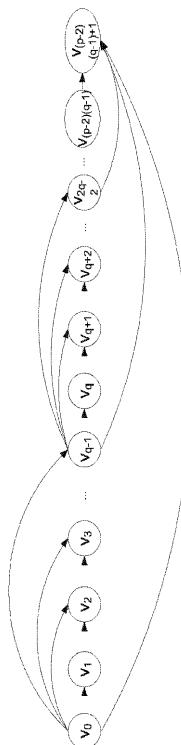

【図11 B】本発明の様々な実施形態に従った、量化子のためのオートマトンに対応するグラフ例を示す。

【図12】本発明の様々な実施形態に従った、量化子のためのオートマトンに対応する別のグラフ例を示す。

【図13】本発明の様々な実施形態に従った、量化子のためのオートマトンに対応するさらに別のグラフ例を示す。

【図14】本発明の様々な実施形態に従った、量化子のためのオートマトンに対応するさらにまた別のグラフ例を示す。

【図15】本発明の様々な実施形態に従った、コンピュータの一例を示す。

40

#### 【 発明を実施するための形態 】

#### 【 0 0 0 5 】

以下の説明および図は、特定の実施形態を当業者が実施できるように十分に説明する。他の実施形態は、構造的、論理的、電気的、プロセス、および他の変更を包含し得る。いくつかの実施形態の部分および特徴は、他の実施形態に含まれ得るか、または他の実施形態のそれらと置き換えられ得る。請求項に規定される実施形態は、それらの請求項の全ての利用可能な均等物を包含する。

#### 【 0 0 0 6 】

本文書では、特に、ソースコードを、有限状態機械の機械コード実装に変換するコンパイラを説明する。機械コードが、ソースコードによって記述された機能を対象装置上で実

50

装するように構成されているという点において、機械コードは、対象装置に対応できる。一例では、対象装置は並列マシンであり、機械コードは、その並列マシン用のイメージを含む。別の例では、対象装置は、フォンノイマン型アーキテクチャを有するコンピュータを含み、機械コードは、そのコンピュータ内のプロセッサによって実行するための命令を含む。

#### 【0007】

いかなる場合にも、コンパイラは、ソースコードを、そのソースコードによって記述された機能を実施する有限状態機械に変換する。ソースコードをコンパイルするプロセスにおいて、コンパイラは、ソースコードをオートマトンに変換する。オートマトンを使用すると、コンパイラは、機械コードで実装された、結果として得られる有限状態機械を最適化するために、ソースコード内の冗長性を識別し、結合できる。さらに、コンパイラは、結果として得られる機械コードの複雑性を減少させ、対象装置の動作効率を向上させるために、オートマトンを形成する際に、対象装置の様相または制限を考慮することができる。

10

#### 【0008】

図1は、コンパイラ例に対する流れ図100を示す。コンパイラは、ソースコードを入力として受け取り、ソースコードによって記述された機能を対象装置上で実装するために、機械コードを生成する。一例では、対象装置は、図5～図9に関して後述するように、並列マシンを含む。並列マシンは、複数の状態のうちの1つに設定できる複数のプログラム可能要素を含む。並列マシンに対する機械コードは、1つまたは複数のプログラム可能要素の状態を設定するためのイメージを含む。別の例では、対象装置は、フォンノイマン型アーキテクチャを有するコンピュータである。コンピュータは、1つまたは複数のプロセッサによって実行するためにその上にソフトウェアを有する、1つまたは複数の記憶装置に結合された1つまたは複数のプロセッサを含む。フォンノイマン型アーキテクチャのための機械コードは、1つまたは複数のプロセッサによって実行するための命令を含む。フォンノイマン型アーキテクチャを有するコンピュータの例は、図15に関して後述される。いかなる場合にも、コンパイラは、オートマトンを中間変換として使用することにより、機械コードを生成する。コンパイラは、オートマトンを、特に、結果として得られるFSMを最適化するため、また、同様に、機械コードを最適化するために使用する。

20

#### 【0009】

一例では、ソースコードは、シンボルグループ内のシンボルのパターンを識別するための検索文字列を記述する。検索文字列を記述するため、ソースコードは、複数の正規表現( regex )を含むことができる。正規表現は、シンボル検索パターンを記述するための文字列であり得る。正規表現は、プログラミング言語、テキストエディタ、ネットワークセキュリティ、およびその他などの、様々なコンピュータドメインで幅広く使用されている。一例では、コンパイラによってサポートされる正規表現は、非構造化データを検索するための検索基準を含む。非構造化データは、自由形式のデータを含み得、データ内のワード(word)に適用された指標付けがない。ワードは、データ内に、印刷可能および印字不能な、バイトの任意の組合せを含み得る。一例では、コンパイラは、Perl(例えば、Perl互換正規表現(PCRE))、PHP、Java(登録商標)、および.NET言語を含む、正規表現を実装するための、複数の異なるソースコード言語をサポートできる。

30

#### 【0010】

図1を再度参照すると、ブロック102で、コンパイラは、ソースコードを解析して、関係的に結合された演算子の配置を形成できる。ソースコードの解析により、ソースコードの一般的表現を作成できる。一例では、一般的表現は、ソースコード内の正規表現の、構文木として知られているツリーグラフの形でコード化された表現を含む。本明細書で説明する例は、そのアレンジメントを構文木(「抽象構文木」としても知られている)と呼ぶが、他の例では、具象構文木または他のアレンジメントも使用できる。

40

#### 【0011】

50

前述したように、コンパイラは、複数言語のソースコードをサポートできるので、解析は、その言語にかかわらず、ソースコードを、例えば、構文木などの、言語固有でない表現に変換する。従って、コンパイラによるさらなる処理（ブロック 104、106、108、110）は、ソースコードの言語にかかわらず、共通の入力構造から動作できる。

#### 【0012】

構文木は、関係的に結合されている複数の演算子を含む。構文木は、複数の異なるタイプの演算子を含むことができ、そこでは、異なるタイプの演算子は、ソースコードによって実装された異なる機能に対応する。すなわち、異なる演算子は、ソースコード内の正規表現によって実装された異なる機能に対応できる。

#### 【0013】

ブロック 104 で、構文木はオートマトンに変換される。オートマトンは、FSM のソフトウェアモデルを含み、それに応じて、決定性または非決定性として分類できる。決定性オートマトンは、一時に、単一経路の実行を有するが、他方、非決定性オートマトンは、複数の並列経路の実行を有する。オートマトンは、複数の状態を含む。構文木をオートマトンに変換するために、構文木内の演算子および演算子間の関係は、状態間の遷移をもつ状態に変換される。

#### 【0014】

対象装置の要素を効果的に利用するために、コンパイラは、対象装置の要素の態様または制限に基づいて、オートマトンを形成できる。例えば、要素は、オートマトン内の所与の状態への、または所与の状態からの遷移の数に関して特定の制約を有し得る。他の例では、ハードの制約は存在しないかも知れないが、コンパイラは、機械コードを生成するため、および / または対象装置上での機械コードの動作効率を向上させるために、コンパイラによって要求される処理を単純化するため、所与の状態への、または所与の状態からの遷移の数を制限し得る。所与の状態への、または所与の状態からの遷移の制限に関するさらなる詳細は、図 3 および図 4A ~ 図 4C に関して、以下で提供される。

#### 【0015】

ブロック 106 で、オートマトンが形成されると、オートマトンは、とりわけ、その複雑性およびサイズを縮小するように最適化される。オートマトンは、特に、同等な状態を結合することにより最適化できる。

#### 【0016】

ブロック 108 で、オートマトンが、対象装置用の機械コードに変換される。一例では、機械コードは、ファンノイマン型アーキテクチャのプロセッサ用の実行可能な命令を含む。ここで、機械コードは、実行可能プログラムを含むことができる。別の例では、機械コードは、並列マシン内のハードウェア要素をプログラムするように構成されたビットを含むことができる。ここで、機械コードは、並列マシン上にロードするためのイメージを含むことができる。

#### 【0017】

ブロック 110 で、機械コードは、コンパイラによって公開できる。一例では、機械コードは、機械コードをコンピュータ可読媒体に保存することによって公開できる。別の例では、機械コードは、機械コードを並列マシン上にロードするためのローダーなど、別の装置に機械コードを送信することによって公開できる。さらに別の例では、機械コードは、機械コードを並列マシン上にロードすることによって公開できる。さらにまた別の例では、機械コードは、機械コードをディスプレイ装置上に表示することにより公開できる。

#### 【0018】

一例では、コンパイラは、ファンノイマン型アーキテクチャを有するコンピュータ用の命令によって実装できる。これらの命令は、コンピュータ上のプロセッサにコンパイラの機能を実装させることができ。例えば、命令は、プロセッサによって実行される場合、プロセッサがアクセス可能なソースコード上のブロック 102、104、106、108、および 110 に記述する動作をプロセッサに実行させることができる。ファンノイマン型アーキテクチャを有するコンピュータ例が図 15 に示され、以下で説明される。

10

20

30

40

50

## 【0019】

ソースコード内に記述できる正規表現の1つのタイプは、量化子を含む。量化子は、当技術分野で周知であり、繰返しパターンを記述するために使用される。一例として、“A(B){n1, n2}C”は、一般的な正規表現であり、ここで、A、BおよびCは部分式であり、また、“(B){n1, n2}”は量化子を含む。本明細書では、大文字は、正規表現または正規表現の一部（例えば、部分式）を表すために使用される。二重引用符が、混乱を避けるために、正規表現または部分式の前後に追加され得る。その結果、式を記述する大文字は、複数の入力シンボルに対する検索文字列に対応できる。例えば、式“A”は、入力文字列‘abbabc’に対応できる。

## 【0020】

10

さらに、本明細書では、式および部分式という用語が関係記述のみのために使用される（例えば、部分式は式の一部である）こと、ならびに式および部分式という用語は、いかなる特定の長さ、構文、または文字数に限定されるべきではないことが理解されるはずである。特に、ソースコードは、文字セット全体またはその任意の個々の部分が「式」と考えられる多数の文字（メタ文字および検索文字を含む）を含むことができる。例えば、以下の各々は、式と見なされ得る：“a(bb|d?) {5, 20}c”、“(b){0, 10}”、“(b|d)”、および“b”。

## 【0021】

量化子は、“(B){n1, n2}”のような正規表現で表され、ここで、Bは、部分式であり、n1およびn2は、先行する部分式が何回出現するのを許可されるかを指定する整数である。Bは、n1およびn2によって指定された回数だけ繰り返される部分式なので、Bは、本明細書では、繰返し部分式（repeated sub-expressionion）と呼ばれる。量化子“(B){n1, n2}”と一致させるため、繰返し部分式Bは、n1～n2回、一致しなければならない。例えば、正規表現“(B){5, 7}”は、部分式Bが5、6、または7回、一致することを必要とするであろう。正規表現“A(B){n1, n2}C”では、部分式Aは、一致する場合、量化子に遷移するので、部分式Aは本明細書では、駆動式（drive expression）と呼ばれる。さらに、量化子のためのカウントの繰返しおよび増分を継続するため、量化子の繰返し部分式が連続して一致しなければならない。つまり、量化子の所与のループ中、繰返し部分式が一致しない場合、量化子が終了する。一例では、シンボル‘?’も量化子に対応し、ここで、‘?’に先行するシンボルは、1回またはゼロ回のどちらかに識別できる。

20

## 【0022】

30

図2は、量化子を有する正規表現に対応するオートマトン例200を示す。オートマトン200は、正規表現“abb? (b|c) {1, 2}”に対応する。オートマトン200は、初期状態202および最終状態212、204を含む。最終状態212、204は、図2では、二重丸で識別される。初期状態202は、最初にアクティブにされ、入力シンボル‘a’で、状態206に遷移する。状態206は、入力シンボル‘b’で、状態208および状態210の両方に遷移する。状態208は、入力シンボル‘b’で状態210に遷移し、入力シンボル‘b’または‘c’のどちらかで、状態212に遷移する。同様に、オートマトン200は、入力シンボル‘b’または‘c’のどちらかで、状態212から状態204に遷移する。状態212または状態204のどちらかのアクティブ化が、オートマトン200が対応する正規表現“abb? (b|c) {1, 2}”との一致を示すので、状態212および204は、最終状態として識別される。

40

## 【0023】

図3は、構文木をオートマトンに変換するための方法300の一例を示す。特に、方法300は、量化子を展開することにより、量化子演算子（本明細書では、単に「量化子」とも呼ぶ）をオートマトンに変換するための手段を示す。量化子を展開することは、例えば、量化子を量化子構文で書き換えること、および非量化子構文をオートマトンに変換することを含み得る。例えば、“(b|c) {1, 2}”は“(b|c)(b|c)?”と書き換えることができる。展開の利点には、結果として得られるオートマトンが有向非巡

50

回グラフ (DAG) であることを含み得、それは、対象装置内で実装するのをさらに容易にし得る。

#### 【0024】

方法300は、量化子の繰返し部分式が空値可能 (nullable) な場合に、量化子が空値不能形式に変換される、ブロック302から始まる。繰返し部分式が空値可能でない場合、方法は、量化子を変換することなく、304に進む。式が、空文字列によって一致され得る場合、式は空値可能である。例えば、式 (bc|) は、入力シンボル 'bc' または空文字列のどちらかによって一致され得る。その結果、式は空文字列によって一致できるので、式 (bc|) は空値可能である。空値可能な繰返し部分式に対応する量化子を、空値不能な繰返し部分式をもつ量化子に変換するために、繰返し部分式の空値可能な部分が取り除かれる。例えば、式 (bc|) は (bc) になる。さらに、量化子と一致させるループの数が、{n1, n2} から {0, n2} に修正される。例えば、式 "AB {n1, n2} C" が "AB' {0, n2} C" に変換され、ここで B' は B の空値不能な形式である。一例では、量化子 "a (bc|) {3, 5} d" は、"a (bc) {0, 5} d" に変換できる。10

#### 【0025】

一例では、ブロック304で、量化子が展開されるかどうかが随意に判断される。前述したように、量化子を展開することは、非量化子構文をもつ量化子を書き換えること、および非量化子構文をオートマトンに変換することを含み得る。量化子のこの書き換えの結果は、結果として生じる展開された構文が、専用状態（例えば、カウンタ）ではなく、汎用状態（例えば、状態機械要素）で実装されることである。しかし、いくつかの状況では、量化子を専用要素（例えば、カウンタ）で実装すること、従って、量化子を展開しないことが望ましくあり得る。他の状況では、量化子は展開される。量化子が展開されない場合、方法300は、その量化子に対して終了する。量化子が、少なくとも一部、展開できる場合、方法300は、ブロック306に進む。以下の条件は、量化子が、いつ、おそらくはカウンタと共に実装できるか、また、いつ、カウンタで実装されず、展開されるかの例を示す。以下のある状況は、おそらくはカウンタで実装されているとして説明されているが、他の例では、これらの状況は展開によって実装され得ることが理解されるはずである。一般に、全ての量化子は、所望であれば、展開によって実装できる。20

#### 【0026】

量化子を実装するためにカウンタが使用できるかどうかを判断する前に、£(B) が空文字を含む場合、"B {n1, n2}" の量化子が "B' {0, n2}" として書き換えられ、ここで、B' は、B の非空文字列バージョンであり、£(B') = £(B) - である。

例えば、"(bc|) {10, 20}" は "(bc) {0, 20}" と書き換えられるが、これは、これらの正規表現が全く同じデータを受け付けるからである。

#### 【0027】

1. (n1 = 0, n2 = -1) の場合、量化子は展開によって実装される。ここで、カウンタは必要ない。

2. (n1 = 1, n2 = -1) の場合、量化子は展開によって実装される。ここで、カウンタは必要ない。40

3. (n1 > 1, n2 = -1) の場合、B {n, -1} が B {n1 - 1} B + と等しいので、量化子は2つの正規表現 B {n1 - 1} および B + に分割される。量化子 B {n1 - 1} は、次いで、おそらくはカウンタで実装でき、他方 B + は、展開によって実装される。

4. (n1 = 0, n2 > 0) の場合、(B {1, n2}) ? が B {0, n2} と等しいので、量化子は (B {1, n2}) ? に修正される。空値不能な B {1, n2} が、次いで、おそらくはカウンタで実装できる。

5. (n1 > 0, n2 > 0) の場合、量化子は、おそらくは、カウンタで B {n1, n2} として実装され得る。50

要約として、おそらくは、修正することなく、カウンタで実装できる量化子は、 $B \{ n_1, n_2 \}$ として記述でき、ここで、 $B$ は空値可能でなく、 $n_1 > 0$ 、 $n_2 > 0$ 、および $n_1 = n_2$ である。

#### 【0028】

ブロック306で、单一のある個数のループと一致し得る量化子は、連続的にリンクされた、複数の繰返し部分式を有するオートマトンを形成するように展開される。单一のある個数のループを有する量化子は、 $n_1$ が $n_2$ に等しい量化子に対応する。例えば、量化子“ $B \{ n_1 \}$ ”は、 $B$ の $n_1$ 個のコピーを有する、“ $B B \dots B$ ”として展開できる。

#### 【0029】

ブロック308で、 $n_1$ が $n_2$ と等しくない場合、および $n_1$ が1と等しく、かつ $n_2$ が1より大きい場合、複数のある個数のループと一致できる量化子が展開される。 $n_1$ が1より大きい場合、量化子は、 $n_1 - 1$ 個のループと一致できる第1の量化子、および1から $n_2 - n_1 + 1$ 個のループと一致できる第2の量化子に分割される。例えば、量化子 $B \{ n_1, n_2 \}$ (ここで、 $n_1 > 1$ 、 $n_2 > 1$ 、および $n_1 < n_2$ )は複数のある個数のループ、特に、 $n_1$ から $n_2$ 個までのループと一致できる。この量化子、 $B \{ n_1, n_2 \}$ は、以下の量化子 $B \{ n_1 - 1 \} B \{ 1, n_2 - n_1 + 1 \}$ に分割できる。第1の量化子は、 $n_1 - 1$ に等しい、いくつかのループに一致できる繰返し部分式 $B$ である。この第1の量化子は、1から $n_2 - n_1 + 1$ までのいくつかのループによって一致できる繰返し部分式を有する第2の量化子と連結される。第1の量化子 $B \{ n_1 - 1 \}$ は、306で記述されるように展開される。

10

#### 【0030】

第2の量化子 $B \{ 1, n_2 - n_1 + 1 \}$ は、結果として生じるオートマトンの入次数(*in-degree*)および/または出次数(*out-degree*)に基づいて展開できる。量化子の展開では、多数の入次数または多数の出次数を有する状態を作成できる。一例では、入次数はオートマトンの状態への遷移数に対応し、出次数はオートマトンの状態からの遷移数に対応する。その結果、第2の量化子は、第2の量化子をオートマトンに変換する際に、状態への遷移(入次数)または状態からの遷移(出次数)を制御するよう展開できる。例えば、量化子は、各展開された状態の入次数を閾値数未満に制限するよう展開できる。入次数の制限は、例えば、対象装置内の要素の態様および/または制限を考慮に入れるように実行できる。さらに、展開中に入次数を制限すると、コンパイラのために、以降の処理を削減できる。

20

#### 【0031】

一例では、量化子 $B \{ 1, n_2 - n_1 + 1 \}$ を展開する際に、入次数と出次数との間のトレードオフとしてオートマトンが生成される。その結果、入次数を減らすと出次数が増加し得、また、出次数を減らすと入次数が増加し得る。一例では、量化子 $B \{ 1, n_2 - n_1 + 1 \}$ のループ構造を展開するため、展開された状態への、または展開された状態からのどちらかの、いくつかの遷移が作成されて、オートマトンが連結された $B$ の任意の文字列 $k$ (ここで、 $1 \leq k \leq n_2 - n_1 + 1$ )を受け入れるようにする。展開された状態への遷移、または展開された状態からの遷移が作成されるかの制御は、オートマトンに対する入次数/出次数を制御するために使用できる。

30

#### 【0032】

方法300は、单一の量化子に対応するものとして説明されているが、方法300は、構文木内の複数の量化子に対して繰り返すことができ、結果として生じる別個のオートマトンが、次いで、さらに大きなオートマトンにリンクできる。

#### 【0033】

図4Aは、式 $A B \{ 1, 4 \}$ が入次数を最小限にするように展開されるオートマトン400の一例を示す。入次数を最小限にするように展開された量化子から生じたオートマトンは、本明細書では、散乱パターン(scatter pattern)とも呼ばれる。式 $A B \{ 1, 4 \}$ の展開されたバージョンの散乱パターンは、式 $A (( ( B ? ) B ) ?$

40

50

B ) ? B ) に直接対応し、それにオートマトン 400 が対応する。オートマトン 400 は、量化子 B { 1 , 4 } に対する駆動状態 402 および、量化子 の第 1 の状態 404 および量化子 の最終状態 408 を含め、複数の展開された状態 404 ~ 408 を含む。一例では、式 A および B の各々は、図示されていない、もっと小さいオートマトンに対する複数の状態に対応できる。オートマトン 400 の入次数を最小限にするために、量化子 に対する遷移が、第 1 の状態 404 から他の展開された状態 405 ~ 408 への出遷移 (out-transition) として割り当てられる。その結果、第 1 の状態 404 は、多数の出次数 (4 つの出遷移) を有し、また、全ての量化子 状態 404 ~ 408 が少ない入次数 (1 つまたは 2 つの入遷移) を有する。

## 【0034】

10

図 4B は、式 A B { 1 , 4 } が出次数を最小限にするように展開されるオートマトン 410 の一例を示す。出次数を最小限にするように展開された量化子 から生じたオートマトンは、本明細書では、マージパターン (merge pattern) とも呼ばれる。式 A B { 1 , 4 } の展開されたバージョンのマージパターンは、展開された式 A B ( B ( B ( B ) ? ) ? ) ? に直接対応する。オートマトン 408 は、状態 402 、 404 ~ 408 の間で異なる遷移をもつオートマトン 400 と同じ状態 402 、 404 ~ 408 を含む。オートマトン 410 の出次数を最小限にするために、量化子 に対する遷移が、量化子 の最終状態 408 への入遷移 (in-transition) として割り当てられる。入遷移は、展開された状態 404 ~ 407 の各々から来る。その結果、量化子 状態 404 ~ 408 の全ては少ない出次数 (1 つまたは 2 つの出遷移) を有するが、量化子 の最終状態 408 は多数の入次数 (4 つの入遷移) を有する。

20

## 【0035】

一例では、量化子 を有する式は、出次数または入次数のうちの 1 つを閾値未満に制限するように展開される。一例では、式 A B { 1 , n1 } を、入次数を閾値に制限するように展開するために、量化子 B { 1 , n1 } に対する閾値までのいくつかの遷移を、入遷移として、量化子 B { 1 , n1 } の最終状態に割り当てる事ができ、また、他の遷移を、出遷移として、量化子 B { 1 , n1 } の第 1 の状態に対して割り当てる事ができる。逆に、式 A B { 1 , n1 } を、出次数を閾値に制限するように展開するために、量化子 B { 1 , n1 } に対する閾値までのいくつかの遷移を、出遷移として、量化子 に対する第 1 の状態に割り当てる事ができ、また、他の遷移を、出遷移として、量化子 B { 1 , n1 } の最終状態に対して割り当てる事ができる。

30

## 【0036】

図 4C は、式 A B { 1 , 4 } が、任意の状態に対する入遷移を 3 以下に制限するように展開されるオートマトン 412 の別の例を示す。オートマトン 412 は、状態 402 、 404 ~ 408 の間で異なる遷移をもつオートマトン 400 および 408 と同じ状態 402 、 404 ~ 408 を含む。一例では、オートマトン 412 の入次数を 3 以下の入遷移に制限するために、量化子 に対する遷移が、最初は、量化子 B { 1 , 4 } の最終状態 408 への入遷移として、制限の 3 に達するまで割り当てられ、また、他の遷移が、量化子 状態 404 ~ 408 からの出遷移として割り当てる。従って、量化子 の最終状態 408 ならびに他の量化子 状態 404 ~ 407 が、制限の 3 つ以下の入次数を有し、また、第 1 の状態 404 が 3 つの出次数を有する。

40

## 【0037】

他の例では、式の入次数および出次数は、互いを特定の割合 (例えば、1 対 1 、 2 対 1 ) に設定できる。さらに別の例では、式の入次数および出次数は、入遷移または出遷移のどちらかに対して閾値に達するまで、互いを特定の割合に設定でき、次いで、別の割合が使用できるか、または遷移の全てが、それぞれ入遷移または出遷移として割り当られる。

## 【0038】

## 〔実施形態例〕

図 5 ~ 15 に関連した以下の説明は、並列マシン内に、制限された入次数および / また

50

は出次数をもつオートマトンを実装する実施形態例に関する。図5～図9に関連した説明は、量化子を実装するための並列マシン例に関し、また、図10～図14に関連した説明は、量化子を実装する並列マシンをプログラムするための機械コードを生成するコンパイラ例に関する。

#### 【0039】

図5は、データ分析用の階層構造を実装するために使用できる並列マシン500の例を示す。並列マシン500は、入力データを受信し、その入力データに基づいて出力を提供できる。並列マシン500は、入力データを受信するためのデータ入力ポート510および出力を別の装置に提供するための出力ポート514を含むことができる。データ入力ポート510は、並列マシン500に入力されるデータ用のインターフェースを提供する。

10

#### 【0040】

並列マシン500は、汎用要素502および専用要素512を含む、複数のプログラム可能要素を含む。汎用要素502は、1つまたは複数の入力504および1つまたは複数の出力506を含み得る。汎用要素502は、複数の状態のうちの1つにプログラムされ得る。汎用要素502の状態は、汎用要素502が、所与の入力に基づいて、何の出力を提供するかを決定する。すなわち、汎用要素502の状態は、プログラム可能要素が所与の入力に基づいてどのように反応するかを決定する。データ入力ポート510に対するデータ入力は、汎用要素502にそれに対する処置を取らせるため、複数の汎用要素502に提供され得る。汎用要素502の例には、以下で詳細に説明する状態機械要素(SME)、および構成可能論理ブロックを含むことができる。一例では、SMEは、所与の入力がデータ入力ポート510で受信される場合に、特定の出力(例えば、高信号つまり「1」信号)を提供するため、所与の状態に設定され得る。所与の入力以外の入力がデータ入力ポート510で受信される場合、SMEは異なる出力(例えば、低信号つまり「0」信号)を提供し得る。一例では、構成可能論理ブロックは、データ入力ポート510で受信された入力に基づいて、ブール論理関数(例えば、AND、OR、NORなど)を実行するように設定できる。

20

#### 【0041】

並列マシン500は、プログラム(例えば、イメージ)を並列マシン500上にロードするためのプログラミングインターフェース511も含むことができる。イメージは、汎用要素502の状態をプログラム(例えば、設定)できる。すなわち、イメージは、所与の入力に対して特定の方法で反応するように汎用要素502を構成できる。例えば、汎用要素502は、文字'a'がデータ入力ポート510で受信される場合、高信号を出力するように設定できる。いくつかの例では、並列マシン500は、汎用要素502の動作のタイミングを制御するためのクロック信号を使用できる。ある例では、並列マシン500は、汎用要素502とやりとりするため、および専用機能を実行するために、専用要素512(例えば、RAM、論理ゲート、カウンタ、ルックアップテーブルなど)を含むことができる。いくつかの実施形態では、データ入力ポート510で受信されるデータは、長い時間をかけて、もしくは一度にそろって受信されたデータの一定のセット、または長い時間をかけて受信されたデータのストリームを含むことができる。データは、並列マシン500に結合された、データベース、センサー、ネットワークなどの任意のソースから受信され得るか、または生成され得る。

30

#### 【0042】

並列マシン500は、並列マシン500の異なる要素(例えば、汎用要素502、データ入力ポート510、出力ポート514、プログラミングインターフェース511、および専用要素512)を選択的に共に結合するための複数のプログラム可能スイッチ508も含む。その結果、並列マシン500は、要素間で形成されたプログラム可能マトリックス(programmable matrix)を含む。一例では、汎用要素502の入力504、データ入力ポート510、プログラミングインターフェース511、または専用要素512が、1つまたは複数のプログラム可能スイッチ508を通して、汎用要素502の出力506、出力ポート514、プログラミングインターフェース511、または専用要

40

50

素 5 1 2 に結合できるように、プログラム可能スイッチ 5 0 8 が、2つ以上の要素を選択的に互いに結合できる。従って、要素間の信号のルーティングが、プログラム可能スイッチ 5 0 8 を設定することによって制御できる。図 5 は、所与の要素とプログラム可能スイッチ 5 0 8 との間の特定数の導体（例えば、ワイヤー）を示しているが、他の例では、異なる数の導体が使用できることが理解されるはずである。また、図 5 は、個別にプログラム可能スイッチ 5 0 8 に結合された各汎用要素 5 0 2 を示しているが、他の例では、複数の汎用要素 5 0 2 がグループ（例えば、図 8 に示すような、ブロック 8 0 2）としてプログラム可能スイッチ 5 0 8 に結合できる。一例では、データ入力ポート 5 1 0、データ出力ポート 5 1 4、および／またはプログラミングインターフェース 5 1 1 はレジスタとして実装でき、レジスタへの書き込みが、それぞれの要素へデータを提供するか、またはそれぞれの要素からデータを提供するようになる。

#### 【 0 0 4 3 】

一例では、単一の並列マシン 5 0 0 が物理デバイス上に実装されるが、他の例では、2つ以上の並列マシン 5 0 0 が単一の物理デバイス（例えば、物理チップ）上に実装できる。一例では、複数の並列マシン 5 0 0 の各々が、別個のデータ入力ポート 5 1 0、別個の出力ポート 5 1 4、別個のプログラミングインターフェース 5 1 1、および汎用要素 5 0 2 の別個のセットを含むことができる。さらに、汎用要素 5 0 2 の各セットは、それらの対応する入力データポート 5 1 0 でデータに反応（例えば、高信号または低信号を出力）できる。例えば、第 1 の並列マシン 5 0 0 に対応する汎用要素 5 0 2 の第 1 のセットは、第 1 の並列マシン 5 0 0 に対応する第 1 のデータ入力ポート 5 1 0 でデータに反応できる。第 2 の並列マシン 5 0 0 に対応する汎用要素 5 0 2 の第 2 のセットは、第 2 の並列マシン 5 0 0 に対応する第 2 のデータ入力ポート 5 1 0 に反応できる。その結果、各並列マシン 5 0 0 は、1 セットの汎用要素 5 0 2 を含み、異なるセットの汎用要素 5 0 2 は、異なる入力データに反応できる。同様に、各並列マシン 5 0 0、および汎用要素 5 0 2 の各対応するセットは、別個の出力を提供できる。いくつかの例では、第 2 の並列マシン 5 0 0 に対する入力データが、第 1 の並列マシン 5 0 0 からの出力データを含むことができるように、第 1 の並列マシン 5 0 0 からの出力ポート 5 1 4 が、第 2 の並列マシン 5 0 0 の入力ポート 5 1 0 に結合できる。

#### 【 0 0 4 4 】

一例では、並列マシン 5 0 0 上にロードするためのイメージは、汎用要素 5 0 2 の状態を設定するため、プログラム可能スイッチ 5 0 8 をプログラミングするため、および並列マシン 5 0 0 内で専用要素 5 1 2 を構成するための複数のビットの情報を含む。一例では、ある入力に基づいて所望の出力を提供するように並列マシン 5 0 0 をプログラムするために、イメージが並列マシン 5 0 0 上にロードできる。出力ポート 5 1 4 は、データ入力ポート 5 1 0 での汎用要素 5 0 2 のデータに対する反応に基づいて、並列マシン 5 0 0 からの出力を提供できる。出力ポート 5 1 4 からの出力は、所与のパターンの一一致を示す单一ビット、複数のパターンに対する一致および不一致を示す複数のビットを含むワード（word）、ならびに所与の時に全てまたは特定の汎用要素 5 0 2 の状態に対応する状態ベクトルを含むことができる。

#### 【 0 0 4 5 】

並列マシン 5 0 0 に関する使用例には、パターン認識（例えば、音声認識、画像認識など）、信号処理、画像処理、コンピュータビジョン、暗号化、およびその他を含む。ある例では、並列マシン 5 0 0 は、有限状態機械（FSM）エンジン、フィールドプログラマブルゲートアレイ（FPGA）、およびそれらの変形を含むことができる。さらに、並列マシン 5 0 0 は、コンピュータ、ポケットベル、携帯電話、電子手帳、携帯音楽プレーヤ、ネットワーク装置（例えば、ルータ、ファイアウォール、スイッチ、またはそれらの任意の組合せ）、制御回路、カメラなどの、大きな装置内のコンポーネントであり得る。

#### 【 0 0 4 6 】

図 6 ~ 図 9 は、本明細書で「FSM エンジン 6 0 0」と称する並列マシンの一例を示す。一例では、FSM エンジン 6 0 0 は、有限状態機械のハードウェア実装を含む。その結

10

20

30

40

50

果、FSMエンジン600は、FSM内の複数の状態に対応する、複数の選択的に結合可能なハードウェア要素（例えば、プログラム可能要素）を実装する。FSM内の状態と同様に、ハードウェア要素は、入力ストリームを分析し、その入力ストリームに基づいて下流のハードウェア要素をアクティブにできる。

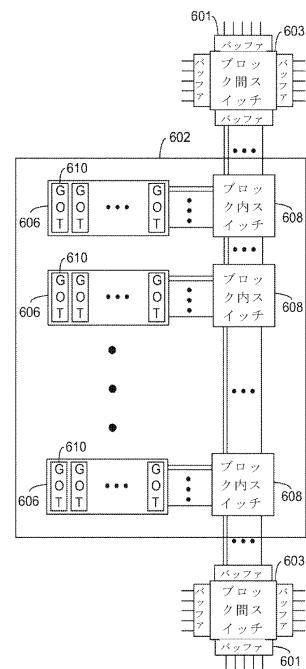

#### 【0047】

FSMエンジン600は、汎用要素および専用要素を含む、複数のプログラム可能要素を含む。汎用要素は、多数の異なる機能を実装するようにプログラムされ得る。これらの汎用要素は、行(row)606（図7および図8に示す）およびブロック602（図6および図7に示す）に階層的に編成されているSME604、605（図9に示す）を含む。階層的に編成されたSME604、605間で信号をルーティングするために、ブロック間スイッチ603（図6および図7に示す）、ブロック内スイッチ608（図7および図8に示す）、ならびに行内(intra-row)スイッチ612（図8に示す）を含む、プログラム可能スイッチの階層が使用される。SME604、605は、FSMエンジン600によって実装されたFSMの状態に対応できる。SME604、605は、以下で説明するように、プログラム可能スイッチの使用によって共に結合できる。その結果、FSMは、状態の機能に対応するようにSME604、605をプログラミングすることにより、また、FSM内の状態間の遷移に対応するため、SME604、605を選択的に共に結合することにより、FSMエンジン600上に実装できる。

#### 【0048】

図6は、FSMエンジン例600の全体図を示す。FSMエンジン600は、プログラム可能ブロック間スイッチ603と選択的に共に結合できる複数のブロック602を含む。さらに、ブロック602は、信号（例えば、データ）を受信するため、およびデータをブロック602に提供するために、入力ブロック609（例えば、データ入力ポート）に選択的に結合できる。ブロック602は、ブロック602から外部デバイス（例えば、別のFSMエンジン600）に信号を提供するために、出力ブロック613（例えば、出力ポート）にも選択的に結合できる。FSMエンジン600は、プログラム（例えば、イメージ）をFSMエンジン600上にロードするために、プログラミングインターフェース611も含み得る。イメージは、SME604、605の状態をプログラム（設定）できる。すなわち、イメージは、入力ブロック609で所与の入力に対して特定の方法で反応するように、SME604、605を構成できる。例えば、SME604は、入力ブロック609で文字‘a’が受信される場合、高信号を出力するように設定できる。

#### 【0049】

一例では、入力ブロック609、出力ブロック613、および／またはプログラミングインターフェース611はレジスタとして実装でき、そのレジスタへの書き込みがそれぞれの要素に対して、またはそれぞれの要素から、データを提供できるようにする。その結果、プログラミングインターフェース611に対応するレジスタ内に格納されているイメージからのビットが、SME604、605上にロードできる。図6は、ブロック602、入力ブロック609、出力ブロック613、およびブロック間スイッチ603の間に特定数の導体（例えば、ワイヤ、線）を示しているが、他の例では、もっと少ないかまたは多い導体が使用できることが理解されるはずである。

#### 【0050】

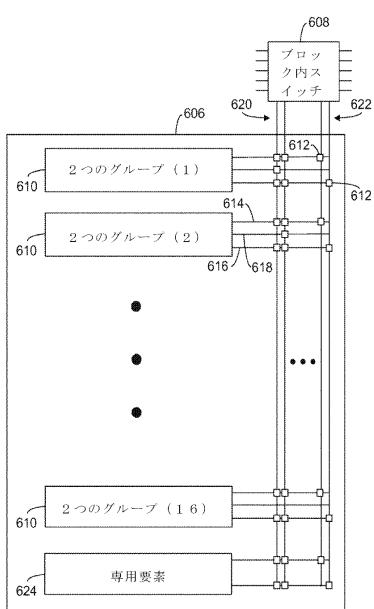

図7は、ブロック602の一例を示す。ブロック602は、プログラム可能ブロック内スイッチ608と選択的に共に結合できる複数の行606を含むことができる。その結果、行606は、ブロック間スイッチ603で、別のブロック602内の別の行606と選択的に結合できる。一例では、バッファ601は、ブロック間スイッチ603への／ブロック間スイッチ603からの信号のタイミングを制御するために含まれる。行606は、本明細書で2つのグループ(GOT:group of tow)610として参照される要素のペアに編成された複数のSME604、605を含む。一例では、ブロック602は、16個の行606を含む。

#### 【0051】

10

20

30

40

50

図8は、行606の一例を示す。GOT 610は、プログラム可能行内スイッチ612によって、行606内の他のGOT 610および任意の他の要素624と選択的に結合できる。また、GOT 610は、ブロック内スイッチ608で他の行606内の他のGOT 610と、またはブロック間スイッチ603で他のブロック602内の他のGOT 610とも結合できる。一例では、GOT 610は、第1および第2の入力614、616ならびに出力618を有する。第1の入力614は、GOT 610の第1のSME 604と結合され、第2の入力614は、GOT 610の第2のSME 604と結合される。

#### 【0052】

一例では、行606は、第1および第2の複数の行相互接続導体620、622を含む。一例では、GOT 610の入力614、616は、1つまたは複数の行相互接続導体620、622に結合でき、出力618は、1つの行相互接続導体620、622に結合できる。一例では、第1の複数の行相互接続導体620は、行606内の各GOT 610の各SME 604に結合できる。第2の複数の行相互接続導体622は、行606内の各GOT 610の1つのSME 604に結合できるが、そのGOT 610の他のSME 604には結合できない。一例では、第2の複数の行相互接続導体622の半分の第1の方が、行606内のSME 604の半分の第1の方（各GOT 610からの1つのSME 604）と結合でき、第2の複数の行相互接続導体622の半分の第2の方が、行606内のSME 604の半分の第2の方（各GOT 610からの他のSME 604）と結合できる。第2の複数の行相互接続導体622とSME 604、605との間の制限された接続性は、本明細書では「パリティ」と呼ばれる。

#### 【0053】

一例では、行606は、カウンタ、プログラム可能プール論理要素、フィールドプログラマブルゲートアレイ（FPGA）、特定用途向け集積回路（ASIC）、プログラム可能プロセッサ（例えば、マイクロプロセッサ）、および他の要素などの、専用要素624も含むことができる。追加として、一例では、専用要素624は、異なる行606内では異なる。例えば、ブロック602内の4つの行606が、専用要素624としてプール論理を含むことができ、ブロック602内の他の8つの行606が、専用要素624としてカウンタを含むことができる。

#### 【0054】

一例では、専用要素624は、カウンタ（本明細書ではカウンタ624とも呼ばれる）を含む。一例では、カウンタ624は、12ビットのプログラマブル減算カウンタを含む。12ビットのプログラマブルカウンタ624は、カウント入力、リセット入力、およびゼロカウント出力を有する。カウント入力は、アサート時に、カウンタ624の値を1だけ減算する。リセット入力は、アサート時に、カウンタ624に、関連したレジスタから初期値をロードさせる。12ビットのカウンタ624に対して、最大で12ビット数が初期値としてロードできる。カウンタ624の値がゼロ（0）に減算されると、ゼロカウント出力がアサートされる。カウンタ624は、少なくとも2つのモード、パルスおよび保留（hold）を有する。カウンタ624がパルスモードに設定されている場合、カウンタ624がゼロに減算されると、第1のクロック周期中にゼロカウント出力がアサートされ、また、次のクロック周期では、たとえカウント入力がアサートされても、ゼロカウント出力はもはやアサートされない。この状態は、カウンタ624が、アサートされているリセット入力によってリセットされるまで、継続する。カウンタ624が保留モードに設定されている場合、カウンタ624がゼロに減算されると、第1のクロック周期中にゼロカウント出力がアサートされ、また、カウント入力がアサートされる場合、カウンタ624が、アサートされているリセット入力によってリセットされるまで、アサートされたままである。

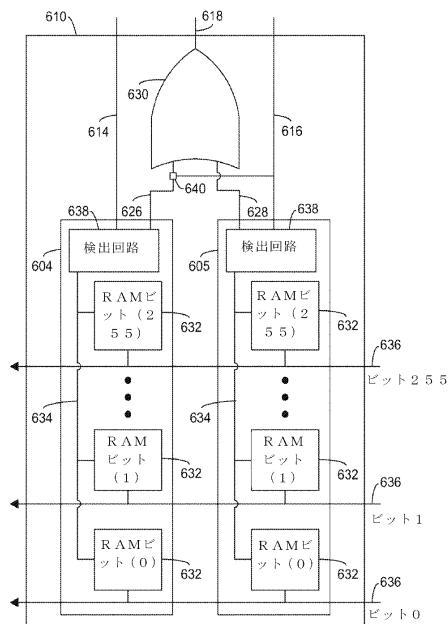

#### 【0055】

図9は、GOT 610の一例を示す。GOT 610は、入力614、616を有し、かつそれらの出力626、628がORゲート630に結合されている、第1および第2

10

20

30

40

50

のSME 604、605を含む。出力626、628は、GOT 610の共通の出力618を形成するため、ORゲート630で共に論理ORされる。一例では、第1および第2のSME 604、605はパリティを示し、そこで、第1のSME 604の入力614は、行相互接続導体622のいくつかに結合でき、第2のSME 605の入力616は、他の行相互接続導体622に結合できる。一例では、GOT 610内の2つのSME 604、605は、第1のSME 604の出力626を第2のSME 605の入力616に結合するために、スイッチ640を設定することにより、カスケード接続できる。

#### 【0056】

一例では、状態機械要素604、605は、検出線634と平行に結合された、ダイナミックランダムアクセスメモリ(DRAM)でしばしば使用されるような、複数のメモリセル632を含む。1つのかかるメモリセル632は、高値または低値(例えば、1または0)のいずれかに対応するものなどの、データ状態に設定できるメモリセルを含む。メモリセル632の出力は、検出線634に結合され、メモリセル632への入力は、データストリーム線636上のデータに基づいて、信号を受信する。一例では、データストリーム線636上の入力が、メモリセル632の1つを選択するために復号される。選択されたメモリセル632は、その格納されたデータ状態を出力として検出線634上に提供する。例えば、データ入力ポート609で受信されたデータがデコーダ(図示せず)に提供でき、デコーダは、データストリーム線636のうちの1本を選択できる。一例では、デコーダは、ASCII文字を256ビットのうちの1つに変換できる。

#### 【0057】

メモリセル632は、それ故、メモリセル632が高値に設定され、かつ、データストリーム線636上のデータがメモリセル632に対応する場合、高信号を検出線634に出力する。データストリーム線636上のデータがメモリセル632に対応し、メモリセル632が低値に設定されている場合、メモリセル632は、低信号を検出線634に出力する。メモリセル632からの検出線634上への出力は、検出回路638によって検知される。一例では、入力線614、616上の信号は、それぞれの検出回路638をアクティブ状態または非アクティブ状態のいずれかに設定する。非アクティブ状態に設定されると、検出回路638は、それぞれの検出線634上の信号にかかわらず、低信号をそれぞれの出力626、628上に出力する。アクティブ状態に設定されると、高信号がそれぞれのSME 604、605のメモリセル634の1つから検出される場合、検出回路638は、高信号をそれぞれの出力線626、628上に出力する。アクティブ状態にある場合、それぞれのSME 604、605のメモリセル634の全てからの信号が低ければ、検出回路638は、低信号をそれぞれの出力線626、628上に出力する。

#### 【0058】

一例では、SME 604、605は、256のメモリセル632を含み、各メモリセル632は、異なるデータストリーム線636に結合される。それ故、SME 604、605は、選択された1つまたは複数のデータストリーム線636がその上に高信号を有する場合、高信号を出力するようにプログラムされ得る。例えば、SME 604は、第1のメモリセル632(例えば、ビット0)を高に設定し、他の全てのメモリセル632(例えば、ビット1~255)を低に設定できる。それぞれの検出回路638がアクティブ状態にあるとき、SME 604は、ビット0に対応するデータストリーム線636がその上に高信号を有する場合、高信号を出力626上に出力する。他の例では、複数のデータストリーム線636のうちの1本が、適切なメモリセル632を高値に設定することにより、その上に高信号を有する場合、SME 604は、高信号を出力するように設定できる。

#### 【0059】

一例では、メモリセル632は、関連したレジスタからビットを読み取ることにより、高値または低値に設定できる。その結果、SME 604は、コンパイラによって作成されたイメージをレジスタ内に格納し、レジスタ内のビットを関連したメモリセル632に

10

20

30

40

50

ロードすることにより、プログラムされ得る。一例では、コンパイラによって作成されたイメージは、高および低（例えば、1および0）ビットのバイナリイメージを含む。イメージは、SME 604、605をカスケード接続することにより、FSMエンジン600をFSMとして動作するようにプログラムできる。例えば、第1のSME 604は、検出回路638をアクティブ状態に設定することにより、アクティブ状態に設定できる。第1のSME 604は、ビット0に対応するデータストリーム線636がその上に高信号を有する場合、高信号を出力するように設定できる。第2のSME 605は、最初は非アクティブ状態に設定できるが、アクティブなとき、ビット1に対応するデータストリーム線636がその上に高信号を有する場合、高信号を出力するように設定できる。第1のSME 604および第2のSME 605は、第1のSME 604の出力626を第2のSME 605の入力616に結合するように設定することにより、カスケード接続できる。従って、高信号が、ビット0に対応するデータストリーム線636上で検知される場合、第1のSME 604は、高信号を出力626上に出力し、第2のSME 605の検出回路638をアクティブ状態に設定する。高信号が、ビット1に対応するデータストリーム線636上で検知される場合、第2のSME 605は、別のSME 605をアクティブにするため、またはFSMエンジン600からの出力のため、高信号を出力628上に出力する。

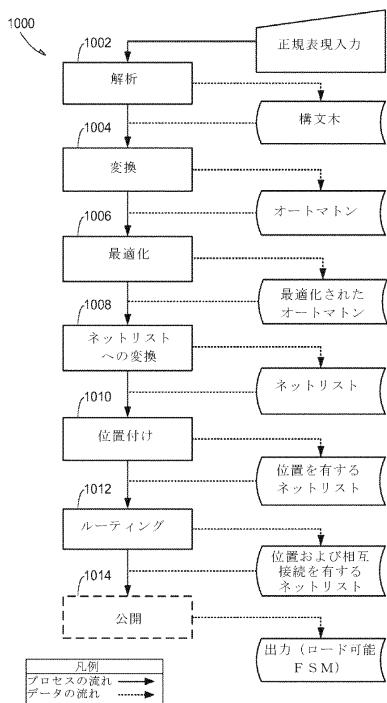

#### 【0060】

図10は、コンパイラがソースコードを、並列マシンをプログラムするように構成されたイメージに変換するための方法1000の一例を示す。方法1000は、ソースコードを構文木に解析すること（ブロック1002）、構文木をオートマトンに変換すること（ブロック1004）、オートマトンを最適化すること（ブロック1006）、オートマトンをネットリストに変換すること（ブロック1008）、ネットリストをハードウェア上に配置すること（ブロック1010）、ネットリストをルーティングすること（ブロック1012）、および結果として生じるイメージを公開すること（ブロック1014）を含む。

#### 【0061】

一例では、コンパイラは、ソフトウェア開発者がFSMエンジン600上でFSMを実装するために、イメージを作成できるようにする、アプリケーションプログラミングインターフェース（API）を含む。コンパイラは、正規表現の入力セットを、FSMエンジン600をプログラムするように構成されているイメージに変換するための方法を提供する。コンパイラは、フォンノイマン型アーキテクチャを有するコンピュータ用の命令によって実装できる。これらの命令は、コンピュータ上のプロセッサにコンパイラの機能を実装させることができる。例えば、命令は、プロセッサによって実行される場合、プロセッサがアクセス可能なソースコード上のブロック1002、1004、1006、1008、1010、1012、および1014に記載する動作をプロセッサに実行させることができる。フォンノイマン型アーキテクチャを有するコンピュータ例が図15に示され、以下で説明される。

#### 【0062】

ブロック1002で、構文木を形成するためにソースコードが解析される。解析することで、図3に関して上述したように、ソースコードの一般的な表現が作成される。さらに、解析することで、FSMエンジン600によってサポートされている正規表現、およびサポートされていない正規表現を考慮に入れることができる。サポートされている正規表現は、適切な機械コード実装に変換できるが、サポートされていない正規表現は、例えば、エラーを生じ得るか、または、機能において、サポートされていない正規表現に近い、サポートされた機械コードに変換され得る。

#### 【0063】

ブロック1004で、構文木は、オートマトンに変換される。図3に関連して前述したように、構文木の変換は、構文木を、複数の状態を含むオートマトンに変換する。一例では、オートマトンは、FSMエンジン600のハードウェアに一部基づいて、変換され得

る。

#### 【0064】

一例では、オートマトンに対する入力シンボルは、アルファベット、0～9の数字、および他の印刷可能な文字のシンボルを含む。一例では、入力シンボルは、バイト値0～255で表される。一例では、オートマトンは、グラフのノードが状態の集合に対応する有向グラフとして表され得る。一例では、入力シンボル  $(p, \cdot)$  を受けての状態  $p$  から状態  $q$  への遷移、すなわち、 $(p, \cdot)$  は、ノード  $p$  からノード  $q$  への有向接続によって示される。

#### 【0065】

一例では、オートマトンは、汎用状態ならびに専用状態を含む。汎用状態および専用状態は、コンパイラがそれに対して機械コードを生成している対象装置によってサポートされる汎用要素および専用要素に対応する。異なるタイプの対象装置は、異なるタイプの汎用要素ならびに1つまたは複数の異なるタイプの専用要素をサポートできる。汎用要素は、通常、幅広い範囲の機能を実装するために使用でき、他方、専用要素は、通常、もっと狭い範囲の機能を実装するために使用できる。しかし、一例では、専用要素は、例えば、その狭い範囲の機能内でより大きな効果を得ることができる。その結果、専用要素は、例えば、対象装置において特定の機能を実装するために必要なマシンサイクルまたはマシンリソースを削減するために使用できる。いくつかの例では、対象装置は、単に専用要素をサポートし、そこで、複数の異なるタイプの専用要素がサポートされる。

#### 【0066】

コンパイラがFSMエンジン600に対して機械コードを生成している例では、汎用状態はSME 604、605に対応でき、汎用状態はそれに応じて本明細書では「SME状態」と呼ばれる。さらに、コンパイラがFSMエンジン600に対して機械コードを生成している場合、専用状態は、カウンタ624に対応でき、それに応じて本明細書では「カウンタ状態」と呼ばれる。一例では、オートマトン内のSME状態は、SMEにマッピングしないオートマトンの開始状態を除いて、FSMエンジン600内のSME（例えば、SME 604、605）に1：1でマッピングする。カウンタ624は、カウンタ状態に1：1でマッピングすることもあれば、しないこともある。

#### 【0067】

一例では、入力シンボル範囲外の特別な遷移シンボルが、オートマトン内で使用され得る。これらの特別な遷移シンボルは、例えば、専用要素224の使用を可能にするために使用できる。さらに、特別な遷移シンボルは、入力シンボル以外の何かを受けて起こる遷移を提供するために使用できる。例えば、特別な遷移シンボルは、第2の状態および第3の状態の両方が有効な場合に、第1の状態が有効にされる（例えば、遷移される）ことを示し得る。その結果、第1の状態は、第2の状態および第3の状態の両方がアクティブにされる場合にアクティブにされ、また、第1の状態への遷移は、入力シンボルに直接依存しない。特に、第2の状態および第3の状態の両方が有効な場合に、第1の状態が有効にされることを示す特別な遷移シンボルは、例えば、専用要素224としてのブール論理によって実行されるブールAND関数を表すために使用できる。一例では、特別な遷移シンボルは、カウンタ状態がゼロに達したこと、従って下流の状態への遷移を示すために使用できる。

#### 【0068】

一例では、オートマトンは、グルシコフの方法などの、標準的な方法の1つを使用して構築できる。一例では、オートマトンは、 $\neg$ のない（-free）均質な（homogeneous）オートマトンであり得る。構文木のオートマトンへの変換に関するさらなる詳細は、以下で、図3、図4A～図4C、図11A、図11B、図12、図13、および図14に関連して提供される。

#### 【0069】

ブロック1006で、構文木がオートマトンに変換されると、オートマトンが最適化される。オートマトンは、とりわけ、その複雑性およびサイズを縮小するように最適化され

10

20

30

40

50

得る。オートマトンは、重複する状態を結合することにより最適化できる。

#### 【0070】

ブロック1008で、最適化されたオートマトンがネットリストに変換される。オートマトンをネットリストに変換することは、オートマトンの各状態をFSMエンジン600上のハードウェア要素（例えば、SME 604、605、専用要素624）のインスタンスにマッピングする。また、インスタンス間の接続が、ネットリストを作成するために決定される。

#### 【0071】

ブロック1010で、ネットリストの各インスタンスに対応する、対象装置の特定のハードウェア要素（例えば、SME 604、605、専用要素624）を選択するために、ネットリストが位置付けられる。一例では、位置付けされると、FSMエンジン600に対する一般入力および出力制約に基づいて、各特定のハードウェア要素が選択される。10

#### 【0072】

ブロック1012で、ネットリストによって記述された接続を達成するために、選択されたハードウェア要素を共に結合するため、位置付けられたネットリストが、プログラム可能スイッチ（例えば、ブロック間スイッチ603、ブロック内スイッチ608、および行内スイッチ612）に対する設定を決定するようにルーティングされる。一例では、プログラム可能スイッチに対する設定が、選択されたハードウェア要素を接続するために使用されるFSMエンジン600の特定の導体を決定することにより決定される。ルーティングは、ブロック1010で位置付けるハードウェア要素間の接続のさらに詳しい制限を考慮に入れることができる。その結果、ルーティングは、FSMエンジン600上の導体の実際の制限を前提として、適切な接続を行うために、グローバルな位置付けによって決定された通りに、いくつかのハードウェア要素の位置付けを調整し得る。20

#### 【0073】

ネットリストが位置付けられルーティングされると、位置付けられルーティングされたネットリストは、FSMエンジン200のプログラミング用に複数のビットに変換できる。複数のビットはここではイメージと呼ばれる。

#### 【0074】

ブロック1014で、イメージがコンパイラによって公開される。イメージは、FSMエンジン600の特定のハードウェア要素および/またはプログラム可能スイッチをプログラミングするための複数のビットを含む。イメージが複数のビット（例えば、0および1）を含む実施形態では、イメージは、バイナリイメージと呼ぶことができる。ビットは、プログラム化されたFSMエンジン600が、ソースコードによって記述された機能を有するFSMを実装するように、SME 604、605の状態、専用要素624、およびプログラム可能スイッチをプログラムするためにFSMエンジン600上にロードできる。位置付け（ブロック1010）およびルーティング（ブロック1012）は、特定のハードウェア要素をFSMエンジン600内の特定の位置で、オートマトン内の特定の状態にマッピングできる。その結果、イメージ内のビットは、特定のハードウェア要素および/またはプログラム可能スイッチを所望の機能を実装するようにプログラムできる。一例では、イメージは、機械コードをコンピュータ可読媒体に保存することにより公開できる。別の例では、イメージは、イメージをディスプレイ装置上に表示することにより公開できる。さらに別の例では、イメージは、イメージをFSMエンジン600上にロードするためのプログラミング装置などの、別の装置にイメージを送信することにより、公開できる。さらにまた別の例では、イメージは、イメージを並列マシン（例えば、FSMエンジン600）上にロードすることにより、公開できる。3040

#### 【0075】

一例では、イメージは、イメージからのビット値をSME 604、605、および他のハードウェア要素624に直接ロードするか、またはイメージを1つまたは複数のレジスタにロードし、次いで、レジスタからのビット値をSME 604、605、および他のハードウェア要素624に書き込むかのいずれかにより、FSMエンジン600上にロードすることにより、公開できる。50

ードできる。一例では、FSMエンジン600のハードウェア要素（例えば、SME 604、605、他の要素624、プログラム可能スイッチ603、608、612）が、プログラミング装置および/またはコンピュータが、イメージを1つまたは複数のメモリアドレスに書き込むことにより、イメージをFSMエンジン600上にロードできるよう に、メモリマップされる。

#### 【0076】

ここで、図3および図4A～図4Cを再度参照すると、構文木をオートマトンに変換する際に、展開された量化子の入次数および/または出次数が制御できる。一例では、入次数および/または出次数は、閾値に基づいて制御される。閾値は、例えば、コンパイラがイメージを準備している並列マシン500のハードウェア制限に基づくことができる。例えば、並列マシン500の汎用要素502が最大14の入遷移を有することができる場合、展開に対する閾値は、14の入遷移以下に設定できる。別の例では、展開に対する閾値は、最大入遷移の一部が使用されるように、設定できる。例えば、最大14の入遷移を有する汎用要素502に対して、閾値は、展開している式中ではない式からの入遷移のために、7つの入遷移に設定できる。10

#### 【0077】

展開は、以下で説明するように、一般的なグラフ問題として定式化できる。図11A、図11B、図12、および図13は、以下で議論する問題1に対する4つの解決策のグラフを示し、そこでは、入次数および出次数が制御される。異なる解決策は異なる最大長を提供するが、それは、入次数および出次数閾値によって決定される。その結果、所望の入次数および出次数に応じて、所与の解決策が選択され得る。結果として得られるオートマトンの入次数および/または出次数は、以下で議論する2つの問題に対してどの解決策が選択されるかの関数である。20

#### 【0078】

問題1（入次数および出次数制約のある経路を拡張する）。長さnの有向路ならびに2つの符号なし整数 $p > 1$ および $q > 1$ を前提とする。 $n + 1$ 個のバーテックスを $v_0 -> v_1 -> v_2 -> \dots -> v_n$ として示す。経路の開始バーテックスが $v_0$ であり、終了バーテックスが $v_n$ である。ループが導入されないように、エッジをこの経路に追加し、任意の $k$  ( $1 \leq k \leq n$ )に対して、長さ $k$ で $v_0$ から $v_n$ までの有向路が存在し；また、全てのバーテックスの入次数は、 $p$ 以下でなければならず、かつ、全てのバーテックスの出次数は $q$ 以下でなければならない。30

#### 【0079】

問題2（入次数および出次数制約のある経路を最大限にする）。無限有向路ならびに2つの符号なし整数 $p > 1$ および $q > 1$ を前提とする。バーテックスを $v_0 -> v_1 -> v_2 -> \dots$ として示す。エッジをこの経路に追加し、 $v_m$ として示される、終了バーテックスを見つけ、任意の $k$  ( $1 \leq k \leq m$ )に対して、長さ $k$ で $v_0$ から $v_m$ までの有向路が存在するようにし；全てのバーテックスの入次数は、 $p$ 以下でなければならず、かつ、全てのバーテックスの出次数は $q$ 以下でなければならない。グラフ内でループは許可されない。最適化の目標は、結果の経路の長さ $m$ を最大限にすることである。40

#### 【0080】

一例では、問題2が最初に解決される。最大限にされた経路長 $m$ が $n$ 以上の場合、問題1は容易に解決できる。図11～図13に関連して以下で説明する4つの解決策は、図4A～図4Cに関連して説明した散乱パターンおよびマージパターンから導出される。最大長は、 $p$ および $q$ の値によって決まる。

#### 【0081】

グラフの用語では、散乱パターンは、 $q$ 個のバーテックスをもつ経路の拡張として説明できる。元の経路を含むエッジに加えて、開始バーテックス、 $v_0$ が他の全てのバーテックスを駆動する。 $v_0$ の出次数が $q - 1$ 、 $v_{q-1}$ が0、および他のバーテックス $v_1 \dots v_{q-2}$ が1である。 $v_0$ の入次数が0、 $v_1$ が1、および $v_2 \dots v_{q-1}$ が2である。全ての $k$  ( $1 \leq k \leq q - 1$ )に対して、長さ $k$ の $v_0$ から $v_{q-1}$ までの経50

路がある。

- $k = 1 : v_0 \rightarrow v_{q-1}$

- $k = 2 : v_0 \rightarrow v_{q-2} \rightarrow v_{q-1}$

- $k = 3 : v_0 \rightarrow v_{q-3} \rightarrow v_{q-2} \rightarrow v_{q-1}$

- . . . .

- $k = q-1 : v_0 \rightarrow v_1 \rightarrow v_2 \rightarrow \dots \rightarrow v_{q-2} \rightarrow v_{q-1}$

### 【0082】

同様に、グラフの用語では、マージパターンは、 $p$ 個のバーテックスをもつ経路として説明できる。元の経路を含むエッジに加えて、終了バーテックス、 $v_{p-1}$ が他の全てのバーテックスによって駆動される。 $v_{p-1}$ の入次数が $q-1$ 、 $v_0$ が0、および他のバーテックス $v_1 \dots v_{q-2}$ が1である。 $v_{p-1}$ の出次数が0、 $v_{p-2}$ が1、および $v_0 \dots v_{q-3}$ が2である。全ての $k$  ( $1 \leq k \leq p-1$ ) に対して、長さ $k$ の $v_0$ から $v_{p-1}$ までの経路がある。

10

- $k = 1 : v_0 \rightarrow v_{p-1}$

- $k = 2 : v_0 \rightarrow v_1 \rightarrow v_{p-1}$

- $k = 3 : v_0 \rightarrow v_1 \rightarrow v_2 \rightarrow v_{p-1}$

- . . . .

- $k = q-1 : v_0 \rightarrow v_1 \rightarrow v_2 \rightarrow \dots \rightarrow v_{p-2} \rightarrow v_{p-1}$

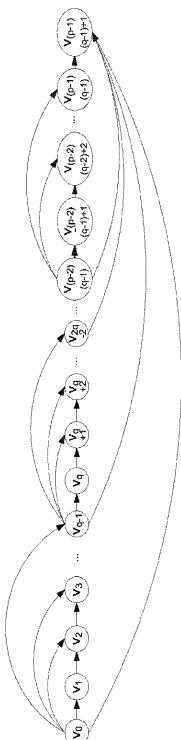

### 【0083】

図11Aは、前述した問題2に対する第1の解決策を示す。構築方法は以下の通り。長さ $q-1$ の散乱パターンのコピーされた $p-1$ を連結し、次いで、最後にもう1つバーテックス、 $v(p-1)(q-1)+1$ を追加する。散乱パターンの終了バーテックスおよび開始バーテックスは、連結中に、接合バーテックス(`junction vertex`)として示される、1つのバーテックスにマージされる。全ての接合バーテックスからのエッジを最後のバーテックス、 $v(p-1)(q-1)+1$ に接続する。実際には、接合バーテックスを $v(p-1)(q-1)+1$ に接続することは、マージパターンを接合バーテックスに適用することである。

20

### 【0084】

ここで、バーテックス、 $v_k$ の出次数は、

- |     |                                 |    |

|-----|---------------------------------|----|

| $q$ | $k = x(q-1), 0 \leq x \leq p-2$ | 30 |

| 0   | $k = (p-1)(q-1)+1$              |    |

| 1   | その他                             |    |

である。

### 【0085】

バーテックス、 $v_k$ の入次数は、

- |     |                                   |  |

|-----|-----------------------------------|--|

| 0   | $k = 0$                           |  |

| 1   | $k = x(q-1)+1, 0 \leq x \leq p-2$ |  |

| $p$ | $k = (p-1)(q-1)+1$                |  |

| 2   | その他                               |  |

である。

40

### 【0086】

全ての $k$  ( $1 \leq k \leq q$ ) に対して、長さ $k$ で $v_0$ から $v(p-1)(q-1)+1$ までの経路は、

- $k = 1 : v_0 \rightarrow v(p-1)(q-1)+1$

- $k = 2 : v_0 \rightarrow v_{q-1} \rightarrow v(p-1)(q-1)+1$

- $k = 3 : v_0 \rightarrow v_{q-2} \rightarrow v_{q-1} \rightarrow v(p-1)(q-1)+1$

- . . . .

- $k = q : v_0 \rightarrow v_1 \rightarrow v_2 \rightarrow \dots \rightarrow v_{q-1} \rightarrow v(p-1)(q-1)+1$

### 【0087】

全ての  $k$  ( $q + 1 \leq k \leq 2q - 1$ ) に対して、長さ  $k$  で  $v^0$  から  $v^{(p-1)(q-1)+1}$ までの経路は、

- $k = q + 1 : v^0 \rightarrow v^1 \rightarrow v^2 \rightarrow \dots \rightarrow v^{q-1} \rightarrow v^{2q-2} \rightarrow v^{(p-1)(q-1)+1}$

- $k = q + 2 : v^0 \rightarrow v^1 \rightarrow v^2 \rightarrow \dots \rightarrow v^{q-1} \rightarrow v^{2q-1} \rightarrow v^{2q-2} \rightarrow v^{(p-1)(q-1)+1}$

- $k = q + 3 : v^0 \rightarrow v^1 \rightarrow v^2 \rightarrow \dots \rightarrow v^{q-1} \rightarrow v^{2q-2} \rightarrow v^{(p-1)(q-1)+1}$

- . . . .

- $k = 2q : v^0 \rightarrow v^1 \rightarrow v^2 \rightarrow \dots \rightarrow v^{q-1} \rightarrow v^q \rightarrow v^{q+1} \rightarrow \dots \rightarrow v^{2q-2} \rightarrow v^{(p-1)(q-1)+1}$

#### 【0088】

その他の  $k$  ( $2q + 1 \leq k \leq (p-1)(q-1) + 1$ ) に対して、経路が同様に構築される。それ故、解決策1の達成された最大経路長は、 $(p-1)(q-1) + 1$ に等しい。

#### 【0089】

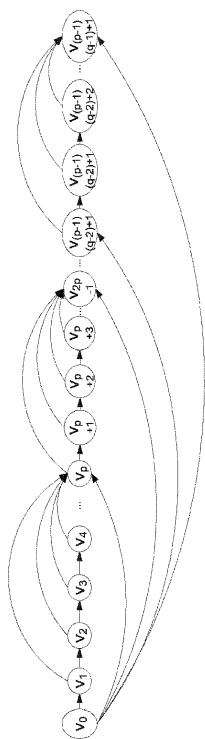

図11Bは、前述した第1の解決策と似ている、問題2に対する第2の解決策を示す。この解決策では、マージパターンおよび散乱パターンの使用が、問題2に対する第1の解決策に関してスワップされる。基本的には、マージパターンが副経路に対して使用され、散乱パターンが接合バーテックスに対して適用される。入次数、出次数、および様々な長さの経路に関する詳細は、解決策1と同様である。解決策1の達成された最大経路長は、 $(p-1)(q-1) + 1$ に等しい。

20

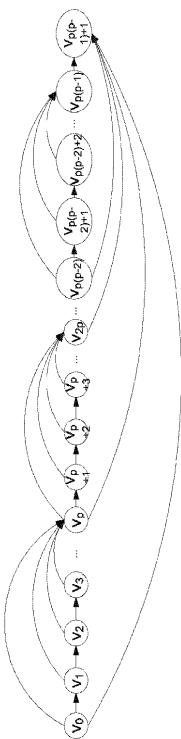

#### 【0090】

図12は、問題2に対する第3の解決策を示す。この解決策は、マージパターンを副経路および接合バーテックスの両方に適用することである。解決策1の達成された最大経路長は、 $p(p-1) + 1$ に等しい。

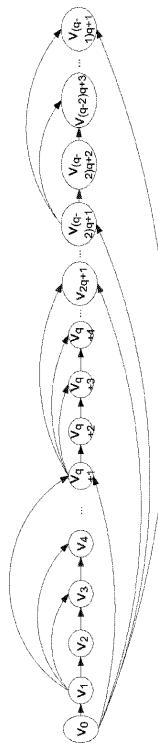

#### 【0091】

図13は、問題2に対する第4の解決策を示す。この解決策は、散乱パターンを副経路および接合バーテックスの両方に適用することである。解決策1の達成された最大経路長は、 $q(q-1) + 1$ に等しい。

30

#### 【0092】

図14は、問題1に対する解決策を示す。前述した4つの解決策から問題1の解決策を得ることは、簡単である。最大長が  $n$  (経路長) 以上の任意の解決策を取ればよい。解決策1が取られ、 $n$  が  $(p-2)(q-1) + 1$  に等しいと仮定する。 $(p-2)(q-1) + 1$  より大きい指標をもつバーテックスを取り除き、次いで、接合バーテックスを  $v^{(p-2)(q-1) + 1}$  に再接続する。結果として得られるグラフが、問題1に対する解決策である。同じ技法が問題2に対する4つの解決策すべてに当てはまる。

#### 【0093】

本明細書で説明する方法例は、少なくとも一部は、機械またはコンピュータ実装できる。いくつかの例は、上の例で説明した方法を実行する電子装置を構成するように動作可能な命令でコード化されたコンピュータ可読媒体または機械可読媒体を含み得る。かかる方法の実装は、マイクロコード、アセンブリ言語コード、高水準言語コード、または同様のものなどの、コードを含み得る。かかるコードは、様々な方法を実行するためのコンピュータ可読命令を含み得る。コードは、コンピュータプログラム製品の一部を形成し得る。さらに、コードは、実行中または他の時に、1つもしくは複数の揮発性または不揮発性のコンピュータ可読媒体上に有形的に格納され得る。これらのコンピュータ可読媒体は、ハードディスク、取り外し可能磁気ディスク、取り外し可能光ディスク（例えば、コンパクトディスクおよびデジタルビデオディスク）、磁気力セット、メモリカードまたはメモリスティック、ランダムアクセスメモリ（RAM）、読み取り専用メモリ（ROM）、および同様のものを含み得るが、これらに限定されない。

40

50

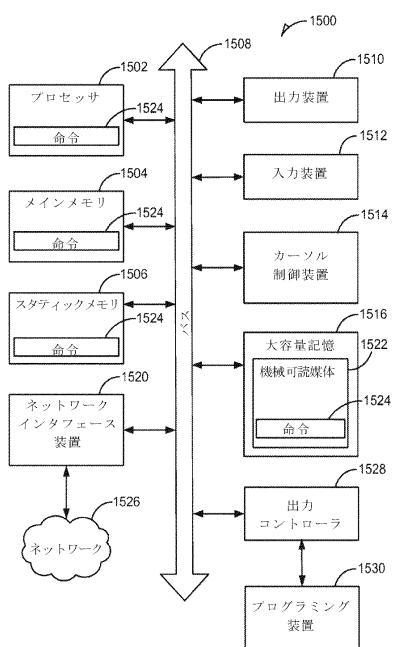

**【 0 0 9 4 】**

図15は、フォンノイマン型アーキテクチャを有するコンピュータ1500の例をおおまかに示す。本開示の内容を読んで理解すると、当業者であれば、ソフトウェアプログラム内に定義された機能を実行するために、ソフトウェアプログラムが、コンピュータベースシステム内のコンピュータ可読媒体から起動できる方法を理解するであろう。当業者は、さらに、本明細書で開示する方法を実装および実行するように設計された1つまたは複数のソフトウェアプログラムを作成するために採用できる様々なプログラム言語を理解するであろう。プログラムは、Java、C++、または1つもしくは複数の他の言語などのオブジェクト指向言語を使用して、オブジェクト指向フォーマットで構造化できる。代替として、プログラムは、アセンブリ、C、などの手続き型言語を使用して、手続き指向フォーマットで構造化できる。ソフトウェアコンポーネントは、リモートプロシージャコールまたはその他を含む、アプリケーションプログラムインタフェースまたはプロセス間通信技術など、当業者に周知の任意の数の機構を使用して、通信できる。様々な実施形態の技術は、任意の特定のプログラム言語または環境に制限されない。

**【 0 0 9 5 】**

このようにして、他の実施形態が実現できる。例えば、コンピュータ、メモリシステム、磁気ディスクもしくは光ディスク、何らかの他の記憶装置、または任意のタイプの電子装置もしくはシステムなどの、製品は、その上に格納された命令1524（例えば、コンピュータプログラム命令）を有するメモリ（例えば、取り外し可能記憶媒体、ならびに電気導体、光導体、または電磁導体を含む任意のメモリ）などの、コンピュータ可読媒体1522に結合された1つまたは複数のプロセッサ1502を含み得、それは、1つまたは複数のプロセッサ1502で実行される場合に、上の方法に関する説明した動作のいずれかを実行する結果となる。

**【 0 0 9 6 】**

コンピュータ1500は、いくつかのコンポーネントに直接、および／またはバス1508を使用して、結合されたプロセッサ1502を有するコンピュータシステムの形をとることができる。かかるコンポーネントには、メインメモリ1504、スタティックまたは不揮発性メモリ1506、および大容量記憶1516を含み得る。プロセッサ1502に結合された他のコンポーネントには、ビデオディスプレイなどの出力装置1510、キーボードなどの入力装置1512、およびマウスなどのカーソル制御装置1514を含み得る。プロセッサ1502および他のコンポーネントをネットワーク1526に結合するためのネットワークインターフェース装置1520は、バス1508にも結合できる。命令1524は、いくつかの周知の転送プロトコル（例えば、HTTP）のうちの任意の1つを利用するネットワークインターフェース装置1520を経由し、ネットワーク1526を通して、さらに転送または受信され得る。バス1508に結合されたこれら要素のいずれかは、実現される特定の実施形態に応じて、存在しないか、単独で存在し得るか、または複数で存在し得る。

**【 0 0 9 7 】**

一例では、1つまたは複数のプロセッサ1502、メモリ1504、1506、または記憶装置1516は各々、コンピュータ1500に、実行時に、本明細書に記載する方法のいずれか1つまたは複数を実行させ得る、命令1524を含むことができる。代替実施形態では、コンピュータ1500は、スタンドアロン装置として動作するか、または他の装置に接続（例えば、ネットワーク接続）できる。ネットワーク化された環境では、コンピュータ1500は、サーバークライアントネットワーク環境内のサーバーもしくはクライアント装置の資格で、または、ピアツーピア（もしくは分散）ネットワーク環境内のピア装置として、動作できる。コンピュータ1500には、パーソナルコンピュータ（PC）、タブレットPC、セットトップボックス（STB）、携帯情報端末（PDA）、携帯電話、ウェブアプライアンス、ネットワークルーター、スイッチもしくはブリッジ、またはその装置によってとられる動作を指定する命令のセットを（連続して、もしくは他の方法で）実行可能な任意の装置を含み得る。さらに、单一のコンピュータ1500のみが示

されているが、「コンピュータ」という用語は、本明細書で説明する方法のいずれか1つまたは複数を実行するための命令のセット(または複数のセット)を単独に、または一緒に実行する装置の任意の集合を含むようにも解釈されるものとする。

#### 【0098】

コンピュータ1500は、1つまたは複数の通信プロトコル(例えば、ユニバーサルシリアルバス(USB)、IEEE 1394など)を使用して周辺機器と通信するための出力コントローラ1528も含むことができる。出力コントローラ1528は、例えば、コンピュータ1500に通信的に結合されているプログラミング装置1530にイメージを提供できる。プログラミング装置1530は、並列マシン(例えば、並列マシン500、FSMエンジン600)をプログラムするように構成できる。他の例では、プログラミング装置1530は、コンピュータ1500と統合されて、バス1508に結合できるか、またはネットワークインターフェース装置1520または別の装置を経由してコンピュータ1500と通信できる。10

#### 【0099】

コンピュータ可読媒体1524は単一の媒体として示されているが、「コンピュータ可読媒体」という用語は、命令1524の1つまたは複数のセットを格納する単一の媒体または複数の媒体(例えば、集中型もしくは分散型データベース、または関連するキャッシュおよびサーバー、ならびに/またはプロセッサ1502レジスタ、メモリ1504、1506、および記憶装置1516などの様々な記憶媒体)を含むように解釈されるべきである。「コンピュータ可読媒体」という用語は、コンピュータによって実行するための命令のセットを格納、コード化、または運搬可能であり、かつ、コンピュータに本発明の方法のいずれか1つまたは複数を実行させるか、または命令のかかるセットによって利用されるか、またはそれに関連したデータ構造を格納、コード化、または運搬可能である、任意の媒体を含むように解釈されるものとする。「コンピュータ可読媒体」という用語は、その結果、ソリッドステートメモリ、光媒体、および磁気媒体などの、有形的媒体を含むように解釈されるものとするが、それらに限定されない。20

#### 【0100】

要約は、読者が技術的開示の本質および要点を確認できるようにする要約を要求する米国特許規則(37 C.F.R.)1.72(b)項に準拠するために提供されている。それは、請求項の範囲または意味を制限または解釈するために使用されないという理解で提示されている。以下の請求項は、これによって詳細な説明に組み込まれ、各請求項が別個の実施形態として権利を主張する。30

#### 【0101】

##### 〔実施形態例〕

例1は、量化子をオートマトンに変換することを含む、コンピュータ実装方法を含み、変換することは、オートマトンの入次数を制御するように量化子を展開すること；および、オートマトンを、対象装置に対応する機械コードに変換することを含む。

#### 【0102】

例2は、命令を含むコンピュータ可読媒体を含み、それは、コンピュータによって実行されるときに、そのコンピュータに、量化子をオートマトンに変換することであって、変換することが、オートマトンの出次数を制御するように量化子を展開することを含む、量化子をオートマトンに変換すること；およびオートマトンを、対象装置に対応する機械コードに変換すること、を含む動作を実行させる。40

#### 【0103】

例3は、ソフトウェアがその上に格納されたメモリ；およびそのメモリに通信的に結合されたプロセッサを含むコンピュータを含む。ソフトウェアは、プロセッサによって実行されるとき、そのプロセッサに：量化子をオートマトンに変換することであって、変換することが、オートマトンの入次数または出次数を制御するように量化子を展開することを含む、量化子をオートマトンに変換すること；およびオートマトンを、対象装置に対応する機械コードに変換すること、をさせる。50

**【0104】**

例4は、量化子をオートマトンに変換することであって、変換することが、オートマトンの入次数または出次数を制御するように量化子を展開することを含む、量化子をオートマトンに変換すること；およびオートマトンを、対象装置に対応する機械コードに変換することを行なうように構成されたコンピュータを含むシステムを含む。

**【0105】**

例5は、量化子をオートマトンに変換することであって、変換することが、オートマトンの出次数を制御するように量化子を展開することを含む、量化子をオートマトンに変換すること；およびオートマトンを、対象装置に対応する機械コードに変換することを含む、コンピュータ実装方法を含む。

10

**【0106】**

例6は、命令を含むコンピュータ可読媒体を含み、それは、コンピュータによって実行されるときに、そのコンピュータに、量化子をオートマトンに変換することであって、変換することが、オートマトンの入次数を制御するように量化子を展開することを含む、量化子をオートマトンに変換すること；およびオートマトンを、対象装置に対応する機械コードに変換すること、を含む動作を実行させる。

**【0107】**

例7では、例1～6のいずれかの主題が、式を、量化子を含む、言語固有でない表現に解析することを、を随意に含み得る。

**【0108】**

20

例8では、例1～7のいずれかの主題が、式を、言語固有でない表現に解析することが、正規表現を構文木に解析することを含むこと、を随意に含み得る。

**【0109】**

例9では、例1～8のいずれかの主題が、変換することが、量化子に対する繰返し式が空値可能である場合、量化子を、ゼロ回一致し得る繰返し式の空値不能形式を有する量化子として展開することを含むこと、を随意に含み得る。

**【0110】**

例10では、例1～9のいずれかの主題が、オートマトンを機械コードに変換することが、オートマトンを、並列マシンをプログラムするように構成されたイメージに変換することを含むこと、を随意に含み得る。

30

**【0111】**

例11では、例1～10のいずれかの主題が、イメージを公開すること、を随意に含み得る。

**【0112】**

例12では、例1～11のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、入次数制限に応じて量化子を展開することを含むこと、を随意に含み得る。

**【0113】**

例13では、例1～12のいずれかの主題が、入次数制限が、オートマトンの状態への遷移数に関する制限を含むこと、を随意に含み得る。

40

**【0114】**

例14では、例1～13のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、対象装置の入次数制約に基づいて展開することを含むこと、を随意に含み得る。

**【0115】**

例15では、例1～14のいずれかの主題が、量化子が正規表現であること、を随意に含み得る。

**【0116】**

例16では、例1～15のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、閾値に基づいてオートマトンの入次数を制御するように量化子

50

を展開することを含むこと、を随意に含み得る。

**【0117】**

例17では、例1～16のいずれかの主題が、閾値が並列マシンのハードウェア制限に基づくこと、を随意に含み得る。

**【0118】**

例18では、例1～17のいずれかの主題が、展開することが、オートマトンの各状態に対する出遷移を閾値数未満に制限することを含むこと、を随意に含み得る。

**【0119】**

例19では、例1～18のいずれかの主題が、展開することが、オートマトンの各状態に対する出遷移を最小限にすることを含むこと、を随意に含み得る。

10

**【0120】**

例20では、例1～19のいずれかの主題が、変換することが、量化子に対する繰返し式が空値可能である場合、量化子を、ゼロ回一致し得る繰返し式の空値不能形式を有する量化子として展開することを含むこと、を随意に含み得る。

**【0121】**

例21では、例1～20のいずれかの主題が、変換することが、量化子が单一のある個数のループと一致し得る場合、量化子を、連続的にリンクされた单一のある個数に等しい、いくつかの式を表す状態を有するオートマトンを形成するように展開することを含み、その式が、量化子に対する繰返し式に対応すること、を随意に含み得る。

20

**【0122】**

例22では、例1～21のいずれかの主題が、量化子が複数のある個数のループと一致し得る場合、複数のある個数のループが、第1の数のループ、n1、および第2の数のループ、n2を含み、量化子を展開することが、量化子を、n1 - 1個のループと一致し得る第1の量化子および、1～n2 - n1 + 1個までのループと一致し得る第2の量化子に分割することを含むこと、を随意に含み得る。

**【0123】**

例23では、例1～22のいずれかの主題が、イメージを並列マシン上にロードすること、を随意に含み得る。

**【0124】**

例24では、例1～23のいずれかの主題が、イメージを、コンピュータ可読媒体上に格納すること、を随意に含み得る。

30

**【0125】**

例25では、例1～24のいずれかの主題が、オートマトン内で入遷移を出遷移に対してトレードオフすることにより、入次数および出次数を制御すること、を随意に含み得る。

**【0126】**

例26では、例1～25のいずれかの主題が、各状態に対する入遷移が、展開時に閾値数未満に制限されること、を随意に含み得る。

**【0127】**

例27では、例1～26のいずれかの主題が、入次数が出次数の割合に制限されること、を随意に含み得る。

40

**【0128】**

例28では、例1～27のいずれかの主題が、オートマトンの状態に対する入遷移の閾値に達するまで、入次数が出次数の割合に制限されること、を随意に含み得る。

**【0129】**

例29では、例1～28のいずれかの主題が、機械コードが、並列マシンをプログラムするように構成されたイメージを含むこと、および、コンピュータに通信的に結合され、かつイメージを並列マシン上にロードするように構成された装置をさらに含むこと、を随意に含み得る。

**【0130】**

50

例 3 0 では、例 1 ~ 2 9 のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、入次数制限に応じて量化子を展開することを含むこと、を隨意に含み得る。

#### 【 0 1 3 1 】

例 3 1 では、例 1 ~ 3 0 のいずれかの主題が、入次数制限が、オートマトンの状態への遷移数に関する制限を含むこと、を隨意に含み得る。

#### 【 0 1 3 2 】

例 3 2 では、例 1 ~ 3 1 のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、対象装置の入次数制約に基づいて展開することを含むこと、を隨意に含み得る。

10

#### 【 0 1 3 3 】

例 3 3 では、例 1 ~ 3 2 のいずれかの主題が、オートマトンの入次数を制御するように量化子を展開することが、閾値に基づいてオートマトンの入次数を制御するように量化子を展開することを含むこと、を隨意に含み得る。

#### 【 0 1 3 4 】

例 3 4 では、例 1 ~ 3 3 のいずれかの主題が、閾値が並列マシンのハードウェア制限に基づくこと、を隨意に含み得る。

#### 【 0 1 3 5 】

例 3 5 では、例 1 ~ 3 4 のいずれかの主題が、正規表現を構文木に解析すること、を隨意に含み得る。

20

#### 【 0 1 3 6 】

例 3 6 では、例 1 ~ 3 5 のいずれかの主題が、オートマトンを機械コードに変換することが、オートマトンを、並列マシンをプログラムするように構成されたイメージに変換することを含むこと、を隨意に含み得る。

#### 【 0 1 3 7 】

例 3 7 では、例 1 ~ 3 6 のいずれかの主題が、イメージを公開すること、を隨意に含み得る。

#### 【 0 1 3 8 】

例 3 8 では、例 1 ~ 3 7 のいずれかの主題が、オートマトンの出次数を制御するように量化子を展開することが、出次数制限に応じて量化子を展開することを含むこと、を隨意に含み得る。

30

#### 【 0 1 3 9 】

例 3 9 では、例 1 ~ 3 8 のいずれかの主題が、出次数制限が、オートマトンの状態からの遷移数に関する制限を含むこと、を隨意に含み得る。

#### 【 0 1 4 0 】

例 4 0 では、例 1 ~ 3 9 のいずれかの主題が、オートマトンの出次数を制御するように量化子を展開することが、対象装置の出次数制約に基づいて展開することを含むこと、を隨意に含み得る。

#### 【 0 1 4 1 】

例 4 1 では、例 1 ~ 4 0 のいずれかの主題が、オートマトンの出次数を制御するように量化子を展開することが、閾値に基づいてオートマトンの出次数を制御するように量化子を展開することを含むこと、を隨意に含み得る。

40

#### 【 0 1 4 2 】

例 4 2 では、例 1 ~ 4 1 のいずれかの主題が、閾値が並列マシンのハードウェア制限に基づくこと、を隨意に含み得る。

#### 【 0 1 4 3 】

例 4 3 では、例 1 ~ 4 2 のいずれかの主題が、展開することが、オートマトンの各状態に対する入遷移を閾値未満に制限することを含むこと、を隨意に含み得る。

#### 【 0 1 4 4 】

例 4 4 では、例 1 ~ 4 3 のいずれかの主題が、展開することが、オートマトンの各状態

50

に対する入遷移を最小限にすることを含むこと、を隨意に含み得る。

#### 【0145】

例45では、例1～44のいずれかの主題が、変換することが、量化子に対する繰返し式が空値可能である場合、量化子を、ゼロ回一致し得る繰返し式の空値不能形式を有する量化子として、展開することを含むこと、を隨意に含み得る。

#### 【0146】

例46では、例1～45のいずれかの主題が、変換することが、量化子が單一のある個数のループと一致し得る場合、連續的にリンクされた單一のある個数に等しい、いくつかの式を表す状態を有するオートマトンを形成するように量化子を展開することを含み、その式が、量化子に対する繰返し式に対応すること、を隨意に含み得る。 10

#### 【0147】

例47では、例1～46のいずれかの主題が、量化子が複数のある個数のループと一致し得る場合、複数のある個数のループが、第1の数のループ、n1、および第2の数のループ、n2を含み、量化子を展開することが、量化子を、n1 - 1個のループと一致し得る第1の量化子および、1～n2 - n1 + 1個までのループと一致し得る第2の量化子に分割することを含むこと、を隨意に含み得る。

#### 【0148】

例48は、例1～47のいずれかの主題を使用して生成されたイメージによってプログラマ化された並列マシンを含む。

【図1】

【図2】

【図3】

【図4A】

FIG. 4A

【 図 4 B 】

FIG. 4B

【図4C】

FIG. 4C

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11A】

FIG. 11A

【図11B】

FIG. 11B

【図12】

FIG. 12

【図13】

FIG. 13

【図14】

FIG. 14

【図15】

---

フロントページの続き

(72)発明者 グレンデニング, ポール

アメリカ合衆国, カリフォルニア州 94062, ウッドサイド, ブレイクウッド ウェイ 32

3

審査官 坂庭 剛史

(56)参考文献 国際公開第2010/018710 (WO, A1)

米国特許出願公開第2010/0185647 (US, A1)

特開2009-093599 (JP, A)

特開2005-353061 (JP, A)

新屋良磨、河野真治, 動的なコード生成を用いた正規表現マッチャの実装, 情報処理学会:シンポジウム > プログラミング・シンポジウム > 冬 > 52回 [online] 第52回プログラミング・シンポジウム予稿集, 一般社団法人情報処理学会, 2011年 1月 7日, p. 173 - 180

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 45