(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6029704号

(P6029704)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

(51) Int.Cl.

F 1

|              |           |            |         |   |

|--------------|-----------|------------|---------|---|

| HO1L 21/76   | (2006.01) | HO1L 21/76 | 21/76   | L |

| HO1L 21/764  | (2006.01) | HO1L 21/76 |         | A |

| HO1L 27/08   | (2006.01) | HO1L 27/08 | 3 3 1 A |   |

| HO1L 21/8249 | (2006.01) | HO1L 27/06 | 3 2 1 C |   |

| HO1L 27/06   | (2006.01) | HO1L 27/10 | 4 3 4   |   |

請求項の数 10 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2015-68517(P2015-68517)

(22) 出願日

平成27年3月30日(2015.3.30)

(62) 分割の表示

特願2009-213345(P2009-213345)

の分割

原出願日 平成21年9月15日(2009.9.15)

(65) 公開番号

特開2015-122543(P2015-122543A)

(43) 公開日

平成27年7月2日(2015.7.2)

審査請求日

平成27年3月30日(2015.3.30)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 大西 一真

兵庫県伊丹市瑞原4丁目1番地 株式会社

ルネサスセミコンダクタエンジニアリング

内

(72) 発明者 大津 良孝

兵庫県伊丹市瑞原4丁目1番地 株式会社

ルネサスセミコンダクタエンジニアリング

内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電型の第1の半導体層と、前記第1の半導体層上に形成され、前記第1導電型と逆導電型の第2導電型の第2の半導体層と、前記第2の半導体層上に形成された、前記第1導電型の第3の半導体層と、を有する半導体基板と、

前記第3の半導体層の主表面上にゲート絶縁膜を介して設けられたゲート電極と、前記第3の半導体層の前記主表面に前記ゲート電極を挟んで形成されたソース領域とドレイン領域とを有するMOSトランジスタと、

前記MOSトランジスタの前記ソース領域または前記ドレイン領域の側面と接し、前記ソース領域または前記ドレイン領域より深い第1の溝内に第1の絶縁膜が埋め込まれてなる第1の分離と、

複数の前記MOSトランジスタと前記第1の分離を含む素子形成領域と、

前記素子形成領域を取り囲む第2の溝からなる第2の分離と、

前記ゲート電極の上を覆い、前記第2の溝内を埋め込む第2の絶縁膜と、を備え、

前記第2の溝は前記第1の溝より深く、

前記第2の分離は前記第2の半導体層を貫いて前記第1の半導体層にまで達し、

前記第2の分離には中空が形成されている、半導体装置。

## 【請求項 2】

前記第2の分離の前記中空は、前記中空の底が前記第1の半導体層の内部まで達する、

10

20

請求項 1 記載の半導体装置。

**【請求項 3】**

前記第 2 の絶縁膜上に形成された配線層と、

前記第 2 の絶縁膜内に形成された導電層と、

をさらに備え、

前記配線層は、前記導電層により、前記MOSトランジスタの前記ソース領域または前記ドレイン領域に接続される、請求項 1 記載の半導体装置。

**【請求項 4】**

前記ゲート電極を覆い、前記第 2 の絶縁膜の下に形成された第 3 の絶縁膜をさらに備え

、

前記第 2 の絶縁膜はTEOS膜であり、前記第 3 の絶縁膜はシリコン窒化膜である、請求項 3 記載の半導体装置。

**【請求項 5】**

前記第 2 の分離は、前記第 1 の分離を貫いて形成される、請求項 1 記載の半導体装置。

**【請求項 6】**

(a) 第 1 導電型の第 1 の半導体層と、

前記第 1 の半導体層上に形成され、前記第 1 導電型と逆導電型の第 2 導電型の第 2 の半導体層と、

前記第 2 の半導体層上に形成された、前記第 1 導電型の第 3 の半導体層と、

前記第 3 の半導体層の主表面にゲート絶縁膜を介して設けられたゲート電極と、前記第 3 の半導体層の前記主表面に前記ゲート電極を挟んで形成されたソース領域およびドレイン領域とを有するMOSトランジスタと、

前記ソース領域または前記ドレイン領域の側面と接し、前記第 3 の半導体層の前記主表面に形成された、前記ソース領域または前記ドレイン領域より深い第 1 の溝内を第 1 の絶縁膜で埋め込んだ第 1 の分離と、

を有する半導体基板を準備する工程と、

(b) 前記(a)工程の後に前記MOSトランジスタと前記第 1 の分離を含む素子形成領域を平面視において取り囲み、前記第 3 の半導体層および前記第 2 の半導体層を貫いて前記第 1 の半導体層の内部にまで達する第 2 の溝を形成する工程と、

(c) 前記ゲート電極の上を覆い、前記第 2 の溝の内部を埋め込む第 2 の絶縁膜を形成する工程と、

を備え、

前記第 2 の溝内には中空が形成される、半導体装置の製造方法。

**【請求項 7】**

前記(c)工程の後に、

(d) 前記第 2 の絶縁膜を貫いて、前記MOSトランジスタの前記ソース領域または前記ドレイン領域に到達する導電層を形成する工程と、

(e) 前記第 2 の絶縁膜上に前記導電層に接続する配線層を形成する工程と、

をさらに備えた、請求項 6 記載の半導体装置の製造方法。

**【請求項 8】**

前記中空の底は、前記第 1 の半導体層の内部にまで達する、請求項 6 記載の半導体装置の製造方法。

**【請求項 9】**

前記(b)工程は、

(b - 1) 前記MOSトランジスタを覆うマスク材を形成する工程と、

(b - 2) 前記マスク材上に、前記第 2 の溝に対応する第 1 開口を有するレジストパターンを形成する工程と、

(b - 3) 前記半導体基板に異方性エッチングを施し、前記マスク材、前記第 1 の絶縁膜、および、前記半導体基板に前記第 2 の溝を形成する工程と、

を有する、請求項 6 記載の半導体装置の製造方法。

10

20

30

40

50

**【請求項 10】**

前記(b-3)工程において、前記半導体基板に前記第2の溝を形成する前記異方性エッチングの際に、前記マスク材はマスクとして機能する、請求項9記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置およびその製造方法に関し、特に、溝を有する半導体装置およびその製造方法に関するものである。

**【背景技術】**

10

**【0002】**

高アスペクト比の溝内に絶縁膜を充填した素子分離(Deep Trench Isolation: DTI)構造は、たとえば特開2002-118256号公報に開示されている。

**【0003】**

この公報に記載の技術では、まず半導体基板の表面に溝が形成され、その後に、その溝内を埋め込むように第1の絶縁膜が半導体基板の表面上に成膜される。この第1の絶縁膜が異方性エッチングされることにより、第1の絶縁膜に溝内に達する開口が形成されるとともに、第1の絶縁膜の開口の上端コーナ部が溝の上端コーナ部よりも緩やかな傾斜とされる。さらに上記の異方性エッチングにより、半導体基板の表面上の第1の絶縁膜の膜厚が減ぜられる。この後、上記開口を埋め込むように第2の絶縁膜が半導体基板の表面上に成膜される。

20

**【0004】**

上記のようにDTI構造が形成された後に、半導体基板にMOSFET(Metal Oxide Semiconductor Field Effect Transistor)などの電子素子が形成される。

**【先行技術文献】****【特許文献】****【0005】****【特許文献1】特開2002-118256号公報****【発明の概要】****【発明が解決しようとする課題】**

30

**【0006】**

上記の方法では、高アスペクト比の溝内を第1および第2の絶縁膜で埋め込む必要がある。このため、2回の絶縁膜堆積と、開口上端部の拡張のための異方性エッチングが必要となり、フロー時間が長くなり、処理時間と費用が掛かるプロセスとなっていた。

**【0007】**

また溝内部に中空が存在すると、その後のウエット処理で中空部が基板表面に露出するおそれがある。溝内部の中空部が基板表面に露出した場合、その露出部からレジスト材などが中空部に入り込んで除去できなくなる。中空部内のレジスト材などは後工程で噴出して異物として現れ、パターン欠陥の原因となる。

**【0008】**

40

本発明は、上記課題を鑑みてなされたものであり、その目的は、簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供することである。

**【課題を解決するための手段】****【0009】**

本発明の一実施例による半導体装置の製造方法は以下の工程を備えている。

MOSトランジスタと第1の分離を含む素子形成領域を平面視において取り囲み、第3の半導体層および第2の半導体層を貫いて第1の半導体層の内部にまで達する第2の溝が形成される。ゲート電極の上を覆い、第2の溝の内部を埋め込む第2の絶縁膜が形成される。第2の溝内には中空が形成される。

50

**【発明の効果】****【0010】**

本実施例によれば、簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を実現することができる。

**【図面の簡単な説明】****【0011】**

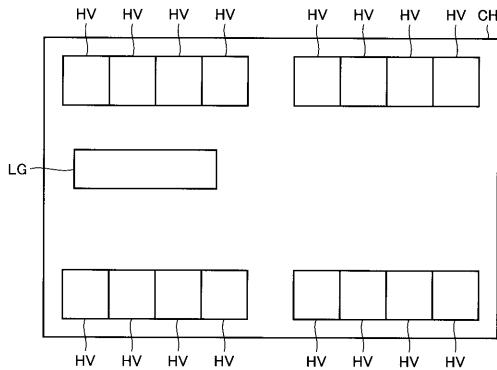

【図1】本発明の実施の形態1におけるチップ状態の半導体装置の構成を示す概略平面図である。

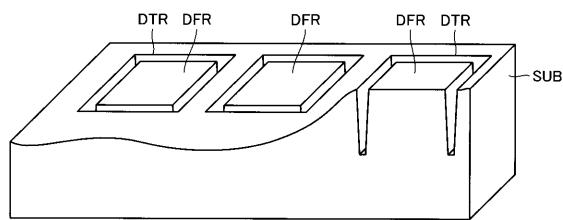

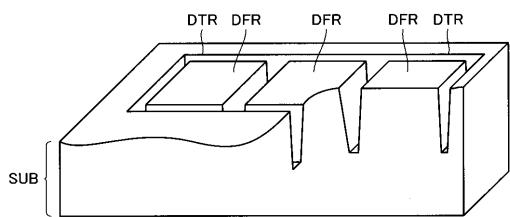

【図2】図1に示す素子形成領域が平面視において溝に取り囲まれた様子を示す一部破断斜視図である。

10

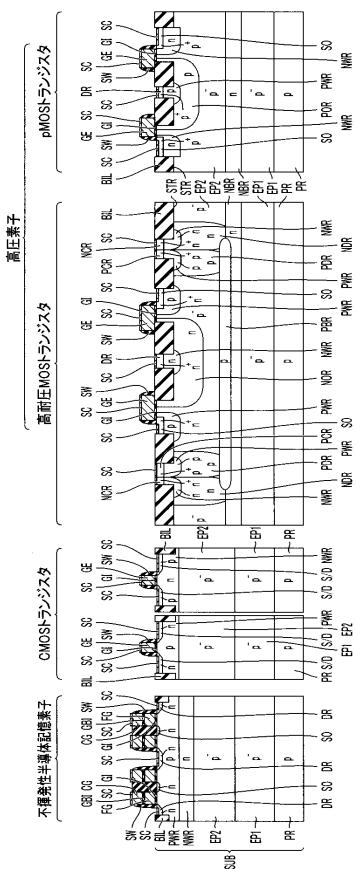

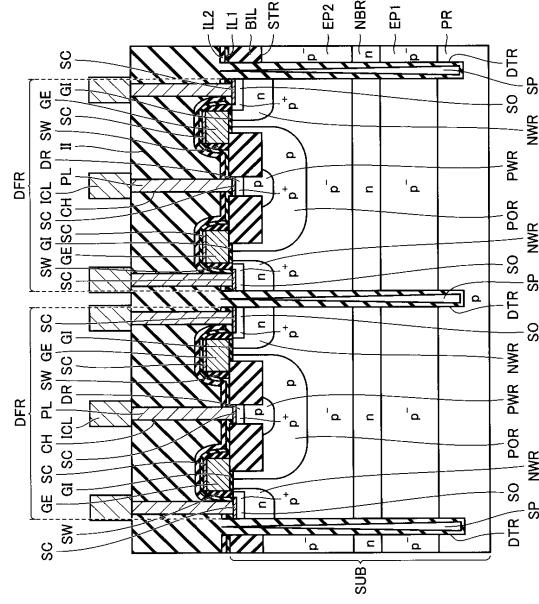

【図3】図2で溝に取り囲まれた素子であって、本発明の実施の形態1における半導体装置の構成を示す概略断面図である。

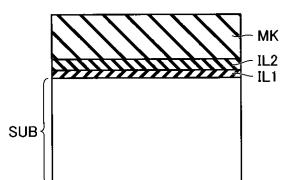

【図4】本発明の実施の形態1における半導体装置の製造方法の第1工程を示す概略断面図である。

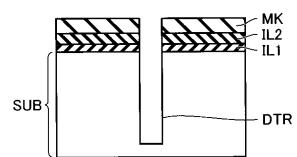

【図5】本発明の実施の形態1における半導体装置の製造方法の第2工程を示す概略断面図である。

【図6】本発明の実施の形態1における半導体装置の製造方法の第3工程を示す概略断面図である。

【図7】本発明の実施の形態1における半導体装置の製造方法の第4工程を示す概略断面図である。

20

【図8】本発明の実施の形態1における半導体装置の製造方法の第5工程を示す概略断面図である。

【図9】本発明の実施の形態1における半導体装置の製造方法の第6工程を示す概略断面図である。

【図10】本発明の実施の形態1における半導体装置の製造方法の第7工程を示す概略断面図である。

【図11】本発明の実施の形態1における半導体装置の製造方法の第8工程を示す概略断面図である。

【図12】本発明の実施の形態1における半導体装置の製造方法の第9工程を示す概略断面図である。

30

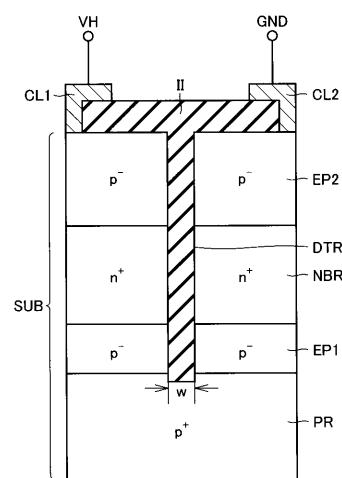

【図13】DTI構造の溝内に中空を設けた場合と設けない場合との素子評価試験に用いるサンプルの構成を示す概略断面図である。

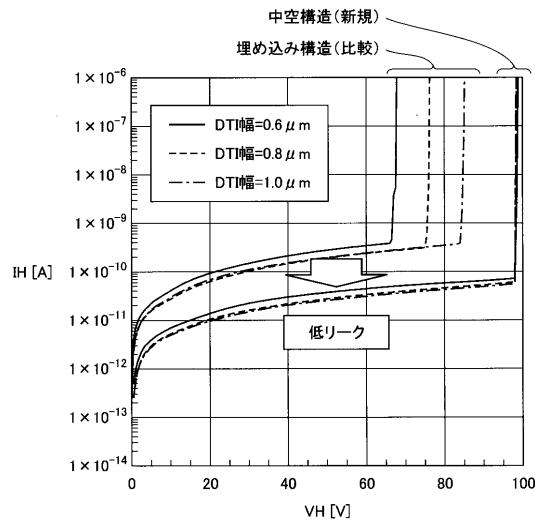

【図14】図13に示すサンプルの一方端子に電圧を印加した際に他方端子に流れる電流値を調べた結果を示す図である。

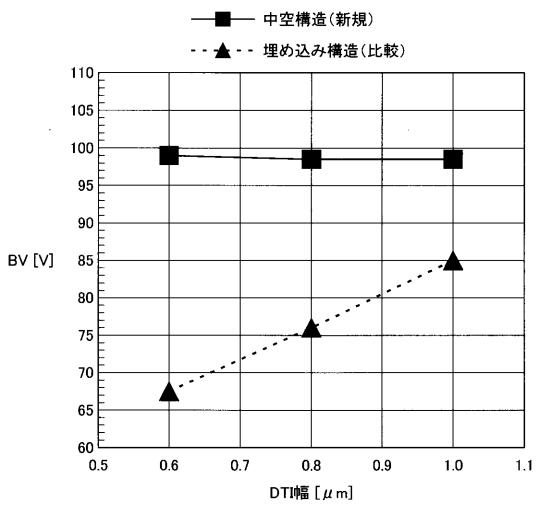

【図15】図13に示すサンプルのDTI構造の幅を変更したときのブレークダウン電圧を調べた結果を示す図である。

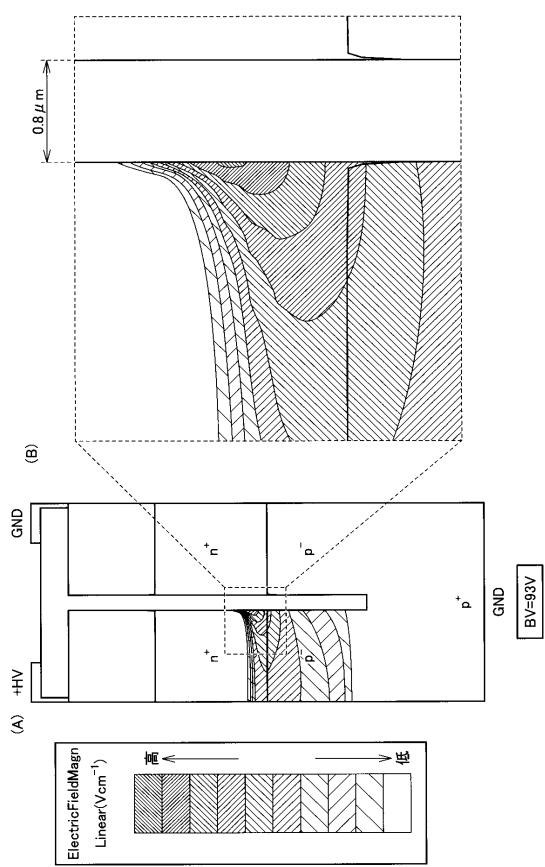

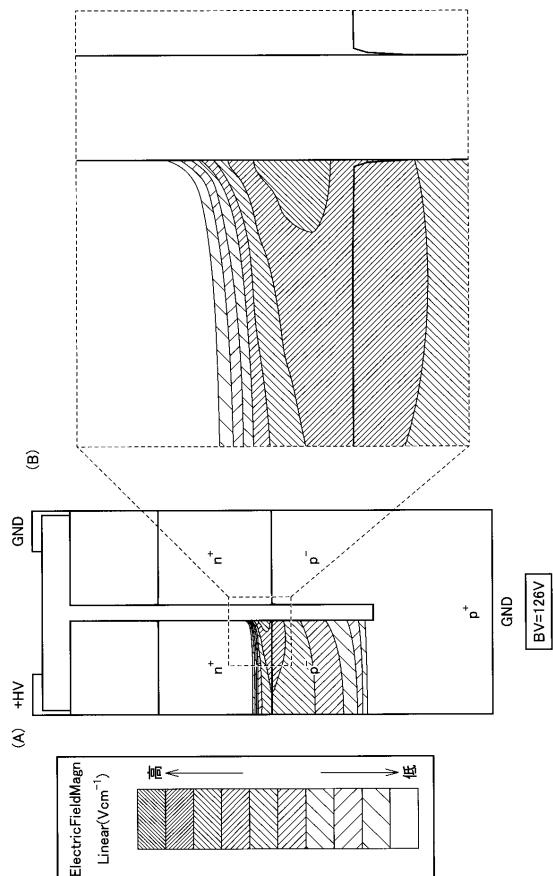

【図16】図13に示すサンプルにおいてDTI構造の溝内に中空を設けない場合の分離耐圧シミュレーションによるブレークダウン時の電界強度分布を示す図(A)およびその一部拡大図(B)である。

【図17】図13に示すサンプルにおいてDTI構造の溝内に中空を設ける場合の分離耐圧シミュレーションによるブレークダウン時の電界強度分布を示す図(A)およびその一部拡大図(B)である。

40

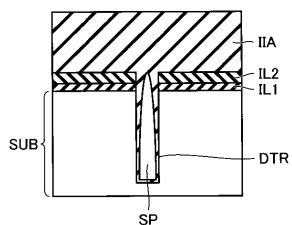

【図18】本発明の実施の形態2における半導体装置の製造方法の第1工程を示す概略断面図である。

【図19】本発明の実施の形態2における半導体装置の製造方法の第2工程を示す概略断面図である。

【図20】本発明の実施の形態2における半導体装置の製造方法の第3工程を示す概略断面図である。

【図21】本発明の実施の形態3における半導体装置の製造方法を示す概略断面図である。

50

【図22】本発明の実施の形態4における半導体装置の製造方法の第1工程を示す概略断面図である。

【図23】本発明の実施の形態4における半導体装置の製造方法の第2工程を示す概略断面図である。

【図24】本発明の実施の形態4における半導体装置の製造方法の第3工程を示す概略断面図である。

【図25】本発明の実施の形態5における半導体装置の製造方法の第1工程を示す概略断面図である。

【図26】本発明の実施の形態5における半導体装置の製造方法の第2工程を示す概略断面図である。 10

【図27】本発明の実施の形態5における半導体装置の製造方法の第3工程を示す概略断面図である。

【図28】DTIによる分離の一の構成を示す概略断面図である。

【図29】DTIによる分離の他の構成を示す概略断面図である。

【図30】DTIによる分離の他の構成を示す一部破断斜視図である。

#### 【発明を実施するための形態】

##### 【0012】

以下、本発明の実施の形態について図に基づいて説明する。

###### (実施の形態1)

図1を参照して、BiC-DMOS (Bipolar Complementary Double-diffused Metal Oxide Semiconductor) の半導体チップCHは、たとえば低耐圧のCMOS (Complementary MOS) ドバイ部LGと、高耐圧素子を用いた出力ドライバ部HVとを有している。上記のロジック部LGではその形成領域がDTI構造によって平面視において取り囲まれている。また出力ドライバ部HVでは素子の1つ1つの形成領域がDTI構造によって平面視において取り囲まれている。 20

##### 【0013】

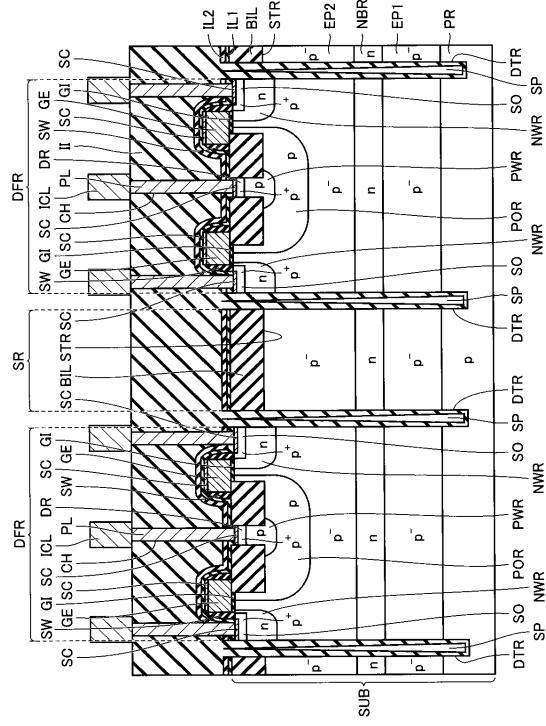

図2を参照して、たとえば出力ドライバ部HVでは、1つ1つの高耐圧素子の素子形成領域DFRがDTI構造をなす溝DTRにより平面的に取り囲まれている。この溝DTRは半導体基板SUBの表面に形成されている。

##### 【0014】

次に、上記の高耐圧素子として高耐圧の横型MOSトランジスタを用いた場合について説明する。 30

##### 【0015】

図3を参照して、半導体基板SUBはたとえばシリコンとなっており、主表面に選択的に溝STRを有している。この溝STR内には埋め込み絶縁膜BILが形成されている。この溝STRと埋め込み絶縁膜BILとによりSTI (Shallow Trench Isolation) 構造が構成されている。

##### 【0016】

半導体基板SUBのp型領域PR上にはp<sup>-</sup>エピタキシャル領域EP1と、n型埋め込み領域NBRとが形成されている。n型埋め込み領域NBR上には、p型埋め込み領域PBRが選択的に形成されている。これらn型埋め込み領域NBRおよびp型埋め込み領域PBR上には、p<sup>-</sup>エピタキシャル領域EP2が形成されている。 40

##### 【0017】

上記のp<sup>-</sup>エピタキシャル領域EP2内であって半導体基板SUBの表面に、高耐圧の横型MOSトランジスタが形成されている。この高耐圧の横型MOSトランジスタは、n型オフセット領域NORと、n型ウエル領域NWRと、p型ウエル領域PWRと、n<sup>+</sup>ドレイン領域DRと、n<sup>+</sup>ソース領域SOと、ゲート絶縁膜GIIと、ゲート電極層GEとを主に有している。

##### 【0018】

n型オフセット領域NORは、p<sup>-</sup>エピタキシャル領域EP2とpn接合を構成するよ

10

20

30

40

50

うに半導体基板 S U B の表面に形成されている。n 型ウエル領域 N W R は n 型オフセット領域 N O R と接するように形成されており、n<sup>+</sup>ドレイン領域 D R は n 型ウエル領域 N W R と接するように半導体基板 S U B の表面に形成されている。

#### 【 0 0 1 9 】

p 型ウエル領域 P W R は、p<sup>-</sup>エピタキシャル領域 E P 2 内であって半導体基板 S U B の表面に形成されている。n<sup>+</sup>ソース領域 S O は、p 型ウエル領域 P W R と p n 接合を構成するように半導体基板 S U B の表面に形成されている。n<sup>+</sup>ソース領域 S O と n 型オフセット領域 N O Rとの間には、半導体基板 S U B の表面に沿って p 型ウエル領域 P W R と p<sup>-</sup>エピタキシャル領域 E P 2 とが挟まれている。

#### 【 0 0 2 0 】

ゲート電極層 G E は、n<sup>+</sup>ソース領域 S O と n 型オフセット領域 N O R とに挟まる p 型ウエル領域 P W R と p<sup>-</sup>エピタキシャル領域 E P 2 とにゲート絶縁膜 G I を介在して対向するように半導体基板 S U B 上に形成されている。またゲート電極層 G E の一方端部は、n 型オフセット領域 N O R 内に形成された S T I 構造上に乗り上げている。ゲート電極層 G E の側壁を覆うように側壁絶縁膜 S W が形成されている。

#### 【 0 0 2 1 】

本実施の形態においては、n<sup>+</sup>ソース領域 S O 、n<sup>+</sup>ドレイン領域 D R およびゲート電極層 G E のそれぞれの表面上にシリサイド層 S C が形成されていることが好ましいが、シリサイド層 S C は省略されてもよい。

#### 【 0 0 2 2 】

また p<sup>-</sup>エピタキシャル領域 E P 2 内には、p 型埋め込み領域 P B R に接するように p 型シンカー (sinker) 領域 P D R が形成されており、この p 型シンカー領域 P D R の半導体基板 S U B の表面側に p 型ウエル領域 P W R と p<sup>+</sup>コンタクト領域 P C R とが形成されている。p<sup>+</sup>コンタクト領域 P C R と n<sup>+</sup>ソース領域 S O とを電気的に分離するために、p<sup>+</sup>コンタクト領域 P C R と n<sup>+</sup>ソース領域 S O との間の半導体基板 S U B の表面には S T I 構造が形成されている。

#### 【 0 0 2 3 】

また p<sup>-</sup>エピタキシャル領域 E P 2 内には、n 型埋め込み領域 N B R に接するように n 型シンカー領域 N D R が形成されており、この n 型シンカー領域 N D R の半導体基板 S U B の表面側に n 型ウエル領域 N W R と n<sup>+</sup>コンタクト領域 N C R とが形成されている。n<sup>+</sup>コンタクト領域 N C R と p<sup>+</sup>コンタクト領域 P C R とのそれぞれの表面上にはシリサイド層 S C が形成されていることが好ましいが、シリサイド層 S C は省略されてもよい。

#### 【 0 0 2 4 】

上記の高耐圧横型 M O S ドラゴンジスタ上を覆うように、絶縁膜 I L 1 、絶縁膜 I L 2 および層間絶縁膜 I I が順に積層されている。絶縁膜 I L 1 はたとえばシリコン酸化膜であり、絶縁膜 I L 2 はたとえばシリコン窒化膜である。層間絶縁膜 I I は、たとえば B P - T E O S (Boro-Phospho-Tetra-Ethyl-Ortho-Silicate) と、その上にプラズマ C V D (Chemical Vapor Deposition) 法により形成されたシリコン酸化膜との積層構造よりなっている。なお層間絶縁膜 I I に含まれる B P - T E O S (BPSG : Boro-Phosphate Silicate Glass) は、P - T E O S (PSG : Phosphorus Silicon Glass) 、 B - T E O S (BSG : Boro Silicata Glass) のような I I I 族元素および V 族元素の少なくともいずれかの不純物を含んだ絶縁膜であればよい。

#### 【 0 0 2 5 】

絶縁膜 I L 1 、絶縁膜 I L 2 および層間絶縁膜 I I にはコンタクトホール C H が形成されており、コンタクトホール C H 内にはプラグ導電層 P L が形成されている。層間絶縁膜 I I 上には配線層 I C L が形成されている。配線層 I C L はコンタクトホール C H 内のプラグ導電層 P L を介して高耐圧横型 M O S ドラゴンジスタの導電部分 (たとえばソース領域 S O 、ドレイン領域 D R 、コンタクト領域 N C R 、 P C R 、ゲート電極層 G E など) に電気的に接続されている。

#### 【 0 0 2 6 】

10

20

30

40

50

上記の高耐圧横型MOSトランジスタの形成領域を平面視において取り囲むようにDTI構造が形成されている。このDTI構造は、半導体基板SUBの表面から内部に延びる溝（第1の溝）DTRと、その溝DTR内に形成される絶縁膜IIとを有している。溝DTRは、半導体基板SUBの表面からp<sup>-</sup>エピタキシャル領域EP2、n型埋め込み領域NBRおよびp<sup>-</sup>エピタキシャル領域EP1を貫通してp型領域PRに達するように形成されている。

#### 【0027】

上記の溝DTR内に形成される絶縁膜IIは、高耐圧横型MOSトランジスタ上に形成される層間絶縁膜IIである。また溝DTR内は、絶縁膜IIで完全に埋め込まれてはおらず、溝DTRの内部には中空（空隙）SPが形成されている。

10

#### 【0028】

この中空SPは、n型埋め込み領域NBRとp<sup>-</sup>エピタキシャル領域EP1との接合部付近に少なくとも形成されていることが好ましい。中空SPは溝の深さとほぼ同じ高さを有していてもよい。溝DTRのアスペクト比（深さ／幅W）は1以上であることが好ましい。また溝DTRの幅Wは80Vのブレークダウン電圧を基準にして0.3μm以上であることが好ましい。

#### 【0029】

また溝DTRはSTI構造が形成された箇所に形成されてもよい。この場合、溝DTRはSTI構造の溝（第2の溝）STRが形成された領域においてその溝STRよりも深く形成されることになる。

20

#### 【0030】

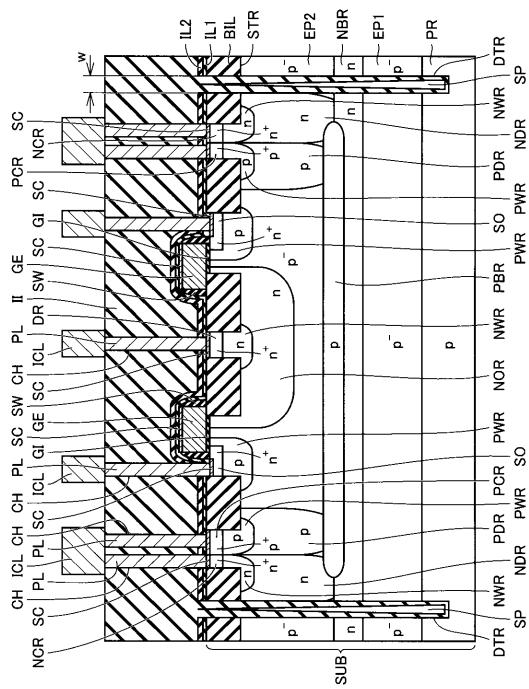

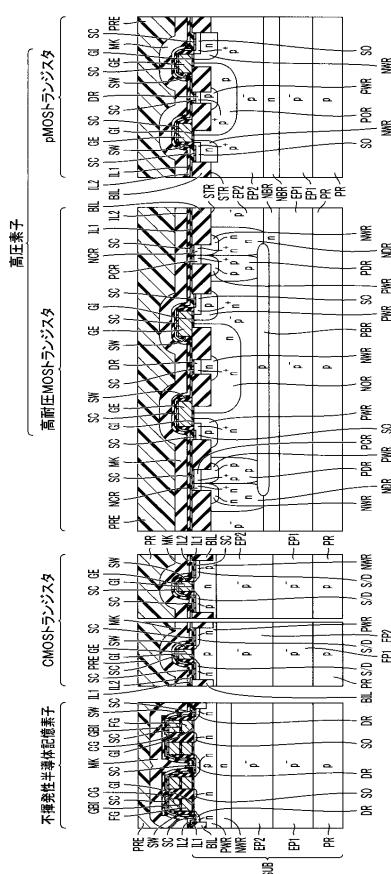

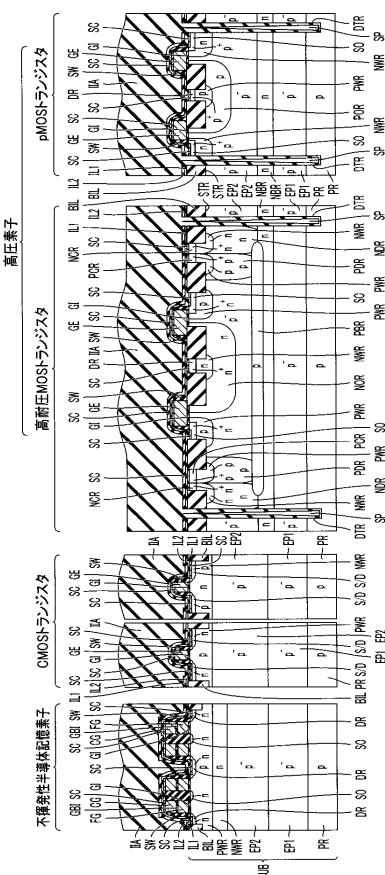

次に、本実施の形態の半導体装置として、高耐圧横型MOSトランジスタだけでなく、pチャネルMOSトランジスタ（pMOSトランジスタと称する）、CMOSトランジスタおよび不揮発性半導体メモリを有する半導体装置の製造方法について図4～図12を用いて説明する。

#### 【0031】

図4を参照して、まず半導体基板SUBの表面に、各素子（高耐圧横型MOSトランジスタ、pMOSトランジスタ、CMOSトランジスタ、不揮発性半導体記憶素子）が完成される。

#### 【0032】

高耐圧横型MOSトランジスタは、n型オフセット領域NORと、n型ウエル領域NWRと、p型ウエル領域PWRと、n<sup>+</sup>ドレイン領域DRと、n<sup>+</sup>ソース領域SOと、ゲート絶縁膜GIIと、ゲート電極層GEとを有するように形成される。

30

#### 【0033】

また高耐圧素子としてのpMOSトランジスタは、p型オフセット領域PORと、n型ウエル領域NWRと、p型ウエル領域PWRと、p<sup>+</sup>ドレイン領域DRと、p<sup>+</sup>ソース領域SOと、ゲート絶縁膜GIIと、ゲート電極層GEとを有するように形成される。

#### 【0034】

またCMOSトランジスタは、pMOSトランジスタとnMOSトランジスタとが完成するように形成される。pMOSトランジスタは、n型ウエル領域NWRと、1対のLDD（Lightly Doped Drain）構造のp型ソース／ドレイン領域S/Dと、ゲート絶縁膜GIIと、ゲート電極層GEとを有するように形成される。nMOSトランジスタは、p型ウエル領域PWRと、1対のLDD構造のn型ソース／ドレイン領域S/Dと、ゲート絶縁膜GIIと、ゲート電極層GEとを有するように形成される。

40

#### 【0035】

また不揮発性半導体記憶素子は、たとえばスタックゲート型のメモリトランジスタにより形成される。このスタックゲート型のメモリトランジスタは、p型ウエル領域PWRと、LDD構造のn型ドレイン領域DRと、n<sup>-</sup>ソース領域SOと、ゲート絶縁膜GIIと、フローティングゲート電極層FGと、ゲート間絶縁膜GBIと、コントロールゲート電極層CGとを有するように形成される。

50

## 【0036】

なお各素子のソース領域、ドレイン領域などの不純物領域の表面およびゲート電極の表面にはシリサイド層SCが形成されてもよい。また各素子のゲート電極層GE、FG、CGの側壁を覆うように側壁絶縁層SWが形成される。

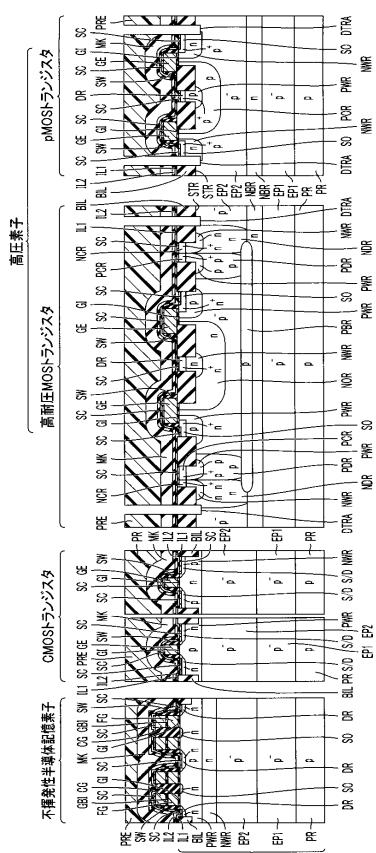

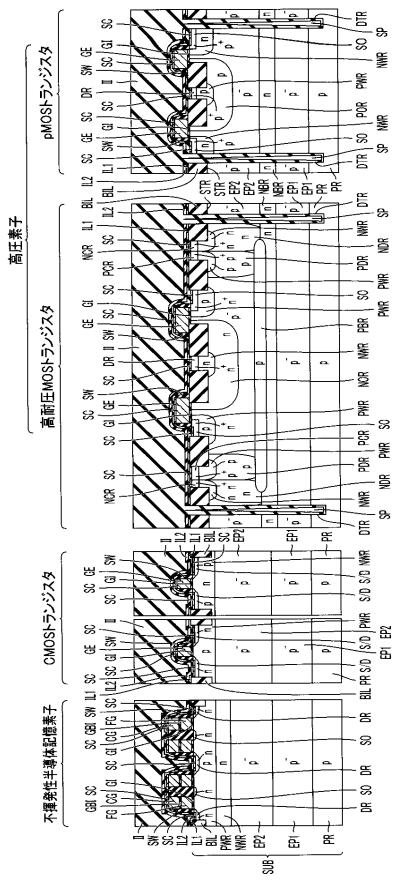

## 【0037】

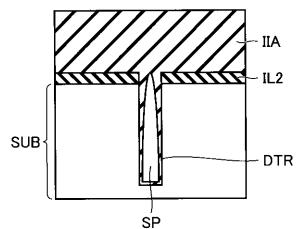

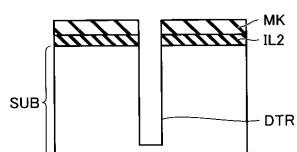

図5を参照して、各素子上を覆うように、絶縁膜IL1、絶縁膜IL2およびマスク材MKが順に積層される。絶縁膜IL1はたとえば20nmの厚みのノンドープのシリコン酸化膜より形成される。また絶縁膜IL2はたとえば50nmの厚みのシリコン窒化膜より形成される。マスク材MKはたとえば700nmの厚みのノンドープのシリコン酸化膜より形成される。このマスク材MK上に、フォトレジストPREが塗布される。

10

## 【0038】

図6を参照して、フォトレジストPREは通常の写真製版技術によりパターニングされる。このパターニングされたレジストパターンPREをマスクとして、マスク材MK、絶縁膜IL2、絶縁膜IL1およびSTI構造が順に異方性エッチングされる。これにより半導体基板SUBの表面に溝DTRが形成される。

## 【0039】

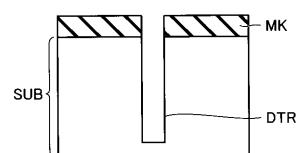

図7を参照して、引き続き、マスク材MKをマスクとして半導体基板SUBに異方性エッチングが施される。これにより、半導体基板SUBの表面からp+エピタキシャル領域EP2、n型埋め込み領域NBRおよびp+エピタキシャル領域EP1を貫通してp型領域PRに達する溝DTRが形成される。この後、マスク材MKが等方性エッチングにより除去される。

20

## 【0040】

図8を参照して、上記の等方性エッチングにより、絶縁膜IL2の上面が露出するとともに、溝DTRの壁面において露出していたSTI構造の埋め込み絶縁膜BILが図中横方向に膜減りする（後退する）。

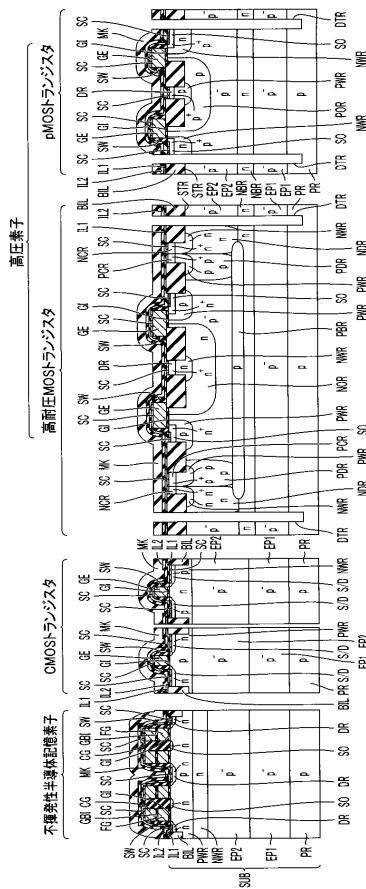

## 【0041】

図9を参照して、各素子上を覆うように、かつ溝DTR内に中空SPを形成するように各素子上および溝DTR内に絶縁膜IIAが形成される。この絶縁膜IIAは、たとえば1450nmの厚みのBPS-TEOSにより形成される。この絶縁膜IIAの上面がたとえばCMP(Chemical Mechanical Polishing)法により平坦化される。これにより絶縁膜IIAの厚みは、たとえば750nmとされる。

30

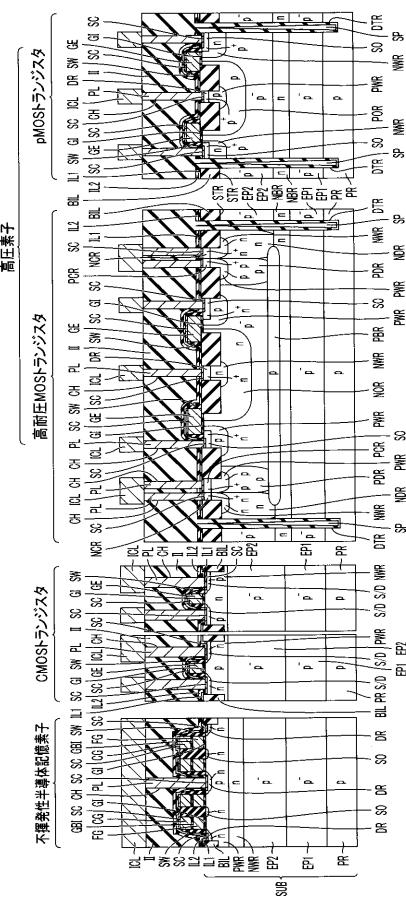

## 【0042】

図10を参照して、上記の絶縁膜IIA上に、プラズマCVD法によりシリコン酸化膜が形成される。この絶縁膜IIAとプラズマCVD法によるシリコン酸化膜とにより層間絶縁膜IIが形成される。

## 【0043】

図11を参照して、通常の写真製版技術およびエッチング技術により、層間絶縁膜II、絶縁膜IL2および絶縁膜IL1を貫通して半導体基板SUBの表面に達するコンタクトホールCHが形成される。このコンタクトホールCHからは、たとえばソース領域やドレイン領域などの表面に形成されたシリサイド層SCの表面が露出する。

40

## 【0044】

図12を参照して、コンタクトホールCH内にプラグ導電層PLが形成される。この後、プラグ導電層PLを介して各素子の導電部分と電気的に接続するように層間絶縁膜II上に配線層ICLが形成される。

## 【0045】

以上により、本実施の形態の半導体装置が製造される。

次に、DTI構造における溝DTR内に中空がある場合とない場合との特性（リーク電流、ブレークダウン電圧、ブレークダウン時の電界強度分布）の違いについて調べた結果を説明する。

## 【0046】

50

まず上記特性を調べるためのサンプルの構成について図13を用いて説明する。

図13を参照して、このサンプルでは、半導体基板SUBのp型領域PR上に、p<sup>-</sup>エピタキシャル領域EP1、n型埋め込み領域NBRおよびp<sup>-</sup>エピタキシャル領域EP2が順に積層して形成されている。半導体基板SUBには、その表面からp<sup>-</sup>エピタキシャル領域EP2、n型埋め込み領域NBRおよびp<sup>-</sup>エピタキシャル領域EP1を貫通してp型領域PRに達する溝DTRが形成されている。この溝DTR内には絶縁膜IIが形成されている。p<sup>-</sup>エピタキシャル領域EP2の溝DTRを挟んだ一方側には導電層CL1が電気的に接続されており、溝DTRを挟んだ他方側には導電層CL2が電気的に接続されている。

#### 【0047】

10

このサンプルにおける溝DTRの幅(DTI幅)Wを0.6μm、0.8μm、1.0μmとして一方側導電層CL1に印加する電圧VHを変化させたときの導電層CL1、CL2間に流れるリーク電流IHの値を調べた。その結果を図14に示す。

#### 【0048】

図14を参照して、いずれの溝DTRの幅Wにおいても、溝DTR内に中空SPがない場合にはリーク電流値が $1 \times 10^{-10} A \sim 1 \times 10^{-9} A$ となったのに対し、溝DTR内に中空SPがある場合にはリーク電流値が $1 \times 10^{-10} A$ 以下となった。このことから、溝DTR内に中空SPがない場合よりも中空SPがある場合の方がリーク電流値が低くなることが分かった。

#### 【0049】

20

また上記のサンプルにおいて溝DTRの幅(DTI幅)Wを変化させたときのブレークダウン電圧の変化を調べた。その結果を図15に示す。

#### 【0050】

図15を参照して、溝DTR内に中空SPがない場合には、溝DTRの幅Wが0.6μm、0.8μm、1.0μmと大きくなるにしたがってブレークダウン電圧BVが上がるものの、いずれのブレークダウン電圧値も8.5V以下であった。

#### 【0051】

30

これに対して溝DTR内に中空SPがある場合には、溝DTRの幅Wが0.6μm、0.8μm、1.0μmのいずれでも、ほとんどブレークダウン電圧BVの値は同じで、9.5V～10.0Vの範囲内であった。このことから、溝DTR内に中空SPがない場合よりも中空SPがある場合の方がブレークダウン電圧BVが高くなることが分かった。

#### 【0052】

また上記のサンプルにおいてDTI構造の溝DTR内に中空SPを設けない場合と設けた場合との分離耐圧シミュレーションによるブレークダウン時の電界強度分布を調べた。その結果を図16および図17に示す。

#### 【0053】

図16を参照して、DTI構造の溝DTR内に中空SPを設けない場合、溝DTRに接したn<sup>+</sup>埋め込み領域NBとp<sup>-</sup>エピタキシャル領域EP1との界面付近が最も高電界となっていることが分かる。またこのときのブレークダウン電圧BVは9.3Vであった。

#### 【0054】

40

図17を参照して、DTI構造の溝DTR内に中空SPを設けた場合、図16の場合と比較して、溝DTRに接したn<sup>+</sup>埋め込み領域NBとp<sup>-</sup>エピタキシャル領域EP1との界面付近での電界強度が緩和されることが分かった。またこのときのブレークダウン電圧は12.6Vであり、図16の場合よりも高くなることが分かった。

#### 【0055】

これらのことから、溝DTR内に中空SPがない場合よりも中空SPがある場合の方が、溝DTRに接する箇所での電界強度を緩和でき、ブレークダウン電圧が高くなることが分かった。

#### 【0056】

次に、本実施の形態の作用効果について説明する。

50

本実施の形態によれば、図4～図7に示すように高耐圧横型MOSトランジスタなどの素子が完成した後にDTI構造の溝DTRが形成されるため、その溝DTRを層間絶縁膜IL1で埋め込むことが可能となる。これにより、溝DTRを埋め込む絶縁膜を層間絶縁膜とは別途に形成する必要がなくなるため、製造方法における工程数を大幅に削減することができる。

#### 【0057】

また高耐圧横型MOSトランジスタなどの素子が完成した後にDTI構造の溝DTRが形成される。素子完成後の製造フローでは素子完成前の製造フローよりも溝DTR内を埋め込む絶縁膜表面がウエットエッチングにさらされる回数が少ない。このため、その溝DTR内に中空SPが存在していても、その中空SPが表面に露出することは抑制される。これにより、表面に露出した中空SP内にレジストなどの異物が入り込むことがないため、製造途中でその中空SP内の異物が噴出することによるパターンの欠陥が生じることも防止できる。10

#### 【0058】

また溝DTR内の中空SPが表面に露出することが防止されるため、溝DTR内に中空SPが存在してもよい。このため、溝DTR内の高い埋め込み性を確保する必要もなくなり、この点からも製造方法における工程数を削減することができる。

#### 【0059】

また溝DTR内に積極的に中空SPを形成することで、図13～図17を用いて説明したように、DTI構造により分離された素子のリーク電流を抑制することができ、ブレーカダウン電圧を高めることができ、かつ溝DTRに接する箇所の電界強度を緩和することができる。20

#### 【0060】

また溝DTR内に中空SPを形成することにより、空乏層の伸びを妨げるような隣接素子からの電界の働き（逆フィールドプレート効果）が抑制でき、結果として分離耐圧を高めることができる。また溝DTR内に中空SPを形成することにより、溝DTR内の応力を低減することができるため、その応力に起因する結晶欠陥の発生を抑制することができる。

#### 【0061】

またSTI構造が形成された領域にDTI構造が形成されているため、溝DTRの開口部での応力集中を緩和できる。これにより、結晶欠陥の発生をさらに抑制することができる。30

#### 【0062】

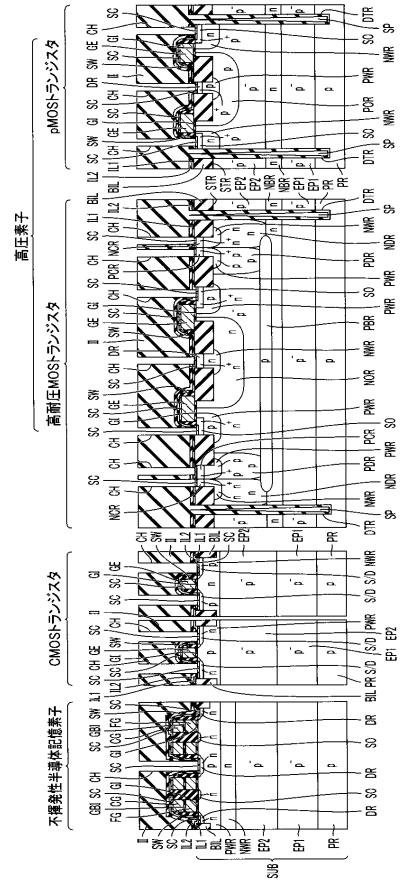

##### （実施の形態2）

実施の形態1においては、製造工程においてSTI構造が形成された領域にDTI構造を形成する場合について説明したが、STI構造が形成されていない領域にDTI構造が形成されてもよい。STI構造が形成されていない領域にDTI構造を形成する場合を実施の形態2として以下に説明する。

#### 【0063】

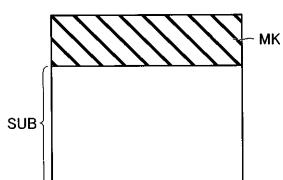

図18を参照して、半導体基板SUBの表面上に、絶縁膜IL1と絶縁膜IL2とマスク材MKとが順に積層して形成される。この工程は実施の形態1の図5に示すフォトレジストPREの形成前の工程に対応する。40

#### 【0064】

図19を参照して、通常の写真製版技術およびエッチング技術により、マスク材MK、絶縁膜IL2および絶縁膜IL1が順に異方性エッチングされる。

#### 【0065】

引き続き、パターニングされたマスク材MKをマスクとして半導体基板SUBに異方性エッチングが施される。これにより、半導体基板SUBの表面から内部に延びる溝DTRが形成される。この後、マスク材MKが等方性エッチングにより除去される。

#### 【0066】

図20を参照して、上記の等方性エッティングにより、絶縁膜IL2の上面が露出するとともに、溝DTRの壁面において露出していたSTI構造の埋め込み絶縁膜BILが図中横方向に膜減りする。各素子(図示せず)上を覆うように、かつ溝DTR内に中空SPを形成するように各素子上および溝DTR内に絶縁膜IIAが形成される。この絶縁膜IIAは、たとえばBP-TEOSにより形成される。

#### 【0067】

この後、図10～図12に示す実施の形態1と同様の工程を経ることにより、STI構造の形成されていない領域にDTI構造が形成された本実施の形態の半導体装置が製造される。

#### 【0068】

本実施の形態によれば、本実施の形態のDTI構造をSTI構造のない簡単な構成のデバイスに適用することが可能となる。

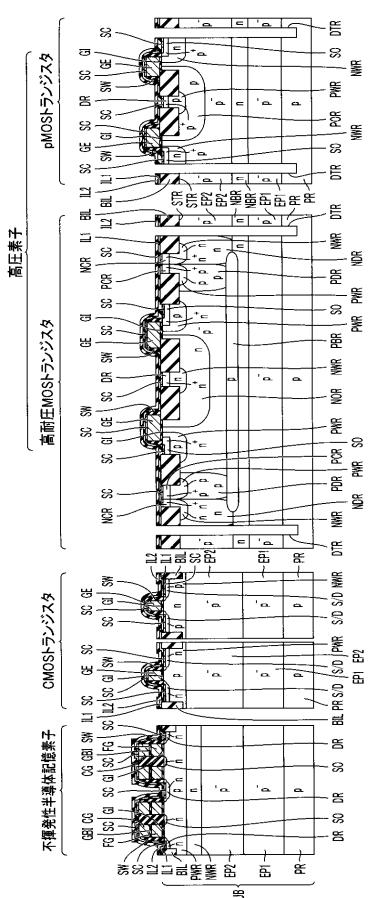

#### 【0069】

##### (実施の形態3)

実施の形態2においては、製造工程においてマスク材MKを等方性エッティングにより削除する場合について説明したが、マスク材MKは削除されずに残されてもよい。マスク材MKを残す場合を実施の形態3として以下に説明する。

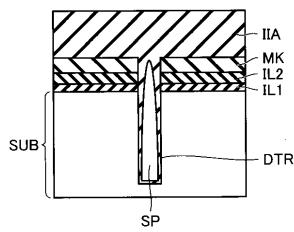

#### 【0070】

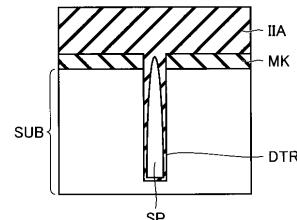

本実施の形態の製造方法は、図18および図19に示す実施の形態2と同様の工程を経る。この後、図21を参照して、マスク材MKを除去せずに残したまま、各素子(図示せず)上を覆うように、かつ溝DTR内に中空SPを形成するようにマスク材MK上および溝DTR内に絶縁膜IIAが形成される。

#### 【0071】

この後、図10～図12に示す実施の形態1と同様の工程を経ることにより、マスク材MKが削除されずに残された本実施の形態の半導体装置が製造される。

#### 【0072】

本実施の形態によれば、マスク材MKの除去工程を省略することができるため、さらなるコスト削減と工期短縮とを期待することができる。

#### 【0073】

##### (実施の形態4)

実施の形態2においては、製造工程において絶縁膜IL1と絶縁膜IL2とマスク材MKとを積層した場合について説明したが、絶縁膜IL1は省略されてもよい。絶縁膜IL1を省略する場合を実施の形態4として以下に説明する。

#### 【0074】

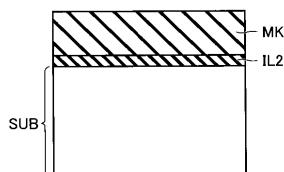

図22を参照して、半導体基板SUBの表面上に、絶縁膜IL2とマスク材MKとが順に積層して形成される。この工程は実施の形態1の図5に示すフォトレジストPRE形成前の工程に対応する。

#### 【0075】

図23を参照して、通常の写真製版技術およびエッティング技術により、マスク材MKおよび絶縁膜IL2が順に異方性エッティングされる。

#### 【0076】

引き続き、マスク材MKをマスクとして半導体基板SUBに異方性エッティングが施される。これにより、半導体基板SUBの表面から内部に延びる溝DTRが形成される。この後、マスク材MKが等方性エッティングにより除去される。

#### 【0077】

図24を参照して、上記の等方性エッティングにより、絶縁膜IL2の上面が露出するとともに、溝DTRの壁面において露出していたSTI構造の埋め込み絶縁膜BILが横方向に膜減りする。各素子上を覆うように、かつ溝DTR内に中空SPを形成するように各素子上および溝DTR内に絶縁膜IIAが形成される。

#### 【0078】

10

20

30

40

50

この後、図10～図12に示す実施の形態1と同様の工程を経ることにより、絶縁膜IL1の省略された本実施の形態の半導体装置が製造される。

#### 【0079】

本実施の形態によれば、絶縁膜IL1を省略することができるため、さらなるコスト削減と工期短縮とを期待することができる。

#### 【0080】

##### (実施の形態5)

実施の形態3においては、製造工程において絶縁膜IL1と絶縁膜IL2とマスク材MKとを積層した場合について説明したが、絶縁膜IL1と絶縁膜IL2とは省略されてもよい。絶縁膜IL1と絶縁膜IL2とを省略する場合を実施の形態5として以下に説明する。10

#### 【0081】

図25を参照して、半導体基板SUBの表面に直接接するようにマスク材MKが形成される。この工程は実施の形態1の図5に示すフォトレジストPRE形成前の工程に対応する。

#### 【0082】

図26を参照して、通常の写真製版技術およびエッチング技術により、マスク材MKが異方性エッチングされる。

#### 【0083】

引き続き、マスク材MKをマスクとして半導体基板SUBに異方性エッチングが施される。これにより、半導体基板SUBの表面から内部に延びる溝DTRが形成される。20

#### 【0084】

図27を参照して、マスク材MKを除去せずに残したまま、各素子上を覆うように、かつ溝DTR内に中空SPを形成するようにマスク材MK上および溝DTR内に絶縁膜IIAが形成される。

#### 【0085】

この後、図10～図12に示す実施の形態1と同様の工程を経ることにより、絶縁膜IL1および絶縁膜IL2の省略された本実施の形態の半導体装置が製造される。

#### 【0086】

本実施の形態によれば、絶縁膜IL1および絶縁膜IL2を省略することができるため、さらなるコスト削減と工期短縮とを期待することができる。30

#### 【0087】

##### (実施の形態6)

図28に示すように、DTI構造により取り囲まれた素子形成領域DFR(図においてはpMOSトランジスタ形成領域)同士は、所定の領域SRを挟んで隣り合うように配置されていてもよい。この場合、所定の領域SRにおける半導体基板SUBの表面にはSTI構造が形成されていてもよい。このSTI構造は上述したように、半導体基板SUBの表面に形成された溝STRと、その溝STR内を埋め込む絶縁膜BILとを有している。

#### 【0088】

また図29および図30に示すように、DTI構造により取り囲まれた素子形成領域DFR同士は、DTI構造をなす1本の溝DTRのみを挟んで隣り合うように配置されてもよい。

#### 【0089】

各素子形成領域DFR間に1本の溝DTRのみを挟む場合には、隣り合う各素子形成領域DFRに、同じ種類の素子が形成されていることが好ましい。つまり、隣り合う一方の素子形成領域にpMOSトランジスタが形成されている場合には、隣り合う他方の素子形成領域にもpMOSトランジスタが形成されていることが好ましい。

#### 【0090】

このように隣り合う素子形成領域DFRの各々に同じ種類の素子が形成されていれば、素子形成領域DFR間に挟まれる溝DTRの両側に同じウエル領域(pMOSトランジス40

タの場合にはn型ウエル領域)が位置することになり、溝DTR形成前のウエル領域の拡散による問題が生じないからである。

#### 【0091】

なお上記の実施の形態1~6においては、素子形成領域DFRに形成される素子として高耐圧MOSトランジスタについて説明したが、本発明はこれ以外にIGBT(Insulated Gate Bipolar Transistor)、ダイオードなどの素子に適用されてもよく、これ以外の高耐圧素子などに適用されてもよい。

#### 【0092】

また製造プロセスにおける素子の完成とは、その素子がその機能を発揮するために必要な主たる要素が形成されたことを意味する。素子の完成とは、具体的には、たとえばダイオードの場合においてはアノード領域とカソード領域とが形成されたことを意味し、たとえばMIS(Metal Insulator Semiconductor)トランジスタの場合においてはソース領域と、ドレイン領域と、ゲート絶縁膜と、ゲート電極が形成されたことを意味し、たとえばIGBTの場合においてはエミッタ領域、ベース領域、ドリフト領域、コレクタ領域、ゲート絶縁膜およびゲート電極が形成されたことを意味する。

#### 【0093】

また実施の形態1~5においては、層間絶縁膜IIとしてたとえばBPTEOSとプラズマCVD法により形成されたシリコン酸化膜との積層構造について説明したが、層間絶縁膜IIはこれに限定されるものではなく、異なる材質からなっていてもよく、また単層からなっていてもよい。また溝DTR内に形成される層間絶縁膜とは、下層の素子と上層の配線などの導電層とを電気的に分離するための絶縁膜であって、上面が平坦化処理されたものを含む。

#### 【0094】

また上記全ての実施の形態において、層間絶縁膜II中のB(ボロン)やP(リン)の固相拡散を防ぐ必要がある場合には、層間絶縁膜IIを堆積する前に、溝DTRの内壁に、酸化、窒化あるいはCVD法によってシリコン酸化膜、シリコン窒化膜などの絶縁膜(ライナー膜)が形成されてもよい。

#### 【0095】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

#### 【産業上の利用可能性】

#### 【0096】

本発明は、溝を有する半導体装置およびその製造方法に特に有利に適用され得る。

#### 【符号の説明】

#### 【0097】

BIL 絶縁膜、CG コントロールゲート電極層、CH コンタクトホール、CL1, CL2 導電層、DFR 素子形成領域、DR ドレイン領域、DTR, STR 溝、EP1, EP2 エピタキシャル領域、FG フローティングゲート電極層、GBI ゲート間絶縁膜、GE ゲート電極層、GI ゲート絶縁膜、HV 出力ドライバ部、ICL 配線層、II 層間絶縁膜、IIA, IL1, IL2 絶縁膜、IL 配線層、LG ロジック部、MK マスク材、NB n<sup>+</sup>埋め込み領域、NBR n型埋め込み領域、NCR n<sup>+</sup>コンタクト領域、NDR n型シンカー領域、NOR n型オフセット領域、NWR n型ウエル領域、PBR p型埋め込み領域、PCR p<sup>+</sup>コンタクト領域、PDR p型シンカー領域、PL プラグ導電層、POR p型オフセット領域、PRE フォトレジスト、PR p型領域、PWR p型ウエル領域、S/D ソース/ドレイン領域、SC シリサイド層、SO ソース領域、SP 中空、SR 所定領域、SUB 半導体基板。

10

20

30

40

【図1】

【 四 2 】

【 四 4 】

【 叁 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図24】

【図25】

【図21】

【図22】

【図23】

【図26】

【図27】

【図28】

【図29】

【図30】

---

フロントページの続き

|                          |                    |

|--------------------------|--------------------|

| (51)Int.Cl.              | F I                |

| H 01 L 21/8247 (2006.01) | H 01 L 29/78 3 7 1 |

| H 01 L 27/115 (2006.01)  |                    |

| H 01 L 21/336 (2006.01)  |                    |

| H 01 L 29/788 (2006.01)  |                    |

| H 01 L 29/792 (2006.01)  |                    |

(72)発明者 木村 広嗣

東京都千代田区大手町二丁目 6 番 2 号 株式会社ルネサステクノロジ内

(72)発明者 新田 哲也

東京都千代田区大手町二丁目 6 番 2 号 株式会社ルネサステクノロジ内

(72)発明者 柳 振一郎

東京都千代田区大手町二丁目 6 番 2 号 株式会社ルネサステクノロジ内

(72)発明者 森井 勝巳

兵庫県伊丹市瑞原 4 丁目 1 番地 株式会社ルネサスセミコンダクタエンジニアリング内

審査官 右田 勝則

(56)参考文献 特開平 09 - 008119 (JP, A)

特開 2009 - 032967 (JP, A)

特開 2005 - 332959 (JP, A)

特開 2009 - 164460 (JP, A)

国際公開第 2007 / 142969 (WO, A1)

特開 2002 - 184854 (JP, A)

特開 2002 - 280447 (JP, A)

特開 2003 - 152071 (JP, A)

特開 2006 - 049828 (JP, A)

特表 2009 - 539260 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|                     |

|---------------------|

| H 01 L 21 / 7 6     |

| H 01 L 21 / 3 3 6   |

| H 01 L 21 / 7 6 4   |

| H 01 L 21 / 8 2 4 7 |

| H 01 L 21 / 8 2 4 9 |

| H 01 L 27 / 0 6     |

| H 01 L 27 / 0 8     |

| H 01 L 27 / 1 1 5   |

| H 01 L 29 / 7 8 8   |

| H 01 L 29 / 7 9 2   |