(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4274597号 (P4274597)

(45) 発行日 平成21年6月10日(2009.6.10)

(24) 登録日 平成21年3月13日(2009.3.13)

(51) Int. Cl. F. I.

G 1 1 C 11/4074 (2006.01) G 1 1 C 11/413 (2006.01) G11C 11/34 354F G11C 11/34 335A

請求項の数 4 (全 14 頁)

(21) 出願番号 特願平10-148899

(22) 出願日 平成10年5月29日 (1998.5.29)

(65) 公開番号 特開平11-339472

(43) 公開日 平成11年12月10日 (1999.12.10) 審査請求日 平成17年5月25日 (2005.5.25) (73)特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

||(74)代理人 100064746

弁理士 深見 久郎

||(74)代理人 100085132

弁理士 森田 俊雄

|(74)代理人 100083703

弁理士 仲村 義平

|(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100098316

弁理士 野田 久登

|(74)代理人 100109162

弁理士 酒井 將行

最終頁に続く

# (54) 【発明の名称】半導体集積回路装置

# (57)【特許請求の範囲】

# 【請求項1】

半導体集積回路装置であって、

外部電源電位より低い内部電源電位を受けて動作する内部回路と、

前記外部電源電位を伝達する外部電源配線と、

前記内部電源電位を前記内部回路に伝達する第1の内部電源配線と、

前記外部電源配線から供給される外部電源電位を受けて前記内部電源電位に変換し、前記第1の内部電源配線に供給する第1の電圧変換手段とを備え、

前記第1の電圧変換手段は、

前記内部電源電位の基準値である参照電位を生成する参照電位発生手段と、

前記第1の内部電源配線の電位が前記参照電位より低い場合に、前記外部電源配線から前記第1の内部電源配線に、第1の電流駆動能力で電流を供給する第1の電圧降下手段と

前記内部回路の活性化に応じて動作し、前記第1の内部電源配線の電位が前記参照電位より低い場合に、前記外部電源配線から前記第1の内部電源配線に、前記第1の電流駆動能力より高い第2の電流駆動能力で電流を供給する第2の電圧降下手段と、

前記第2の電流駆動能力を前記半導体集積回路装置の動作周波数に応じて制御する駆動 能力制御手段とを含み、

前記駆動能力制御手段は、

前記内部回路の活性時に、前記動作周波数に対応した周期を有する外部クロック信号を

受けて、第1の電圧レベルと第2の電圧レベルとを有する周期的な2値信号であり、前記動作周波数に応じて、前記第1の電圧レベルとなる第1の期間と前記第2電圧レベルとなる第2の期間の比率を調整した制御パルス信号を生成する制御パルス信号生成手段と、

前記制御パルス信号の前記第1の期間と前記第2の期間との比率に応じた電圧レベルを 有する前記制御信号を生成する制御信号生成手段とを含み、

前記第2の電圧降下手段は、

前記内部電源電位を供給する第1の内部電源配線の電位と前記参照電位との差を増幅して出力する差動増幅手段と、

前記外部電源配線と前記第1の内部電源配線との間に接続され、前記差動増幅手段の出力を受けて、前記第1の内部電源配線の電位が前記参照電位より低い場合に前記外部電源配線から前記第1の内部電源配線に電流を供給する電流供給手段と、

前記制御信号の電圧レベルに応じた電流を前記差動増幅手段に供給することにより、前記第2の電流駆動能力を制御する電流制御手段とを含む、半導体集積回路装置。

# 【請求項2】

前記制御パルス信号生成手段は、

前記外部クロックを遅延させた遅延信号を出力する遅延回路と、

前記外部クロック信号と前記遅延信号とが入力され、前記制御パルス信号を出力する論理回路とを有し、

前記制御信号生成手段は、

ソースが前記第1の内部電源配線と結合する第1導電型の第1のMOSトランジスタと

`

前記第1導電型のMOSトランジスタを介して、前記第1の内部電源配線と結合する内部 ノードと、

前記第1の内部電源配線に対応する接地配線と、

前記内部ノードと前記接地配線との間に結合される第2導電型の第2のMOSトランジスタと、

前記内部ノードと前記接地配線との間に結合されるキャパシタと、

前記内部ノードの電位を平滑して前記制御信号を出力するローパスフィルタとを含み、 前記第1および第2のMOSトランジスタは、前記制御パルス信号を各々の制御電極に 受けて導通状態が制御され、

前記キャパシタは、前記第1および第2のMOSトランジスタの導通状態に応じて前記内部ノードの電位を調整する請求項1記載の半導体集積回路装置。

### 【請求項3】

前記制御パルス信号生成手段は、

前記外部クロック信号を分周する分周手段をさらに有し、

前記分周手段によって得られた信号の周波数に基づいて、前記制御パルス信号を生成する、請求項 1 記載の半導体集積回路装置。

# 【請求項4】

前記外部電源配線から前記外部電源電位を受けて前記内部電源電位に変換する第2の電圧変換手段と、

前記第2の電圧変換手段から前記内部電源電位を伝達する前記第2の内部電源配線とを

前記第1導電型の<u>第1のMOS</u>トランジスタのソースは、前記第2の内部電源配線と結合する、請求項2に記載の半導体集積回路装置。

【発明の詳細な説明】

# [0001]

# 【発明の属する技術分野】

本発明は、外部より供給された電源電位をより低い内部電源電位に変換する電圧降下回路 (Voltage Down Converter; VDC)を備える半導体集積回路装置に関し、動作周波数に 応じた電流駆動能力を制御することができる電圧降下回路の構成に関するものである。

20

10

30

40

#### [0002]

# 【従来の技術】

近年、LSIメモリの低電圧動作化が進んでいる。その中で、半導体集積回路装置内部のトランジスタは、外部から印加される電源電圧よりも低い電圧によって、動作することが強く要求されるようになっている。LSIメモリの消費電力の低減およびトランジスタの微細化に伴う信頼性の確保が低電圧化の主な目的である。

#### [0003]

特に、DRAM (Dynamic Random Access Memory)では、メモリセルにおける容量蓄積部となるキャパシタの誘電体膜の信頼性確保の面から、低電圧化は重要な課題である。

#### [0004]

これらの理由によって、半導体集積回路装置の内部素子を駆動する電源電圧の上限は、世代を追うにつれて全体システムで用いられる外部電源電圧に対して低下してきている。

#### [0005]

この要求に応えるために、外部電源から供給された電圧を受けて、半導体集積回路装置内部において安定した内部電源電圧を発生する回路として電圧降下回路が設けられている。

#### [0006]

図11は、従来の電圧降下回路の一般的な構成を示すための概略ブロック図である。

### [00007]

図11を参照して、電圧降下回路10は、外部電源電圧(以下Ext. Vccという)を外部電源配線70より受けて、変換された内部電源電圧(以下Int. Vccという)を内部電源配線80に出力する。内部電源配線80は、Int. Vccを周辺回路21,アレイ制御回路22等へ供給する。

# [00008]

電圧降下回路10は、Int.Vccのレベルの基準値である参照電位(以下Vref.という)を生成する基準電位発生部11と、Vref.に基づいて、Ext.VccをInt.Vccに変換する電圧降下部12とを含む。

#### [0009]

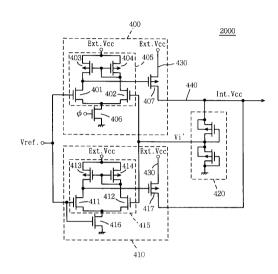

図12は、複数の電圧降下部を含む従来の構成の電圧降下回路2000の回路図である。

# [0010]

図12を参照して、電圧降下回路2000は、電圧降下部12として活性時用電圧降下回路400(以下活性時用VDCという)と待機時用電圧降下回路410(以下待機時用VDCという)とを含む。さらに、電圧降下回路2000は、Int.Vccを分圧し、上記活性時用VDC400および待機時用VDC410にフィードバックする分圧回路420とを含む。また、内部電源配線440は、内部回路群に負荷電流を供給する。

# [0011]

まず、上記活性時用VDC400の動作を説明する。

活性時用VDC400は、カレントミラータイプの差動増幅器405を構成するトランジスタ401~404と、トランジスタ401~404の駆動電流を制御する電流制御トランジスタ406と、外部電源配線430と内部電源配線440との間に接続されるP型のドライバトランジスタ407とを備える。

# [0012]

差動増幅器405は、Vref.と分圧回路420によって分圧されたInt.Vccである電圧Vi とをトランジスタ401および402のゲートに受けて、両者の差を増幅してドライバトランジスタ407のゲートに出力する。

#### [0013]

上記 V i が V r e f . より低い、すなわち I n t . V c c の電位が所望のレベルより低下している場合、差動増幅器 4 0 5 は、両者の電位差が増幅されたマイナスの電位を、ドライバトランジスタ 4 0 7 はゲート電位の低下に見合う電流を、外部電源配線 4 3 0 から内部電源配線 4 4 0 に供給する。これにより、 I n t . V c c の電位は回復する。

10

20

30

40

#### [0014]

一方、上記 V i が V r e f . とほぼ等しい場合、すなわち I n t . V c c が所望のレベルである場合には、差動増幅器 4 0 5 によって、ドライバトランジスタ 4 0 7 は非導通となり、内部電源配線 4 4 0 には電流が供給されない。

# [0015]

上記の動作により、Int.Vccは所望の一定レベルに保たれる。

しかし、実際にはInt.Vccの変動をフィードバックして差動増幅器405で増幅し、ドライバトランジスタ407のゲート電位を変化させて内部電源配線440に電流を供給する一連の動作は、時間的な遅延を生じさせる。

#### [0016]

このため、Int.Vccのレベルには、アンダーシュートやオーバーシュートといった過渡的な変動が生じる。

#### [0017]

この変動を改善するために、差動増幅器405の応答性を向上させて、VDCの電流駆動能力を大きくする必要がある。具体的には、差動増幅器405を構成するトランジスタ401~404の駆動電流を大きくすることが必要である。

#### [0018]

しかし、トランジスタの駆動電流を大きくすることは、消費電力の増大につながる。

#### [0019]

一般に、半導体集積回路装置は、動作選択がなされた場合(以下活性化時という)と、それ以外の場合(以下待機時という)では、内部回路群で消費される負荷電流が大きく異なる。

# [0020]

よって、負荷電流が大きい活性化時には、Int.Vccの安定化を図るためにVDCの電流駆動能力を大きくする必要がある一方で、Int.Vccの変動が小さい待機時には、VDCの電流駆動能力は小さいもので十分である。

### [0021]

そこで、Int.Vccの変動に対する良好な追従性と、消費電力の低減とを両立するために、待機時用VDC410が必要となる。待機時用VDC410の基本的な構成および動作は活性時用VDCと同じである。

# [0022]

しかし、待機時用 V D C 4 1 0 において、電流制御トランジスタ 4 1 6 は、差動増幅器 4 1 5 を構成するトランジスタ 4 1 1 ~ 4 1 <u>4</u> に、常に一定の微小電流を供給するように 線型領域で動作する。

# [0023]

一方、活性時用 V D C 4 0 0 において、電流制御トランジスタ 4 0 6 は、活性化時に"H"レベル,待機時に"L"レベルをとる活性化信号 をゲートに受けて、活性化時にのみ導通し、待機時は非導通となるように飽和領域で動作する。これにより、活性時用 V D C は、活性化時にのみ電流駆動能力が大きい状態で作動する。

### [0024]

以上のように、駆動電流の小さい差動増幅器を備えた電流駆動能力が小さく消費電流の少ない待機時用VDCと、駆動電流の大きい差動増幅器を備えた電流駆動能力の大きい活性時用VDCとを並列に配置して、必要な場合にのみ活性時用VDCを動作させることにより、常時消費されるスタンバイ電流を増加させずに、活性化時のInt.Vccの電圧変動に対する応答特性が良好な電圧降下回路を得ることができる。

# [0025]

このような構成の電圧降下回路については、たとえば超 L S I メモリ ( 伊藤清男著 , 培風館 ) p p . 3 0 7 ~ 3 1 0 に記載されている。

# [0026]

【発明が解決しようとする課題】

10

20

30

しかしながら、デバイス動作の高速化に伴い、電圧降下回路の応答特性の問題は、さらに 重要視されている。

#### [0027]

動作周波数に応じた外部クロック信号が印加されるたびに、データの書込や読出といった 動作が行なわれるため、活性化時における半導体集積回路装置の負荷電流は、動作周波数 に伴って変化する。

#### [0028]

デバイスの高速化に伴って、半導体集積回路装置は、より幅広い動作周波数の下で動作するようになっており、たとえば、汎用品のメモリを考えた場合、従来の技術によって高速動作に対応するように設計された電圧降下回路を搭載した半導体集積回路装置は、組込まれたシステムの動作周波数が低い時には、無駄な電流を消費してしまう。

### [0029]

この発明は、上記のような問題点を解決するためになされたものであって、その目的は、 幅広い動作周波数の下で十分な応答特性と消費電力の抑制とを両立できる構成を有する電 圧降下回路を備えた、半導体集積回路装置を提供することである。

#### [0030]

# 【課題を解決するための手段】

請求項1記載の半導体集積回路装置は、外部電源電位より低い内部電源電位を受けて動 作する内部回路と、外部電源電位を伝達する外部電源配線と、内部電源電位を内部回路に 伝達する第1の内部電源配線と、外部電源配線から供給される外部電源電位を受けて内部 電源電位に変換し、第1の内部電源配線に供給する第1の電圧変換手段とを備え、第1の 電圧変換手段は、内部電源電位の基準値である参照電位を生成する参照電位発生手段と、 第1の内部電源配線の電位が参照電位より低い場合に、外部電源配線から第1の内部電源 配線に、第1の電流駆動能力で電流を供給する第1の電圧降下手段と、内部回路の活性化 に応じて動作し、第1の内部電源配線の電位が参照電位より低い場合に、外部電源配線か ら第1の内部電源配線に、第1の電流駆動能力より高い第2の電流駆動能力で電流を供給 する第2の電圧降下手段と、第2の電流駆動能力を半導体集積回路装置の動作周波数に応 じて制御する駆動能力制御手段とを含み、駆動能力制御手段は、内部回路の活性時に、動 作周波数に対応した周期を有する外部クロック信号を受けて、第1の電圧レベルと第2の 電圧レベルとを有する周期的な2値信号であり、動作周波数に応じて、第1の電圧レベル となる第1の期間と第2電圧レベルとなる第2の期間の比率を調整した制御パルス信号を 生成する制御パルス信号生成手段と、制御パルス信号の第1の期間と第2の期間との比率 に応じた電圧レベルを有する制御信号を生成する制御信号生成手段とを含み、第2の電圧 降下手段は、内部電源電位を供給する第1の内部電源配線の電位と参照電位との差を増幅 して出力する差動増幅手段と、外部電源配線と第1の内部電源配線との間に接続され、差 動増幅手段の出力を受けて、第1の内部電源配線の電位が参照電位より低い場合に外部電 源配線から第1の内部電源配線に電流を供給する電流供給手段と、制御信号の電圧レベル に応じた電流を差動増幅手段に供給することにより、第2の電流駆動能力を制御する電流 制御手段とを含む。

# [0031]

請求項2記載の半導体集積回路装置は、請求項1記載の半導体集積回路装置において、制御パルス信号生成手段は、外部クロックを遅延させた遅延信号を出力する論理回路とを有し、制御信号生成手段は、ソースが第1の内部電源配線と結合する第1導電型の第1のMOSトランジスタと、第1導電型のMOSトランジスタを介して、第1の内部電源配線と結合する内部ノードと、第1の内部電源配線に対応する接地配線と、内部ノードと接地配線との間に結合される第2導電型の第2のMOSトランジスタと、内部ノードと接地配線との間に結合されるキャパシタと、内部ノードの電位を平滑して制御信号を出力するローパスフィルタとを含み、第1および第2のMOSトランジスタは、制御パルス信号を各々の制御電極に受けて導通状態が制御され、キャパシタは、第1および第2のMOSトランジ

10

20

30

40

# スタの導通状態に応じて内部ノードの電位を調整する。

#### [0033]

請求項<u>3</u>記載の半導体集積回路装置は、請求項<u>1</u>記載の半導体集積回路装置において、制御パルス信号生成手段は、外部クロック信号を分周する分周手段をさらに有し、分周手段によって得られた信号の周波数に基づいて、制御パルス信号を生成する。

#### [0034]

請求項<u>4</u>記載の半導体集積回路装置は、請求項<u>2</u>に記載の半導体集積回路装置であって、外部電源配線から外部電源電位を受けて内部電源電位に変換する第2の電圧変換手段と、第2の電圧変換手段から内部電源電位を伝達する第2の内部電源配線とをさらに備え、第1導電型の第1のMOSトランジスタのソースは、第2の内部電源配線と結合する。

[0035]

【発明の実施の形態】

「実施の形態1]

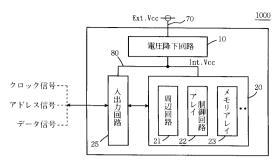

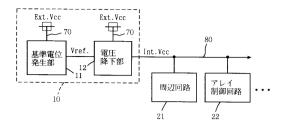

図1は、この発明の実施の形態の半導体集積回路装置1000の全体構成を示す概略プロック図である。

[0036]

図1を参照して、半導体集積回路装置1000は、外部電源配線70より受けた外部電源電圧E×t.Vccを内部電源電圧Int.Vccに変換する電圧降下回路10と、内部電源配線80よりInt.Vccを受けて動作する周辺回路21,アレイ制御回路22,メモリアレイ23等からなる内部回路群20と、クロック信号,アドレス信号,データ等を外部と授受し内部回路群20とこれらの信号を授受する入出力回路25とを備える。

[0037]

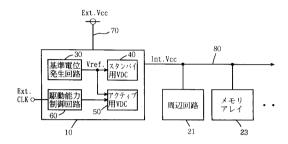

図2は、図1のうち電圧降下回路10の構成をより詳細に示すブロック図である。

[0038]

図2を参照して、電圧降下回路10は、Int.Vccの基準値であるVref.を生成する基準電位発生回路30と、待機時に動作する電流駆動能力の小さい電圧降下回路(以下スタンバイ用VDCという)40と、活性化時に動作する電流駆動能力の大きい電圧降下回路(以下アクティブ用VDCという)50と、外部クロック信号を受けて動作周波数に応じてアクティブ用VDC50の電流駆動能力を調整するための制御信号を生成する駆動能力制御回路60とを備える。

[0039]

電圧降下回路10は、外部電源配線70よりE×t.Vccを受けて、Int.Vccに変換し、内部電源配線80に供給する。

[0040]

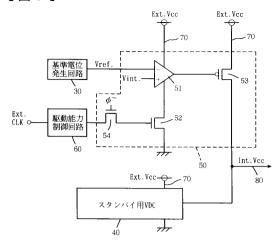

図3は、図2のアクティブ用VDC50の構成をより詳細に示すブロック図である。

[0041]

図3を参照して、スタンバイ用 V D C 4 0 は、構成および動作とも図11で説明した待機時用 V D C 4 1 0 と同様である。

[0042]

また、アクティブ用 V D C 5 0 の基本的な構成および動作は、図 1 2 における活性時用 V D C 4 0 0 と同一である。

[0043]

すなわち、活性時用 V D C 4 0 0 におけるカレントミラータイプの差動増幅器 4 0 5 は、 差動増幅器 5 1 に対応し、電流制御トランジスタ 4 0 6 およびドライバトランジスタ 4 0 7 は、それぞれトランジスタ 5 2 および 5 3 に相当する。

[0044]

アクティブ用 V D C 5 0 は、活性時用 V D C 4 0 0 に加えて駆動能力制御回路 6 0 および動作選択トランジスタ 5 4 をさらに備える。

[0045]

動作選択トランジスタ54は、ゲートに活性化信号 を受けて飽和領域で動作する。すな

10

20

30

わち、動作選択トランジスタ54は活性化時に導通し、待機時には非導通となる。

# [0046]

駆動能力制御回路 6 0 は、外部クロック信号を受けて制御信号を出力する。この制御信号は、動作周波数に応じたレベルの直流電圧を有する。

# [0047]

これにより、活性化時においては、動作周波数に応じた制御信号が電流駆動トランジスタ52のゲートに与えられる。ここで制御信号は、電流駆動トランジスタ52を線形領域で動作させるレベルとなるように設定される。

#### [0048]

よって、電流駆動トランジスタ52が差動増幅器51に供給する電流は、動作周波数に応じて決定される。供給される電流が大きいほど、差動増幅器51の応答速度が向上し、アクティブ用VDC50の電流駆動能力は大きくなる。

#### [0049]

すなわち、動作周波数に応じて電流駆動能力を調整することが可能な、アクティブ用 V D C 5 0 が得られる。

#### [0050]

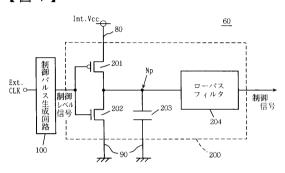

図4は、図3の駆動能力制御回路60の構成を詳細に示す概略ブロック図である。

### [0051]

図4を参照して、駆動能力制御回路60は、外部クロック信号を受けて制御パルスを生成する制御パルス生成回路100と、制御パルスを受けて制御信号を生成する制御信号生成回路200とを備える。

#### [0052]

駆動能力制御回路60の動作を説明するために、まず制御パルス信号について説明する。

#### [0053]

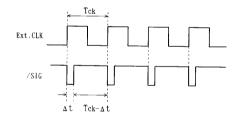

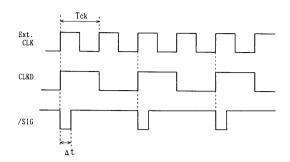

図5は、制御パルス信号について説明するための波形図である。

図 5 を参照して、外部クロック(以下 E x t . C L K という)は、外部より入力されるクロック信号である。

# [0054]

Ext.CLKは、動作周波数に対応した信号であり、その周期はTckである。Ext.CLKに基づいて、制御パルス(以下/SIG信号という)が作られる。

#### [0055]

/ SIG信号は、Ext. CLKの立上がリタイミングで一定期間 tの間だけ "L"レベルとなり、その他の期間は "H"レベルとなる。

### [0056]

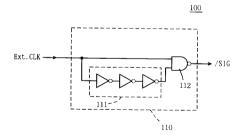

図 6 は、 E x t . C L K により / S I G 信号を生成する制御パルス生成回路 1 0 0 の構成の具体例である。

# [0057]

Ext. CLKは、インバータ列111によって反転され、かつ一定期間 tだけ遅延される。インバータ列111によって反転、遅延されたExt. CLKと、元のExt. CLKとをNANDゲート112に入力することにより、上記の / SIG信号を得ることができる。

# [0058]

次に、制御信号生成回路200の動作を説明する。

再び図4を参照して、制御信号生成回路は、ソースが内部電源配線80と結合するP型トランジスタ201と、P型トランジスタ201のドレインと結合するノードNpと、ノードNpと接地配線90との間に結合されるN型トランジスタ202とを有する。

# [0059]

さらに制御信号生成回路200は、ノードNpと接地電位配線90との間に接続されたキャパシタ203と、ノードNpの電位Vpを平滑して制御信号を出力するローパスフィルタ204とを有する。

10

20

30

•

40

#### [0060]

すなわち、ノードNpの電位Vpによって制御信号のレベルが決定される。 よって制御信号は、キャパシタ203に蓄えられた電荷量によって決定される。

#### [0061]

P型トランジスタ 2 0 1 および N 型トランジスタ 2 0 2 のゲートには、上記 / S I G 信号が与えられる。 P 型トランジスタ 2 0 1 もしくは N 型トランジスタ 2 0 2 は、 / S I G 信号の " L ", " H " レベルに応じて導通し、これに伴ってキャパシタ 2 0 3 は充放電される。キャパシタ 2 0 3 に蓄えられる電荷量に応じて、 ノード N p の電位 V p も変化する。

# [0062]

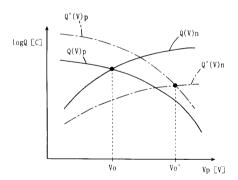

図 7 は、ノード N p の電位 V p とキャパシタ 2 0 3 へ充電あるいは放電される電荷量との 10 関係を示すための概念図である。

#### [0063]

図 7 を参照して、 Q ( v ) p は P 型 トランジスタ 2 0 1 を通じてキャパシタ 2 0 3 に充電される電荷量であり、 Q ( v ) n は N 型 トランジスタ 2 0 2 を通じてキャパシタ 2 0 3 から放電される電荷量である。

#### [0064]

一定の / S I G 信号が与えられた下では、充電量 Q ( v ) p と放電量 Q ( v ) n は、釣り合った状態で平衡する。

# [0065]

すなわち、ノードNpの電圧Vpは、図7の曲線で求められるように下式(1)が成り立 つ電位 voで平衡する。

#### [0066]

Q(vo)p = Q(vo)n ...(1)

# [0067]

ids(vo)px t=ids(vo)<u>n</u>x(Tck-t) ...(2) /SIG信号は、"L"レベルの期間が t、"H"レベルの期間がTck-tの比率を持つ信号である。/SIG信号は"L"レベルとなる期間 tは、図6のインバータ列111によって発生する遅延時間に等しく、 tはExt.CLKの周期によらず一定である。

# [0068]

よって、 $E \times t$  .  $C \setminus K$  の周期が小さい、すなわち動作周波数が高い場合には、 $/S \setminus G$  信号の " $\cup$ " レベルとなる期間の比率が大きくなる。

# [0069]

この場合、式(2)において平衡状態のノードNpの電位Vpが変化する。

このように動作周波数が高くなった場合における、 P 型トランジスタ 2 0 1 からの充電量  $^{40}$  を Q ( v ) p , N 型トランジスタ 2 0 2 からの放電量を Q ( v ) n として、 J ード N p の電位 V p の変化を考える。

# [0070]

再び図 7 を参照して、一点鎖線で示された上記 Q (v) p および Q (v) n を、先に説明した Q (v) p および Q (v) n と比較する。

# [0071]

動作周波数が高くなったことにより、P型トランジスタ201の導通する時間の割合が増加するので、Q (v)pは、Q(v)pより大きい値となる。逆に、Q (v)nはQ(v)nより小さい値となる。よって、ノードNpの電位Vpは、voより高い電位voで平衡する。この結果、制御信号のレベルは大きくなる。

20

30

### [0072]

一方、動作周波数が低くなった場合には、/SIG信号における"L"レベル期間の割 合が小さくなるため、キャパシタ203の充電量は低下し、放電量が増加する。

この結果、ノードNpの電位Vpはより低い電圧で平衡する。よって制御信号のレベルは 小さくなる。

#### [0074]

以上の様な動作によって、駆動能力制御回路60は、動作周波数に応じてレベルが変化す る直流電圧を有する制御信号を生成することができる。

#### [0075]

線型領域で動作する電流駆動トランジスタ52は、制御信号に対応した電流を、差動増幅 手段51に供給する。これにより、アクティブ用VDC50の電流駆動能力が制御される

# [0076]

このように、アクティブ用VDC50は、高い応答特性が要求される高速動作時には、電 流駆動能力を大きくする一方で、応答特性が必要とされない低速動作時には、電流駆動能 力を小さくすることにより消費電流の増大を防ぐ。

### [0077]

すなわち、アクティブ用VDC50を備える半導体集積回路装置1000は、組込まれる システムに応じて電圧降下回路の設計を変形することなく、幅広い動作周波数の下で適正 な応答特性を消費電力を無用に増大させることなく確保することができる。

#### [0078]

また、動作周波数が変化するシステムに組込まれた場合にも、消費電力を抑制すると同時 に、常に必要な応答特性を自動的に得ることができる。

#### [0079]

制御信号生成回路200において、P型トランジスタ201を通じてキャパシタ203 に電流を供給する電源配線の電位が変動すると、同一の/SIG信号の下でもキャパシタ 203に蓄えられる電荷量すなわちノードNpの電位Vpが変動する。

#### [0800]

したがって、動作周波数に応じて安定したレベルを持つ制御信号を得るためには、より電 位の変動の少ない電源を用いることが必要である。

# [0081]

よって、実施の形態1において、制御信号生成回路200は、外部電源配線ではなく、内 部電源配線によって駆動されている。

# [0082]

# 「実施の形態21

実施の形態1では、制御パルス生成回路100において、Ext.CLKから/SIG信 号を生成した。実施の形態2においては、/SIG信号の生成にあたってExt.CLK を分周した信号を用いる。

### [0083]

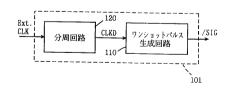

図8は、実施の形態2における制御パルス生成回路101の構成を示すブロック図である

#### [0084]

図8を参照して、制御パルス生成回路101は、実施の形態1の制御パルス生成回路10 0と同一の構成であるワンショットパルス生成回路110に加えて、分周回路120をさ らに備える。

#### [0085]

図9は、図8の制御パルス生成回路101の動作を説明するための波形図である。

# [0086]

図8および図9を参照して、分周回路120は、外部クロック信号であるExt.CLK

10

20

30

40

を受けて、2分周された信号 CLKDを出力する。CLKDはワンショットパルス生成回路 1 1 0 に与えられる。ワンショットパルス生成回路 1 1 0 の動作は、図 6 に示した制御パルス生成回路 1 0 0 と同一であり、CLKD信号のパルス立上がり時に一定期間 tだけ"L"レベルを有する / SIG信号が生成される。

# [0087]

上述したように、<u>/</u>SIG信号の t期間はインバータ列111によって生成される遅延時間に相当するため、上記 t期間はインバータ列111を構成するトランジスタの特性値に依存して決定される。

# [0088]

よって、製造プロセスのばらつきによって、インバータ列111を構成するトランジスタの特性が変動した場合には、/SIG信号の t期間も影響を受けて変動する。

#### [0089]

よって、動作周波数に応じて電流駆動能力の制御を正確に行なうことが困難になる。動作周波数が高くなるほど、/SIG信号のパルス間隔は狭くなるため、トランジスタ特性の変動の影響は大きくなる。

#### [0090]

ここで、Ext.CLKを分周して得られるCLKDに基づいて/SIG信号を作成することにより、動作周波数が高い場合にも広いパルス間隔を確保することが可能となる。

#### [0091]

これにより、制御パルス生成回路101は、トランジスタの特性の変動が t期間に及ぼす影響の小さい、/SIG信号を得ることができる。

#### [0092]

すなわち、実施の形態 2 の構成の電圧降下回路は、動作周波数が高い場合にもインバータ列 1 1 1 を構成するトランジスタの特性のばらつきの影響を軽減して制御パルス信号を得ることができ、広い動作周波数の下で安定した電流駆動能力の制御を行なうことができる

### [0093]

なお分周器を複数用いることによって、4分周や8分周を設定することも可能である。

# [0094]

# [実施の形態3]

実施の形態 1 では、制御信号生成回路 2 0 0 は、内部電源配線 8 0 によって駆動されていたが、実施の形態 3 では、制御信号生成回路 2 0 0 を駆動するために、専用の V D C を設ける。

### [0095]

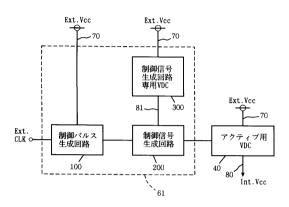

図10は、実施の形態3における駆動能力制御回路61の構成を示すブロック図である。

#### [0096]

図10を参照して、駆動能力制御回路61は、実施の形態1の駆動能力制御回路60の構成に加えて、制御信号生成回路専用VDC300をさらに備える。

#### [0097]

制御信号生成回路 6 1 は、内部電源配線 8 0 より独立した専用内部電源配線 8 1 によって 40 、制御信号生成回路専用 V D C 3 0 0 から電源電位を供給される。

#### [0098]

先に述べたように、制御信号生成回路 2 0 0 を駆動する電源電位の安定性は、得られる制御信号の安定性に大きな影響を及ぼす。よって、実施の形態 3 の構成とすることにより、内部回路群で消費される負荷電流の影響により内部電源配線 8 0 の電位 I n t . V c c が不安定なレベルとなった場合にも、安定した制御信号を生成することができる。

#### [0099]

すなわち、Int.Vccレベルの変動に対して、より的確にフィードバックを施すことができ、より安定した電流駆動能力の制御性を有するVDCを得ることができる。

# [0100]

50

10

20

制御信号生成回路専用VDC300は、図12で示す従来の構成あるいは、図3で示す本発明の構成のいずれによっても実現される。

#### [0 1 0 1]

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

# [0102]

# 【発明の効果】

請求項1,2,3記載の半導体集積回路装置は、動作周波数によって電流駆動能力を制御することができる電圧降下回路を備えている。したがって、幅広い動作周波数の下で、動作周波数に応じた適正な電圧応答特性を、消費電力を無用に増大させることなく確保することができる。

# [0103]

請求項4記載の半導体集積回路装置は、請求項3記載の半導体集積回路装置が奏する効果を、制御回路を構成するトランジスタの製造ばらつきによる影響を軽減し、広い動作周波数の下で安定して得ることができる。

### [0104]

請求項5記載の半導体集積回路装置は、請求項3ないし4に記載の半導体集積回路装置が奏する効果に加えて、内部電源電位の変動をより安定的に制御することができる。

【図面の簡単な説明】

- 【図1】 本発明の実施の形態の半導体集積回路装置1000の全体構成を示す概略プロック図である。

- 【図2】 図1の電圧降下回路10の構成をより詳細に示すプロック図である。

- 【図3】 図2のアクティブ用 V D C 5 0 の構成をより詳細に示すためのブロック図である。

- 【図4】 図3の駆動能力制御回路60の構成を詳細に示すための概略ブロック図である

- 【図5】 制御パルス信号について説明するための波形図である。

- 【図6】 制御パルス生成回路100の構成の一例を示す概略図である。

- 【図7】 ノードNpの電位とキャパシタ103への充放電電荷量の関係を示す概念図である。

- 【図8】 実施の形態2における制御パルス生成回路101の構成を示す概略ブロック図である。

- 【図9】 制御パルス生成回路101の動作を説明するための波形図である。

- 【図10】 実施の形態3における駆動能力制御回路61の構成を示す概略ブロック図である。

- 【図11】 従来の電圧降下回路の一般的な構成を示す概略ブロック図である。

- 【図12】 複数の電圧降下部を含む従来の技術の電圧降下回路2000 の構成を示す回路図である。

# 【符号の説明】

1 0 電圧降下回路、 2 0 内部回路群、 2 1 周辺回路、 2 2 アレイ制御回路、 2 3 メモリアレイ、 2 5 入出力回路、 3 0 基準電位発生回路、 4 0 スタンバイ用 V D C 、 5 0 アクティブ用 V D C 、 5 1 差動増幅器、 5 2 電流制御トランジスタ、 5 3 ドライバトランジスタ、 5 4 動作選択トランジスタ、 6 0 , 6 1 駆動能力制御回路、 7 0 外部電源配線、 8 0 , 8 1 内部電源配線、 9 0 接地配線、 1 0 0 , 1 0 1 制御パルス生成回路、 1 1 0 ワンショットパルス生成回路、 1 1 インバータ列、 1 1 2 N A N D ゲート、 1 2 0 分周回路、 2 0 0 制御信号生成回路、 2 0 1 , 2 0 2 トランジスタ、 2 0 3 キャパシタ、 2 0 4 ローパスフィルタ、 3 0 0 制御信号生成回路 路専用 V D C。

10

20

30

40

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

# 【図6】

# 【図7】

【図8】

# 【図9】

# 【図10】

# 【図11】

【図12】

# フロントページの続き

(72)発明者 小林 真子 兵庫県伊丹市荻野 1 丁目 1 3 2 番地 大王電機株式会社内

(72)発明者 森下 玄 東京都千代田区丸の内二丁目 2 番 3 号 三菱電機株式会社内

審査官 堀田 和義

(56)参考文献 特開平8-190437(JP,A) 特開平9-293789(JP,A) 特開平10-269768(JP,A)

(58)調査した分野(Int.CI., DB名) G11C 11/4074